# Quad-SHARC® DSP Multiprocessor Family

# AD14060/AD14060L

### PERFORMANCE FEATURES

ADSP-21060 Core Processor (... ×4)

480 MFLOPS Peak, 320 MFLOPS Sustained

25 ns Instruction Rate, Single-Cycle

Instruction Execution-Each of Four Processors

16 Mbit Shared SRAM (Internal to SHARCs)

4 Gigawords Addressable Off-Module Memory

Twelve 40 Mbyte/s Link Ports (Three per SHARC)

Four 40 Mbit/s Independent Serial Ports (One from Each SHARC)

One 40 Mbit/s Common Serial Port 5 V and 3.3 V Operation 32-Bit Single Precision and 40-Bit Extended Precision IEEE Floating Point Data Formats, or 32-Bit Fixed Point Data Format IEEE JTAG Standard 1149.1 Test Access Port and

# On-Chip Emulation PACKAGING FEATURES

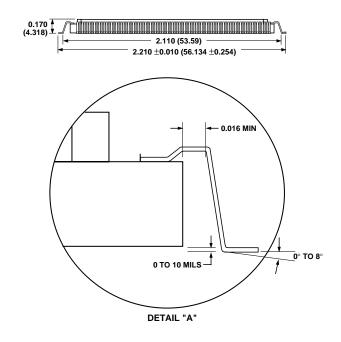

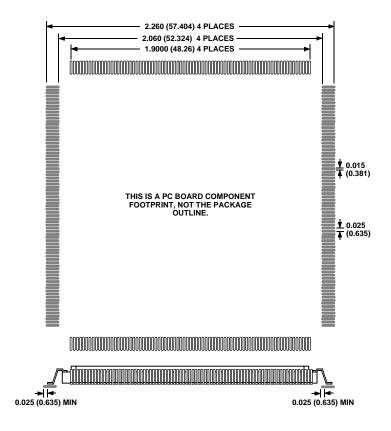

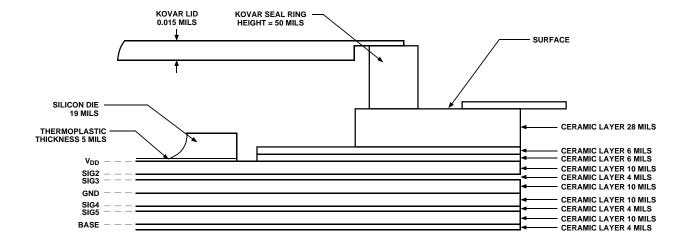

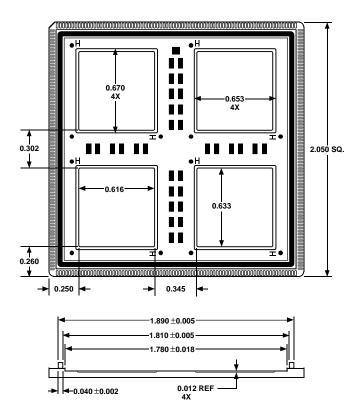

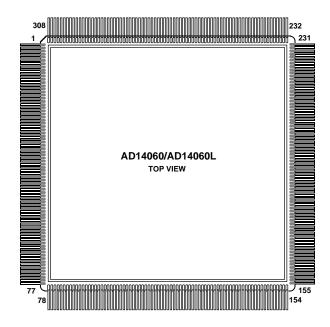

308-Lead Ceramic Quad Flatpack (CQFP) 2.05" (52 mm) Body Size Cavity Up or Down, Configurable Low Profile, 0.160" Height Hermetic 25 Mil (0.65 mm) Lead Pitch 29 Grams (typical)  $\theta_{JC} = 0.36$ °C/W

### **GENERAL DESCRIPTION**

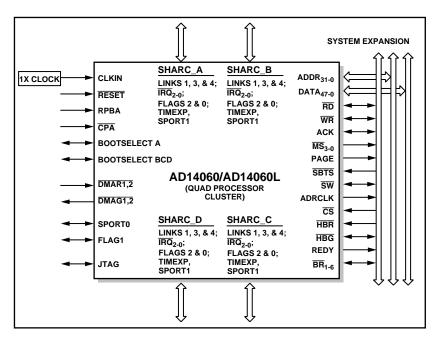

The AD14060/AD14060L Quad-SHARC is the first in a family of high performance DSP multiprocessor modules. The core of the multiprocessor is the ADSP-21060 DSP microcomputer. The AD14060/AD14060L modules have the highest performance —density and lowest cost—performance ratios of any in their class. They are ideal for applications requiring higher levels of performance and/or functionality per unit area.

The AD14060/AD14060L takes advantage of the built-in multi-processing features of the ADSP-21060 to achieve 480 peak MFLOPS with a single chip type, in a single package. The on-chip SRAM of the DSPs provides 16 Mbits of on-module shared SRAM. The complete shared bus (48 data, 32 address) is also brought off-module for interfacing with expansion memory or other peripherals.

SHARC is a registered trademark of Analog Devices, Inc.

### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

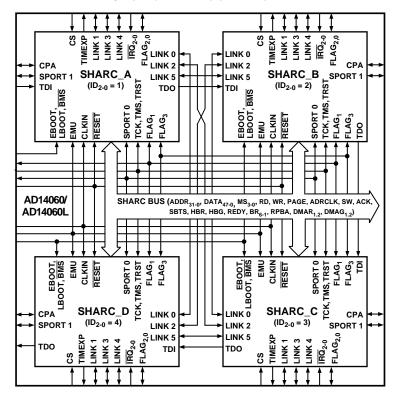

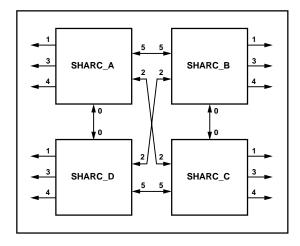

### FUNCTIONAL BLOCK DIAGRAM

The ADSP-21060 link ports are interconnected to provide direct communication among the four SHARCs as well as high speed off-module access. Internally, each SHARC has a direct link port connection. Externally, each SHARC has a total of 120 Mbytes/s link port bandwidth.

Multiprocessor performance is enhanced with embedded power and ground planes, matched impedance interconnect, and optimized signal routing lengths and separation. The fully tested and ready-to-insert multiprocessor also significantly reduces board space.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site: http://www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 1997

### DETAILED DESCRIPTION Architectural Features ADSP-21060 Core

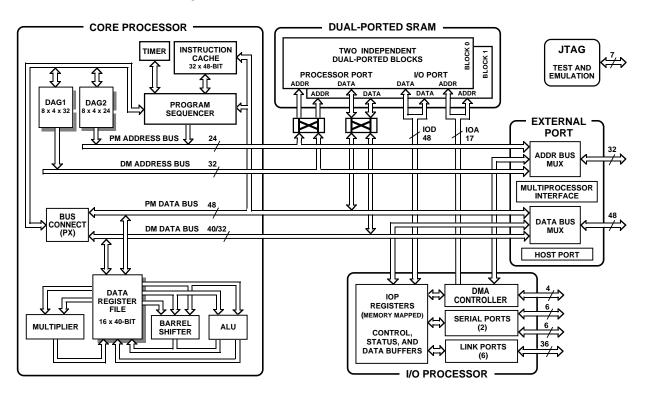

The AD14060/AD14060L is based on the powerful ADSP-21060 (SHARC) DSP chip. The ADSP-21060 SHARC combines a high performance floating-point DSP core with integrated, on-chip system features including a 4 Mbit SRAM memory, host processor interface, DMA controller, serial ports, and both link port and parallel bus connectivity for glueless DSP multiprocessing, (see Figure 1). It is fabricated in a high speed, low power CMOS process, and has a 25 ns instruction cycle time. The arithmetic/ logic unit (ALU), multiplier and shifter all perform single-cycle instructions, and the three units are arranged in parallel, maximizing computational throughput.

The SHARC features an enhanced Harvard architecture in which the data memory (DM) bus transfers data, and the program memory (PM) bus transfers both instructions and data. There is also an on-chip instruction cache which selectively caches only those instructions whose fetches conflict with the PM bus data accesses. This combines with the separate program and data memory buses to enable three-bus operation for fetching an instruction and two operands, all in a single cycle. The SHARC also contains a general purpose data register file, which is a 10-port, 32-register (16 primary, 16 secondary) file. Each SHARC's core also implements two data address generators (DAGs), implementing circular data buffers in hardware. The DAGs contain sufficient registers to allow the creation of up to 32 circular buffers. The 48-bit instruction word accommodates a variety of parallel operations, for concise programming. For example, the ADSP-21060 can conditionally execute a multiply, an add, a subtract, and a branch, all in a single instruction.

The SHARCs contain 4 Mbits of on-chip SRAM each, organized as two blocks of 2 Mbits, which can be configured for different combinations of code and data storage. The memory can be configured as a maximum of 128K words of 32-bit data, 256K words of 16-bit data, 80K words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to 4 megabits. A 16-bit floating-point storage format is supported which effectively doubles the amount of data that may be stored on chip. Conversion between the 32-bit floating point and 16-bit floating point formats is done in a single instruction. Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor or DMA controller. The dual-ported memory and separate on-chip buses allow two data transfers from the core and one from I/O, all in a single cycle.

### **Shared Memory Multiprocessing**

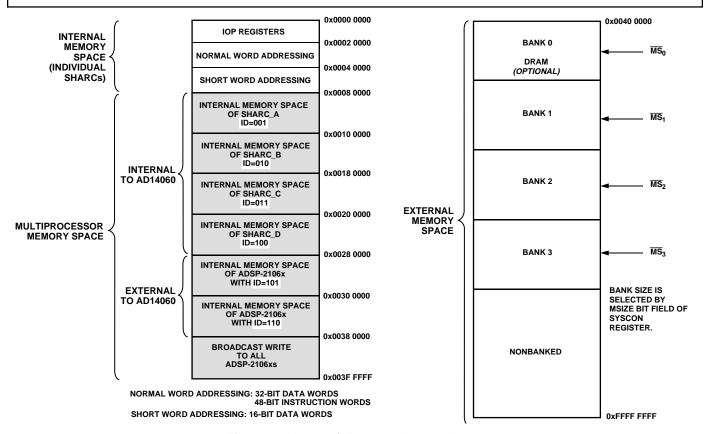

The AD14060/AD14060L takes advantage of the powerful multiprocessing features built into the SHARC. The SHARCs are connected to maximize the performance of this cluster-of-four architecture, and still allow for off-module expansion. The AD14060/AD14060L in itself is a complete shared memory multiprocessing system, as shown in Figure 3. The unified address space of the SHARCs allows direct interprocessor accesses of each SHARCs' internal memory. In other words, each SHARC can directly access the internal memory and IOP registers of each of the other SHARCs by simply reading or writing to the appropriate address in multiprocessor memory space (see Figure 2)—this is called a *direct read or direct write*.

Figure 1. ADSP-21060 Processor Block Diagram (Core of the AD14060)

-2- REV. A

Figure 2. AD14060/AD14060L Memory Map

Figure 3. Complete Shared Memory Multiprocessing System

REV. A \_3\_

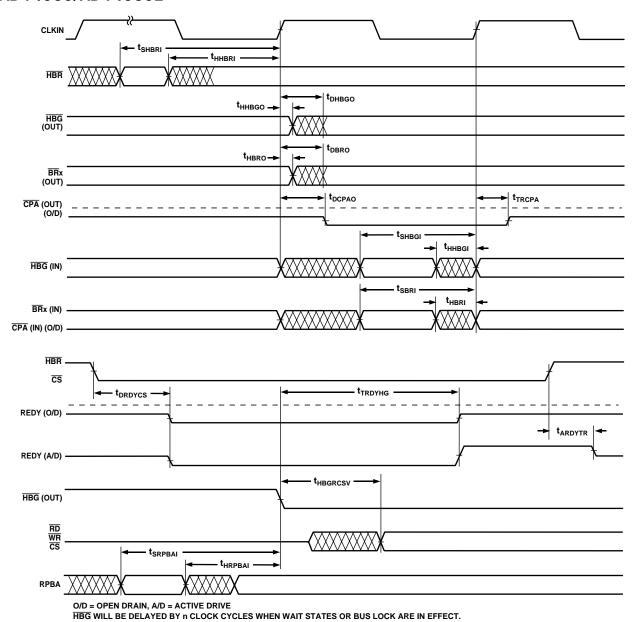

Bus arbitration is accomplished with the on-SHARC arbitration logic. Each SHARC has a unique ID, and drives the Bus-Request (BR) line corresponding to its ID, while monitoring all others.  $\overline{BR}1-\overline{BR}4$  are used within the AD14060/AD14060L, while  $\overline{BR}5$  and  $\overline{BR}6$  can be used for expansion. All bus requests ( $\overline{BR}1-\overline{BR}6$ ) are included in the module I/O.

Two different priority schemes, fixed and rotating, are available to resolve competing bus requests. The RPBA pin selects which scheme is used: when RPBA is high, rotating priority bus arbitration is selected, and when RPBA is low, fixed priority is selected.

**Table I. Rotating Priority Arbitration Example**

|       |      | Hard |      |     |     |      |                              |

|-------|------|------|------|-----|-----|------|------------------------------|

| Cycle | ID1  | ID2  | ID3  | ID4 | ID5 | ID6  |                              |

| 1     | M    | 1    | 2 BR | 3   | 4   | 5    | Initial Priority Assignments |

| 2     | 4    | 5 BR | M-BR | 1   | 2   | 3    |                              |

| 3     | 4    | 5 BR | M    | 1   | 2   | 3    |                              |

| 4     | 5 BR | M    | 1    | 2   | 3   | 4 BR |                              |

| 5     | 1 BR | 2    | 3    | 4   | 5   | M    | Final Priority Assignments   |

NOTES

1-5 = Assigned Priority.

M = Bus Mastership (in that cycle).

BR = Requesting Bus Mastership with BRx.

Bus mastership is passed from one SHARC to another during a bus transition cycle. A bus transition cycle only occurs when the current bus master deasserts its BR line and one of the slave SHARCs asserts its BR line. The bus master can therefore retain bus mastership by keeping its BR line asserted. When the bus master deasserts its BR line, and no other BR line is asserted, then the master will not lose any bus cycles. When more than one SHARC asserts its BR line, the SHARC with the highest priority request becomes bus master on the following cycle. Each SHARC observes all of the BR lines, and therefore tracks when a bus transition cycle has occurred, and which processor has become the new bus master. Master processor changeover incurs only one cycle of overhead. An example bus transition sequence is shown in Table I.

Bus locking is possible, allowing indivisible read-modify-write sequences for semaphores. In either the fixed or rotating priority scheme, it is also possible to limit the number of cycles the master can control the bus. The AD14060/AD14060L also provides the option of using the Core Priority Access (CPA) mode of the SHARC. Using the CPA signal allows external bus accesses by the core processor of a slave SHARC to take priority over ongoing DMA transfers. Also, each SHARC can broadcast write to all other SHARCs simultaneously, allowing the implementation of reflective semaphores.

The bus master can communicate with slave SHARCs by writing messages to their internal IOP registers. The MSRG0–MSRG7 registers are general-purpose registers that can be used for convenient message passing, semaphores and resource sharing between the SHARCs. For message passing, the master communicates with a slave by writing and/or reading any of the eight message registers on the slave. For vector interrupts, the master can issue a vector interrupt to a slave by writing the address of an interrupt service routine to the slave's VIRPT register. This causes an immediate high priority interrupt on the slave which, when serviced, will cause it to branch to the specified service routine.

### **Off-Module Memory and Peripherals Interface**

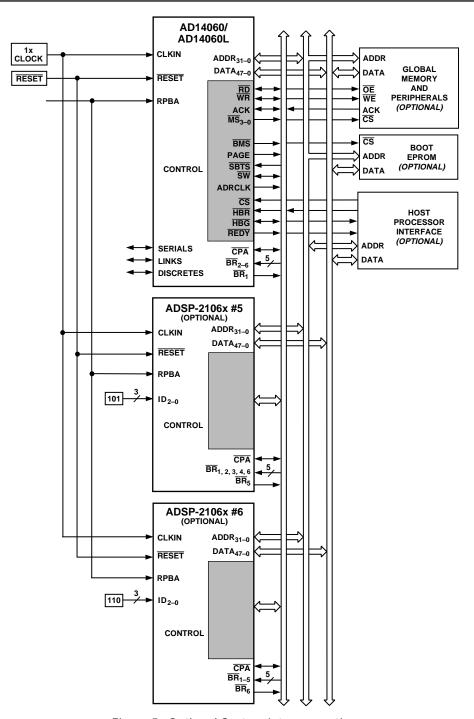

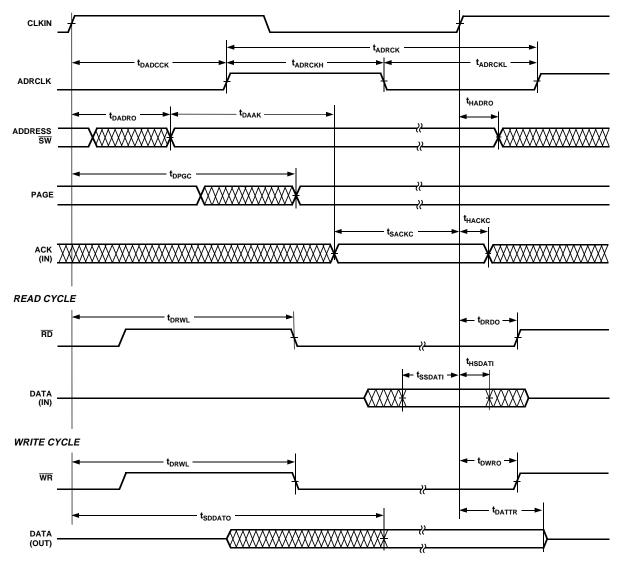

The AD14060/AD14060L's external port provides the interface to

off-module memory and peripherals (see Figure 5). This port consists of the complete external port bus of the SHARC, bused together in common among the four SHARCs.

The 4-gigaword off-module address space is included in the ADSP-14060's unified address space. Addressing of external memory devices is facilitated by each SHARC internally decoding the high order address lines to generate memory bank select signals. Separate control lines are also generated for simplified addressing of page-mode DRAM. The AD14060/ AD14060L also supports programmable memory wait states and external memory acknowledge controls to allow interfacing to DRAM and peripherals with variable access, hold and disable time requirements.

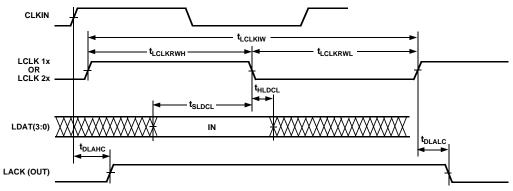

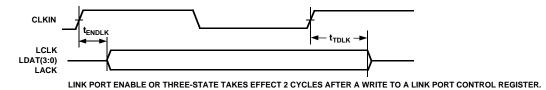

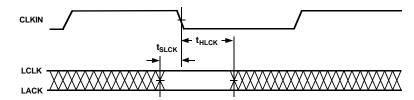

### Link Port I/O

Each individual SHARC features six 4-bit link ports that facilitate SHARC-to-SHARC communication and external I/O interfacing. Each link port can be configured for either  $1\times$  or  $2\times$  operation, allowing each to transfer either 4 or 8 bits per cycle. The link ports can operate independently and simultaneously, with a maximum bandwidth of 40 MBytes/s each, or a total of 240 MBytes/s per SHARC.

The AD14060/AD14060L optimizes the link port connections internally, and brings a total of twelve of the link ports off-module for user-defined system connections. Internally, each SHARC has a connection to the other three SHARCs with a dedicated link port interface. Thus, each SHARC can directly interface with its nearest and next-nearest neighbor. The remaining three link ports from each SHARC are brought out independently from each SHARC. A maximum of 480 MBytes/s link port bandwidth is then available off of the AD14060/AD14060L. The link port connections are detailed in Figure 4.

Figure 4. Link Port Connections

Link port 4, the boot link port, is brought off independently from each SHARC. Individual booting is then allowed, or chained link port booting is possible as described under "Link Port Booting."

Link port data is packed into 32-bit or 48-bit words, and can be directly read by the SHARC core processor or DMA-transferred to on-SHARC memory.

Each link port has its own double-buffered input and output registers. Clock/acknowledge handshaking controls link port transfers. Transfers are programmable as either transmit or receive.

Figure 5. Optional System Interconnections

REV. A -5-

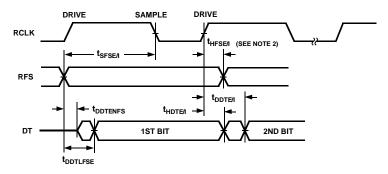

### **Serial Ports**

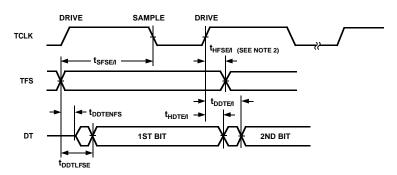

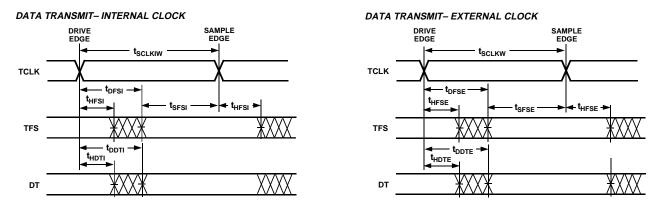

The SHARC serial ports provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. Each SHARC has two serial ports. The AD14060/AD14060L provides direct access to Serial Port 1 of each SHARC. Serial Port 0 is bused together in common to each SHARC, and brought off-module.

The serial ports can operate at the full clock rate of the module, providing each with a maximum data rate of 40 Mbit/s. Independent transmit and receive functions provide more flexible communications. Serial port data can be automatically transferred to and from on-SHARC memory via DMA, and each of the serial ports offers time division multiplexed (TDM) multichannel mode.

The serial ports can operate with little-endian or big-endian transmission formats, with word lengths selectable from 3 bits to 32 bits. They offer selectable synchronization and transmit modes as well as optional  $\mu$ -law or A-law companding. Serial port clocks and frame syncs can be internally or externally generated.

### **Program Booting**

The AD14060/AD14060L supports automatic downloading of programs following power-up or a software reset. The SHARC offers four options for program booting: 1) from an 8-bit EPROM; 2) from a host processor; 3) through the link ports; and 4) no-boot. In no-boot mode, the SHARC starts executing instructions from address 0x0040 0004 in external memory. The boot mode is selected by the state of the following signals: BMS, EBOOT, and LBOOT.

On the AD14060/AD14060L, SHARC\_A's boot mode is separately controlled, while SHARCs B, C, and D are controlled as a group. With this flexibility, the AD14060/AD14060L can be configured to boot in any of the following methods.

### **Multiprocessor Host Booting**

To boot multiple ADSP-21060 processors from a host, each ADSP-21060 must have its EBOOT, LBOOT and BMS pins configured for host booting: EBOOT = 0, LBOOT = 0, and BMS = 1. After system power-up, each ADSP-21060 will be in the idle state and the  $\overline{BRx}$  bus request lines will be deasserted. The host must assert the  $\overline{HBR}$  input and boot each ADSP-21060 by asserting its CS pin and downloading instructions.

### **Multiprocessor EPROM Booting**

There are two methods of booting the multiprocessor system from an EPROM.

SHARC\_A Is Booted, Which Then Boots the Others. The EBOOT pin on the SHARC\_A must be set high for EPROM booting. All other ADSP-21060s should be configured for host booting (EBOOT = 0, LBOOT = 0, and BMS = 1), which leaves them in the idle state at start-up and allows SHARC\_A to become bus master and boot itself. Only the BMS pin of SHARC\_A is connected to the chip select of the EPROM. When SHARC\_A has finished booting, it can boot the remaining ADSP-21060s by writing to their external port DMA buffer 0 (EPB0) via multiprocessor memory space.

All ADSP-21060s Boot in Turn From a Single EPROM. The BMS signals from each ADSP-21060 may be wire-ORed together to drive the chip select pin of the EPROM. Each ADSP-21060 can boot in turn, according to its priority. When the last one has finished booting, it must inform the others (which may be in the idle state) that program execution can begin.

### Multiprocessor Link Port Booting

Booting can also be accomplished from a single source through the link ports. Link Buffer 4 must always be used for booting. To simultaneously boot all of the ADSP-21060s, a parallel common connection is available through Link Port 4 on each of the processors. Or, using the daisy chain connection that exists between the processors' link ports, each ADSP-21060 can boot the next one in turn. In this case, the Link Assignment Register (LAR) must be programmed to configure the internal link ports with Link Buffer 4.

### Multiprocessor Booting From External Memory

If external memory contains a program after reset, then SHARC\_A should be set up for *no boot* mode; it will begin executing from address 0x0040 0004 in external memory. When booting has completed, the other ADSP-21060s may be booted by SHARC\_A if they are set up for host booting, or they can begin executing out of external memory if they are set up for *no boot* mode. Multiprocessor bus arbitration will allow this booting to occur in an orderly manner.

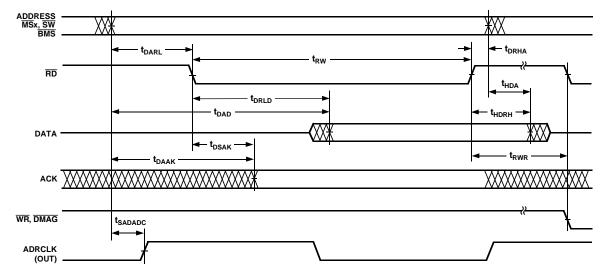

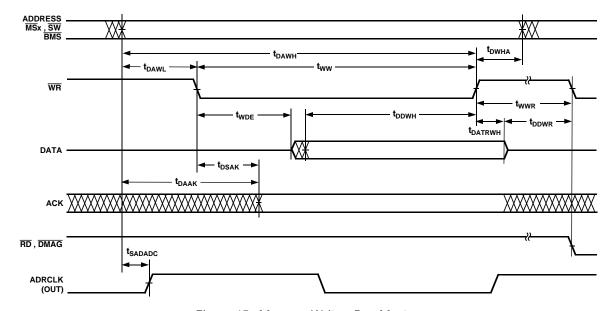

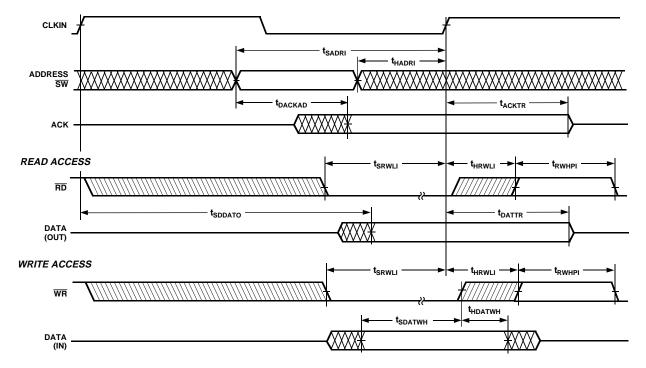

### **Host Processor Interface**

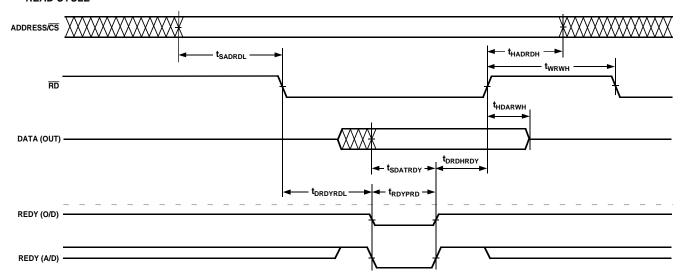

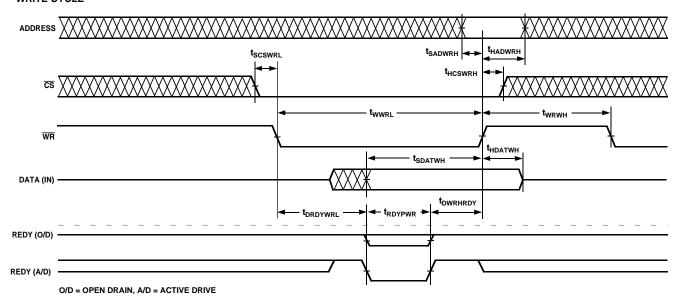

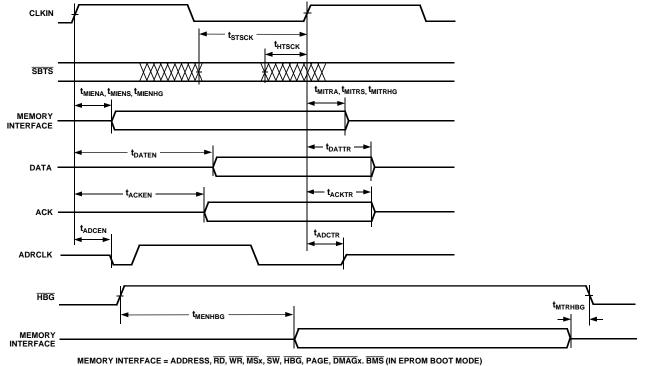

The AD14060/AD14060L's host interface allows for easy connection to standard microprocessor buses, both 16-bit and 32-bit, with little additional hardware required. Asynchronous transfers at speeds up to the full clock rate of the module are supported. The host interface is accessed through the AD14060/AD14060L external port and is memory-mapped into the unified address space. Four channels of DMA are available for the host interface; code and data transfers are accomplished with low software overhead.

The host processor requests the AD14060/AD14060L's external bus with the host bus request ( $\overline{HBR}$ ), host bus grant ( $\overline{HBG}$ ), and ready (REDY) signals. The host can directly read and write the internal memory of the SHARCs, and can access the DMA channel setup and mailbox registers. Vector interrupt support is provided for efficient execution of host commands.

### **Direct Memory Access (DMA) Controller**

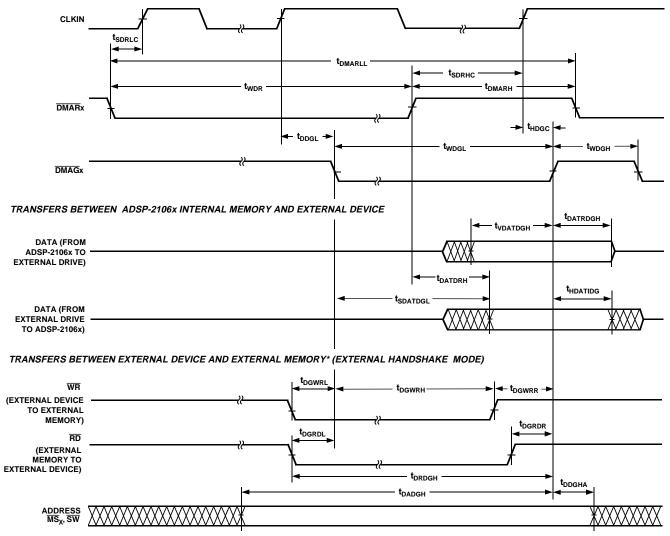

The SHARCs on-chip DMA control logic allows zero-overhead data transfers without processor intervention. The DMA controller operates independently and invisibly to each SHARCs processor core, allowing DMA operations to occur while the core is simultaneously executing its program instructions.

DMA transfers can occur between SHARC internal memory and either external memory, external peripherals, or a host processor. DMA transfers can also occur between the SHARC's internal memory and its serial ports or link ports. DMA transfers between external memory and external peripheral devices are another option. External bus packing to 16-, 32- or 48-bit words is performed during DMA transfers.

Ten channels of DMA are available on the SHARCs—two via the link ports, four via the serial ports, and four via the processor's external port (for either host processor, other SHARCs, memory, or I/O transfers). Four additional link port DMA channels are shared with serial port 1 and the external port. Programs can be downloaded to the SHARCs using DMA transfers. Asynchronous off-module peripherals can control two DMA channels using DMA Request/Grant lines (DMAR1-2, DMAG1-2). Other DMA features include interrupt generation upon completion of DMA transfers and DMA chaining for automatic linked DMA transfers.

-6- REV. A

### **Development Tools**

The ADSP-14060 is supported with a complete set of software and hardware development tools, including an EZ-LAB® In-Circuit Emulator, and development software.

Analog Devices' ADSP-21000 Family Development Software includes an easy to use Assembler based on an algebraic syntax, an Assembly Library/Librarian, a Linker, an Instruction-Level Simulator, an ANSI C optimizing Compiler, the CBug $^{\text{TM}}$  C Source-Level Debugger, and a C Runtime Library including DSP and mathematical functions. The Optimizing Compiler includes Numerical C extensions based on the work of the ANSI Numerical C Extensions Group. Numerical C provides extensions to the C language for array selection, vector math operations, complex data types, circular pointers and variably dimensioned arrays. The ADSP-21000 Family Development Software is available for both the PC and Sun platforms.

The SHARC EZ-KIT combines the ADSP-21000 Family Development Software for the PC and the EZ-LAB Development Board in one package.

The ADSP-2106x EZ-ICE® Emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-2106x processor to monitor and control the target board processor during emulation. The EZ-ICE provides full-speed emulation, allowing inspection and modification of memory, registers and processor stacks.

Nonintrusive in-circuit emulation is assured by the use of the processor's JTAG interface—the emulator does not affect target system loading or timing.

Further details and ordering information are available in the *ADSP-21000 Family Hardware & Software Development Tools* data sheet (ADDS-2100xx-TOOLS). This data sheet can be requested from any Analog Devices sales office or distributor, or from the Literature Center.

EZ-ICE and EZ-LAB are registered trademarks of Analog Devices, Inc. CBug is a trademark of Analog Devices, Inc.

In addition to the software and hardware development tools available from Analog Devices, third parties provide a wide range of tools supporting the SHARC processor family. Hardware tools include SHARC PC plug-in cards, multiprocessor SHARC VME boards, and daughter card modules with multiple SHARCs and additional memory. These modules are based on the SHARCPAC module specification. Third party software tools include an Ada compiler, DSP libraries, operating systems and block diagram design tools.

### **Quad-SHARC Development Board**

The BlackTip-MCM, AD14060 development board and software, is available from Bittware Research Systems, Inc. This board has one AD14060 BITSI interface, PROM and SRAM expansion options on an ISA card. It is supported by Bittware's SHARC software development package. Bittware can be contacted at 1-800-848-0436.

### **Other Package Details**

The AD14060/AD14060L contains 16 on-module 0.018 microfarad bypass capacitors. It is recommended that in the target system at least four additional capacitors, of 0.018 microfarad value, be placed around the module—one near each of the four corners.

The top surface, lid, of the AD14060/AD14060L is electrically connected to GND on the industrial and military grade parts.

### **Additional Information**

This data sheet provides a general overview of the AD14060/AD14060L architecture and functionality. For detailed information on the ADSP-2106x SHARC and the ADSP-21000 Family core architecture and instruction set, refer to the ADSP-2106x SHARC *User's Manual.*

REV. A -7-

### PIN FUNCTION DESCRIPTIONS

AD14060/AD14060L pin definitions are listed below. Inputs identified as synchronous (S) must meet timing requirements with respect to CLKIN (or with respect to TCK for TMS, TDI). Inputs identified as asynchronous (A) can be asserted asynchronously to CLKIN (or to TCK for  $\overline{TRST}$ ).

Unused inputs should be tied or pulled to  $V_{DD}$  or GND, except for ADDR<sub>31-0</sub>, DATA<sub>47-0</sub>, FLAG<sub>2-0</sub>,  $\overline{SW}$ , and inputs that have internal pull-up or pull-down resistors (CPA, ACK, DTx, DRx,

TCLKx, RCLKx, LxDAT<sub>3-0</sub>, LxCLK, LxACK, TMS and TDI)—these pins can be left floating. These pins have a logic-level hold circuit that prevents the input from floating internally.

$\begin{array}{ll} I = Input & P = Power \ Supply & (A/D) = Active \ Drive \\ O = Output & S = Synchronous & (O/D) = Open \ Drain \\ \end{array}$

G = Ground A = Asynchronous

T = Three-State (when  $\overline{SBTS}$  is asserted, or when the AD14060/AD14060L is a bus slave)

| Pin                      | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR <sub>31-0</sub>     | I/O/T | <b>External Bus Address.</b> (Common to all SHARCs) The AD14060/AD14060L outputs addresses for external memory and peripherals on these pins. In a multiprocessor system, the bus master outputs addresses for read/writes on the internal memory or IOP registers of slave ADSP-2106xs. The AD14060/AD14060L inputs addresses when a host processor or multiprocessing bus master is reading or writing the internal memory or IOP registers of internal ADSP-21060s.                                                                                                                                                                                                                                                                                                                                        |

| DATA <sub>47-0</sub>     | I/O/T | <b>External Bus Data</b> . (Common to all SHARCs) The AD14060/AD14060L inputs and outputs data and instructions on these pins. 32-bit single-precision floating-point data and 32-bit fixed-point data is transferred over bits 47-16 of the bus. 40-bit extended-precision floating-point data is transferred over bits 47-8 of the bus. 16-bit short word data is transferred over bits 31-16 of the bus. In PROM boot mode, 8-bit data is transferred over bits 23-16. Pull-up resistors on unused DATA pins are not necessary.                                                                                                                                                                                                                                                                            |

| <u>MS</u> <sub>3-0</sub> | O/T   | <b>Memory Select Lines.</b> (Common to all SHARCs) These lines are asserted (low) as chip selects for the corresponding banks of external memory. Memory bank size must be defined in the individual ADSP-21060's system control registers (SYSCON). The $\overline{\rm MS}_{3-0}$ lines are decoded memory address lines that change at the same time as the other address lines. When no external memory access is occurring the $\overline{\rm MS}_{3-0}$ lines are inactive; they are active, however, when a conditional memory access instruction is executed, whether or not the condition is true. $\overline{\rm MS}_0$ can be used with the PAGE signal to implement a bank of DRAM memory (Bank 0). In a multiprocessing system, the $\overline{\rm MS}_{3-0}$ lines are output by the bus master. |

| RD                       | I/O/T | <b>Memory Read Strobe.</b> (Common to all SHARCs) This pin is asserted (low) when the AD14060/AD14060L reads from external devices or when the internal memory of internal ADSP-2106xs is being accessed. External devices (including other ADSP-2106xs) must assert $\overline{\text{RD}}$ to read from the AD14060/AD14060L's internal memory. In a multiprocessing system, $\overline{\text{RD}}$ is output by the bus master and is input by all other ADSP-2106xs.                                                                                                                                                                                                                                                                                                                                       |

| WR                       | I/O/T | <b>Memory Write Strobe.</b> (Common to all SHARCs) This pin is asserted (low) when the AD14060/ AD14060L writes to external devices or when the internal memory of internal ADSP-2106xs is being accessed. External devices (including other ADSP-2106xs) must assert $\overline{WR}$ to write to the AD14060/ AD14060L's internal memory. In a multiprocessing system $\overline{WR}$ is output by the bus master and is input by all other ADSP-2106xs.                                                                                                                                                                                                                                                                                                                                                     |

| PAGE                     | O/T   | <b>DRAM Page Boundary.</b> (Common to all SHARCs) The AD14060/AD14060L asserts this pin to signal that an external DRAM page boundary has been crossed. DRAM page size must be defined in the individual ADSP-21060's memory control register (WAIT). DRAM can only be implemented in external memory Bank 0; the PAGE signal can only be activated for Bank 0 accesses. In a multiprocessing system, PAGE is output by the bus master.                                                                                                                                                                                                                                                                                                                                                                       |

| ADRCLK                   | O/T   | <b>Clock Output Reference.</b> (Common to all SHARCs) In a multiprocessing system, ADRCLK is output by the bus master.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SW                       | I/O/T | <b>Synchronous Write Select.</b> (Common to all SHARCs) This signal is used to interface the AD14060/AD14060L to synchronous memory devices (including other ADSP-2106xs). The AD14060/AD14060L asserts $\overline{SW}$ (low) to provide an early indication of an impending write cycle, which can be aborted if $\overline{WR}$ is not later asserted (e.g., in a conditional write instruction). In a multiprocessing system, $\overline{SW}$ is output by the bus master and is input by all other ADSP-2106xs to determine if the multiprocessor memory access is a read or write. $\overline{SW}$ is asserted at the same time as the address output. A host processor using synchronous writes must assert this pin when writing to the AD14060/AD14060L.                                              |

| ACK                      | I/O/S | <b>Memory Acknowledge.</b> (Common to all SHARCs) External devices can deassert ACK (low) to add wait states to an external memory access. ACK is used by I/O devices, memory controllers, or other peripherals to hold off completion of an external memory access. The AD14060/AD14060L deasserts ACK, as an output, to add wait states to a synchronous access of its internal memory. In a multiprocessing system, a slave ADSP-2106x deasserts the bus master's ACK input to add wait state(s) to an access of its internal memory. The bus master has a keeper latch on its ACK pin that maintains the input at the level it was last driven to.                                                                                                                                                        |

-8- REV. A

| Pin                     | Type  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-------------------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SBTS                    | I/S   | Suspend Bus Three-State. (Common to all SHARCs) External devices can assert \$\overline{SBTS}\$ (low) to place the external bus address, data, selects, and strobes in a high impedance state for the following cycle If the AD14060/AD14060L attempts to access external memory while \$\overline{SBTS}\$ is asserted, the processor will halt and the memory access will not be completed until \$\overline{SBTS}\$ is deasserted. \$\overline{SBTS}\$ should only be used to recover from host processor/AD14060/AD14060L deadlock, or used with a DRAM controller. |

| HBR                     | I/A   | <b>Host Bus Request.</b> (Common to all SHARCs) Must be asserted by a host processor to request control of the AD14060/AD14060L's external bus. When $\overline{HBR}$ is asserted in a multiprocessing system, the ADSP-2106x that is bus master will relinquish the bus and assert $\overline{HBG}$ . To relinquish the bus, the ADSP-2106x places the address, data, select, and strobe lines in a high impedance state. $\overline{HBR}$ has priority over all ADSP-2106x bus requests $(\overline{BR}_{6-1})$ in a multiprocessing system.                         |

| HBG                     | I/O   | Host Bus Grant. (Common to all SHARCs) Acknowledges an $\overline{HBR}$ bus request, indicating that the host processor may take control of the external bus. $\overline{HBG}$ is asserted (held low) by the AD14060/AD14060L until $\overline{HBR}$ is released. In a multiprocessing system, $\overline{HBG}$ is output by the ADSP-2106x bus master and is monitored by all others.                                                                                                                                                                                 |

| CSA                     | I/A   | Chip Select. Asserted by host processor to select SHARC_A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\overline{\text{CSB}}$ | I/A   | Chip Select. Asserted by host processor to select SHARC_B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\overline{\text{CSC}}$ | I/A   | Chip Select. Asserted by host processor to select SHARC_C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| $\overline{\text{CSD}}$ | I/A   | <b>Chip Select.</b> Asserted by host processor to select SHARC_D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

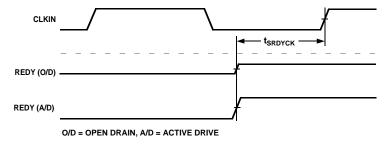

| REDY (O/D)              | О     | <b>Host Bus Acknowledge.</b> (Common to all SHARCs) The AD14060/AD14060L deasserts REDY (low) to add wait states to an asynchronous access of its internal memory or IOP registers by a host. Open drain output (O/D) by default; can be programmed in ADREDY bit of SYSCON register of individual ADSP-21060s to be active drive (A/D). REDY will only be output if the CS and HBR inputs are asserted.                                                                                                                                                               |

| BR <sub>6-1</sub>       | I/O/S | <b>Multiprocessing Bus Requests.</b> (Common to all SHARCs) Used by multiprocessing ADSP-2106xs to arbitrate for bus mastership. An ADSP-2106x only drives its own $\overline{BRx}$ line (corresponding to the value of its ID2-0 inputs) and monitors all others. In a multiprocessor system with less than six ADSP-2106xs, the unused $\overline{BRx}$ pins should be pulled high; $\overline{BR}_{4-1}$ must not be pulled high or low because they are outputs.                                                                                                   |

| RPBA                    | I/S   | <b>Rotating Priority Bus Arbitration Select.</b> (Common to all SHARCs) When RPBA is high, rotating priority for multiprocessor bus arbitration is selected. When RPBA is low, fixed priority is selected. This signal is a system configuration selection that must be set to the same value on every ADSP-2106x. If the value of RPBA is changed during system operation, it must be changed in the same CLKIN cycle on every ADSP-2106x.                                                                                                                            |

| CPAy (O/D)              | I/O   | Core Priority Access. (y = SHARC_A, B, C, D) Asserting its CPA pin allows the core processor of an ADSP-2106x bus slave to interrupt background DMA transfers and gain access to the external bus. CPA is an open drain output that is connected to all ADSP-2106x in the system if this function is required. The CPA pin of each internal ADSP-21060 is brought out individually. The CPA pin has an internal $5~\mathrm{k}\Omega$ pull-up resistor. If core access priority is not required in a system, the CPA pin should be left unconnected.                    |

| DT0                     | O/T   | <b>Data Transmit</b> (Common Serial Ports 0 to all SHARCs, TDM). DT pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DR0                     | I     | <b>Data Receive</b> (Common Serial Ports 0 to all SHARCs, TDM). DR pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| TCLK0                   | I/O   | <b>Transmit Clock</b> (Common Serial Ports 0 to all SHARCs, TDM). TCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RCLK0                   | I/O   | <b>Receive Clock</b> (Common Serial Ports 0 to all SHARCs, TDM). RCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| TFS0                    | I/O   | Transmit Frame Sync (Common Serial Ports 0 to all SHARCs, TDM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RFS0                    | I/O   | Receive Frame Sync (Common Serial Ports 0 to all SHARCs, TDM).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DTy1                    | O/T   | <b>Data Transmit</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) DT pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| DRy1                    | I     | <b>Data Receive</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) DR pin has a 50 kΩ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                   |

REV. A \_9\_

| Pin       | Туре   | Function                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TCLKy1    | I/O    | <b>Transmit Clock</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) TCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                          |

| RCLKy1    | I/O    | <b>Receive Clock</b> (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) RCLK pin has a 50 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                           |

| TFSy1     | I/O    | Transmit Frame Sync (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D)                                                                                                                                                                                                                                                                                                                                    |

| RFSy1     | I/O    | Receive Frame Sync (Serial Port 1 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D)                                                                                                                                                                                                                                                                                                                                     |

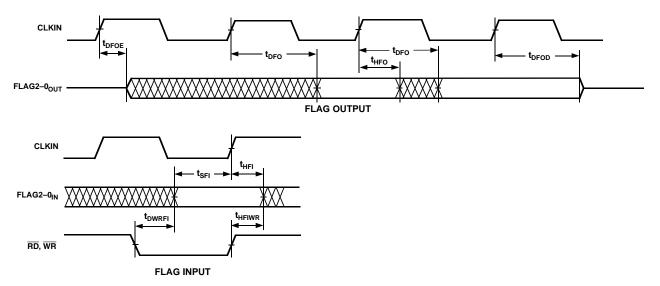

| FLAGy0    | I/O/A  | <b>Flag Pins.</b> (FLAG0 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) Each is configured via control bits as either an input or output. As an input, it can be tested as a condition. As an output, it can be used to signal external peripherals.                                                                                                                                                                 |

| FLAG1     | I/O/A  | <b>Flag Pins.</b> (FLAG1 common to all SHARCs) Configured via control bits internal to individual ADSP-21060s as either an input or output. As an input, it can be tested as a condition. As an output, it can be used to signal external peripherals.                                                                                                                                                                    |

| FLAGy2    | I/O/A  | <b>Flag Pins.</b> (FLAG2 individual from SHARC_A, SHARC_B, SHARC_C, SHARC_D) Each is configured via control bits as either an input or output. As an input, it can be tested as a condition. As an output, it can be used to signal external peripherals.                                                                                                                                                                 |

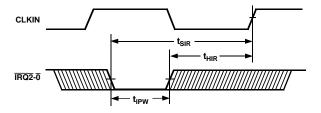

| ĪRQy2-0   | I/A    | <b>Interrupt Request Lines.</b> (Individual $\overline{IRQ}$ 2-0 from y = SHARC_A, SHARC_B, SHARC_C, SHARC_D) May be either edge-triggered or level-sensitive.                                                                                                                                                                                                                                                            |

| DMAR1     | I/A    | DMA Request 1 (DMA Channel 7). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                              |

| DMAR2     | I/A    | DMA Request 2 (DMA Channel 8). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                              |

| DMAG1     | O/T    | DMA Grant 1 (DMA Channel 7). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                                |

| DMAG2     | O/T    | DMA Grant 2 (DMA Channel 8). Common to SHARC_A, SHARC_B, SHARC_C, SHARC_D.                                                                                                                                                                                                                                                                                                                                                |

| LyxCLK    | I/O    | <b>Link Port Clock</b> (y = SHARC_A, B, C, D; x = Link Ports 1, 3, 4) <sup>1</sup> . Each LyxCLK pin has a 50 k $\Omega$ internal pull-down resistor which is enabled or disabled by the LPDRD bit of the LCOM register, of the ADSP-20160.                                                                                                                                                                               |

| LyxDAT3-0 | I/O    | <b>Link Port Data</b> (y = SHARC_A, B, C, D; x = Link Ports 1, 3, 4) <sup>1</sup> . Each LyxDAT pin has a 50 k $\Omega$ internal pull-down resistor which is enabled or disabled by the LPDRD bit of the LCOM register, of the ADSP-21060.                                                                                                                                                                                |

| LyxACK    | I/O    | <b>Link Port Acknowledge</b> (y = SHARC_A, B, C, D; x = Link Ports 1, 3, 4) <sup>1</sup> . Each LyxACK pin has a 50 k $\Omega$ internal pull-down resistor which is enabled or disabled by the LPDRD bit of the LCOM register, of the ADSP-21060.                                                                                                                                                                         |

| EBOOTA    | I      | <b>EPROM Boot Select.</b> (SHARC_A) When EBOOTA is high, SHARC_A is configured for booting from an 8-bit EPROM. When EBOOTA is low, the LBOOTA and BMSA inputs determine booting mode for SHARC_A. See the following table. This signal is a system configuration selection which should be hardwired.                                                                                                                    |

| LBOOTA    | I      | <b>Link Boot.</b> When LBOOTA is high, SHARC_A is configured for link port booting. When LBOOTA is low, SHARC_A is configured for host processor booting or no booting. See the following table. This signal is a system configuration selection which should be hardwired.                                                                                                                                               |

| BMSA      | I/O/T² | <b>Boot Memory Select.</b> <i>Output:</i> Used as chip select for boot EPROM devices (when EBOOTA = 1, LBOOTA = 0). In a multiprocessor system, BMS is output by the bus master. <i>Input:</i> When low, indicates that no booting will occur and that SHARC_A will begin executing instructions from external memory. See the following table. This input is a system configuration selection which should be hardwired. |

| EBOOTBCD  | I      | <b>EPROM Boot Select.</b> (Common to SHARC_B, SHARC_C, SHARC_D) When EBOOTBCD is high, SHARC_B, C, D are configured for booting from an 8-bit EPROM. When EBOOTBCD is low, the LBOOTBCD and BMSBCD inputs determine booting mode for SHARC_B, C and D. See the following table. This signal is a system configuration selection which should be hardwired.                                                                |

| LBOOTBCD  | I      | <b>LINK Boot.</b> (Common to SHARC_B, SHARC_C, SHARC_D) When LBOOTBCD is high, SHARC_B, C, D are configured for link port booting. When LBOOTBCD is low, SHARC_B, C, D are configured for host processor booting or no booting. See the following table. This signal is a system configuration selection which should be hardwired.                                                                                       |

-10- REV. A

| Pin                  | Туре               | Function                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| BMSBCD               | I/O/T <sup>2</sup> | <b>Boot Memory Select.</b> <i>Output:</i> Used as chip select for boot EPROM devices (when EBOOTBCD = 1, LBOOTBCD = 0). In a multiprocessor system, $\overline{BMS}$ is output by the bus master. <i>Input:</i> When low, indicates that no booting will occur and that SHARC_B, C, D will begin executing instructions from external memory. See table below. This input is a system configuration selection which should be hardwired. |  |  |  |  |  |

|                      |                    | EBOOT LBOOT BMS Booting Mode                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|                      |                    | 1 0 Output EPROM (Connect BMS to EPROM chip select) 0 0 1 (Input) Host Processor 0 1 1 (Input) Link Port 0 0 0 (Input) No Booting. Processor executes from external memory. 0 1 0 (Input) Reserved 1 x (Input) Reserved                                                                                                                                                                                                                  |  |  |  |  |  |

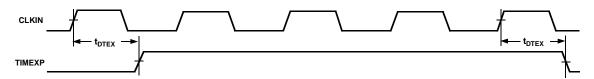

| TIMEXPy              | О                  | <b>Timer Expired.</b> (Individual TIMEXP from y = SHARC_A, SHARC_B, SHARC_C, SHARC_D) Asserted for four cycles when the timer is enabled and TCOUNT decrements to zero.                                                                                                                                                                                                                                                                  |  |  |  |  |  |

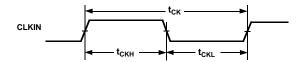

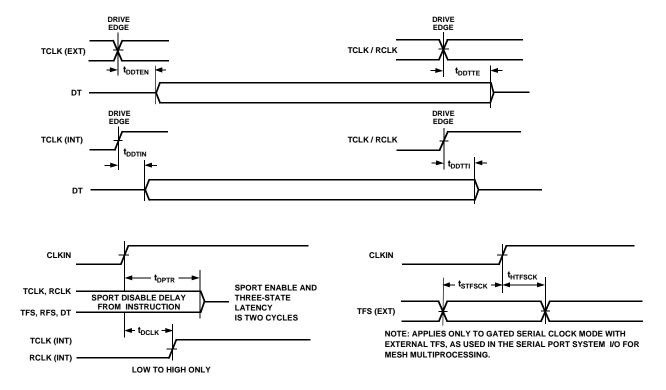

| CLKIN                | I                  | <b>Clock In.</b> (Common to all SHARCs) External clock input to the AD14060/AD14060L. The instruction cycle rate is equal to CLKIN. CLKIN may not be halted, changed, or operated below the minimum specified frequency.                                                                                                                                                                                                                 |  |  |  |  |  |

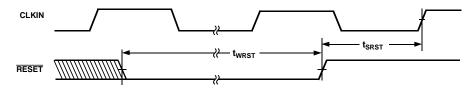

| RESET                | I/A                | <b>Module Reset.</b> (Common to all SHARCs) Resets the AD14060/AD14060L to a known state. This input must be asserted (low) at power-up.                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

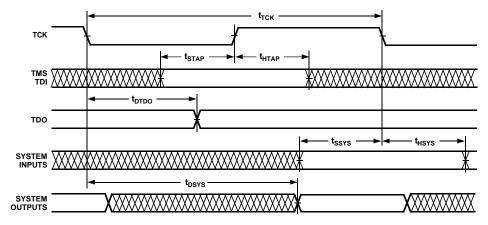

| TCK                  | I                  | <b>Test Clock (JTAG).</b> (Common to all SHARCs) Provides an asynchronous clock for JTAG boundary scan.                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| TMS                  | I/S                | <b>Test Mode Select (JTAG).</b> (Common to all SHARCs) Used to control the test state machine. TMS has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| TDI                  | I/S                | <b>Test Data Input (JTAG).</b> Provides serial data for the boundary scan logic chain starting at SHARC_A. TDI has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| TDO                  | О                  | <b>Test Data Output (JTAG).</b> Serial scan output of the boundary scan chain path, from SHARC_D.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| TRST                 | I/A                | <b>Test Reset (JTAG).</b> (Common to all SHARCs) Resets the test state machine. $\overline{TRST}$ must be asserted (pulsed low) after power-up or held low for proper operation of the AD14060/AD14060L. $\overline{TRST}$ has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                |  |  |  |  |  |

| <del>EMU</del> (O/D) | О                  | <b>Emulation Status.</b> (Common to all SHARCs) Must be connected to the ADSP-2106x EZ-ICE target board connector <i>only</i> .                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| $V_{DD}$             | P                  | <b>Power Supply.</b> Nominally +5.0 V dc for 5 V devices or +3.3 V dc for 3.3 V devices (26 pins).                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| GND                  | G                  | Power Supply Return. (28 pins).                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

### NOTES

REV. A -11-

FLAG3 is connected internally, common to SHARC\_A, B, C, and D. ID pins are hardwired internally as depicted in the block diagram.  $^1\text{LINK PORTS 0, 2}$  and 5 are connected internally as described earlier in Link Port I/O.  $^2\text{Three-statable only in EPROM boot mode (when <math display="inline">\overline{BMS}$  is an output).

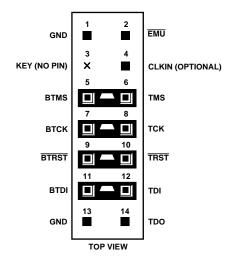

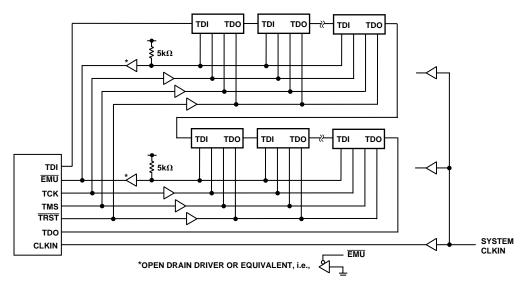

### TARGET BOARD CONNECTOR FOR EZ-ICE PROBE

The ADSP-2106x EZ-ICE Emulator uses the IEEE 1149.1 JTAG test access port of the ADSP-2106x to monitor and control the target board processor during emulation. The EZ-ICE probe requires that the AD14060/AD14060L's CLKIN (optional), TMS, TCK,  $\overline{TRST}$ , TDI, TDO,  $\overline{EMU}$  and GND signals be made accessible on the target system via a 14-pin connector (a pin strip header) such as that shown in Figure 6. The EZ-ICE probe plugs directly onto this connector for chip-on-board emulation. You must add this connector to your target board design if you intend to use the ADSP-2106x EZ-ICE. The length of the traces between the connector and the AD14060/ AD14060L's JTAG pins should be as short as possible.

Figure 6. Target Board Connector for ADSP-2106x EZ-ICE Emulator (Jumpers in Place)

The 14-pin, 2-row pin strip header is keyed at the Pin 3 location; Pin 3 must be removed from the header. The pins must be 0.025 inch square and at least 0.20 inch in length. Pin spacing should be  $0.1 \times 0.1$  inches. Pin strip headers are available from vendors such as 3M, McKenzie and Samtec.

The BTMS, BTCK,  $\overline{BTRST}$  and BTDI signals are provided so that the test access port can also be used for board-level testing. When the connector is not being used for emulation, place jumpers between the Bxxx pins and the xxx pins as shown in Figure 6. If you are not going to use the test access port for board testing, tie  $\overline{BTRST}$  to GND and tie or pull up BTCK to  $\overline{V_{DD}}$ . The  $\overline{TRST}$  pin must be asserted after power-up (through  $\overline{BTRST}$  on the connector) or held low for proper operation of the AD14060/AD14060L. None of the Bxxx pins (Pins 5, 7, 9, 11) are connected on the EZ-ICE probe.

The JTAG signals are terminated on the EZ-ICE probe as follows:

| Signal                    | Termination                                        |

|---------------------------|----------------------------------------------------|

| TMS                       | Driven through 22 Ω Resistor (16 μA–3.2 μA Driver) |

| TCK                       | Driven at 10 MHz through 22 Ω Resistor (16 μA-     |

|                           | 3.2 μA Driver)                                     |

| TRST                      | Driven by Open-Drain Driver* (Pulled Up by On-Chip |

|                           | 20 kΩ resistor)                                    |

| TDI                       | Driven by 16 μA-3.2 μA Driver                      |

| TDO                       | One TTL Load, No Termination                       |

| CLKIN                     | One TTL Load, No Termination (Optional Signal)     |

| $\overline{\mathrm{EMU}}$ | 4.7 kΩ Pull-Up Resistor, One TTL Load (Open-Drain  |

|                           | Output from ADSP-2106x)                            |

$<sup>*\</sup>overline{TRST}$  is driven low until the EZ-ICE probe is turned on by the EZ-ICE software (after the invocation command).

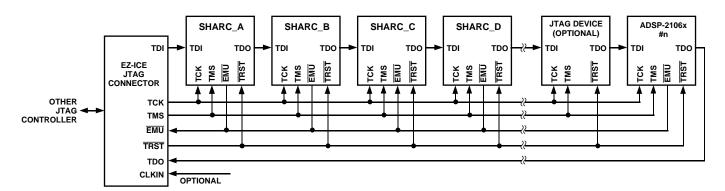

Figure 7 shows JTAG scan path connections for the multi-processor system.

Connecting CLKIN to Pin 4 of the EZ-ICE header is optional. The emulator only uses CLKIN when directed to perform

Figure 7. JTAG Scan Path Connections for the AD14060/AD14060L

-12- REV. A

operations such as starting, stopping and single-stepping multiple ADSP-2106xs in a synchronous manner. If you do not need these operations to occur synchronously on the multiple processors, simply tie Pin 4 of the EZ-ICE header to ground.

If synchronous multiprocessor operations are needed and CLKIN is connected, clock skew between the AD14060/AD14060L and the CLKIN pin on the EZ-ICE header must be minimal. If the skew is too large, synchronous operations may be off by one cycle between processors. For synchronous multiprocessor operation TCK, TMS, CLKIN and  $\overline{\rm EMU}$  should be treated as critical signals in terms of skew, and should be laid out as short

as possible on your board. If TCK, TMS and CLKIN are driving a large number of ADSP-2106xs (more than eight) in your system, then treat them as a "clock tree" using multiple drivers to minimize skew. (See Figure 8 JTAG Clock Tree and Clock Distribution in the "High Frequency Design Considerations" section of the *ADSP-2106x User's Manual*).

If synchronous multiprocessor operations are not needed (i.e., CLKIN is not connected), just use appropriate parallel termination on TCK and TMS. TDI, TDO,  $\overline{\text{EMU}}$  and  $\overline{\text{TRST}}$  are not critical signals in terms of skew.

Figure 8. JTAG Clocktree for Multiple ADSP-2106x Systems

REV. A -13-

# AD14060/AD14060L—SPECIFICATIONS

# RECOMMENDED OPERATING CONDITIONS

|                              |                            |    | B Grade |      | K Grade |      |       |  |

|------------------------------|----------------------------|----|---------|------|---------|------|-------|--|

| Parameter                    | •                          | M  | in N    | Лах  | Min     | Max  | Units |  |

| $\overline{V_{\mathrm{DD}}}$ | Supply Voltage (5 V)       | 4. | 75 5    | 5.25 | 4.75    | 5.25 | V     |  |

| 22                           | Supply Voltage (3.3 V)     | 3. | 15 3    | 3.6  | 3.15    | 3.6  | V     |  |

| $T_{CASE}$                   | Case Operating Temperature | -4 | ł0 -    | -100 | 0       | +85  | °C    |  |

# ELECTRICAL CHARACTERISTICS (3.3 V, 5 V SUPPLY)

| Parame                        | ter                                                 | Case<br>Temp | Test<br>Level | Test Condition                                | 5 V<br>Min Typ | Max                | 3.3 V<br>Min Typ |                       | Units |

|-------------------------------|-----------------------------------------------------|--------------|---------------|-----------------------------------------------|----------------|--------------------|------------------|-----------------------|-------|

| $\overline{V_{\mathrm{IH1}}}$ | High Level Input Voltage <sup>1</sup>               | Full         | I             | @ V <sub>DD</sub> = max                       | 2.0            | $V_{\rm DD} + 0.5$ | 2.0              | V <sub>DD</sub> + 0.5 | V     |

| $V_{IH2}$                     | High Level Input Voltage <sup>2</sup>               | Full         | I             | @ V <sub>DD</sub> = max                       | 2.2            | $V_{\rm DD} + 0.5$ |                  | $V_{\rm DD} + 0.5$    | V     |

| $V_{IL}$                      | Low Level Input Voltage <sup>1, 2</sup>             | Full         | I             | $@V_{DD} = min$                               |                | 0.8                |                  | 0.8                   | V     |

| $V_{OH}$                      | High Level Output Voltage <sup>3, 4</sup>           | Full         | I             | @ $V_{DD} = min, I_{OH} = -2.0 \text{ mA}^4$  | 4.1            |                    | 2.4              |                       | V     |

| $V_{OL}$                      | Low Level Output Voltage <sup>3, 4</sup>            | Full         | I             | @ $V_{DD} = min, I_{OL} = 4.0 \text{ mA}^4$   |                | 0.4                |                  | 0.4                   | V     |

| $I_{IH}$                      | High Level Input Current <sup>5, 6, 7</sup>         | Full         | I             | $@V_{DD} = max, V_{IN} = V_{DD} max$          |                | 10                 |                  | 10                    | μA    |

| $I_{IL}$                      | Low Level Input Current <sup>5</sup>                | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 10                 |                  | 10                    | μA    |

| $I_{ILP}$                     | Low Level Input Current <sup>6</sup>                | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 150                |                  | 150                   | μA    |

| $I_{ILPX4}$                   | Low Level Input Current <sup>7</sup>                | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 600                |                  | 600                   | μA    |

| $I_{OZH}$                     | Three-State Leakage Current <sup>8, 9, 10, 14</sup> | Full         | I             | $@V_{DD} = max, V_{IN} = V_{DD} max$          |                | 10                 |                  | 10                    | μA    |

| $I_{OZL}$                     | Three-State Leakage Current <sup>8, 11</sup>        | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 10                 |                  | 10                    | μA    |

| $I_{OZHP}$                    | Three-State Leakage Current <sup>11</sup>           | Full         | I             | $@V_{DD} = max, V_{IN} = V_{DD} max$          |                | 350                |                  | 350                   | μA    |

| $I_{OZLC}$                    | Three-State Leakage Current <sup>12</sup>           | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 1.5                |                  | 1.5                   | mA    |

| $I_{OZLA}$                    | Three-State Leakage Current <sup>13</sup>           | Full         | I             | @ $V_{DD} = max$ , $V_{IN} = 1.5 V (5 V)$ ,   |                |                    |                  |                       |       |

|                               | ~                                                   |              |               | 2 V (3.3 V)                                   |                | 350                |                  | 350                   | μA    |

| $I_{OZLAR}$                   | Three-State Leakage Current <sup>10</sup>           | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 4.2                |                  | 4.2                   | mA    |

| $I_{OZLS}$                    | Three-State Leakage Current <sup>9</sup>            | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 150                |                  | 150                   | μA    |

| $I_{OZLSX4}$                  | Three-State Leakage Current <sup>14</sup>           | Full         | I             | $@V_{DD} = max, V_{IN} = 0 V$                 |                | 600                |                  | 600                   | μA    |

| $I_{DDIN}$                    | Supply Current (Internal) <sup>15</sup>             | Full         | IV            | $t_{CK} = 25 \text{ ns}, V_{DD} = \text{max}$ | 1.4            | 3.4                | 1.0              | 2.2                   | A     |

| $I_{DDIDLE}$                  | Supply Current (Idle) <sup>16</sup>                 | Full         | I             | $V_{DD} = max$                                |                | 800                |                  | 760                   | mA    |

| $C_{IN}$                      | Input Capacitance <sup>17, 18</sup>                 | +25°C        | V             |                                               | 15             |                    | 15               |                       | pF    |

### EXPLANATION OF TEST LEVELS

### Test Level

100% Production Tested19.

100% Production Tested at +25°C, and Sample Tested at Specified Temperatures. II

Sample Tested Only. III

Parameter is guaranteed by design and analysis, and characterization testing on discrete SHARCs.

Parameter is typical value only.

VI All devices are 100% production tested at +25°C; sample tested at temperature extremes.

### NOTES

Applies to input and bidirectional pins:  $DATA_{47.0}$ ,  $ADDR_{31.0}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ,  $\overline{SW}$ , ACK,  $\overline{SBTS}$ ,  $\overline{IRQ}y_{2.0}$ , FLAGy0, FLAGy2,  $\overline{HBG}$ ,  $\overline{CSy}$ ,  $\overline{DMAR1}$ ,  $\overline{DMAR2}$ ,  $\overline{BR}_{8-1}$ , RPBA,  $\overline{CPAy}$ , TFS0, TFSy1, RFS0, TFSy1,  $LyxDAT_{3.0}$ , LyxCLK, LyxACK, EBOOTA, LBOOTA, EBOOTBCD, LBOOTBCD,  $\overline{BMSA}$ ,  $\overline{BMSBCD}$ , TMS,  $\overline{TDI}$ , TCK,  $\overline{HBR}$ , DR0, DRy1, TCLK0, TCLKy1, RCLK0, RCLKy1.

<sup>2</sup> Applies to input pins: CLKIN, RESET, TRST.

<sup>3</sup>Applies to output and bidirectional pins: DATA  $_{47-0}$ , ADDR  $_{31-0}$ ,  $\overline{MS}_{3-0}$   $\overline{RD}$ ,  $\overline{WR}$ , PAGE, ADRCLK,  $\overline{SW}$ , ACK, FLAGy0, FLAG1, FLAGy2, TIMEXPY,  $\overline{HBG}$ , REDY,  $\overline{DMAG1}$ ,  $\overline{DMAG2}$ ,  $\overline{BR}_{6-1}$ , CPAy, DTO, DTy1, TCLK0, TCLKy1, RCLK0, RCLKy1, TFS0, TFSy1, RFS0, RFSy1 LyxDAT  $_{3-0}$ , LyxCLK, LyxACK, BMSA, BMSBCD, TDO, EMU.

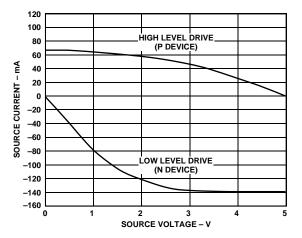

See Output Drive Currents for typical drive current capabilities.

Applies to input pins: SBTS, IRQy<sub>2-0</sub>, HBR, CSy, DMARI, DMAR2, RPBA, EBOOTA, LBOOTA, EBOOTBCD, LBOOTBCD, CLKIN, RESET, TCK.

2106x is not requesting bus mastership. HBG AND EMU are not tested for leakage current.)

<sup>9</sup> Applies to three-statable pins with internal pull-ups: DTy1, TCLKy1, RCLKy1.  $^{10}$  Applies to ACK pin when pulled up. (Note that ACK is pulled up internally with 2 kΩ during reset in a multiprocessor system, when ID<sub>2-0</sub> = 001 and another

ADSP-2106x is not requesting bus mastership.)

11 Applies to three-statable pins with internal pull-downs: LyxDAT<sub>3-0</sub>, LyxCLK, LyxACK.

<sup>12</sup>Applies to CPAy pin.

Applies to ACK pin when keeper latch enabled.

Applies to bused three-statable pins with internal pull-ups: DT0, TCLK0, RCLK0.

<sup>15</sup>Applies to V<sub>DD</sub> pins. Conditions of operation: each processor executing radix-2 FFT butterfly with instruction in cache, one data operand fetched from each internal memory block, and one DMA transfer occurring from/to internal memory at  $t_{\rm CK} = 25$  ns.

<sup>16</sup> Applies to  $V_{\rm DD}$  pins. Idle denotes AD14060/AD14060L state during execution of IDLE instruction.

<sup>17</sup>Applies to all signal pins.

<sup>18</sup>Guaranteed but not tested.

-14-

Specifications subject to change without notice.

<sup>19</sup> Link and Serial Ports: All are 100% tested at die level prior to assembly. All are 100% ac tested at module level; Link-4 and Serial-0 are also dc tested at the module level. See Timing Specifications.

### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage (5 V)0.3 V to +7 V                                 |

|-------------------------------------------------------------------|

| Supply Voltage (3.3 V)0.3 V to +4.6 V                             |

| Input Voltage0.5 V to $V_{DD}$ + 0.5 V                            |

| Output Voltage Swing $-0.5 \text{ V}$ to $V_{DD} + 0.5 \text{ V}$ |

| Load Capacitance 200 pF                                           |

| Junction Temperature Under Bias                                   |

| Storage Temperature Range65°C to +150°C                           |

| Lead Temperature (5 seconds) +280°C                               |

<sup>\*</sup>Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD SENSITIVITY**