# AMDA

# Élan™SC310

## Single-Chip, 32-Bit, PC/AT Microcontroller

## DISTINCTIVE CHARACTERISTICS

# ■ Highly integrated, single-chip CPU and system logic

- Optimized for embedded PC applications

- Combines 32 bit, x86 compatible, low-voltage CPU with memory controller, PC/AT peripheral controllers, real-time clock, and PLL clock generators

- 0.7 micron, low-voltage, CMOS process, fully static

## ■ Enhanced Am386<sup>®</sup>SXLV CPU core

- 25 MHz or 33 MHz operating frequencies

- 3.3 V core, 3.3 V or 5 V memory and I/O

- Low-power, fully static design for long battery life

- System Management Mode (SMM) for power management control

## ■ Integrated power management functions

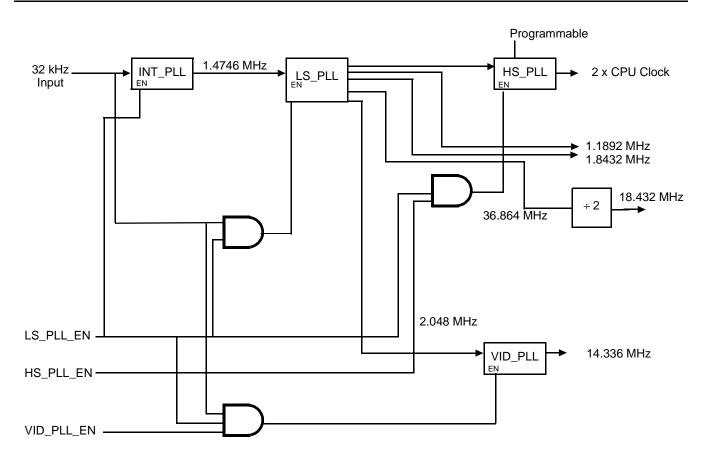

- Internal clock generators (using multiple Phase-Locked Loops and one external 32-KHz crystal)

- Supports CPU System Management Mode (SMM)

- Multiple operating modes: High Speed PLL, Low Speed PLL, Doze, Sleep, Suspend, and Off. Fully static design allows stopped clock.

- Comprehensive control of system and peripheral clocks

- Five external power management control pins

- Suspend refresh of DRAM array

- Clock switching during ISA cycles

- Low power consumption: 0.12 mW typical Suspend mode power

- Simultaneous multiple-voltage I/O pads operate at either 3.3 V or 5 V. Core operates at 3.3 V for minimum power consumption.

## ■ Integrated memory controller

- Controls symmetrically addressable DRAM or asymmetrical 512 Kbyte x 8 bit or 1 Mbyte x 16 bit DRAM or SRAM as main memory

- Zero wait-state access with 70 ns, Page mode DRAMs

- Supports up to 16 Mbyte system memory

- Supports up to 16 Mbyte of application ROM/ Flash, and 320 Kbyte direct ROM BIOS access. Also supports shadow RAM

- Fully PC/AT compatible

## ■ Integrated PC/AT-lompatible leripheral logic

- One programmable interval timer (fully 8254 compatible)

- Two programmable interrupt controllers (8259A compatible)

- Two DMA controllers (8237A compatible)

- Built-in real-time clock (146818A compatible), with an additional 114 bytes of RAM

- Internal Phase-Locked Loops (PLL) generate all clocks from single 32.768 kHz crystal input

### ■ Bus configurations

- 16-bit data path

- Optional bus configurations:

- 386 Local Bus mode with subset ISA

- Maximum ISA Bus mode

- Four programmable chip selects

- Built-in 8042 chip select

#### ■ Serial port controller (16450 UART compatible)

■ Bidirectional parallel port (EPP compliant)

#### **GENERAL DESCRIPTION**

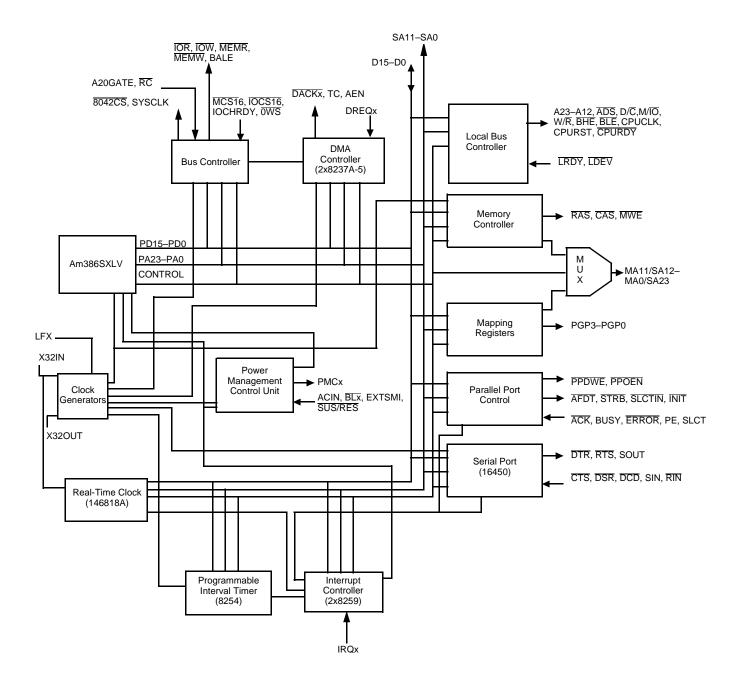

The ÉlanSC310 microcontroller is a highly integrated, low-voltage, single-chip implementation of the Am386SXLV microprocessor plus most of the additional logic needed for an AT-compatible personal computer. It is ideal for embedded PC applications, such as point-of-sale equipment, web appliances, industrial controls, and communication equipment.

The ÉlanSC310 microcontroller from AMD is part of the growing Élan family of mobile computing products, which leverage existing AMD core modules. The ÉlanSC310 microcontroller demonstrates the feasibility of constructing highly integrated components built from standard cores and getting these products to market quickly.

The ÉlanSC310 microcontroller does this by combining an Am386SXLV low-voltage microprocessor core with a memory control unit, a Power Management Unit (PMU), and the bus control and peripheral control logic of a PC/AT-compatible computer. For more information about the Am386 microprocessors, see the Am386 SX/SXL/SXLV Data Sheet, order #21020 and the AM386 DX/DXL Data Sheet, order #21017.

For more information about the ÉlanSC310 microcontroller, see the Élan<sup>TM</sup>SC310 Microcontroller Programmer's Reference Manual, order #20665.

The ÉlanSC310 microcontroller includes a memory controller that supports up to 16 Mbyte of DRAM, Flash, or ROM; power management functions; a bus

controller that supports local or ISA bus; a serial port controller that is 16450 UART compatible; a bidirectional EPP-compliant parallel port; a 146818A-compatible real-time clock; internal phase-locked loops for clock generation; and standard PC logic chip functions (8259A, 8237A, and 8254).

The ÉlanSC310 microcontroller's true static design and low operating voltage enable battery-powered operation and lower weight for embedded PC applications. The internal core of the ÉlanSC310 microcontroller operates at 3.3 V and the I/O pads allow either 3.3-V or 5-V operation. Lowering typical operating voltage from 5 V to 3.3 V can dramatically reduce power consumption.

Functionally, the ÉlanSC310 microcontroller is a 100% DOS/Windows-compatible, PC/AT-compatible computer on a chip that is designed to furnish the customer with a high-performance, low-power system solution, providing state-of-the-art power management in a small physical footprint.

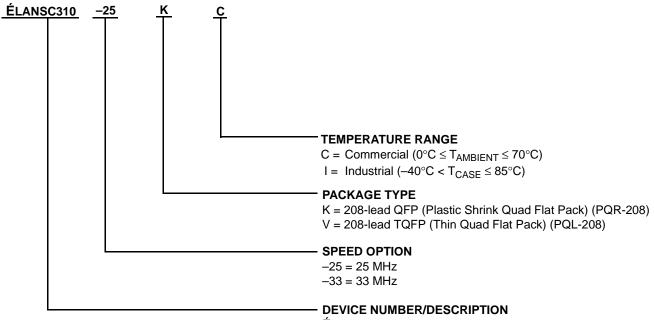

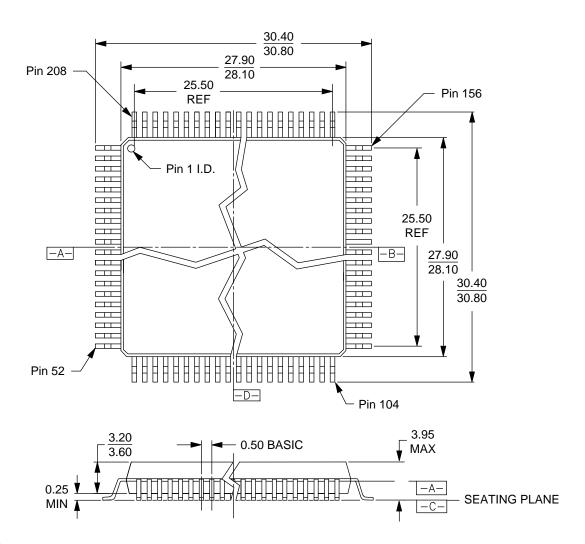

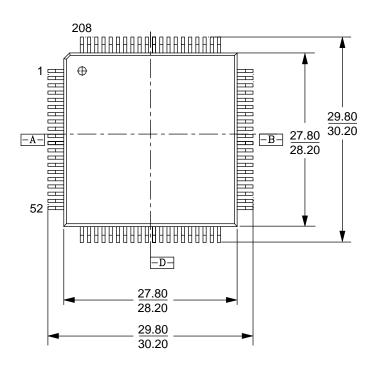

The ÉlanSC310 microcontroller is available in both 25and 33-MHz versions, in a 208-lead Plastic Shrink Quad Flat Pack (QFP) (PQR package) and a 208-lead Thin Quad Flat Pack (TQFP) (PQL package).

**Note:** Unless specified otherwise, the timings in this data sheet are based on the 33-MHz version of the ÉlanSC310 microcontroller.

#### **CUSTOMER SERVICE**

The AMD customer service network includes U.S. offices, international offices, and a customer training center. Expert technical assistance is available from the AMD worldwide staff of field application engineers and factory support staff who can answer E86 family hardware and software development questions.

#### **Hotline and World Wide Web Support**

For answers to technical questions, AMD provides a toll-free number for direct access to our corporate applications hotline. Also available is the AMD World Wide Web home page and FTP site, which provides the latest E86 family product information.

## **Corporate Applications Hotline**

(800) 222-9323 Toll-free for U.S. and Canada 44-(0) 1276-803-299 U.K. and Europe hotline

## World Wide Web Home Page and FTP Site

To access the AMD home page, go to http://www.amd.com.

Questions, requests, and input concerning AMD's WWW pages can be sent via E-mail to webmaster@amd.com.

To download documents and software, ftp to ftp.amd.com and log on as anonymous using your e-mail address as a password. Or via your web browser, go to ftp://ftp.amd.com.

#### **Documentation and Literature**

Free E86 family information such as data books, user's manuals, data sheets, application notes, the FusionE86 Partner Solutions Catalog, and other literature is available with a simple phone call. Internationally, contact your local AMD sales office for complete E86 family literature.

## Literature Ordering

(800) 222-9323 Toll-free for U.S. and Canada

(512) 602-5651 Direct dial worldwide

## **BLOCK DIAGRAM**

## ORDERING INFORMATION

AMD standard products are available in several packages and operating ranges. The order numbers (Valid Combinations) are formed by a combination of the elements below.

| ElanSC310 microcontroller highly integrated, |

|----------------------------------------------|

| low-power, 32-bit microprocessor and system  |

| logic                                        |

|                                              |

| Valid Combinati | ons |

|-----------------|-----|

| ELANSC310-25    | KC  |

| ELANSC310-33    | KC  |

| ELANSC310-25    | KI  |

| ELANSC310-33    | KI  |

| ELANSC310-25    | VC  |

| ELANSC310-33    | VC  |

### **Valid Combinations**

Valid Combinations list configurations planned to be supported in volume for this device. Consult the local AMD sales office to confirm availability of specific valid combinations and to check on newly released combinations.

## **TABLE OF CONTENTS**

| Distinctive Characteristics                                |      |

|------------------------------------------------------------|------|

| General Description                                        | 2    |

| Customer Service                                           | 2    |

| Block Diagram                                              | 3    |

| Ordering Information                                       | 4    |

| Connection Diagram                                         | . 11 |

| ÉlanSC310 Microcontroller Pin Designations                 |      |

| Pin Designations (Sorted by Pin Number)                    |      |

| Pin Designations (Sorted By Pin Name)                      |      |

| Pin State Tables                                           |      |

| Pin Characteristics                                        |      |

| Pin Descriptions                                           |      |

| Memory Bus Interface                                       |      |

| CAS1H [SRCS3], CAS1L [SRCS2], CAS0H [SRCS1], CAS0L [SRCS0] | 30   |

| DOSCS                                                      |      |

| MA11-MA0/SA23-SA12                                         | 30   |

| MWE                                                        |      |

| RAS1-RAS0                                                  |      |

|                                                            |      |

| ROMCS                                                      |      |

| System Interface                                           |      |

| AEN [TDI]                                                  |      |

| D15–D0                                                     |      |

| <u>DACK2</u> [TCK]                                         |      |

| DBUFOE                                                     |      |

| DRQ2 [TDO]                                                 |      |

| ENDIRH                                                     |      |

| ENDIRL                                                     |      |

| IOCHRDY                                                    |      |

| IOCS16                                                     |      |

| TOR                                                        |      |

| <del>IOW</del>                                             | . 31 |

| IRQ1, IRQ14                                                | . 32 |

| MCS16                                                      | 32   |

| MEMR                                                       | . 32 |

| MEMW                                                       | . 32 |

| PIRQ0 (IRQ6), PIRQ1 (IRQ3)                                 | 32   |

| RSTDRV                                                     |      |

| SA11-SA0                                                   |      |

| SBHE                                                       |      |

| SPKR                                                       |      |

| TC [TMS]                                                   |      |

| Keyboard Interface                                         |      |

| 8042CS [XTDAT]                                             |      |

| A20GATE                                                    |      |

| RC                                                         |      |

| SYSCLK [XTCLK]                                             |      |

| •                                                          |      |

| Parallel Port Interface                                    |      |

| ACK                                                        |      |

| AFDT [X14OUT]                                              |      |

| BUSY                                                       |      |

| ERROR                                                      |      |

|                                                            |      |

| PE                                                         | . 33 |

| PPDWE [PPDCS]                                   | 33 |

|-------------------------------------------------|----|

| PPOEN                                           | 33 |

| SLCT                                            | 33 |

| SLCTIN                                          | 33 |

| STRB                                            |    |

| Serial Port Interface                           |    |

| CTS                                             |    |

| DCD                                             |    |

| DSR                                             |    |

| DTR/CFG1                                        |    |

|                                                 |    |

| RIN                                             |    |

| RTS/CFG0                                        |    |

| SIN                                             |    |

| SOUT                                            |    |

| Power Management Interface                      |    |

| ACIN                                            |    |

| BL4-BL1                                         |    |

| EXTSMI                                          | 34 |

| <u> </u>                                        | 34 |

| PGP3-PGP0                                       | 34 |

| PMC4-PMC0                                       | 34 |

| SUS/RES                                         |    |

| Miscellaneous Interface                         |    |

| LF1, LF2, LF3, LF4 (Analog inputs)              |    |

| X1OUT [BAUD-OUT]                                | 35 |

| X140UT                                          |    |

| X32IN, X32OUT                                   |    |

| Local Bus Interface                             |    |

|                                                 |    |

| ADS                                             |    |

| BHE                                             |    |

| BLE                                             |    |

| CPUCLK (PULLUP)                                 |    |

| CPURDY                                          |    |

| CPURST (RSVD)                                   |    |

| D/C                                             |    |

| LDEV (RSVD)                                     | 35 |

| <u>LRDY</u>                                     | 36 |

| M/IO                                            | 36 |

| W/R                                             | 36 |

| A23–A12                                         | 36 |

| Maximum ISA Bus Interface                       | 36 |

| 0WS                                             |    |

| BALE                                            |    |

| DACK7, DACK6, DACK5, DACK3, DACK2, DACK1, DACK0 |    |

| DRQ7, DRQ6, DRQ5, DRQ3, DRQ2, DRQ1, DRQ0        |    |

| IOCHCHK                                         |    |

| IRQ15, IRQ14, IRQ12–IRQ9, IRQ7–IRQ3, IRQ1       | 30 |

|                                                 |    |

| LA23-LA17                                       |    |

| LTAG Boundary Coop Interfere                    |    |

| JTAG Boundary Scan Interface                    |    |

| JTAGEN                                          |    |

| [TCK]                                           |    |

| [TDI]                                           |    |

| [TDO]                                           |    |

| [TMS]                                           | 37 |

| Reset and Power                                                 | 37 |

|-----------------------------------------------------------------|----|

| AGND                                                            | 37 |

| AVCC                                                            | 37 |

| GND                                                             | 37 |

| IORESET                                                         | 37 |

| RESIN                                                           |    |

| VCC                                                             |    |

| VCC1                                                            |    |

| VCC5                                                            |    |

| VMEM                                                            |    |

| VSYS                                                            |    |

| VSYS2                                                           | 38 |

| Functional Description                                          |    |

| Am386SXLV CPU Core                                              |    |

| Memory Controller                                               |    |

| SRAM                                                            |    |

| The PMU Modes and Clock Generators                              |    |

| ÉlanSC310 Microcontroller Power Management                      |    |

| Micro Power Off Mode                                            |    |

| Core Peripheral Controllers                                     |    |

| Additional Peripheral Controllers                               |    |

| Parallel Port Anomalies                                         |    |

| PC/AT Support Features                                          |    |

| Local Bus or Maximum ISA Bus Controller                         |    |

| Alternate Pin Functions                                         |    |

| Maximum ISA Interface versus Local Bus Interface                |    |

| Alternate Pin Functions Selected Via Firmware                   |    |

| SRAM Interface                                                  |    |

| Unidirectional/Bidirectional Parallel Port                      |    |

| X1OUT [BAUD_OUT] Clock Source                                   |    |

| PC/XT Keyboard                                                  |    |

| 14-MHz Clock Source                                             |    |

| ISA Bus Descriptions                                            |    |

| System Test and Debug                                           |    |

| JTAG Instruction Opcodes                                        |    |

| Absolute Maximum Ratings                                        |    |

| Operating Ranges                                                |    |

| Thermal Characteristics                                         |    |

| Typical Power Numbers                                           |    |

| Derating Curves                                                 |    |

| Voltage Partitioning                                            |    |

| Crystal Specifications                                          |    |

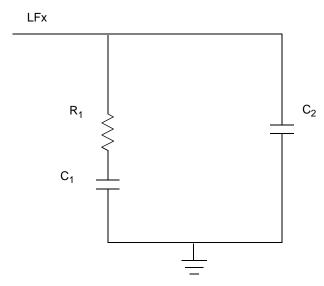

| Loop Filters                                                    |    |

| AC Switching Characteristics and Waveforms                      |    |

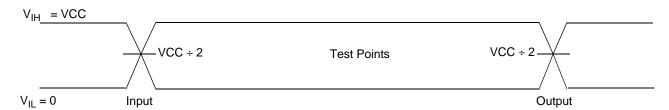

| AC Switching Test Waveforms                                     |    |

| AC Switching Characteristics over Commercial Operating Ranges   |    |

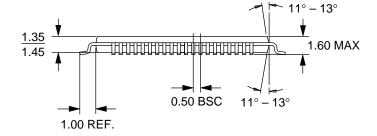

| Physical Dimensions                                             |    |

| PQR 208, Trimmed and Formed Plastic Shrink Quad Flat Pack (QFP) |    |

| PQL 208, Trimmed and Formed Thin Quad Flat Pack (TQFP)          |    |

## **LIST OF FIGURES**

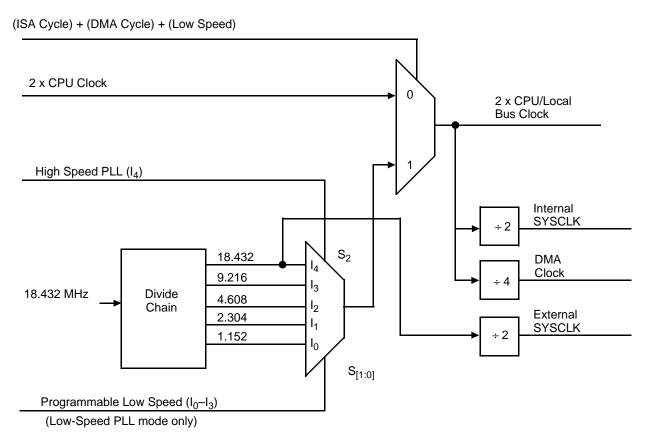

| Figure 1.  | PLL Block Diagram                                                              | 42   |

|------------|--------------------------------------------------------------------------------|------|

| Figure 2.  | Clock Steering Block Diagram                                                   | 43   |

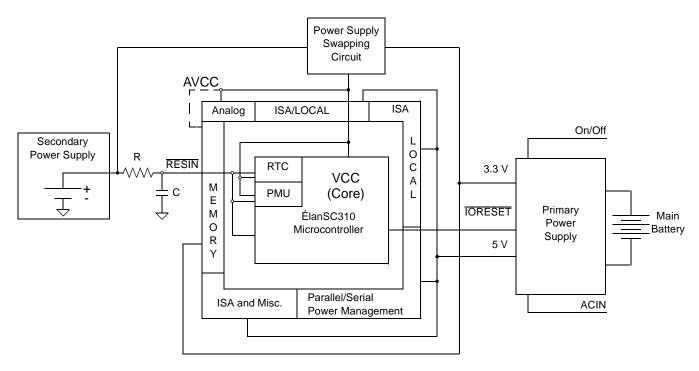

| Figure 3.  | Typical System Design with Secondary Power Supply to Maintain RTC When         |      |

|            | Primary Power Supply is Off (DRAM Refresh is Optional.)                        | 47   |

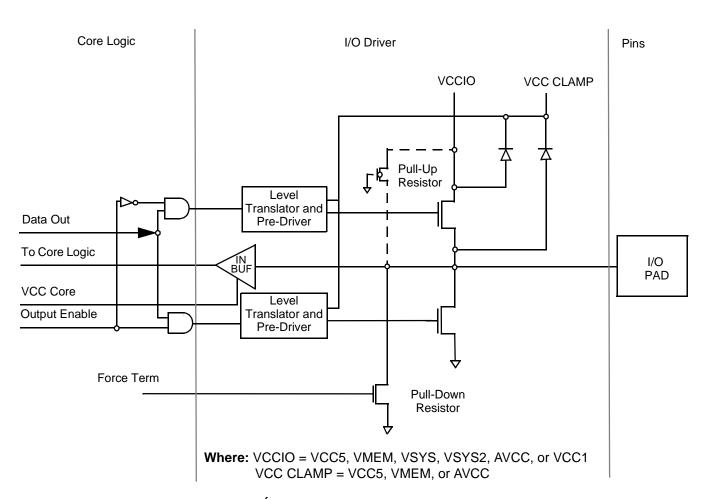

| Figure 4.  | ÉlanSC310 Microcontroller I/O Structure                                        | 48   |

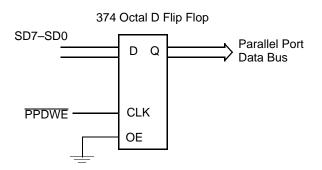

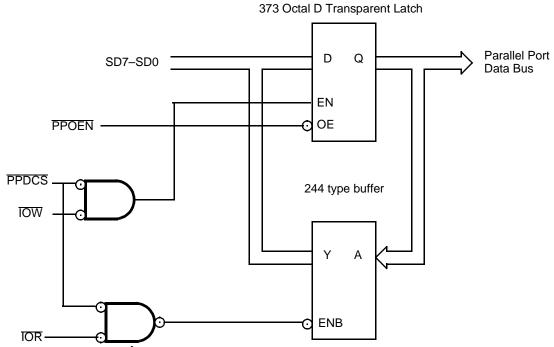

| Figure 5.  | ÉlanSC310 Microcontroller Unidirectional Parallel Port Data Bus Implementation | . 52 |

| Figure 6.  | The ÉlanSC310 Microcontroller Bidirectional Parallel Port                      |      |

| Ü          | and EPP Implementation                                                         | 53   |

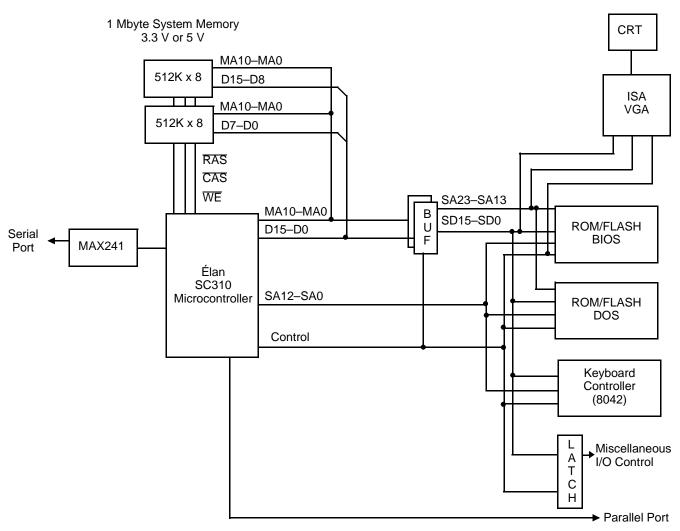

| Figure 7.  | Typical System Block Diagram (Maximum ISA Mode)                                |      |

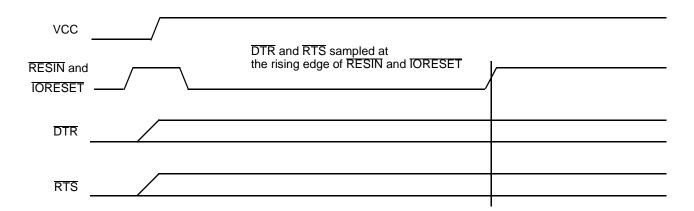

| Figure 8.  | Bus Option Configuration Select                                                |      |

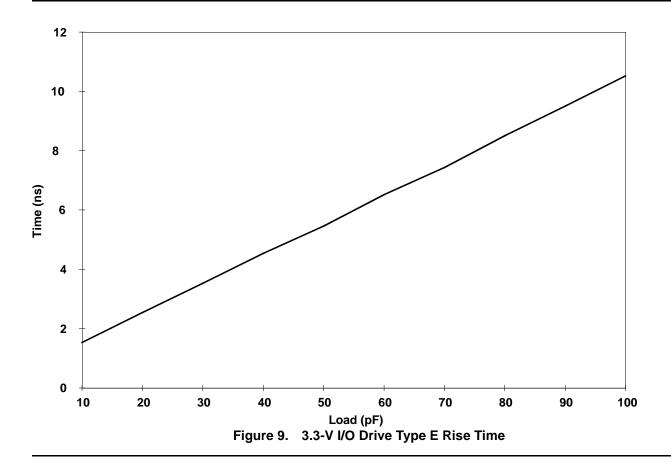

| Figure 9.  | 3.3-V I/O Drive Type E Rise Time                                               |      |

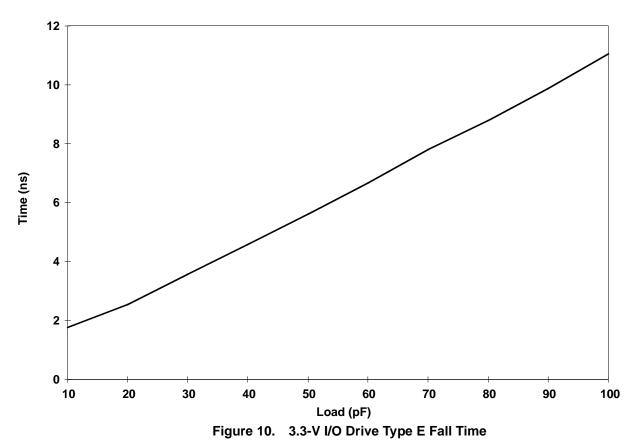

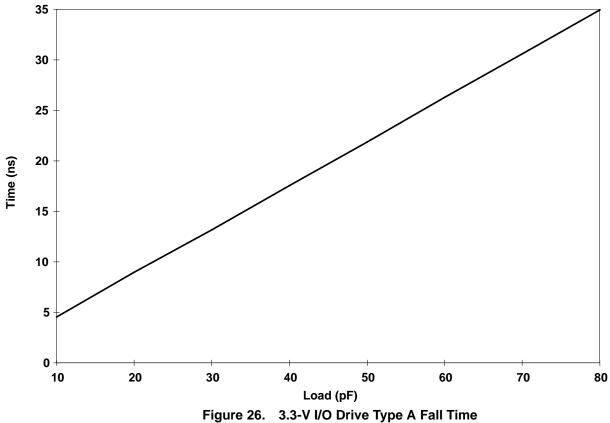

| •          | 3.3-V I/O Drive Type E Fall Time                                               |      |

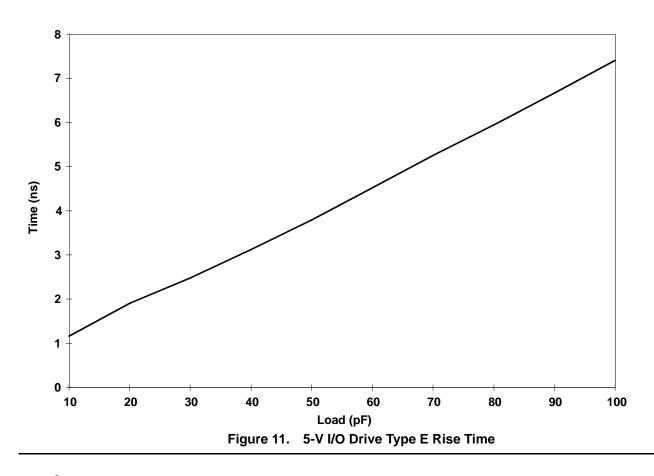

| •          | 5-V I/O Drive Type E Rise Time                                                 |      |

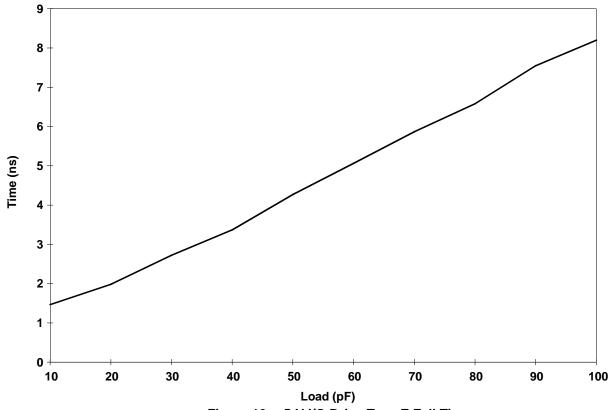

| •          | 5-V I/O Drive Type E Fall Time                                                 |      |

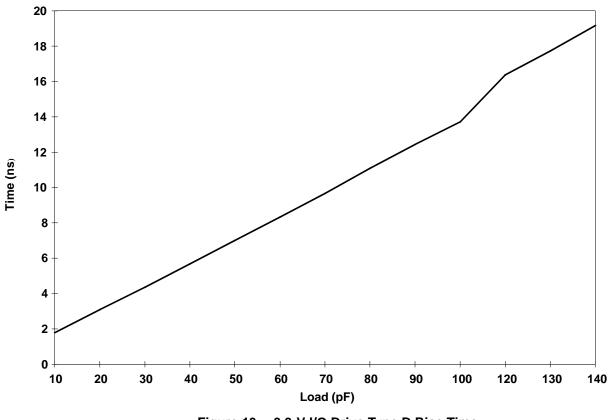

|            | 3.3-V I/O Drive Type D Rise Time                                               |      |

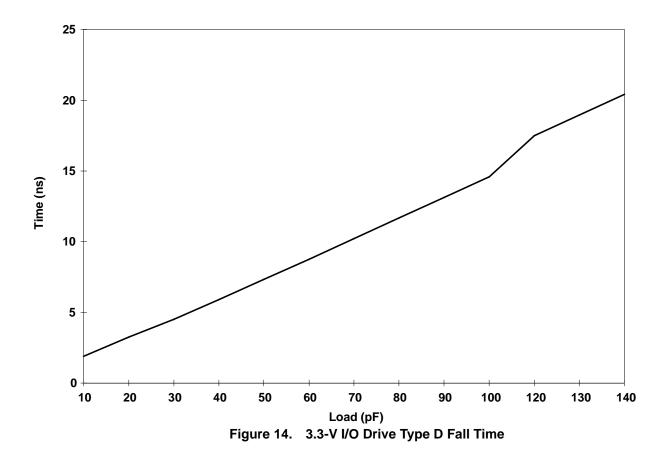

|            | 3.3-V I/O Drive Type D Fall Time                                               |      |

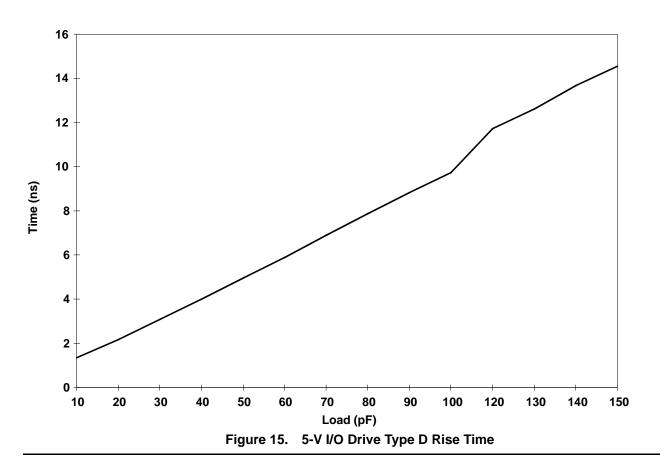

|            | 5-V I/O Drive Type D Rise Time                                                 |      |

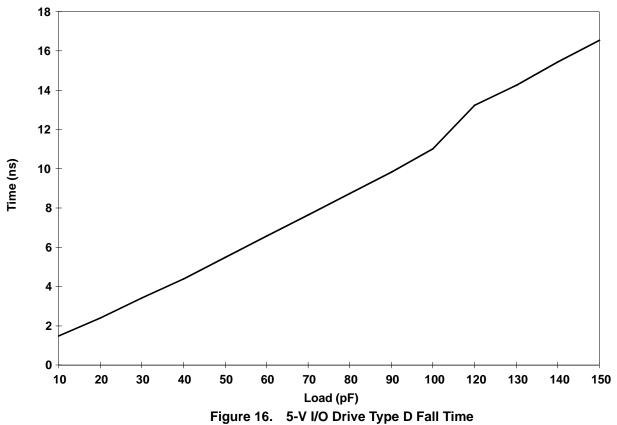

|            | 5-V I/O Drive Type D Fall Time                                                 |      |

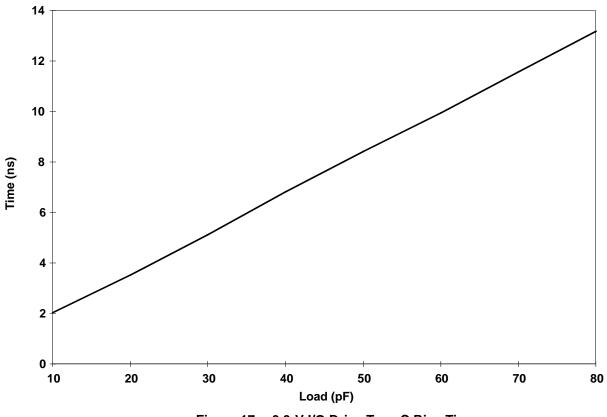

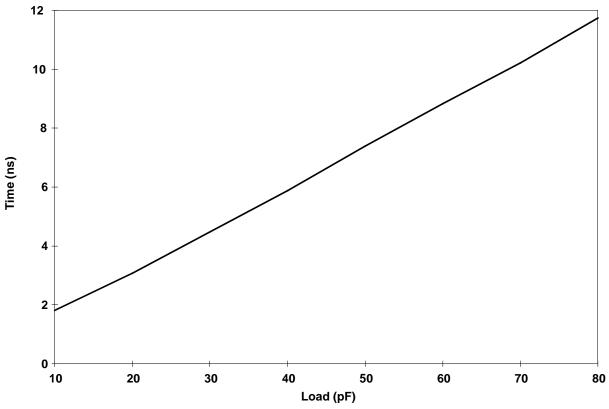

|            | 3.3-V I/O Drive Type C Rise Time                                               |      |

|            | 3.3-V I/O Drive Type C Fall Time                                               |      |

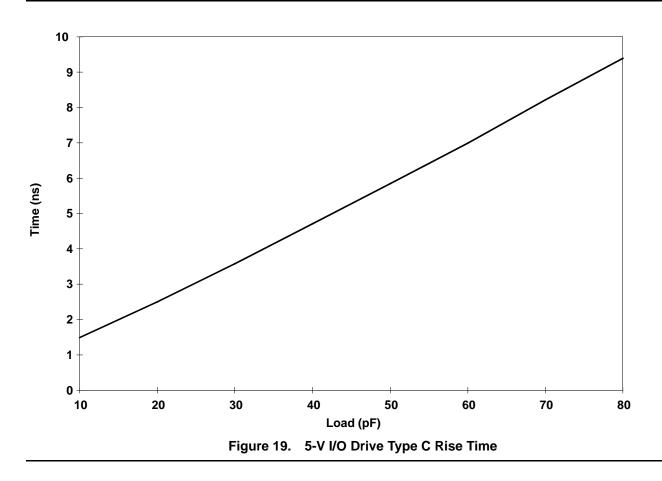

| •          | 5-V I/O Drive Type C Rise Time                                                 |      |

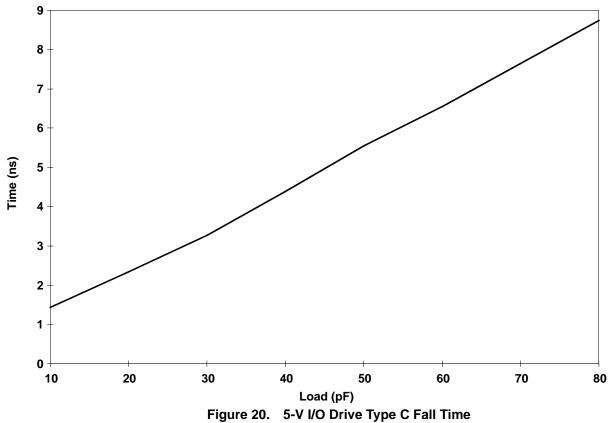

|            | 5-V I/O Drive Type C Fall Time                                                 |      |

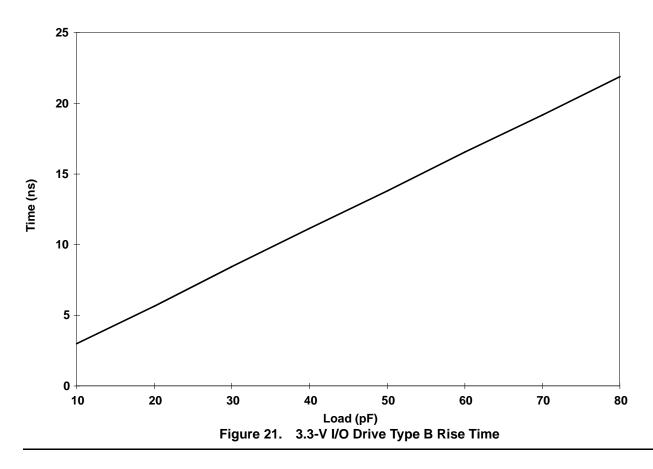

|            | 3.3-V I/O Drive Type B Rise Time                                               |      |

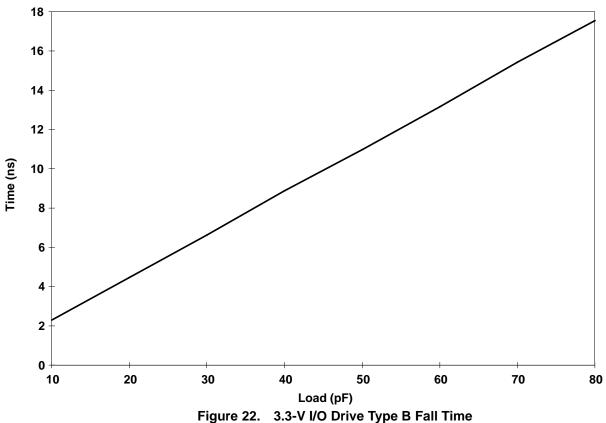

| -          | 3.3-V I/O Drive Type B Fall Time                                               |      |

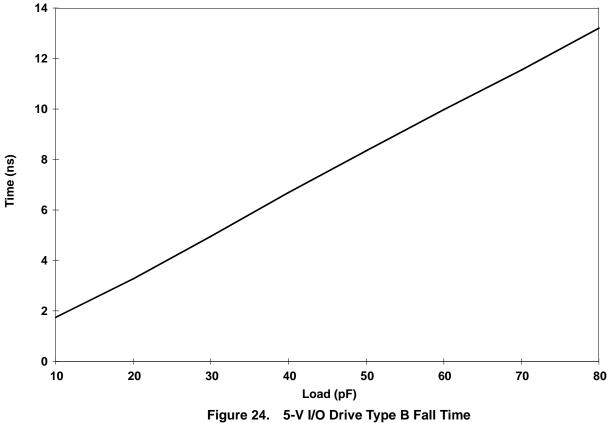

| •          | 5-V I/O Drive Type B Fall Time                                                 |      |

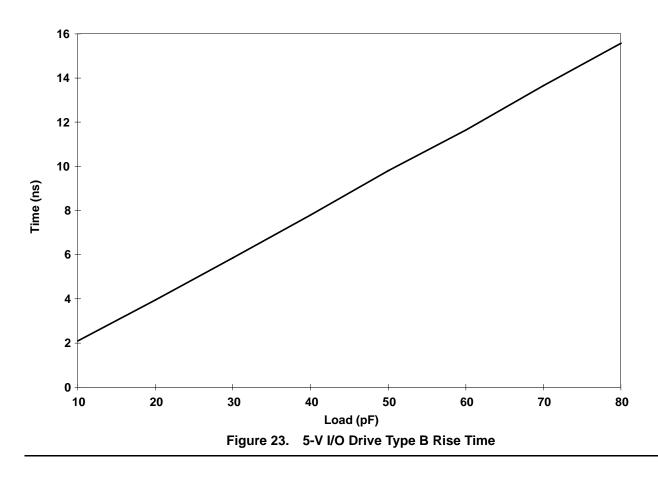

|            | 5-V I/O Drive Type B Rise Time                                                 |      |

| •          |                                                                                |      |

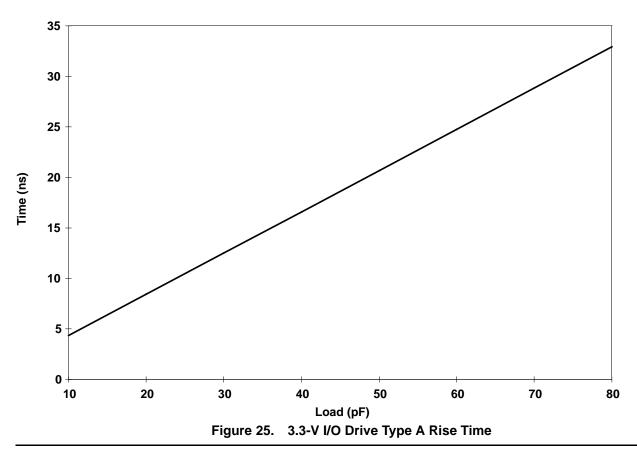

| •          | 3.3-V I/O Drive Type A Rise Time                                               |      |

| •          | 3.3-V I/O Drive Type A Rice Time                                               |      |

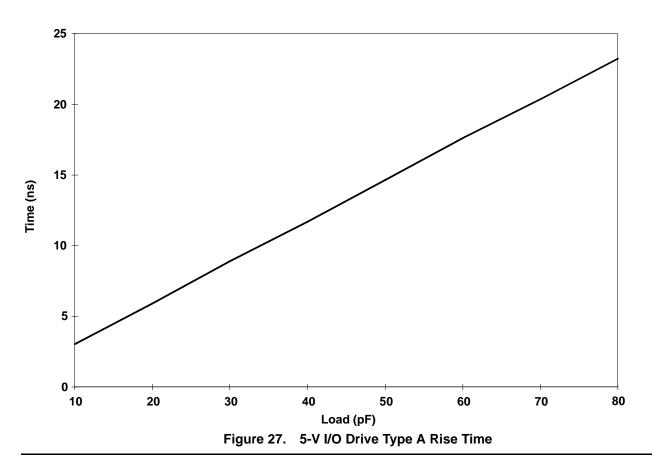

| •          | 5-V I/O Drive Type A Rise Time                                                 |      |

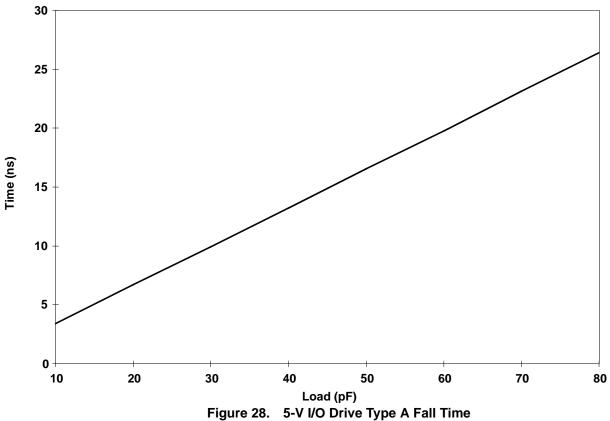

| •          | 5-V I/O Drive Type A Fall Time                                                 |      |

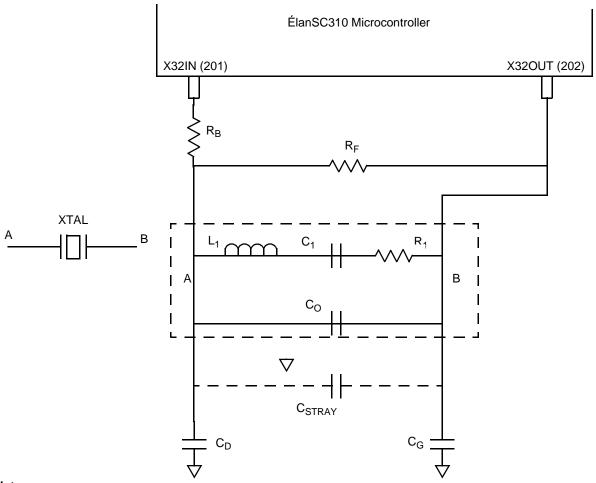

| •          | X32 Oscillator Circuit                                                         |      |

| •          | Loop-Filter Component                                                          |      |

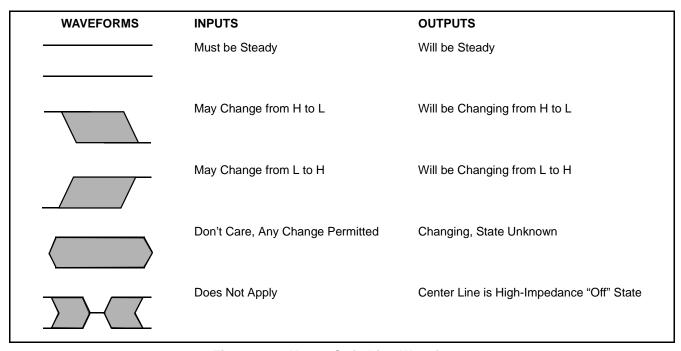

| •          | Key to Switching Waveforms                                                     |      |

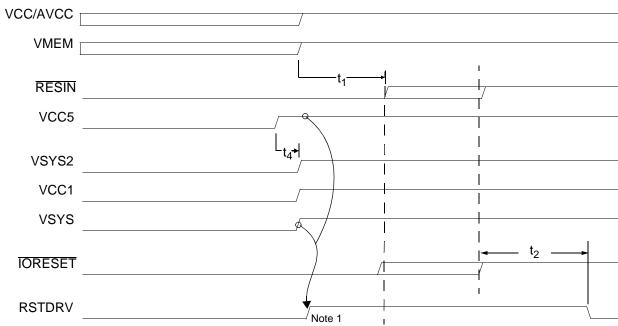

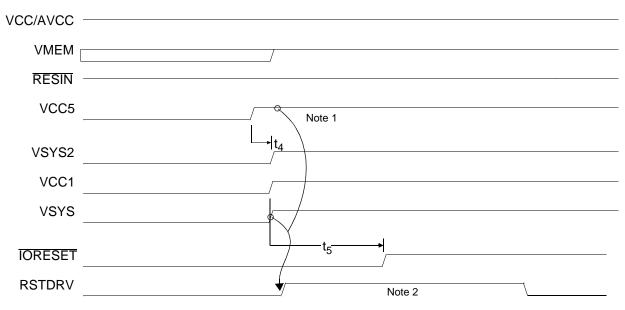

| •          | Power-Up Sequence Timing                                                       |      |

| 9          |                                                                                | . 90 |

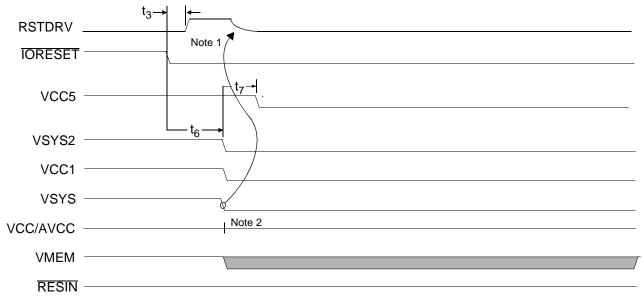

| •          | Entering Micro Power Off Mode (DRAM Refresh Disabled)                          |      |

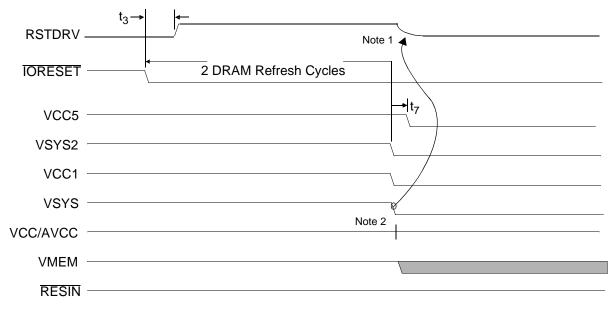

|            | Entering Micro Power Off Mode (DRAM Refresh Enabled)                           |      |

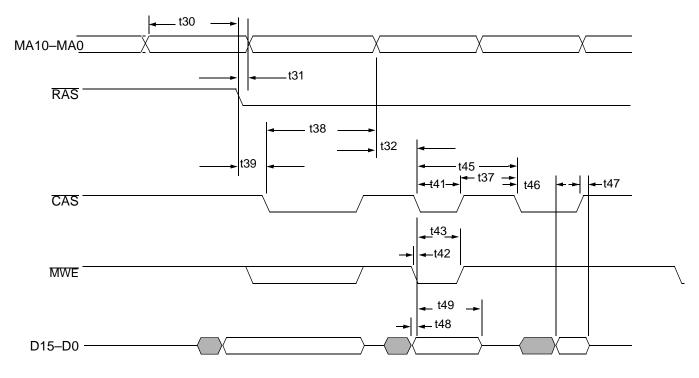

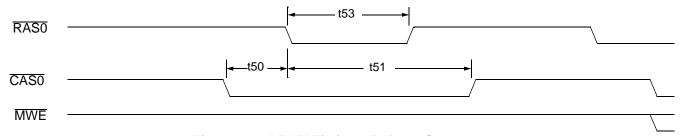

| Figure 36. | DRAM Timings, Page Hit                                                         | 93   |

|            | DRAM Timings, Refresh Cycle                                                    |      |

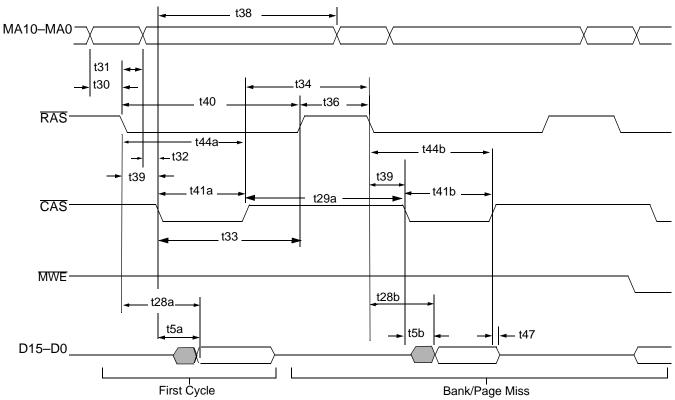

|            | DRAM First Cycle and Bank/Page Miss (Read Cycles)                              |      |

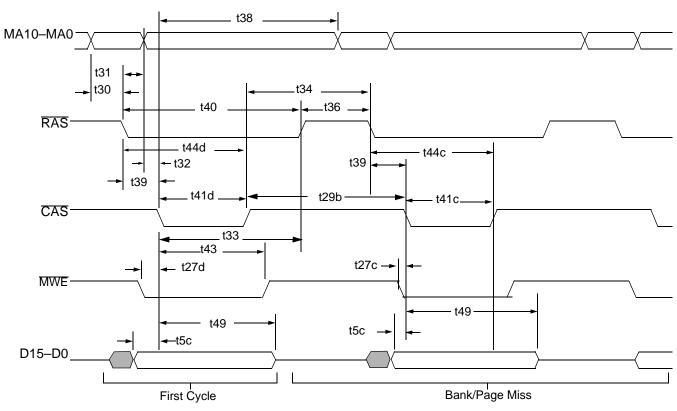

|            | DRAM First Cycle Bank/Page Miss (Write Cycles)                                 |      |

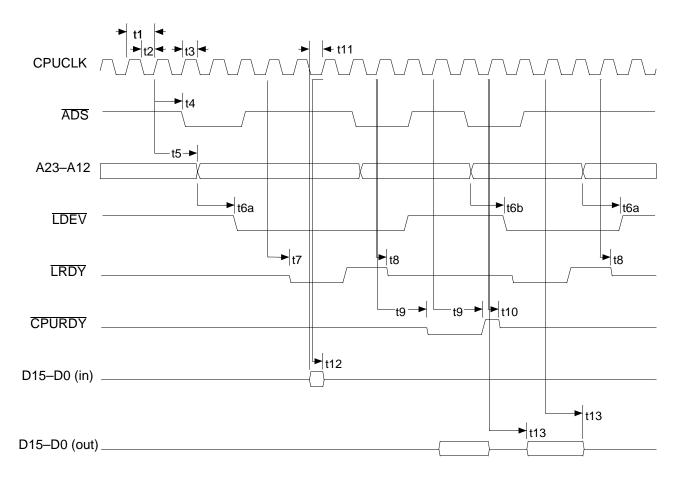

|            | Local Bus Interface                                                            |      |

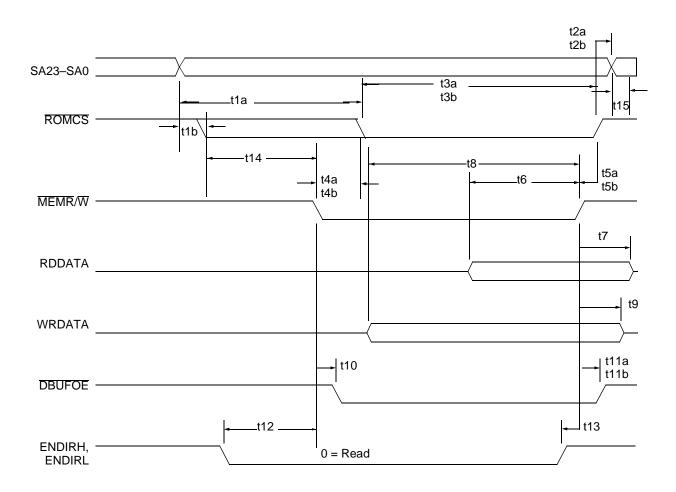

|            | BIOS ROM Read/Write 8-Bit Cycle                                                |      |

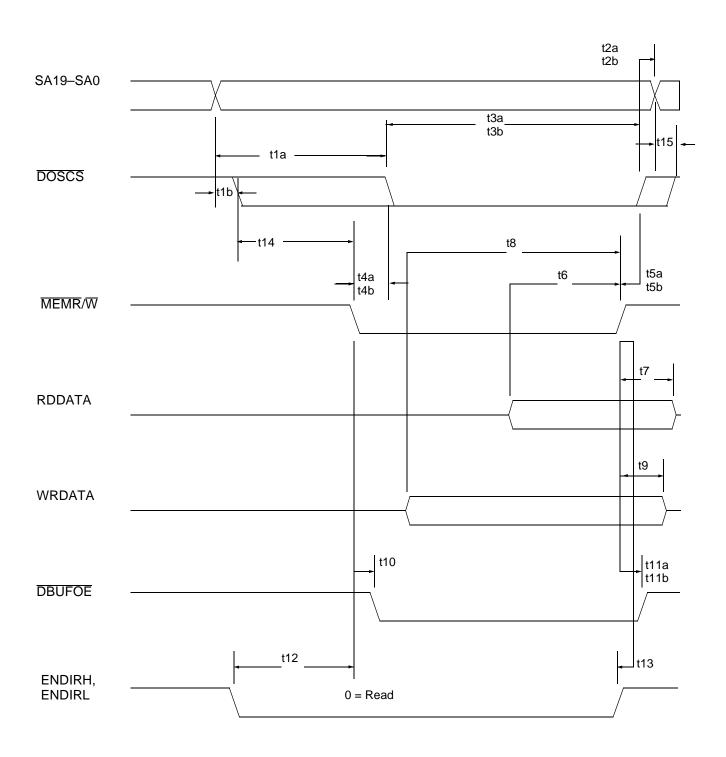

|            | DOS ROM Read/Write 8-Bit Cycle                                                 |      |

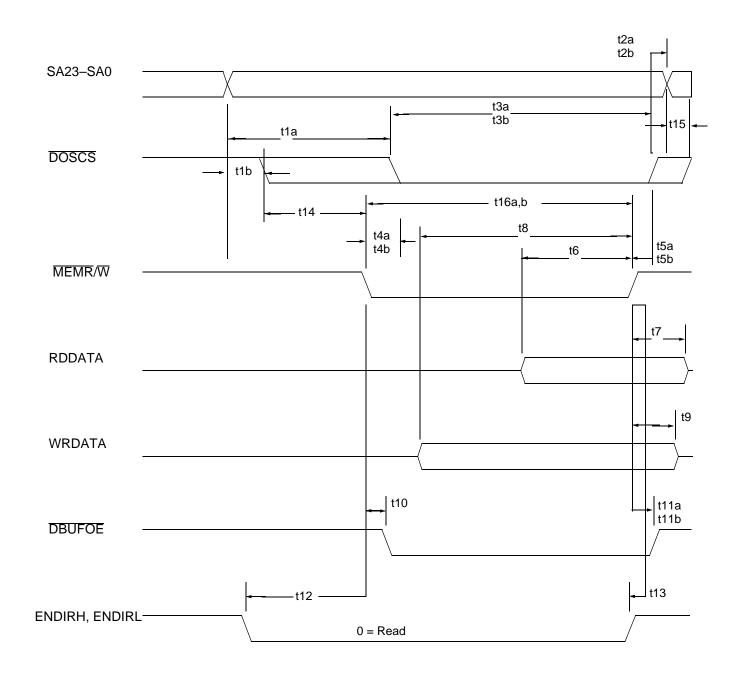

| •          | DOS ROM Read/Write 16-Bit Cycle                                                |      |

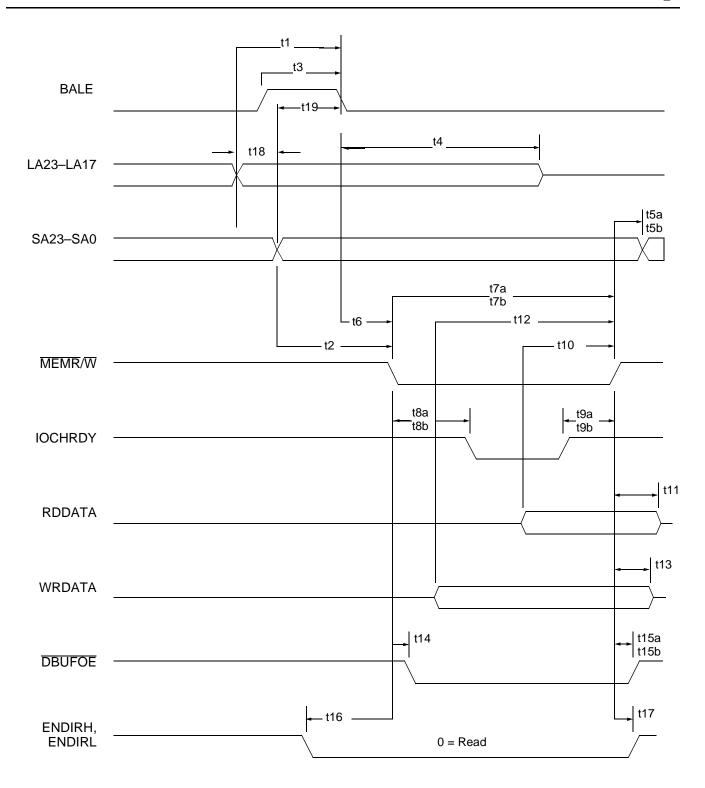

|            | ISA Memory Read/Write 8-Bit Cycle                                              |      |

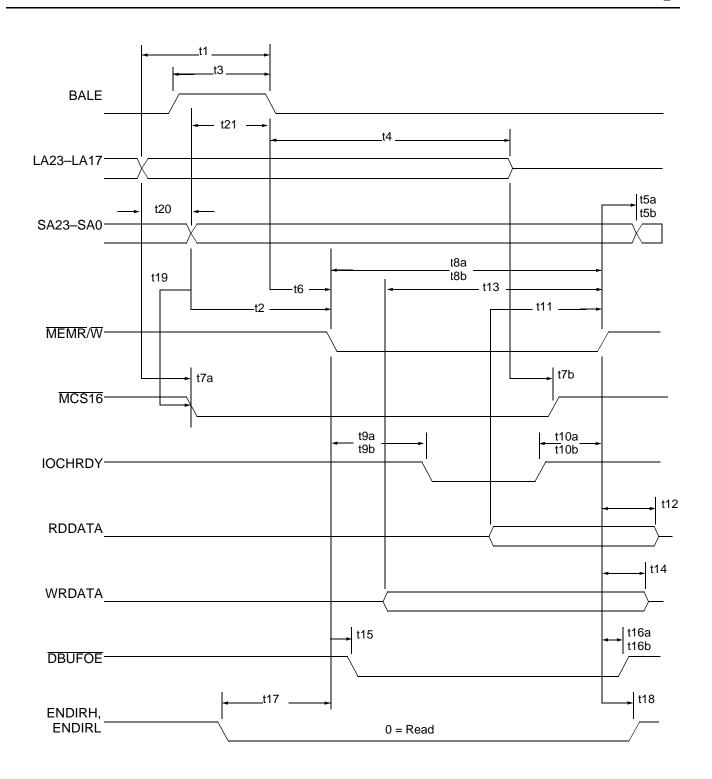

| Figure 45. | ISA Memory Read/Write 16-Bit Cycle                                             | 109  |

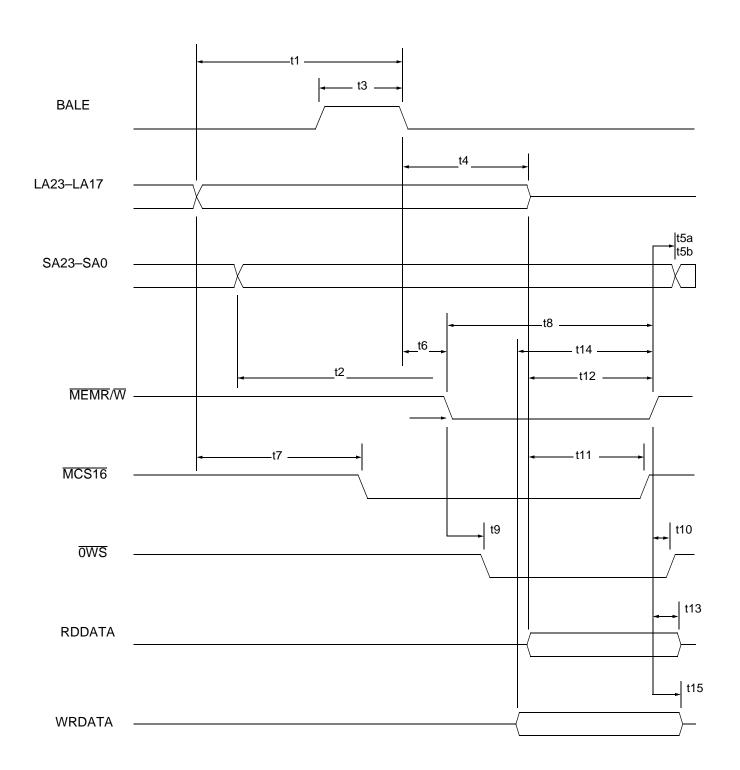

| Figure 46. | ISA Memory Read/Write 0 Wait State Cycle                                       | 111  |

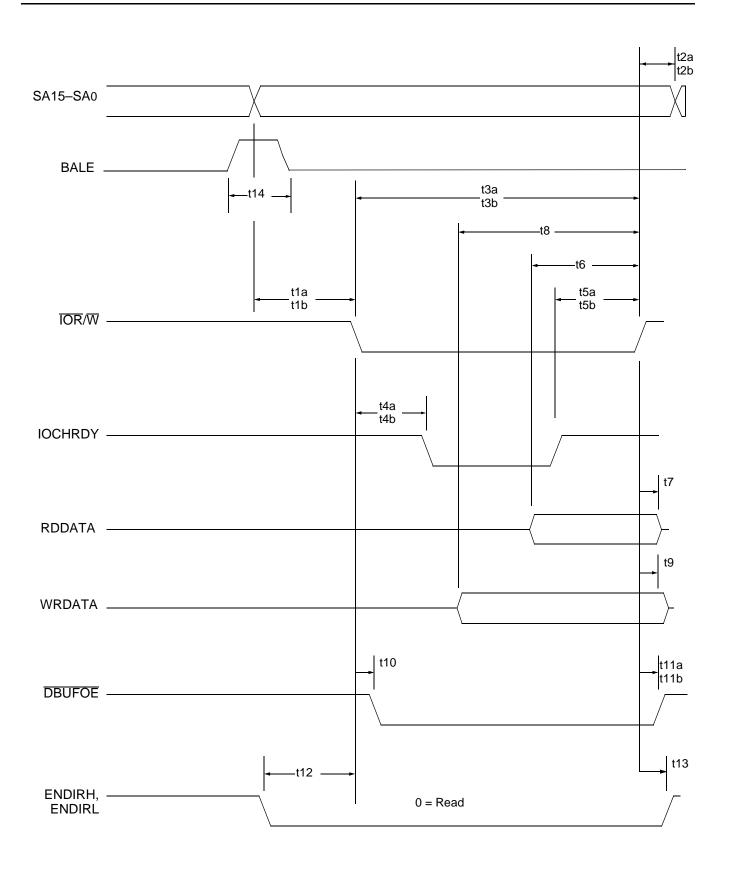

|            | ISA I/O 8-Bit Read/Write Cycle                                                 |      |

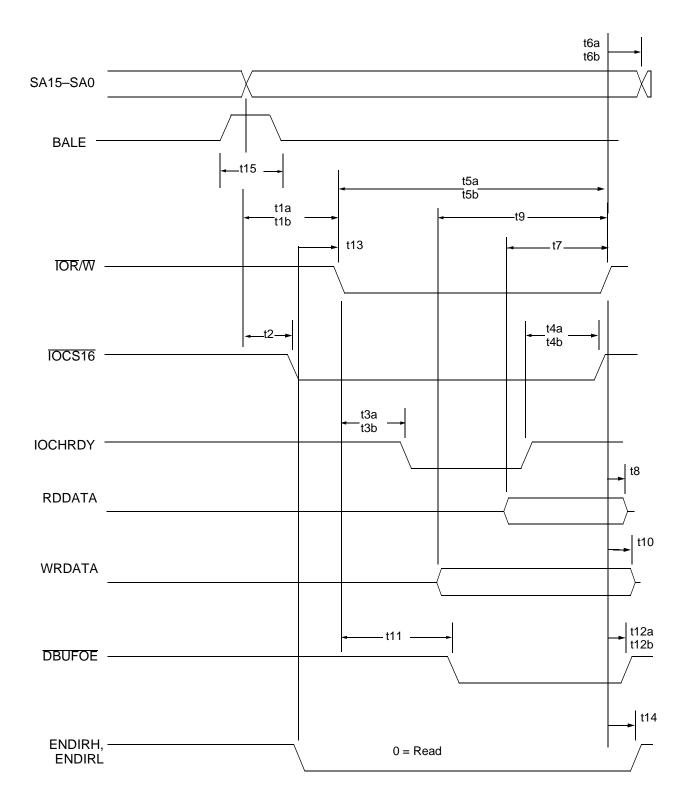

|            | ISA I/O 16-Bit Read/Write Cycle                                                |      |

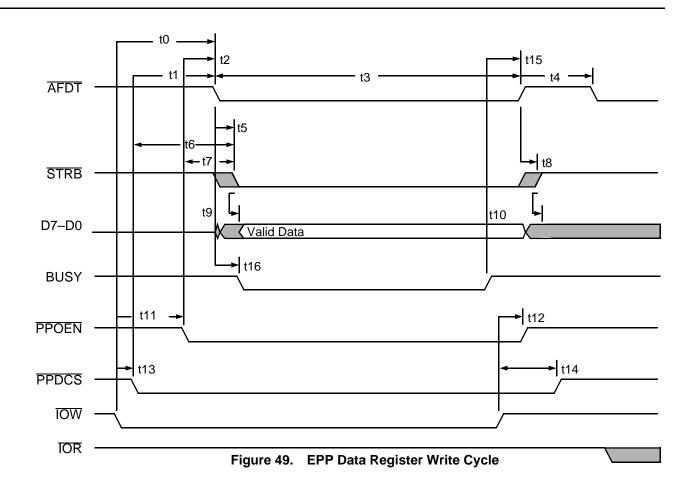

|            | EPP Data Register Write Cycle                                                  |      |

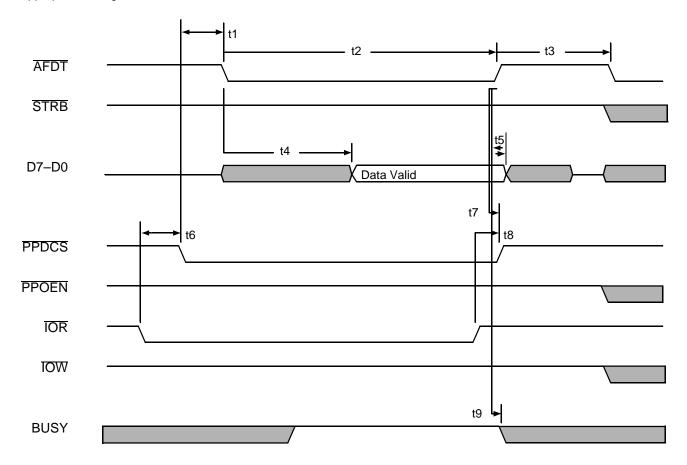

| Figure 50. | EPP Data Register Read Cycle                                                   | 117  |

## **LIST OF TABLES**

| Table 1.  | I/O Pin Voltage Level                                                                          | 21  |

|-----------|------------------------------------------------------------------------------------------------|-----|

| Table 2.  | Memory Bus Interface                                                                           | 22  |

| Table 3.  | System Interface                                                                               | 23  |

| Table 4.  | Keyboard Interface                                                                             | 24  |

| Table 5.  | Parallel Port Interface                                                                        | 25  |

| Table 6.  | Serial Port Interface                                                                          | 25  |

| Table 7.  | Power Management Interface                                                                     |     |

| Table 8.  | Local Bus Interface                                                                            |     |

| Table 9.  | Miscellaneous Interface                                                                        |     |

| Table 10. | Power Pins                                                                                     |     |

| Table 11. | Non-Multiplexed Address Signals Provided by MA11–MA0                                           |     |

| Table 12. | DRAM Mode Selection                                                                            |     |

| Table 13. | MA and SA Signal Pin Sharing                                                                   |     |

| Table 14. | Supported DRAM/SRAM Configuration                                                              |     |

| Table 15. | DRAM Address Translation (Page Mode)                                                           |     |

| Table 16. | DRAM Address Translation (Enhanced Page Mode)                                                  |     |

| Table 17. |                                                                                                |     |

| Table 18. |                                                                                                |     |

| Table 19. | High-Speed CPU Clock Frequencies                                                               |     |

| Table 20. | PLL Output                                                                                     |     |

| Table 21. | PMU Modes                                                                                      |     |

| Table 22. | Internal Clock States                                                                          |     |

| Table 23. | Internal I/O Pulldown States                                                                   |     |

| Table 24. | Parallel Port EPP Mode Pin Definition                                                          |     |

| Table 25. | External Resistor Requirements                                                                 |     |

| Table 26. | Bus Option Select Bit Logic                                                                    |     |

| Table 27. | Pins Shared Between Maximum ISA Bus and Local Bus Interface Functions                          |     |

| Table 28. |                                                                                                |     |

| Table 29. |                                                                                                |     |

| Table 30. | X1OUT Clock Source Pin Description                                                             |     |

| Table 31. | XT Keyboard Pin Description                                                                    |     |

| Table 32. | 14-MHz Clock Source                                                                            |     |

| Table 33. | ISA Bus Functionality                                                                          |     |

| Table 34. | ISA Bus Functionality Lost when Configured for Local Bus Mode                                  |     |

|           | Boundary Scan (JTAG) Cells—Order and Type                                                      |     |

|           | ÉlanSC310 Microcontroller JTAG Instruction Opcodes                                             |     |

| Table 37. | •                                                                                              | 03  |

| Table 07. | (Plastic Shrink Quad Flat Pack (QFP), 33 MHz, 3.3 V)                                           | 70  |

| Table 38. |                                                                                                | , 0 |

| Table 50. | (Plastic Shrink Quad Flat Pack (QFP), 33 MHz, 5 V)                                             | 71  |

| Table 39. |                                                                                                | 71  |

| Table 39. | Thermal Resistance (°C/Watt) $\psi_{JT}$ and $\theta_{JA}$ for 208-pin QFP and TQFP packages . | 72  |

| Table 41. | Typical Maximum ISA Mode Power Consumption                                                     |     |

| Table 41. | I/O Drive Type Description (Worst Case)                                                        |     |

| Table 43. | Recommended Oscillator Component Value Limits                                                  |     |

| Table 44. | Loop-Filter Component Values                                                                   |     |

| Table 45. | ·                                                                                              |     |

| Table 45. | DRAM Memory Interface, Page Hit and Refresh Cycle                                              |     |

| Table 46. |                                                                                                |     |

| Table 47. | DRAM First Cycle Read Access  DRAM Bank/Page Miss Read Cycles                                  |     |

| Table 46. | · · · · · · · · · · · · · · · · · · ·                                                          |     |

|           | DRAM First Cycle Write Access                                                                  |     |

| Table 50. | DRAM Bank/Page Miss Write Cycles                                                               | 90  |

## ADVANCE INFORMATION

| Table 51. | Local Bus Interface                               | . 98 |

|-----------|---------------------------------------------------|------|

| Table 52. | BIOS ROM Read/Write 8-Bit Cycle                   | 100  |

| Table 53. | DOS ROM Read/Write 8-Bit Cycle                    | 102  |

| Table 54. | DOS ROM and Fast DOS ROM Read/Write 16-Bit Cycles | 104  |

| Table 55. | ISA Memory Read/Write 8-Bit Cycle                 | 106  |

| Table 56. | ISA Memory Read/Write 16-Bit Cycle                | 108  |

| Table 57. | ISA Memory Read/Write 0 Wait State Cycle          | 110  |

| Table 58. | ISA I/O 8-Bit Read/Write Cycle                    | 112  |

| Table 59. | ISA I/O 16-Bit Read/Write Cycle                   | 114  |

| Table 60. | EPP Data Register Write Cycle                     | 116  |

| Table 61. | EPP Data Register Read Cycle                      | 117  |

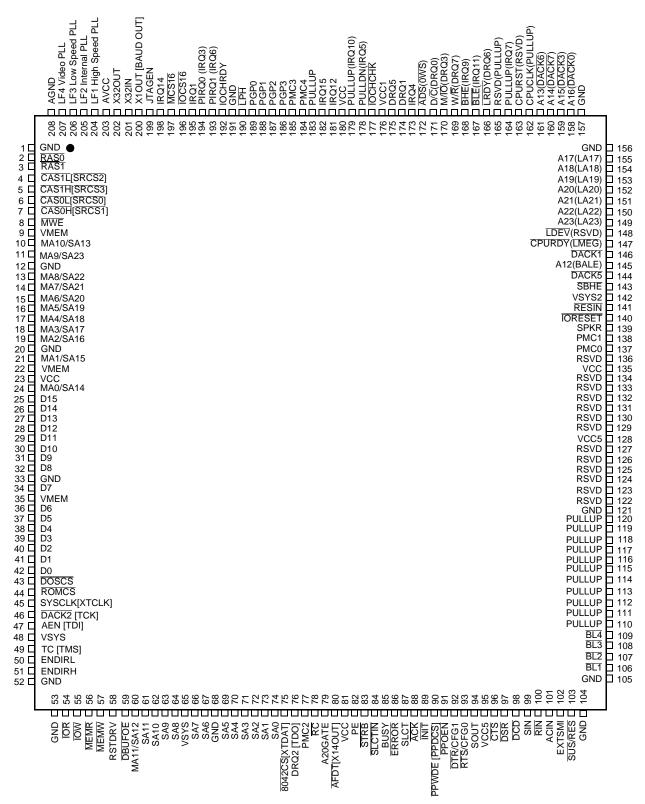

## CONNECTION DIAGRAM

## Notes:

Pin 1 is marked for designation purposes only.

## **ÉLANSC310 MICROCONTROLLER PIN DESIGNATIONS**

This section, beginning with the Connection Diagram on the preceding page, identifies the pins of the ÉlanSC310 microcontroller and lists the signals associated with each pin. Tables 2–10, beginning on page 22, group these signals according to function. The table beginning on page 13 lists the pins sorted by pin number; the table beginning on page 15 lists the pins sorted by pin name along with the corresponding pin number, functional grouping, Pin State table number, and the page number where a description of the pin is located.

The Signal Name column in the pin designation table (sorted by pin number), and in Tables 2–10, is decoded as follows:

## NAME1 / NAME2 [NAME3] (NAME4)

**NAME1 -** This is the pin function when the ÉlanSC310 microcontroller has been configured, at reset, for the Local Bus mode of operation. If the pin only has one function regardless of the mode, NAME1 is the only name given.

**NAME2 -** This is the secondary pin function (by default) when the ÉlanSC310 microcontroller has been configured, at reset, for the Local Bus mode of operation. If the pin always has two functions regardless of the mode, NAME1 followed by NAME2 are the only names given.

**NAME3 -** This is a tertiary pin function that must be enabled specifically by firmware. As an example, for pins DACK2[TCK], DRQ2[TDO], AEN[TDI], and TC[TMS], the NAME3 function is selected by the JTAGEN pin being asserted High (JTAG ENABLE).

**NAME4** - Designates the pin function when the ÉlanSC310 microcontroller has been configured, at reset, for the Maximum ISA mode of operation.

**RSVD** - Pins marked with this designator are required to remain unconnected.

**PULLUP - Needs external pull-up resistor.**

PULLDN - Needs external pull-down resistor.

The Signal Name column in the pin designation table (sorted by pin name), beginning on page 13, contains an alphabetical listing of all pin names, followed by their corresponding alternate pin names in the applicable format from those listed here:

NAME1 / NAME2 [NAME3] (NAME4 / NAME5) NAME2 / NAME1 [NAME3] (NAME4 / NAME5) [NAME3] (NAME4 / NAME5) NAME1 / NAME2 (NAME4 / NAME5) NAME1 / NAME2 [NAME3] (NAME5 / NAME4) NAME1 / NAME2 [NAME3]

For more information about how pins are shared and which functions are available in each bus mode, see "Alternate Pin Functions" on page 59

## PIN DESIGNATIONS (SORTED BY PIN NUMBER)

| Pin No. | Signal Name<br>(Alternate Functions) | Pin No. | Signal Name<br>(Alternate Functions) | Pin No. | Signal Name<br>(Alternate Functions) |  |

|---------|--------------------------------------|---------|--------------------------------------|---------|--------------------------------------|--|

| 1       | GND                                  | 44      | ROMCS                                | 87      | SLCT                                 |  |

| 2       | RAS0                                 | 45      | SYSCLK [XTCLK]                       | 88      | ACK                                  |  |

| 3       | RAS1                                 | 46      | DACK2 [TCK]                          | 89      | ĪNĪT                                 |  |

| 4       | CAS1L [SRCS2]                        | 47      | AEN [TDI]                            | 90      | PPDWE [PPDCS]                        |  |

| 5       | CAS1H [SRCS3]                        | 48      | VSYS                                 | 91      | PPOEN                                |  |

| 6       | CASOL [SRCSO]                        | 49      | TC [TMS]                             | 92      | DTR/CFG1                             |  |

| 7       | CASOH [SRCS1]                        | 50      | ENDIRL                               | 93      | RTS/CFG0                             |  |

| 8       | MWE                                  | 51      | ENDIRH                               | 94      | SOUT                                 |  |

| 9       | VMEM                                 | 52      | GND                                  | 95      | VCC5                                 |  |

| 10      | MA10/SA13                            | 53      | GND                                  | 96      | CTS                                  |  |

| 11      | MA9/SA23                             | 54      | ĪŌR                                  | 97      | DSR                                  |  |

| 12      | GND                                  | 55      | ĪŌW                                  | 98      | DCD                                  |  |

| 13      | MA8/SA22                             | 56      | MEMR                                 | 99      | SIN                                  |  |

| 14      | MA7/SA21                             | 57      | MEMW                                 | 100     | RIN                                  |  |

| 15      | MA6/SA20                             | 58      | RSTDRV                               | 101     | ACIN                                 |  |

| 16      | MA5/SA19                             | 59      | DBUFOE                               | 102     | EXTSMI                               |  |

| 17      | MA4/SA18                             | 60      | MA11/SA12                            | 103     | SUS/RES                              |  |

| 18      | MA3/SA17                             | 61      | SA11                                 | 104     | GND                                  |  |

| 19      | MA2/SA16                             | 62      | SA10                                 | 105     | GND                                  |  |

| 20      | GND                                  | 63      | SA9                                  | 106     | BL1                                  |  |

| 21      | MA1/SA15                             | 64      | SA8                                  | 107     | BL2                                  |  |

| 22      | VMEM                                 | 65      | VSYS                                 | 108     | BL3                                  |  |

| 23      | VCC                                  | 66      | SA7                                  | 109     | BL4                                  |  |

| 24      | MA0/SA14                             | 67      | SA6                                  | 110     | PULLUP                               |  |

| 25      | D15                                  | 68      | GND                                  | 111     | PULLUP                               |  |

| 26      | D14                                  | 69      | SA5                                  | 112     | PULLUP                               |  |

| 27      | D13                                  | 70      | SA4                                  | 113     | PULLUP                               |  |

| 28      | D12                                  | 71      | SA3                                  | 114     | PULLUP                               |  |

| 29      | D11                                  | 72      | SA2                                  | 115     | PULLUP                               |  |

| 30      | D10                                  | 73      | SA1                                  | 116     | PULLUP                               |  |

| 31      | D9                                   | 74      | SA0                                  | 117     | PULLUP                               |  |

| 32      | D8                                   | 75      | 8042CS [XTDAT]                       | 118     | PULLUP                               |  |

| 33      | GND                                  | 76      | DRQ2 [TDO]                           | 119     | PULLUP                               |  |

| 34      | D7                                   | 77      | PMC2                                 | 120     | PULLUP                               |  |

| 35      | VMEM                                 | 78      | RC                                   | 121     | GND                                  |  |

| 36      | D6                                   | 79      | A20GATE                              | 122     | RSVD                                 |  |

| 37      | D5                                   | 80      | ĀFDT [X14OUT]                        | 123     | RSVD                                 |  |

| 38      | D4                                   | 81      | VCC                                  | 124     | RSVD                                 |  |

| 39      | D3                                   | 82      | PE                                   | 125     | RSVD                                 |  |

| 40      | D2                                   | 83      | STRB                                 | 126     | RSVD                                 |  |

| 41      | D1                                   | 84      | SLCTIN                               | 127     | RSVD                                 |  |

| 42      | D0                                   | 85      | BUSY                                 | 128     | VCC5                                 |  |

| 43      | DOSCS                                | 86      | ERROR                                | 129     | RSVD                                 |  |

| Pin No. | Signal Name<br>(Alternate Functions) | Pin No. | Signal Name<br>(Alternate Functions) | Pin No. | Signal Name<br>(Alternate Functions) |

|---------|--------------------------------------|---------|--------------------------------------|---------|--------------------------------------|

| 130     | RSVD                                 | 157     | GND                                  | 184     | PMC4                                 |

| 131     | RSVD                                 | 158     | A16 (DACKO)                          | 185     | PMC3                                 |

| 132     | RSVD                                 | 159     | A15 (DACK3)                          | 186     | PGP3                                 |

| 133     | RSVD                                 | 160     | A14 (DACK7)                          | 187     | PGP2                                 |

| 134     | RSVD                                 | 161     | A13 (DACK6)                          | 188     | PGP1                                 |

| 135     | VCC                                  | 162     | CPUCLK (PULLUP)                      | 189     | PGP0                                 |

| 136     | RSVD                                 | 163     | CPURST (RSVD)                        | 190     | LPH .                                |

| 137     | PMC0                                 | 164     | PULLUP (IRQ7)                        | 191     | GND                                  |

| 138     | PMC1                                 | 165     | RSVD (PULLUP)                        | 192     | IOCHRDY                              |

| 139     | SPKR                                 | 166     | LRDY (DRQ6)                          | 193     | PIRQ1(IRQ6)                          |

| 140     | IORESET                              | 167     | BLE (IRQ11)                          | 194     | PIRQ0 (IRQ3)                         |

| 141     | RESIN                                | 168     | BHE (IRQ9)                           | 195     | IRQ1                                 |

| 142     | VSYS2                                | 169     | W/R (DRQ7)                           | 196     | IOCS16                               |

| 143     | SBHE                                 | 170     | M/IO (DRQ3)                          | 197     | MCS16                                |

| 144     | DACK5                                | 171     | D/C (DRQ0)                           | 198     | IRQ14                                |

| 145     | A12(BALE)                            | 172     | ADS (OWS)                            | 199     | JTAGEN                               |

| 146     | DACK1 (DACK1)                        | 173     | IRQ4                                 | 200     | X1OUT [BAUD_OUT]                     |

| 147     | CPURDY (LMEG)                        | 174     | DRQ1                                 | 201     | X32IN                                |

| 148     | LDEV (RSVD)                          | 175     | DRQ5                                 | 202     | X32OUT                               |

| 149     | A23 (LA23)                           | 176     | VCC1                                 | 203     | AVCC                                 |

| 150     | A22 (LA22)                           | 177     | IOCHCHK                              | 204     | LF1                                  |

| 151     | A21 (LA21)                           | 178     | PULLDN (IRQ5)                        | 205     | LF2                                  |

| 152     | A20 (LA20)                           | 179     | PULLUP (IRQ10)                       | 206     | LF3                                  |

| 153     | A19 (LA19)                           | 180     | VCC                                  | 207     | LF4                                  |

| 154     | A18 (LA18)                           | 181     | IRQ12                                | 208     | AGND                                 |

| 155     | A17 (LA17)                           | 182     | IRQ15                                | -       | -                                    |

| 156     | GND                                  | 183     | PULLUP                               | -       | -                                    |

## PIN DESIGNATIONS (SORTED BY PIN NAME)

| Signal Name                       | Pin No. | Function                   | Pin State<br>Table No. | Description Page No. |

|-----------------------------------|---------|----------------------------|------------------------|----------------------|

| ( <del>OWS</del> ) <del>ADS</del> | 172     | Maximum ISA bus interface  | 7                      | 36                   |

| 8042CS [XTDAT]                    | 75      | Keyboard interface         | 3                      | 32                   |

| A12 (BALE)                        | 145     | Local bus interface        | 7                      | 36                   |

| A13 ( <del>DACK6</del> )          | 161     | Local bus interface        | 7                      | 36                   |

| A14 ( <del>DACK7</del> )          | 160     | Local bus interface        | 7                      | 36                   |

| A15 ( <del>DACK3</del> )          | 159     | Local bus interface        | 7                      | 36                   |

| A16 ( <del>DACK0</del> )          | 158     | Local bus interface        | 7                      | 36                   |

| A17 (LA17)                        | 155     | Local bus interface        | 7                      | 36                   |

| A18 (LA18)                        | 154     | Local bus interface        | 7                      | 36                   |

| A19 (LA19)                        | 153     | Local bus interface        | 7                      | 36                   |

| A20 (LA20)                        | 152     | Local bus interface        | 7                      | 36                   |

| A20GATE                           | 79      | Keyboard interface         | 3                      | 33                   |

| A21 (LA21)                        | 151     | Local bus interface        | 7                      | 36                   |

| A22 (LA22)                        | 150     | Local bus interface        | 7                      | 36                   |

| A23 (LA23)                        | 149     | Local bus interface        | 7                      | 36                   |

| ACIN                              | 101     | Power management interface | 6                      | 34                   |

| ACK                               | 88      | Parallel port interface    | 4                      | 33                   |

| ADS (OWS)                         | 172     | Local bus interface        | 7                      | 35                   |

| AEN [TDI]                         | 47      | System interface           | 2                      | 31                   |

| AFDT [X14OUT]                     | 80      | Parallel port interface    | 4                      | 33                   |

| AGND                              | 208     | Power                      | 9                      | 37                   |

| AVCC                              | 203     | Power                      | 9                      | 37                   |

| (BALE) A12                        | 145     | Maximum ISA bus interface  | 7                      | 36                   |

| [BAUD_OUT] X1OUT                  | 200     | Miscellaneous interface    | 8                      | 35                   |

| BHE (IRQ9)                        | 168     | Local bus interface        | 7                      | 35                   |

| BL1                               | 106     | Power management interface | 6                      | 34                   |

| BL2                               | 107     | Power management interface | 6                      | 34                   |

| BL3                               | 108     | Power management interface | 6                      | 34                   |

| BL4                               | 109     | Power management interface | 6                      | 34                   |

| BLE (IRQ11)                       | 167     | Local bus interface        | 7                      | 35                   |

| BUSY                              | 85      | Parallel port interface    | 4                      | 33                   |

| CAS0H [SRCS1]                     | 7       | Memory bus interface       | 1                      | 30                   |

| CASOL [SRCSO]                     | 6       | Memory bus interface       | 1                      | 30                   |

| CAS1H [SRCS3]                     | 5       | Memory bus interface       | 1                      | 30                   |

| CAS1L [SRCS2]                     | 4       | Memory bus interface       | 1                      | 30                   |

| CFG0/RTS                          | 93      | Serial port interface      | 5                      | 34                   |

| CFG/DTR                           | 92      | Serial port interface      | 5                      | 34                   |

| CPUCLK (PULLUP)                   | 162     | Local bus interface        | 7                      | 35                   |

| CPURDY (LMEG)                     | 147     | Local bus interface        | 7                      | 35                   |

| CPURST (RSVD)                     | 163     | Local bus interface        | 7                      | 35                   |

| CTS                               | 96      | Serial port interface      | 5                      | 33                   |

| D/C (DRQ0)                        | 171     | Maximum ISA bus interface  | 7                      | 35                   |

| D0                                | 42      | System interface           | 2                      | 31                   |

| Signal Name Pin N        |                                                    | Function                            | Pin State<br>Table No. | Description Page No. |  |

|--------------------------|----------------------------------------------------|-------------------------------------|------------------------|----------------------|--|

| D1                       | 41                                                 | System interface                    | 2                      | 31                   |  |

| D10                      | 30                                                 | System interface                    | 2                      | 31                   |  |

| D11                      | 29                                                 | System interface                    |                        |                      |  |

| D12                      | 28                                                 | System interface                    | 2                      | 31                   |  |

| D13                      | 27                                                 | System interface                    | 2                      | 31                   |  |

| D14                      | 26                                                 | System interface                    | 2                      | 31                   |  |

| D15                      | 25                                                 | System interface                    | 2                      | 31                   |  |

| D2                       | 40                                                 | System interface                    | 2                      | 31                   |  |

| D3                       | 39                                                 | System interface                    | 2                      | 31                   |  |

| D4                       | 38                                                 | System interface                    | 2                      | 31                   |  |

| D5                       | 37                                                 | System interface                    | 2                      | 31                   |  |

| D6                       | 36                                                 | System interface                    | 2                      | 31                   |  |

| D7                       | 34                                                 | System interface                    | 2                      | 31                   |  |

| D8                       | 32                                                 | System interface                    | 2                      | 31                   |  |

| D9                       | 31                                                 | System interface                    | 2                      | 31                   |  |

| ( <del>DACK0</del> ) A16 | 158                                                | Maximum ISA bus interface           | 7                      | 36                   |  |

| DACK1 (DACK1)            | 146                                                | Local and maximum ISA bus interface | 2                      | 36                   |  |

| DACK2 [TCK]              | 46                                                 | Local and maximum ISA bus interface | 2                      | 31, 36               |  |

| (DACK3) A15              | 159                                                | Maximum ISA bus interface           | 7                      | 36                   |  |

| DACK5                    | 144                                                | Maximum ISA bus interface           | 2                      | 36                   |  |

| ( <del>DACK6</del> ) A13 | 161                                                | Maximum ISA bus interface           | 7                      | 36                   |  |

| (DACK7) A14              | 160                                                | Maximum ISA interface               | 7                      | 36                   |  |

| DBUFOE                   | 59                                                 | System interface                    | 2                      | 31                   |  |

| D/C (DRQ0)               | 171                                                | Local bus interface                 | 2                      | 35                   |  |

| DCD                      | 98                                                 | Serial port interface               | 5                      | 33                   |  |

| DOSCS                    | 43                                                 | Memory bus interface                | 1                      | 30                   |  |

| (DRQ0) D/C               | 171                                                | Maximum ISA bus interface           | 7                      | 36                   |  |

| DRQ1                     | 174                                                | Local and Maximum ISA bus interface | 2                      | 36                   |  |

| DRQ2 [TDO]               | 76                                                 | Local and Maximum ISA interface     | 2                      | 31, 36               |  |

| (DRQ3) M/IO              | 170                                                | Maximum ISA bus interface           | 7                      | 36                   |  |

| DRQ5                     | 175                                                | Local and Maximum ISA bus interface | 2                      | 36                   |  |

| (DRQ6) LRDY              | 166                                                | Maximum ISA bus interface           | 7                      | 36                   |  |

| (DRQ7) W/R               | 169                                                | Maximum ISA bus interface           | •                      | 36                   |  |

| DSR                      | 97                                                 | Serial port interface               | 5                      | 33                   |  |

| DTR/CFG1                 | 92                                                 | Serial port interface               | 5                      | 34                   |  |

| ENDIRH                   | 51                                                 | System interface                    | 2                      | 31                   |  |

| ENDIRL                   | 50                                                 | System interface                    | 2                      | 31                   |  |

| ERROR                    | 86                                                 | Parallel port interface             | 4                      | 33                   |  |

| EXTSMI                   | 102                                                | Power management interface          | 6                      | 34                   |  |

| GND                      | 1, 12, 20,<br>33, 52, 53,<br>68, 104,<br>105, 121, | Power                               | 9                      | 37                   |  |

|                          | 105, 121,<br>156, 157,<br>191                      |                                     |                        |                      |  |

| Signal Name    | Pin No. | Function                             | Pin State<br>Table No. | Description Page No. |

|----------------|---------|--------------------------------------|------------------------|----------------------|

| ĪNIT           | 89      | Parallel port interface              | 4                      | 33                   |

| TOCHCHK        | 177     | Maximum ISA bus interface            | 2                      | 36                   |

| IOCHRDY        | 192     | System interface                     | 2                      | 31                   |

| IOCS16         | 196     | System interface                     | 2                      | 31                   |

| ĪŌR            | 54      | System interface                     | 2                      | 31                   |

| IORESET        | 140     | Reset and power                      | 8                      | 37                   |

| ĪOW            | 55      | System interface                     | 2                      | 31                   |

| IRQ1           | 195     | System and maximum ISA bus interface | 2                      | 32, 36               |

| (IRQ10) PULLUP | 179     | Maximum ISA bus interface            | 7                      | 36                   |

| (IRQ11) BLE    | 167     | Maximum ISA bus interface            | 7                      | 36                   |

| IRQ12          | 181     | System interface                     | 2                      | 36                   |

| IRQ14          | 198     | System and maximum ISA bus interface | 2                      | 32, 36               |

| IRQ15          | 182     | System interface                     | 2                      | 36                   |

| (IRQ3) PIRQ0   | 194     | System interface                     | 2                      | 36                   |

| IRQ4           | 173     | System interface                     | 2                      | 36                   |

| (IRQ5) PULLDN  | 178     | Maximum ISA bus interface            | 7                      | 36                   |

| (IRQ6) PIRQ1   | 193     | Maximum ISA bus interface            | 2                      | 36                   |

| (IRQ7) PULLUP  | 164     | Maximum ISA bus interface            | 7                      | 36                   |

| (IRQ9) BHE     | 168     | Maximum ISA bus interface            | 7                      | 36                   |

| JTAGEN         | 199     | JTAG boundary scan interface         | 8                      | 37                   |

| (LA17) A17     | 155     | Maximum ISA bus interface            | 7                      | 36                   |

| (LA18) A18     | 154     | Maximum ISA bus interface            | 7                      | 36                   |

| (LA19) A19     | 153     | Maximum ISA bus interface            | 7                      | 36                   |

| (LA20) A20     | 152     | Maximum ISA bus interface            | 7                      | 36                   |

| (LA21) A21     | 151     | Maximum ISA bus interface            | 7                      | 36                   |

| (LA22) A22     | 150     | Maximum ISA bus interface            | 7                      | 36                   |

| (LA23) A23     | 149     | Maximum ISA bus interface            | 7                      | 36                   |

| LDEV (RSVD)    | 148     | Local bus interface                  | 7                      | 35                   |

| LF1            | 204     | Miscellaneous interface              | 8                      | 35                   |

| LF2            | 205     | Miscellaneous interface              | 8                      | 35                   |

| LF3            | 206     | Miscellaneous interface              | 8                      | 35                   |

| LF4            | 207     | Miscellaneous interface              | 8                      | 35                   |

| (LMEG) CPURDY  | 147     | Maximum ISA bus interface            | 7                      | 36                   |

| LPH            | 190     | Power management interface           | 6                      | 34                   |

| LRDY (DRQ6)    | 166     | Local bus interface                  | 7                      | 36                   |

| M/IO (DRQ3)    |         |                                      | 7                      | +                    |

| MA0/SA14       | 170     | Local bus interface                  |                        | 36                   |

|                | 24      | Memory bus interface                 | 1                      | 30                   |

| MA1/SA15       | 21      | Memory bus interface                 | 1                      | 30                   |

| MA10/SA13      | 10      | Memory bus interface                 | 1                      | 30                   |

| MA11/SA12      | 60      | Memory bus interface                 | 1                      | 30                   |

| MA2/SA16       | 19      | Memory bus interface                 | 1                      | 30                   |

| MA3/SA17       | 18      | Memory bus interface                 | 1                      | 30                   |

| MA4/SA18       | 17      | Memory bus interface                 | 1                      | 30                   |

| MA5/SA19       | 16      | Memory bus interface                 | 1                      | 30                   |

| Signal Name     | Pin No.                      | Function                             | Pin State<br>Table No. | Description Page No. |

|-----------------|------------------------------|--------------------------------------|------------------------|----------------------|

| MA6/SA20        | 15                           | Memory bus interface                 | 1                      | 30                   |

| MA7/SA21        | 14                           | Memory bus interface                 | 1                      | 30                   |

| MA8/SA22        | 13                           | Memory bus interface                 | 1                      | 30                   |

| MA9/SA23        | 11                           | Memory bus interface                 | 1                      | 30                   |

| MCS16           | 197                          | System interface                     | 2                      | 32                   |

| MEMR            | 56                           | System interface                     | 2                      | 32                   |

| MEMW            | 57                           | System interface                     | 2                      | 32                   |

| MWE             | 8                            | Memory bus interface                 | 1                      | 30                   |

| PE              | 82                           | Parallel port interface              | 4                      | 33                   |

| PGP0            | 189                          | Power management interface           | 6                      | 34                   |

| PGP1            | 188                          | Power management interface           | 6                      | 34                   |

| PGP2            | 187                          | Power management interface           | 6                      | 34                   |

| PGP3            | 186                          | Power management interface           | 6                      | 34                   |

| PIRQ0 (IRQ3)    | 194                          | System and maximum ISA bus interface | 2                      | 32, 36               |

| PIRQ1 (IRQ6)    | 193                          | System and maximum ISA bus interface | 2                      | 32, 36               |

| PMC0            | 137                          | Power management interface           | 6                      | 34                   |

| PMC1            | 138                          | Power management interface           | 6                      | 34                   |

| PMC2            | 77                           | Power management interface           | 6                      | 34                   |

| PMC3            | 185                          | Power management interface           | 6                      | 34                   |

| PMC4            | 184                          | Power management interface           | 6                      | 34                   |

| PPDCS           | 90                           | Parallel port interface              | 4                      | 33                   |

| PPDWE [PPDCS]   | 90                           | Parallel port interface              | 4                      | 33                   |

| PPOEN           | 91                           | Parallel port interface              | 4                      | 33                   |

| PULLDN (IRQ5)   | 178                          | Miscellaneous interface              | 8                      | 12                   |

| PULLUP          | 110–120,<br>164, 179,<br>183 | Miscellaneous interface              | 8                      | 12                   |

| (PULLUP) CPUCLK | 162                          | Local bus interface                  | 7                      | 12                   |

| (PULLUP) RSVD   | 165                          | Local bus interface                  | 7                      | 12                   |

| RAS0            | 2                            | Memory bus interface                 | 1                      | 30                   |

| RAS1            | 3                            | Memory bus interface                 | 1                      | 30                   |

| RC              | 78                           | Keyboard interface                   | 3                      | 33                   |

| RESIN           | 141                          | Reset and power                      | 8                      | 37                   |

| RIN             | 100                          | Serial port interface                | 5                      | 34                   |

| ROMCS           | 44                           | Memory bus interface                 | 1                      | 30                   |

| RSTDRV          | 58                           | System interface                     | 2                      | 32                   |

| RSVD            | 122–127,<br>129–134,<br>136  | Miscellaneous interface              | 8                      | 12                   |

| RSVD (PULLUP)   | 165                          | Miscellaneous interface              | 7                      | 12                   |

| (RSVD) CPURST   | 163                          | Miscellaneous interface              | 7                      | 35                   |

| (RSVD) LDEV     | 148                          | Miscellaneous interface              | 7                      | 35                   |

| RTS/CFG0        | 93                           | Serial port interface                | 5                      | 34                   |

| SA0             | 74                           | System interface                     | 2                      | 32                   |

| SA1             | 73                           | System interface                     | 2                      | 32                   |

| Signal Name    | Pin No.             | Function                     | Pin State<br>Table No. | Description Page No. |

|----------------|---------------------|------------------------------|------------------------|----------------------|

| SA10           | 62                  | System interface             | 2                      | 32                   |

| SA11           | 61                  | System interface             | 2                      | 32                   |

| SA12/MA11      | 60                  | System interface             | 2                      | 30                   |

| SA13/MA10      | 10                  | System interface             | 2                      | 30                   |

| SA14/MA0       | 24                  | System interface             | 2                      | 30                   |

| SA15/MA1       | 21                  | System interface             | 2                      | 30                   |

| SA16/MA2       | 19                  | System interface             | 2                      | 30                   |

| SA17/MA3       | 18                  | System interface             | 2                      | 30                   |

| SA18/MA4       | 17                  | System interface             | 2                      | 30                   |

| SA19/MA5       | 16                  | System interface             | 2                      | 30                   |

| SA2            | 72                  | System interface             | 2                      | 32                   |

| SA20/MA6       | 15                  | System interface             | 2                      | 30                   |

| SA21/MA7       | 14                  | System interface             | 2                      | 30                   |

| SA22/MA8       | 13                  | System interface             | 2                      | 30                   |

| SA23/MA9       | 11                  | System interface             | 2                      | 30                   |

| SA3            | 71                  | System interface             | 2                      | 32                   |

| SA4            | 70                  | System interface             | 2                      | 32                   |

| SA5            | 69                  | System interface             | 2                      | 32                   |

| SA6            | 67                  | System interface             | 2                      | 32                   |

| SA7            | 66                  | System interface             | 2                      | 32                   |

| SA8            | 64                  | System interface             | 2                      | 32                   |

| SA9            | 63                  | System interface             | 2                      | 32                   |

| SBHE           | 143                 | System interface             | 2                      | 32                   |

| SIN            | 99                  | Serial port interface        | 5                      | 34                   |

| SLCT           | 87                  | Parallel port interface      | 4                      | 33                   |

| SLCTIN         | 84                  | Parallel port interface      | 4                      | 33                   |

| SOUT           | 94                  | Serial port interface        | 5                      | 34                   |

| SPKR           | 139                 | Miscellaneous interface      | 8                      | 32                   |

| [SRCS0] CAS0L  | 6                   | Memory bus interface         | 1                      | 30                   |

| [SRCS1] CAS0H  | 7                   | Memory bus interface         | 1                      | 30                   |

| [SRCS2] CAS1L  | 4                   | Memory bus interface         | 1                      | 30                   |

| [SRCS3] CAS1H  | 5                   | Memory bus interface         | 1                      | 30                   |

| STRB           | 83                  | Parallel port interface      | 4                      | 33                   |

| SUS/RES        | 103                 | Power management interface   | 6                      | 35                   |

| SYSCLK [XTCLK] | 45                  | System interface             | 2                      | 32                   |

| TC [TMS]       | 49                  | System interface             | 2                      | 32                   |

| [TCK] DACK2    | 46                  | JTAG boundary scan interface | 2                      | 37                   |

| [TDI] AEN      | 47                  | JTAG boundary scan interface | 2                      | 37                   |

| [TD0] DRQ2     | 76                  | JTAG boundary scan interface | 2                      | 37                   |

| [TMS] TC       | 49                  | JTAG boundary scan interface | 2                      | 37                   |

| VCC            |                     | Power                        | 9                      | +                    |

| v C C          | 23, 81,<br>135, 180 | rowel                        | 9                      | 38                   |

| VCC1           | 176                 | Power                        | 9                      | 38                   |

| VCC5           | 95, 128             | Power                        | 9                      | 38                   |

| Signal Name      | Pin No.   | Function                | Pin State<br>Table No. | Description Page No. |

|------------------|-----------|-------------------------|------------------------|----------------------|

| VMEM             | 9, 22, 35 | Power                   | 9                      | 38                   |

| VSYS             | 48, 65    | Power                   | 9                      | 38                   |

| VSYS2            | 142       | Power                   | 9                      | 38                   |

| W/R (DRQ7)       | 169       | Local bus interface     | 7                      | 36                   |

| [X14OUT] AFDT    | 80        | Miscellaneous interface | 8                      | 35                   |

| X1OUT [BAUD_OUT] | 200       | Miscellaneous interface | 8                      | 35                   |

| X32IN            | 201       | Miscellaneous interface | 8                      | 35                   |