## **MCP18480**

### -48V Hot Swap Controller

#### Features

- Allows safe board removal and insertion from a live backplane

- Accurate (<1.5%) internal voltage reference for fault detection and precision timing

- Programmable foldback current limiting

- Programmable circuit breaker current limiting

- · Auto restart option for all faults

- Adjustable Undervoltage lockout thresholds

- · Adjustable Overvoltage protection threshold

- Adjustable Power Good delay

- Configurable Power Good output polarity

- · Low-side drive of an external N-channel FET

#### **CMOS** Technology

- High-Voltage Operation

- Temperature range: Industrial (I): -40°C to +85°C

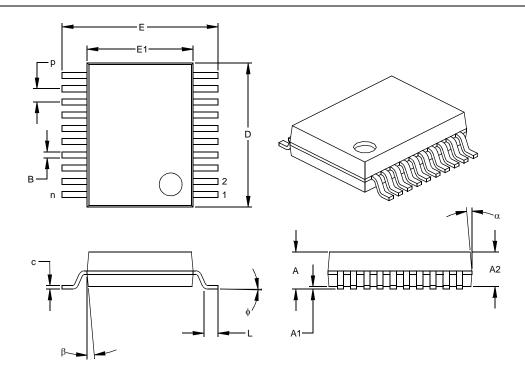

#### Packaging

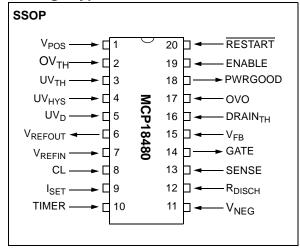

20-lead SSOP

#### Package Type

#### Description

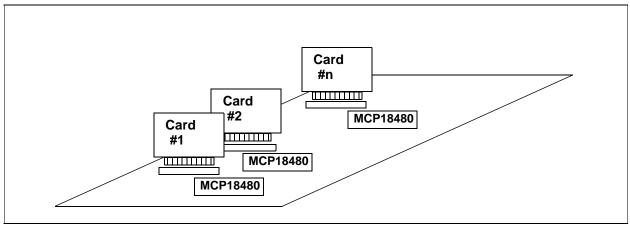

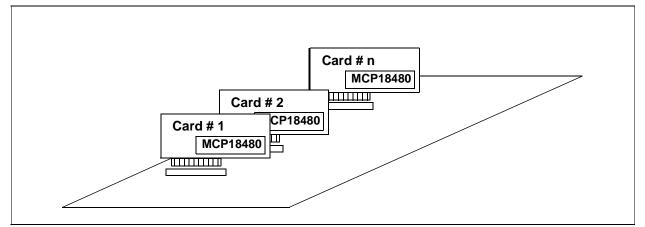

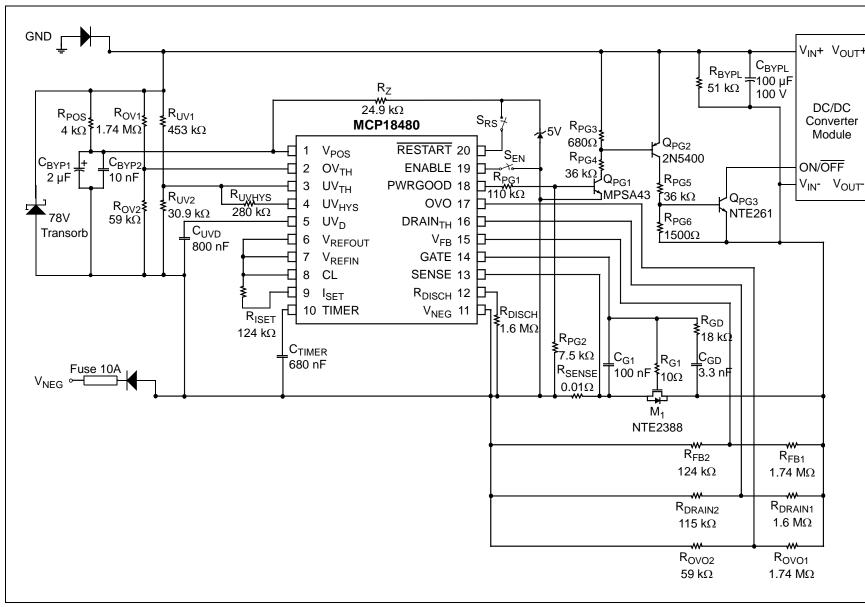

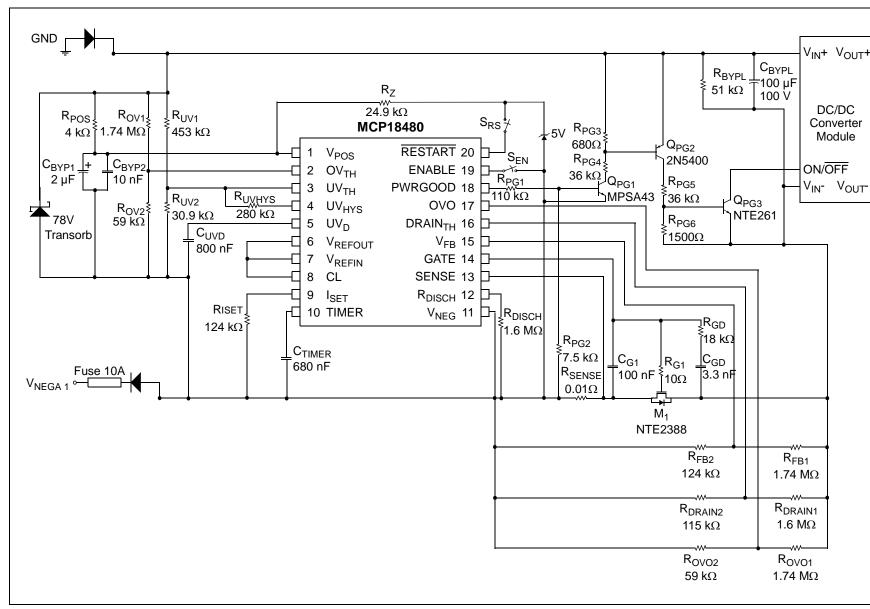

The MCP18480 is a Hot Swap controller that allows boards to be safely removed or inserted from an active backplane using -48V.

When PCBs are inserted into a live backplane, highpeak or transient currents from the source are generated due to the charging of the bypass capacitors on the supply. The high transient currents can destroy connectors and capacitors. The high inrush current can pull the input voltage BUS down and reset the system.

The MCP18480 solves this problem by controlling the slew rate of the backplane voltage to the board so that these transients are eliminated. This allows boards to be removed and inserted without causing damage to connector pins and input bulk capacitors, in addition to preventing false resets to the other boards on the backplane.

The MCP18480 can be used in applications in several areas including:

- Telecom Line Cards

- Network Switches

- Network Routers and Servers

- Base Station Line Cards

- Power-Over-LAN

- Power-Over-MDI

- IP Phone Switches/Routers

- Mid-Span, Power-Over-MDI

Two forms of current limit are provided in the MCP18480. These are:

- Foldback

- · Circuit breaker

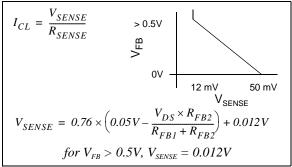

The foldback current-limiting circuit uses an external sense resistor and a voltage that is proportional to the external MOSFET's drain voltage. These are used to keep the MOSFET in its Safe Operating Area (SOA).

If the device remains in current limit for a programmed time period, the external N-channel FET is turned off. The option exists to configure the device to automatically restart after a programmed time delay. A programmable catastrophic current limit threshold shuts down the switch (circuit breaker) if excessive current is sensed due to a short-circuit condition. Internal comparators are incorporated to add hysteresis for adjusting the Undervoltage Lockout (UVLO) threshold. The external N-channel MOSFET is turned on when the input is below the user-programmable, Overvoltage threshold and above the userprogrammable, Undervoltage threshold. The PWRGOOD pin indicates the status of the MCP18480 and is active when the device has completed power-up and the system is not in an Undervoltage, Overvoltage or current-limit condition.

PWRGOOD can be externally configured to either active-high or active-low to accommodate external circuitry (power supplies) that have either enabling logic.

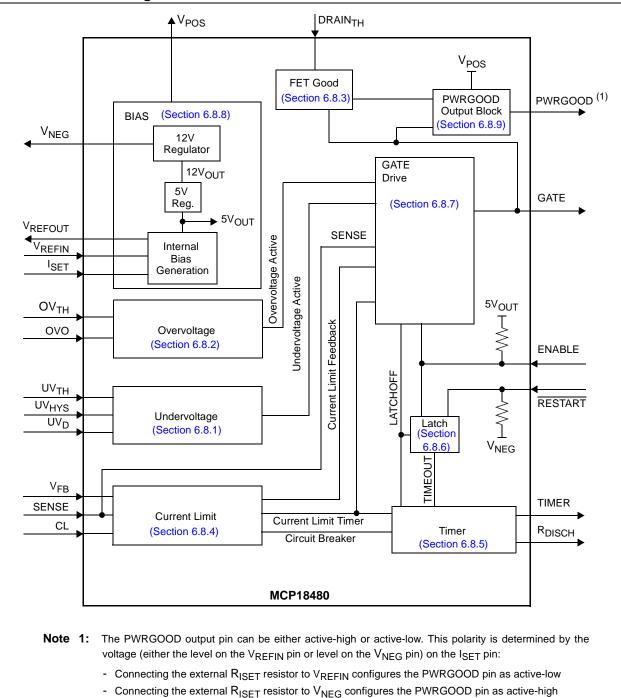

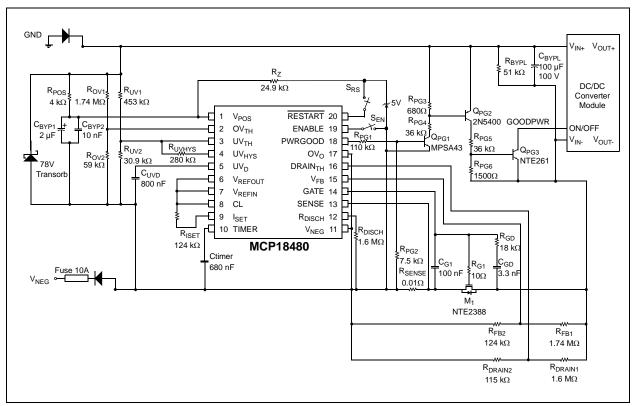

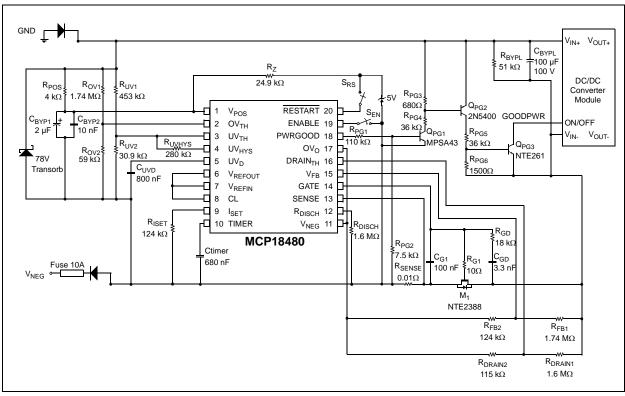

A block diagram of the MCP18480 is shown below.

#### MCP18480 Block Diagram

#### 1.0 ELECTRICAL CHARACTERISTICS

#### Absolute Maximum Ratings†

| Ambient Temperature under bias –40°C to +85°C                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                                                                                                                                       |

| Voltage on $V_{\text{POS}}$ with respect to $V_{\text{NEG}}$ -0.3V to +15.0V                                                                                                            |

| Voltage on DV <sub>TH</sub> , UV <sub>TH</sub> , V <sub>FB</sub> , OVO and UV <sub>HYS</sub> pins with respect to V <sub>NEG</sub> V <sub>NEG</sub> – 0.3V to (V <sub>POS</sub> + 0.3V) |

| Voltage on $V_{REFIN}$ , CL, SENSE, DRAIN <sub>TH</sub> , ENABLE<br>and RESTART pins with respect to $V_{NEG}$                                                                          |

|                                                                                                                                                                                         |

| Total Power Dissipation (Note 1)800 mW                                                                                                                                                  |

| Max. Current out of $V_{\mbox{NEG}}$ pin                                                                                                                                                |

| Max. Current into $V_{\text{POS}}$ pin                                                                                                                                                  |

| Max. Output Current sunk by Gate pin80 mA                                                                                                                                               |

| Max. Output Current sunk by $V_{\mbox{\scriptsize REFOUT}}$ pin5 mA                                                                                                                     |

| Max. Output Current sunk by any other                                                                                                                                                   |

| Output pin25 mA                                                                                                                                                                         |

| Max. Output Current sourced by V <sub>REFOUT</sub> pin5 mA                                                                                                                                                                                                                                                                                                                                          |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Max. Output Current sourced by any other<br>Output pin25 mA                                                                                                                                                                                                                                                                                                                                         |

| Junction to Ambient, $\Theta_{JA}$ (20 pin SSOP Package) Derating108.1°C/W                                                                                                                                                                                                                                                                                                                          |

| Junction to Case, $\Theta_{JC}$ (20 pin SSOP Package) Derating32.2°C/W                                                                                                                                                                                                                                                                                                                              |

| Lead Temperature, Soldering, 10 seconds 300°C                                                                                                                                                                                                                                                                                                                                                       |

| <b>†</b> Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability. |

**Note 1:** Power Dissipation is calculated as follows:

$\mathsf{P}_{\mathsf{DIS}} = \mathsf{V}_{\mathsf{DD}} \mathrel{\mathsf{x}} \{\mathsf{I}_{\mathsf{DD}} \mathrel{\mathsf{-}} \varSigma \mathrel{\mathsf{I}_{\mathsf{OH}}}\} + \varSigma \{(\mathsf{V}_{\mathsf{DD}} \mathrel{\mathsf{-}} \mathsf{V}_{\mathsf{OH}}) \mathrel{\mathsf{x}} \mathrel{\mathsf{I}_{\mathsf{OH}}}\} + \varSigma (\mathsf{V}_{\mathsf{OL}} \mathrel{\mathsf{x}} \mathrel{\mathsf{I}_{\mathsf{OL}}})$

| Param.<br>No. | Parameter Sym Min Typ <sup>(1)</sup> Max                                                                                     |         | Units               | Conditions                        |                              |                                  |    |                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|-----------------------------------|------------------------------|----------------------------------|----|-------------------------------|

| MD001         | 0001 Current into shunt regulator<br>that produces V <sub>POS</sub> output volt-<br>age that meets MD001A speci-<br>fication |         | I <sub>POS1</sub>   | 5                                 |                              | 25                               | mA | ENABLE pin = 5V               |

|               |                                                                                                                              |         |                     | 5                                 | _                            | 25                               |    | ENABLE pin = V <sub>NEG</sub> |

| MD001A        | Regulated Output Voltage<br>Differential of V <sub>POS</sub> to V <sub>NEG</sub>                                             |         | V <sub>POS</sub>    | 10.4                              | 12.0                         | 13.4                             | V  | See MD001                     |

| MD002         | V <sub>REFOUT</sub> pin output voltage                                                                                       |         | V <sub>REFOUT</sub> | 2.463                             | 2.5                          | 2.538                            | V  | Load = 50 µA                  |

| MD010         | V <sub>GATE</sub> pin output voltage                                                                                         |         | V <sub>GATE</sub>   | V <sub>POS</sub> - 2              | V <sub>POS</sub> -1          | V <sub>POS</sub>                 | V  |                               |

| MD011         | Voltage on I <sub>SET</sub> pin                                                                                              |         | V <sub>ISET</sub>   | (V <sub>REFIN</sub> /2) -<br>0.02 | V <sub>REFIN</sub> /2        | (V <sub>REFIN</sub> /2)<br>+0.02 | V  |                               |

| MD012A        | Voltage on SENSE pin to                                                                                                      |         | V <sub>SENSE</sub>  | 40                                | 50                           | 60                               | mV | $V_{FB} = V_{NEG}$            |

| MD012B        | trigger current-limit                                                                                                        | ing     |                     | 25                                | 31.0                         | 40                               | mV | $V_{FB} = V_{NEG} + 0.25V$    |

| MD012C        |                                                                                                                              |         |                     | 7                                 | 12                           | 17                               | mV | $V_{FB} = V_{NEG} + 0.5V$     |

| MD013         | Undervoltage Thre                                                                                                            | shold   | UV <sub>TH</sub>    | V <sub>REFIN</sub><br>- 0.03      | V <sub>REFIN</sub>           | V <sub>REFIN</sub><br>+ 0.03     | V  |                               |

| MD014A        | Overvoltage<br>Threshold                                                                                                     | rising  | OV <sub>TH</sub>    | V <sub>REFIN</sub><br>- 0.05      | V <sub>REFIN</sub>           | V <sub>REFIN</sub><br>+ 0.05     | V  | V <sub>REFIN</sub> = 2.5V     |

| MD014B        |                                                                                                                              | falling | OV <sub>TH</sub>    | V <sub>REFIN</sub><br>- 0.035     | V <sub>REFIN</sub><br>- 0.02 | V <sub>REFIN</sub><br>- 0.005    | V  | V <sub>REFIN</sub> = 2.5V     |

| MD015         | DRAIN Pin Input Threshold<br>Voltage                                                                                         |         | V <sub>DTH</sub>    | 90                                | 100                          | 130                              | mV |                               |

DC CHARACTERISTICS

Note 1: Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

2: Negative current is defined as current sourced by the pin.

**3:** All voltages are with respect to the V<sub>NEG</sub> pin voltage.

#### **DC Characteristics (Continued)**

| Param.<br>No. | Parameter                    |           | Parameter Sym Min Typ <sup>(1)</sup> Max |                                                  | Units | Conditions                                       |    |                                                                                         |

|---------------|------------------------------|-----------|------------------------------------------|--------------------------------------------------|-------|--------------------------------------------------|----|-----------------------------------------------------------------------------------------|

| MD020         | DRAIN pin current            |           | I <sub>DRAIN</sub>                       | —                                                |       | 0.1                                              | μA | $DRAIN_{TH} pin = V_{NEG}$                                                              |

| MD021         | SENSE pin current            |           | ISENSE                                   | —                                                | _     | 0.1                                              | μA |                                                                                         |

| MD022         | GATE pin current             | Pull-up   | I <sub>GATE</sub>                        |                                                  |       |                                                  |    | SENSE pin = V <sub>NEG</sub><br>GATE pin = V <sub>NEG</sub> +4V                         |

| MD022A        |                              |           |                                          | -30                                              | -50   | -75                                              | μA | $V_{FB} = V_{NEG}$                                                                      |

| MD022B        |                              |           |                                          | -9                                               | -17   | -33                                              | μA | $V_{FB} = V_{NEG} + 500 \text{ mV}$                                                     |

| MD022C        |                              | Pull-down | I <sub>GATE</sub>                        | 31                                               | 49    | 72                                               | mA | Any fault condition                                                                     |

| MD023         | UV <sub>D</sub> pin current  |           | I <sub>UVD</sub>                         | -7                                               | -10   | -15                                              | μA | UV <sub>TH</sub> < V <sub>REFIN</sub>                                                   |

| MD024A        | TIMER pin current            | Pull-up   | I <sub>TIMER</sub>                       | -100                                             | -160  | -200                                             | μA | R <sub>ISET</sub> = 125 kΩ,<br>V <sub>REFIN</sub> = 2.5V                                |

| MD024B        |                              | Pull-down |                                          | 52                                               | 78    | 104                                              | nA | R <sub>ISET</sub> = 125 kΩ,<br>V <sub>REFIN</sub> = 2.5V<br>R <sub>DISCH</sub> = 1.6 MΩ |

| MD025         | I <sub>SET</sub> pin current |           | I <sub>ISET</sub>                        | V <sub>ISET(MIN)</sub><br>R <sub>ISET(MAX)</sub> | _     | V <sub>ISET(MAX)</sub><br>R <sub>ISET(MIN)</sub> | A  | See MD011                                                                               |

Note 1: Data in the Typical ("Typ") column is based on characterization results at +25°C. This data is for design guidance only and is not tested.

2: Negative current is defined as current sourced by the pin.

3: All voltages are with respect to the  $\mathsf{V}_{\mathsf{NEG}}$  pin voltage.

#### **DC Characteristics (Continued)**

| Param # | Parameter                                                                                                                 | Sym                | Min                  | Тур                   | Max              | Units | Conditions                                                             |

|---------|---------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------|-----------------------|------------------|-------|------------------------------------------------------------------------|

| MD030   | Input Low Voltage                                                                                                         | V <sub>IL</sub>    |                      |                       |                  |       |                                                                        |

| MD031   | ENABLE pin                                                                                                                |                    | V <sub>NEG</sub>     | —                     | 0.8              | V     |                                                                        |

| MD032   | RESTART pin                                                                                                               |                    | V <sub>NEG</sub>     | -                     | 0.8              |       |                                                                        |

| MD040   | Input High Voltage                                                                                                        | V <sub>IH</sub>    |                      |                       |                  |       |                                                                        |

| MD041   | ENABLE pin                                                                                                                |                    | 2.0                  | —                     | 5.0              | V     |                                                                        |

| MD042   | RESTART pin                                                                                                               |                    | 2.0                  | -                     | 5.0              | V     |                                                                        |

| MD050   | Internal Resistance on UV <sub>HYS</sub> pin                                                                              | R <sub>UVHYS</sub> | 500                  | 1200                  | 2100             | Ω     | V <sub>UVTH</sub> < V <sub>REFIN</sub> ,<br>I <sub>UVHYS</sub> = 30 μA |

|         |                                                                                                                           |                    | 50                   | 100                   | —                | MΩ    | V <sub>UVTH</sub> > V <sub>REFIN</sub> ,<br>I <sub>UVHYS</sub> = 30 μA |

|         | Input Leakage Current<br>(Notes 2, 3)                                                                                     |                    |                      |                       |                  |       |                                                                        |

| MD060A  | $\text{OV}_{\text{TH}}, \text{UV}_{\text{TH}}, \text{V}_{\text{FB}}, \text{OVO} \text{ and } \text{UV}_{\text{HYS}}$ pins | Ι <sub>ΙL</sub>    | -1                   | —                     | +1               | μA    | $V_{NEG} \le V_{PIN} \le 11V$ , Pin at high-impedance                  |

| MD060B  | V <sub>REFIN</sub> , CL, SENSE, DRAIN <sub>TH</sub> ,<br>ENABLE and RESTART pins                                          |                    | —                    | —                     | ±1               | μA    | $V_{NEG} \le V_{PIN} \le 5V$ , Pin at hi-impedance                     |

| MD070   | Minimum current into ENABLE pin to disable MCP18480                                                                       | I <sub>EN</sub>    | _                    | 10                    | 30               | μA    | I <sub>POS</sub> = 5 mA,<br>ENABLE = 0.8V                              |

|         | Output Low Voltage                                                                                                        | V <sub>OL</sub>    |                      |                       |                  |       |                                                                        |

| MD080   | PWRGOOD pin                                                                                                               |                    | 0                    | —                     | 0.4              | V     | I <sub>OL</sub> = 5 mA                                                 |

|         | Output High Voltage                                                                                                       | V <sub>OH</sub>    |                      | _                     |                  |       |                                                                        |

| MD090   | PWRGOOD pin                                                                                                               |                    | 0.8 V <sub>POS</sub> | 0.96 V <sub>POS</sub> | V <sub>POS</sub> | V     | $I_{OH} = 2 \text{ mA},$<br>7 mA $\leq I_{POS} \leq 12 \text{ mA}$     |

| MD100   | Offset Voltage at the internal<br>comparator input that is connected<br>to the CL pin.                                    | V <sub>CL</sub>    | -15                  | _                     | +15              | mV    | V <sub>FB</sub> = 0                                                    |

Note 1: All voltages are with respect to the V<sub>NEG</sub> pin voltage.

2: The leakage currents on the ENABLE and RESTART pins are strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

3: Negative current is defined as coming out of the pin.

#### 1.1 Timing Parameter Symbology and Load Conditions

The timing parameter symbols have been created using one of the following formats:

#### 1.1.1 TIMING CONDITIONS

The temperature and voltages specified in Table 1-2 apply to all timing specifications, unless otherwise noted. Figure 1-1 specifies the load conditions for the timing specifications.

#### TABLE 1-1:SYMBOLOGY

| 1. TppS2 | 2ppS                                     | 2. TppS |              |  |

|----------|------------------------------------------|---------|--------------|--|

| Т        |                                          |         |              |  |

| F        | Frequency                                | Т       | Time         |  |

| E        | Error                                    |         |              |  |

| Lowerca  | se letters (pp) indicate the device pin. |         |              |  |

| Upperca  | se letters and their meanings:           |         |              |  |

| S        |                                          |         |              |  |

| F        | Fall                                     | Р       | Period       |  |

| FR       | Fast Ramp                                | R       | Rise         |  |

| н        | High                                     | V       | Valid        |  |

| I        | Invalid (Hi-impedance)                   | Z       | Hi-impedance |  |

| L        | Low                                      |         |              |  |

#### TABLE 1-2: AC TEMPERATURE AND VOLTAGE SPECIFICATIONS

|                    | Standard Operating Conditions (unless otherwise stated)                     |

|--------------------|-----------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature: $-40^{\circ}C \le T_A \le +85^{\circ}C$ (industrial) |

|                    | Operating voltage VDD range as described in DC spec Section 1.0.            |

FIGURE 1-1: Load Conditions for Device Timing Specifications.

## **MCP18480**

#### 1.2 Timing Diagrams and Specifications

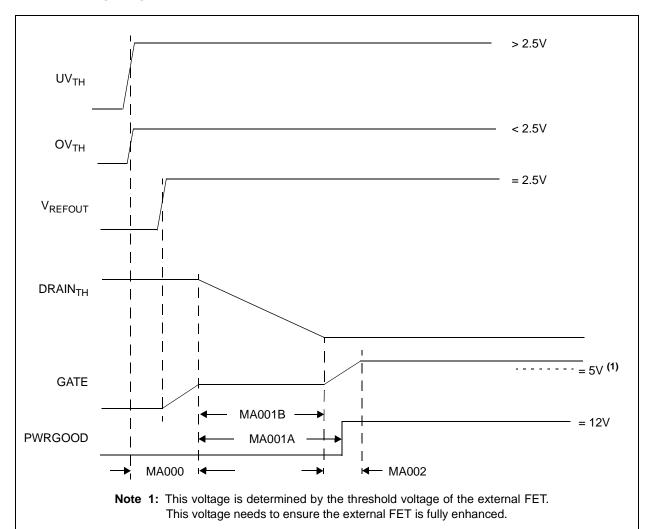

FIGURE 1-2: Startup Waveforms.

| TABLE 1-3: STARTUP TIMING REQUIREME |

|-------------------------------------|

|-------------------------------------|

| Param.<br>No. | Parameter                                                                                            | Sym                                     | Min | Тур  | Max | Units | Conditions |

|---------------|------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|------|-----|-------|------------|

| MA000         | UV <sub>TH</sub> /OV <sub>TH</sub> High (V <sub>POS</sub> applied) to<br>DRAIN <sub>TH</sub> falling | T <sub>UVOV</sub> H2 <sub>DTH</sub> F   | —   | 20.2 | —   | ms    |            |

| MA001A        | DRAIN <sub>TH</sub> falling to PWRGOOD High                                                          | T <sub>DTH</sub> F2 <sub>GATE</sub> PGH |     | 19.3 | —   | ms    |            |

| MA001B        | DRAIN <sub>TH</sub> falling to GATE Fast Ramp                                                        | T <sub>DTH</sub> F2 <sub>GATE</sub> FR  |     | 13.1 |     | ms    |            |

| MA002         | GATE Fast Ramp to external FET<br>fully enhanced                                                     | TGATEFR2FET <sub>E</sub>                |     | 16.1 |     | ms    |            |

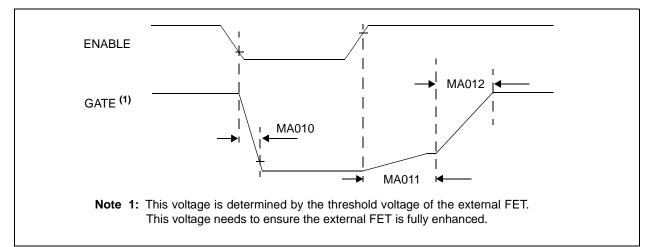

FIGURE 1-3: ENABLE-to-GATE Waveforms.

#### TABLE 1-4: ENABLE-TO-GATE TIMING REQUIREMENTS

| Param.<br>No. | Parameter                     | Sym                                   | Min | Тур  | Max | Units | Conditions |

|---------------|-------------------------------|---------------------------------------|-----|------|-----|-------|------------|

| MA010         | ENABLE Low to GATE Low        | T <sub>EN</sub> L2 <sub>GATE</sub> L  |     | 23.6 |     | μs    |            |

| MA011         | ENABLE High to GATE Fast Ramp | T <sub>EN</sub> H2 <sub>GATE</sub> FR |     | 41   |     | ms    |            |

| MA012         | GATE Fast Ramp to GATE High   | $T_{GATE}FR2_{GATE}H$                 |     | 17.8 |     | ms    |            |

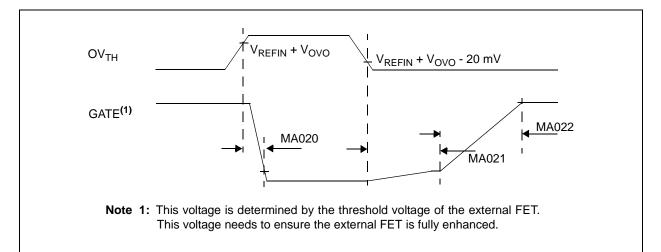

FIGURE 1-4: OV<sub>TH</sub>-to-gate Waveform.

| <b>TABLE 1-5</b> : | OV <sub>TH</sub> -TO-GATE TIMING REQUIREMENTS |

|--------------------|-----------------------------------------------|

|--------------------|-----------------------------------------------|

| Param.<br>No. | Parameter                              | Sym                                   | Min | Тур  | Max | Units | Conditions |

|---------------|----------------------------------------|---------------------------------------|-----|------|-----|-------|------------|

| MA020         | OV <sub>TH</sub> High to GATE Low      | T <sub>OV</sub> H2 <sub>GATE</sub> L  |     | 58.4 |     | μs    |            |

| MA021         | OV <sub>TH</sub> Low to GATE Fast Ramp | T <sub>OV</sub> L2 <sub>GATE</sub> FR |     | 40.8 |     | μs    |            |

| MA022         | GATE Fast Ramp to GATE High            | $T_{GATE}FR2_{GATE}H$                 |     | 17.8 |     | ms    |            |

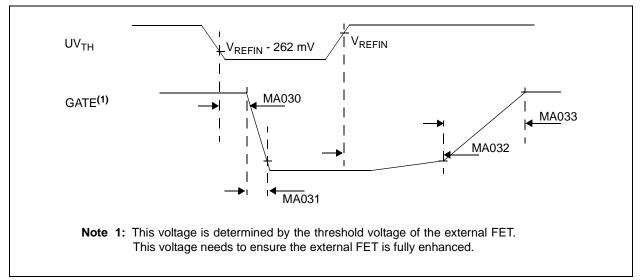

| FIGURE 1-5: | UV <sub>TH</sub> -to-gate Waveform |

|-------------|------------------------------------|

|-------------|------------------------------------|

| TABLE 1-6: | UVTH-TO-GATE TIMING REQUIREMENTS |

|------------|----------------------------------|

|------------|----------------------------------|

| Param.<br>No. | Parameter                                 | Sym                                     | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                |

|---------------|-------------------------------------------|-----------------------------------------|-----|--------------------|-----|-------|---------------------------|

| MA030         | UV <sub>TH</sub> Low to GATE Falling Edge | T <sub>UV</sub> L2 <sub>GATE</sub> F    | _   | 108                | —   | μs    | C <sub>UVD</sub> = 800 nF |

| MA031         | GATE High to GATE Low                     | T <sub>GATE</sub> H2 <sub>GATE</sub> L  | _   | 25.8               |     | μs    |                           |

| MA032         | ENABLE High to GATE Fast Ramp             | T <sub>UV</sub> H2 <sub>GATE</sub> FR   | -   | 40.4               | _   | ms    |                           |

| MA033         | GATE Fast Ramp to GATE High               | T <sub>GATE</sub> FR2 <sub>GATE</sub> H | _   | 58.4               | _   | ms    |                           |

**Note 1:** Data in the Typical ("Typ") column is at 5V, 25°C, unless otherwise stated.

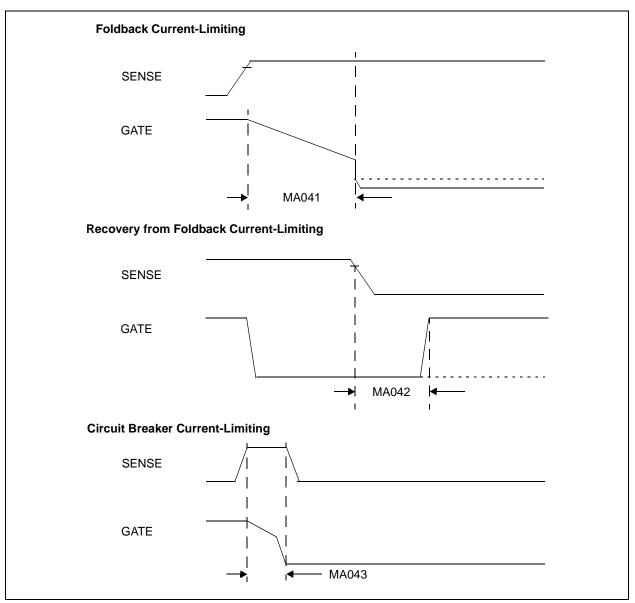

FIGURE 1-6: Sense-to-gate Waveform.

#### TABLE 1-7: SENSE-TO-GATE TIMING REQUIREMENTS

| Param.<br>No. | Parameter                      | Sym                                     | Min | Тур  | Max | Units | Conditions                                                 |

|---------------|--------------------------------|-----------------------------------------|-----|------|-----|-------|------------------------------------------------------------|

| MA041         | GATE Current Limit to GATE Off | T <sub>GATE</sub> CL2 <sub>GATE</sub> O |     | 5.5  |     | ms    | C <sub>TIMER</sub> = 0.68 μF<br>R <sub>ISET</sub> = 124 kΩ |

| MA042         | GATE Current Limit Recovery    | T <sub>GATE</sub> CL                    |     | 10.2 |     |       | C <sub>TIMER</sub> = 0.68 μF<br>R <sub>ISET</sub> = 124 kΩ |

| MA043         | SENSE High to GATE Off         | T <sub>SENSE</sub> H2 <sub>GATE</sub> O |     | 3.6  |     | ms    |                                                            |

| Param.<br>No. | Parameter                                         | Sym                                        | Min | Тур  | Max | Units | Conditions                                                   |

|---------------|---------------------------------------------------|--------------------------------------------|-----|------|-----|-------|--------------------------------------------------------------|

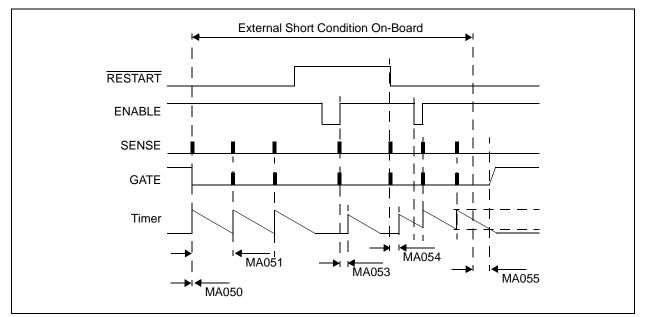

| MA050         | External Short to Timer period start              | T <sub>SHORT</sub> 2 <sub>TIMER</sub> S    | —   | 171  | —   | mS    |                                                              |

| MA051         | Timer period                                      | T <sub>TIMER</sub> P                       | _   | 5.8  | —   | sec   | C <sub>TIMER</sub> = 0.68 μF<br>R <sub>DISCH</sub> = 1.6 MΩ  |

| MA053         | ENABLE High to Timer period start                 | T <sub>ENABLE</sub> H2 <sub>TIMER</sub> S  | —   | 30.5 | —   | mS    | C <sub>TIMER</sub> = 0.68 μF<br>R <sub>DISCH</sub> = 1.6 MΩ  |

| MA054         | RESTART Low to Timer period start                 | T <sub>RESTART</sub> L2 <sub>TIMER</sub> S | _   | 30.9 | —   | mS    | C <sub>TIMER</sub> = 0.68 μF<br>R <sub>DISCH</sub> = 11.6 MΩ |

| MA055         | External Short removed to Timer off <b>Note 2</b> | T <sub>NOSHORT</sub> 2 <sub>TIMER</sub> O  | —   | 5.8  | _   | sec   | C <sub>TIMER</sub> = 0.68 μF<br>R <sub>DISCH</sub> = 1.6 MΩ  |

Note 1: Minimum and maximum specifications will be provided in future revisions of this data sheet.

2: This is up to one additional timer period because the external short circuit is removed asynchronously to the timer. The timer must time out before normal operation returns.

NOTES:

#### 2.0 DC CHARACTERISTIC CURVES

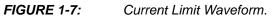

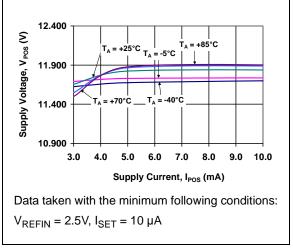

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

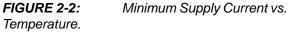

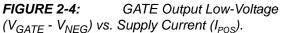

**FIGURE 2-1:** Supply Current  $(I_{POS})$  vs. Supply Voltage  $(V_{POS})$ .

**FIGURE 2-3:** GATE Output High-Voltage  $(V_{POS}, V_{GATE})$  vs. Supply Current  $(I_{POS})$ .

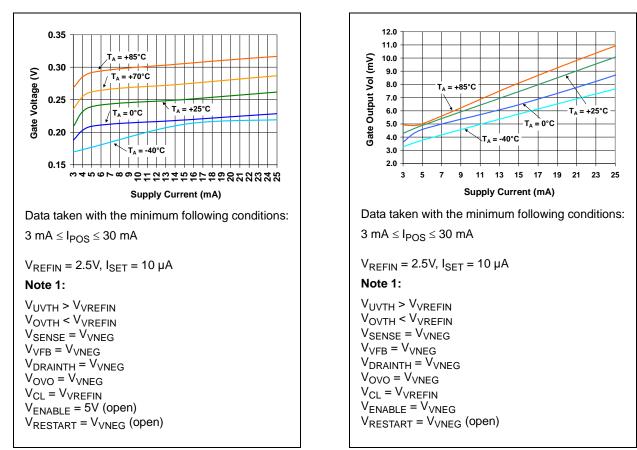

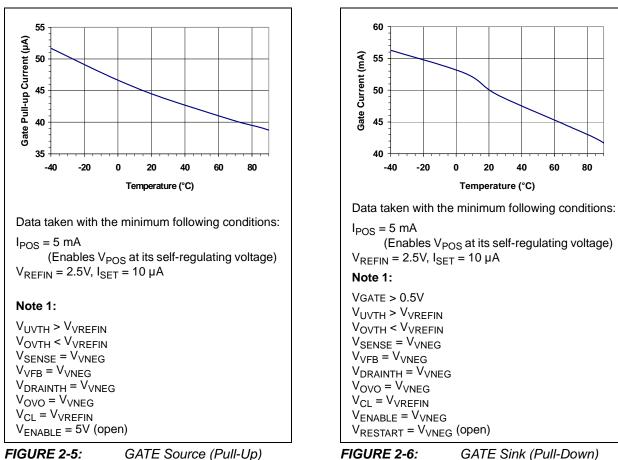

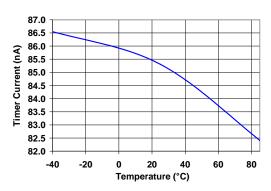

Current vs. Temperature.

FIGURE 2-6: GATE Sink (Pull-Down) Current vs. Temperature.

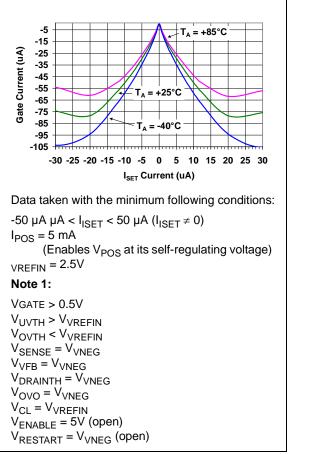

**FIGURE 2-7:** GATE Source Current vs. I<sub>SET</sub> Pin Current.

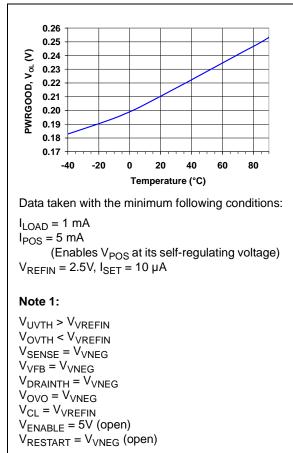

**FIGURE 2-8:** PWRGOOD Output Low Voltage (V<sub>OI</sub>) vs. Temperature.

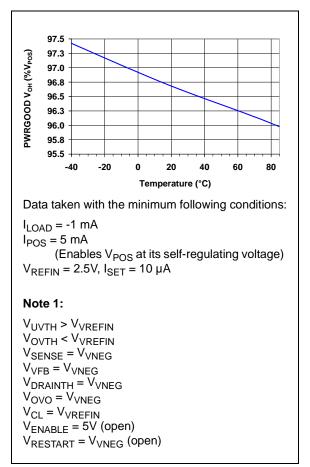

**FIGURE 2-9:** PWRGOOD Output High-Voltage (V<sub>OH</sub>) vs. Temperature.

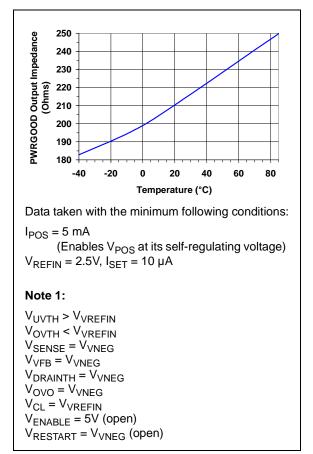

FIGURE 2-10: PWRGOOD Output High-Impedance vs. Temperature.

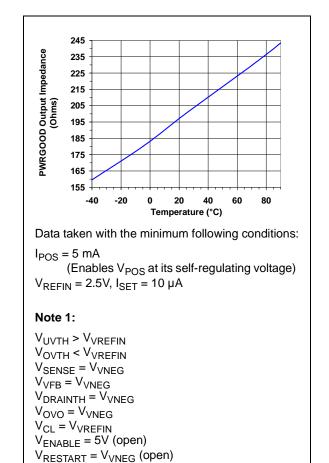

FIGURE 2-11: PWRGOOD Output Low-Impedance vs. Temperature.

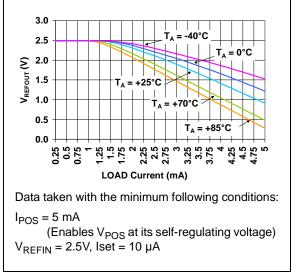

**FIGURE 2-12:**  $V_{REFOUT}$  vs. Supply Current  $(I_{POS})$ .

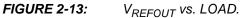

FIGURE 2-14: TIMER Pin Output Low Current vs. R<sub>DISCH</sub> Current.

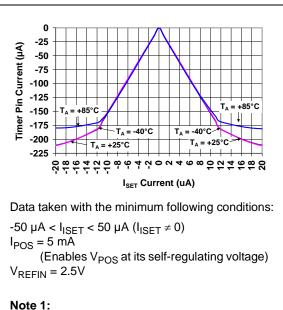

# $V_{UVTH} > V_{VREFIN}$ $V_{OVTH} < V_{VREFIN}$ $V_{SENSE} \ge 100mV$ $V_{VFB} = V_{VNEG}$

$V_{DRAINTH} = V_{VNEG}$  $V_{OVO} = V_{VNEG}$  $V_{CL} = V_{VREFIN}$  $V_{ENABLE} = 5V (open)$  $V_{RESTART} = V_{VNEG} (open)$

FIGURE 2-15: TIMER Pin Output High Current vs. I<sub>SET</sub> Current.

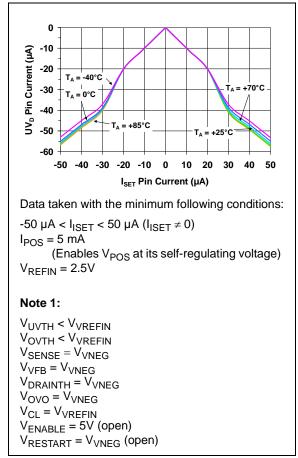

**FIGURE 2-16:** UV<sub>D</sub> Pin Current vs. I<sub>SET</sub> Pin Current.

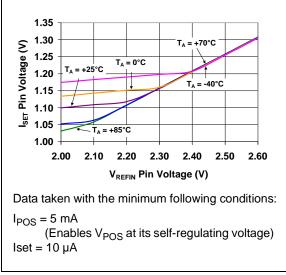

**FIGURE 2-17:** I<sub>SET</sub> Pin Voltage vs. V<sub>REFIN</sub> Pin Voltage.

$V_{UVTH} > V_{VREFIN}$   $V_{OVTH} < V_{VREFIN}$   $V_{SENSE} = V_{VNEG}$   $V_{VFB} = V_{VNEG}$   $V_{OVO} = V_{VNEG}$   $V_{CL} = V_{VREFIN}$   $V_{ENABLE} = 5V (open)$   $V_{RESTART} = V_{VNEG} (open)$

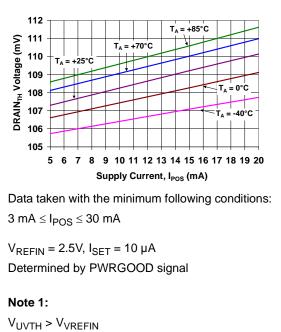

**FIGURE 2-18:** DRAINTH Threshold Voltage vs. Supply current (I<sub>POS</sub>).

$V_{SENSE} = V_{VNEG}$   $V_{VFB} = V_{VNEG}$   $V_{DRAINTH} = V_{VNEG}$   $V_{OVO} = V_{VNEG}$   $V_{CL} = V_{VREFIN}$   $V_{ENABLE} = 5V (open)$   $V_{RESTART} = V_{VNEG} (open)$

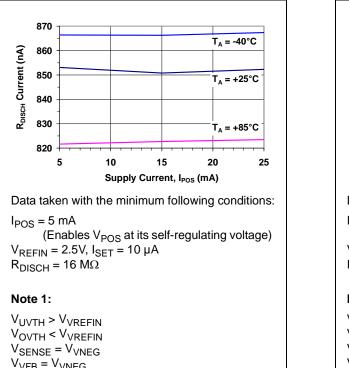

**FIGURE 2-19:** R<sub>DISCH</sub> Current vs. Supply Current (I<sub>POS</sub>).

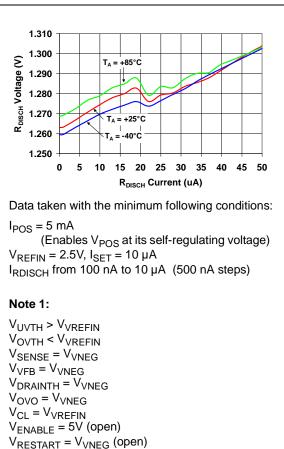

R<sub>DISCH</sub> Voltage vs. R<sub>DISCH</sub>

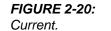

FIGURE 2-21: ENABLE/RESTART Pin Trip Point Voltage vs. Temperature.

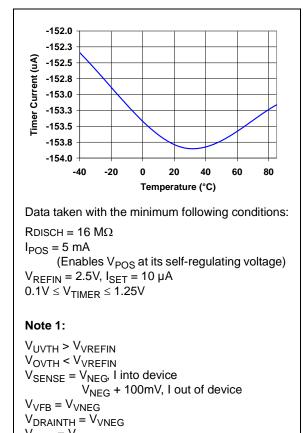

Data taken with the minimum following conditions:

Rdisch = 16 M $\Omega$

$$\begin{split} I_{POS} &= 5 \text{ mA} \\ (Enables \ V_{POS} \text{ at its self-regulating voltage}) \\ V_{REFIN} &= 2.5 \text{V}, \ I_{SET} = 10 \ \mu\text{A} \\ 0.1 \text{V} \leq \text{V}_{TIMER} \leq 1.25 \text{V} \end{split}$$

#### Note 1:

$V_{UVTH} > V_{VREFIN}$   $V_{OVTH} < V_{VREFIN}$   $V_{SENSE} = V_{NEG}, I \text{ into device}$   $V_{NEG} + 100\text{mV}, I \text{ out of device}$   $V_{VFB} = V_{VNEG}$   $V_{OVO} = V_{VNEG}$   $V_{OL} = V_{VREFIN}$   $V_{ENABLE} = 5V \text{ (open)}$   $V_{RESTART} = V_{VNEG} \text{ (open)}$

FIGURE 2-22: TIMER Output Sink Current vs. Temperature.

$V_{OVO} = V_{VNEG}$   $V_{CL} = V_{VREFIN}$   $V_{ENABLE} = 5V \text{ (open)}$  $V_{RESTART} = V_{VNEG} \text{ (open)}$

FIGURE 2-23: TIMER Output Source Current vs. Temperature.

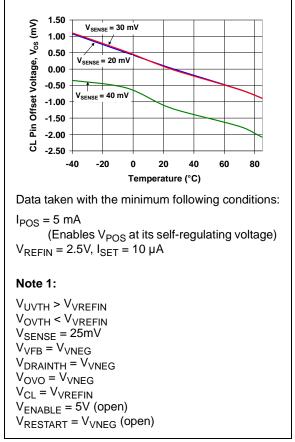

FIGURE 2-24: CL pin Input Offset Voltage vs. Temperature.

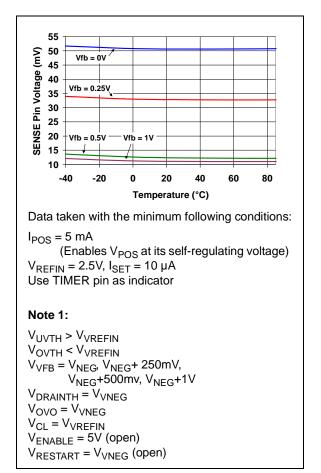

FIGURE 2-25: SENSE Pin Input Threshold vs. Temperature.

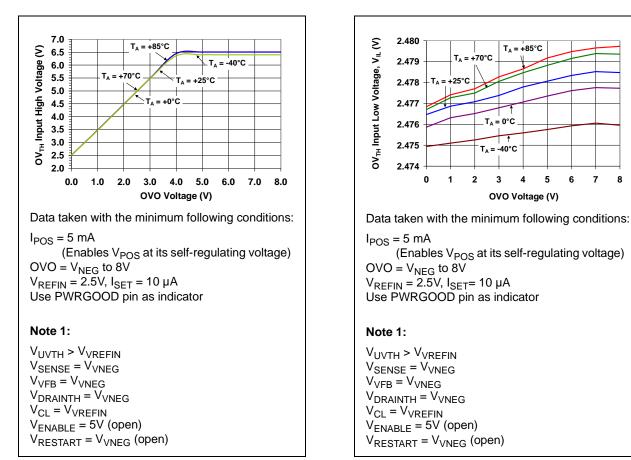

FIGURE 2-26: OV<sub>TH</sub> Input Rising Threshold vs. OVO Voltage.

FIGURE 2-27: OV<sub>TH</sub> Input Falling Threshold vs. OVO Voltage.

8

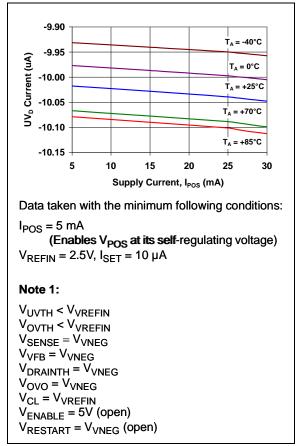

FIGURE 2-28: UV<sub>D</sub> Current vs. Supply Current (IPOS).

Data taken with the minimum following conditions:

$$\begin{split} I_{POS} &= 5 \text{ mA} \\ & (\text{Enables } V_{POS} \text{ at its self-regulating voltage}) \\ UV_{TH} &< V_{REFIN}, \ UV_{TH} > V_{REFIN} \\ V_{REFIN} &= 2.5 \text{V}, \ I_{SET} &= 10 \ \mu\text{A} \end{split}$$

#### Note 1:

$\label{eq:Vovth} \begin{array}{l} V_{OVTH} < V_{VREFIN} \\ V_{SENSE} = V_{VNEG} \\ V_{VFB} = V_{VNEG} \\ V_{DRAINTH} = V_{VNEG} \\ V_{OVO} = V_{VNEG} \\ V_{CL} = V_{VREFIN} \\ V_{ENABLE} = 5V \mbox{ (open)} \\ V_{RESTART} = V_{VNEG} \mbox{ (open)} \end{array}$

FIGURE 2-29: Temperature. UV<sub>HYS</sub> Pin Impedance vs.

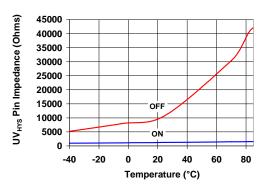

FIGURE 2-30: UV<sub>TH</sub> Input Rising Threshold vs. Temperature.

FIGURE 2-31: UV<sub>TH</sub> Input Falling Threshold vs. Temperature.

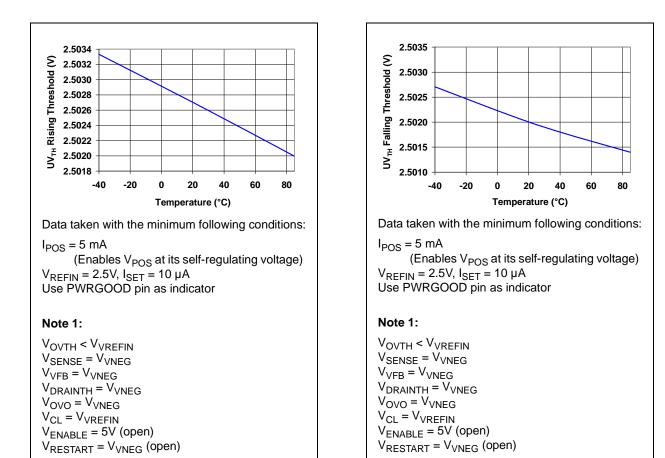

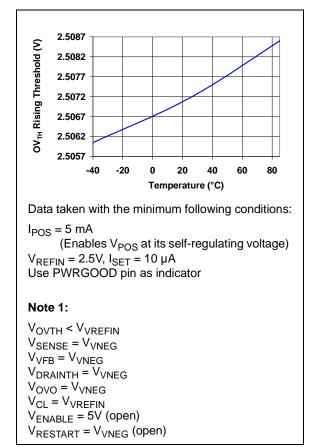

**FIGURE 2-32:** OV<sub>TH</sub> Input Rising Threshold vs. Temperature.

$$\begin{split} I_{POS} &= 5 \text{ mA} \\ (Enables \ V_{POS} \text{ at its self-regulating voltage}) \\ V_{REFIN} &= 2.5 \text{V}, \ I_{SET} = 10 \ \mu\text{A} \\ V_{UVHYS} &= V_{NEG} \\ \text{Use PWRGOOD pin as indicator} \end{split}$$

#### Note 1:

$V_{OVTH} < V_{VREFIN}$  $V_{SENSE} = V_{VNEG}$  $V_{VFB} = V_{VNEG}$  $V_{DRAINTH} = V_{VNEG}$  $V_{OVO} = V_{VNEG}$  $V_{CL} = V_{VREFIN}$  $V_{ENABLE} = 5V (open)$  $V_{RESTART} = V_{VNEG} (open)$

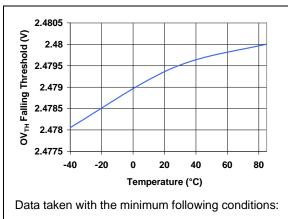

**FIGURE 2-33:** OV<sub>TH</sub> Input Falling Threshold vs. Temperature.

NOTES:

#### 3.0 PIN DESCRIPTIONS

| Pin Name          | Pin<br>Number | Pin<br>Direction | Buffer    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-------------------|---------------|------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                   | SSOP          | Direction        | Туре      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| V <sub>POS</sub>  | 1             | I                | Р         | Positive supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|                   |               |                  |           | Internal Shunt Regulator connected between V <sub>POS</sub> and V <sub>NEG</sub> limits the potential to 12V between these two pins. A series resistor must be placed on the V <sub>POS</sub> pin to limit the current into the device.                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| OV <sub>TH</sub>  | 2             | I                | А         | Overvoltage protection threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                   |               |                  |           | An external resistor divider network is connected to this input pin to program the overvoltage protection threshold. The selected external resistor values for the $OV_{TH}$ to system ground and $OV_{TH}$ to $V_{NEG}$ resistors should have currents in the 1 mA range. A typical Overvoltage threshold is -76V. Internal hysteresis in the overvoltage input comparator will allow proper operation once $V_{NEG}$ falls below the selected threshold.                                                                                                                                                                                                                       |  |  |  |

| UV <sub>TH</sub>  | 3             | I                | Α         | Undervoltage lockout threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                   |               |                  |           | An external resistor divider network is connected to this input pin to program the undervoltage lockout threshold. If the voltage on UV <sub>TH</sub> is less than $V_{NEG}$ + 2.5V, the undervoltage comparator will trip, indicating an Undervoltage condition.                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|                   |               |                  |           | An external hysteresis resistor can be used to set the high-to-low (V <sub>THF</sub> ) threshold below the low-to-high (V <sub>THR</sub> ) threshold. For telecom network equipment, it is desirable to have shutdown occur at -38.5V and the startup set at -43.0V.                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| UV <sub>HYS</sub> | 4             | I                | Α         | Undervoltage internal comparator hysteresis.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|                   |               |                  |           | An external resistor is connected between this input to the $UV_{TH}$ input pin to adjust the hysteresis of the internal Undervoltage comparator. Since it is desirable to shut down at -38.5V and restart at -43.0V in telecom switch equipment.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| UVD               | 5             | I/O              | A         | Undervoltage event delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                   |               |                  |           | An external capacitor is connected to this input pin to set the delay between when the UV <sub>TH</sub> pin drops below the trip point specified by the voltage on the V <sub>REFIN</sub> pin and when the system shutdown occurs (causing the PWRGOOD pin to be driven to an inactive level and the GATE pin to be pulled to the V <sub>NEG</sub> pin voltage level). The UV <sub>D</sub> pin sources a current equivalent to the I <sub>ISET</sub> (in typical applications, the I <sub>ISET</sub> current equals 10 $\mu$ A), which charges this external capacitor while an internal comparator compares this voltage on the UV <sub>D</sub> pin to  V <sub>REFIN</sub>  /2. |  |  |  |

|                   |               |                  |           | Typically, for telecom equipment, the system is expected to shut down when the input voltage falls below -38.5V ( $\pm$ 1.0V DC) for greater than 100 ms.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

|                   |               | patible input    | O :<br>CN | <ul> <li>Schmitt Trigger input with CMOS levels</li> <li>Output</li> <li>IOS = CMOS-compatible input</li> <li>Digital</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

#### TABLE 3-1:MCP18480 PIN DESCRIPTIONS

#### TABLE 3-1: MCP18480 PIN DESCRIPTIONS (CONTINUED)

| Pin Name                                                                                                                                                                                       | Pin<br>Number | Pin<br>Direction | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| V                                                                                                                                                                                              | SSOP<br>6     | 0                | A              | Reference output.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |

| V <sub>REFOUT</sub>                                                                                                                                                                            | 0             |                  |                | Internal reference output voltage (typically 2.5V). Usually tied back to the $V_{\text{REFIN}}$ pin unless an external high-precision reference voltage is desired.                                                                                                                                                                                                                                                                                                         |  |

| V <sub>REFIN</sub>                                                                                                                                                                             | 7             | I                | Α              | Reference input.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                                                                |               |                  |                | This pin allows a high-precision reference voltage for the following functions:                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                |               |                  |                | Undervoltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                |               |                  |                | Overvoltage Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |

|                                                                                                                                                                                                |               |                  |                | DRAIN Comparator                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

|                                                                                                                                                                                                |               |                  |                | Current Limit Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                |               |                  |                | If the precision of the $V_{\text{REFOUT}}$ output voltage is acceptable, tie the $V_{\text{REFOUT}}$ pin to the $V_{\text{REFIN}}$ pin.                                                                                                                                                                                                                                                                                                                                    |  |

| CL                                                                                                                                                                                             | 8             | I                | Α              | Current Limit.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|                                                                                                                                                                                                |               |                  |                | Input used to set the maximum current limit threshold allowed by the system via a resistor divider network (with the resistor $R_{CL1}$ between the $V_{REFIN}$ pin and the CL pin and resistor $R_{CL}$ between the $V_{NEG}$ pin and the CL pin). If the voltage across the sense resistor exceeds the voltage on the CL pin, it implies that there is excessive current over the allowed limit and forces the GATE pin to the $V_{NEG}$ pin voltage level without delay. |  |

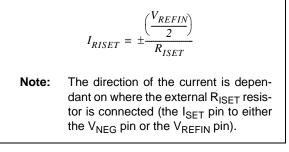

| I <sub>SET</sub>                                                                                                                                                                               | 9             | I                | Α              | Current source set.                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                |               |                  |                | Establishes the internal I <sub>SOURCE</sub> for the following:                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                |               |                  |                | Undervoltage Delay                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|                                                                                                                                                                                                |               |                  |                | Current Limit Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |

|                                                                                                                                                                                                |               |                  |                | GATE Pin Source Current                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |

|                                                                                                                                                                                                |               |                  |                | An external resistor $R_{ISET}$ from the $I_{SET}$ pin must be connected to either the $V_{NEG}$ pin or the $V_{REFIN}$ pin to set $I_{BIAS}$ , which will then establish the current sources throughout the device. The $I_{BIAS}$ current is the same for either connection.                                                                                                                                                                                              |  |

|                                                                                                                                                                                                |               |                  |                | Connecting the R <sub>ISET</sub> resistor to the V <sub>NEG</sub> pin will establish the PWRGOOD pin output polarity to be active-high. Connecting the R <sub>ISET</sub> resistor to the V <sub>REFIN</sub> pin will establish the PWRGOOD pin output polarity to be active-low.                                                                                                                                                                                            |  |

| Legend: TTL                                                                                                                                                                                    |               | patible input    |                | = Schmitt Trigger input with CMOS levels                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

| $ \begin{array}{l} I = Input \\ P = Power \\ \hline \end{array} \qquad \qquad$ |               |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| P = PowerCMOS = CMOS-compatible inputA = AnalogD = Digital                                                                                                                                     |               |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                                                                                                                                                                                |               |                  |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

| TABLE 3-1: | MCP18480 PIN DESCRIPTIONS (CONTINUED) |

|------------|---------------------------------------|

|            |                                       |

| Pin Name           | Pin<br>Number<br>SSOP | Pin<br>Direction | Buffer<br>Type | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------|-----------------------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TIMER              | 10                    | I                | A              | Current Limit Timer.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                    |                       |                  |                | The value of the external capacitor ( $C_{TIMER}$ ) connected to the TIMER pin sets the two time periods used during a current-limit event. These are:                                                                                                                                                                                                                                                                                                                                   |

|                    |                       |                  |                | <ul> <li>The time that the GATE pin will limit the current through the<br/>external FET</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                       |

|                    |                       |                  |                | <ul> <li>The time that the GATE pin will disable the external FET</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                             |

|                    |                       |                  |                | During current limit, a pull-up current source charges up the external capacitor. Until the voltage on the TIMER pin reaches $V_{REFIN}/2$ , the GATE pin is driven to maintain a reduced current flow determined by the $V_{DS}$ of the external FET.                                                                                                                                                                                                                                   |

|                    |                       |                  |                | While the capacitor is being discharged by the pull-down current (pull-<br>up current is off), the GATE pin is at $V_{NEG}$ and the PWRGOOD pin is<br>deasserted. When the TIMER voltage falls below approximately<br>100 mV, the GATE pin turns on, if the RESTART pin is low, to reset the<br>internal fault latch. If the RESTART pin is high, the GATE pin remains<br>off until the ENABLE pin is forced low. It is then forced high or the<br>RESTART pin is forced low (asserted). |

|                    |                       |                  |                | The PWRGOOD pin reasserts after the voltages on the $\text{DRAIN}_{\text{TH}}$ and GATE pins meet the appropriate conditions.                                                                                                                                                                                                                                                                                                                                                            |

|                    |                       |                  |                | The TIMER pin pull-up current is proportioned to the I <sub>ISET</sub> current (approximately a multiple of 16).                                                                                                                                                                                                                                                                                                                                                                         |

| V <sub>NEG</sub>   | 11                    | I                | Р              | Negative supply input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                    |                       |                  |                | The negative voltage applied to the board by the backplane (typically the most negative voltage in the system).                                                                                                                                                                                                                                                                                                                                                                          |

| R <sub>DISCH</sub> | 12                    | I                | A              | External MOSFET activation delay.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                    |                       |                  |                | An external resistor ( $R_{RDISCH}$ ) is connected between the $R_{DISCH}$ pin<br>and the $V_{NEG}$ pin and is used to set the delay between the deactivation<br>and activation of the external pass MOSFET during a current-limit<br>event. The delay is set by the values of the external capacitor ( $C_{TIMER}$ )<br>and the external resistor ( $R_{RDISCH}$ ). The formulas are:                                                                                                   |

|                    |                       |                  |                | T <sub>DEACT</sub> = (C <sub>TIMER</sub> x R <sub>ISET</sub> ) / 16                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                    |                       |                  |                | $T_{ACT} = (9.2 \times R_{RDISCH} \times C_{TIMER})$                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Legend: TTL        | = TTL com             | patible input    | ST             | = Schmitt Trigger input with CMOS levels                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| =  r               |                       |                  |                | = Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                    | Power<br>Analog       |                  |                | IOS = CMOS-compatible input                                                                                                                                                                                                                                                                                                                                                                                                                                                              |