# TX-Standard Description and Implementation Guideline

# Concept

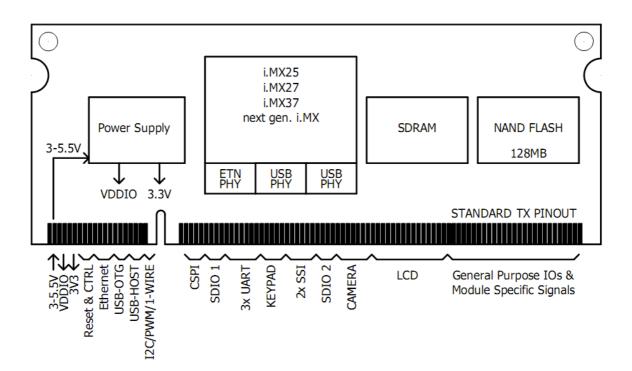

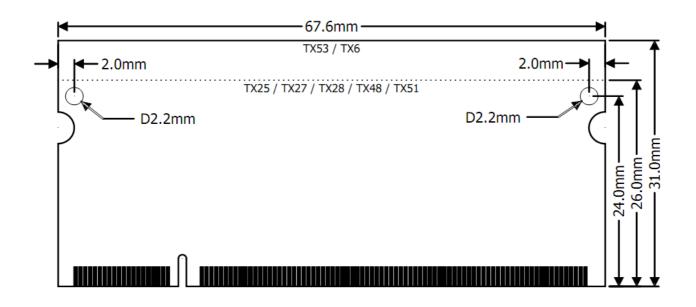

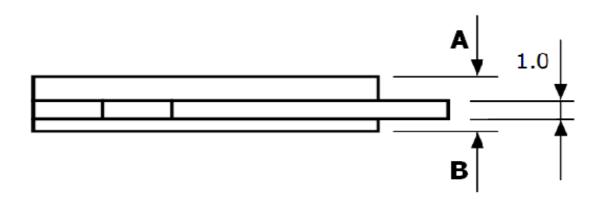

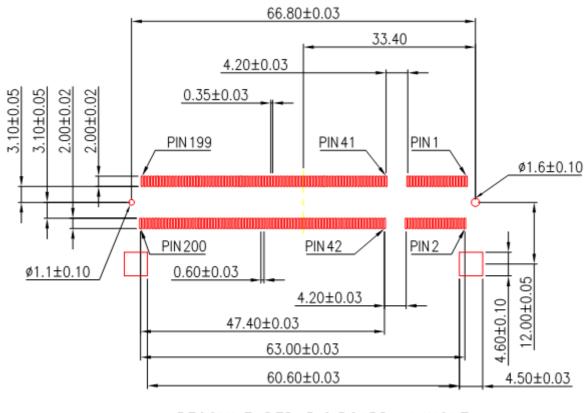

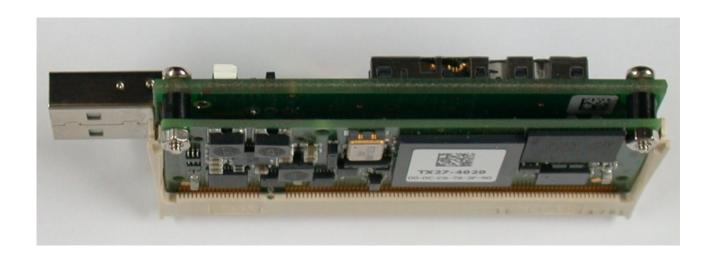

The TX embedded module integrates all the core components of a common PC and is mounted onto an application specific carrier board. TX modules have a standardized form factor of 67,6mm x 26mm, have specified pinouts and provide the functional requirements for an embedded application. These functions include, but are not limited to, graphics, network and multiple USB ports. A single ruggedized SO-DIMM connector provides the carrier board interface to carry all the I/O signals to and from the TX module. This SO-DIMM connector is a well known and proven high speed signal interface connector that is commonly used for memory cards in notebooks.

Carrier board designers can utilize as little or as many of the I/O interfaces as deemed necessary. The carrier board can therefore provide all the interface connectors required to attach the system to the application specific peripherals. This versatility allows the designer to create a dense and optimized package, which results in a more reliable product while simplifying system integration. Most importantly, TX applications are scalable, which means once a product has been developed, the product range can be diversified by using TX modules with a different performance class. Simply unplug one module and replace it with another, no redesign is necessary.

# Disclaimer

The information contained within this Specification, including but not limited to any product specification, is subject to change without notice.

Ka-Ro electronics provides no warranty with regard to this Specification or any other information contained herein and hereby expressly disclaims any implied warranties of merchantability or fitness for any particular purpose with regard to any of the foregoing.

# **Intended Audience**

This TX-Standard electromechanical description is intended for technically qualified personnel. It is not intended for general audiences.

# Copyright Notice

Copyright © 2010, Ka-Ro electronics GmbH. All rights reserved. All text, pictures and graphics are protected by copyrights. No copying is permitted without written permission.

We have made every attempt to ensure that the information in this document is accurate yet the information contained within is supplied "as-is".

# **Trademarks**

ARM ® is a registered trademark of ARM Limited.

All other brand and product names, trademarks, and copyrights are the property of their respective owners.

# Acronyms and Abbreviations

| Abbreviation | Explanation                                                                       |

|--------------|-----------------------------------------------------------------------------------|

| 100-Base-T   | Ethernet type that uses 100 Mega bits per second speed on RJ45 connectors and     |

|              | twisted pair wiring                                                               |

| ARM          | Advanced RISC Machines Limited CPU architecture                                   |

| JTAG         | Joint Test Action Group. This abbreviation is commonly used to refer to a test    |

|              | interface found on many modern integrated circuits. The JTAG test interface is a  |

|              | boundary scan register with serial interface and is described by an IEEE standard |

| GPIO         | General Purpose Input/Output                                                      |

| LCD          | Liquid Crystal Display                                                            |

| LED          | Light Emitting Diode.                                                             |

|              | An electronic component used as a visual indicator (light).                       |

| NC           | Not connected                                                                     |

| PCB          | Printed Circuit Board                                                             |

| RAM          | Random Access Memory                                                              |

| RoHS         | Restriction on Hazardous Substances: The Directive on the Restriction of the Use  |

|              | of Certain Hazardous Substances in Electrical and Electronic Equipment            |

|              | 2002/95/EC.                                                                       |

| UART         | Universal Asynchronous Receiver/Transmitter                                       |

| USB          | Universal Serial Bus                                                              |

# TX-Guide

# **Table of contents**

| 1 Feature Overview                                                    |    |

|-----------------------------------------------------------------------|----|

| 2 Connector Pin Assignments and Signal Descriptions                   |    |

| 2.1 Power Supply                                                      |    |

| 2.2 Reset & Bootmode                                                  |    |

| 2.3 RTC & Power-Button                                                |    |

| 2.4 Ethernet Signals                                                  |    |

| 2.4.1 Ethernet Physical Layer Layout Guidelines                       |    |

| 2.4.2 Power and Ground Planes                                         |    |

| 2.4.3 4 Layer Stackup                                                 |    |

| 2.4.4 2 Layer Stackup                                                 |    |

| 2.4.5 Component Placement                                             |    |

| 2.4.6 Design Techniques for EMI Suppression                           |    |

| · · · · · · · · · · · · · · · · · · ·                                 |    |

| 2.4.7 Controlled Impedance for Differential Signals                   |    |

| 2.4.8 Magnetics Module                                                |    |

| 2.5 USB                                                               |    |

| 2.5.1 USB Physical Layer Layout Guidelines                            |    |

| 2.5.2 Controlled Impedance for USB Traces                             |    |

| 2.5.3 Isolation of DP/DM Traces                                       |    |

| 2.5.4 Isolated shielding on the USB connector                         |    |

| 2.5.5 Optional VBUS protection                                        |    |

| 2.5.6 USB recommendations                                             | 22 |

| 2.6 I2C                                                               | 23 |

| 2.6.1 Example I2C Voltage Level Translator (TX27 and TX51 only)       | 24 |

| 2.6.1 I2C recommendations                                             | 25 |

| 2.7 PWM / 1-WIRE                                                      | 26 |

| 2.8 CSPI – Configurable Serial Peripheral Interface                   | 27 |

| 2.9 SDIO Interfaces                                                   |    |

| 2.9.1 SD-Card example diagram using level shifters                    |    |

| 2.9.2 SD-Card example diagram only for 3.3V modules                   |    |

| 2.10 UARTs                                                            |    |

| 2.10.1 UART Example diagram                                           |    |

| 2.11 Keypad Interface                                                 | 31 |

| 2.11 Reypad Interface                                                 |    |

| 2.12 Digital Addio Forts                                              |    |

|                                                                       |    |

| 2.14 Extended and 2nd CMOS Sensor Interface (TX51, TX53 and TX6 only) |    |

| 2.15 LCD Interface                                                    | 34 |

| 2.16 LVDS/SATA option (TX53, TX6 only)                                |    |

| 2.16.1 LVDS pin mapping                                               |    |

| 2.16.2 LVDS recommendations                                           |    |

| 2.16.3 SATA pin mapping                                               |    |

| 2.16.4 SATA recommendations                                           |    |

| 2.17 CAN Interface                                                    |    |

| 2.18 2nd Ethernet RMII (TX28 only)                                    |    |

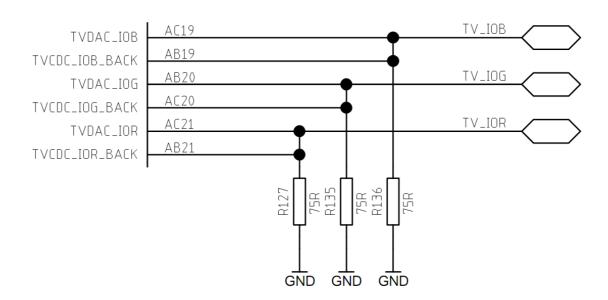

| 2.19 TV out (TX51, TX53 only)                                         | 38 |

| 2.19.1 TV Encoder Recommendations                                     | 38 |

| 2.20 PCI express (TX6 only)                                           | 39 |

| 2.20.1 PCI Express interface recommendations                          | 39 |

| ·                                                                     |    |

# TX-Guide

| 2.20.1.1 PCI Express general routing guidelines | 39 |

|-------------------------------------------------|----|

| 2.20.1.2 PCI Express coupling lane              |    |

| 2.20.2 PCIe recommendations                     |    |

| 2.21 GPIO and module specific signals           | 40 |

| 3 Optional Debugging Connector                  |    |

| 3.1 Debug Connector Signal Assignment           |    |

| 3.2 Debug connector location                    | 42 |

| 4 Mechanical                                    | 43 |

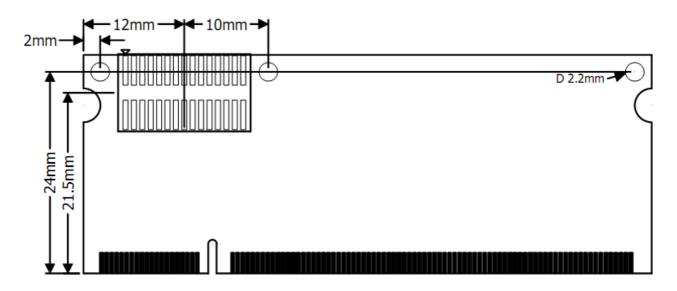

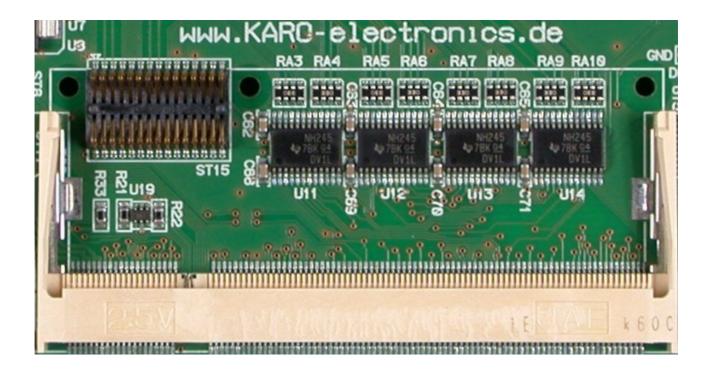

| 4.1 TX module outline                           | 43 |

| 4.2 SO-DIMM connector                           |    |

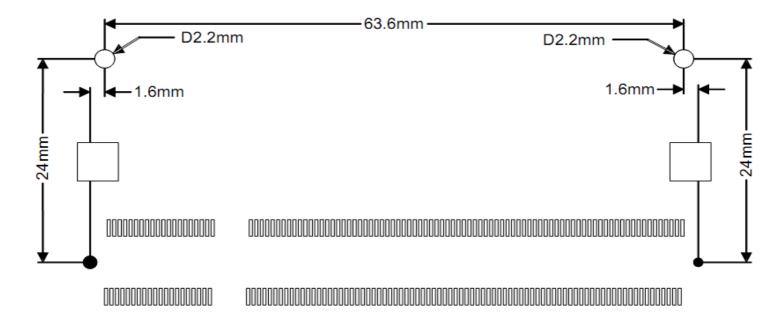

| 4.3 DIMM Connector PCB Layout example           | 45 |

| 4.4 TX Fastener Kit                             | 46 |

| 4.5 TX Heatsink Kit (17 K/W)                    | 47 |

| 4.6 TX Heatsink Kit (7 K/W)                     | 48 |

| 4.7 Heat conductive gel foil                    |    |

| 5 Document Revision history                     | 50 |

# 1 Feature Overview

TX modules offers the newest I/O technologies on a minimum size form factor. This includes serial high speed buses such as:

- Ethernet

- USB

- SD Secure Digital Card

- SPI Serial Peripheral Interface

#### Multimedia interfaces

- CMOS Sensor Interface

- LCD True Color Display Interface (24bpp)

#### Other Standard Interfaces

- UART Universal Asynchronous Receiver/Transmitters

- I2C Inter-Integrated Circuit

- PWM Pulse-Width Modulator

- 1-WIRE Interface

Plus additional control and power management signals. The versatile power supply outputs can also be used for the baseboard and defines the IO voltage used for the module. 1.8V and 3.3V IO voltage modules can be used on universal baseboards like the Starterkit V without the need for any change on the baseboard or jumper setting.

# 2 Connector Pin Assignments and Signal Descriptions

Signal names beginning with a "#" symbol indicates that the active, or asserted state, occurs when the signal is at a low voltage level. When "#" is not present, the signal is asserted when at a high voltage level. Differential pairs are indicated by trailing 'P' and 'N' for the positive or negative signal.

The following terminology is used to describe columns for the tables located below.

| Term  | Describtion                                                                                                                     |  |  |  |  |

|-------|---------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| I     | Input                                                                                                                           |  |  |  |  |

| 0     | Output                                                                                                                          |  |  |  |  |

| I/O   | Bi-directional Input/Output Pin                                                                                                 |  |  |  |  |

| VDDIO | I/O type depends on the VDDIO voltage of the module                                                                             |  |  |  |  |

| 3V3   | I/O type: CMOS 3.3V                                                                                                             |  |  |  |  |

| 5V    | I/O type: CMOS 3.3V to 5V                                                                                                       |  |  |  |  |

| power | Power supply pin                                                                                                                |  |  |  |  |

| USB   | Universal Serial Bus differential pair signals In compliance with the Universal Serial Bus Specification 2.0                    |  |  |  |  |

| ETN   | Ethernet Media Dependent Interface differential pair signals. In compliance with IEEE 802.3ab 100Base-T Ethernet Specification. |  |  |  |  |

| NC    | Not Connected                                                                                                                   |  |  |  |  |

| PU    | Pull-up resistor                                                                                                                |  |  |  |  |

|       |                                                                                                                                 |  |  |  |  |

|       |                                                                                                                                 |  |  |  |  |

|       |                                                                                                                                 |  |  |  |  |

# 2.1 Power Supply

| Pin                                                                       | Signal |                                                                                                     |                        | type                                   | I/O   |   |

|---------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------|------------------------|----------------------------------------|-------|---|

| 1-4                                                                       | VDDIN  | Module power supply input (ob                                                                       | serve DIMM socket co   | ontact current rating)                 | power | I |

|                                                                           |        | 1.8V or 3.3V I/O power supply<br>This output can be used for the<br>or for peripherals which are op | e module side supply o |                                        |       |   |

|                                                                           |        | Module                                                                                              | Rer                    | mark                                   |       |   |

|                                                                           |        | TX27                                                                                                | VDDIO=1.8V             | max. 900mA                             |       |   |

| 5-7                                                                       | VDDIO  | TX51                                                                                                | VDDIO=1.6V             | max. 200mA                             | power | 0 |

|                                                                           |        | TX28S                                                                                               |                        | max. 20mA                              |       |   |

|                                                                           |        | TX25, TX28                                                                                          | VDDIO-3 3V             | max. 200mA                             |       |   |

|                                                                           |        | TX48, TX53                                                                                          | VDDIO=3.3V             | max. 900mA                             |       |   |

|                                                                           |        | TX6                                                                                                 |                        | Max. 300mA                             |       |   |

|                                                                           |        | +3.3V Power supply output                                                                           |                        |                                        |       |   |

|                                                                           |        | Module                                                                                              | Rer                    | nark                                   |       |   |

| 9-12                                                                      | VDD33  | TX27                                                                                                | man,                   | . 1 1                                  | power | 0 |

|                                                                           |        | TX51                                                                                                | max. 1A                |                                        |       |   |

|                                                                           |        | TX25, TX28, TX48, TX53, TX6                                                                         |                        | are connected on the to ratings above. |       |   |

| 18,26,32,39,50,58,71,82,<br>88,94,102,111,116,129,<br>142,147,160,171,200 | GND    |                                                                                                     |                        |                                        |       |   |

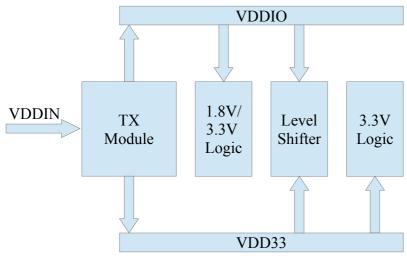

TX modules operates on a single 3.3V to 5.5V supply and provide regulated power supply outputs to the baseboard.

The use of level shifters on the baseboard to interface to 3.3V logic allows for universal module selection, because the voltage is automatically translated between VDDIO (1.8V or 3.3V) and VDD33 (3.3V) levels. Level shifters can be omitted on 3.3V only modules like the TX25, but in that case it's not possible to use 1.8V modules anymore.

# 2.2 Reset & Bootmode

| Pin | Signal     |                                                                                                                                                                           | Description                                                                                                                                                                                                                                                                                                                         | type     | I/O |

|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----|

|     |            | system reso                                                                                                                                                               | ot Mode Select - The operational system boot mode of the module upon et is determined by the settings of this pin.  E=H: Boot from NAND / L: Boot from UART/USB  en or connect to VDDIO if not used.                                                                                                                                | VDDIO    |     |

| 8   | BOOTMODE   |                                                                                                                                                                           | Remark                                                                                                                                                                                                                                                                                                                              | PU       | I   |

|     |            | TX28                                                                                                                                                                      | Depending on BOOTMODE external pull-up/-down resistors are selected on LCD interface signals LD0LD5 and LCD_RS (pin 146). Refer to the TX28 datasheet for resistor values and level needed at startup!                                                                                                                              |          |     |

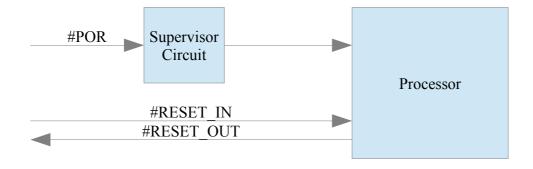

| 15  | #RESET_OUT | #RESET_O the module                                                                                                                                                       | Reset carrier board peripherals  UT may be used to reset peripherals on the carrier board. Depending on type this signal might be asserted automatically by a system reset, but troller by a GPIO function during runtime on all modules.                                                                                           | VDDIO    | 0   |

| 16  | #POR       | Typically a A supervisor device asse programme                                                                                                                            | Reset - active low input signal.  push button reset, pull low to force a reset.  or circuit is used on the TX module to monitor the power supply. This  ert a processor system reset (POR_B) if the power supply falls outside the  ed threshold or a manual reset (#POR) is asserted externally.  o VIN or leave open if not used. | 5V<br>PU | I   |

|     |            | Module                                                                                                                                                                    | Remark                                                                                                                                                                                                                                                                                                                              | FU       |     |

|     |            | TX28                                                                                                                                                                      | The i.MX28 power-on reset is generated internally.  If low the module power supply is disconnected.                                                                                                                                                                                                                                 |          |     |

|     |            | TX28S                                                                                                                                                                     | Not connected                                                                                                                                                                                                                                                                                                                       |          |     |

| 17  | #RESET_IN  | Master Reset - external active low Schmitt trigger input signal. When this signal goes active, all modules (except the reset module, SDRAMC module, and the clock control |                                                                                                                                                                                                                                                                                                                                     |          |     |

# 2.3 RTC & Power-Button

| Pin | Signal      |                                                   | Description                                                                                                                                                                                                                                                                             |       |   |  |  |  |

|-----|-------------|---------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---|--|--|--|

|     |             | 3.7V for prope<br>lithium button<br>super cap whe | backup power supply. Supply voltage must be held between 1.3V and er RTC operation. This pin can be connected to a primary cell such as a cell. Additionally, this pin can be connected to a rechargeable cell or a en used with the trickle charge feature.  39 datasheet for details. |       |   |  |  |  |

| 13  | VBACKUP     | Module                                            | Remark                                                                                                                                                                                                                                                                                  | power | I |  |  |  |

|     |             | TX25                                              | Connected to BAT_VDD DRYICE backup power supply input, max. 1.55V The i.MX25 internal RTC is not supported                                                                                                                                                                              |       |   |  |  |  |

|     |             | TX6 without DS1339                                | i.MX6 RTC backup power supply. Supply voltage must be held between 2.9V and 3.3V for proper RTC operation.                                                                                                                                                                              |       |   |  |  |  |

|     |             | PMIC depende                                      | ent Function. Leave unconnected if not used.                                                                                                                                                                                                                                            |       |   |  |  |  |

|     |             | Module                                            | Remark                                                                                                                                                                                                                                                                                  |       |   |  |  |  |

|     |             | TX25                                              | No PMIC onboard - Not connected                                                                                                                                                                                                                                                         |       |   |  |  |  |

|     |             | TX28                                              | PSWITCH - Used for chip power on or recovery. PSWITCH is at MID level by default. Refer to i.MX28 reference manual for details.                                                                                                                                                         |       |   |  |  |  |

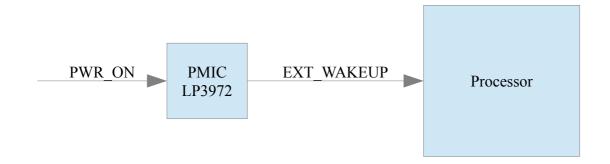

| 14  | PMIC_PWR_ON | TX27, TX51                                        | This is an active high push button input which can be used to signal PWR_ON and PWR_OFF events to the CPU by controlling the PMIC EXT_WAKEUP. Refer to LP3972 datasheet, page 49 for details.                                                                                           |       | I |  |  |  |

|     |             | TX48, TX53                                        | Connected to LTC3589 WAKE. To power down, drive this pin LOW. Refer to LTC3589 datasheet, page 29 for details.                                                                                                                                                                          |       |   |  |  |  |

|     |             | TX6                                               | Connected to PMIC ON. Refer to PMIC datasheet for details.                                                                                                                                                                                                                              |       |   |  |  |  |

# 2.4 Ethernet Signals

| Pin | Signal             |                               | Description                                                                                                                                                        | type | I/O |  |  |  |

|-----|--------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|--|--|--|

| 1   | ETN_TXN<br>ETN_TXP | 100Base-TX or                 | 10Base-T differential transmit output to magnetics.                                                                                                                | ETN  | 0   |  |  |  |

|     |                    | Active low LINI               | CON indication: Active indicates that the link is on.                                                                                                              |      |     |  |  |  |

| 20  | #FTN   TNUZ FD     | Module                        | Module Remark                                                                                                                                                      |      |     |  |  |  |

| 20  | #ETN_LINKLED       | TX28, TX48,<br>TX53, TX6      | WILL OU TOUCH WHEN THE ODERSHING SHEET IS THINDDS OF CHIRDOLINE                                                                                                    |      |     |  |  |  |

| 22  | ETN_3V3            |                               | 3.3V analogue power supply output to magnetics. This power supply can be turned ff on the module to reduce the power consumption in the case Ethernet is not eeded |      |     |  |  |  |

| 1   | ETN_RXN<br>ETN_RXP | 100Base-TX or                 | 10Base-T differential receive input from magnetics.                                                                                                                | ETN  | I   |  |  |  |

|     |                    | Active low ACT the active PMD | ctive low ACTIVITY indication: Active indicates that there is Carrier sense (CRS) from the active PMD.                                                             |      |     |  |  |  |

| 24  | #ETN_ACTLED        | Module                        | Module Remark                                                                                                                                                      |      |     |  |  |  |

|     |                    | TX28, TX48,<br>TX53, TX6      |                                                                                                                                                                    |      |     |  |  |  |

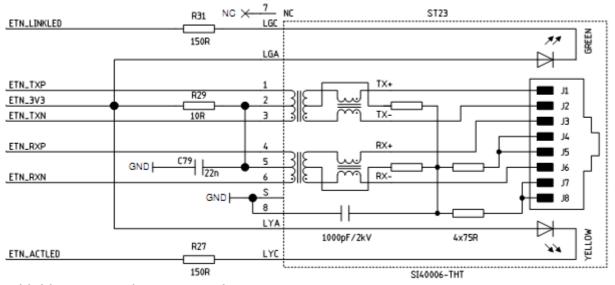

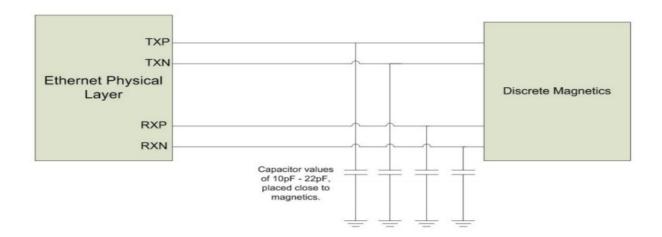

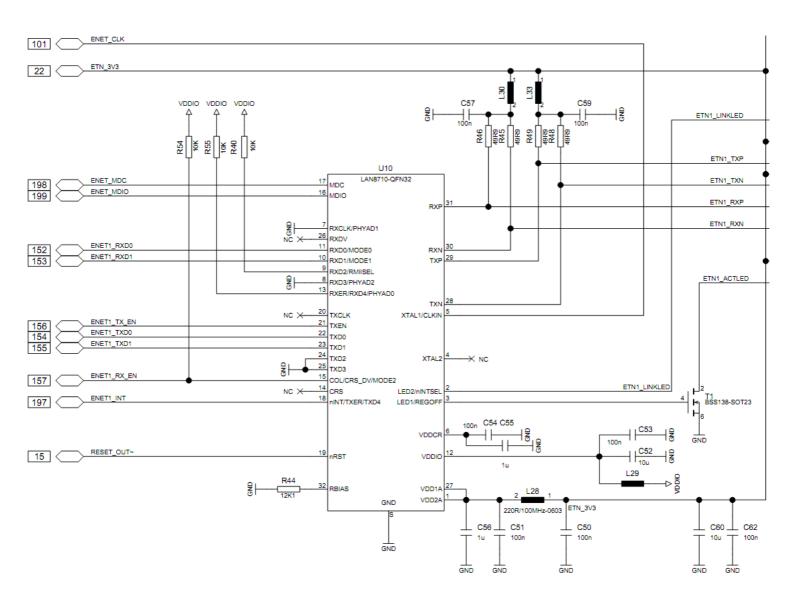

Abbildung 2.1: Ethernet Sample Diagram

#### 2.4.1 Ethernet Physical Layer Layout Guidelines

TX modules are designed for 10 or 100 Mbps Ethernet systems. They are based on IEEE 10BASE-T and 100BASE-TX standards. The IEEE 802.3-2005 standard for 100BASE-TX defines networking over two pairs of Category 5 unshielded twisted pair cable or Type 1 shielded twisted pair cable. The following recommendations for the printed circuit board layout are not the only way to layout TX modules. Every board designer will have a preference. Complexity, board space, number and types of devices will dictate routing and placement strategies.

#### 2.4.2 Power and Ground Planes

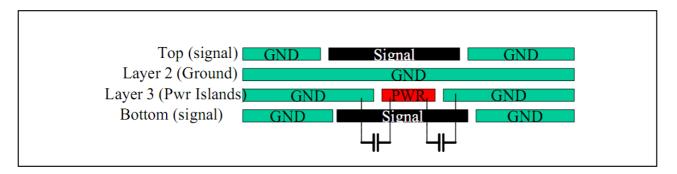

The sections below describe typical 2 and 4 layer board stackups. The goal of the 4 layer designs is to keep the signal routing on outer layers, isolated by the power and ground planes. These power and ground planes also serve the purpose of reference planes for the signal traces. The signal traces should run over continuous reference planes when possible. When 2 layer board designs are required, it remains necessary that the signal traces run over continuous reference planes when possible.

# 2.4.3 4 Layer Stackup

- TOP (Layer 1) Signal with ground plane except where noted.

- Layer 2 Continuous ground plane. No signals should be routed on this layer.

- Layer 3 Power planes with ground planes except where noted. Signals may be routed on this layer if needed.

- Bottom (Layer 4) Signal with ground plane except where noted.

- Decouple ground floods and ground layer as practical. When signal traces are re-referenced to power island planes, decoupling capacitors (10nF ceramic) are required between the ground plane and power plane.

- Signal traces routed on bottom layer over power islands that are on Layer 3 layer should have decoupling capacitors (10nF ceramic) near the trace to enable short (direct) return current paths.

- When signal traces are re-referenced to power island planes, decoupling capacitors (10nF ceramic) are required between the ground plane and power plane as shown below.

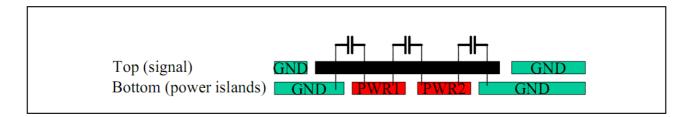

# 2.4.4 2 Layer Stackup

- TOP (Layer 1) Signal with ground plane except where noted.

- Bottom (Layer 1) Ground plane and power islands. A limited number of slow speed signals may be routed on the bottom layer.

- Signal traces should be surrounded by ground or ground trace along at least one edge. If ground trace is used, it should be connected to ground plane on this layer and decoupled to ground plane on top layer.

- Decouple ground planes as practical, as shown below. This will allow short (direct) return current paths when signal traces are re-referenced to different power island planes.

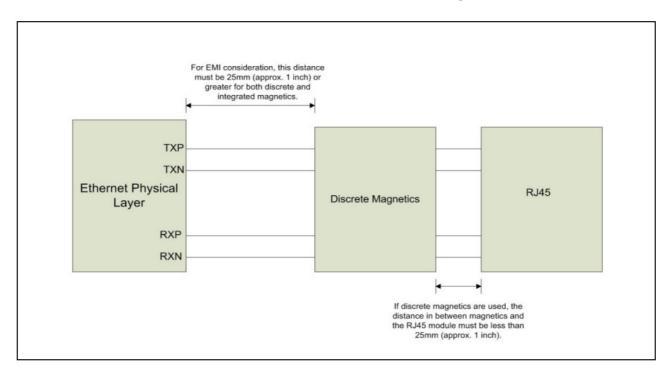

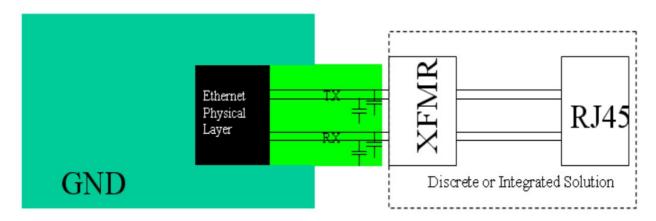

# 2.4.5 Component Placement

Component placement can affect signal quality, emissions, and component operating temperature. Careful component placement can decrease potential EMI problems and simplify the task of routing traces.

- If the magnetic is a discrete component, then the distance between the magnetic and the RJ-45 needs to have the highest consideration and be kept to under 25mm (approx. 1 inch) of separation.

- The distance between the SO-DIMM socket and the magnetics needs to be 20mm or greater. Among PHY vendors, the 25mm (approx. 1 inch) rule is considered good design practice for EMI considerations. The intention is to isolate the PHY from the magnetics.

# 2.4.6 Design Techniques for EMI Suppression

The following techniques may improve EMI margin.

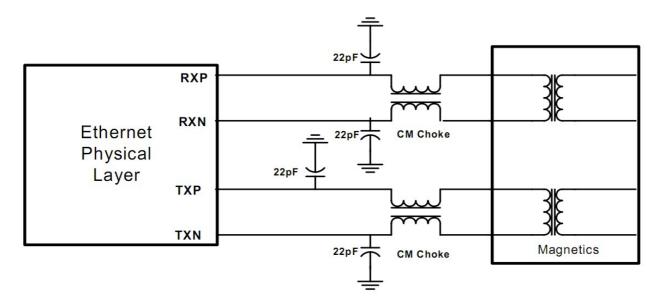

• Common mode capacitors may be added to the TX+/- and RX+/- signals for high frequency attenuation , as shown below. One end of each capacitor should be connected to the system

ground plane, and placed within 10mm (approx. 400mils) of the magnetics. Typical capacitance values should be between 10pF and 22pF. Values higher than 22pF may negatively impact the TX and RX signalling.

• Common mode chokes may be added to the TX and RX differential pairs as shown below. The common mode chokes should be placed within 10mm (approx. 400mils) of the integrated RJ45 module, and on the magnetics side of the common mode EMI suppression capacitors. Typical common mode impedance of the common mode choke selected should be  $2k\Omega@100MHz$  or higher.

In general, no ground plane should extend under the TX and RX differential pairs, under the magnetics, or under the RJ45 jack. In the case where common mode capacitors used for EMI suppression, a ground plane may be located under the TX and RX signals, however the plane must not exceed beyond the capacitors. When designing 4 layer boards, the ground plane should exist on layer 4, assuming the differential pair is routed on layer 1. On 2 layer boards, the ground plane can be located on layer 2, the adjacent layer to the TX and RX signal pairs. Under no circumstances should a ground plane exist under the magnetics, the RJ45 connector or in between the magnetics and RJ45 connector.

# 2.4.7 Controlled Impedance for Differential Signals

The 802.3-2005 specifications requires the TX and RX lines to run in differential mode. The TXP and TXN are a differential pair and need to be designed to a 100 ohm differential impedance. The RXP and RXN traces are also a differential pars and need to be designed to a 100 ohm differential impedance target.

The board designer must maintain 100 ohm differential impedance in the layout for all differential pairs. For differential dielectric thickness, copper weight or board stack-up, trace width and spacings will need to be calculated.

Differential pair nets must maintain symmetry. TXP and TXN must be equal length and symmetric with regards of shape, length, and via count. RXP and RXN must also be equal length and symmetric.

Isolation of TX/RX traces. The TX/RX traces must be isolated from nearby circuitry and signals. Maintain a distance of parts to lines that are greater than or equal to 5 times the distance of the spacing between the traces. Do not route differential pairs under parts. Do not cross TX/RX lines with other PCB traces unless the traces are on the opposite side of the ground plane from TX/RX.

# 2.4.8 Magnetics Module

The magnetics module has a critical effect on overall IEEE and emissions conformance. The device should meet the performance required for a design with reasonable margin to allow manufacturing variation. Occasionally, components that meet basic specifications may cause the system to fail IEEE testing, because of interactions with other components or the Printed Circuit Board itself. Carefully qualifying new magnetics modules can go a long way toward preventing this type of problem.

Suggested magnetics have not been tested in order to verify proper operation. This category of magnetic has been evaluated by the contents of the vendor supplied data sheet and legacy performance only. However, the designer can assume with some degree of confidence, that with proper PCB design techniques, the magnetics presented as suggested magnetics will perform to high standards.

Qualified magnetics have been tested by the PHY vendor in order to verify proper operation. The designer can assume with a high degree of confidence, that with proper PCB design techniques, the qualified magnetics perform to the highest standards.

| Vendor                       | Part Number                          | Package         | Temp      | Status               |

|------------------------------|--------------------------------------|-----------------|-----------|----------------------|

| Pulse                        | H1102                                | 16-pin SOIC     | 0°+70°C   | Qualified            |

| Halo                         | TG110-RP55N5                         | 16-pin SOIC     | 0°+70°C   | Qualified            |

| Halo                         | HFJ11-RP26E-L12RL                    | Integrated RJ45 | 0°+70°C   | Qualified            |

| Delta                        | RJSE1R5310A                          | Integrated RJ45 | 0°+70°C   | Qualified            |

| Pulse                        | J0011D01B                            | Integrated RJ45 | 0°+70°C   | Suggested            |

| Bothhand                     | TS6121C                              | 16-pin SOIC     | 0°+70°C   | Suggested            |

| Bothhand                     | LU1S041X-43                          | Integrated RJ45 | 0°+70°C   | Suggested            |

| Pulse                        | HX1102                               | 16-pin SOIC     | -40°+85°C | Qualified            |

| Halo                         | TG110-RPE5N5                         | 16-pin SOIC     | -40°+85°C | Qualified            |

| Halo                         | HFJ11-RPE26E-L12RL                   | Integrated RJ45 | -40°+85°C | Qualified            |

| TDK                          | TLA-6T717W                           | Integrated RJ45 | -40°+85°C | Qualified            |

| Delta                        | LFE8505T                             | 16-pin SOIC     | -40°+85°C | Qualified            |

| Midcom                       | 000-7090-37R                         | 16-pin SOIC     | -40°+85°C | Suggested            |

| Midcom                       | MIC66211-5171T-LF3                   | Integrated RJ45 | -40°+85°C | Suggested            |

| Elec & Eltek                 | 820-M0323R                           | 16-pin SOIC     | -40°+85°C | Suggested            |

| Midcom /<br>Würth-Elektronik | MIC24013-5101T-LF3<br>749 901 121 11 | Integrated RJ45 | 0°+70°C   | Used on Starterkit 5 |

| Bel Stewart                  | SI-60005-F                           | Integrated RJ45 | N/A       |                      |

#### 2.5 USB

| Pin      | Signal                       |                  | Description                                                                                                                          | type | I/O |  |

|----------|------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------|------|-----|--|

| 27<br>34 | USBH_VBUSEN<br>USBOTG_VBUSEN | This pin is used | I to enable the external VBUS power supply.                                                                                          | 3V3  | 0   |  |

| 28<br>36 | #USBH_OC<br>#USBOTG_OC       |                  | rive low over-current indicator input connected to a GPIO. s signal can be used as an input only.                                    |      |     |  |

|          |                              | VBUS pin of the  | JS pin of the USB cable. This pin is used for the VBUS comparator inputs.                                                            |      |     |  |

| 30       | USBH_VBUS                    | Module           | Remark                                                                                                                               | Γ\/  | _   |  |

| 38       | USBOTG_VBUS                  | TX25             | USBH_VBUS / USBOTG_VBUS unused / Not connected                                                                                       | 5V   | 1   |  |

|          |                              | TX28             | USBH_VBUS unused / Not connected                                                                                                     |      |     |  |

| 31<br>29 | USBH_DP<br>USBH_DM           | USB Host port    | differential data signal                                                                                                             | USB  | I/O |  |

| 37<br>35 | USBOTG_DP<br>USBOTG_DM       | USB OTG port     | differential data signal                                                                                                             | USB  | I/O |  |

| 33       | USBOTG_ID                    | ID pin of the Ut | pin of the USB cable. For an A-Device ID is grounded. For a B-Device ID is ated.                                                     |      |     |  |

|          | Module Remark                |                  |                                                                                                                                      |      |     |  |

|          |                              |                  | SEN, USBOTG_OC are also used for the $2^{nd}$ CAN interface. In than inctionality may be omitted or other GPIO's may be used instead |      | e   |  |

# 2.5.1 USB Physical Layer Layout Guidelines

The TX modules includes the physical layer interface (PHY) for systems using Hi-Speed USB. Proper design techniques must be used in printed circuit board (PCB) layout to maintain the signal integrity required for 480 Mbps operation.

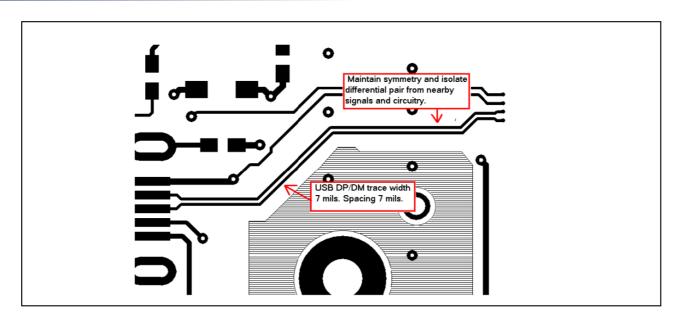

### 2.5.2 Controlled Impedance for USB Traces

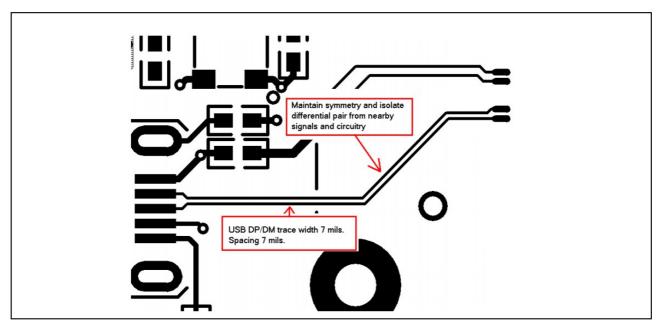

the USB 2.0 specification requires that the USB DP/DM traces maintain a nominal 90 Ohms +/- 15% differential impedance (see USB specification Rev. 2.0, paragraph 7.1.1.3 for more details). In the example design the traces are 7 mil (175um) wide with line spacing of 7 mils. These numbers are derived for 5 mil (125um) distance from ground reference plane. A continuous ground plane is required directly beneath the DP/DM traces and extending at least 5 times the spacing width to either side of DP/DM lines.

Maintain symmetry between DP/DM lines in regards to shape and length.

Single sided impedance is not as critical as differential impedance. A range of 42 to 78 Ohms is acceptable (equivalently, common mode impedance must be between 21 Ohms and 39 Ohms).

The figures show DP/DM traces with approximately equal trace length and symmetry. It is important to maintain a conductor width and spacing that provides differential and common mode impedance compliant with the USB specification. Use 45 degree turns to minimize impedance discontinuities.

# 2.5.3 Isolation of DP/DM Traces

The DP/DM lines must be isolated from nearby circuits and signals. Maintain a distance of components to lines that is greater or equal to 5 times the distance of the spacing between the traces. Do not route differential pairs under components. Do not cross DP/DM lines with other PCB traces unless the traces are on the opposite side of the ground plane from DP/DM. Route DP/DM over solid ground plane with no ground plane splits under the traces.

# 2.5.4 Isolated shielding on the USB connector

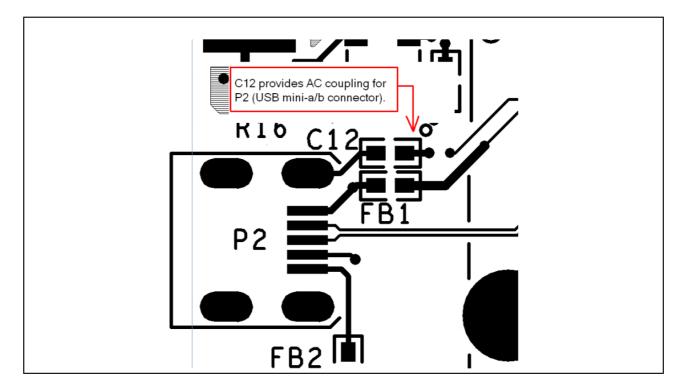

The figure shows the Mini-AB connector housing is isolated but AC coupled to the device ground. Industry convention is to ground only the host side of the cable shield. This is done to provide cable shielding while preventing possible ground currents from flowing in the USB cable if there happens to be a potential difference between the host and device grounds. If DC grounding is required replace C12 with a zero Ohms resistor.

In OTG applications the shield may be DC grounded at both ends of the cable.

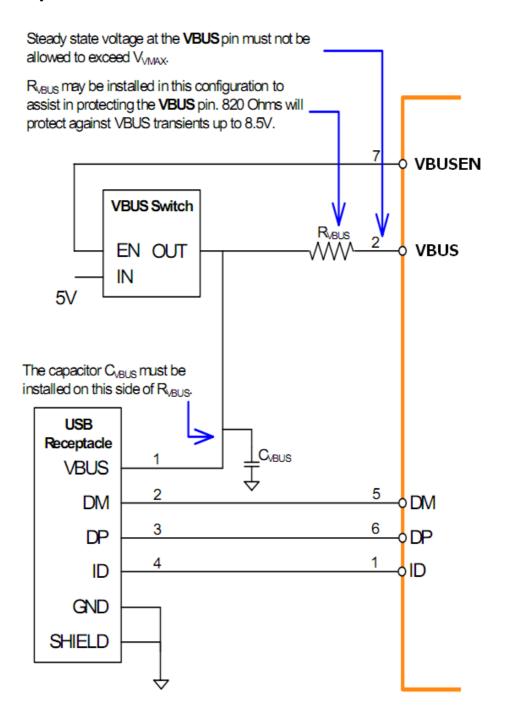

# 2.5.5 Optional VBUS protection

#### 2.5.6 USB recommendations<sup>1</sup>

In summary use the following recommendations for the USB.

- Route DP and DM signals on the top or bottom layer of the board

- The trace width and spacing of the DP and DM signals should be such that the differential impedance is  $90~\Omega$ .

- Route traces over continuous planes (power and ground).

- They should not pass over any power/GND plane slots or anti-etch.

- When placing connectors, make sure the ground plane clearouts around each pin have ground continuity between all pins.

- Maintain the parallelism (skew matched) between DP and DM; these traces should be the same overall length.

- Do not route DP and DM traces under oscillators or parallel to clock traces and/or data buses.

- Minimize the lengths of high speed signals that run parallel to the DP and DM pair.

- Keep DP and DM traces as short as possible.

- Route DP and DM signals with a minimum amount of corners. Use 45-degree turns instead of 90degree turns.

- Avoid layer changes (vias) on Dm and Dp signals. Do not create stubs or branches.

1

<sup>1</sup> Freescale Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors, Chap. 2.11

#### 2.6 I2C

| Pin  | Signal                       | Descr                                                                          | iption             | type         | I/O         |

|------|------------------------------|--------------------------------------------------------------------------------|--------------------|--------------|-------------|

| 40   | I2C_DATA                     | I2C Data                                                                       |                    | VDDIO        | I/O         |

| 41   | I2C_CLK                      | I2C Clock                                                                      |                    | VDDIO        | 0           |

|      | Module                       | Devices connect                                                                | ted to this I2C bu | ıs           |             |

|      | TX27, TX28S,<br>1, TX53, TX6 | No devices are connected to this I2C bus.  No pullup's are used on the module. |                    |              |             |

|      |                              | Name                                                                           | Туре               | Speed [kbps] | Address     |

|      | TV20                         | DS1339                                                                         | RTC                | 400          | 1101000 r/w |

|      | TX28                         | PCA9554                                                                        | IO                 | 400          | 0100000 r/w |

| TX48 |                              | DS1339                                                                         | RTC                | 400          | 1101000 r/w |

|      | 1740                         | LTC3589                                                                        | PMIC               | 400          | 0110100 r/w |

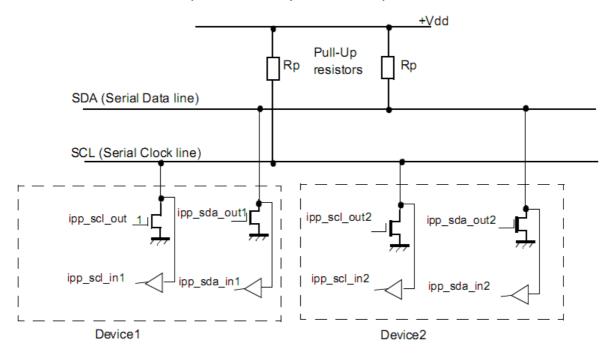

The I2C is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices. This bus is suitable for applications requiring occasional communications over a short distance between many devices. The flexible I2C allows additional devices to be connected to the bus for expansion and system development.

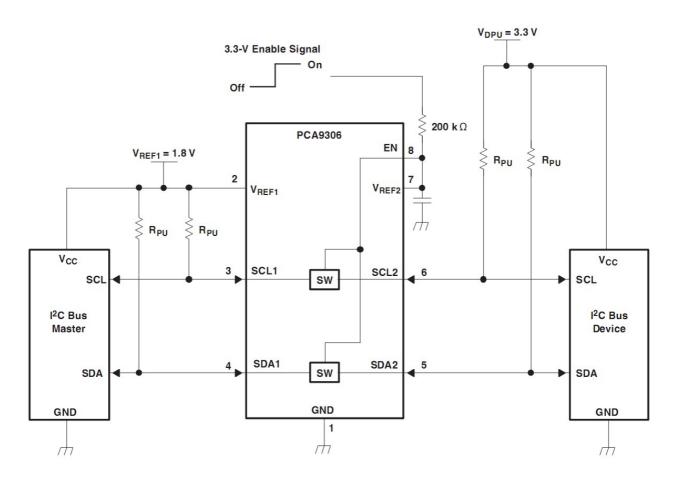

# 2.6.1 Example I2C Voltage Level Translator (TX27 and TX51 only)

The Texas Instruments PCA9306 allows bidirectional voltage translations between 1.2 V and 5 V, without the use of a direction pin.

Be aware of the PCA9306 min. supply voltage: VREF2 > VREF1 + 0.6V. Because of this limitation a Texas Instruments TXS0102 should be used instead if the design is intended to be used with 1.8V and 3.3V TX modules.

As with the standard I2C system, pullup resistors are required to provide the logic high levels on the translator's bus. The PCA9306 has a standard open-collector configuration of the I2C bus. The size of these pullup resistors depends on the system, but each side of the repeater must have a pullup resistor. The device is designed to work with standard-mode and fast-mode I2C devices, in addition to SMBus devices. Standard-mode I2C devices only specify 3 mA in a generic I2C system where standard-mode devices and multiple masters are possible. Under certain conditions, high termination currents can be used.

#### PULLUP RESISTOR VALUES(1)(2)

|                  | PULLUP RESISTOR VALUE (Ω) |                     |         |          |         |                     |  |  |

|------------------|---------------------------|---------------------|---------|----------|---------|---------------------|--|--|

| .,               | 15                        | mA                  | 10      | mA       | 3 r     | n <b>A</b>          |  |  |

| V <sub>DPU</sub> | NOMINAL                   | +10% <sup>(3)</sup> | NOMINAL | +10% (3) | NOMINAL | +10% <sup>(3)</sup> |  |  |

| 5 V              | 310                       | 341                 | 465     | 512      | 1550    | 1705                |  |  |

| 3.3 V            | 197                       | 217                 | 295     | 325      | 983     | 1082                |  |  |

| 2.5 V            | 143                       | 158                 | 215     | 237      | 717     | 788                 |  |  |

| 1.8 V            | 97                        | 106                 | 145     | 160      | 483     | 532                 |  |  |

| 1.5 V            | 77                        | 85                  | 115     | 127      | 383     | 422                 |  |  |

| 1.2 V            | 57                        | 63                  | 85      | 94       | 283     | 312                 |  |  |

<sup>(1)</sup> Calculated for  $V_{OL} = 0.35 \text{ V}$

# 2.6.1 I2C recommendations<sup>2</sup>

| Recommendation                                                                                                                                                                                 | Explanation                                                                                                                                                                                                                                      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Verify the target I2C interface clock rates.                                                                                                                                                   | The bus can only operate as fast as the slowest peripheral on the bus. If faster operation is required, move the slow devices to another I2C port. A slow peripheral may unpredictably take over the bus or might malfunction in some other way. |

| Verify that the target I2C address range is supported and does no conflict with other peripherals. If there is an unavoidable address conflict, move the offending device to another I2C port. | If it is undesirable to move a conflicting device to another I2C port, review the peripheral operation to see if it supports remapping the address.                                                                                              |

| Do not place more than one set of pullup resistors on the I2C lines                                                                                                                            | This can result in excessive loading. Good design practice is to place one pair of pullups only.                                                                                                                                                 |

<sup>(2)</sup> Assumes output driver V<sub>OL</sub> = 0.175 V at stated current (3) +10% to compensate for V<sub>DD</sub> range and resistor tolerance

Freescale Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors, Table 1-4

# 2.7 PWM / 1-WIRE

| Pin | Signal |                  | Description                                                     | type  | I/O |

|-----|--------|------------------|-----------------------------------------------------------------|-------|-----|

|     |        | Pulse-Width Modu | lator (PWM) Output                                              |       |     |

| 42  | PWM    | Module           | Remark                                                          | VDDIO | 0   |

|     |        | TX51             | Be aware of the voltage level on this pin: 3.1V instead of 1.8V |       |     |

|     |        | 1-Wire           |                                                                 |       |     |

| 43  | OWIRE  | Module           | Remark                                                          | VDDIO | I/O |

|     |        | TX28/TX48/TX6    | No 1-Wire controller – a GPIO is used instead                   |       |     |

1-Wire is a registered trademark of Dallas Semiconductor for a device communications bus systems designed by Dallas Semiconductor that provides low-speed data, signalling and power over a single signal, albeit using two wires, one for ground, one for power and data. 1-Wire is similar in concept to I2C, but with lower data rates and longer range. It is typically used to communicate with small inexpensive devices.

# 2.8 CSPI – Configurable Serial Peripheral Interface

| Pin | Signal    | Description                                                                                                                                                                                                                                                                                                      | type  | I/O |

|-----|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|

| 44  | CSPI_SS0  | Slave Select bidirectional, selectable polarity signal, output in master mode, and                                                                                                                                                                                                                               | VDDIO | I/O |

| 45  | CSPI_SS1  | input in slave mode.                                                                                                                                                                                                                                                                                             | VDDIO | I/O |

| 46  | CSPI_MOSI | Master Out Slave In bidirectional signal, which is TxD output signal from the data shift register in master mode. In Slave mode it is RxD input to the data shift register.                                                                                                                                      | VDDIO | I/O |

| 47  | CSPI_MISO | Master In Slave Out bidirectional signal, which is RxD input signal to the data shift register in master mode. In Slave mode it is TxD output from the data shift register.                                                                                                                                      | VDDIO | I/O |

| 48  | CSPI_SCLK | CSPI Clock bidirectional signal, which is CSPI clock output in master mode. In slave mode it is an input CSPI clock signal.                                                                                                                                                                                      | VDDIO | I/O |

| 49  | CSPI_RDY  | Serial Data Ready signal - This input signal is used for hardware control only in master mode. It indicates that external SPI slave is ready to receive data. It will edge or level trigger a CSPI burst if used. If the hardware control enabled, CSPI will transfer data only when external SPI slave is ready | VDDIO | I/O |

The i.MX processors contains Configurable Serial Peripheral Interface (CSPI) modules that allow rapid data communication with fewer software interrupts than conventional serial communications. Each CSPI is equipped with two data FIFOs and is a master/slave configurable serial peripheral interface module, allowing processor to interface with both external SPI master and slave devices.

# 2.9 SDIO Interfaces

| Pin | Signal                           | Description                                                                     | type      | I/O |

|-----|----------------------------------|---------------------------------------------------------------------------------|-----------|-----|

|     | SD1_CD<br>SD2_CD                 | SD Card Detect – connected to a GPIO                                            | VDDIO     | I   |

| 52, | SD1_D[0]                         |                                                                                 |           |     |

| 1   | SD2_D[0]<br>SD1_D[1]             |                                                                                 |           |     |

|     | SD2_D[1]<br>SD1_D[2]             | SD Data bidirectional signals                                                   | VDDIO     | I/O |

|     | SD2_D[2]<br>SD1_D[3]<br>SD2_D[3] |                                                                                 |           |     |

| 56, | SD1_CMD<br>SD2_CMD               | SD Command bidirectional signal                                                 | VDDIO     | I/O |

| 57, | SD1_CLK<br>SD2_CLK               | SD Output Clock.                                                                | VDDIO     | О   |

|     | Module                           | Remark                                                                          |           |     |

|     | TX25, TX28, TX48                 | Only one SD-Card available on standard pinout, SD Interface 2 is not used / not | connected | t   |

|     | TX28                             | Pin 101 is used as ENET_CLK                                                     |           |     |

The TX pinout provides two dedicated SDIO interfaces. SDIO stands for Secure Digital Input Output which can also be used for SD-Memory-Cards.

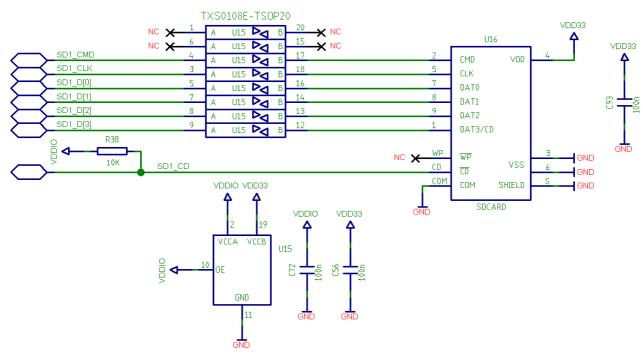

# 2.9.1 SD-Card example diagram using level shifters

No external pullups are needed here. Each port of the TXS0108E has an internal pull-up resistor. These have a value of  $40~k\Omega$  when the output is driving low and a value of  $4~k\Omega$  when the output is driving high. Unfortunately the card detect feature commonly used for Micro-SD cards on DAT3/CD cannot be used. A dedicated card detect switch is required.

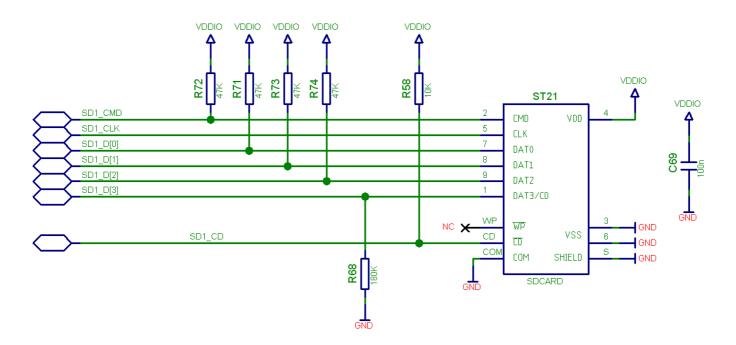

# 2.9.2 SD-Card example diagram only for 3.3V modules

Either the use of the processor internal pullups or the use of pullups on the baseboard is possible.

#### **2.10 UARTs**

| Pin | Signal    | Description                  | type  | I/O |

|-----|-----------|------------------------------|-------|-----|

| 59, | UART1_TXD |                              |       |     |

| 63, | UART2_TXD | Transmit Data output signal  | VDDIO | 0   |

| 67  | UART3_TXD |                              |       |     |

| 60, | UART1_RXD |                              |       |     |

| 64, | UART2_RXD | Receive Data input signal    | VDDIO | I   |

| 68  | UART3_RXD |                              |       |     |

| 61, | UART1_RTS |                              |       |     |

| 65, | UART2_RTS | Request to Send input signal | VDDIO | I   |

| 69  | UART3_RTS |                              |       |     |

| 62, | UART1_CTS |                              |       |     |

| 66, | UART2_CTS | Clear to Send output signal  | VDDIO | 0   |

| 70  | UART3_CTS |                              |       |     |

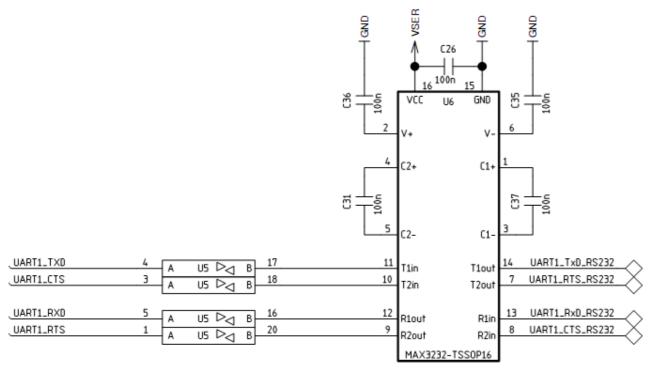

# 2.10.1 UART Example diagram

Keep attention to the unusual DCE naming converntion Freescale is using for CTS(output)/RTS(input).

MAX3232CUE SMD TSSOP16 MAX

# 2.11 Keypad Interface

| Pin | Signal        |          | Description                                                                                                                                              | type  | I/O |  |  |  |

|-----|---------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|--|--|--|

| 72  | KP_COL[0]     | Keypad ( | Column selection signals.                                                                                                                                | VDDIO |     |  |  |  |

| 73  | KP_COL[1]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

| 74  | KP_COL[2]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

| 75  | KP_COL[3]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

| 76  | KP_COL[4]     |          | \                                                                                                                                                        |       |     |  |  |  |

| 77  | KP_ROW[0]     | Keypad F | eypad Row selection signals.                                                                                                                             |       |     |  |  |  |

| 78  | KP_ROW[1]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

| 79  | KP_ROW[2]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

| 80  | KP_ROW[3]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

| 81  | KP_ROW[4]     |          |                                                                                                                                                          | VDDIO |     |  |  |  |

|     | Module        |          | Remark                                                                                                                                                   |       |     |  |  |  |

|     | TX28          |          | A PCA9554 8-bit I2C-bus I/O port is used for $KP\_COL[0-3]$ and $KP\_ROW[0-1]$ KP_COL[4], $KP\_ROW[4]$ is not part of the keypad interface, used for CAN |       |     |  |  |  |

| TX  | 25, TX48, TX5 | 3, TX6   | KP_COL[4], KP_ROW[4] can also be used for the 1 <sup>st</sup> CAN interface.                                                                             |       |     |  |  |  |

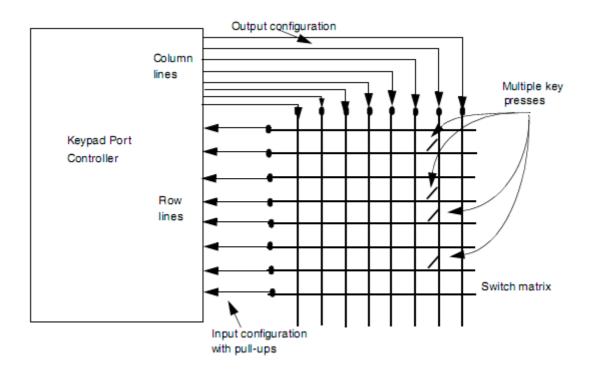

The Keypad Port (KPP) is designed to interface with the keypad matrix with 2-point contact or 3-point contact keys. The KPP is designed to simplify the software task of scanning a keypad matrix. With appropriate software support, the KPP is capable of detecting, debouncing, and decoding one or multiple keys pressed simultaneously on the keypad.

# 2.12 Digital Audio Ports

| Pin | Signal      |            | Description type I/O                                     |  |  |  |  |  |  |  |  |  |

|-----|-------------|------------|----------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|     | SSI1_INT    | Interrupt  | Int .                                                    |  |  |  |  |  |  |  |  |  |

| 89  | SSI2_INT    | interrupt  | •                                                        |  |  |  |  |  |  |  |  |  |

|     | SSI1_RXD    | Receive of | serial data                                              |  |  |  |  |  |  |  |  |  |

| 90  | SSI2_RXD    | INCCCIVC S | Schal data                                               |  |  |  |  |  |  |  |  |  |

| 85  | SSI1_TXD    | Transmit   | serial data                                              |  |  |  |  |  |  |  |  |  |

| 91  | SSI2_TXD    | Halisillic | Serial data                                              |  |  |  |  |  |  |  |  |  |

| 86  | SSI1_CLK    | Serial clo | ock                                                      |  |  |  |  |  |  |  |  |  |

| 92  | SSI2_CLK    | Serial Cic | JCK                                                      |  |  |  |  |  |  |  |  |  |

| 87  | SSI1_FS     | Frame Sy   | un c                                                     |  |  |  |  |  |  |  |  |  |

| 93  | SSI2_FS     | riallie 3  | /IIC                                                     |  |  |  |  |  |  |  |  |  |

|     | Module      |            | Remark                                                   |  |  |  |  |  |  |  |  |  |

|     | TX28S, TX48 | 3          | Only one SSI port available, SSI2 pins are not connected |  |  |  |  |  |  |  |  |  |

|     | TX28, TX28  | S          | On this module the SSI is a half-duplex serial port      |  |  |  |  |  |  |  |  |  |

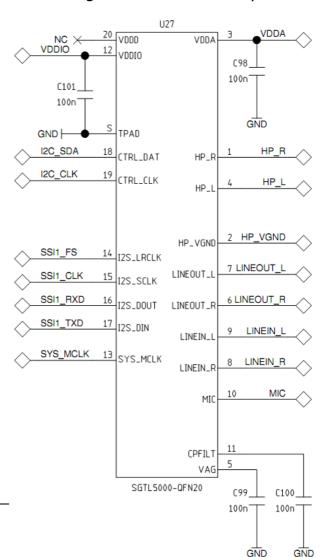

The SSI is a full-duplex, serial port that allows the chip to communicate with a variety of serial devices. These serial devices can be standard CODer-DECoder (CODECs), Digital Signal Processors (DSPs), microprocessors, peripherals, and popular industry audio CODECs that implement the inter-IC sound bus standard (I2S) standard.

SSI is typically used to transfer samples in a periodic manner. The SSI consists of independent transmitter and receiver sections with independent clock generation and frame synchronization.

Audio Codec example:

#### 2.13 CMOS Sensor Interface

| Pin     | n Signal Description                       |                                                                         |          |   |  |  |  |

|---------|--------------------------------------------|-------------------------------------------------------------------------|----------|---|--|--|--|

| 103-110 | CSI1_D                                     | Sensor port data (8 bit)                                                | VDDIO    | I |  |  |  |

| 112     | 112 CSI1_HSYNC Sensor port horizontal sync |                                                                         | VDDIO    | I |  |  |  |

| 113     | CSI1_VSYNC                                 | Sensor port vertical sync                                               | VDDIO    | I |  |  |  |

| 114     | CSI1_PIXCLK                                | Sensor port data latch clock                                            | VDDIO    | I |  |  |  |

| 115     | CSI1_MCLK                                  | Sensor port master clock                                                | VDDIO    | 0 |  |  |  |

| Module  |                                            | Remark                                                                  |          |   |  |  |  |

| TX28    |                                            | The TX28 has no camera interface. Refer to TX28 datasheet for alternate | e usage. |   |  |  |  |

The CMOS Sensor Interface (CSI) enables the chip to connect directly to external CMOS image sensors. CMOS image sensors are separated into two classes, dumb and smart. Dumb sensors are those that support only traditional sensor timing (Vertical SYNC and Horizontal SYNC) and output only Bayer and statistics data, while smart sensors support CCIR656 video decoder formats and perform additional processing of the image (for example, image compression, image pre-filtering, and various data output formats).

The standard CSI can support to connect one 8-bit sensor.

# 2.14 Extended and 2<sup>nd</sup> CMOS Sensor Interface (TX51, TX53 and TX6 only)

| Pin           | Signal                                                     | Description                                                             | type  | I/O |

|---------------|------------------------------------------------------------|-------------------------------------------------------------------------|-------|-----|

| 161-164       | CSI1_D[8-11]                                               | Sensor port data (4 bit)                                                | VDDIO | I   |

| 152-159       | CSI2_D[12-19]                                              | 2 <sup>nd</sup> Sensor port data                                        | VDDIO | I   |

| 151           | 151 CSI2_HSYNC 2 <sup>nd</sup> Sensor port horizontal sync |                                                                         | VDDIO | I   |

| 150           | CSI2_VSYNC                                                 | 2 <sup>nd</sup> Sensor port vertical sync                               | VDDIO | I   |

| 149           | CSI2_PIXCLK                                                | 2 <sup>nd</sup> Sensor port data latch clock                            | VDDIO | I   |

| 148 CSI2_MCLK |                                                            | 2 <sup>nd</sup> Sensor port master clock                                | VDDIO | 0   |

| М             | odule                                                      | Remark                                                                  |       |     |

| TX25, TX2     | 27, TX28, TX48                                             | Not available – other module specific functions are used on these pins. |       |     |

TX51 and TX53 provide a second camera interface and four additional data bits for the first camera interface. The complete interface is available on the module specific section of the TX-Standard pinout.

#### 2.15 LCD Interface

| Pin                 | Signal      | Description                                                                                                                           | type | I/O |

|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|

| 117-128,<br>130-141 | LCD_D[0-23] | LCD Data                                                                                                                              |      |     |

| 143                 | HSYNC       | Line Pulse or HSync                                                                                                                   |      |     |

| 144                 | VSYNC       | Frame Sync or VSync—This signal also serves as the clock signal output for gate; driver (dedicated signal SPS for Sharp panel HR-TFT) |      |     |

| 145                 | OE_ACD      | Alternate Crystal Direction/Output Enable                                                                                             |      |     |

| 146                 | LSCLK       | Shift Clock                                                                                                                           |      |     |

The LCD Controller of the i.MX processors provides display data for external greyscale or color LCD panels. The LCD Controller is capable of supporting black-and-white, greyscale, passive-matrix color (passive color or CSTN), and active-matrix color (active color or TFT) LCD panels.

The TX LCD Interface defines a generic 24 bit Panel Interface LCD\_D[23..0]. The TFT color channel assignments are shown in the table below:

| LCD_D                       | 23       | 22       | 21       | 20       | 19       | 18       | 17       | 16       | 15       | 14       | 13       | 12       | 11       | 10       | 9        | 8        | 7        | 6        | 5        | 4        | 3        | 2        | 1        | 0        |

|-----------------------------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|----------|

| TX28<br>TX51<br>TX53<br>TX6 | LD<br>23 | LD<br>22 | LD<br>21 | LD<br>20 | LD<br>19 | LD<br>18 | LD<br>17 | LD<br>16 | LD<br>15 | LD<br>14 | LD<br>13 | LD<br>12 | LD<br>11 | LD<br>10 | LD<br>9  | LD<br>8  | LD<br>7  | LD<br>6  | LD<br>5  | LD<br>4  | LD<br>3  | LD<br>2  | LD<br>1  | LD<br>0  |

| TX48                        | LD<br>4  | LD<br>3  | LD<br>2  | LD<br>1  | LD 0     | LD<br>16 | LD<br>18 | LD<br>21 | LD<br>10 | LD<br>9  | LD<br>8  | LD<br>7  | D 6      | LD<br>5  | LD<br>19 | LD<br>22 | LD<br>15 | LD<br>14 | LD<br>13 | LD<br>12 | LD<br>11 | LD<br>17 | LD<br>20 | LD<br>23 |

| TX25<br>TX27                | LD<br>17 | LD<br>16 | LD<br>15 | LD<br>14 | LD<br>13 | LD<br>12 | GP<br>IO | GP<br>IO | LD<br>11 | LD<br>10 | LD<br>9  | LD<br>8  | LD<br>7  | LD<br>6  | GP<br>IO | GP<br>IO | LD<br>5  | LD<br>4  | LD<br>3  | LD<br>2  | LD<br>1  | LD<br>0  | GP<br>IO | GP<br>IO |

| 24bpp                       | R7       | R6       | R5       | R4       | R3       | R2       | R1       | R0       | G7       | G6       | G5       | G4       | G3       | G2       | G1       | G0       | В7       | B6       | B5       | B4       | В3       | B2       | B1       | ВО       |

| 18bpp                       | R5       | R4       | R3       | R2       | R1       | R0       |          |          | G5       | G4       | G3       | G2       | G1       | G0       |          |          | B5       | B4       | В3       | B2       | B1       | В0       |          |          |

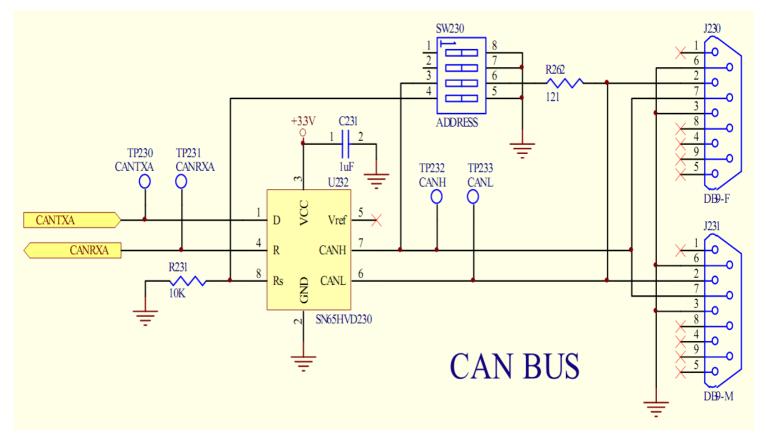

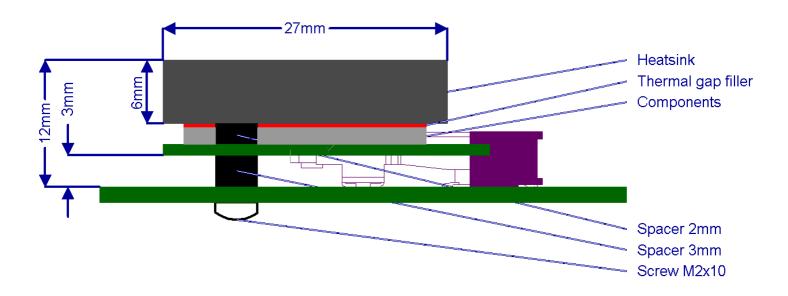

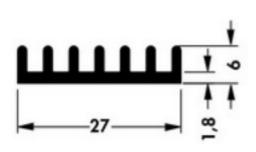

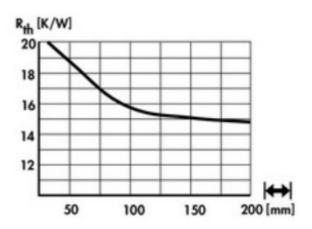

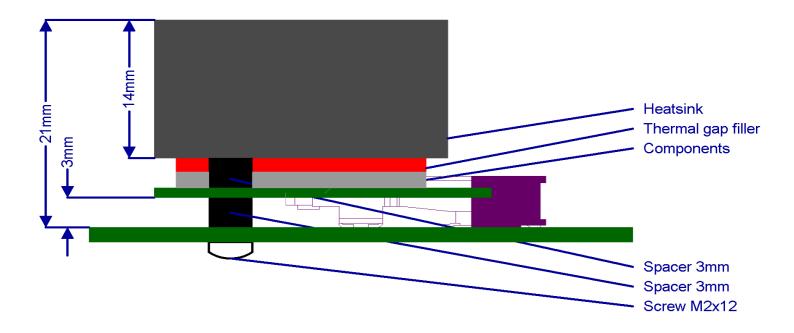

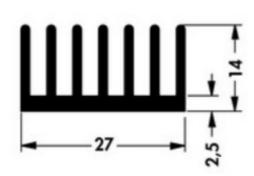

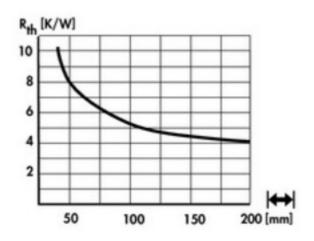

| 16bpp³                      | R4       | R3       | R2       | R1       | R0       |          |          |          | G5       | G4       | G3       | G2       | G1       | G0       |          |          | B4       | В3       | B2       | B1       | В0       |          |          |          |