LTC1426

# Micropower Dual 6-Bit PWM DAC

# FEATURES

- Wide Supply Range: 2.7V ≤ V<sub>CC</sub> ≤ 5.5V

- Wide Reference Voltage Range: 0V to 5.5V

- Two Interface Modes: Pulse Mode (Increment Only) Pushbutton Mode (Increment/Decrement)

- Low Supply Current: 50μA

- 0.2µA Supply Current in Shutdown

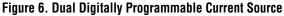

- Available in 8-Pin MSOP and SO Packages

- DAC Contents Are Retained in Shutdown

- DACs Power-Up at Midrange

- Low Output Impedance: <100Ω</p>

- Output Frequency: 5kHz Typ

# **APPLICATIONS**

- LCD Contrast and Backlight Brightness Control

- Power Supply Voltage Adjustment

- Battery Charger Voltage and Current Adjustment

- GaAs FET Bias Adjustment

- Trimmer Pot Elimination

# DESCRIPTION

The LTC<sup>®</sup>1426 is a dual micropower 6-bit PWM DAC featuring versatile PWM outputs and a flexible pushbutton compatible digital interface. The DAC outputs provide a PWM signal that swings from 0V to  $V_{REF}$ , allowing the full-scale output to be varied by adjusting the voltage at  $V_{REF}$ . The PWM output frequency is typically 5kHz, easing output filtering requirements.  $V_{CC}$  supply current is typically 50µA and drops to 0.2µA in shutdown.

The LTC1426 can be controlled using one of two interface modes: pushbutton and pulse. The LTC1426 automatically configures itself into the appropriate mode at startup by monitoring the state of the CLK pins. In pushbutton mode, the CLK pins can be directly connected to external pushbuttons to control the DAC output. In pulse mode, the CLK pins can be connected to CMOS compatible logic. The DAC outputs initially power up at half scale and the contents of the internal DAC registers are retained in shutdown.

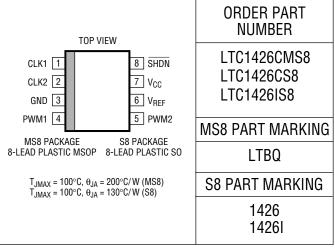

The LTC1426 is available in 8-pin MSOP and SO packages.

C, LTC and LT are registered trademarks of Linear Technology Corporation.

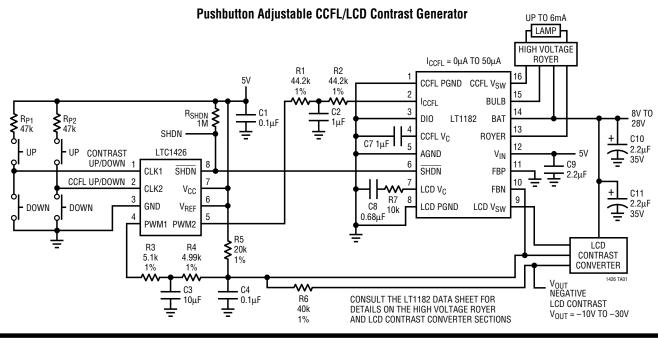

# TYPICAL APPLICATION

# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Total Supply Voltage (V <sub>CC</sub> ) 7V                   |

|--------------------------------------------------------------|

| Reference Voltage (V <sub>REF</sub> )–0.3 to 7V              |

| Input Voltage (All Inputs) – 0.3 to (V <sub>CC</sub> + 0.3V) |

| DAC Output Short-Circuit Duration Indefinite                 |

| I <sub>PWM(MAX)</sub> 100mA                                  |

| Operating Temperature Range                                  |

| LTC1426C0°C to 70°C                                          |

| LTC1426I40°C to 85°C                                         |

| Storage Temperature Range –65°C to 150°C                     |

| Lead Temperature (Soldering, 10 sec)                         |

## PACKAGE/ORDER INFORMATION

Consult factory for Military grade parts.

### **ELECTRICAL CHARACTERISTICS** $T_A = 25$ °C, (Note 2) unless otherwise specified.

| SYMBOL           | PARAMETER                                | CONDITIONS                                                                                                                                                                                      |                    |    | MIN             | ТҮР               | MAX            | UNITS      |

|------------------|------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|----|-----------------|-------------------|----------------|------------|

| V <sub>CC</sub>  | Supply Voltage                           |                                                                                                                                                                                                 |                    | •  | 2.7             |                   | 5.5            | V          |

| V <sub>REF</sub> | Reference Voltage                        |                                                                                                                                                                                                 |                    | •  | 0               |                   | 5.5            | V          |

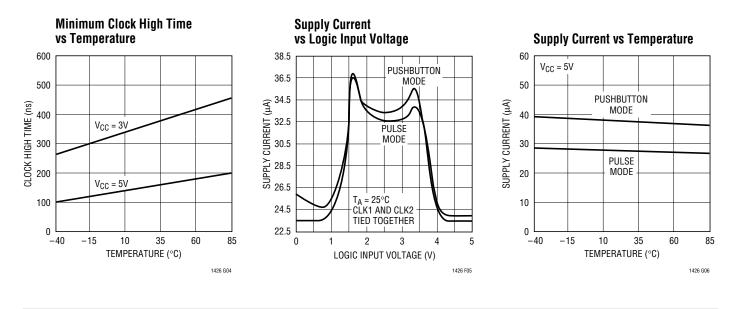

| I <sub>CC</sub>  | Supply Current                           | Pulse Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = 0V$ , PWM1 = PWM2 = NC<br>Pushbutton Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = PWM1 = PWM2 = NC$<br>SHDN = 0 (Note 3)         |                    |    | 40<br>50<br>0.2 | 100<br>100<br>±10 | μΑ<br>μΑ<br>μΑ |            |

| I <sub>REF</sub> | Reference Current                        | Pulse Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = 0V$ , PWM1 = PWM2 = NC<br><u>Pushb</u> utton Mode: $V_{SHDN} = V_{CC}$ , $V_{CLK1} = V_{CLK2} = PWM1 = PWM2 = NC$<br>SHDN = 0 (Note 3) |                    |    | 75<br>75<br>0.2 | 150<br>150<br>±10 | μΑ<br>μΑ<br>μΑ |            |

|                  | DAC Resolution                           |                                                                                                                                                                                                 |                    |    |                 | 6                 |                | bits       |

|                  | DAC Frequency                            | $\begin{array}{l} 0^{\circ}C \leq T_{A} \leq 70^{\circ}C \\ -40^{\circ}C \leq T_{A} \leq 85^{\circ}C \end{array}$                                                                               |                    | •• | 3<br>2          | 5<br>5            | 6<br>6         | kHz<br>kHz |

|                  | DAC Output Impedance                     | V <sub>CC</sub> = 2.7V, V <sub>REF</sub> = 0.5V                                                                                                                                                 |                    | •  |                 | 20                | 100            | Ω          |

|                  | DAC Full-Scale Duty Cycle                |                                                                                                                                                                                                 |                    |    |                 | 98.44             |                | %          |

|                  | DAC Zero-Scale Duty Cycle                |                                                                                                                                                                                                 |                    |    |                 | 0                 |                | %          |

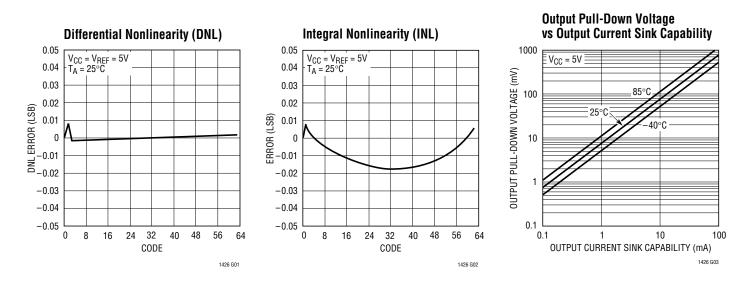

| DNL              | DAC Differential Nonlinearity            | Monotonicity Guaranteed (Note 4)                                                                                                                                                                |                    | •  |                 |                   | ±0.05          | LSB        |

| INL              | DAC Integral Nonlinearity                | (Note 4)                                                                                                                                                                                        |                    | •  |                 |                   | ±0.05          | LSB        |

| FS Error         | DAC Full-Scale Error                     |                                                                                                                                                                                                 |                    | •  |                 |                   | ±0.50          | LSB        |

| I <sub>IN</sub>  | Logic Input Current                      | Pulse Mode: $0V \le V_{IN} \le V_{CC}$                                                                                                                                                          | SHDN<br>CLK1, CLK2 | •  |                 |                   | ±5<br>±5       | μA<br>μA   |

|                  |                                          | Pushbutton Mode: $0V \le V_{IN} \le V_{CC}$                                                                                                                                                     | SHDN<br>CLK1, CLK2 | •• |                 |                   | ±5<br>±10      | μA<br>μA   |

| V <sub>IH</sub>  | CLK High Level<br>Input Voltage (Note 5) | V <sub>CC</sub> = 5.5V                                                                                                                                                                          | SHDN<br>CLK1, CLK2 | •  | 2.0<br>4.4      |                   |                | V<br>V     |

|                  |                                          | V <sub>CC</sub> = 3.6V                                                                                                                                                                          | SHDN<br>CLK1, CLK2 | •  | 1.9<br>2.9      |                   |                | V<br>V     |

# **ELECTRICAL CHARACTERISTICS** $T_A = 25^{\circ}C$ , (Note 2) unless otherwise specified.

| SYMBOL              | PARAMETER                               | CONDITIONS                                                               |                    |   | MIN        | ТҮР  | MAX          | UNITS      |

|---------------------|-----------------------------------------|--------------------------------------------------------------------------|--------------------|---|------------|------|--------------|------------|

| V <sub>IL</sub>     | CLK Low Level<br>Input Voltage (Note 5) | V <sub>CC</sub> = 4.5V                                                   | SHDN<br>CLK1, CLK2 | • |            |      | 0.8<br>0.8   | V<br>V     |

|                     |                                         | V <sub>CC</sub> = 2.7V                                                   | SHDN<br>CLK1, CLK2 | • |            |      | 0.45<br>0.45 | V<br>V     |

| l <sub>oz</sub>     | Three-State Output Leakage              | SHDN = 0                                                                 |                    | • |            |      | ±5           | μA         |

| Z <sub>IN</sub>     | CLK Input Resistance                    | Pushbutton Mode, CLK1/CLK2                                               |                    |   |            | 2.5  |              | MΩ         |

| f <sub>CLK</sub>    | Clock Frequency                         | Pulse Mode, $V_{CC} = 3.3V$<br>Pulse Mode, $V_{CC} = 2.7V$               |                    | • |            |      | 1<br>750     | MHz<br>kHz |

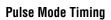

| t <sub>СКНІ</sub>   | Clock High Time                         | Pulse Mode, V <sub>CC</sub> = 3.3V<br>Pulse Mode, V <sub>CC</sub> = 2.7V |                    | • | 450<br>600 |      |              | ns<br>ns   |

| t <sub>CKLO</sub>   | Clock Low Time                          | Pulse Mode, V <sub>CC</sub> = 3.3V<br>Pulse Mode, V <sub>CC</sub> = 2.7V |                    | • | 450<br>600 |      |              | ns<br>ns   |

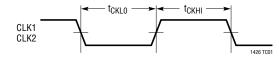

| t <sub>PW</sub>     | Pulse Width                             | Pushbutton Mode                                                          |                    | • | 670        |      |              | μs         |

| t <sub>DEB</sub>    | Debounce Time                           | Pushbutton Mode                                                          |                    | • | 10.7       | 12.8 | 21.3         | ms         |

| t <sub>DELAY</sub>  | Repeat Rate Delay                       | Pushbutton Mode                                                          |                    | • | 340        | 410  | 680          | ms         |

| f <sub>REPEAT</sub> | Repeat Frequency                        | Pushbutton Mode                                                          |                    | • | 11.7       | 19.5 | 23.4         | Hz         |

The  $\bullet$  denotes the specifications which apply over the full operating temperature range.

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of the device may be impaired.

**Note 2:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground, unless otherwise specified. All typicals are given for  $V_{CC} = V_{REF} = 5V$ ,  $T_A = 25^{\circ}C$  and PWM1/PWM2 output to GND,  $C_{PWM} = 10pF$ .

Note 3: Shutdown current can be negative due to leakage currents if  $V_{CC}$  >  $V_{REF}$  or  $V_{REF}$  >  $V_{CC}.$

**Note 4:** Guaranteed by Design. Decouple the V<sub>CC</sub> and V<sub>REF</sub> pins to GND using high quality, low ESR, low ESL  $0.1\mu$ F capacitors to eliminate PWM switching noise that may otherwise get coupled into the CLK1/CLK2 high impedance input buffers. The decoupling capacitors should be located in close proximity to these pins and the ground line to have maximum effect. **Note 5:** Input thresholds apply for both pushbutton and pulse modes.

## TYPICAL PERFORMANCE CHARACTERISTICS

# TYPICAL PERFORMANCE CHARACTERISTICS

## PIN FUNCTIONS

CLK1 (Pin 1): Channel 1 Clock/Pushbutton Input.

CLK2 (Pin 2): Channel 2 Clock/Pushbutton Input.

**GND (Pin 3):** Ground. It is recommended that GND be tied to a ground plane.

PWM1 (Pin 4): Channel 1 PWM Output.

PWM2 (Pin 5): Channel 2 PWM Output.

$V_{REF}$  (Pin 6): Voltage Reference Input.  $V_{REF}$  powers the DAC output buffers and can be used to control the output

span. Bypass  $V_{\text{REF}}$  to GND with an external capacitor to minimize output errors.  $V_{\text{REF}}$  can be tied to  $V_{\text{CC}}$  if desired.

**V<sub>CC</sub> (Pin 7):** Voltage Supply. This supply must be kept free from noise and ripple by bypassing directly to the ground plane.

**SHDN** (Pin 8): Shutdown. A logic low puts the chip into shutdown mode with the PWM outputs in high impedance. The digital settings for the DACs are retained in shutdown.

## TIMING DIAGRAMS

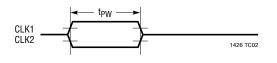

# **BLOCK DIAGRAM**

Figure 1. LTC1426 Block Diagram

# DEFINITIONS

**LSB:** The least significant bit or the ideal duty cycle difference between two successive codes.

$LSB = DC_{MAX}/64$

$DC_{MAX}$  = The DAC output maximum duty cycle

**Resolution:** The resolution is the number of DAC output states (64) that divide the full-scale output duty cycle range. The resolution does not necessarily imply linearity.

**INL:** End point integral nonlinearity is the maximum deviation from a straight line passing through the end points of the DAC transfer curve. The INL error at a given code is calculated as follows:

$$\label{eq:INL} \begin{split} \text{INL} &= (\text{DC}_{\text{OUT}} - \text{DC}_{\text{IDEAL}})/\text{LSB} \\ \text{DC}_{\text{IDEAL}} &= (\text{Code})(\text{LSB}) \\ \text{DC}_{\text{OUT}} &= \text{the DAC output duty cycle measured at the} \\ \text{given number of clocked in pulses.} \end{split}$$

# APPLICATIONS INFORMATION

#### **Dual 6-Bit PWM DAC**

Figure 1 shows a block diagram of the LTC1426. Each 6-bit PWM DAC is guaranteed monotonic and is digitally adjustable in 64 equal steps, which corresponds from 0% to 98.5% duty cycle full scale. At power-up, the counters reset to 100000B and both DAC outputs assume midscale duty cycle. The PWM outputs have an output impedance

**DNL:** Differential nonlinearity is the difference between the measured duty cycle change and the ideal 1LSB duty cycle change between any two adjacent codes. The DNL error between any two codes is calculated as follows:

$$\label{eq:DNL} \begin{split} &\text{DNL} = (\Delta DC_{OUT} - LSB)/LSB \\ &\Delta DC_{OUT} = \text{The measured duty cycle difference between} \\ &\text{two adjacent codes.} \end{split}$$

**Full-Scale Error:** Full-scale error is the difference between the ideal and measured DAC output duty cycles with all bits set to one (Code = 63). The full-scale error is calculated as follows:

$FSE = (DC_{OUT} - DC_{IDEAL})/LSB$  $DC_{IDEAL} = DC_{MAX}$

of less than 100 $\Omega$ . The DAC outputs swing from 0V to the reference voltage, V<sub>REF</sub>, which can be biased from 0V to 5.5V. The frequency of the DAC outputs is above 3kHz, easing output filtering.

In the case of a pure resistive load, the voltage measured across load RL is given by:

$V = (V_{PWM})R_L/(R_L + R_{OUT})$

# APPLICATIONS INFORMATION

where  $V_{PWM}$  is the no load DAC output voltage,  $R_L$  is the resistive load and  $R_{OUT}$  is the DAC output impedance. Therefore, the resistive load  $R_L$  should be sufficiently large to ignore the effect of output impedance on the load voltage.

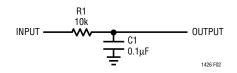

Figure 2 shows a typical lowpass filter recommended to filter the PWM outputs. Without filtering, results obtained from unfiltered outputs can be erroneous when taking measurements from a voltmeter. The ratio of the filter time constant, t, to the PWM frequency determines the amount of output ripple frequency that feeds into the system. In addition, the loading of the output also determines an additional error voltage drop across R1.

Figure 2. Lowpass Filter for PWM Averaging

#### **Digital Interface**

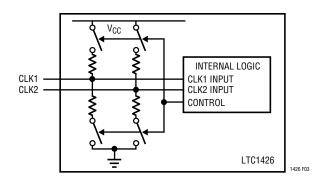

The LTC1426 can be controlled by using one of two interface modes: pulse mode and pushbutton mode. The operating interface mode is determined during power-up. If both CLK1 and CLK2 inputs are floating on power-up, then an interface mode detect circuit configures the chip in pushbutton mode until the next  $V_{CC}$  reset (Figure 3). However, if either of CLK1 or CLK2 is at logic 0 or 1 at

# TYPICAL APPLICATIONS

Typical applications for this part include digital calibration, industrial process control, automatic test equipment, cellular telephones and portable battery-powered applications. Figures 4 and 5 show how easy this part is to use. In all applications, the PWM full-scale output voltage is set by  $V_{\text{REF}}$ . This makes interfacing convenient when a variety of reference spans are needed.

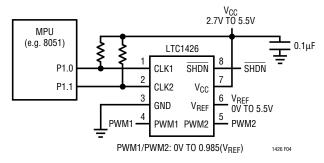

### **Pulse Mode**

Figure 4 shows the LTC1426 in a pulse mode, stand-alone application. The LTC1426 can interface directly with minimum external components to most popular micro-

power-up, then the chip configures in pulse mode until the next  $V_{\mbox{CC}}$  reset.

Figure 3 shows the simplified logic for determining the interface mode at power-up. A set of pull-up/pull-down resistors allow the LTC1426 to sense the state of the CLK pins at power-up. If both CLK1 and CLK2 pins are floating on power-up then the control signal from the LTC1426 leaves these resistors in place, allowing the LTC1426 to detect three operating states at each CLK pin: high, low and "middle" (floating). If the CLK pins are tied to either logic 0 or 1 at power-up, then the control signal will disconnect these resistors, making CLK1 and CLK2 CMOS compatible input pins.

Note that both CLK pins will always be in the same mode. If one pin is floating and the other is at logic high/low on power-up, the LTC1426 will assume pulse mode.

Figure 3. Interface Mode Detect Circuit

processors (MPUs). The Intel 8051 was chosen to demonstrate direct interface for the LTC1426, as this

### TYPICAL APPLICATIONS

microprocessor has "quasi-bidirectional" ports that eliminate additional pull-up resistors to  $V_{CC}$ . However, external pull-up resistors should be used if the microprocessor doesn't pull the port pins high during reset.

In pulse mode, each clock pulse applied to the CLK1 or CLK2 input increments the respective counter by one count. When the counter increases beyond full scale (111111B), the counter rolls over and becomes zero scale (000000B). In this way, a single pulse applied to the CLK1 or CLK2 input increases the respective counter by one count, and 63 pulses decrease that counter by one count.

#### **Pushbutton Mode**

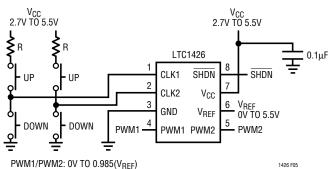

Figure 5 shows how to use the LTC1426 in a typical pushbutton application. In pushbutton mode, a logic 1 pulse applied to the CLK1 or CLK2 input increments the

LIMITING RESISTOR R PREVENTS SHORTING OF V<sub>CC</sub> and GND when both buttons are simultaneously pushed. This resistor can be placed either in the V<sub>CC</sub> or GND leg and this determines the function when both buttons are pushed. Value of R < 50k

#### Figure 5. Pushbutton Mode Interface

respective counter by one count, and stops incrementing when the counter reaches full scale (111111B). A logic 0 pulse applied to the CLK1 or CLK2 input decrements the respective counter by one count, and stops decrementing when the counter reaches zero scale (000000B). An onchip debouncing circuit has a debounce time of 12.8ms to prevent unintended counts with bouncing pushbuttons. After a time delay of 410ms, the counter will begin to increment/decrement at a repeat rate of 19.5Hz if the pushbutton remains pressed.

Care should be taken to avoid running the CLK and PWM traces close to one another. Since the CLK pins are high impedance input nodes in pushbutton mode, current spikes caused by the switching of the PWM outputs feedthrough via any stray capacitance between PWM and CLK lines if not properly routed. Use of proper grounding techniques and spacing of these lines are highly recommended for optimal performance.

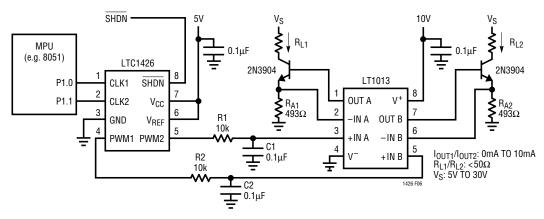

Figure 6 shows a dual digitally programmable current source using the LT®1013 dual precision op amp and two NPN transistors (2N3904). After the lowpass filter combination of R1, C1 (R2, C2), its output swings from 0V to 4.93V. In the configuration shown, this voltage will be forced across the resistor R<sub>A1</sub> (R<sub>A2</sub>). If R<sub>A1</sub> (R<sub>A2</sub>) is chosen to be 493 $\Omega$ , the output current will range from 0mA at zero scale to 10mA at full scale. The minimum voltage for V<sub>S</sub> is determined by the load resistor R<sub>L1</sub> (R<sub>L2</sub>) and Q1(Q2)'s V<sub>CESAT</sub> voltage. With a load resistor of 50 $\Omega$ , the voltage source can be as low as 5V.

# TYPICAL APPLICATIONS

#### Shutdown Mode

Upon the application of a logic low shutdown signal, the entire IC converts to micropower shutdown mode where  $V_{CC}$  supply current reduces to less than 0.3µA typical. The

shutdown function features the data retention of the current PWM1 and PWM2 codes so that upon release from a shutdown condition, these states are reinstated. This is a functional difference in comparison to the half-scale preset for both PWM1 and PWM2 outputs upon power-up.

# **RELATED PARTS**

| PART NUMBER                   | DESCRIPTION                                                                                                                                                | COMMENTS                                                       |  |  |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|

| LT1182/LT1183                 | CCFL/LCD Contrast Switching Regulators                                                                                                                     | 3V to 30V Single Supply in 16-Pin SO                           |  |  |

| LTC1257                       | Single 12-Bit V <sub>OUT</sub> DAC, Full Scale: 2.048V,<br>V <sub>CC</sub> : 4.75V to 15.75V. Reference Can Be Overdriven<br>Up to 12V, i.e., FS Max = 12V | 5V to 15V Single Supply, Complete V <sub>OUT</sub> DAC in SO-8 |  |  |

| LTC1329/LTC1329-10/LTC1329-50 | Micropower I <sub>OUT</sub> 8-Bit Current DAC                                                                                                              | 2.7V to 6.5V Single Supply in SO-8                             |  |  |

| LTC1446/LTC1446L              | Dual, Serial I/O V <sub>OUT</sub> 12-Bit DAC in SO-8                                                                                                       | Rail-to-Rail V <sub>OUT</sub> , 5V/3V Single Supply            |  |  |

| LTC1451/LTC1452/LTC1453       | Complete Serial I/O V <sub>OUT</sub> 12-Bit DACs                                                                                                           | Rail-to-Rail V <sub>OUT</sub> , 3V/5V Single Supply in S0-8    |  |  |

| LTC1590                       | Dual, Serial I/O Multiplying I <sub>OUT</sub> 12-Bit DAC                                                                                                   | 5V Single Supply in 16-pin SO Package                          |  |  |

| LTC8043                       | Serial I/O Mulitplying I <sub>OUT</sub> 12-Bit DAC                                                                                                         | 5V Single Supply in SO-8                                       |  |  |

8

1426f LT/GP 0597 7K • PRINTED IN USA

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.