# 67 MSPS Digital Receive Signal Processor

# AD6620

#### FEATURES

**High Input Sample Rate 67 MSPS Single Channel Real** 33.5 MSPS Diversity Channel Real 33.5 MSPS Single Channel Complex **NCO Frequency Translation** Worst Spur Better than -100 dBc **Tuning Resolution Better than 0.02 Hz** 2nd Order Cascaded Integrator Comb FIR Filter Linear Phase, Fixed Coefficients Programmable Decimation Rates: 2, 3...16 **5th Order Cascaded Integrator Comb FIR Filter** Linear Phase, Fixed Coefficients Programmable Decimation Rates: 1, 2, 3 ... 32 **Programmable Decimating RAM Coefficient FIR Filter** Up to 134 Million Taps per Second 256 20-Bit Programmable Coefficients Programmable Decimation Rates: 1, 2, 3...32 **Bidirectional Synchronization Circuitry Phase Aligns NCOs** Synchronizes Data Output Clocks Serial or Parallel Baseband Outputs Pin Selectable Serial or Parallel Serial Works with SHARC®, ADSP-21xx, Most Other **DSPs** 16-Bit Parallel Port, Interleaved I and Q Outputs **Two Separate Control and Configuration Ports** Generic µP Port, Serial Port 3.3 V Optimized CMOS Process **JTAG Boundary Scan**

#### **GENERAL DESCRIPTION**

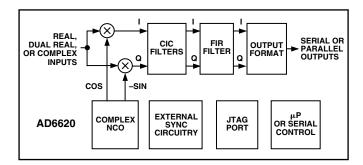

The AD6620 is a digital receiver with four cascaded signalprocessing elements: a frequency translator, two fixedcoefficient decimating filters, and a programmable coefficient decimating filter. All inputs are 3.3 V LVCMOS compatible. All outputs are LVCMOS and 5 V TTL compatible.

As ADCs achieve higher sampling rates and dynamic range, it becomes increasingly attractive to accomplish the final IF stage of a receiver in the digital domain. Digital IF Processing is less expensive, easier to manufacture, more accurate, and more flexible than a comparable highly selective analog stage.

The AD6620 diversity channel decimating receiver is designed to bridge the gap between high-speed ADCs and general purpose DSPs. The high resolution NCO allows a single carrier to be selected from a high speed data stream. High dynamic range decimation filters with a wide range of decimation rates allow

SHARC is a registered trademark of Analog Devices, Inc.

#### REV. A

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### FUNCTIONAL BLOCK DIAGRAM

both narrowband and wideband carriers to be extracted. The RAM-based architecture allows easy reconfiguration for multimode applications.

The decimating filters remove unwanted signals and noise from the channel of interest. When the channel of interest occupies less bandwidth than the input signal, this rejection of out-ofband noise is called "processing gain." By using large decimation factors, this "processing gain" can improve the SNR of the ADC by 36 dB or more. In addition, the programmable RAM Coefficient filter allows antialiasing, matched filtering, and static equalization functions to be combined in a single, costeffective filter.

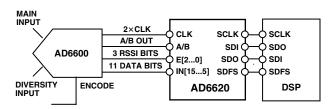

The input port accepts a 16-bit Mantissa, a 3-bit Exponent, and an A/B Select pin. These allow direct interfacing with the AD6600, AD6640, AD6644, AD9042 and most other highspeed ADCs. Three input modes are provided: Single Channel Real, Single Channel Complex, and Diversity Channel Real.

When paired with an interleaved sampler such as the AD6600, the AD6620 can process two data streams in the Diversity Channel Real input mode. Each channel is processed with coherent frequency translation and output sample clocks. In addition, external synchronization pins are provided to facilitate coherent frequency translation and output sample clocks among several AD6620s. These features can ease the design of systems with diversity antennas or antenna arrays.

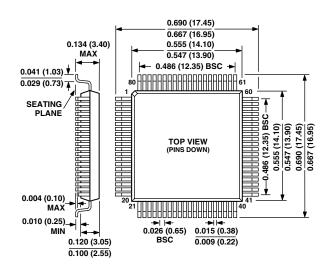

Units are packaged in an 80-lead PQFP (plastic quad flatpack) and specified to operate over the industrial temperature range  $(-40^{\circ}C \text{ to } +85^{\circ}C)$ .

#### TABLE OF CONTENTS

| GENERAL DESCRIPTION 1                           |

|-------------------------------------------------|

| ARCHITECTURE 2                                  |

| SPECIFICATIONS 4                                |

| TIMING 5                                        |

| ABSOLUTE MAXIMUM RATINGS 11                     |

| EXPLANATION OF TEST LEVELS 11                   |

| ORDERING GUIDE 11                               |

| PIN FUNCTION DESCRIPTIONS 12                    |

| PIN CONFIGURATIONS 13                           |

| INPUT DATA PORT 15                              |

| OUTPUT DATA PORT 18                             |

| FREQUENCY TRANSLATOR 19                         |

| SECOND ORDER CASCADED INTEGRATOR<br>COMB FILTER |

| FIFTH ORDER CASCADED INTEGRATOR<br>COMB FILTER  |

| RAM COEFFICIENT FILTER                          |

| CONTROL REGISTERS AND ON-CHIP RAM 27            |

| PROGRAMMING THE AD6620 30                       |

| ACCESS PROTOCOLS                                |

| MICROPORT CONTROL 32                            |

| SERIAL PORT CONTROL 35                          |

| JTAG BOUNDARY SCAN                              |

| APPLICATIONS                                    |

| OUTLINE DIMENSIONS 44                           |

#### ARCHITECTURE

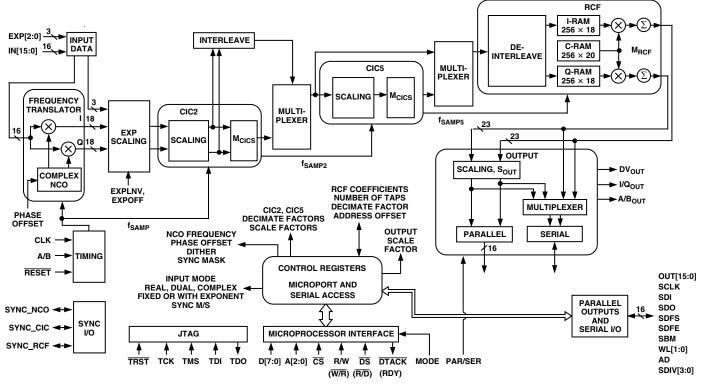

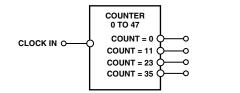

As shown in Figure 1, the AD6620 has four main signal processing stages: a Frequency Translator, two Cascaded Integrator Comb FIR Filters (CIC2, CIC5), and a RAM Coefficient FIR Filter (RCF). Multiple modes are supported for clocking data into and out of the chip. Programming and control is accomplished via serial and microprocessor interfaces.

Input data to the chip may be real or complex. If the input data is real, it may be clocked in as a single channel or interleaved with a second channel. The two-channel input mode, called Diversity Channel Real, is typically used in diversity receiver applications. Input data is clocked in 16-bit parallel words, IN[15:0]. This word may be combined with exponent input bits EXP[2:0] when the AD6620 is being driven by floating-point or gain-ranging analog-to-digital converters such as the AD6600.

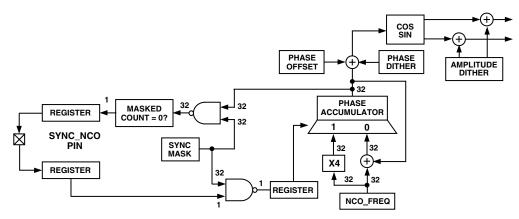

Frequency translation is accomplished with a 32-bit complex Numerically Controlled Oscillator (NCO). Real data entering this stage is separated into in-phase (I) and quadrature (Q) components. This stage translates the input signal from a digital intermediate frequency (IF) to baseband. Phase and amplitude dither may be enabled on-chip to improve spurious performance of the NCO. A phase offset word is available to create a known phase relationship between multiple AD6620s.

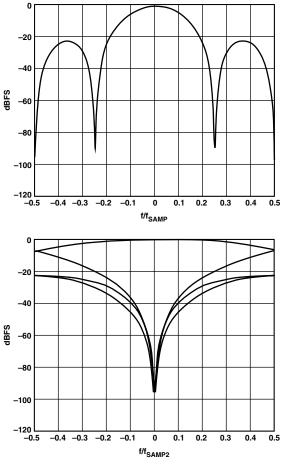

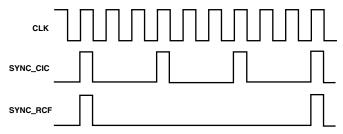

Following frequency translation is a fixed coefficient, high speed decimating filter that reduces the sample rate by a programmable ratio between 2 and 16. This is a second order, cascaded integrator comb FIR filter shown as CIC2 in Figure 1. (Note: Decimation of 1 in CIC2 requires  $2\times$  or greater clock into AD6620). The data rate into this stage equals the input data rate, f<sub>SAMP</sub>. The data rate out of CIC2, f<sub>SAMP2</sub>, is determined by the decimation factor, M<sub>CIC2</sub>.

Figure 1. Block Diagram

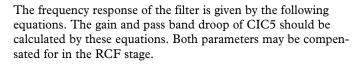

Following CIC2 is the second fixed-coefficient decimating filter. This filter, CIC5, further reduces the sample rate by a programmable ratio from 1 to 32. The data rate out of CIC5,  $f_{SAMP5}$ , is determined by the decimation factors of  $M_{CIC5}$  and  $M_{CIC2}$ .

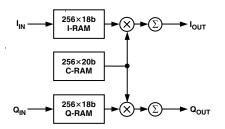

Each CIC stage is a FIR filter whose response is defined by the decimation rate. The purpose of these filters is to reduce the data rate of the incoming signal so that the final filter stage, a FIR RAM coefficient sum-of-products filter (RCF), can calculate more taps per output. As shown in Figure 1, on-chip multiplexers allow both CIC filters to be bypassed if a multirate clock is used.

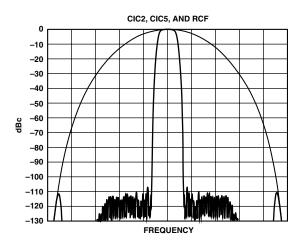

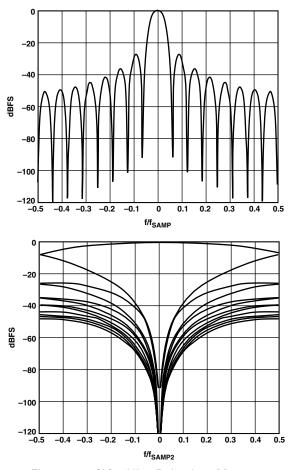

The fourth stage is a sum-of-products FIR filter with programmable 20-bit coefficients, and decimation rates programmable from 1 to 32. The RAM Coefficient FIR Filter (RCF in Figure 1) can handle a maximum of 256 taps. The overall filter response for the AD6620 is the composite of all three cascaded decimating filters: CIC2, CIC5, and RCF. Each successive filter stage is capable of narrower transition bandwidths but requires a greater number of CLK cycles to calculate the output. More decimation in the first filter stage will minimize overall power consumption. Data comes out via a parallel port or a serial interface.

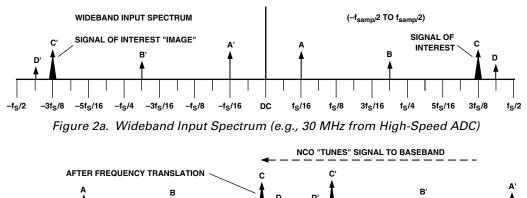

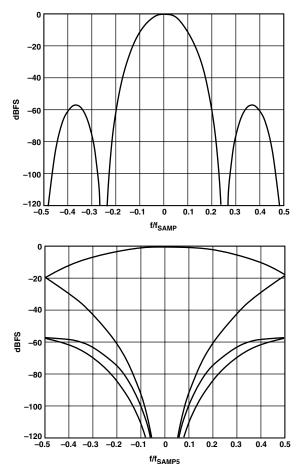

Figure 2 illustrates the basic function of the AD6620: to select and filter a single channel from a wide input spectrum. The frequency translator "tunes" the desired carrier to baseband. CIC2 and CIC5 have fixed order responses; the RCF filter provides the sharp transitions. More detail is provided in later sections of the data sheet.

Figure 2b. Frequency Translation (e.g., Single 1 MHz Channel Tuned to Baseband)

Figure 2c. Baseband Signal is Decimated and Filtered by CIC2, CIC5, RCF

## AD6620-SPECIFICATIONS **RECOMMENDED OPERATING CONDITIONS**

|                      | Test  |     | AD6620 | AS  |      |

|----------------------|-------|-----|--------|-----|------|

| Parameter            | Level | Min | Тур    | Max | Unit |

| VDD                  | Ι     | 3.0 | 3.3    | 3.6 | V    |

| T <sub>AMBIENT</sub> | IV    | -40 | +25    | +85 | °C   |

### **ELECTRICAL CHARACTERISTICS**

|                                                                |      | Test  |      | AD6620A   | 15        |      |

|----------------------------------------------------------------|------|-------|------|-----------|-----------|------|

| Parameter (Conditions)                                         | Temp | Level | Min  | Тур       | Max       | Unit |

| LOGIC INPUTS <sup>1, 2, 3, 4, 5, 6, 7</sup> (NOT 5 V TOLERANT) |      |       |      |           |           |      |

| Logic Compatibility                                            | Full |       |      | 3.3 V CMC | DS        |      |

| Logic "1" Voltage                                              | Full | I     | 2.0  |           | VDD + 0.3 | V    |

| Logic "0" Voltage                                              | Full | I     | -0.3 |           | 0.8       | V    |

| Logic "1" Current                                              | Full | I     |      | 1         | 10        | μA   |

| Logic "0" Current                                              | Full | I     |      | 1         | 10        | μA   |

| Input Capacitance                                              | 25°C | V     |      | 4         |           | pF   |

| LOGIC OUTPUTS <sup>2, 4, 7, 8, 9, 10, 11</sup>                 |      |       |      |           |           |      |

| Logic Compatibility                                            | Full |       |      | 3.3 V CMC | DS/TTL    |      |

| Logic "1" Voltage ( $I_{OH} = 0.5 \text{ mA}$ )                | Full | I     | 2.4  | VDD - 0.2 |           | V    |

| Logic "0" Voltage ( $I_{OL} = 1.0 \text{ mA}$ )                | Full | I     |      | 0.2       | 0.4       | V    |

| IDD SUPPLY CURRENT                                             |      |       |      |           |           |      |

| $CLK = 20 \text{ MHz}^{12}$                                    | Full | v     |      | 52        |           | mA   |

| $CLK = 65 \text{ MHz}^{13}$                                    | Full | I     |      | 167       | 227       | mA   |

| Reset Mode <sup>14</sup>                                       | Full | I     |      |           | 1         | mA   |

| POWER DISSIPATION                                              |      |       |      |           |           |      |

| $CLK = 20 \text{ MHz}^{12}$                                    | Full | v     |      | 170       |           | mW   |

| $CLK = 65 \text{ MHz}^{13}$                                    | Full | I     |      | 550       | 750       | mW   |

| Reset Mode <sup>14</sup>                                       | Full | I     |      |           | 3.3       | mW   |

NOTES

<sup>1</sup>Input-Only Pins: CLK, RESET, IN[15:0], EXP[2:0], A/B, PAR/SEL.

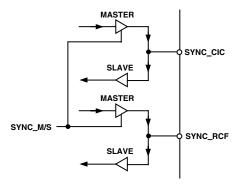

<sup>2</sup>Bidirectional Pins: SYNC\_NCO, SYNC\_CIC, SYNC\_RCF.

<sup>3</sup>Microinterface Input Pins:  $\overline{\text{DS}}$  ( $\overline{\text{RD}}$ ), R/W ( $\overline{\text{WR}}$ ),  $\overline{\text{CS}}$ .

<sup>4</sup>Microinterface Bidirectional Pins: A[2:0], D[7:0].

<sup>5</sup>JTAG Input Pins: TRST, TCK, TMS, TDI.

<sup>6</sup>Serial Mode Input Pins: SDI, SBM, WL[1:0], AD, SDIV[3:0].

<sup>7</sup>Serial Mode Bidirectional Pins: SCLK, SDFS.

<sup>8</sup>Output Pins: OUT[15:0], DV<sub>OUT</sub>, A/B<sub>OUT</sub>, I/Q<sub>OUT</sub>.

<sup>9</sup>Microinterface Output Pins: DTACK (RDY).

<sup>10</sup>JTAG Output Pins: TDO.

<sup>11</sup>Serial Mode Output Pins: SDO, SDFE.

$^{12}$ Conditions for IDD @ 20 MHz.  $M_{CIC2} = 2$ ,  $M_{CIC5} = 2$ ,  $M_{RCF} = 1$ , 4 RCF taps of alternating positive and negative full scale.

<sup>13</sup>Conditions for IDD  $\overset{\frown}{@}$  65 MHz.  $M_{CIC2}$  = 2,  $M_{CIC5}$  = 2,  $M_{RCF}$  = 1, 4 RCF taps of alternating positive and negative full scale.

<sup>14</sup>Conditions for IDD in Reset ( $\overline{\text{RESET}} = 0$ ).

Specifications subject to change without notice.

## TIMING CHARACTERISTICS (CLOAD = 40 pF All Outputs)

| Parameter (Co           | anditions)                            | Tome | Test<br>Level | Min                       | AD6620AS                                       | Max  | Uni |

|-------------------------|---------------------------------------|------|---------------|---------------------------|------------------------------------------------|------|-----|

|                         | · · · · · · · · · · · · · · · · · · · | Temp | Level         | 79111                     | Тур                                            | Max  | UII |

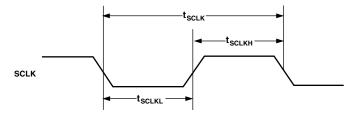

| CLK Timing Re           |                                       |      |               | 1                         |                                                |      |     |

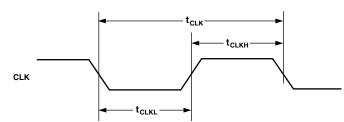

| OLI C                   | CLK Period                            | Full | I             | 14.93 <sup>1</sup>        |                                                |      | ns  |

| <b>ODI</b>              | CLK Period                            | Full | I             | 15.4                      |                                                |      | ns  |

| ona                     | CLK Width Low                         | Full | IV            | 7.0                       | $0.5 \times t_{CLK}$                           |      | ns  |

| t <sub>CLKH</sub> (     | CLK Width High                        | Full | IV            | 7.0                       | $0.5 \times t_{\text{CLK}}$                    |      | ns  |

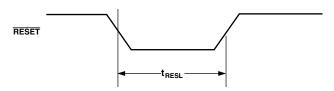

| Reset Timing R <u>e</u> |                                       |      |               |                           |                                                |      |     |

| t <sub>RESL</sub> F     | RESET Width Low                       | Full | Ι             | 30.0                      |                                                |      | ns  |

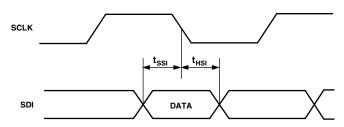

|                         | ing Requirements:                     |      |               |                           |                                                |      |     |

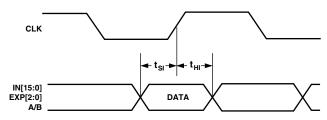

|                         | nput <sup>2</sup> to CLK Setup Time   | Full | IV            | -1.0                      |                                                |      | ns  |

| t <sub>HI</sub> I       | nput <sup>2</sup> to CLK Hold Time    | Full | IV            | 6.5                       |                                                |      | ns  |

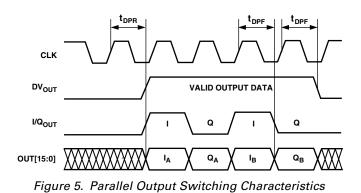

| Parallel Output         | Switching Characteristics:            |      |               |                           |                                                |      |     |

|                         | CLK to OUT[15:0] Rise Delay           | Full | IV            | 8.0                       |                                                | 19.5 | ns  |

|                         | CLK to OUT[15:0] Fall Delay           | Full | IV            | 7.5                       |                                                | 19.5 | ns  |

|                         | CLK to DV <sub>OUT</sub> Rise Delay   | Full | IV            | 6.5                       |                                                | 19.0 | ns  |

|                         | CLK to DV <sub>OUT</sub> Fall Delay   | Full | IV            | 5.5                       |                                                | 11.5 | ns  |

|                         | CLK to IQ <sub>OUT</sub> Rise Delay   | Full | IV            | 7.0                       |                                                | 19.5 | ns  |

|                         | CLK to IQ <sub>OUT</sub> Fall Delay   | Full | IV            | 6.0                       |                                                | 13.5 | ns  |

|                         | CLK to AB <sub>OUT</sub> Rise Delay   | Full | IV            | 7.0                       |                                                | 19.5 | ns  |

|                         | CLK to AB <sub>OUT</sub> Fall Delay   | Full | IV            | 5.5                       |                                                | 13.5 | ns  |

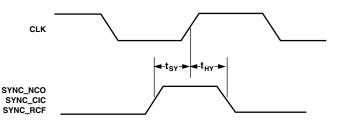

| SYNC Timing I           | Requirements                          |      |               |                           |                                                |      |     |

|                         | SYNC <sup>3</sup> to CLK Setup Time   | Full | IV            | -1.0                      |                                                |      | ns  |

|                         | SYNC3 to CLK Hold Time                | Full | IV            | 6.5                       |                                                |      | ns  |

|                         | g Characteristics:                    |      |               |                           |                                                |      |     |

|                         | CLK to SYNC <sup>4</sup> Delay Time   | Full | v             | 7.0                       |                                                | 23.5 | ns  |

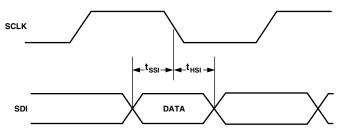

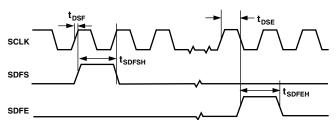

| Serial Input Tim        | ing.                                  |      |               |                           |                                                |      |     |

|                         | DI to SCLK↓ Setup Time                | Full | IV            | 1.0                       |                                                |      | ns  |

|                         | DI to SCLK Hold Time                  | Full | IV            | 2.0                       |                                                |      | ns  |

| 1101                    | SDFS to SCLK <sup>†</sup> Hold Time   | Full | IV            | 4.0                       |                                                |      | ns  |

|                         | DFS to SCLK↓ Setup Time <sup>5</sup>  | Full | IV            | 1.0                       |                                                |      | ns  |

|                         | DFS to SCLK↓ Hold Time <sup>5</sup>   | Full | IV            | 2.0                       |                                                |      | ns  |

| Serial Frame Ou         |                                       |      |               |                           |                                                |      |     |

|                         | CLK <sup>†</sup> to SDFE Delay Time   | Full | IV            | 3.5                       |                                                | 11.0 | ns  |

|                         | DFE Width High                        | Full | V             | 5.5                       | t <sub>SCLK</sub>                              | 11.0 | ns  |

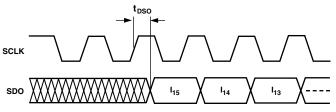

|                         | SCLK <sup>†</sup> to SDO Delay Time   | Full | IV            | 4.5                       | SCLK                                           | 11.0 | ns  |

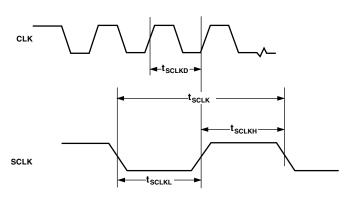

|                         | g Characteristics, SBM = "1":         |      |               |                           |                                                |      |     |

|                         | SCLK Period <sup>4</sup> $T$          | Full | I             | $2 \times t_{\text{CLK}}$ |                                                |      | ns  |

|                         | CLK Width Low                         | Full | V             | 2 A CLK                   | $0.5 \times t_{SCLK}$                          |      | ns  |

|                         | CLK Width High                        | Full | V             |                           | $0.5 \times t_{SCLK}$<br>$0.5 \times t_{SCLK}$ |      | ns  |

|                         | CLK to SCLK Delay Time                | Full | V             | 6.5                       | 0.9 ^ tSCLK                                    | 13.0 | ns  |

|                         | •                                     |      |               | 0.5                       |                                                | 10.0 | 110 |

|                         | ning, $SBM = "1"$ :                   | E11  |               | 1.0                       |                                                | 4.0  |     |

|                         | CLK <sup>†</sup> to SDFS Delay Time   | Full | IV            | 1.0                       |                                                | 4.0  | ns  |

|                         | DFS Width High                        | Full | V             |                           | t <sub>SCLK</sub>                              |      | ns  |

|                         | Requirements, $SBM = "0"$ :           |      | _             | 1.5.4                     |                                                |      |     |

|                         | CLK Period                            | Full | I             | 15.4                      | - <b>-</b>                                     |      | ns  |

| COLLER C                | CLK Width Low                         | Full | IV            | $0.4 \times t_{SCLK}$     |                                                |      | ns  |

| t <sub>SCLKH</sub> S    | CLK Width High                        | Full | IV            | $0.4 \times t_{SCLK}$     | $0.5 \times t_{SCLK}$                          |      | ns  |

NOTES

<sup>1</sup>This specification valid for VDD >= 3.3 V. t<sub>CLKL</sub> and t<sub>CLKH</sub> still apply. <sup>2</sup>Specification pertains to: IN[15:0], EXP[2:0], A/B.

<sup>3</sup>Specification pertains to: SYNC\_NCO, SYNC\_CIC, SYNC\_RCF. <sup>4</sup>SCLK period will be  $\geq 2 \times t_{CLK}$  when AD6620 is Serial Bus Master (SBM = 1) depending on the SDIV word.

<sup>5</sup>SDFS setup and hold time must be met, even when configured as outputs, since internally the signal is sampled at the pad.

Specifications subject to change without notice.

## AD6620 **TIMING CHARACTERISTICS** ( $C_{LOAD} = 40 \text{ pF All Outputs}$ )

| Parameter (Conditions)                                                                  | Tomm        | Test<br>Level | Min   | AD6620AS | Max  | Unit |

|-----------------------------------------------------------------------------------------|-------------|---------------|-------|----------|------|------|

|                                                                                         | Temp        | Level         | IVIII | Тур      | Max  | Unit |

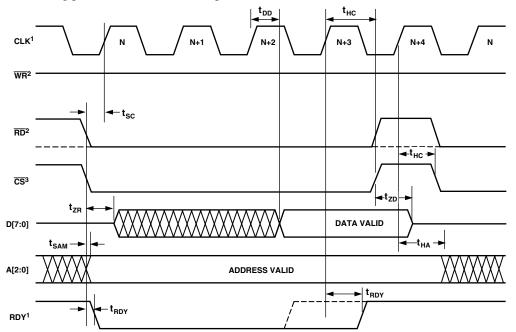

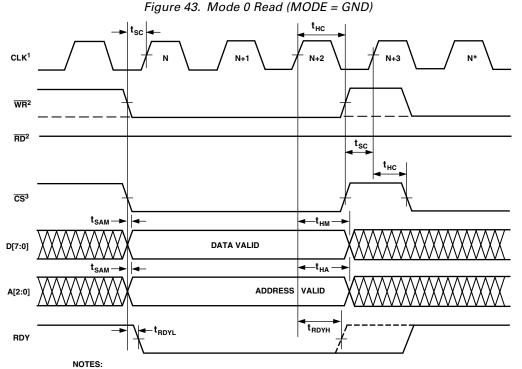

| MICROPROCESSOR PORT, MODE = 0                                                           |             |               |       |          |      |      |

| MODE0 Input Timing Requirements:                                                        |             |               |       |          |      |      |

| t <sub>SC</sub> Control <sup>1</sup> to CLK Setup Time                                  | Full        | IV            | 3.0   |          |      | ns   |

| $t_{HC}$ Control <sup>1</sup> to CLK Hold Time                                          | Full        | IV            | 5.0   |          |      | ns   |

| $t_{HA}$ Address <sup>2</sup> to CLK Hold Time                                          | Full        | IV            | 3.0   |          |      | ns   |

| $\overline{CS}$ to Data Enabled Time                                                    | Full        | IV            |       | 5.0      |      | ns   |

| $\overline{\text{CS}}$ to Data Disabled Time                                            | Full        | IV            |       | 5.0      |      | ns   |

| $\overline{CS}$ to Address/Data Setup Time                                              | Full        | IV            | 0.0   |          |      | ns   |

| MODE0 Read Switching Characteristics:                                                   |             |               |       |          |      |      |

| t <sub>DD</sub> CLK to Data Valid Time                                                  | Full        | I             | 10.0  | 15.0     | 30.0 | ns   |

| $t_{RDY}$ RD to RDY Time                                                                | Full        | IV            | 4.0   |          | 19.5 | ns   |

|                                                                                         |             |               |       |          |      |      |

| MODE0 Write Timing Requirements:                                                        | <b>F</b> 11 |               | 2.0   |          |      |      |

| $t_{SC}$ Control <sup>1</sup> to CLK Setup Time                                         | Full        | IV            | 3.0   |          |      | ns   |

| $t_{\rm HC}$ Control <sup>1</sup> to CLK Hold Time                                      | Full        | IV            | 5.0   |          |      | ns   |

| $t_{HM}$ Micro Data <sup>3</sup> to CLK Hold Time                                       | Full        | IV            | 3.0   |          |      | ns   |

| $t_{\rm HA}$ Address <sup>2</sup> to CLK Hold Time                                      | Full        | IV            | 3.0   |          |      | ns   |

| $t_{SAM}$ Address/Data Setup Time to $\overline{CS}$                                    | Full        | IV            | 0.0   |          |      | ns   |

| MODE0 Write Switching Characteristics:                                                  |             |               |       |          |      |      |

| $t_{RDY}$ RD to RDY Time                                                                | Full        | IV            | 4.0   |          | 19.5 | ns   |

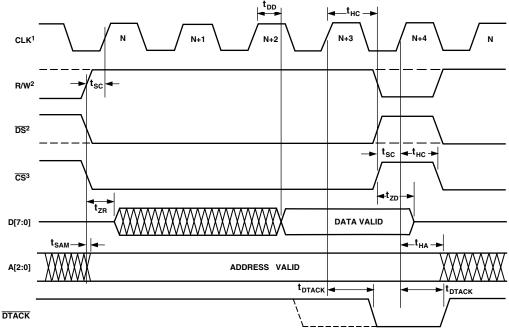

| MICROPROCESSOR PORT, MODE = 1                                                           |             |               |       |          |      |      |

| MODE1 Input Timing Requirements:                                                        |             |               |       |          |      |      |

| t <sub>SC</sub> Control <sup>1</sup> to CLK Setup Time                                  | Full        | IV            | 3.0   |          |      | ns   |

| t <sub>HC</sub> Control <sup>1</sup> to CLK Hold Time                                   | Full        | IV            | 5.0   |          |      | ns   |

| $t_{HA}$ Address <sup>2</sup> to CLK Hold Time                                          | Full        | IV            | 3.0   |          |      | ns   |

| $\overline{CS}$ to Data Enabled Time                                                    | Full        | IV            |       | 5.0      |      | ns   |

| $\overline{CS}$ to Data Disabled Time                                                   | Full        | IV            |       | 5.0      |      | ns   |

| $t_{SAM}$ Address/Data Setup Time to $\overline{CS}$                                    | Full        | IV            | 0.0   |          |      | ns   |

| MODE1 Read Switching Characteristics:                                                   |             |               |       |          |      |      |

| t <sub>DD</sub> CLK to Data Valid Time                                                  | Full        | I             | 10.0  |          | 30.0 | ns   |

| t <sub>DTACK</sub> CLK to DTACK Time                                                    | Full        | V             | 5.5   |          | 15.5 | ns   |

| MODE1 Write Timing Requirements:                                                        |             |               |       |          |      |      |

| $t_{SC}$ Control <sup>1</sup> to CLK Setup Time                                         | Full        | IV            | 0.0   |          |      | ns   |

| $t_{HC}$ Control <sup>1</sup> to CLK Hold Time                                          | Full        | IV            | 5.0   |          |      | ns   |

| $t_{HM}$ Micro Data <sup>3</sup> to CLK Hold Time                                       | Full        | IV            | 6.5   |          |      | ns   |

|                                                                                         | Full        | IV            | 3.0   |          |      | ns   |

|                                                                                         | Full        | IV            | 0.0   |          |      | ns   |

| t <sub>SAM</sub> Address/Data Setup Time to CS<br>MODE1 Write Switching Characteristic: |             | 1 1           | 0.0   |          |      | 115  |

|                                                                                         | Full        | v             | 5.5   |          | 15.5 | ns   |

| t <sub>DTACK</sub> CLK to DTACK Time                                                    | 1 un        | v             | ر.ر   |          | 19.9 | 115  |

NOTES <sup>1</sup>Specification pertains to: R/W ( $\overline{WR}$ ),  $\overline{DS}$  ( $\overline{RD}$ ),  $\overline{CS}$ . <sup>2</sup>Specification pertains to: A[2:0]. <sup>3</sup>Specification pertains to: D[7:0].

Specifications subject to change without notice.

### **TIMING DIAGRAMS**

#### **CLK, INPUTS, PARALLEL OUTPUTS**

RESET with PAR/SER = "1" establishes Parallel Outputs active.

Figure 3. CLK Timing Requirements

Figure 4. Input Data Timing Requirements

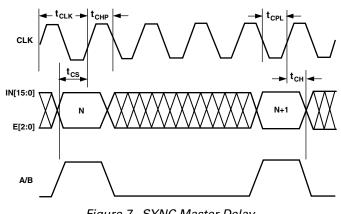

### SYNC PULSES: SLAVE OR MASTER

NOTE: IN THE SLAVE MODE WITH SINGLE CHANNEL OPERATION, THE WIDTH OF THE SYNC\_NCO SHOULD BE ONE SAMPLE CLOCK CYCLE. IN DUAL CHANNEL MODE, THE PULSEWIDTH SHOULD BE TWO SAMPLE CLOCK CYCLES. IF A PULSE LONGER THAN SPECIFIED IS USED, THE NCO WILL BE INHIBITED AND NOT INCREMENT PROPERLY.

Figure 6. SYNC Slave Timing Requirements

Figure 7. SYNC Master Delay

Figure 8. Reset Timing Requirements

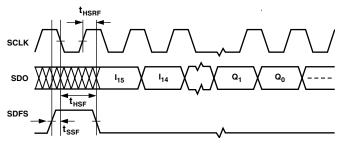

#### SERIAL PORT: BUS MASTER

RESET with PAR/SER = "0" establishes Serial Port active. SBM = "1" puts AD6620 in Serial Bus Master mode SCLK is output; SDFS is output.

Figure 9. SCLK Switching Characteristics

Figure 10. Serial Input Data Timing Requirements

Figure 11. Serial Frame Switching Characteristics

Figure 12. Serial Output Data Switching Characteristics

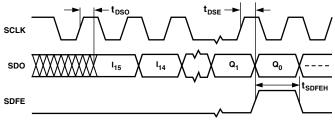

#### SERIAL PORT: CASCADE MODE

RESET with PAR/SER = "0" establishes Serial Port active. SBM = "0" puts AD6620 in Serial Port Cascade mode, SCLK is input; SDFS is input.

Figure 13. SCLK Timing Requirements

Figure 14. Serial Input Data Timing Requirements

Figure 15. SDO/SDFS Timing Requirements

Figure 16. SDO, SDFE Switching Characteristics

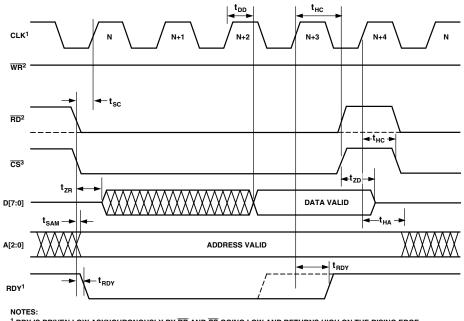

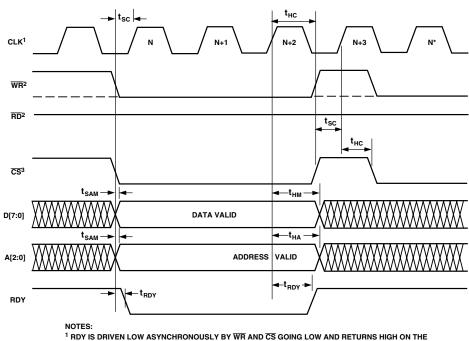

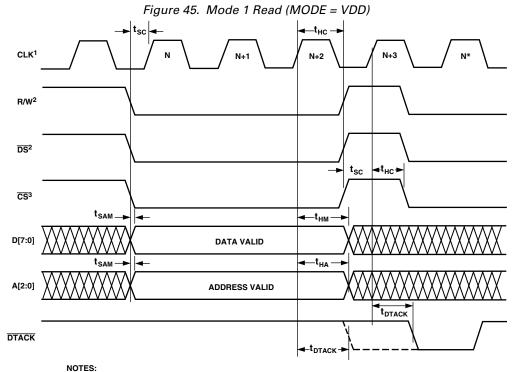

#### **MICROPORT MODE0, READ**

Timing is synchronous to CLK; MODE = 0.

<sup>1</sup> RDY IS DRIVEN LOW ASYNCHRONOUSLY BY RD AND CS GOING LOW AND RETURNS HIGH ON THE RISING EDGE OF CLK "N+3" FOR INTERNAL ACCESS (A[2:0] = 000), CLK "N+2" OTHERWISE.

<sup>2</sup> THE SIGNAL, WR, MAY REMAIN HIGH AND RD MAY REMAIN LOW TO CONTINUE READ MODE.

<sup>3</sup> CS MUST RETURN TO HIGH STATE AND BE SAMPLED BY CLK (N+4 SHOWN) TO COMPLETE READ.

#### **MICROPORT MODE0, WRITE**

Timing is synchronous to CLK; MODE = 0.

RDY IS DRIVEN LOW ASYNCHRONOUSLY BY WR AND CS GOING LOW AND RETURNS HIGH ON RISING EDGE OF CLK "N+2".

$^2$  THESE SIGNALS (R/W AND  $\overline{\text{DS}}$ ) MAY REMAIN IN LOW STATE TO CONTINUE WRITING DATA.

<sup>3</sup> CS MUST RETURN TO HIGH STATE AND BE SAMPLED BY CLK (N+3 SHOWN) TO COMPLETE WRITE.

\* THE NEXT WRITE MAY BE INITIATED ON CLK, N\*.

Figure 18. MODE0 Write Timing Requirements and Switching Characteristics

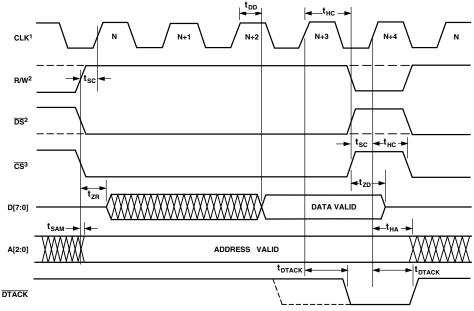

#### **MICROPORT MODE1, READ**

Timing is synchronous to CLK; MODE = 1.

NOTES:

<sup>1</sup> DTACK IS DRIVEN LOW ON THE RISING EDGE OF CLK "N+3" FOR INTERNAL ACCESS (A[2:0] = 000), CLK "N=2" OTHERWISE.

<sup>3</sup> CS MUST RETURN TO HIGH STATE AND BE SAMPLED BY CLK (N+4 SHOWN) TO COMPLETE ACCESS AND FORCE DTACK HIGH.

Figure 19. MODE1 Read Timing Requirements and Switching Characteristics

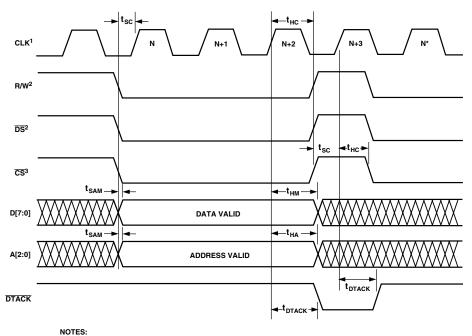

#### MICROPORT MODE1, WRITE

Timing is synchronous to CLK; MODE = 1.

<sup>1</sup> ON RISING EDGE OF "N+3" CLK, DTACK IS DRIVEN LOW.

<sup>2</sup> THESE SIGNALS (R/W AND DS) MAY REMAIN IN LOW STATE TO CONTINUE WRITING DATA.

<sup>3</sup> CS MUST RETURN TO HIGH STATE AND BE SAMPLED BY CLK (N+3 SHOWN) TO COMPLETE WRITE

AND FORCE DTACK HIGH.

\* THE NEXT WRITE MAY BE INITIATED ON CLK, N\*.

Figure 20. MODE1 Write Timing Requirements and Switching Characteristics

<sup>&</sup>lt;sup>2</sup> THE SIGNAL, R/W MAY REMAIN HIGH AND DS MAY REMAIN LOW TO CONTINUE READ MODE.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage                                       |

|------------------------------------------------------|

| Input Voltage0.3 V to VDD + 0.3 V (Not 5 V Tolerant) |

| Output Voltage Swing –0.3 V to VDD + 0.3 V           |

| Load Capacitance                                     |

| Junction Temperature Under Bias 130°C                |

| Storage Temperature Range65°C to +150°C              |

| Lead Temperature (5 sec) 280°C                       |

|                                                      |

\*Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Thermal Characteristics**

80-Lead Plastic Quad Flatpack:  $\theta_{IA} = 44^{\circ}C/W$

$\theta_{IC} = 11^{\circ}C/W$

#### **EXPLANATION OF TEST LEVELS**

- 100% Production Tested. I.

- II. 100% Production Tested at 25°C, and Sampled Tested at Specified Temperatures.

- III. Sample Tested Only.

- IV. Parameter Guaranteed by Design and Analysis.

- V. Parameter is Typical Value Only.

- VI. 100% Production Tested at 25°C, and Sampled Tested at Temperature Extremes.

#### **ORDERING GUIDE**

| Model                   | Temperature Range        | Package Description                                                                 | Package<br>Option |

|-------------------------|--------------------------|-------------------------------------------------------------------------------------|-------------------|

| AD6620AS<br>AD6620S/PCB | -40°C to +85°C (Ambient) | 80-Lead PQFP (Plastic Quad Flatpack)<br>Evaluation Board with AD6620AS and Software | S-80A             |

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD6620 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

#### PIN FUNCTION DESCRIPTIONS

| Name                                             | Туре  | Description                                                                             |

|--------------------------------------------------|-------|-----------------------------------------------------------------------------------------|

| VDD                                              | Р     | 3.3 V Supply                                                                            |

| VSS                                              | G     | Ground                                                                                  |

| CLK                                              | Ι     | Input Clock                                                                             |

| RESET                                            | Ι     | Active Low Reset Pin                                                                    |

| IN[15:0]                                         | Ι     | Input Data (Mantissa)                                                                   |

| EXP[2:0]                                         | Ι     | Input Data (Exponent)                                                                   |

| A/B                                              | Ι     | Channel (A/B) Select                                                                    |

| SYNC_NCO                                         | I/O   | Sync Signal for NCO                                                                     |

| SYNC_CIC                                         | I/O   | Sync Signal for CIC Stages                                                              |

| SYNC_RCF                                         | I/O   | Sync Signal for RCF                                                                     |

| MODE                                             | Ι     | Sets Microport Mode: Mode 1, (MODE = 1), Mode 0, (MODE = 0)                             |

| A[2:0]                                           | Ι     | Microprocessor Interface Address                                                        |

| D[7.0]                                           | I/O/T | Microprocessor Interface Data                                                           |

| $\overline{\text{DS}}$ or $\overline{\text{RD}}$ | Ι     | Mode 1: Data Strobe Line, Mode 0: Read Signal                                           |

| R/W or $\overline{WR}$                           | Ι     | Read/Write Line (Write Signal)                                                          |

| CS                                               | Ι     | Chip Select, Enables the Chip for µP Access                                             |

| $\overline{\text{DTACK}}$ or RDY                 | 0     | Acknowledgment of a Completed Transaction (Signals when µP Port Is Ready for an Access) |

| PAR/SER                                          | Ι     | Parallel/Serial Control Select (PAR = 1, SER = 0)                                       |

| DV <sub>OUT</sub>                                | 0     | Data Valid Pin for the Parallel Output Data                                             |

| A/B <sub>OUT</sub>                               | 0     | Signals to Which Channel the Output Belongs to $(A = 1, B = 0)$                         |

| I/Q <sub>OUT</sub>                               | 0     | Signals Whether I or Q Data Is Present $(I = 1, Q = 0)$                                 |

| TRST                                             | Ι     | Test Reset Pin                                                                          |

| TCK                                              | Ι     | Test Clock Input                                                                        |

| TMS                                              | Ι     | Test Mode Select Input                                                                  |

| TDI                                              | Ι     | Test Data Input                                                                         |

| TDO                                              | Ι     | Test Data Output                                                                        |

Pin Types: I = Input, O = Output, P = Power Supply, G = Ground, T = Three-state.

#### SHARED PINS

| Para     | Parallel Outputs (PAR/SER = 1 at RESET) |                            |                       | Serial Port (PAR/SER = 0 at RESET) |                                                                                   |  |

|----------|-----------------------------------------|----------------------------|-----------------------|------------------------------------|-----------------------------------------------------------------------------------|--|

| Name     | Туре                                    | Description                | Name Type Description |                                    | Description                                                                       |  |

| OUT15    | 0                                       | Parallel Output Data       | SCLK                  | I/O                                | Serial Clock Input (SBM =0)<br>Serial Clock Output (SBM = 1)                      |  |

| OUT14    | 0                                       | Parallel Output Data       | SDI                   | I                                  | Serial Data Input                                                                 |  |

| OUT13    | 0                                       | Parallel Output Data       | SDO                   | O/T                                | Serial Data Output                                                                |  |

| OUT12    | 0                                       | Parallel Output Data       | SDFS                  | I/O                                | Serial Data Frame Sync Input (SBM = 0)<br>Serial Data Frame Sync Output (SBM = 1) |  |

| OUT11    | 0                                       | Parallel Output Data       | SDFE                  | 0                                  | Serial Data Frame End                                                             |  |

| OUT10    | 0                                       | Parallel Output Data       | SBM                   | I                                  | Serial Bus Master (Master = 1, Cascade = 0)                                       |  |

| OUT9     | 0                                       | Parallel Output Data       | WL1                   | I                                  | Serial Port Word Length, Bit 1                                                    |  |

| OUT8     | 0                                       | Parallel Output Data       | WL0                   | I                                  | Serial Port Word Length, Bit 0                                                    |  |

| OUT7     | 0                                       | Parallel Output Data       | AD                    | I                                  | Append Data                                                                       |  |

| OUT[6:4] | 0                                       | Parallel Output Data       | NC                    | NC                                 | Unused, Do Not Connect                                                            |  |

| OUT3     | 0                                       | Parallel Output Data       | SDIV3                 | I                                  | SCLK Divide Value, Bit 3                                                          |  |

| OUT2     | 0                                       | Parallel Output Data       | SDIV2                 | I                                  | SCLK Divide Value, Bit 2                                                          |  |

| OUT1     | 0                                       | Parallel Output Data       | SDIV1                 | I                                  | SCLK Divide Value, Bit 1                                                          |  |

| OUT0     | 0                                       | Parallel Output Data (LSB) | SDIV0                 | Ι                                  | SCLK Divide Value, Bit 0                                                          |  |

Pin Types: I = Input, O = Output, P = Power Supply, G = Ground, T = Three-state.

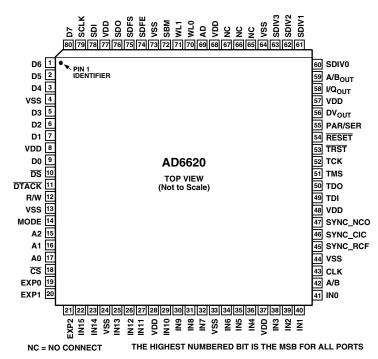

#### PIN CONFIGURATIONS

Parallel Output Data

Serial Port

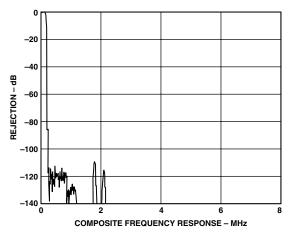

### **AD6620–Typical Performance Characteristics**

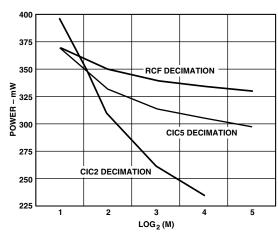

TPC 1. Typical Power vs. Decimation Rates

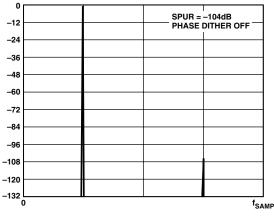

TPC 2. Typical NCO Spur Without Dither

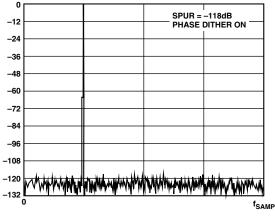

TPC 3. Typical NCO Spur with Dither

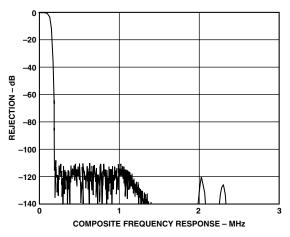

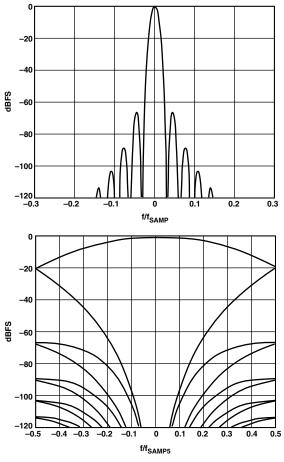

TPC 4. High Decimation GSM Filter

Input sample rate 65 MSPS, decimation is 240, FIR taps is 240. Unshown spectrum is below that shown. Decimation distribution is 3, 10, 8, respectively.

TPC 5. High Decimation AMPS Filter

Input sample rate 58.32 MSPS, decimation is 300, FIR taps is 128. Unshown spectrum is below that shown. Decimation distribution among CIC2, CIC5, and RCF is 10, 30 and 1, respectively.

#### INPUT DATA PORT

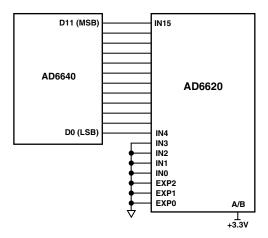

The input data port accepts a clock (CLK), a 16-bit mantissa IN[15:0], a 3-bit exponent EXP[2:0], and channel select Pin A/B. These pins allow direct interfacing to both standard fixed-point ADCs such as the AD9225 and AD6640, as well as to gain-ranging ADCs such as the AD6600. These inputs are not 5 V tolerant and the ADC I/O should be set to 3.3 V.

The input data port accepts data in one of three input modes: Single Channel Real, Diversity Channel Real, or Single Channel Complex. The input mode is selected by programming the Input Mode Control Register located at internal address space 300h.

Single Channel Real mode is used when a single channel ADC drives the input to the AD6620. Diversity Channel Real mode is the two channel mode used primarily for diversity receiver applications. Single Channel Complex mode accepts complex data in conjunction with the A/B input which identifies in-phase and quadrature samples (primarily for cascaded 6620s).

The input data port is sampled on the rising edge of CLK at a maximum rate of 67 MSPS. The 16-bit mantissa, IN[15:0] is interpreted as a *twos complement integer*. For most applications with ADCs having fewer than 16 bits, the active bits should be MSB justified and the unused LSBs should be tied low.

The 3-bit exponent, EXP[2:0] is interpreted as an unsigned integer. The exponent can be modified by the 3-bit exponent offset ExpOff (Control Register 0x305, Bits (7–5)) and an exponent invert ExpInv (Control Register 0x305, Bit 4).

ExpOff sets the offset of the input exponent, EXP[2:0]. ExpInv determines the direction of this offset. Equations below show how the exponent is handled.

scaled \_input =  $IN \times 2^{-mod(Exp+ExpOff,8)}$ , ExpInv = 0

scaled input =  $IN \times 2^{-mod(7-Exp+ExpOff, 8)}$ , ExpInv = 1

where: *IN* is the value of IN[15:0], *Exp* is the value of EXP[2:0], and *ExpOff* is the value of ExpOff.

#### **Input Scaling**

In general there are two reasons for scaling digital data. The first is to avoid "clipping" or, in the case of the AD6620 register, "wrap-around" in subsequent stages. Wrap-around is not a concern for the input data since the NCO is designed to accept the largest possible input at the AD6620 data port.

The second use of scaling is to preserve maximum dynamic range through the chip. As data flows from one stage to the next it is important to keep the math functions performed in the MSBs. This will keep the desired signal as far above the noise floor as possible, thus maximizing signal-to-noise ratio.

#### Scaling with Fixed-Point ADCs

For fixed-point ADCs, the AD6620 exponent inputs EXP[2:0] are typically not used and should be tied low. The ADC outputs are tied directly to the AD6620 Inputs, MSB-justified. The exponent offset (ExpOff) and exponent invert (ExpInv) should both be programmed to 0. Thus the input equation,

scaled\_input =

$$IN \times 2^{-mod(Exp+ExpOff, 8)}$$

,  $ExpInv = 0$

where: *IN* is the value of IN[15:0], Exp is the value of EXP[0:2], and ExpOff is the value of ExpOff, simplifies to,

scaled input =

$$IN \times 2^{-\mod(0,8)}$$

Thus for fixed-point ADCs, the exponents are typically static and no input scaling is used in the AD6620.

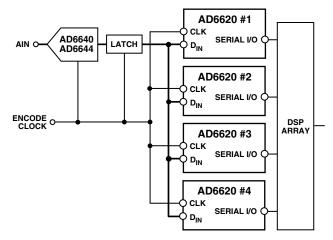

Figure 21. Typical Interconnection of the AD6640 Fixed Point ADC and the AD6620

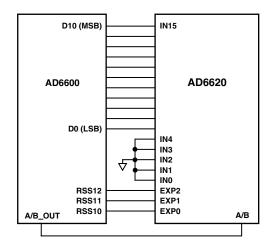

#### Scaling with Floating-Point ADCs

An example of the exponent control feature combines the AD6600 and the AD6620. The AD6600 is an 11-bit ADC with three bits of gain ranging. In effect, the 11-bit ADC provides the mantissa, and the three bits of relative signal strength indicator (RSSI) are the exponent. Only five of the eight available steps are used by the AD6600. See the AD6600 data sheet for additional details.

For gain-ranging ADCs such as the AD6600,

scaled\_input =

$$IN \times 2^{-mod(7-Exp+ExpOff,8)}$$

,  $ExpInv = 1$

where: *IN* is the value of IN[15:0], *Exp* is the value of EXP[2:0], and *ExpOff* is the value of ExpOff.

The RSSI output of the AD6600 numerically grows with increasing signal strength of the analog input (RSSI = 5 for a large signal, RSSI = 0 for a small signal). With the Exponent Offset equal to zero and the Exponent Invert Bit equal to zero, the AD6620 would consider the smallest signal at the parallel input (EXP = 0) the largest and, as the signal and EXP word increase, it shifts the data down internally (EXP = 5, will shift the 11-bit data right by 5 bits internally before going into the CIC2). The AD6620 regards the largest signal possible on the AD6600 as the smallest signal. Thus the Exponent Invert Bit is used to make the AD6620 exponent agree with the AD6600 RSSI. When it is set high, it forces the AD6620 to shift the data up for growing EXP instead of down. The exponent invert bit should always be set high for use with the AD6600.

## Table I. AD6600 Transfer Function with AD6620 ExpInv = 1,and No ExpOff

| ADC Input<br>Level | AD6600<br>RSSI[2.0] | AD6620<br>Data | Signal<br>Reduction |

|--------------------|---------------------|----------------|---------------------|

| Largest            | 101 (5)             | ÷ 4 (>> 2)     | -12 dB              |

| -                  | 100 (4)             | ÷ 8 (>> 3)     | -18 dB              |

|                    | 011 (3)             | ÷ 16 (>> 4)    | -24 dB              |

|                    | 010 (2)             | ÷ 32 (>> 5)    | -30 dB              |

|                    | 001 (1)             | ÷ 64 (>> 6)    | -36 dB              |

| Smallest           | 000 (0)             | ÷ 128 (>> 7)   | -42 dB              |

(ExpInv = 1, ExpOff = 0)

The Exponent Offset is used to shift the data right. For example, Table I shows that with no ExpOff shift, 12 dB of range is lost when the ADC input is at the largest level. This is undesired because it lowers the Dynamic Range and SNR of the system by reducing the signal of interest relative to the quantization noise floor.

To avoid this automatic attenuation of the full-scale ADC signal, the Exponent Offset is used to move the largest signal (RSSI = 5) up to the point where there is no downshift. In other words, once the Exponent Invert bit has been set, the Exponent Offset should be adjusted so that  $mod(7-5 + ExpOff_8) = 0$ . This is the case when Exponent Offset is set to 6 since mod(8, 8) = 0. Table II illustrates the use of ExpInv and ExpOff when used with the AD6600 ADC.

Table II. AD6600 Transfer Function with AD6620 ExpInv = 1, and ExpOff = 6

| ADC Input<br>Level | AD6600<br>RSSI[2.0] | AD6620<br>Data | Signal<br>Reduction |

|--------------------|---------------------|----------------|---------------------|

| Largest            | 101 (5)             | ÷ 1 (>> 0)     | -0 dB               |

|                    | 100 (4)             | ÷ 2 (>> 1)     | -6 dB               |

|                    | 011 (3)             | ÷ 4 (>> 2)     | -12 dB              |

|                    | 010 (2)             | ÷ 8 (>> 3)     | -18 dB              |

|                    | 001 (1)             | ÷ 16 (>> 4)    | -24 dB              |

| Smallest           | 000 (0)             | ÷ 32 (>> 5)    | -30 dB              |

(ExpInv = 1, ExpOff = 6)

This flexibility in handling the exponent allows the AD6620 to interface with other gain ranging ADCs besides the AD6600. The Exponent Offset can be adjusted to allow up to seven RSSI(EXP) ranges to be used as opposed to the AD6600s five. It also allows the AD6620 to be tailored in a system that employs the AD6600, but does not utilize all of its signal range. For example, if only the first four RSSI ranges are expected to occur then the Exponent Offset could be adjusted to five, which would then make RSSI = 4 correspond to the 0 dB point of the AD6620.

#### Input Timing

The CLK signal is used to sample the input port and clock the synchronous signal processing stages that follow. The CLK signal can operate up to 67 MHz and have a duty cycle of 45% to 55%. In applications using high speed ADCs, the ADC sample

clock is typically used to clock the AD6620. Applications that require a faster signal processing clock than the ADC sample clock, may employ fractional rate input timing as shown in the following sections. The input timing requirements vary according to the mode of operation. Fractional rate input timing creates a longer "don't care" time for the input data so that slower ADCs need only meet the setup-and-hold conditions for their data with respect to their own sample clock cycle, rather than the faster signal processing clock. The ADC sample clock may be any integer fraction of CLK up to and including 1, as long as the clock and data rate are less than or equal to 67 MSPS.

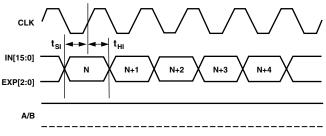

#### Single Channel Real Mode

In the Single Channel Real mode the A/B input pin functions as an active high input enable. If the A/D sample clock is fast enough to perform the necessary filter functions, full rate input timing can be used and A/B should be tied high as shown in Figure 23.

Figure 23. Full Rate Input Timing, Single Channel Real Mode

When a faster processing clock is used to achieve better filter performance, the A/D data must be synchronized with the faster AD6620 CLK signal. This is achieved by having the ADC clock rate an integer fraction of the AD6620 clock rate. AD6620 input data is sampled at the slower ADC clock rate. In the Single Channel Real Mode this is achieved by dynamically controlling the A/B input and bringing it high before each rising CLK edge that data is to be sampled on. A/B must be returned low before the next high speed clock pulse and the duty cycle of the A/B signal will therefore be equal to the data-to-clock ratio.

Figure 24. Fractional Rate Input Timing (4× CLK), Single Channel Real Mode

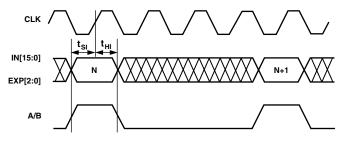

#### **Diversity Channel Real Mode**

In the Diversity Channel Real mode the A/B pin serves not only as an input enable but also to determine which channel is being sampled on a given CLK edge. A high on the A/B pin marks channel A data and a low on A/B marks channel B data. The AD6620 only accepts the first sample after an A/B transition. All subsequent samples are disregarded until A/B changes again.

When full rate input timing is employed in the Diversity Channel Real mode, A/B must toggle on every rising edge of CLK for new data to be clocked into the AD6620.

IF CLK 2x IS USED TO CLOCK THE AD6620, THE FIRST RISING EDGE AFTER THE A/B TRANSITION WILL LATCH THE DATA.

## Figure 25. Full Rate Input Timing, Diversity Channel Real Mode

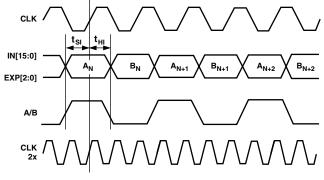

If fractional rate input timing is necessary in the Diversity Channel Real Mode, the A/B pin must toggle at half the rate of the A/D sample clock. The timing diagram below shows a  $3\times$  processing clock. In this situation there will be one ADC encode pulse for every three AD6620 CLK pulses and data must be taken on every third CLK pulse. The CLK edges that correspond to the latching of A and B channel data are shown in Figure 26.

Figure 26. Fractional Rate Input Timing (3× CLK), Diversity Channel Real Mode

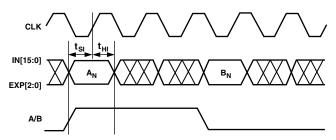

#### Single Channel Complex Mode

In the Single Channel Complex input mode, A/B high identifies the in-phase samples and A/B low identifies quadrature samples. The quadrature samples are paired with the previous in-phase samples. The timing for this mode is the same as that of the Diversity Channel Real Mode. This mode is useful for accepting complex output data from another AD6620 or another source to increase filtering and or decimation rates.

In the Single Channel Complex Mode the CIC2 decimation must be set to two ( $M_{CIC2} = 2$ ). This is necessary in order to allow enough CLK cycles to process the complex input data as described below.

First clock cycle: (A/B high).

- I data loaded from the input port.

- The I data-path gets  $I \times cosine$ .

- The Q data-path gets  $I \times sine$ .

- The first integrator of the CIC2 adds these values to its previous sums.

- The rest of the CIC2 is idle.

Second clock cycle: (A/B low).

- Q data loaded from the input port.

- The I data-path gets  $Q \times sine$ .

- The Q data-path gets  $Q \times cosine$ .

- The first integrator of the I path of the CIC2 completes the sum (I × cosine - Q × sine) and the first integrator of the Q path of the CIC2 completes the sum j(I × sine + Q × cosine).

- The rest of the CIC2 operates on these sums, which is the complete complex multiply. The data is then multiplexed through the rest of the chip as if it were single channel real data.

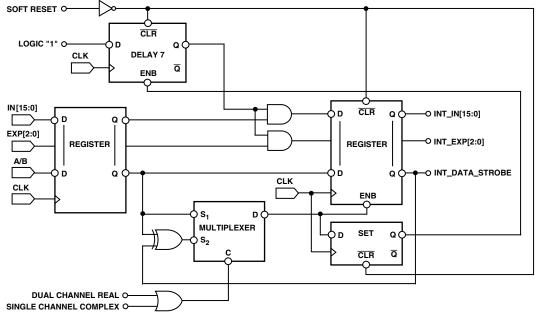

#### **Simplified Input Data Port Schematic**

Figure 27 details a simplified schematic for the input data port. The first thing to note is that IN[15:0], EXP[2:0] and A/B are all synchronously latched with CLK. Note also that upon soft reset, a seven pipeline delay (sample clock delay) exists in the data path. This delay is synchronous with CLK, but is in fact seven valid sample data delays. For instance, in single channel

Figure 27. Simplified Input Data Port Schematic for the AD6620

real mode with full rate timing the delay is seven CLKs. If instead the data rate is one-fourth CLK, then 28 CLKs (i.e., seven sample data delays, gated via A/B) occur before valid data is passed to the NCO stage.

#### Interfacing AD6620 Inputs to 5 V Logic Gates

None of the inputs to the AD6620 are tolerant of 5 V logic signals. When interfacing 5 V devices to this product, an interface gate such as the 74LCX2244 is recommended. If latching must be performed, 74LCX574 latches may be used. This gate runs from the 3.3 V supply and is tolerant of 5 V inputs.

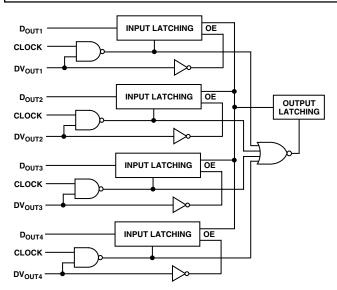

#### OUTPUT DATA PORT Parallel Output Data Port

The AD6620 provides a choice of two output ports: a 16-bit

parallel port and a synchronous serial port. Output operation using the serial port is discussed in the next section. The parallel port is limited to 16 bits. Because pins are shared between the parallel and serial output ports, only one output mode can be used. The output mode must be set with a hard reset generated by at least a 30 ns low time on the RESET pin. If the PAR/SER line is high (Logic "1"), then parallel output data is activated. The PAR/SER pin should remain static after the output mode has been set (i.e., PAR/SER should only change when RESET is low). Data out of the AD6620 is two's complement.

A scale factor is associated with the output port, which allows the signal level to be adjusted. This scale factor is mapped to location 309h, Bits 2–0 in the AD6620 internal address space. This scalar controls the weight of the 16-bit data going to the parallel port. The scale factor is discussed in the RAM Coefficient Filter (RCF) section.

The Parallel Mode provides a 16-bit output port, which constitutes the I and Q data for either one or both channels. This port can run at a maximum of 67 MHz (33.5 MHz I, 33.5 MHz Q).

This rate assumes that there is a minimum decimation of 2 in the first filter stage (CIC2) or a  $2\times$  or greater CLK is used. This decimation is required because for every input word there is both an I and a Q output. When the data rate and clock rate are the same (Full Rate Input Timing), the minimum decimation of 2 must occur in CIC2. Refer to CIC2 for more detail.

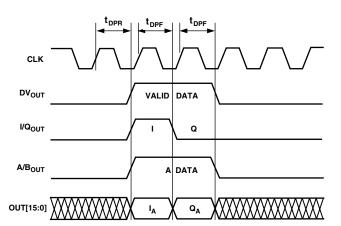

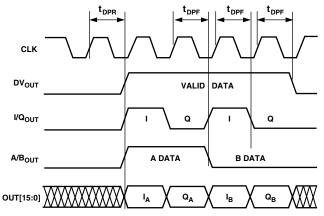

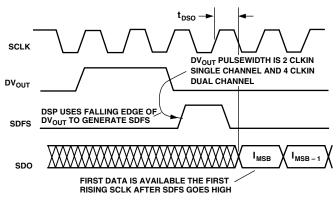

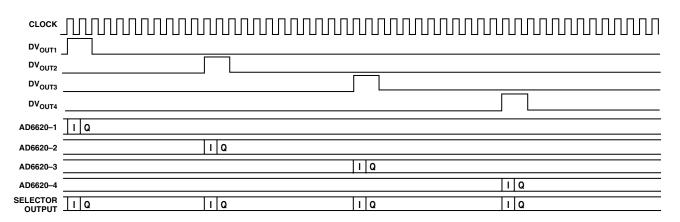

#### DVOUT

$DV_{OUT}$  is provided to signal that valid data is present. If this pin is high, there is a valid data word on the bus.  $DV_{OUT}$  remains high for two high-speed clock cycles in Single Channel Real and Single Channel Complex Mode and for four high-speed clock cycles in Diversity Channel Real mode. After  $DV_{OUT}$  returns low the Q data will remain until the next data sample.

#### I/Q<sub>OUT</sub>

When this pin is high the data word represents I data; when  $I/Q_{OUT}$  is low Q data is present. This signal will also be low when  $DV_{OUT}$  is low since the last word of every data phase is Q data.

#### A/B<sub>OUT</sub>

If  $DV_{OUT}$  is low,  $A/B_{OUT}$  is always low. When  $A/B_{OUT}$  is high, A Channel data is available on the output. If  $DV_{OUT}$  remains high while  $A/B_{OUT}$  is low, then B Channel data is on the output pins of the chip OUT[15:0].

Figure 28. Parallel Output Data Timing (Single-Channel Mode)

Figure 29. Parallel Output Data Timing (Diversity Channel Mode)

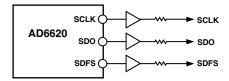

#### Serial Output Data Port

The AD6620 provides a choice of two output ports: a 16-bit parallel port and a synchronous serial port. The advantage of using the serial port is that all 23 bits of available data can be output in the 24-bit or 32-bit mode. The serial output port shares some of the same pins used by the parallel output port. As a result, one or the other mode of output may be utilized, but not both. The output mode must be set with a hard reset generated by at least a 30 ns low time on the RESET pin. If the PAR/SER line is low (Logic "0") upon reset, then serial output data is activated. The PAR/SER pin should remain static after the output mode has been set (i.e., PAR/SER should only change when RESET is low).

Note that the AD6620 cannot be booted through the serial port. The microport must be used to initialize the device, then serial operation is supported.

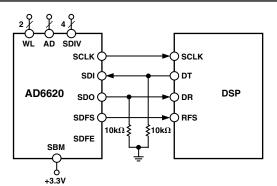

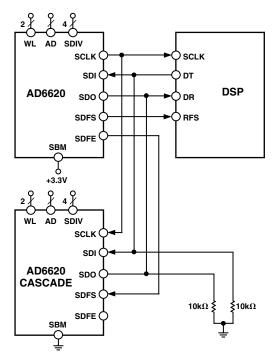

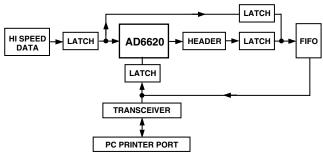

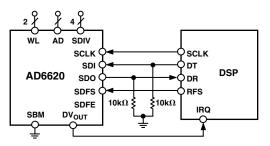

Figure 30 shows the typical interconnections between an AD6620 in serial master mode and a DSP. Refer to the Serial Control Port section for a detailed description of pin functions and procedures for writing and reading with relation to the serial port. Note the 10 k $\Omega$  resistors connected to SDI and SDO. These prevent the lines from toggling when the AD6620 or DSP three-states these pins.

Figure 30. Typical Serial Data Output Interface to DSP (Serial Master Mode, SBM = 1)

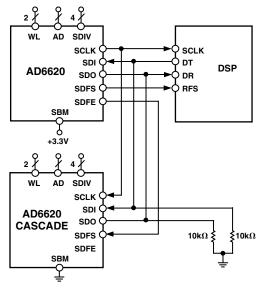

Figure 31 shows two AD6620s illustrating the cascade capability for the chip. The first is connected as a serial master and the second is configured in serial cascade mode. The SDFE signal of the master is connected to the SDFS of the slave. This allows the master AD6620 data to be obtained first by the DSP, followed by the cascaded AD6620 data.

Figure 31. Typical Serial Data Output Interface to DSP (Serial Cascade Mode, SBM = 0)

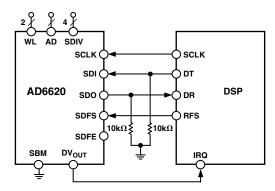

The AD6620 also supports a serial slave mode, where the serial clock and interface is provided by a DSP or ASIC that is set to operate in the master mode. Note that the AD6620 cannot be booted through the serial port. The microport must be used to initialize the device, then serial operation is supported.

In the serial slave mode,  $DV_{OUT}$  is valid and indicates the presence of a new word in the output buffers of the shift register. This pin may thus be used by the DSP to generate an interrupt to service the serial port. The DSP then generates an SFDS pulse to drive the AD6620. The first serial clock rising edge after SDFS makes the first bit available at SDO. The falling edge of serial clock can be used to sample the data. The total number of bits are then read from the AD6620 (determined by the serial port word length). If the DSP has the ability to count bits, the DSP will know when the complete frame is read. If not, the DSP can monitor the SDFE pin to determine that the complete frame is read. The serial clock provided by the DSP can be asynchronous with the AD6620 clock and input data.

Figure 32. Typical Serial Data Output Interface to DSP (Serial Slave Mode, SBM = 0)

In either the serial master or slave mode, there are two constraints that must be observed. The first is that the clock must be fast enough to read the serial frame prior to the next frame becoming available. Since the AD6620 output is synchronous with its input sample rate, the output update rate can be determined by the user-programmed decimation rate. The timing diagram in Figure 33 details how serial slave mode is implemented. The second constraint is that the time between serial frames may be either zero SCLK periods (the end of one frame adjoins the beginning of the next) or two or more SCLK periods. One SCLK period between frames is not allowed.

Figure 33. Timing for Serial Slave Mode (SBM = 0)

#### FREQUENCY TRANSLATOR

The first signal processing stage is a frequency translator consisting of two multipliers and a 32-bit complex numerically controlled oscillator (NCO). The NCO serves as a quadrature local oscillator capable of producing any analytic frequency between  $-f_{SAMP}/2$  and  $+f_{SAMP}/2$  with a resolution of  $f_{SAMP}/2^{32}$ . In the Single Channel Real input mode,  $f_{SAMP}$  is equal to  $f_{CLK}$  multiplied by the fraction of CLK cycles that A/B is high. In the Diversity Channel Real and Single Channel Complex input

modes,  $f_{SAMP}$  is equal to  $f_{CLK}$  multiplied by the fraction of CLK cycles on which A/B has been toggled. The NCO worst case discrete spur is better than -100 dBc for all output frequencies.

The control word, NCO\_FREQ is interpreted as a 32-bit unsigned integer. To translate a channel centered at  $f_{CH}$  to dc, calculate NCO\_FREQ using the equation below. The mod function is used here to allow for Super Nyquist sampling where the IF carrier (fCH) is larger than the sample rate (fSAMP). The mod removes the integer portion of the number and forces it into the 32-bit NCO Frequency Register. If the fraction remaining is larger than 0.5, the NCO will be tuning above the Nyquist rate. The corresponding signal is then aliased back into the first Nyquist Zone as a negative frequency.

$$NCO\_FREQ = 2^{32} \times mod\left(\frac{f_{CH}}{f_{SAMP}}, 1\right)$$

In both Single and Diversity Channel Real Input modes, the output of the translation stage is the complex product of the real input samples and the complex samples from the NCO. It is necessary for the subsequent decimating filters to reject the unwanted image of the channel of interest, as well as any unwanted neighboring signals (and their images) not rejected by previous analog filters.

In the Diversity Channel Real Input mode, the same NCO output words are used for both channel A and B streams, resulting in identical phase shifts. In Single Channel Complex mode both I and Q inputs are multiplied by the quadrature outputs of the NCO. The I and Q products of the multiply are then processed in the AD6620 filter stages.

In single channel real or dual channel real operation, the frequency translation and filtering processes provide a gain of -6 dB. This can be visualized since the input data is usually a real sampled signal consisting of both positive and negative frequency components (Figure 2a). After being mixed with the complex NCO, the normal filtering of the AD6620 will remove one component or the other resulting in an analytic signal (Figure 2b). This filtering thus removes one-half or 6 dB of the signal keeping consistent with the mathematics involved. If however, the filtering of the device allows both the positive and negative frequency components to pass (i.e., the original signal is near dc), the gain of the frequency translation is 0 dB. Finally, if the NCO is bypassed, the gain of the frequency translation block is -12 dB.

#### **Phase Dither**

The AD6620 provides a phase dither option for improving the spurious performance of the NCO. This is controlled via the NCO Control Register at address 301 hex. When phase dither is enabled by setting Bit 1 of this register high, spurs due to phase truncation in the NCO are randomized. The energy from these spurs is spread into the noise floor and Spurious Free Dynamic Range is increased at the expense of very slight decreases in the SNR. Phase dither should be experimented with for each desired NCO frequency and if it is seen to reduce spurs, it should be considered. The choice of whether Phase Dither is used in a system will ultimately be decided by the system goals. If lower spurs are desired at the expense of a slightly raised noise floor, it should be employed. If a low noise floor is desired and the higher spurs can be tolerated or filtered by subsequent stages, then Phase Dither is not needed.

#### **Amplitude Dither**

The second dither option is Amplitude Dither or "Complex Dither." Amplitude Dither is enabled by setting Bit 2 of the NCO Control Register at address 0x301 high. Amplitude Dither improves performance by randomizing the amplitude quantization errors within the angular to Cartesian conversion of the NCO. This dither will be particularly useful when the NCO frequency is close to an integer submultiple of the Input Data Rate. However, this option may reduce spurs at the expense of a slightly raised noise floor. Amplitude Dither and Phase Dither can be used together, separately or not at all.

#### Phase Offset

The phase offset register adds an offset to the phase accumulator of the NCO. This is a 16-bit register and is interpreted as a 16-bit unsigned integer. A 0 in this register corresponds to a 0 Radian offset and an FFFF hex corresponds to an offset of  $2\pi$  (1 – 1/(2^16)) Radians. This register can be used to allow multiple AD6620s whose NCOs are synchronized to produce sine waves with a known and steady phase difference.

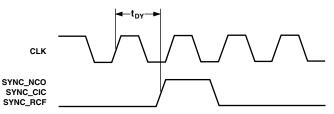

#### **NCO Synchronization**

In order to achieve phase coherence between several AD6620s, a SYNC\_NCO pin is provided. When the internal register bit, SYNC\_M/S (Bit 3 of internal register 0x300), is set high, SYNC\_NCO provides a synchronization pulse on the rising edge of CLK. When the SYNC\_M/S bit is low, SYNC\_NCO accepts an external synchronization signal sampled on the rising edge of CLK. When the AD6620 is a slave, the SYNC\_NCO signal need not be a short pulse. It may be taken high and held for more than a CLK cycle in which case the NCO will be held inactive until this pin is again lowered. If the device is run as a sync slave in Single Channel Mode, the SYNC\_NCO pin must be held low for one sample period, usually one clock cycle. If the device is run in Diversity Channel Real mode, the SYNC\_NCO must be high for two sample periods (clock cycles). In a system with an array of AD6620s it is not necessary to use one as a master. It may be desirable to generate a synchronization signal elsewhere in the system and use that to control the AD6620. An example of this may be in systems that receive packets of data. In this case, the NCO may be resynchronized prior to the beginning of the packet, thus giving a consistent phase relationship on each burst. This allows for ease of use in a large system where many AD6620s need be synchronized accurately across a large backplane or installation.

NOTE: IN THE SLAVE MODE WITH SINGLE CHANNEL OPERATION, THE WIDTH OF THE SYNC\_NCO SHOULD BE ONE SAMPLE CLOCK CYCLE. IN DUAL CHANNEL MODE, THE PULSEWIDTH SHOULD BE TWO SAMPLE CLOCK CYCLES. IF A PULSE LONGER THAN SPECIFIED IS USED, THE NCO WILL BE INHIBITED AND NOT INCREMENT PROPERLY.

Figure 34. SYNC\_NCO Pin

Figure 35. NCO Block Diagram

The frequency of the SYNC\_NCO pulses, and therefore the accuracy of the synchronization, is determined by the value of the NCO Sync Control Register at address 302 hex. The value in this register is the SYNC\_MASK and is interpreted as a 32-bit unsigned integer. This value controls the window around the zero crossing of the NCO output sine wave in which the NCO will output a SYNC\_NCO pulse as a master. As a slave, the value in this register will determine the number of MSBs of the output sine wave that are synchronized with the master. The Master and all slaves should use the same SYNC\_MASK word. This value should almost always be written as all 1s (FFFFFFF hex).

#### Effects of A/B Input on the NCO

If the AD6620 is run in Single Channel Real mode using fractional rate input timing, the A/B input is used to enable the NCO advancement. If the A/B line is held high longer than one clock period, the NCO will advance for each rising edge of the CLK while A/B is high. This is not normally the desired result and thus A/B must be taken low after the first CLK period to prevent anomalous NCO results. See additional details under Fractional Rate Timing.

#### Phase Continuous Tuning with the AD6620

For synchronization purposes, the AD6620 NCO phase is reset each time the NCO frequency register is either written to or read from. This is accomplished by forcing an NCO Sync to occur. Normally, phase-continuous tuning is required on the transmit path to control spectral leakage. On the receive path this in not usually a constraint. However, if phase-continuous tuning is required with the AD6620, it can be accomplished by configuring the AD6620 as a Sync Slave. In this manner, no internal NCO sync is generated when the NCO frequency register is written to. If multiple AD6620s are synchronized together, a common external sync pulse can be used to lock each of the receivers together at the appropriate point in time. It is also possible to reconfigure the AD6620 after the NCO frequency register has been written so that the chip is once again a Sync Master. The next time the NCO phase cycles through 0 degrees, the NCO sync is exerted and the chip is again synchronized.

**2ND ORDER CASCADED INTEGRATOR COMB FILTER** The CIC2 filter is a fixed-coefficient, decimating filter. It is constructed as a second order CIC filter whose characteristics

constructed as a second order CIC filter whose characteristics are defined only by the decimation rate chosen. This filter can process signals at the full rate of the input port (67 MHz) in all input modes. The output rate of this stage is given by the equation below.

$$f_{SAMP2} = \frac{f_{SAMP}}{M_{CIC2}}$$

The decimation ratio, MCIC2, is an unsigned integer that may be between 1 and 16. This stage may be bypassed under certain conditions by setting,  $M_{CIC2}$  equal to 1. For this to happen the processing clock rate,  $f_{CLK}$  must be two or more times the input data rate,  $f_{SAMP}$ . This is because the I and Q data is processed in parallel within the CIC2 filter, and the I and Q output data is then multiplexed through the same data pipe before it enters the CIC5 filter.

The frequency response of the CIC2 filter is given by the following equations.

$$H(z) = \frac{1}{2^{S_{CIC2}}} \times \left(\frac{1 - z^{-M_{CIC2}}}{1 - z^{-1}}\right)^2$$

$$H(f) = \frac{1}{2^{S_{CIC2}}} \times \left(\frac{\sin\left(\pi \frac{M_{CIC2} \times f}{f_{SAMP}}\right)}{\sin\left(\pi \frac{f}{f_{SAMP}}\right)}\right)^2$$

The scale factor,  $S_{CIC2}$  is a programmable unsigned integer between 0 and 6. This serves as an attenuator that can reduce the gain of the CIC2 in 6 dB increments. For the best dynamic range,  $S_{CIC2}$  should be set to the smallest value possible (i.e., lowest attenuation) without creating an overflow condition. This can be safely accomplished using the equation below, where *input\_level* is the largest fraction of full scale possible at the input to this AD6620 (normally 1). The CIC2 scale factor is not ignored when the CIC2 is bypassed.

$$S_{CIC2} = ceil \left( \log_2(M_{CIC2}^2 \times input\_level) \right)$$

$$OL_{CIC2} = \frac{1}{2^{S_{CIC2}}} \times input\_level$$

The equations for calculating CIC2 output level is correct when stage is not bypassed (normal operation). However, when bypassed, the following equations should be used instead.

#### $OL_{CIC2} = Input Level$

The gain and pass band droop of the CIC2 should be calculated by the equations above, as well as the filter transfer equations that follow. If these are unacceptable, they can be compensated for in subsequent stages.

#### **CIC2** Rejection

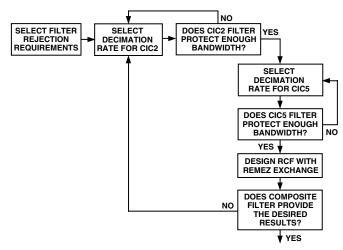

The table below illustrates the amount of bandwidth in percent of the data rate into the CIC2 stage. The data in this table may be scaled to any allowable sample rate up to 67 MHz in Single Channel Mode or 33.5 MHz in Diversity Channel Mode. The table can be used as a tool to decide how to distribute the decimation between CIC2, CIC5 and the RCF.

The data in this table may be scaled to any allowable sample rate up to 67 MHz in Single Channel Mode or 33.5 MHz in Diversity Channel Mode.

Table III. SSB CIC2 Alias Rejection Table ( $f_{SAMP}$  = 1) Bandwidth Shown in Percentage of  $f_{SAMP}$

| M <sub>CIC2</sub> | -50 dB | -60 dB | -70 dB | -80 dB | -90 dB | -100 dB |

|-------------------|--------|--------|--------|--------|--------|---------|

| 2                 | 1.79   | 1.007  | 0.566  | 0.318  | 0.179  | 0.101   |

| 3                 | 1.508  | 0.858  | 0.486  | 0.274  | 0.155  | 0.087   |

| 4                 | 1.217  | 0.696  | 0.395  | 0.223  | 0.126  | 0.071   |

| 5                 | 1.006  | 0.577  | 0.328  | 0.186  | 0.105  | 0.059   |

| 6                 | 0.853  | 0.49   | 0.279  | 0.158  | 0.089  | 0.05    |

| 7                 | 0.739  | 0.425  | 0.242  | 0.137  | 0.077  | 0.044   |

| 8                 | 0.651  | 0.374  | 0.213  | 0.121  | 0.068  | 0.038   |

| 9                 | 0.581  | 0.334  | 0.19   | 0.108  | 0.061  | 0.034   |