# Freescale Semiconductor, Inc.

10/97

# MPC8XXFADS Design Specification—Rev 0.1

PRELIMINARY

For More Information On This Product, Go to: www.freescale.com

# Freescale Semiconductor, Inc.

#### How to Reach Us:

Home Page: www.freescale.com

E-mail: support@freescale.com

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor Technical Information Center, CH370 1300 N. Alma School Road Chandler, Arizona 85224 +1-800-521-6274 or +1-480-768-2130 support@freescale.com

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) support@freescale.com

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor Hong Kong Ltd. Technical Information Center 2 Dai King Street Tai Po Industrial Estate Tai Po, N.T., Hong Kong +800 2666 8080 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800-441-2447 or 303-675-2140 Fax: 303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.com RoHS-compliant and/or Pb- free versions of Freescale products have the functionality and electrical characteristics of their non-RoHS-compliant and/or non-Pb- free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale.s Environmental Products program, go to http://www.freescale.com/epp.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document. Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters which may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

# 1 - General Information

# 1•1 Introduction

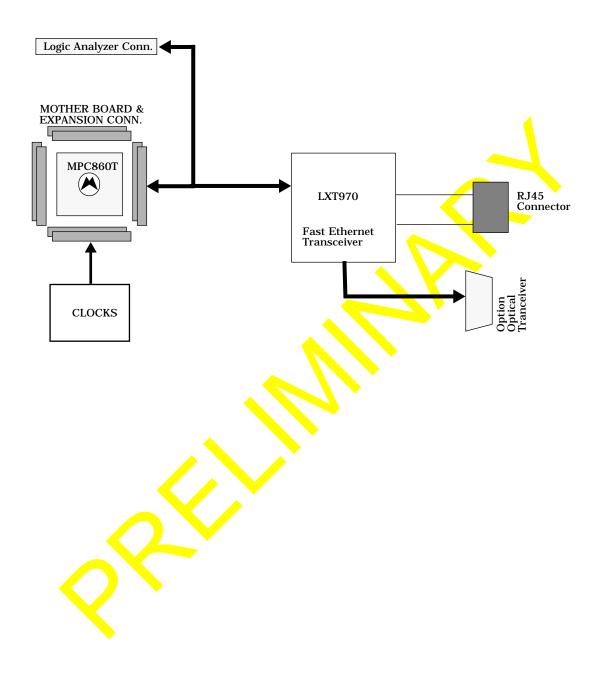

This document is an operation guide for the MPC8XXFADS board. It contains operational, functional and general information about the FADS. The MPC8XXFADS is meant to serve as a platform for s/ w and h/w development around the MPC8XX family processors. Using its on-board resources and its associated debugger, a developer is able to download his code, run it, set breakpoints, display memory and registers and connect his own proprietary h/w via the expansion connectors, to be incorporated to a desired system with the MPC8XX processor.

This board could also be used as a demonstration tool, i.e., application s/w may be burned<sup>A</sup> into its flash memory and ran in exhibitions etc'.

# 1•2 MPC8XX Family Support

The MPC8XXFADS supports the following MPC8XX family members:

- □ MPC801

- □ MPC821

- □ MPC823

- □ MPC850

- □ MPC860

- □ MPC860SAR

- □ MPC860T

# 1•3 Abbreviations' List

- FADS<sup>B</sup> the MPC8XXFADS, the subject of this document.

- UPM User Programmable Machine

- GPCM General Purpose Chip-select Machine

- GPL General Purpose Line (associated with the UPM)

- I/R Infra-Red

- BCSR Board Control & Status Register.

- ZIF Zero Input Force

- BGA Ball Grid Array

- SIMM Single In-line Memory Module

# **1•4** Related Documentation

- MPC8XX User's Manuals.

- ADI Board Specification.

MPC8XXFADS Design Specification—Rev 0.1 For More Information On This Product PRELIMINARY GUBBEEW WIFE Sciences and WIFE Structure NOTICE

A. Either on or off-board.

B. Not to be mistaken for the M683XX Family Ads

# **1•5** SPECIFICATIONS

The MPC8XXFADS specifications are given in TABLE 1-1.

# TABLE 1-1. MPC8XXFADS Specifications

| CHARACTERISTICS                               | SPECIFICATIONS                                                                                                                |

|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Power requirements (no other boards attached) | +5Vdc @ 1.7 A (typical), 3 A (maximum)<br>+12Vdc - @1A.                                                                       |

| Microprocessor                                | MPC8XX running upto @ 50 MHz                                                                                                  |

| Addressing<br>Total address range:            | 4 GigaBytes                                                                                                                   |

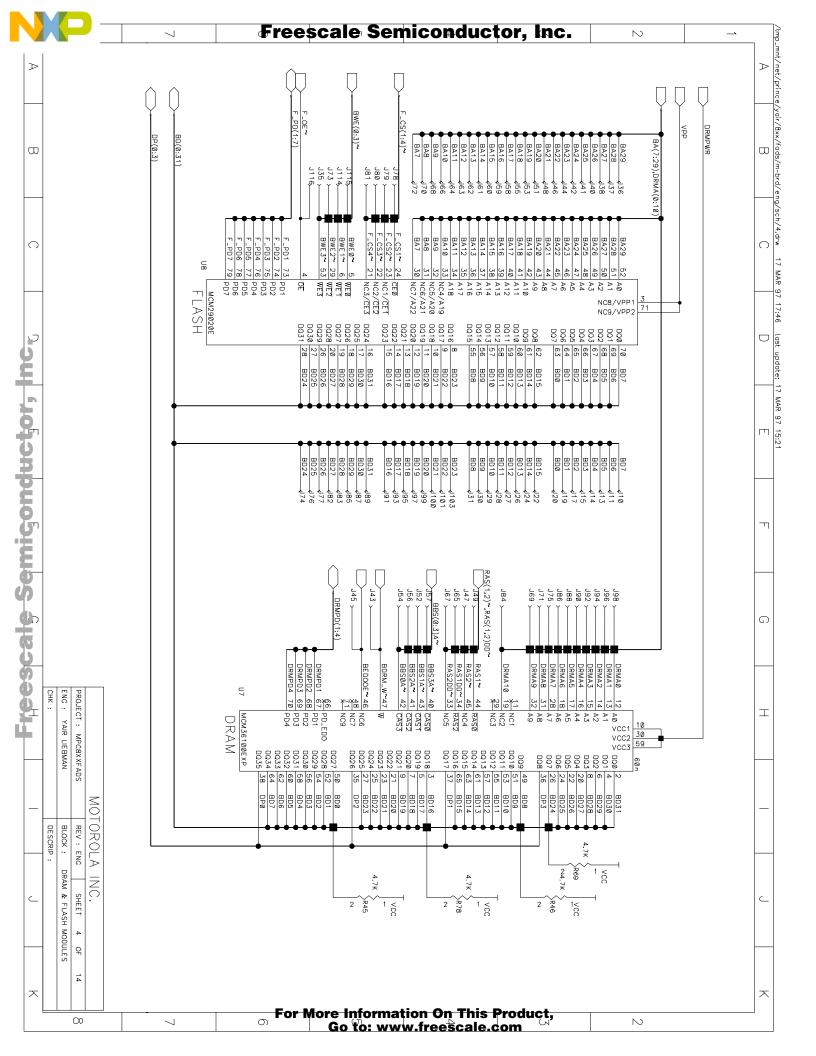

| Flash Memory<br>Dynamic RAM                   | 2 MByte, 32 bits wide expandable to 8 MBytes<br>4 MByte, 32 bits wide EDO SIMM<br>Support for up to 32 MByte, EDO or FPM SIMM |

| Synchronous DRAM                              | 4 MBytes, organized as 1 Meg X 32 bit.                                                                                        |

| Operating temperature                         | 0°C - 30°C                                                                                                                    |

| Storage temperature                           | -25°C to 85°C                                                                                                                 |

| Relative humidity                             | 5% to 90% (non-condensing)                                                                                                    |

| Dimensions:<br>Length<br>Width<br>Thickness   | 9.173" (233 mm)<br>6.3" (160 mm)<br>0.063" (1.6 mm)                                                                           |

# 1•6 MPC8XXFADS Features

- □ 4 MByte, Unbuffered, Synchronous Dram On-Board.

- 4 MByte EDO 60nsec delay DRAM SIMM. Support for 4 32 MByte FPM or EDO Dram SIMM, with Automatic Dram SIMM identification. 16 Bit Data-Bus Width Support.

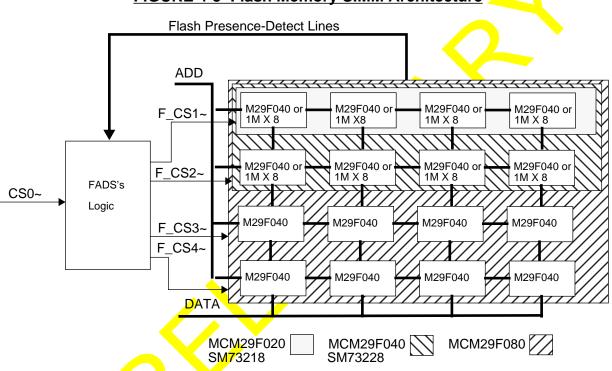

- 2 MByte Flash SIMM. Support for upto 8 MByte, 5V or 12V Programmable, with Automatic Flash SIMM identification.

- D Memory Disable Option for each local memory map slaves.

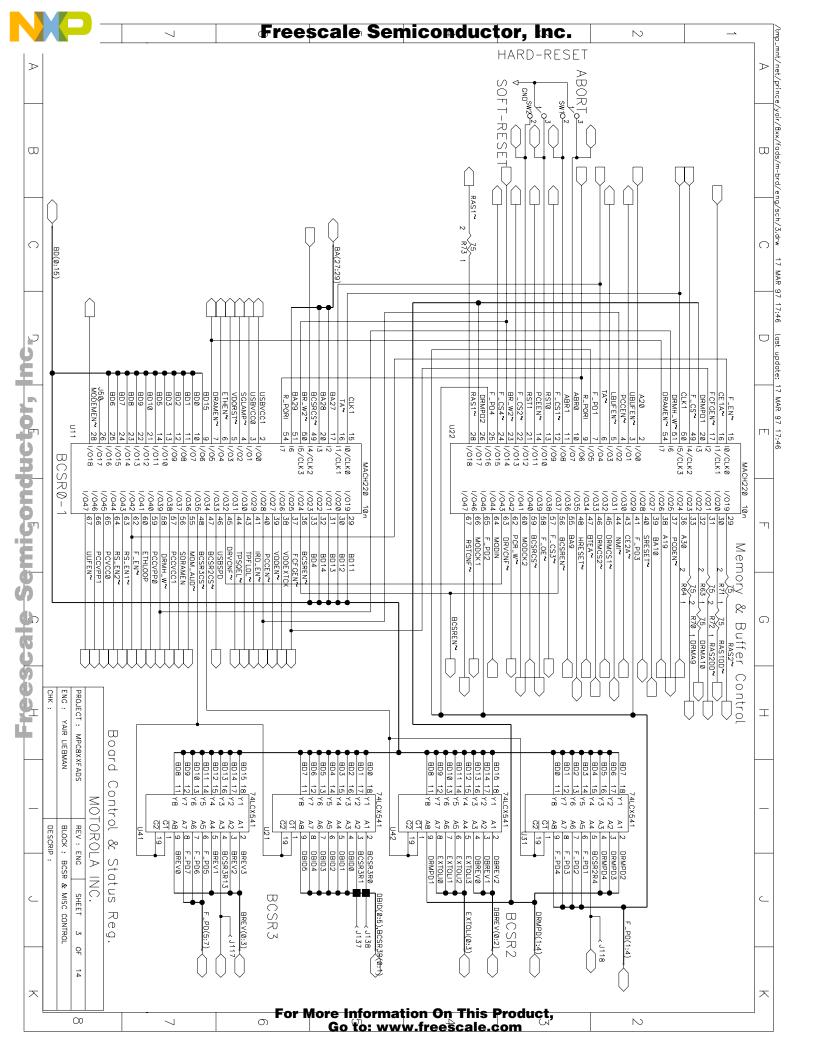

- Development Board Control & Status Register BCSR, Controlling Board's Operation.

- Dependence of the set of the set

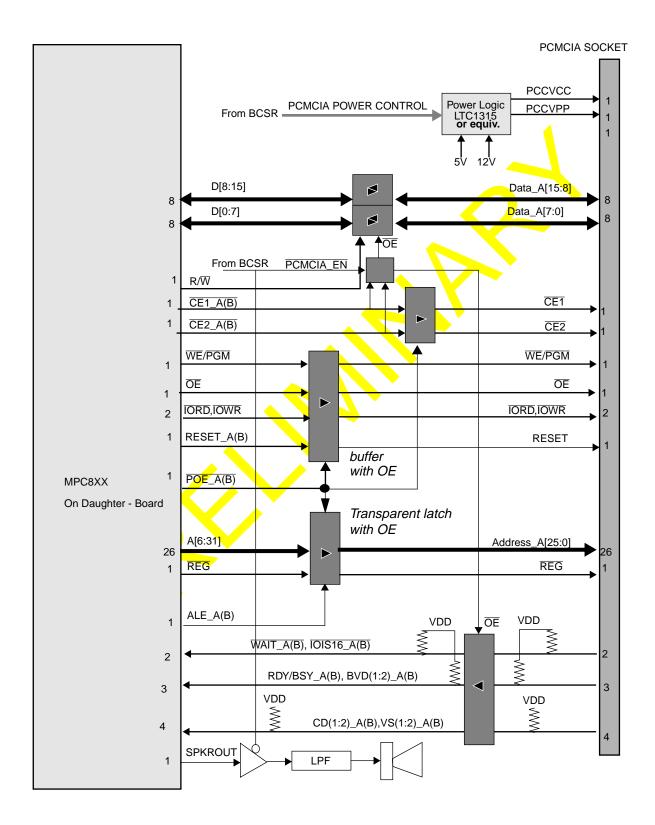

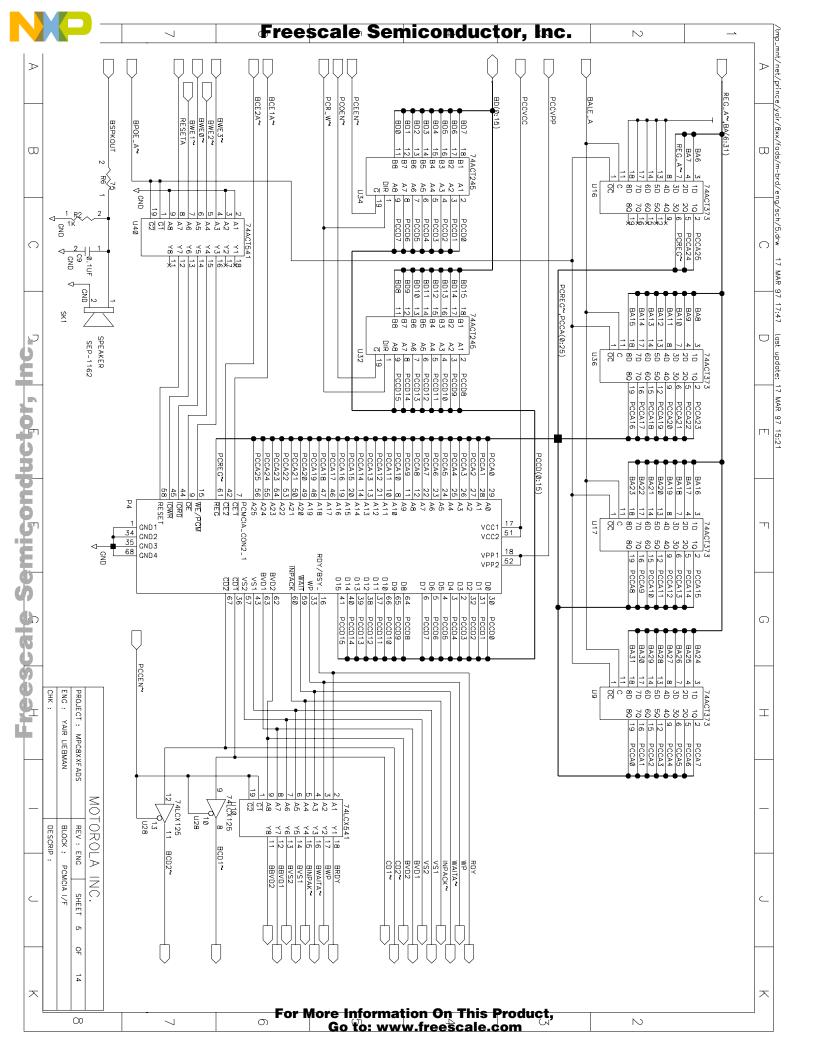

- □ 5V only PCMCIA Socket With Full Buffering, Power Control and Port Disable Option. Complies with PCMCIA 2.1+ Standard.

- □ Module Enable Indications.

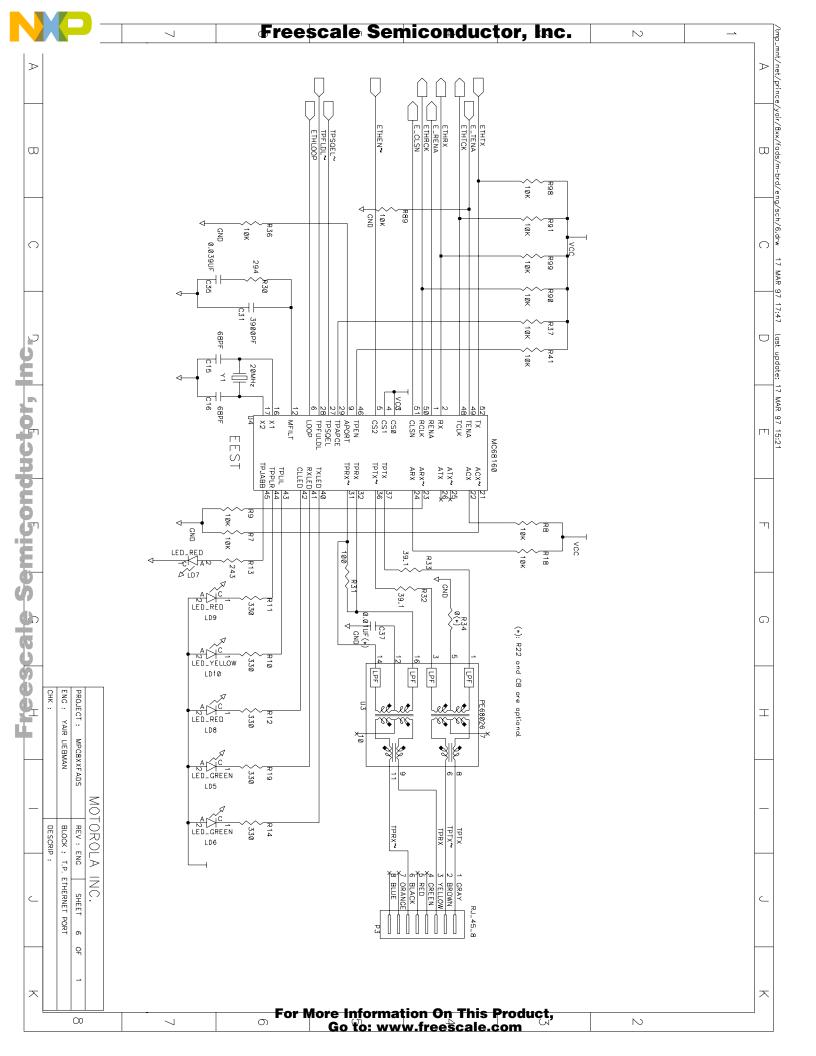

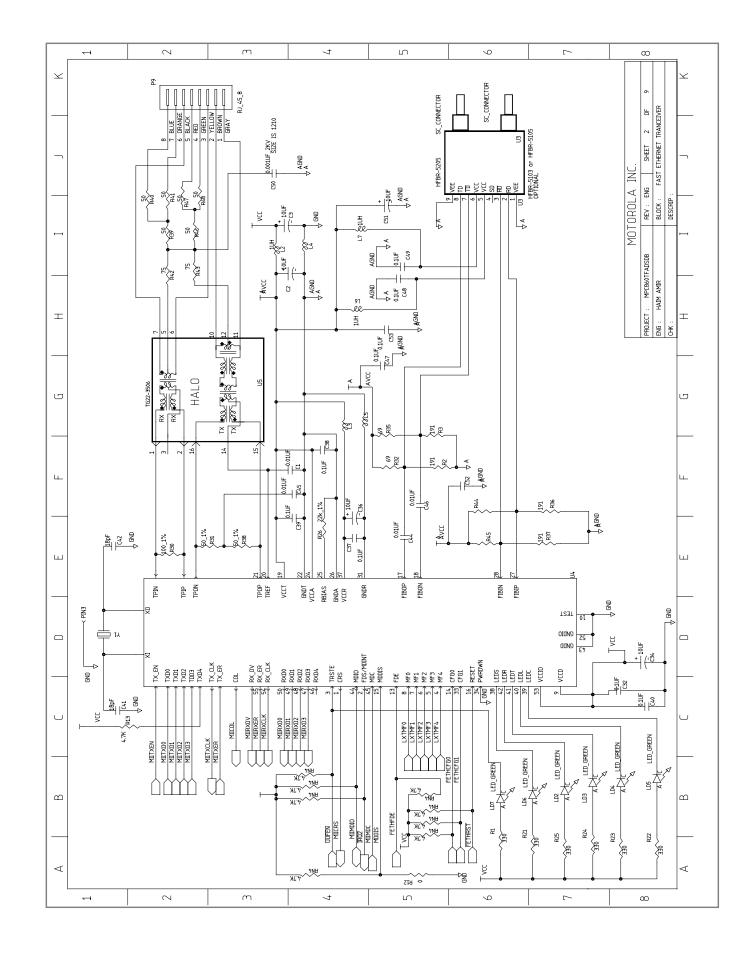

- □ 10-Base-T Port On-Board, with Stand-By Mode.

- □ Fast-IrDA (4MBps) Port with Stand-By Mode.

- Dual RS232 port with Low-Power Option per each port.

- On Board Debug Port Controller with ADI I/F.

- MPC8XXFADS Serving as Debug Station for Target System option.

- Optional Hard-Reset Configuration Burned in Flash<sup>A</sup>.

- External **Tools' Identification** Capability, via BCSR.

- □ Soft / Hard<sup>B</sup> Reset Push Button

- ABORT Push Button

- Single<sup>C</sup> 5V Supply.

- Reverse / Over Voltage Protection for Power Inputs.

- **3**.3V / 2V MPC Internal Logic Operation<sup>D</sup>, 3.3V MPC I/O Operation.

- Dever Indications for Each Power Bus.

- □ Software Option Switch provides 16 S/W options via BCSR.

A. Available only if supported also on the MPC8XX.

B. Hard reset is applied by depressing BOTH Soft Reset & ABORT buttons.

C. Unless a 12V supply is required for a PCMCIA card or for a 12V programmable Flash SIMM.

D. Implemented on Daughter Board.

General Information

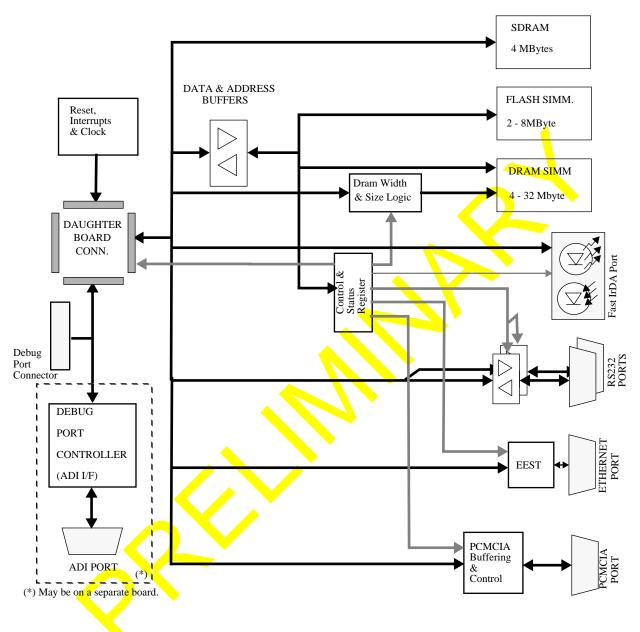

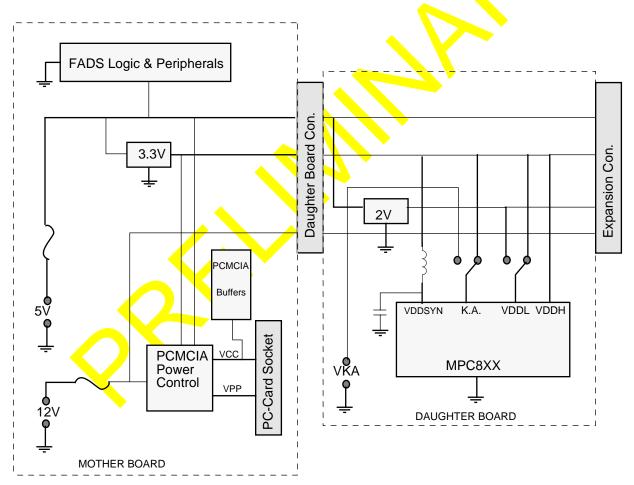

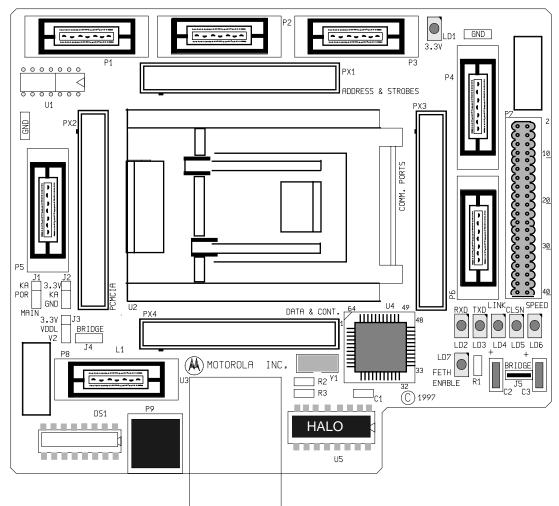

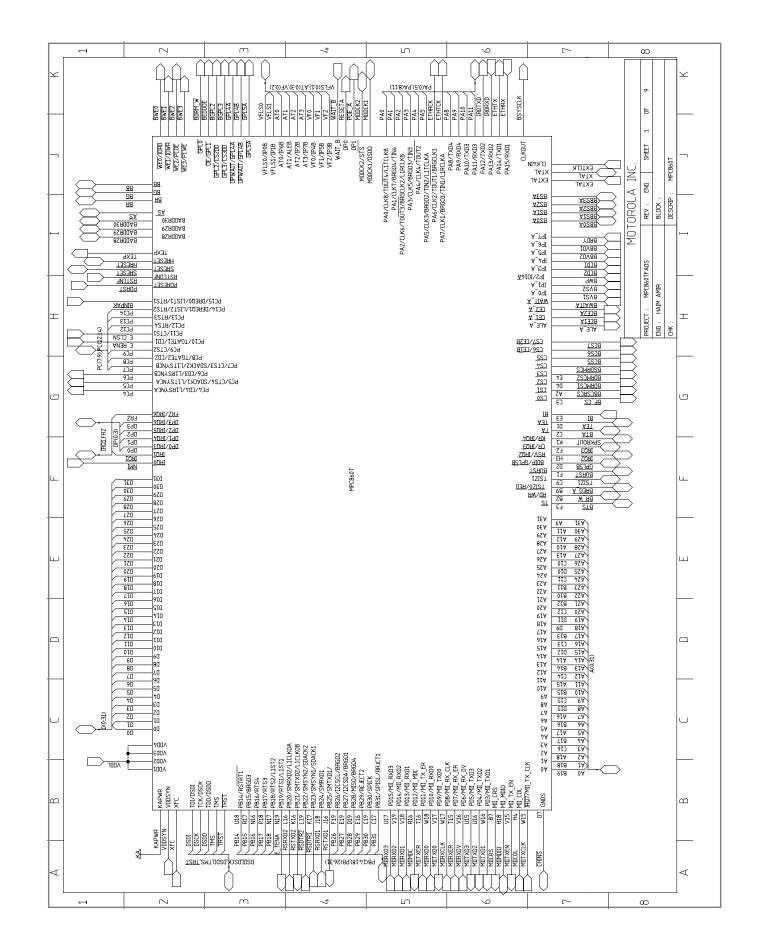

FIGURE 1-1 MPC8XXFADS Motherboard Block Diagram

# 1•7 MPC8XXFADS Goals

The MPC8XXFADS is meant to become a general platform for s/w and h/w development around the MPC8XX family. Using its on-board resources and its associated debugger, the developer is able to load his code, run it, set breakpoints, display memory and registers and connect his own proprietary h/w via the expansion connectors, to be incorporated to a system with the MPC.

This board could also be used as a demonstration tool, i.e., application s/w may be programmed<sup>A</sup> into its flash memory and ran in exhibitions etc.

WITHOUT NOTICE

MPC8XXFADS Design Specification For More Information On This P PRELIMINARY GUBIEWww.freescale.c

A. Either on or off-board.

# 2 - Hardware Preparation and Installation

# 2•1 INTRODUCTION

This chapter provides unpacking instructions, hardware preparation, and installation instructions for the MPC8XXFADS.

# 2•2 UNPACKING INSTRUCTIONS

## <u>NOTE</u>

If the shipping carton is damaged upon receipt, request carrier's agent to be present during unpacking and inspection of equipment.

Unpack equipment from shipping carton. Refer to packing list and verify that all items are present. Save packing material for storing and reshipping of equipment.

#### CAUTION

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITRY; STATIC DISCHARGE CAN DAMAGE CIRCUITS.

# 2•3 HARDWARE PREPARATION

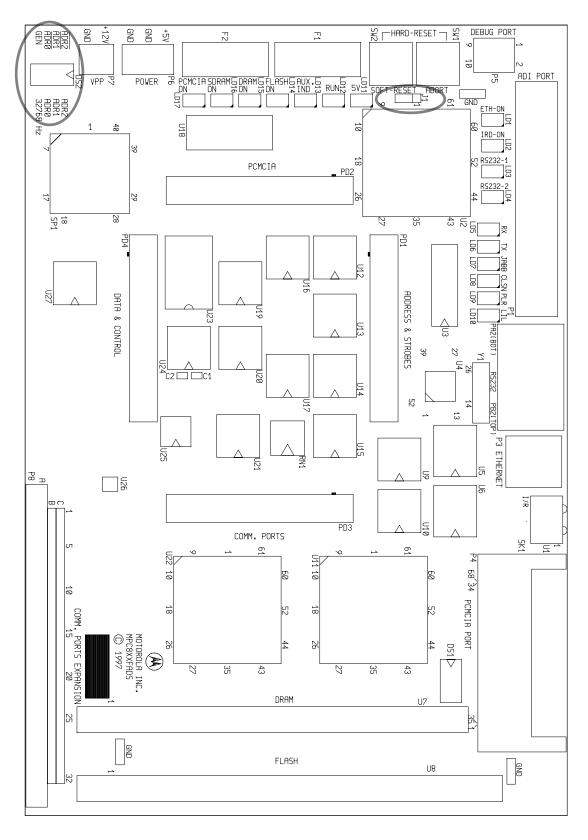

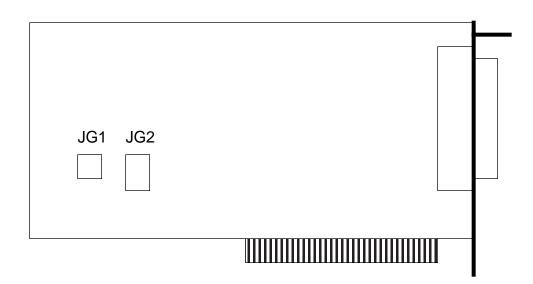

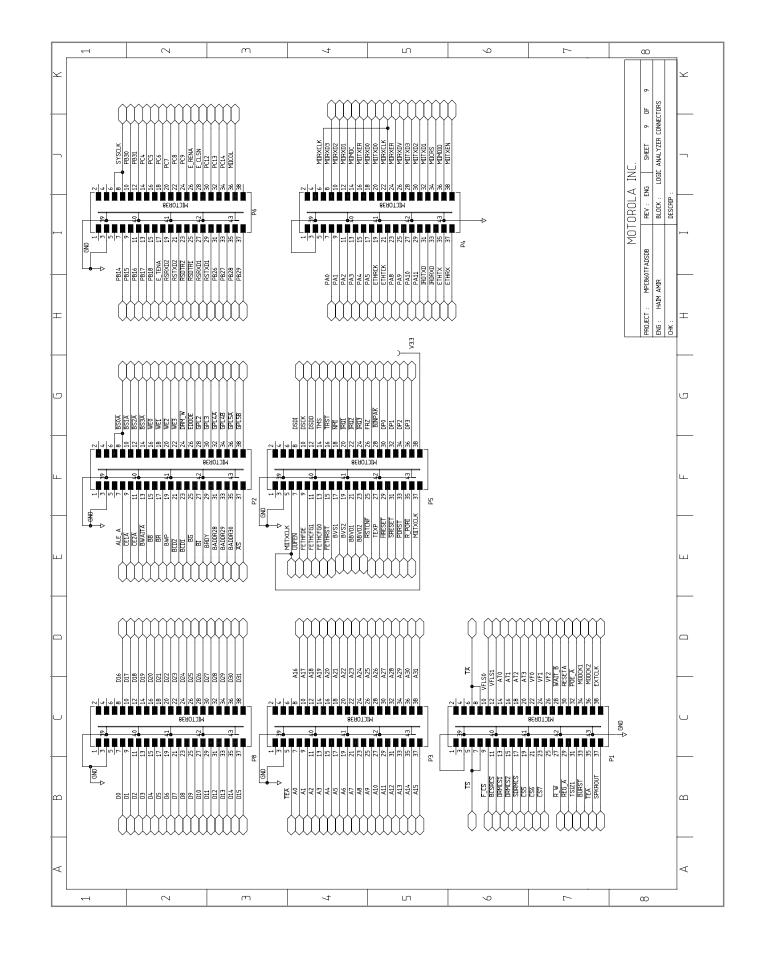

To select the desired configuration and ensure proper operation of the MPC8XXFADS board, changes of the Dip-Switch settings may be required before installation. The location of the switches, LEDs, Dip-Switches, and connectors is illustrated in FIGURE 2-1. The board has been factory tested and is shipped with Dip-Switch settings as described in the following paragraphs. Parameters can be changed for the following conditions:

- ADI port address

- MPC Clock Source

- Power-On Reset Source.

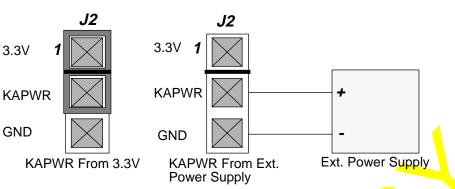

- MPC Keep Alive Power Source

- MPC Internal Logic Supply Source

- Debug Mode Indication Source

FIGURE 2-1 MPC8XXFADS Top Side Part Location diagram

### 2•3•1 ADI Port Address Selection

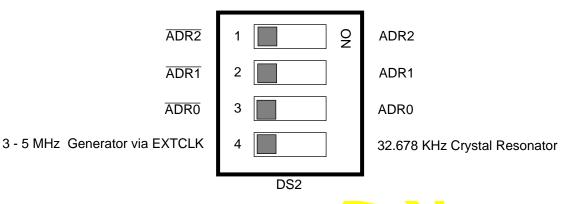

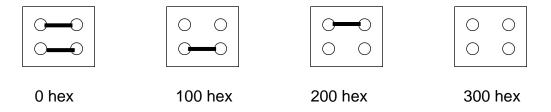

The MPC8XXFADS can have eight possible slave addresses set for its ADI port, enabling up to eight MPC8XXFADS boards to be connected to the same ADI board in the host computer. The selection of the slave address is done by setting switches 1, 2 & 3 in the Dip-Switch - DS2. Switch 1 stands for the most-significant bit of the address and switch 3 stands for the least-significant bit. If the switch is in the 'ON' state, it stands for logical '1'. In FIGURE 2-2 DS1 is shown to be configured to address '0'.

Table 2-1 describes the switch settings for each slave address:

Table 2-1 ADI Address Selection

| ADDRESS | Switch 1 | Switch 2 | Switch 3 |

|---------|----------|----------|----------|

| 0       | OFF      | OFF      | OFF      |

| 1       | OFF      | OFF      | ON       |

| 2       | OFF      | ON       | OFF      |

| 3       | OFF      | ON       | ON       |

| 4       | ON       | OFF      | OFF      |

| 5       | ON       | OFF      | ON       |

| 6       | ON       | ON       | OFF      |

|         | ON       | ON       | ON       |

# 2•3•2 Clock Source Selection

Switch #4 on DS2 selects the clock source for the MPC. When it is in the 'ON' position while the FADS is powered-up, the on-board 32.768 KHz crystal resonator<sup>A</sup> becomes the clock source and the PLL multiplication factor becomes 1:513. When switch #4 is in the 'OFF' position while the FADS is powered-up, the on-board 4<sup>B</sup>MHz clock generator<sup>A</sup> becomes the clock source while the PLL multiplication factor becomes 1:5.

#### 2•3•3 Power-On Reset Source Selection

As there are differences between MPC revisions regarding the functionality of the Power-On Reset logic, it is therefore necessary to select different sources for Power-ON reset generation.

The above selection is done on the Daughter Board and therefore, documented in the specific

A. Located on the Daughter-Board

B. A 5MHz clock generator is packed as well.

Daughter Board user's manual.

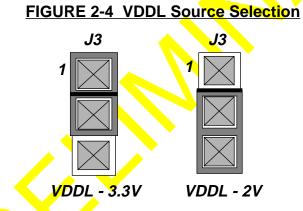

#### 2•3•4 VDDL Source Selection

This selection is done on the Daughter Board and therefore, documented in the specific Daughter Board user's manual.

### 2•3•5 Keep Alive Power Source Selection

This selection is done on the Daughter Board and therefore, documented in the specific Daughter Board user's manual.

#### 2•3•6 Debug Mode Indication Source Selection

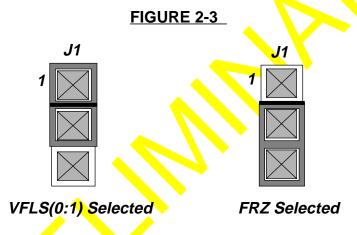

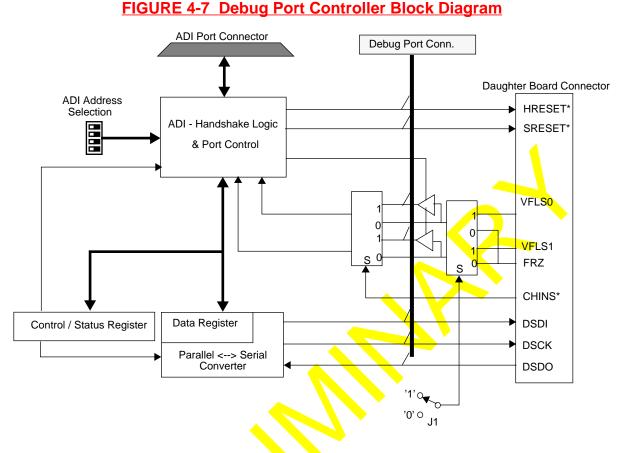

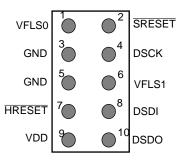

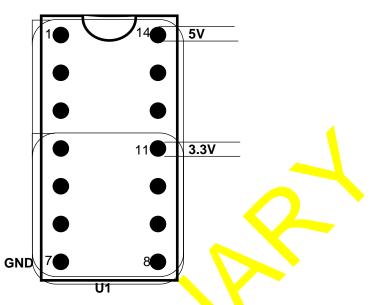

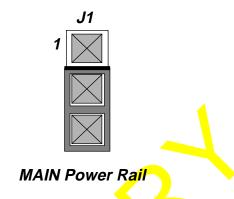

Jumper J1 selects between VFLS(0:1) signals and FRZ signal of the MPC as an indication for debug mode state. Since with the MPC8XXs, each of these signals has alternate function, it may be necessary to switch between the two sources, in favor of alternate function being used.

When a jumper is positioned between pins 1 and 2 of J1 - VFLS(0:1) are selected towards the debugport controller. When a jumper is placed between positions 2 - 3 of J1(2) - FRZ signal is selected.

# 2•4 INSTALLATION INSTRUCTIONS

When the MPC8XXFADS has been configured as desired by the user, it can be installed according to the required working environment as follows:

- Host Controlled Operation

- Debug Port Controller for Target System

- Stand-Alone

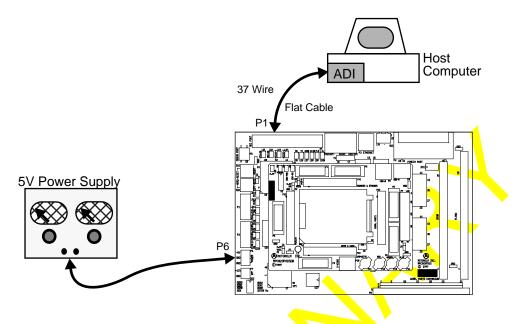

#### 2•4•1 Host Controlled Operation

In this configuration the MPC8XXFADS is controlled by a host computer via the ADI through the debug port. This configuration allows for extensive debugging using on-host debugger.

### FIGURE 2-4 Host Controlled Operation Scheme

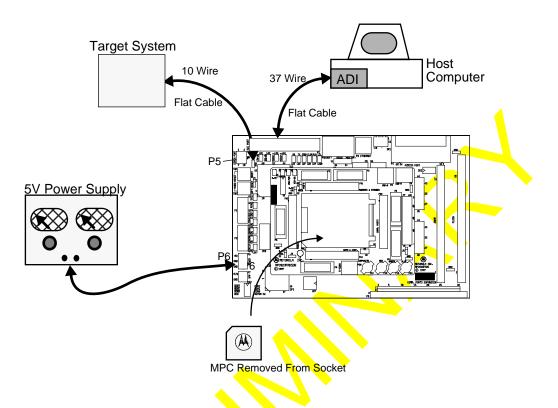

#### 2•4•2 Debug Port Controller For Target System

This configuration resembles the previous, but here the local MPC is removed from its socket while the FADS is connected via a 10 lead Flat-Cable between P5 and a matching connector on a target system.

# WARNNING

When connecting the FADS to a target system via P5 and a 10 lead flat-cable, the MPC MUST be RE-MOVED from its SOCKET. Otherwise, PERMANENT DAMAGE might be inflicted to either the Local MPC or to the Target MPC.

With this mode of operation, all on-board modules are disabled and can not be accessed in anyway, except for the debug port controller. Also, all indications except for 5V power, 3.3V-Power<sup>A</sup> and RUN are darkened.

All debugger commands and debugging features are available in this mode, including s/w download, breakpoints, etc... The target system may be reset or interrupted by the debug port or reset by the FADS's RESET switches. It is the responsibility of the target system designer, to provide Power-On-Reset and HARD-Reset configurations, while SOFT-Reset configuration is provided by the debug-port controller. See also 4•12•1 "MPC8XXFADS As Debug Port Controller For Target System" on page 58.

A. On Daughter Board.

# FIGURE 2-5 Debug Port Controller For Target System Operation Scheme

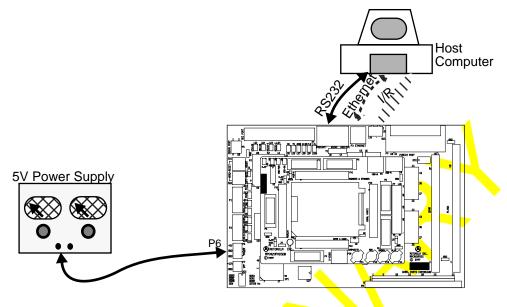

### 2•4•3 Stand Alone Operation

In this mode, the FADS is not controlled by the host via the ADI/Debug port. It may connect to host via one of its other ports, e.g., RS232 port, I/R port, Ethernet port, etc<sup>4</sup>. Operating in this mode requires an application program to be programmed into the board's Flash memory (while with the host controlled operation, no memory is required at all).

## FIGURE 2-6 Stand Alone Configuration

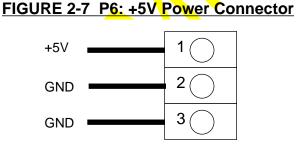

### 2•4•4 +5V Power Supply Connection

The MPC8XXFADS requires +5 Vdc @ 5 A max, power supply for operation. Connect the +5V power supply to connector P6 as shown below:

P6 is a 3 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires. To provide solid ground, two Gnd terminals are supplied. It is recommended to connect both Gnd wires to the common of the power supply, while VCC is connected with a single wire.

#### **NOTE**

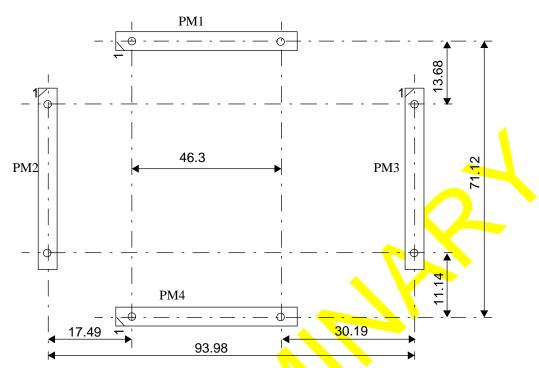

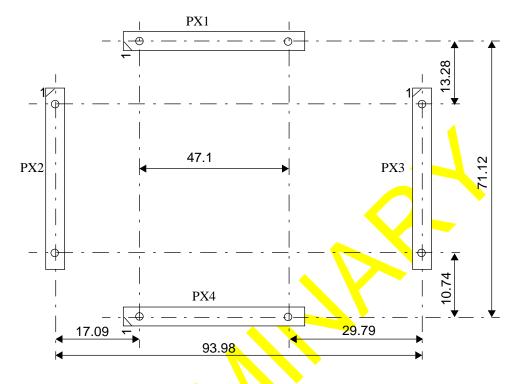

Since hardware applications may be connected to the MPC8XXFADS via the Daughter-Boards' expansion connectors PX1, PX2 PX3, PX4 or FADS's P8, the additional power consumption should be taken into consideration when a power supply is connected to the MPC8XXFADS.

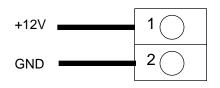

# 2•4•5 P7: +12V Power Supply Connection

The MPC8XXFADS requires +12 Vdc @ 1 A max, power supply for the PCMCIA channel Flash programming capability or for 12V programmable Flash SIMM. The MPC8XXFADS can work properly without the +12V power supply, if there is no need to program either a 12V programmable PCMCIA flash card or a 12V programmable Flash SIMM.

Connect the +12V power supply to connector P7 as shown below:

FIGURE 2-8 P7: +12V Power Connector

P7 is a 2 terminal block power connector with power plug. The plug is designed to accept 14 to 22 AWG wires. It is recommended to use 14 to 18 AWG wires.

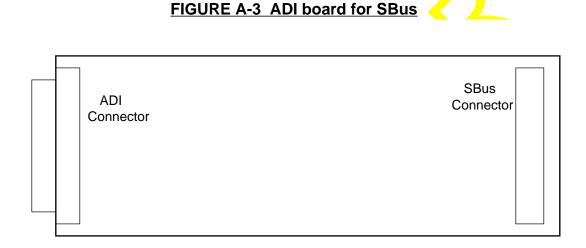

## 2•4•6 ADI Installation

For ADI installation on various host computers, refer to APPENDIX C - "ADI Installation" on page 155.

#### 2•4•7 Host computer to MPC8XXFADS Connection

The MPC8XXFADS ADI interface connector, P1, is a 37 pin, male, D type connector. The connection between the MPC8XXFADS and the host computer is by a 37 line flat cable, supplied with the ADI board. FIGURE 2-9 below shows the pin configuration of the connector.

#### 1 N.C Gnd 20 2 D\_C~ HST\_ACK Gnd 21 3 Gnd 22 4 ADS\_SRESET Gnd 23 5 ADS HRESET Gnd 24 ADS\_SEL2 6 Gnd 25 7 ADS\_SEL1 (+ 12 v) N.C. 26 8 ADS SEL0 HOST\_VCC 27 9 HOST REQ HOST VCC 28 10 ADS REQ HOST\_VCC 29 ADS ACK 11 30 HOST\_ENABLE~ 12 N.C. Gnd 31 13 N.C. Gnd 32 N.C. 14 Gnd 33 15 N.C. PD0 34 16 PD1 PD2 35 17 PD3 PD4 36 PD5 18 PD6 37 19 PD7

# FIGURE 2-9 P1 - ADI Port Connector

NOTE: Pin 26 on the ADI is connected to +12 v power supply, but it is not used in the MPC8XXFADS.

#### 2•4•8 Terminal to MPC8XXFADS RS-232 Connection

A serial (RS232) terminal or any other RS232 equipment, may be connected to the RS-232 connectors PA2 and PB2. The RS-232 connectors is a 9 pin, female, Stacked D-type connector as shown in FIGURE 2-10.

The connectors are arranged in a manner that allows for 1:1 connection with the serial port of an IBM-AT<sup>A</sup> or compatibles, i.e. via a flat cable.

MPC8XXFADS Design Specification For More Internation Op This F MNARY GUB: Www.freescale.c

**JOUT NOTICE**

A. IBM-AT is a trademark of International Business Machines Inc.

### FIGURE 2-10 PA2, PB2 - RS-232 Serial Port Connectors

| CD  | 1 | 0 |      |

|-----|---|---|------|

| ТΧ  | 2 | 6 | DSR  |

|     |   | 7 | RTS  |

| RX  | 3 | 8 | CTS  |

| DTR | 4 | • |      |

|     |   | 9 | N.C. |

| GND | 5 |   |      |

|     |   |   |      |

NOTE: The RTS line (pin 7) is not connected on the MPC8XXFADS.

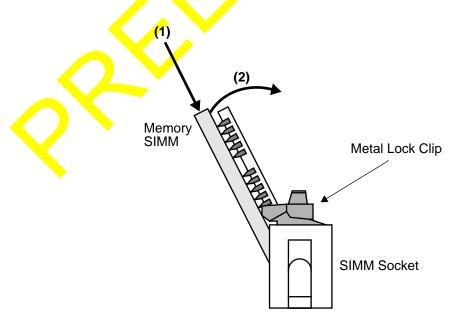

#### 2•4•9 Memory Installation

The MPC8XXFADS is supplied with two types of memory SIMM:

- Dynamic Memory SIMM

- Flash Memory SIMM.

To avoid shipment damage, these memories are packed aside rather than being installed in their sockets. Therefore, they should be installed on site. To install a memory SIMM, it should be taken out of its package, put diagonally in its socket (no error can be made here, since the Flash socket has 80 contacts, while the DRAM socket has 72) and then twisted to a vertical position until the metal lock clips are locked. See FIGURE 2-11 "Memory SIMM Installation" below.

#### **CAUTION**

The memory SIMMs have alignment nibble near their # 1 pin. It is important to align the memory correctly before it is twisted, otherwise damage might be inflicted to both the memory SIMM and its socket.

FIGURE 2-11 Memory SIMM Installation

# 3 - OPERATING INSTRUCTIONS

#### INTRODUCTION 3•1

This chapter provides necessary information to use the MPC8XXFADS in host-controlled and standalone configurations. This includes controls and indicators, memory map details, and software initialization of the board.

#### 3•2 CONTROLS AND INDICATORS

The MPC8XXFADS has the following switches and indicators.

#### 3•2•1 ABORT Switch SW1

The ABORT switch is normally used to abort program execution, this by issuing a level 0 interrupt to the

MPC. If the FADS is in stand alone mode, it is the responsibility of the user to provide means of handling

the interrupt, since there is no resident debugger with the MPC8XXFADS. The ABORT switch signal is

debounced, and can not be disabled by software.

#### 3-2-2 SOFT RESET Switch SW2

The SOFT RESET switch SW2 performs Soft reset to the MPC internal modules, maintaining MPC's configuration (clocks & chip-selects) Dram and SDram contents. The switch signal is debounced, and it is not possible to disable it by software. At the end of the Soft Reset Sequence, the Soft Reset Configuration is sampled and becomes valid.

#### 3-2-3 HARD RESET - Switches SW1 & SW2

When BOTH switches - SW1 and SW2 are depressed simultaneously, HARD reset is generated to the MPC. When the MPC is HARD reset, all its configuration is lost, including data stored in the DRAM or SDRAM and the MPC has to be re-initialized. At the end of the Hard Reset sequence, the Hard Reset Configuration stored in BCSR0 becomes valid.

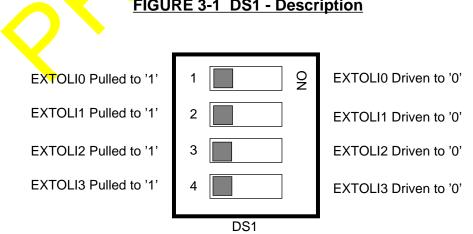

#### 3•2•4 DS1 - Software Options Switch

DS1 is a 4-switches Dip-Switch. This switch is connected over EXTOLI(0:3) lines which are available at BCSR, S/W options may be manually selected, according to DS1 state.

# FIGURE 3-1 DS1 - Description

#### 3-2-5 GND Bridges

There are 3 GND bridges on the MPC8XXFADS. They are meant to assist general measurements

and logic-analyzer connection.

#### **Warning**

#### When connecting to a GND bridge, use only INSU-LATED GND clips. Failure in doing so, might result in permanent damage to the MPC8XXFADS.

# 3•2•6 ETH ON - LD1

When the yellow ETH ON led is lit, it indicates that the ethernet port transceiver - the MC68160 EEST, is active. When it is dark, it indicates that the EEST is in power down mode, enabling the use of its associated SCC pins off-board via the expansion connectors.

# 3•2•7 IRD ON - LD2

When the yellow IRD ON led is lit, it indicates that the Infra-Red transceiver - the TFDS6000, is active and enables communication via that medium. When it is dark, the I/R transceiver is in shutdown mode, enabling the use of its associated SCC pins off-board via the expansion connectors.

# 3•2•8 RS232 Port 1 ON - LD3

When the yellow RS232 Port 1 ON led is lit, it designates, that the RS232 transceiver connected to PA2, is active and communication via that medium is allowed. When darkened, it designates that the transceiver is in shutdown mode, so its associated MPC pins may be used off-board via the expansion connectors.

# 3•2•9 RS232 Port 2 ON - LD4

When the yellow RS232 Port 2 ON led is lit, it designates that the RS232 transceiver connected to PB2,

is active and communication via that medium is allowed. When darkened, it designates, that the transceiver is in shutdown mode, so its associated MPC pins may be used off-board via the expansion connectors.

# 3•2•10 Ethernet RX Indicator - LD5

The green Ethernet Receive LED indicator blinks whenever the EEST is receiving data from one of the Ethernet port.

#### 3•2•11 Ethernet TX Indicator - LD6

The green Ethernet Receive LED indicator blinks whenever the EEST is transmitting data via the Ethernet port.

# 3•2•12 Ethernet JABB Indicator - LD7

The red Ethernet TP Jabber LED indicator - JABB, lights whenever a jabber condition is detected on the TP ethernet port.

# 3•2•13 Ethernet CLSN Indicator LD8

The red Ethernet Collision LED indicator CLSN, blinks whenever a collision condition is detected on the ethernet port, i.e., simultaneous receive and transmit.

#### 3•2•14 Ethernet PLR Indicator - LD9

The red Ethernet TP Polarity LED indicator - PLR, lights whenever the wires connected to the receiver input of the ethernet port are reversed. The LED is lit by the EEST, and remains on while the EEST has automatically corrected for the reversed wires.

# 3•2•15 Ethernet LIL Indicator - LD10

The yellow Ethernet Twisted Pair Link Integrity LED indicator - LIL, lights to indicate good link integrity on the TP port. The LED is off when the link integrity fails.

# **DPERATING INSTRUCTION Freescale Semiconductor, Inc.**

#### 3•2•16 5V Indicator - LD11

The yellow 5V led, indicates the presence of the +5V supply at P6.

#### 3•2•17 RUN Indicator - LD12

When the green RUN led - LD12 is lit, it indicates that the MPC is not in debug mode, i.e., VFLS0 & VFLS1 == 0 (or FRZ == 0, which ever selected by J1).

#### 3•2•18 AUXILARY Indicator LD13

This indication has no dedicated function over the FADS. It is meant to provide some visibility for program behavior. It is controlled by the Signal Lamp bit in BCSR4.

#### 3•2•19 FLASH ON - LD14

When the yellow FLASH ON led is lit, it indicates that the FLASH SIMM is enabled in the BCSR1 register. I.e., any access done to the CS0~ address space will hit the flash memory. When it is dark, the flash is disabled and CS0~ may be used off-board via the expansion connectors.

#### 3•2•20 DRAM ON - LD15

When the yellow DRAM ON led is lit, it indicates the DRAM SIMM is enabled in BCSR1. Therefore, any access made to CS2~ (or CS3~) will hit on the DRAM. When it is dark, it indicates that either the DRAM is disabled in BCSR1, enabling the use of CS2~ and CS3~ off-board via the expansion connectors.

#### 3•2•21 SDRAM ON - LD16

When the yellow SDRAM ON led is lit, it indicates the SDRAM is enabled in BCSR1. Therefore, any access made to CS4~ (will hit on the SDRAM. When it is dark, it indicates that either the SDRAM is disabled in BCSR1, enabling the use of CS4~ off-board via the expansion connectors.

#### 3•2•22 PCMCIA ON - LD17

When the yellow PCMCIA ON led is lit, it indicates the following:

- 1) Address & strobe buffers are driven towards the PCMCIA card

- 2) Data buffers are driven to / from the PCMCIA card whenever CE1A~<sup>A</sup> or CE2A~<sup>B</sup> signals are asserted.

- 3) Card status lines are driven towards the MPC from the PCMCIA card.

When it is dark, it indicates that all the above buffers are tri-stated and the pins associated with PCMCIA channel A<sup>C</sup>, may be used off-board via the expansion connectors.

# 3•3 **MEMORY** MAP

All accesses to MPC8XXFADS's memories are controlled by the MPC's memory controller. Therefore, the memory map is reprogrammable to the desire of the user. After Hard Reset is performed by the debug station, the debugger checks to see the size, delay and type of the DRAM and FLASH SIMMs mounted on board and initializes the chip-selects accordingly. The DRAM,

A. Connected to CE1B~ for MPC823FADSDB.

B. Connected to CE2B~ for MPC823FADSDB.

C. Or B for MPC823FADSDB.

SDRAM and the FLASH memory respond to all types of memory access i.e., user / supervisory, program / data and DMA.

| ADDESS RANGE        | Memory Type                      |                         | Device Type             |                         |                         |                 |  |  |

|---------------------|----------------------------------|-------------------------|-------------------------|-------------------------|-------------------------|-----------------|--|--|

| 00000000 - 003FFFFF | DRAM SIMM                        | MB321Bx <sup>a</sup> 08 | MB322Bx <sup>a</sup> 08 | MC324Cx <sup>a</sup> 00 | MB328Cx <sup>a</sup> 00 | 32              |  |  |

| 00400000 - 007FFFFF |                                  |                         |                         |                         |                         | 32              |  |  |

| 00800000 - 00FFFFF  |                                  |                         |                         |                         |                         | 32              |  |  |

| 01000000 - 01FFFFFF |                                  |                         |                         |                         |                         | 32              |  |  |

| 02000000 - 020FFFFF | Empty Space                      |                         |                         |                         |                         |                 |  |  |

| 02100000 - 02103FFF | BCSR(0:4) <sup>b</sup>           |                         |                         |                         |                         | 32 <sup>c</sup> |  |  |

| 02100000 - 02103FE3 | BCSR0                            |                         |                         |                         | •                       |                 |  |  |

| 2100004 - 02103FE7  | BCSR1                            |                         |                         |                         |                         |                 |  |  |

| 2100008 - 02103FEB  | BCSR2                            |                         |                         |                         |                         |                 |  |  |

| 210000C - 02103FEF  | BCSR3                            |                         |                         |                         |                         |                 |  |  |

| 2100010 - 02103FF3  | BCSR4                            |                         |                         |                         |                         |                 |  |  |

| 02104000 - 021FFFFF | Empty Space                      |                         |                         |                         |                         |                 |  |  |

| 02200000 - 02207FFF | MPC Internal<br>MAP <sup>d</sup> |                         |                         |                         |                         | 32              |  |  |

| 02208000 - 027FFFFF | Empty Space                      |                         |                         |                         |                         |                 |  |  |

| 02800000 - 029FFFFF | Flash SIMM                       | MCM29F020               | MCM29F040               | MCM29F080               |                         | 32              |  |  |

| 02A00000 - 02BFFFFF |                                  |                         | SM732A1000A             | SM732A2000              |                         | 32              |  |  |

| 02C00000 - 02FFFFFF |                                  |                         | 1                       |                         |                         | 32              |  |  |

| 03000000 - 033FFFFF | SDRAM                            |                         |                         | 1                       | ,                       | 32              |  |  |

| 03400000 - FFFFFFFF | Empty Space                      |                         |                         |                         |                         |                 |  |  |

#### TABLE 3-1. MPC8XXADS Main Memory Map

a. x ∈ [B,T]

b. The device appears repeatedly in multiples of its size. E.g., BCSR0 appears at memory locations 2100000, 2100020, 2100040..., while BCSR1 appears at 2100004, 2100024, 2100044... and so on.

c. Only upper 16 bit (D0-D15) are in fact used.

d. Refer to the relevant MPC User's Manual for complete description of the MPC internal memory map.

DS Design Specif niormation On UB: WWW.frees

OUTNOTICE

# **3•4 Programming The MPC Registers**

The MPC provides the following functions on the MPC8XXFADS:

- 1) DRAM Controller

- 2) SDRAM Controller

- 3) Chip Select generator.

- 4) UART for terminal or host computer connection.

PRELIMINARY

- 5) Ethernet controller.

- 6) Infra-Red Port Controller

- 7) General Purpose I/O signals.

The internal registers of the MPC must be programmed after Hard reset as described in the following paragraphs. The addresses and programming values are in hexadecimal base.

For better understanding the of the following initializations refer to the MPC821 or to the MPC860 User's Manual for more information.

| Register | Init Value[hex] | Description                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

|----------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| SIUMCR   | 01032440        | Internal arbitration, External master arbitration priority $\sim$ 0, External arbitration priority $\sim$ 0, PCMCIA channel II pins - PCMCIA, Debug Port on JTAG port pins, FRZ/IRQ6~ - FRZ, debug register - locked, No parity for non-CS regions, DP(0:3)/IRQ(3:6)~ pins - DP(0:3), reservation disabled, SPKROUT - Tri-stated, BS_A(0:3)~ and WE(0:3)~ are driven just on their dedicated pins, GPL_B5~ enabled, GPL_A/B(2:3)~ function as GPLs. |  |  |  |  |

| SYPCR    | FFFFF88         | Software watchdog timer count - FFFF, Bus-monitor timing FF, Bus-monitor -<br>Enabled, S/W watch-dog - Freeze, S/W watch-dog - disabled, S/W watch-dog (if<br>enabled) causes NMI, S/W (if enabled) not prescaled.                                                                                                                                                                                                                                  |  |  |  |  |

| TBSCR    | 00C2            | No interrupt level, reference match indications cleared, interrupts disabled, no freeze, time-base disabled.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| RTCSC    | 00C2            | Interrupt request level - 0, 32768 Hz source, second interrupt disabled, Alarm interrupt disabled, Real-time clock - FREEZE, Real-time clock enabled.                                                                                                                                                                                                                                                                                               |  |  |  |  |

| PISCR    | 0082            | No level for interrupt request, Periodic interrupt disabled, clear status, interrupt disabled, FREEZE, periodic timer disabled.                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

### TABLE 3-2. SIU REGISTERS' PROGRAMMING

# 3•4•1 Memory Controller Registers Programming

The memory controller on the MPC8XXFADS is initialized to 50 MHz operation. I.e., registers' programming is based on 50 MHZ timing calculation except for refresh timer which is initialized to 16.67Mhz, the lowest frequency at which the FADS may wake up. Since the FADS may be made to wake-up at 25MHz<sup>A</sup> as well, the initializations are not efficient, since there are too many wait-states inserted. Therefore, additional set of initialization is provided to support efficient 25MHz operation.

The reason for initializing the FADS for 50Mhz is to allow proper (although not efficient) FADS operation through all available FADS clock frequencies.

**OUT NOTICE**

Design

A. The only parameter which is initialized to the start-up frequency, is the refresh rate, which would have been inadequate if initialized to 50Mhz while board is running at a lower frequency. Therefore, for best bus bandwidth availability, refresh rate should be adapted to the current system clock frequency.

### **Warning**

Due to availability problems with few of the supported memory components, the below initializations were not tested with all parts. Therefore, the below initializations are liable to CHANGE, throughout the testing period.

# TABLE 3-3. Memory Controller Initializations For 50Mhz

| Register | Device Type                               | Init Value [hex] | Description                                                                          |

|----------|-------------------------------------------|------------------|--------------------------------------------------------------------------------------|

| BR0      | All Flash SIMMs supported.                | 02200001         | Base at 2200000, 32 bit port size, no parity, GPCM                                   |

| OR0      | MCM29F020-90                              | FFE00D34         | 2MByte block size, all types access, CS early negate,<br>6 w.s., Timing relax        |

|          | MCM29F040-90<br>SM732A1000A-9             | FFC00D34         | 4MByte block size, all types access, CS early negate,<br>6 w.s., Timing relax        |

|          | MCM29F080-90<br>SM732A2000-9              | FF800D34         | 8MByte block size, all types access, CS early negate,<br>6 w.s., Timing relax        |

|          | MCM29F020-12                              | FFE00D44         | 2MByte block size, all types access, CS early negate,<br>8 w.s., Timing relax        |

|          | MCM29F040-12<br>SM732A1000A-12            | FFC00D44         | 4MByte block size, all types access, CS early negate,<br>8 w.s., Timing relax        |

|          | MCM29F080-12<br>SM732A2000-12             | FF800D44         | 8MByte block size, all types access, CS early negate,<br>8 w.s., Timing relax        |

| BR1      | BCSR                                      | 02100001         | Base at 2100000, 32 bit port size, no parity, GPCM                                   |

| OR1      |                                           | FFFF8110         | 32 KByte block size, all types access, CS early negate, 1 w.s.                       |

| BR2      | All Dram SIMMs<br>Supported               | 00000081         | Base at 0, 32 bit port size, no parity, UPMA                                         |

| OR2      | MCM36100/200-60/70                        | FFC00800         | 4MByte block size, all types access, initial address multiplexing according to AMA.  |

|          | MCM36400/800-60/70<br>MT8/16D432/832X-6/7 | FF000800         | 16MByte block size, all types access, initial address multiplexing according to AMA. |

| BR3      | MCM36200-60/70                            | 00400081         | Base at 400000, 32 bit port size, no parity, UPMA                                    |

|          | MCM36800-60/70<br>MT16D832X-6/7           | 01000081         | Base at 1000000, 32 bit port size, no parity, UPMA                                   |

| OR3      | MCM36200-60/70                            | FFC00800         | 4MByte block size, all types access, initial address multiplexing according to AMA   |

|          | MCM36800-60/70<br>MT16D832X-6/7           | FF000800         | 16MByte block size, all types access, initial address multiplexing according to AMA. |

| BR4      | MB811171622A-100                          | 030000C1         | Base at 3000000, on UPM B                                                            |

| OR4      |                                           | FFC00A00         | 4 MByte block size, all types access, initial address multiplexing according to AMB. |

MPC8XXFADS Design Specification—Rev 0.1 For More Information On This Product PRELIMINARY Goute: Www.freescale.com

|          | 1                           |                                                                         |                                                                                                                                                                                                                                                                                        |

|----------|-----------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register | Device Type                 | Init Value [hex]                                                        | Description                                                                                                                                                                                                                                                                            |

| MPTPR    | All Dram SIMMs<br>Supported | 0400                                                                    | Divide by 16 (decimal)                                                                                                                                                                                                                                                                 |

| MAMR     | MB321BT08TASN60             | 40A21114 <sup>a</sup><br>60A21114 <sup>b</sup><br>C0A21114 <sup>c</sup> | refresh clock divided by 40 <sup>a</sup> or 60 <sup>b</sup> or C0 <sup>c</sup> , periodic timer enabled, type 2 address multiplexing scheme, 1 cycle disable timer, GPL4 disabled for data sampling edge flexibility, 1 loop read, 1 loop write, 4 beats refresh burst.                |

|          | MB322BT08TASN60             | 20A21114 <sup>a</sup><br>30A21114 <sup>b</sup><br>60A21114 <sup>c</sup> | refresh clock divided by 20 <sup>a</sup> or 30 <sup>b</sup> or 60 <sup>c</sup> , periodic<br>timer<br>enabled, type 2 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 disabled for data sampling edge<br>flexibility, 1 loop read, 1 loop write, 4 beats refresh<br>burst. |

|          | MB324CT00TBSN60             | 40B21114 <sup>a</sup><br>60B21114 <sup>b</sup><br>C0B21114 <sup>c</sup> | refresh clock divided by 40 <sup>a</sup> or 60 <sup>b</sup> or C0 <sup>c</sup> , periodic<br>timer<br>enabled, type 3 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 disabled for data sampling edge<br>flexibility, 1 loop read, 1 loop write, 4 beats refresh<br>burst. |

|          | MB328CT00TBSN60             | 20B21114 <sup>a</sup><br>30B21114 <sup>b</sup><br>60B21114 <sup>c</sup> | refresh clock divided by 20 <sup>a</sup> or 30 <sup>b</sup> or 60 <sup>c</sup> , periodic<br>timer<br>enabled, type 3 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 disabled for data sampling edge<br>flexibility, 1 loop read, 1 loop write, 4 beats refresh<br>burst. |

| MBMR     | MB811171622A-100            | D0802114 <sup>c</sup><br>80802114 <sup>d</sup>                          | refresh clock divided by D0 or 80, periodic timer<br>enabled, type 0 address multiplexing scheme, 1 cycle<br>disable timer, GPL4enabled, 1 loop read, 1 loop write,<br>4 beats refresh burst.                                                                                          |

| TABLE 3-3. | Memory | Controller | Initializations | For 50Mhz |

|------------|--------|------------|-----------------|-----------|

|------------|--------|------------|-----------------|-----------|

a. Assuming 16.67 MHz BRGCLK.

b. Assuming 25MHz BRGCLK

c. For 50MHz BRGCLK

d. Assuming 32MHz BRGCLK.

| Cycle Type Single Read Bu |                     | Burst Read | Single Write | Burst Write | Refresh                | Exception |          |

|---------------------------|---------------------|------------|--------------|-------------|------------------------|-----------|----------|

| Offset in UPI             | in UPM 0 8 18 20 30 |            | 30           | 3C          |                        |           |          |

| Contents                  | 0                   | 8FFFEC24   | 8FFFEC24     | 8FAFCC24    | 8FAFCC24               | C0FFCC84  | 33FFCC07 |

| @ Offset +                | 1                   | 0FFFEC04   | 0FFFEC04     | 0FAFCC04    | 0FAFCC04               | 00FFCC04  | Х        |

|                           | 2                   | 0CFFEC04   | 08FFEC04     | 0CAFCC00    | 0CAFCC00               | 07FFCC04  | Х        |

|                           | 3                   | 00FFEC04   | 00FFEC0C     | 11BFCC47    | 03AFCC4C               | 3FFFCC06  | x        |

|                           | 4                   | 00FFEC00   | 03FFEC00     | Х           | 0CAFCC00               | FFFFCC85  |          |

|                           | 5                   | 37FFEC47   | 00FFEC44     | Х           | 03AFCC <mark>4C</mark> | FFFFCC05  |          |

|                           | 6                   | Х          | 00FFCC08     | Х           | 0CAFCC00               | X         |          |

|                           | 7                   | Х          | 0CFFCC44     | Х           | 03AFCC4C               | Х         |          |

|                           | 8                   |            | 00FFEC0C     |             | 0CAFCC00               | Х         |          |

|                           | 9                   |            | 03FFEC00     |             | 33BFCC4F               | Х         |          |

|                           | А                   |            | 00FFEC44     |             | X                      | Х         |          |

|                           | В                   |            | 00FFCC00     |             | х                      | Х         |          |

|                           | С                   |            | 3FFFC847     |             | Х                      |           |          |

|                           | D                   |            | x            |             | Х                      |           |          |

|                           | Е                   |            | ×            |             | Х                      |           |          |

|                           | F                   |            | X            |             | Х                      |           |          |

TABLE 3-4. UPMA Initializations for 60nsec DRAMs @ 50MHz

| Cycle Type    | ycle Type Single Read Burst Read Single Write Burs |          | Burst Write | Refresh  | Exception |          |          |

|---------------|----------------------------------------------------|----------|-------------|----------|-----------|----------|----------|

| Offset in UPI | И                                                  | 0        | 8           | 18       | 20        | 30       | 3C       |

| Contents      | 0                                                  | 8FFBEC24 | 8FFFEC24    | 8FFFCC24 | 8FFFCC24  | C0FFCC84 | 33FFCC07 |

| @ Offset +    | 1                                                  | 0FF3EC04 | 0FFBEC04    | 0FEFCC04 | 0FEFCC04  | 00FFCC04 | Х        |

|               | 2                                                  | 0CF3EC04 | 0CF3EC04    | 0CAFCC00 | 0CAFCC00  | 07FFCC04 | Х        |

|               | 3                                                  | 00F3EC04 | 00F3EC0C    | 11BFCC47 | 03AFCC4C  | 3FFFCC06 | X        |

|               | 4                                                  | 00F3EC00 | 0CF3EC00    | Х        | 0CAFCC00  | FFFFCC85 |          |

|               | 5                                                  | 37F7EC47 | 00F3EC4C    | Х        | 03AFCC4C  | FFFFCC05 |          |

|               | 6                                                  | Х        | 0CF3EC00    | Х        | 0CAFCC00  | х        |          |

|               | 7                                                  | Х        | 00F3EC4C    | Х        | 03AFCC4C  | X        |          |

|               | 8                                                  |          | 0CF3EC00    |          | 0CAFCC00  | Х        |          |

|               | 9                                                  |          | 00F3EC44    |          | 33BFCC4F  | Х        |          |

|               | А                                                  |          | 03F3EC00    |          | x         | Х        |          |

|               | В                                                  |          | 3FF7EC47    |          | X         | Х        |          |

|               | С                                                  |          | X           |          | х         |          |          |

|               | D                                                  |          | x           |          | Х         |          |          |

|               | Е                                                  |          | x           |          | Х         |          |          |

|               | F                                                  |          | X           |          | Х         |          |          |

|               |                                                    | ·        |             |          |           |          |          |

| TABLE 3-5. | UPMA Initializations for 60nsec EDO DRAMs @ 50MHz |

|------------|---------------------------------------------------|

|------------|---------------------------------------------------|

TABLE 3-6. Memory Controller Initializations For 20Mhz

| Register |             | Device Ty       | /pe   | Init Value [hex] | Description                                        |

|----------|-------------|-----------------|-------|------------------|----------------------------------------------------|

| BR0      | All<br>supp | Flash<br>orted. | SIMMs | 02200001         | Base at 2200000, 32 bit port size, no parity, GPCM |

| Register         | Device Type                    | Init Value [hex] | Description                                                                          |

|------------------|--------------------------------|------------------|--------------------------------------------------------------------------------------|

| OR0              | MCM29F020-90                   | FFE00D20         | 2MByte block size, all types access, CS early negate, 2 w.s.                         |

|                  | MCM29F040-90<br>SM732A1000A-9  | FFC00D20         | 4MByte block size, all types access, CS early negate, 2 w.s.                         |

|                  | MCM29F080-90<br>SM732A2000-9   | FF800920         | 8MByte block size, all types access, CS early negate, 2 w.s., Timing relax           |

|                  | MCM29F020-12                   | FFE00D30         | 2MByte block size, all types access, CS early negate, 3 w.s.                         |

|                  | MCM29F040-12<br>SM732A1000A-12 | FFC00D30         | 4MByte block size, all types access, CS early negate, 3 w.s.                         |

|                  | MCM29F080-12<br>SM732A2000-12  | FF800930         | 8MByte block size, all types access, CS early negate, 3 w.s.                         |

| BR1              | BCSR                           | 02100001         | Base at 2100000, 32 bit port size, no parity, GPCM                                   |

| OR1              |                                | FFFF8110         | 32 KByte block size, all types access, CS early negate, 1 w.s.                       |

| BR2              | All Dram SIMMs<br>Supported    | 00000081         | Base at 0, 32 bit port size, no parity, UPMA                                         |

| OR2              | MB321/2BT08TASN60              | FFC00800         | 4MByte block size, all types access, initial address multiplexing according to AMA.  |

|                  | MB324/8CT00TBSN60              | FF000800         | 16MByte block size, all types access, initial address multiplexing according to AMA. |

| BR3 <sup>a</sup> | MB322BT08TASN60                | 00400081         | Base at 400000, 32 bit port size, no parity, UPMA                                    |

|                  | MB328CT00TBSN60                | 01000081         | Base at 1000000, 32 bit port size, no parity, UPMA                                   |

| OR3              | MB322BT08TASN60                | FFC00800         | 4MByte block size, all types access, initial address multiplexing according to AMA   |

|                  | MB328CT00TBSN60                | FF000800         | 16MByte block size, all types access, initial address multiplexing according to AMA. |

| BR4              | MB811171622A-100               | 030000C1         | Base at 3000000, on UPM B.                                                           |

| OR4              |                                | FFC00A00         | 4MByte block size, all types access, initial address multiplexing according to AMB   |

| MPTPR            | All Dram SIMMs<br>Supported    | 0400             | Divide by 16 (decimal)                                                               |

# TABLE 3-6. Memory Controller Initializations For 20Mhz

| Register | Device Type      | Init Value [hex]      | Description                                                                                                                                                                                                                     |

|----------|------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAMR     | MB321BT08TASN60  | 60A21114              | refresh clock divided by 60, periodic timer enabled,<br>type 2 address multiplexing scheme, 1 cycle disable<br>timer, GPL4 disabled for data sampling edge flexibility,<br>1 loop read, 1 loop write, 4 beats refresh burst.    |

|          | MB322BT08TASN60  | 30A21114              | refresh clock divided by 30, periodic timer<br>enabled, type 2 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 disabled for data sampling edge<br>flexibility, 1 loop read, 1 loop write, 4 beats refresh<br>burst. |

|          | MB324CT00TBSN60  | 60B21114              | refresh clock divided by 60, periodic timer<br>enabled, type 3 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 disabled for data sampling edge<br>flexibility, 1 loop read, 1 loop write, 4 beats refresh<br>burst. |

|          | MB328CT00TBSN60  | 30B21114              | refresh clock divided by 30, periodic timer<br>enabled, type 3 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 disabled for data sampling edge<br>flexibility, 1 loop read, 1 loop write, 4 beats refresh<br>burst. |

| MBMR     | MB811171622A-100 | 42802114 <sup>b</sup> | refresh clock divided by 42, periodic timer enabled,<br>type 0 address multiplexing scheme, 1 cycle<br>disable timer, GPL4 enabled, 1 loop read, 1 loop write,<br>4 beats refresh burst.                                        |

| TABLE 3-6. Memory Controller Initializations For 20Mhz |

|--------------------------------------------------------|

|--------------------------------------------------------|

a. BR3 is not initialized for MB321xx or MB324xx EDO DRAM SIMMs.

b. Assuming 16.67MHz BRGCLK

| Cycle Type    |   | Single Read | Burst Read | Single Write | Burst Write | Refresh  | Exception |

|---------------|---|-------------|------------|--------------|-------------|----------|-----------|

| Offset in UPM |   | 0           | 8          | 18           | 20          | 30       | 3C        |

| Contents      | 0 | 8FFFCC04    | 8FFFCC04   | 8FEFCC00     | 8FEFCC00    | 80FFCC84 | 33FFCC07  |

| @ Offset +    | 1 | 08FFCC00    | 08FFCC08   | 39BFCC47     | 09AFCC48    | 17FFCC04 | Х         |

|               | 2 | 33FFCC47    | 08FFCC08   | Х            | 09AFCC48    | FFFFCC86 | Х         |

|               | 3 | Х           | 08FFCC08   | Х            | 09AFCC48    | FFFFCC05 | Х         |

|               | 4 | Х           | 08FFCC00   | Х            | 39BFCC47    | ×        |           |

|               | 5 | Х           | 3FFFCC47   | Х            | Х           | x        |           |

|               | 6 | Х           | Х          | Х            | X           | х        |           |

|               | 7 | Х           | Х          | Х            | X           | X        |           |

|               | 8 |             | Х          |              | х           | Х        |           |

|               | 9 |             | Х          |              | X           | Х        |           |

|               | А |             | Х          |              | x           | Х        |           |

|               | В |             | Х          |              | X           | Х        |           |

|               | С |             | X          |              | х           |          |           |

|               | D |             | Х          |              | Х           |          |           |

|               | Е |             | x          |              | Х           |          |           |

|               | F |             | X          |              | Х           |          |           |

|               |   |             |            |              |             |          |           |

# TABLE 3-7. UPMA Initializations for 60nsec EDO DRAMs @ 20MHz

|               |         |                       |            |              |             | •        |           |

|---------------|---------|-----------------------|------------|--------------|-------------|----------|-----------|

| Cycle Type    |         | Single Read           | Burst Read | Single Write | Burst Write | Refresh  | Exception |

| Offset In UPM |         | 0                     | 8          | 18           | 20          | 30       | 3C        |

| Contents      | 0       | 0126CC04              | 0026FC04   | 0E26BC04     | 0E26BC00    | 1FF5FC84 | 7FFFFC07  |

| @ Offset +    | 1       | 0FB98C00              | 10ADFC00   | 01B93C00     | 10AD7C00    | FFFFFC04 | Х         |

|               | 2       | 1FF74C47              | F0AFFC00   | 1FF77C47     | F0AFFC00    | FFFFFC84 | Х         |

|               | 3       | Х                     | F1AFFC00   | Х            | F0AFFC00    | FFFFFC07 | Х         |

|               | 4       | Х                     | EFBBBC00   | Х            | E1BBBC04    | ×        |           |

|               | 5       | 1FE77C34 <sup>a</sup> | 1FF77C47   | Х            | 1FF77C47    | ×        |           |

|               | 6       | EFAABC34              | Х          | Х            | X           | х        |           |

|               | 7       | 1FA57C35              | Х          | Х            | X           | X        |           |

|               | 8       |                       | Х          |              | х           | Х        |           |

|               | 9       |                       | Х          |              | X           | Х        |           |

|               | А       |                       | Х          |              | x           | Х        |           |

|               | В       |                       | Х          |              | X           | Х        |           |

|               | С       |                       | X          |              | х           |          |           |

|               | D       |                       | Х          |              | Х           |          |           |

|               | Е       |                       | X          |              | Х           |          |           |

|               | F       |                       | X          |              | Х           |          |           |

|               | · · · · |                       |            |              | •           |          |           |

a. MRS initialization. Uses Free space.

| Cycle Type    |   | Single Read           | Burst Read | Single Write | Burst Write            | Refresh  | Exception |

|---------------|---|-----------------------|------------|--------------|------------------------|----------|-----------|

| Offset In UPM |   | 0                     | 8          | 18           | 20                     | 30       | 3C        |

| Contents      | 0 | 1F07FC04              | 1F07FC04   | 1F27FC04     | 1F07FC04               | 1FF5FC84 | 7FFFFC07  |

| @ Offset +    | 1 | EEAEFC04              | EEAEFC04   | EEAEBC00     | EEAEBC00               | FFFFFC04 | Х         |

|               | 2 | 11ADFC04              | 10ADFC04   | 01B93C04     | 10AD7C00               | FFFFFC04 | Х         |

|               | 3 | EFBBBC00              | F0AFFC00   | 1FF77C47     | F0AFFC00               | FFFFFC04 | Х         |

|               | 4 | 1FF77C47              | F0AFFC00   | Х            | F0AFFC00               | FFFFFC84 |           |

|               | 5 | 1FF77C34 <sup>a</sup> | F1AFFC00   | Х            | E1BBBC04               | FFFFFC07 |           |

|               | 6 | EFEABC34              | EFBBBC00   | Х            | 1FF77C <mark>47</mark> | х        |           |

|               | 7 | 1FB57C35              | 1FF77C47   | Х            | X                      | X        |           |

|               | 8 |                       | Х          |              | Х                      | Х        |           |

|               | 9 |                       | Х          |              | X                      | Х        |           |

|               | А |                       | Х          |              | x                      | Х        |           |

|               | В |                       | Х          |              | X                      | Х        |           |

|               | С |                       | X          |              | х                      |          |           |

|               | D |                       | Х          |              | Х                      |          |           |

|               | Е |                       | x          |              | Х                      |          |           |

|               | F |                       | X          |              | Х                      |          |           |

|               | • |                       |            |              |                        |          |           |

# TABLE 3-9. UPMB Initializations for MB811171622A-100, 32+MHz - 50MHz

a. MRS initialization, Uses free space.

# 4 - Functional Description

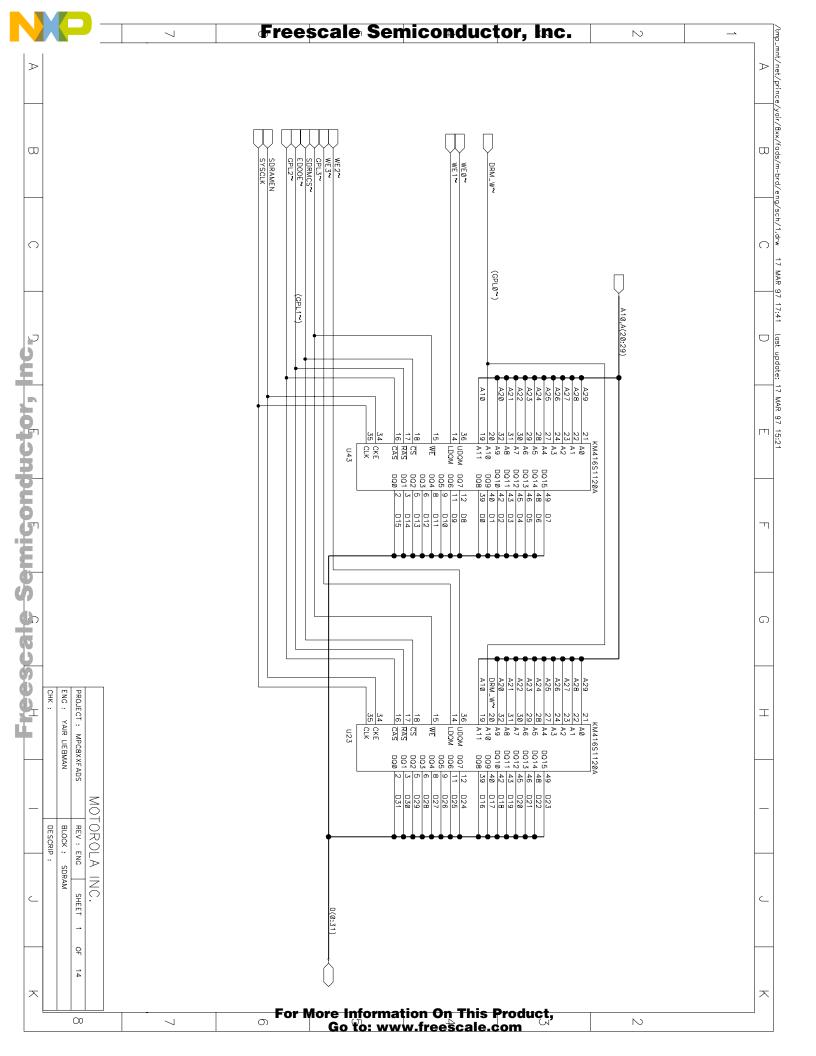

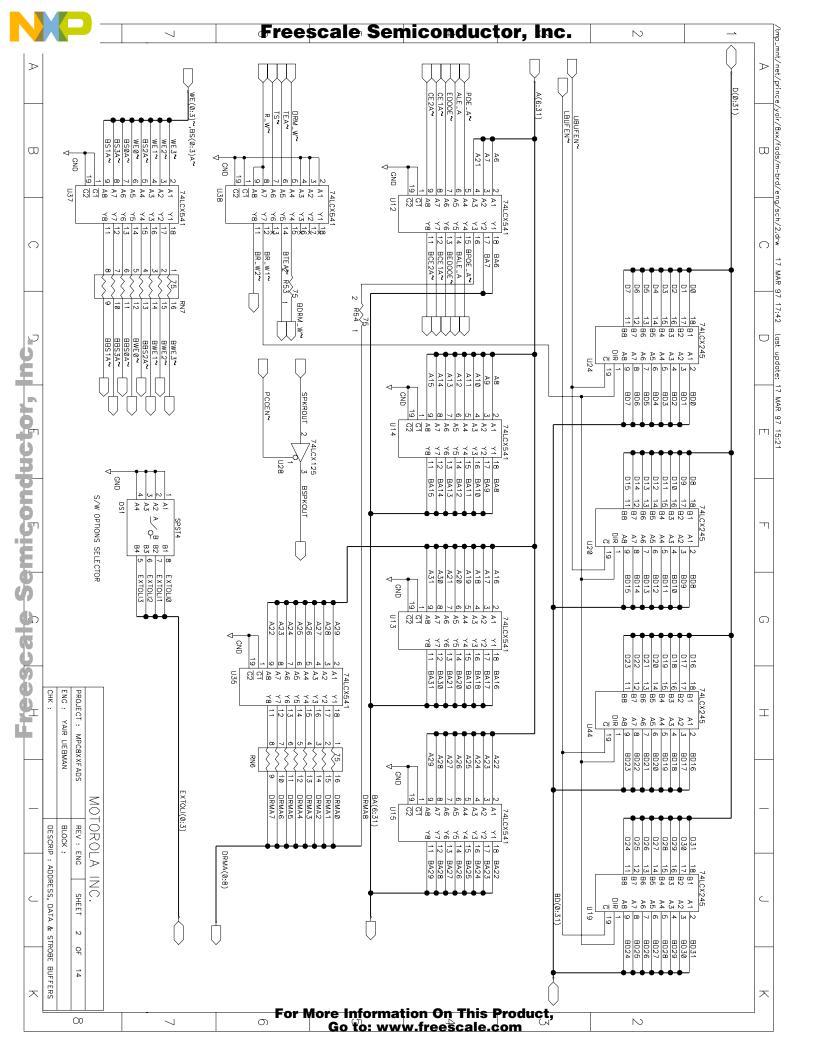

In this chapter the various modules combining the MPC8XXFADS are described to their design details.

# 4•1 Reset & Reset - Configuration

There are several reset sources on the FADS:

- 1) Keep Alive Power-On Reset<sup>A</sup>

- 2) Regular Power On Reset

- 3) Manual Soft-Reset

- 4) Manual Hard-Reset

- 5) MPC Internal Sources. (See the appropriate Spec or U/M)

#### 4•1•1 Keep Alive Power-On Reset

The Keep Alive Power - On Reset logic resides on the daughter board this since the Keep Alive power bus is on that board and it also allows the use of the daughter board connected directly to a user's application.

### 4•1•2 Regular Power - On Reset

The regular power on reset operates in the same manner as the keep alive power-on reset, using a similar device - the Seiko - S-8052ANY-NH-X with detection voltage of 2.595V to 2.805V. The reference voltage of this device is the MAIN VDDH bus of the MPC while the reset line asserted<sup>B</sup>, is the HRESET\* line.

When HRESET~ is asserted to the MPC, Hard-Reset configuration is made available to the MPC, via BCSR0. See 4•1•6•2 "Hard Reset Configuration" on page 29 and TABLE 4-9. "BCSR0 Description" on page 46.

# 4•1•3 Manual Soft Reset

To support application development not around the debug port and resident debuggers, a soft reset push-button is provided. (SW2) Depressing that button, asserts the SRESET\* pin of the MPC, generating a SOFT RESET sequence.

When the SRESET line is asserted to the MPC, the Soft-Reset configuration is made available to the MPC, by the debug-port controller. See 4•1•6•3 "Soft Reset Configuration" on page 29.

# 4•1•4 Manual Hard Reset

To support application development not around the debug port, a Hard-Reset push-button is provided<sup>C</sup>. When the Soft Reset push-button (SW2) is depressed in conjunction with the ABORT pushbutton (SW1), the HRESET\* line is asserted, generating a HARD RESET sequence. The button sharing is for economy and board space saving and does not effect in any way, functionality.

#### 4•1•5 MPC Internal Sources

Since the HRESET\* and SRESET\* lines of the MPC are open-drain and the on-board reset logic drives these lines with open-drain gates, the correct operation of the internal reset sources of the MPC is facilitated. As a rule, an internal reset source asserts HRESET\* and / or SRESET\* for a minimum time of 512 system clocks. It is beyond the scope of this document to describe these sources, however Debug-Port Soft / Hard Resets which are part of the development system<sup>D</sup>, are

DS Design Specific

OUT NOTICE

A. In fact generated on the daughter board.

B. Again not directly.

C. It is not a dedicated button.

regarded as such.

#### 4•1•6 Reset Configuration

During reset the MPC device samples the state of some external pins to determine its operation modes and pin configuration. There are 3 kinds of reset levels to the MPC each level having its own configuration sampled:

- 1) Power On Reset configuration

- 2) Hard Reset configuration

- 3) Soft Reset Configuration.

#### 4•1•6•1 Power - On Reset Configuration

Just before PORESET\* is negated by the external logic, the power-on reset configuration which include the MODCK(1:2) pins is sampled. These pins determine the clock operation mode of the MPC. Two clock modes are supported on the MPC8XXFADS:

1) 1:5 PLL operation via on-board clock generator.

In this mode MODCK(1:2) are driven with '11' during<sup>A</sup> power on reset.

2) 1:513 PLL operation via on-board clock generator.

In this mode MODCK(1:2) are driven with '00'. during power-on reset.

#### 4•1•6•2 Hard Reset Configuration

During HARD reset sequence, when RSTCONF\* pin is asserted, the MPC data bus state is sampled to acquire the MPC's hard reset configuration. The reset configuration word is driven by BCSR0 register, defaults of which are set during power-on reset. The BCSR0 drives half of the configuration word, i.e., data bits D(0:15) in which the reserved bits are designated RSRVxx. If the hard-reset configuration is to be changed<sup>B</sup>, BCSR0 may be written with new values, which become valid after HARD reset is applied to the MPC.

On the FADS, the RSTCONF\* line is always driven during HARD reset, i.e., no use is possible with the MPC's internal HARD reset configuration defaults.

The system parameters to which BCSR0 defaults during power-on reset and are driven at hard-reset, are listed below:

- 1) Arbitration: internal arbitration is selected.

- 2) Interrupt Prefix: The internal default is interrupt prefix at 0xFFF00000. It is overridden to provide interrupt prefix at address 0, which is located within the DRAM.

- 3) Boot Disable: Boot is enabled.

- 4) Boot Port Size: 32 bit boot port size is selected.

- 5) Initial Internal Space Base: Immediately after HARD reset, the internal space is located at \$FF000000.

- 6) Debug pins configuration: PCMCIA port B<sup>C</sup> pins become PCMCIA port B pins.

- 7) Debug port pins configuration. Debug port pins are on the JTAG port.

- 8) External Bus Division Factor: 1:1 internal to external clocks' frequencies ratio is selected.

#### 4•1•6•3 Soft Reset Configuration

The rising edge of SRESET\* is used to configure the development port. Before the negation of SRESET\*, DSCK<sup>D</sup> is sampled to determine for debug-mode enable / disable. After SRESET\* is

D. And therefore mentioned.

A. The MODCK lines are in fact driven longer - by HRESET~ line.

B. With respect the FADS's power-on defaults.

C. Where they exist.

negated, if debug mode was enabled, DSCK is sampled again for debug-mode entry / non-entry.

DSDI is used to determine the debug port clock mode and is sampled after the negation of SRESET\*.

The Soft Reset configuration is provided by the debug-port controller via the ADI I/F. Option is given to enter debug mode directly or only after exception.

# 4•2 Local Interrupter

The only external interrupt which is applied to the MPC via its interrupt controller is the ABORT (NMI), which is generated by a push-button. When this button is depressed, the NMI input to the MPC is asserted. The purpose of this type of interrupt, is to support the use of resident debuggers if any is made available to the FADS. All other interrupts to the MPC, are generated internally by the MPC's peripherals and by the debug port.

To support external (off-board) generation of an NMI, the IRQ0\* line which is routed as an NMI input, is driven by an open-drain gate. This allows for external h/w to also drive this line. If an external h/w indeed does so, it is compulsory that IRQ0\* is driven by an open-drain (or open-collector) gate.

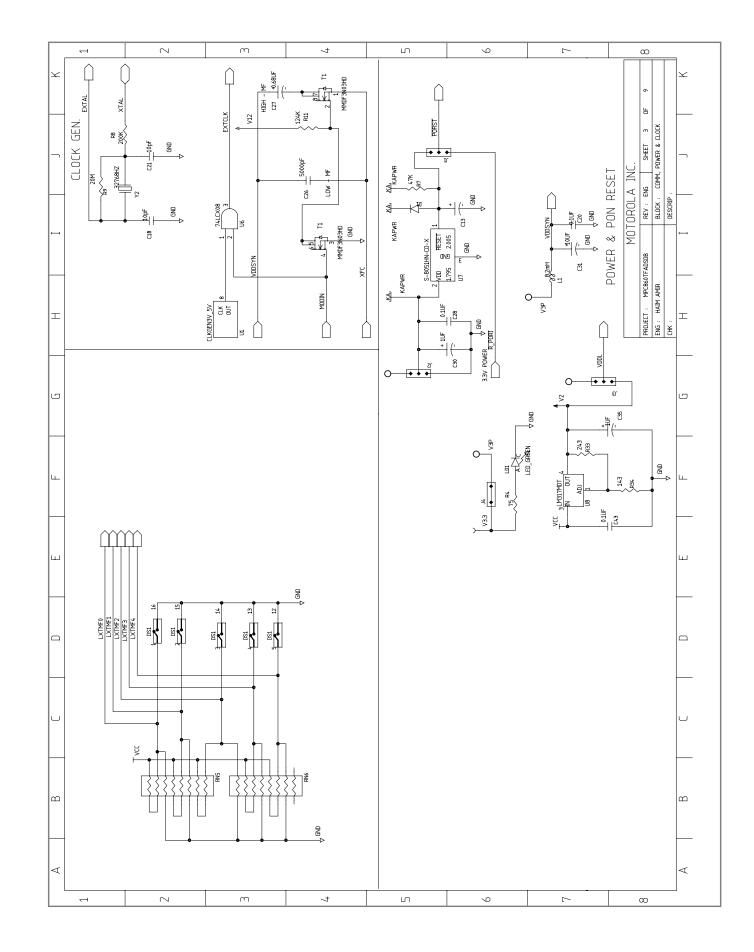

# 4•3 Clock Generator<sup>A</sup>

There are 2 ways to clock the MPC on the MPC8XXFADS:

- 1) 3 5MHz Clock generator<sup>B</sup> connected to CLK4IN input. 1:5 PLL mode.

- 2) 32.768 KHz crystal resonator<sup>B</sup> via EXTAL-XTAL pair of the MPC, 1:513 initial PLL multiplication factor.

The selection between the above modes is done using Dip-switch (DS2 / 4) with dual functionality: it is responsible to the combination driven to the MODCK lines during power-on reset and to the connection of the appropriate capacitor between MPC's XFC and VDDSYN lines to match the PLL's multiplication factor. When 1:5 mode is selected, a capacitor of 5nF is connected, while when 1:513 mode is selected a  $0.68\mu$ F capacitor is connected parallel to it via a TMOS gate. The capacitors' values are calculated to support a wider range of multiplication factors as possible.

When mode (2) above is selected, the output of the clock generator is gated from EXTCLK input and driven to '0' constantly so that a jitter-free system clock is generated.

On-board logic is clocked by the MPC's CLKOUT coming from the Daughter board. This clock is multiplexed with the debug port's clock generator, so that on-board logic is always clocked, even when the MPC is removed from its socket<sup>C</sup>.

# 4•4 Buffering

As the FADS meant to serve also as a hardware development platform, it is necessary to buffer the MPC from the local bus, so the MPC's capacitive drive capability is not wasted internally and remains available for user's off-board applications via the expansion connectors.

Buffers are provided for address and strobe<sup>D</sup> lines while transceivers are provided for data. Since the capacitive load over dram's address lines might<sup>E</sup> exceed 200 pF, the dram address lines are separately buffered. Use is done with 74LCX buffers which are 3.3V operated and are 5V tolerant. This

DS Design Specific

OUT NOTICE

D. DSCK is configured at hard-reset to reside on the JTAG port.

A. Although this module resides on the DAUGHTER boards, it is described here, as it is common to all MPC8XX supported.

B. Located On the Daughter Board.

C. When the FADS serves a debug station for target system.

D. If necessary.

E. Depended on dram SIMM's internal structure.

type of buffers reduces noise on board due to reduced transitions' amplitude.

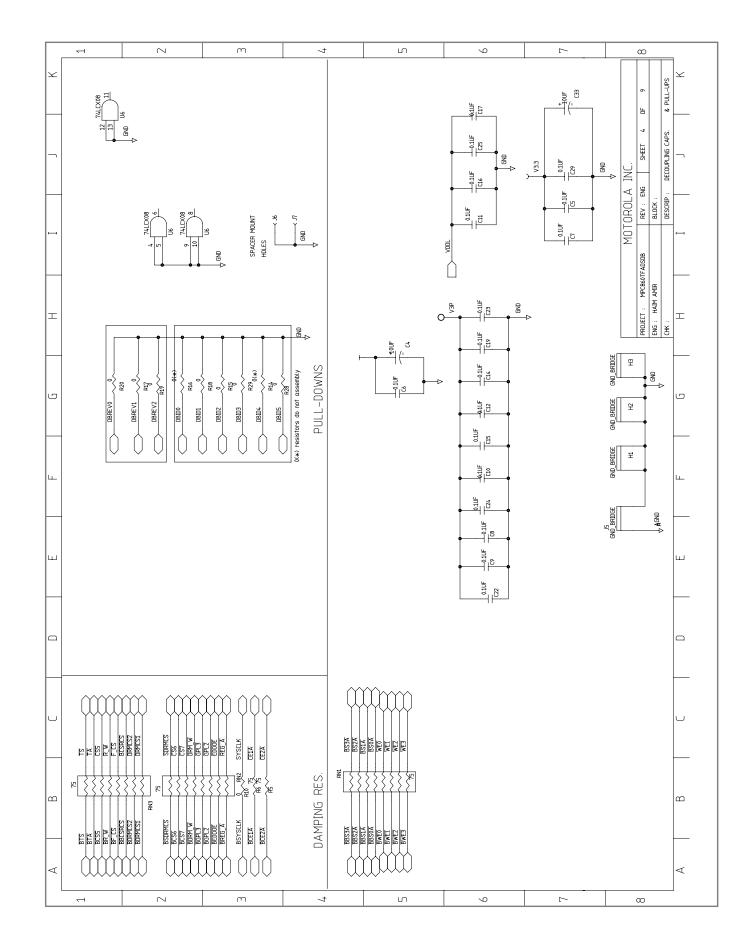

To further reduce noise and reflections, series resistors are placed over dram's address and strobe lines.

The data transceivers open only if there is an access to a valid<sup>A B</sup> board address or during Hard -Reset configuration<sup>C</sup>. That way data conflicts are avoided in case an off-board memory is read, provided that it is not mapped to an address valid on board. It is the users' responsibility to avoid such errors.

# 4•5 Chip - Select Generator

The memory controller of the MPC is used as a chip-select generator to access on-board<sup>D</sup> memories, saving board's area reducing cost, power consumption and increasing flexibility. To enhance off-board application development, memory modules (including the BCSRx) may be disabled via BCSR1<sup>E</sup> in favor of an external memory connected via the expansion connectors. That way, a CS line may be used off-board via the expansion connectors, while its associated local memory is disabled.

When a CS region is disabled via BCSR1, the local data transceivers do not open during access to that region, avoiding possible<sup>F</sup> contention over data lines.

The MPC's chip-selects assignment to the various memories / registers on the FADS are as shown in TABLE 4-1. "MPC8XXFADS Chip Selects' Assignment" below:

| Chip Select:  | Assignment               |

|---------------|--------------------------|

| CS0*          | Flash Memory             |

| CS1*          | BCSR                     |

| CS2*          | DRAM Bank 1              |

| CS3*          | DRAM Bank 2 <sup>a</sup> |

| CS4*          | SDRAM                    |

| CS(5-7)*      | Unused, user available   |

| a. If exists. | ,                        |

# TABLE 4-1. MPC8XXFADS Chip Selects' Assignment

# 4•6 DRAM

The MPC8XXFADS is provided with 4 MBytes of 60nsec delay EDO Dram SIMM. Support is given to any 5V powered FPM / EDO Dram SIMM configured as 1M X32 upto 2 X 4M X 32, with 60 nsec or 70nsec delay.

All dram configurations are supported via the Board Control & Status Register (BCSR), i.e., DRAM size (4M to 32M) and delay (60 / 70 nsec) are read from BCSR2 and the associated registers (includ-

A. An address which covered in a Chip-Select region.

B. Except for SDRAM, which is Unbuffered.

C. To allow a configuration word stored in Flash memory become active.

D. And off-board. See further.

E. After the BCSR is removed from the local memory map, there is no way to access it but to re-apply power to the FADS.

F. During read cycles.

ing the UPM) are programmed accordingly.

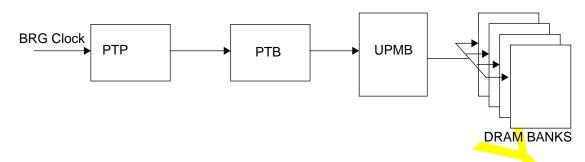

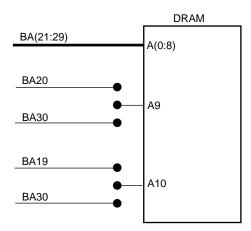

Dram timing control is performed by UPMA of the MPC via CS2 (and CS3 for a dual-bank SIMM) region(s), i.e., RAS and CAS signals' generation, during normal<sup>A</sup> access as well as during refresh cycles and the necessary address multiplexing<sup>B</sup> are performed using UPMA. CS2\* and CS3\* signals are buffered from the DRAM and each is split to 2 to overcome the capacitive load over the Dram SIMM RAS lines.

The DRAM module may enabled / disabled at any time by writing the DRAMEN~ bit in BCSR1. See TABLE 4-10. "BCSR1 Description" on page 48.

#### 4•6•1 DRAM 16 Bit Operation

To enhance evaluation capabilities, support is given to Dram with 16-bit and 32-bit data bus width. That way users can tailor dram configuration, to get best fit to their application requirements. When the DRAM is in 16 bit mode, half of it can not be used, i.e., the memory portion that is connected to data lines D(16:31).

To configure the DRAM for 16 bit data bus width operation, the following steps should be taken:

- 1) Set the Dram\_Half\_Word bit in BCSR1 to Half-Word. See TABLE 4-10. "BCSR1 Description" on page 48

- 2) The Port Size bits of BR2~ (and of BR3~ for a 2-bank DRAM simm) should be set to 16 bits.

- 3) The AM bits in OR2 register should be set to **1/2** of the nominal single-bank DRAM simm volume or to **1/4** of the nominal **dual-bank** DRAM simm volume.

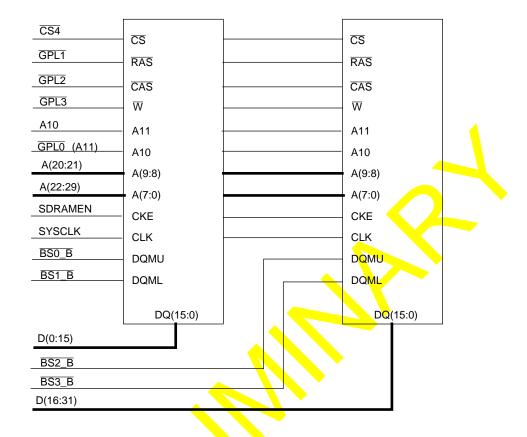

If a Dual-Bank DRAM simm is being used: