#

# Low-Power, 16-Bit Multichannel DAS with Internal Reference,10-Bit DACs, and RTC

## **General Description**

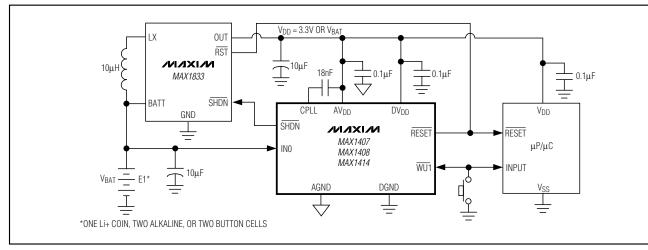

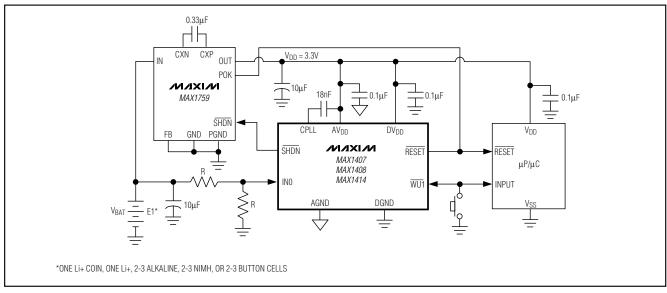

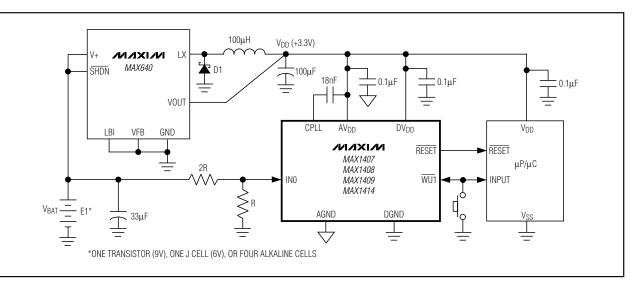

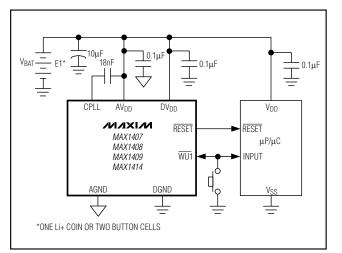

The MAX1407/MAX1408/MAX1409/MAX1414 are lowpower, general-purpose, multichannel data-acquisition systems (DAS). These devices are optimized for lowpower applications. All the devices operate from a single +2.7V to +3.6V power supply and consume a maximum of 1.15mA in Run mode and only 2.5 $\mu$ A in Sleep mode.

The MAX1407/MAX1408/MAX1414 feature a differential 8:1 input multiplexer to the ADC, a programmable three-state digital output, an output to shutdown an external power supply, and a data ready output from the ADC. The MAX1408 has eight auxiliary analog inputs, while the MAX1407/MAX1414 include four auxiliary analog inputs and two 10-bit force/sense DACs. The MAX1414 features a 50mV trip threshold for the signal-detect comparator while the others have a 0mV trip threshold. The MAX1409 is a 20-pin version of the DAS family with a differential 4:1 input multiplexer to the ADC, one auxiliary analog input, and one 10-bit force/sense DAC.

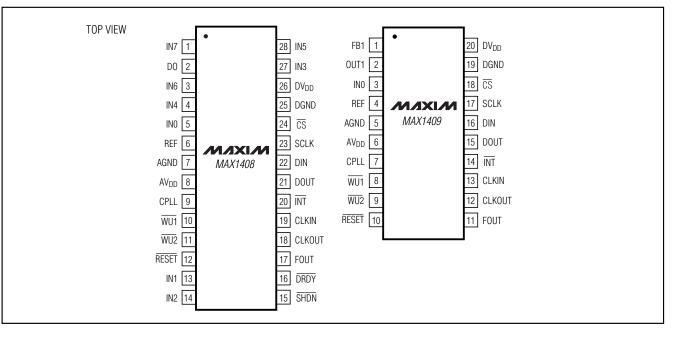

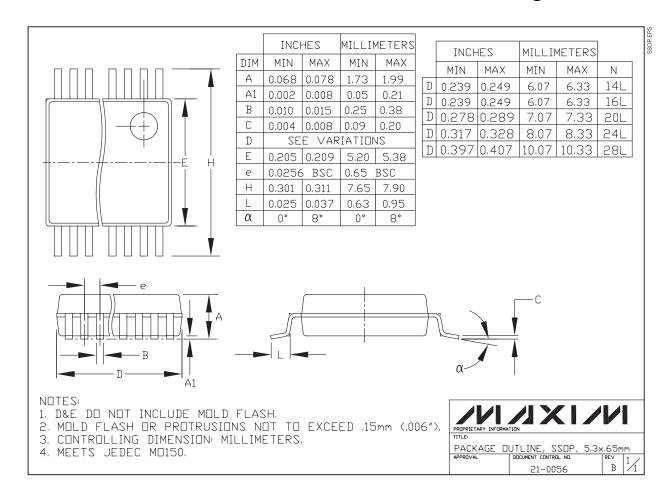

The MAX1407/MAX1408/MAX1414 are available in space-saving 28-pin SSOP packages, while the MAX1409 is available in a 20-pin SSOP package.

## **Applications**

- Medical Instruments

- Industrial Control Systems

- Portable Equipment

- Data-Acquisition System

- Automatic Testing

- Robotics

#### Pin Configurations TOP VIEW FB2 1 28 OUT2 D0 2 27 IN3 FB1 3 26 DV<sub>DD</sub> OUT1 4 25 DGND 24 <u>CS</u> INO 5 REF 6 23 SCLK MIXIM 22 DIN AGND 7 MAX1407 MAX1414 AV<sub>DD</sub> 8 21 DOUT 20 INT CPLL 9 WU1 10 19 CLKIN 18 CLKOUT WU2 11 RESET 12 17 FOUT 16 DRDY IN1 13 15 SHDN IN2 14

##

## \_Features

- +2.7V to +3.6V Supply Voltage Range in Standby, Idle, and Run Mode (Down to 1.8V in Sleep Mode)

- 1.15mA Run Mode Supply Current

- 2.5µA Sleep Mode Supply Current (Wake-Up, RTC, and Voltage Monitor Active)

- Multichannel 16-Bit Sigma-Delta ADC ±1.5 LSB (typ) Integral Nonlinearity 30Hz or 60Hz Continuous Conversion Rate Buffered or Unbuffered Mode Gain of +1/3, +1, or +2V/V Unipolar or Bipolar Mode On-Chip Offset Calibration

- ♦ 10-Bit Force/Sense DACs

- Buffered 1.25V, 18ppm/°C (typ) Bandgap Reference Output

- ♦ SPI™/QSPI™ or MICROWIRE™-Compatible Serial Interface

- System Support Functions RTC (Valid til 9999) and Alarm High-Frequency <u>PLL Clock Output (2.4576MHz)</u> +1.8V and +2.7V RESET and Power-Supply Voltage Monitors Signal Detect Comparator Interrupt Generator (INT and DRDY) Three-State Digital Output Wake-Up Circuitry

- 28-Pin SSOP (MAX1407/MAX1408/MAX1414), 20-Pin SSOP (MAX1409)

## **Ordering Information**

| PART       | TEMP. RANGE  | PIN-PACKAGE |

|------------|--------------|-------------|

| MAX1407CAI | 0°C to +70°C | 28 SSOP     |

| MAX1408CAI | 0°C to +70°C | 28 SSOP     |

| MAX1409CAP | 0°C to +70°C | 20 SSOP     |

| MAX1414CAI | 0°C to +70°C | 28 SSOP     |

#### Pin Configurations continued at end of data sheet. Typical Operating Circuit appears at end of data sheet.

SPI and QSPI are trademarks of Motorola, Inc. MICROWIRE is a trademark of National Semiconductor Corp.

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| AVDD to AGND                           | 0.3V to +6V                 |

|----------------------------------------|-----------------------------|

| AV <sub>DD</sub> to DV <sub>DD</sub>   | 0.3V to +0.3V               |

| Analog Inputs to AGND                  | 0.3V to $+(AV_{DD} + 0.3V)$ |

| Digital Inputs to DGND                 | 0.3V to +6V                 |

| Maximum Current Input Into Any Pin     | 50mA                        |

| Continuous Power Dissipation ( $T_A =$ | +70°C)                      |

| 20-Pin SSOP (derate 8.0mW/°C ab        | ove +70°C)640mW             |

| 28-Pin SSOP (derate 9.52mW/°C a        | bove +70°C)762mW            |

| DV <sub>DD</sub> to DGND               | 0.3V to +6V                 |

| AGND to DGND                           | 0.3V to +0.3V               |

| Analog Outputs to AGND            | 0.3V to +(AV <sub>DD</sub> + 0.3V) |

|-----------------------------------|------------------------------------|

| Digital Outputs to DGND           | $0.3V$ to $+(AV_{DD} + 0.3V)$      |

| REF to AGND                       | $0.3V$ to $+(AV_{DD} + 0.3V)$      |

| Operating Temperature Range:      |                                    |

| MAX14_CA                          | 0°C to +70°C                       |

| MAX14EA                           | 40°C to +85°C                      |

| Lead Temperature (soldering, 10s) | +300 °C                            |

| Storage Temperature Range         | 65°C to +150°C                     |

| Junction Temperature              | +150°C                             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

$(DV_{DD} = AV_{DD} = +2.7V \text{ to } 3.6V, 4.7\mu\text{F} \text{ at REF}, \text{ internal } V_{REF}, 18n\text{F} \text{ between CPLL and } AV_{DD}, 32.768\text{kHz crystal across CLKIN and CLKOUT, } T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.)$

| PARAMETER                     | SYMBOL | CON                                                   | DITIONS                                                 | MIN  | ТҮР   | MAX | UNITS    |

|-------------------------------|--------|-------------------------------------------------------|---------------------------------------------------------|------|-------|-----|----------|

| ADC ACCURACY                  |        |                                                       |                                                         |      |       |     |          |

| Resolution (No Missing Codes) | RES    |                                                       |                                                         | 16   |       |     | Bits     |

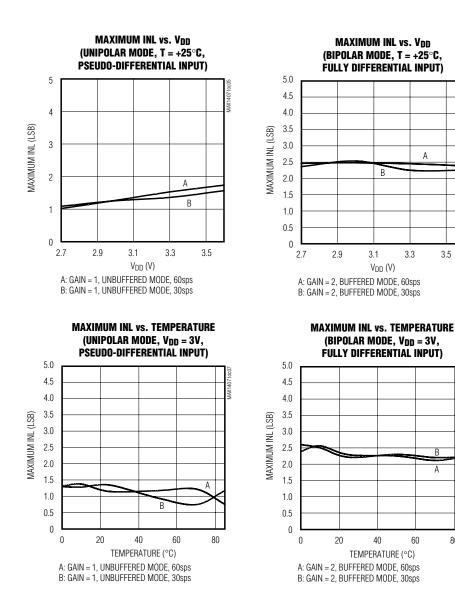

|                               |        |                                                       | Jnipolar mode, gain = 1,<br>differential input (Note 7) |      | 1.5   | 3.5 |          |

| late and Marchine and         |        |                                                       | Jnipolar mode, gain = 2,<br>udo-differential input      |      | 1.75  |     |          |

| Integral Nonlinearity         | INL    | Unbuffered mode, I<br>V <sub>NEG</sub> = 0.625V, full |                                                         | 1.70 |       | LSB |          |

|                               |        | Buffered mode, Bip<br>V <sub>NEG</sub> = 0.625V, full |                                                         | 2.50 |       |     |          |

|                               |        | Unipolar                                              | Gain = 2                                                |      | ±5    |     |          |

|                               |        |                                                       | Gain = 1                                                |      | ±10   |     |          |

| Output RMS Noise (Note 1)     |        |                                                       | Gain = 1/3                                              |      | ±30   |     |          |

| Output hims hoise (hote 1)    |        |                                                       | Gain = 2                                                |      | ±8    |     | μVrms    |

|                               |        | Bipolar Mode                                          | Gain = 1                                                |      | ±16.5 |     |          |

|                               |        |                                                       | Gain = 1/3                                              |      | ±48.5 |     |          |

| Offset Error                  |        | On-chip calibration                                   | n removes this error                                    |      |       | ±1  | % of FSR |

| Offset Drift                  |        |                                                       |                                                         |      | ±0.5  |     | µV/°C    |

| Gain Error                    |        | Excludes offset an                                    | d reference errors                                      |      |       | ±1  | % of FSR |

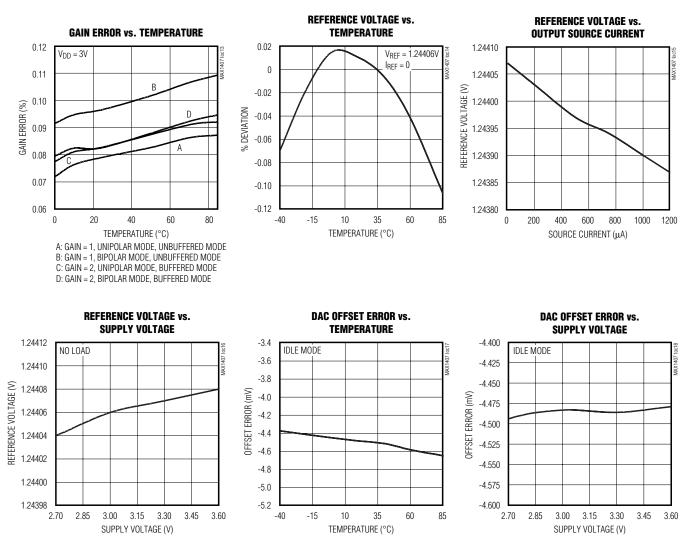

| Gain Drift                    |        | Excludes offset an                                    | d reference errors                                      |      | ±1    |     | ppm/°C   |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V$  to 3.6V, 4.7µF at REF, internal V<sub>REF</sub>, 18nF between CPLL and AV<sub>DD</sub>, 32.768kHz crystal across CLKIN and CLKOUT, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                  | SYMBOL | CONDIT                   | IONS                  | MIN               | ТҮР    | MAX                | UNITS |  |

|------------------------------------------------------------|--------|--------------------------|-----------------------|-------------------|--------|--------------------|-------|--|

|                                                            |        |                          |                       |                   | 1/3    |                    |       |  |

| PGA Gain                                                   |        | See PGA Gain section     |                       |                   | 1      |                    | V/V   |  |

|                                                            |        |                          |                       |                   | 2      |                    |       |  |

| Power-Supply Rejection Ratio                               |        | Gain = 1, unipolar and   | d buffered mode       |                   | 70     |                    | dB    |  |

| Output Lindata Data                                        |        | Continuous               | RATE bit = 0          |                   | 30     |                    |       |  |

| Output Update Rate                                         |        | conversion               | RATE bit = 1          |                   | 60     |                    | Hz    |  |

| Turn-On Time                                               |        | Excluding reference      |                       |                   | 50     |                    | μs    |  |

| SIGNAL DETECT COMPARATO                                    | DR     |                          |                       |                   |        |                    |       |  |

| Differential Input-Detection                               |        | MAX1407/MAX1408/         | /AX1409               | -10               | 0      | 10                 |       |  |

| Threshold Voltage                                          |        | MAX1414                  |                       | 44                | 50     | 56                 | mV    |  |

| Common-Mode Input Voltage                                  |        |                          |                       | 0                 |        | 0.8                | V     |  |

| Turn-On Time                                               |        |                          |                       |                   | 10     |                    | μs    |  |

| ANALOG INPUTS                                              | ·      |                          |                       | •                 |        |                    | ·     |  |

|                                                            |        |                          | ADC gain = 1          | 0                 |        | VREF               |       |  |

|                                                            |        | Unipolar mode            | ADC gain = 2          | 0                 |        | V <sub>REF/2</sub> |       |  |

| Differential Input Voltage Range                           |        |                          | ADC gain = 1/3        | 0                 |        | AVDD               |       |  |

|                                                            |        |                          | ADC gain = 1          | -V <sub>REF</sub> |        | VREF               |       |  |

|                                                            |        | Bipolar mode             | ADC gain = 2          | -VREF/2           |        | V <sub>REF/2</sub> |       |  |

|                                                            |        |                          | ADC gain = $1/3$      | -AV <sub>DD</sub> |        | AVDD               |       |  |

|                                                            |        | Unbuffered               |                       | -0.05             |        | AV <sub>DD</sub>   |       |  |

| Absolute Input Voltage Range                               |        | Buffered                 |                       | 0.05              |        | 1.40               | V     |  |

| Common-Mode Input Voltage                                  |        | Unbuffered               |                       | AGND              |        | AV <sub>DD</sub>   |       |  |

| Range                                                      |        | Buffered                 |                       | 0.05              |        | 1.40               | V     |  |

| Common-Mode Rejection Ratio                                |        | Gain = 1, unipolar an    | d buffered mode       |                   | 90     |                    | dB    |  |

|                                                            |        |                          | 30Hz data rate        |                   | 15.360 |                    |       |  |

| Input Sampling Rate                                        |        | FOUT = 2.4576MHz         | 60Hz data rate        |                   | 30.720 |                    | kHz   |  |

| Input Current                                              |        | Buffered mode            |                       |                   | ±0.5   |                    | nA    |  |

| Input Capacitance                                          |        |                          |                       |                   | 15     |                    | pF    |  |

| FORCE-SENSE DAC (all measur<br>(MAX1407/MAX1409/MAX1414 or |        | th FB1(2) shorted to OU1 | [1(2), unless otherwi | se noted).        |        |                    |       |  |

| Resolution                                                 |        |                          |                       | 10                |        |                    | Bits  |  |

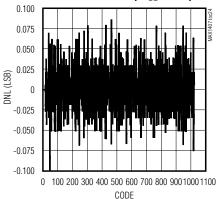

| Differential Nonlinearity                                  |        | Guaranteed monoton       | ic (Note 2)           |                   |        | ±1.0               | LSB   |  |

| Integral Nonlinearity                                      |        | (Note 2)                 |                       |                   |        | ±1.0               | LSB   |  |

| Offset Error                                               |        | (Note 3)                 |                       |                   |        | ±20                | mV    |  |

| Offset Drift                                               |        |                          |                       |                   | ±5     |                    | μV/°C |  |

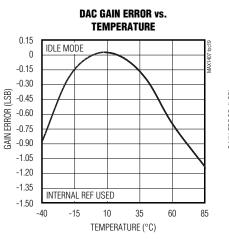

| Gain Error                                                 |        | Excludes offset and re   | eference drift        |                   |        | 3.6                | mV    |  |

| Gain Drift                                                 |        | Excludes offset and re   | eference drift        |                   | 10     |                    | ppm/° |  |

| Line Regulation                                            |        |                          |                       |                   | 190    |                    | μV/V  |  |

| Current into FB1(2)                                        |        |                          |                       | 1                 | ±0.5   |                    | nA    |  |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V$  to 3.6V, 4.7µF at REF, internal V<sub>REF</sub>, 18nF between CPLL and AV<sub>DD</sub>, 32.768kHz crystal across CLKIN and CLKOUT, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                       | SYMBOL                           | CO                                                            | NDITIONS                                                                                     | MIN   | ТҮР        | MAX                       | UNITS  |

|-------------------------------------------------|----------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------|------------|---------------------------|--------|

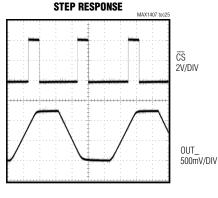

| Output Slew Rate                                |                                  | 010hex to 3FFhe<br>code swing, R <sub>L</sub> =               |                                                                                              | 18.0  |            | V/ms                      |        |

| Output Settling Time                            |                                  | scale with code                                               | 10-bit accuracy) of full-<br>transition from 010hex<br>12k $\Omega$ , C <sub>L</sub> = 200pF |       | 65         |                           | μs     |

| Turn-On Time                                    |                                  |                                                               |                                                                                              |       | 100        |                           | μs     |

| OUT1, OUT2 Output Range                         |                                  | No Load (Note 4                                               | .)                                                                                           | 0.05  |            | AV <sub>DD</sub><br>- 0.2 | V      |

| EXTERNAL REFERENCE (inter                       | nal reference po                 | wered down)                                                   |                                                                                              | •     |            |                           |        |

| Input Voltage Range                             |                                  |                                                               |                                                                                              |       | 1.25 ±0.10 | C                         | V      |

| Input Resistance                                |                                  |                                                               |                                                                                              |       | 540        |                           | kΩ     |

| Input Current                                   |                                  |                                                               |                                                                                              |       | 2.3        |                           | μA     |

| INTERNAL REFERENCE (AVDD                        | ) = 3V, unless oth               | nerwise noted)                                                |                                                                                              |       |            |                           |        |

| Output Voltage                                  |                                  | $T_A = +25^{\circ}C$                                          |                                                                                              | 1.225 | 1.25       | 1.275                     | V      |

| Output Voltage Temperature<br>Coefficient       |                                  |                                                               |                                                                                              |       | 18         |                           | ppm/°C |

| Output Short-Circuit Current                    |                                  |                                                               |                                                                                              |       | 3.4        |                           | mA     |

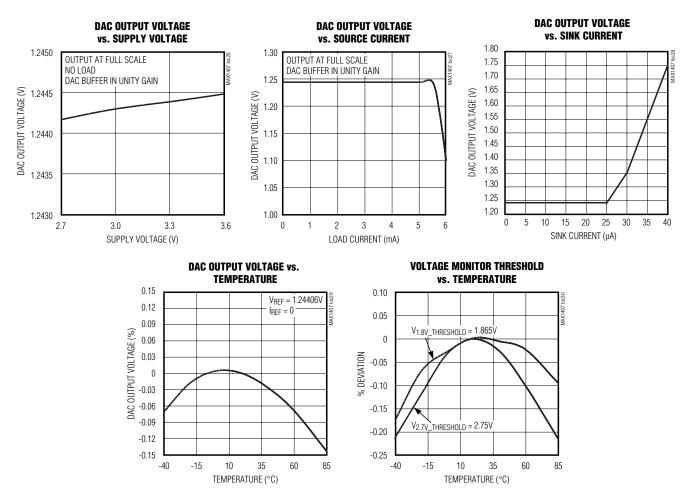

| Line Regulation                                 | $\Delta V_{REF} / \Delta V_{DD}$ | 2.7 <av<sub>DD&lt;3.6V</av<sub>                               |                                                                                              |       | 80         |                           | μV/V   |

| Load Regulation                                 |                                  | Isource = 0µA t                                               | o 500µA, T <sub>A</sub> = +25°C                                                              |       |            | 1                         |        |

| Load Regulation                                 |                                  | $I_{SINK} = 0\mu A$ to 5                                      | 0μΑ, Τ <sub>Α</sub> = +25°C                                                                  |       |            | 2                         | μV/μΑ  |

| Noise Voltage                                   | 0.5.1.5                          | 0.1Hz to 10Hz                                                 |                                                                                              |       | 40         |                           |        |

| Noise Voltage                                   | eout                             | 10Hz to 10kHz                                                 |                                                                                              |       | 400        |                           | µ∨р-р  |

| Power-Supply Rejection Ratio                    |                                  | ±100mV, f = 120                                               | )Hz                                                                                          |       | 70         |                           | dB     |

| Turn-On Time                                    |                                  |                                                               |                                                                                              |       | 3          |                           | ms     |

| μP RESET                                        |                                  |                                                               |                                                                                              |       |            |                           |        |

| Supply Voltage Range                            |                                  | For valid RESET                                               |                                                                                              | 1     |            | 3.6                       | V      |

| RESET Trip Threshold Low                        |                                  | AV <sub>DD</sub> falling                                      | Bit VM = 1                                                                                   | 1.800 | 1.865      | 1.930                     | V      |

| RESET THP THreshold Low                         | V <sub>TH</sub>                  | Avoolianng                                                    | Bit VM = 0                                                                                   | 2.70  | 2.75       | 2.80                      | V      |

| Low AV <sub>DD</sub> Trip Threshold             |                                  | For Normal, Idle, and Standby modes, AV <sub>DD</sub> falling |                                                                                              | 2.70  | 2.75       | 2.80                      | V      |

| RESET Output Low Voltage<br>(Open-Drain Output) |                                  | $I_{SINK} = 1$ mA, AV <sub>DD</sub> = 1.8V                    |                                                                                              |       |            | 0.4                       | V      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V$  to 3.6V, 4.7µF at REF, internal V<sub>REF</sub>, 18nF between CPLL and AV<sub>DD</sub>, 32.768kHz crystal across CLKIN and CLKOUT, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                          | SYMBOL          | CONDITIONS                                                                                  | MIN                       | ТҮР    | MAX                        | UNITS  |

|----------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------|---------------------------|--------|----------------------------|--------|

| RESET Output Leakage                               |                 | $AV_{DD} \ge V_{TH}, \overline{RESET}$ deasserted                                           |                           | 0.002  | 0.1                        | μA     |

| Turn-On Time                                       |                 |                                                                                             |                           | 2      |                            | ms     |

| CRYSTAL OSCILLATOR                                 |                 |                                                                                             |                           |        |                            | •      |

| Crystal Frequency                                  |                 | $AV_{DD} = +3V$                                                                             |                           | 32.768 |                            | kHz    |

| Crystal Load Capacitance                           |                 |                                                                                             |                           | 6      |                            | pF     |

| Oscillator Stability                               |                 | $AV_{DD} = +1.8V$ to +3.6V, excluding crystal                                               |                           | 0      |                            | ppm/V  |

| Oscillator Startup Time                            |                 |                                                                                             |                           | 1.5    |                            | S      |

| PLL                                                |                 |                                                                                             |                           |        |                            | •      |

| FOUT Frequency                                     |                 | $AV_{DD} = +3V$                                                                             |                           | 2.4576 |                            | MHz    |

| Absolute Clock Jitter                              |                 | Cycle-to-cycle                                                                              |                           | 10     |                            | ns     |

| Frequency Tolerance/Stability                      |                 | Overtemperature excluding crystal,<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |                           | 0      |                            | ppm/°C |

|                                                    |                 | Oversupply voltage, +2.7V< AV <sub>DD</sub> < +3.6V                                         |                           | 0      |                            | ppm/mV |

| FOUT Rise/Fall Time                                |                 | 20% to 80% waveform, $C_L = 30 pF$                                                          |                           | 15     | 30                         | ns     |

| Duty Cycle                                         |                 |                                                                                             | 40                        | 50     | 60                         | %      |

| DIGITAL INPUTS (DIN, SCLK, CS                      | 5, WU1, WU2     | )                                                                                           |                           |        |                            |        |

| Input High Voltage                                 |                 | $DV_{DD} = +1.8V$ to $+3.6V$                                                                | 0.7 x<br>DV <sub>DD</sub> |        |                            | V      |

| Input Low Voltage                                  |                 | $DV_{DD} = +1.8V$ to $+3.6V$                                                                |                           |        | 0.3 x<br>DV <sub>DD</sub>  | V      |

| Input Hysteresis                                   |                 | DV <sub>DD</sub> = +3V                                                                      |                           | 200    |                            | mV     |

| DIN, SCLK, CS, Input Current                       |                 | $V_{IN} = 0 \text{ or } V_{IN} = DV_{DD}$                                                   |                           | ±0.01  | ±10                        | μA     |

| WU1, WU2 Input Current                             |                 | $V_{IN} = AV_{DD}$                                                                          |                           | 0.01   | 10                         | μA     |

| WU1, WU2 Pullup Current                            |                 | $V_{IN} = 0$                                                                                |                           | 10     |                            | μA     |

| Input Capacitance                                  |                 |                                                                                             |                           | 10     |                            | рF     |

| DIGITAL OUTPUTS (DOUT, FOU                         | T, INT, DRDY    | , <del>SHDN</del> , D0)                                                                     |                           |        |                            |        |

| DOUT, FOUT, DRDY, INT<br>Output Low Voltage        | V <sub>OL</sub> | $I_{SINK} = 1$ mA, $DV_{DD} = +1.8V$ to +3.6V                                               |                           |        | 0.4                        | V      |

| DOUT, FOUT, DRDY, INT,<br>SHDN Output High Voltage | V <sub>OH</sub> | $I_{SOURCE} = 0.2 \text{mA}, DV_{DD} = +1.8 \text{V to } +3.6 \text{V}$                     | 0.8 x D'                  | VDD    |                            | V      |

| DOUT Three-State Leakage                           |                 |                                                                                             |                           | ±0.01  | ±10                        | μA     |

| DOUT Three-State Capacitance                       |                 |                                                                                             |                           | 15     |                            | pF     |

| SHDN Output Low Voltage                            |                 | $I_{SINK}$ = 1mA, $DV_{DD}$ = +1.8V to +3.6V                                                |                           |        | 0.4                        |        |

| (MAX1407/MAX1408/MAX1414<br>only)                  |                 | $I_{SINK} = 50\mu A$ , $DV_{DD} = +1.8V$ to +3.6V                                           |                           |        | 0.04 x<br>DV <sub>DD</sub> | V      |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(DV_{DD} = AV_{DD} = +2.7V$  to 3.6V, 4.7µF at REF, internal V<sub>REF</sub>, 18nF between CPLL and AV<sub>DD</sub>, 32.768kHz crystal across CLKIN and CLKOUT, T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                   | SYMBOL          | CONDITIONS                                     |                                     | MIN                       | ТҮР | MAX  | UNITS |

|-------------------------------------------------------------|-----------------|------------------------------------------------|-------------------------------------|---------------------------|-----|------|-------|

| D0 Output Low Voltage<br>(MAX1407/MAX1408/MAX1414<br>only)  |                 | I <sub>SINK</sub> = 200µA, D                   | $V_{DD} = +2.7V \text{ to } +3.6V$  |                           |     | 0.7  | mV    |

| D0 Output High Voltage<br>(MAX1407/MAX1408/MAX1414<br>only) |                 | ISOURCE = $2mA$ , $DV_{DD} = +2.7V$ to $+3.6V$ |                                     | DV <sub>DD</sub><br>- 0.1 |     |      | V     |

| POWER REQUIREMENTS                                          |                 |                                                |                                     |                           |     |      |       |

| Supply Voltage Bange                                        |                 | Run, Idle, and Standby mode                    |                                     | 2.7                       |     | 3.6  | V     |

| Supply Voltage Range                                        | V <sub>DD</sub> | Sleep mode                                     |                                     | 1.8                       |     | 3.6  | V     |

|                                                             |                 | Run mode                                       | MAX1407/MAX1414                     |                           |     | 1.15 | mA    |

|                                                             |                 |                                                | MAX1408                             |                           |     | 1.03 |       |

|                                                             |                 |                                                | MAX1409                             |                           |     | 1.09 |       |

|                                                             |                 |                                                | MAX1407/MAX1414                     |                           |     | 650  |       |

| Supply Current (Note E)                                     |                 | Idle mode                                      | MAX1408                             |                           |     | 530  |       |

| Supply Current (Note 5)                                     | IDD             |                                                | MAX1409                             |                           |     | 590  |       |

|                                                             |                 | Standby mode                                   | MAX1407/MAX1408/<br>MAX1409/MAX1414 |                           |     | 330  | μA    |

|                                                             |                 | Sleep mode<br>V <sub>DD</sub> = 2.7V           | MAX1407/MAX1408/<br>MAX1409/MAX1414 |                           | 1.7 | 2.5  |       |

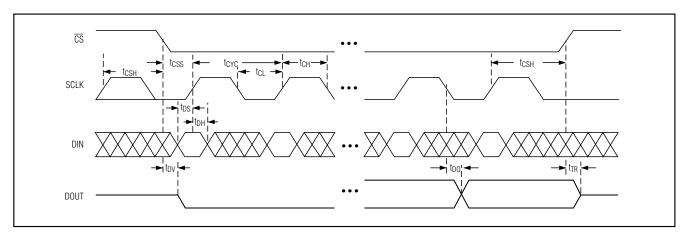

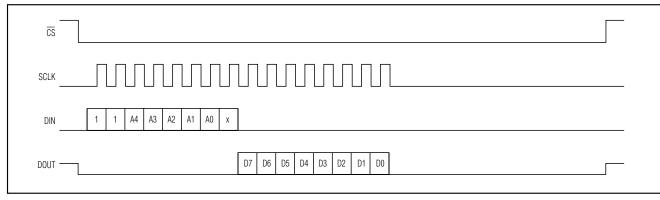

## TIMING CHARACTERISTICS

(MAX1407/MAX1408/MAX1409/MAX1414: AV<sub>DD</sub> = DV<sub>DD</sub> = 2.7V to 3.6V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                 | SYMBOL           | CONDITIONS                               | MIN | ТҮР | МАХ | UNITS |

|-------------------------------------------|------------------|------------------------------------------|-----|-----|-----|-------|

| TIMING PARAMETERS                         |                  |                                          |     |     |     |       |

| SCLK Operating Frequency                  | <b>f</b> SCLK    |                                          |     |     | 2.1 | MHz   |

| SCLK Cycle Time                           | tCYC             |                                          | 476 |     |     | ns    |

| SCLK Pulse Width High                     | tсн              |                                          | 190 |     |     | ns    |

| SCLK Pulse Width Low                      | tCL              |                                          | 190 |     |     | ns    |

| DIN to SCLK Setup                         | t <sub>DS</sub>  |                                          | 100 |     |     | ns    |

| DIN to SCLK Hold                          | t <sub>DH</sub>  |                                          | 0   |     |     | ns    |

| SCLK Fall to Output Data Valid            | tDO              | $C_L = 50 pF$ (see load circuit)         |     |     | 200 | ns    |

| CS Fall to Output Enable                  | t <sub>DV</sub>  | $C_L = 50 pF$ (see load circuit)         |     |     | 240 | ns    |

| CS Rise to Output Disable                 | t <sub>TR</sub>  | C <sub>L</sub> = 50pF (see load circuit) |     |     | 240 | ns    |

| $\overline{\text{CS}}$ to SCLK Rise Setup | tcss             |                                          | 100 |     |     | ns    |

| $\overline{\text{CS}}$ to SCLK Rise Hold  | t <sub>CSH</sub> |                                          | 0   |     |     | ns    |

## TIMING CHARACTERISTICS (continued)

(MAX1407/MAX1408/MAX1409/MAX1414: AV<sub>DD</sub> = DV<sub>DD</sub> = 2.7V to 3.6V,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted.)

| PARAMETER                                                      | SYMBOL            | CONDITIONS                                                                                                                                                                                                                                                                                                                                               | MIN | ТҮР   | MAX | UNITS |

|----------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----|-------|

| TYPICAL TIMING PARAMETERS                                      | 5                 |                                                                                                                                                                                                                                                                                                                                                          |     |       |     |       |

| OUT1/OUT2 Turn-Off Time                                        |                   | Input impedance > $1M\Omega$<br>(MAX1407/MAX1409/MAX1414 only)                                                                                                                                                                                                                                                                                           |     | 100   |     | μs    |

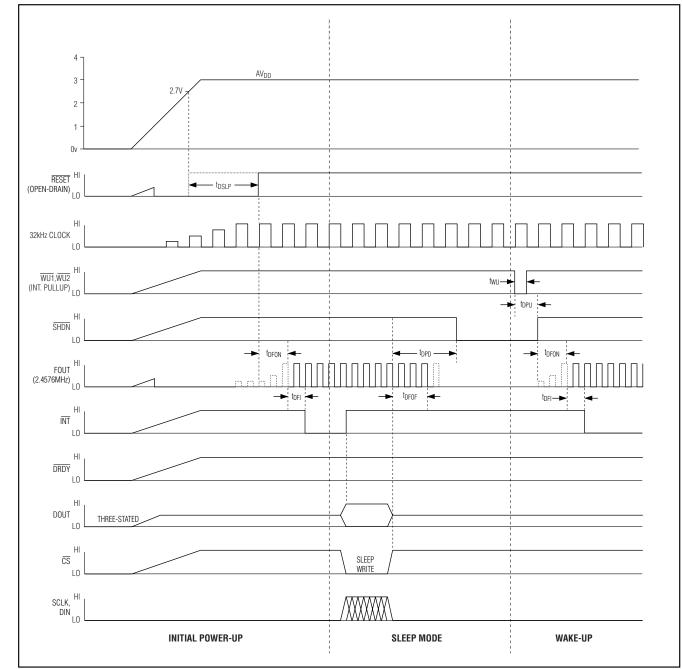

| Sleep Voltage Monitor Timeout<br>Period                        | tDSLP             | The delay for the sleep voltage monitor<br>output, $\overrightarrow{\text{RESET}}$ , to go high after AV <sub>DD</sub> rises<br>above the reset threshold (+1.8V when bit<br>VM = 1 and +2.7V, when bit VM = 0); this is<br>largely driven by the startup of the 32kHz<br>oscillator                                                                     |     | 1.54  |     | S     |

| $\overline{\text{WU1}}$ or $\overline{\text{WU2}}$ Pulse Width | tw∪               | Minimum pulse width required to detect a wake-up event                                                                                                                                                                                                                                                                                                   |     | 1     |     | μs    |

| Shutdown Deassert Delay                                        | tDPU              | The delay for SHDN to go high after a valid wake-up event                                                                                                                                                                                                                                                                                                |     | 1     |     | μs    |

| FOUT Turn-On Time                                              | <sup>t</sup> dfon | The turn-on time for the high-frequency clock; it is gated by an AND function with three signals—the RESET signal, the internal low voltage $V_{DD}$ monitor signal, and the assertion of the PLL; the time delay is timed from when the low-voltage monitor trips or the RESET going high, whichever happens later; FOUT always starts in the low state |     | 31.25 |     | ms    |

| INT Delay                                                      | tDFI              | The delay for $\overline{\text{INT}}$ to go low after the FOUT clock output has been enabled; $\overline{\text{INT}}$ is used as an interrupt signal to inform the $\mu$ P the high-frequency clock has started                                                                                                                                          |     | 7.82  |     | ms    |

| FOUT Disable Delay                                             | tDFOF             | The delay after a shutdown command has<br>asserted and before FOUT is disabled; this<br>gives the microcontroller time to clean up<br>and go into Sleep mode properly                                                                                                                                                                                    |     | ms    |     |       |

| SHDN Assertion Delay                                           | tDPD              | The delay after a shutdown command has asserted and before SHDN is pulled low (turning off the DC-DC converter) (Note 6)                                                                                                                                                                                                                                 |     | 2.93  |     | ms    |

Note 1: Single conversion.

Note 2: DNL and INL are measured between code 010hex and 3FFhex.

Note 3: Offset error is referenced to code 010hex.

Note 4: Output swing is a function of external gain-setting feedback resistors and REF voltage.

Note 5: Measured with no load on FOUT, DOUT, and the DAC amplifiers. SCLK is idle, and all digital inputs are at DGND or DVDD.

Note 6: SHDN stays high if the PLL is on.

Note 7: Actual worst-case performance is ±2.5LSB. Guaranteed limit of ±3.5LSB is due to production test limitation.

Note 8: Guaranteed by design. Not production tested.

#### **Load Circuits** $\mathsf{DV}_\mathsf{DD}$ $\mathsf{DV}_\mathsf{DD}$ 6kΩ $6k\Omega$ DOUT DOUT DOUT DOUT CLOAD $C_{\text{LOAD}}$ CLOAD CLOAD $6k\Omega$ 6kC 50pF 50pF 50pF 50pF - DGND - DGND DGND DGND a) VOH TO HIGH-Z b) V<sub>OL</sub> TO HIGH-Z a) HIGH-Z TO VOH AND VOL TO VOH b) HIGH-Z TO VOL AND VOH TO VOL LOAD CIRCUITS FOR DISABLE TIME LOAD CIRCUITS FOR ENABLE TIME Typical Operating Characteristics $(A_{VDD} = D_{VDD} = 3V, MAX1407 \text{ used}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$ **SUPPLY CURRENT vs. SUPPLY CURRENT vs.** SUPPLY VOLTAGE **TEMPERATURE** 700 700 600 600 RUN MODE RUN MODE 005 (July CURRENT (July) 007 (July CURRENT (July) 007 (July CURRENT (July ) 007 (July CURRENT (July ) ( 1 500 IDLE MODE IDLE MODE SUPPLY CURRENT 400 300 STANDBY STANDBY 200 100 100 0 0 2.70 2.85 3.00 3.15 3.30 3.45 3.60 -40 -15 10 35 60 85 SUPPLY VOLTAGE (V) TEMPERATURE (°C) **SLEEP MODE SUPPLY CURRENT SLEEP CURRENT vs. FALLING VDD** vs. TEMPERATURE 4.0 3.0 3.5 2.5 SUPPLY CURRENT (µA) SLEEP CURRENT (µA) 3.0 2.0 2.5 1.5

1.0

0.5

0

-40

-15

10

TEMPERATURE (°C)

35

60

85

8

2.0

1.5

1.0 1.80

2.30

2.80

SUPLLY VOLTAGE (V)

3.30

MIXIM

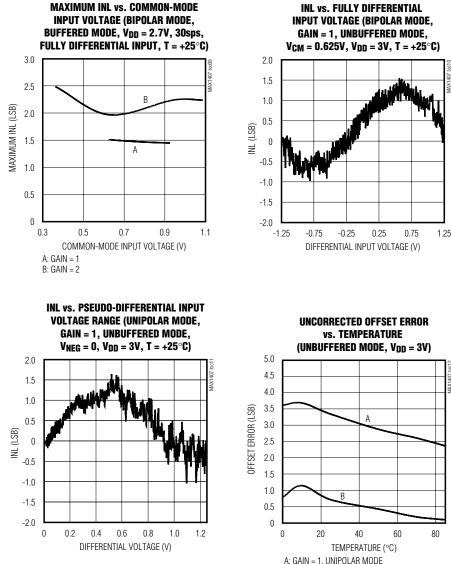

**Typical Operating Characteristics (continued)**

A

3.3

3.5

A

80

60

В

(AVDD = DVDD = 3V, MAX1407 used, TA = +25°C, unless otherwise noted.)

MAX1407/MAX1408/MAX1409/MAX1414

## **Typical Operating Characteristics (continued)**

$(A_{VDD} = D_{VDD} = 3V, MAX1407 \text{ used}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

A. GAIN = 1, UNIPULAR MOD B: GAIN = 2, BIPOLAR MODE

## **Typical Operating Characteristics (continued)**

$(A_{VDD} = D_{VDD} = 3V, MAX1407 \text{ used}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# MAX1407/MAX1408/MAX1409/MAX1414

## \_Typical Operating Characteristics (continued)

$(A_{VDD} = D_{VDD} = 3V, MAX1407 \text{ used}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

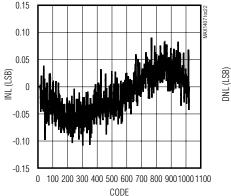

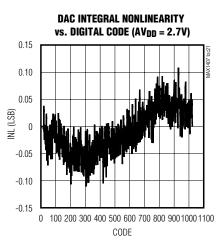

DAC INTEGRAL NONLINEARITY vs. Digital Code (AV<sub>DD</sub> = 3.6V)

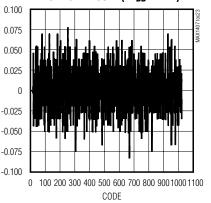

DAC DIFFERENTIAL NONLINEARITY vs. Digital Code (AV<sub>DD</sub> = 2.7V)

DAC LARGE-SIGNAL OUTPUT

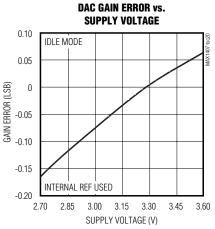

DAC DIFFERENTIAL NONLINEARITY vs. DIGITAL CODE (AVDD = 3.6V)

$V_{REF} = 1.25V, \, AV_{DD} = 3.0V, \, R_L = 0$

## **Typical Operating Characteristics (continued)**

$(A_{VDD} = D_{VDD} = 3V, MAX1407 \text{ used}, T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## **Pin Description**

| MAX1407<br>MAX1414 | MAX1408 | MAX1409 | PIN              | FUNCTION                                                                                                                                                                                                                                            |

|--------------------|---------|---------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | _       |         | FB2              | Force/Sense DAC2 Feedback Input                                                                                                                                                                                                                     |

| _                  | 1       |         | IN7              | Analog Input. Analog input to the negative mux only.                                                                                                                                                                                                |

| _                  |         | 1       | FB1              | Force/Sense DAC1 Feedback Input                                                                                                                                                                                                                     |

| 2                  | 2       |         | D0               | Digital Output. Three-state general-purpose digital output.                                                                                                                                                                                         |

| 3                  |         |         | FB1              | Force/Sense DAC1 Feedback Input                                                                                                                                                                                                                     |

| _                  | 3       |         | IN6              | Analog Input. Analog input to the negative mux only.                                                                                                                                                                                                |

| 4                  |         | 2       | OUT1             | Force/Sense DAC1 Output                                                                                                                                                                                                                             |

| _                  | 4       |         | IN4              | Analog Input. Analog input to the positive mux only.                                                                                                                                                                                                |

| 5                  | 5       | 3       | INO              | Analog Input. Analog input to both the positive and negative mux.                                                                                                                                                                                   |

| 6                  | 6       | 4       | REF              | 1.25V Reference Buffer Output/External Reference Input. Reference voltage for the ADC and the DAC. Connect a $4.7\mu$ F capacitor to REF between REF and AGND.                                                                                      |

| 7                  | 7       | 5       | AGND             | Analog Ground. Reference point for the analog circuitry. AGND connects to the IC substrate.                                                                                                                                                         |

| 8                  | 8       | 6       | AV <sub>DD</sub> | Analog Supply Voltage                                                                                                                                                                                                                               |

| 9                  | 9       | 7       | CPLL             | PLL Capacitor Connection Pin. Connect an 18nF ceramic capacitor between CPLL and $AV_{DD}$ .                                                                                                                                                        |

| 10                 | 10      | 8       | WU1              | Active-Low Wake-Up Input. Internally pulled up. The device will wake-up from Sleep mode to Standby mode when WU1 is asserted.                                                                                                                       |

| 11                 | 11      | 9       | WU2              | Active-Low Wake-Up Input. Internally pulled up. The device will wake-up from Sleep mode to Standby mode when WU2 is asserted.                                                                                                                       |

| 12                 | 12      | 10      | RESET            | Active-Low RESET Output. It remains low while AV <sub>DD</sub> is below the threshold<br>and stays low for a timeout period after AV <sub>DD</sub> rises above the threshold.<br>RESET is an open-drain output.                                     |

| 13                 | 13      | _       | IN1              | Analog Input. Analog input to both the positive and negative mux.                                                                                                                                                                                   |

| 14                 | 14      | _       | IN2              | Analog Input. Analog input to both the positive and negative mux.                                                                                                                                                                                   |

| 15                 | 15      | _       | SHDN             | Programmable Shutdown Output. Goes low in Sleep mode.                                                                                                                                                                                               |

| 16                 | 16      | _       | DRDY             | Active-Low Data Ready Output. A logic low indicates that a new conversion result is available in the Data register. DRDY returns high upon completion of a full output word read operation. DRDY also signals the end of an ADC offset-calibration. |

| 17                 | 17      | 11      | FOUT             | 2.4576MHz Clock Output. FOUT can be used to drive the input clock of a $\mu$ P.                                                                                                                                                                     |

| 18                 | 18      | 12      | CLKOUT           | 32kHz Crystal Output. Connect a 32kHz crystal between CLKIN and CLKOUT.                                                                                                                                                                             |

| 19                 | 19      | 13      | CLKIN            | 32kHz Crystal Input. Connect a 32kHz crystal between CLKIN and CLKOUT.                                                                                                                                                                              |

## Pin Description (continued)

| MAX1407<br>MAX1414 | MAX1408 | MAX1409 | PIN              | FUNCTION                                                                                                                                                                                                                                                       |

|--------------------|---------|---------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20                 | 20      | 14      | INT              | Active-Low Interrupt Output. INT goes low when the PLL output is ready, when the signal-detect comparator is tripped, or when the alarm is triggered.                                                                                                          |

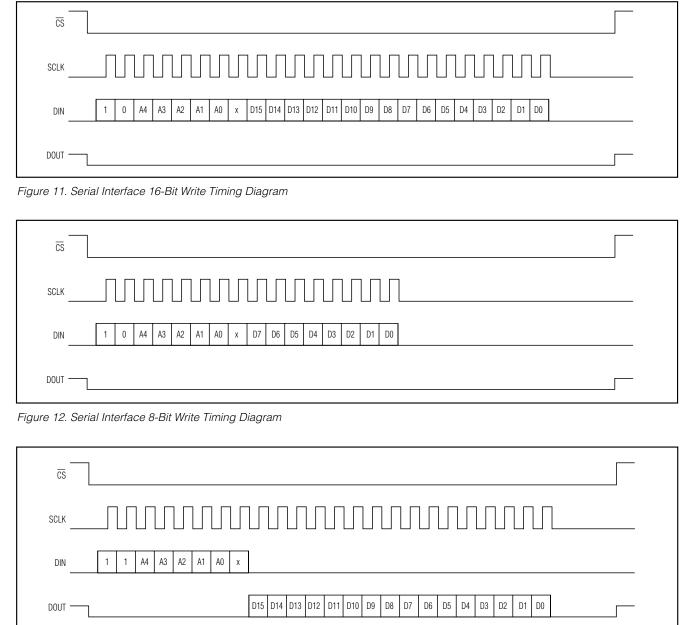

| 21                 | 21      | 15      | DOUT             | Serial Data Output. DOUT outputs serial data from the internal shift register on SCLK's falling edge. When $\overline{\text{CS}}$ is high, DOUT is three-stated.                                                                                               |

| 22                 | 22      | 16      | DIN              | Serial Data Input. Data on DIN is written to the input shift register and is clocked in at SCLK's rising edge when $\overline{CS}$ is low.                                                                                                                     |

| 23                 | 23      | 17      | SCLK             | Serial Clock Input. Apply an external serial clock to transfer data to and from the device. This serial clock can be continuous, with data transmitted in a train of pulses, or intermittent while $\overline{\text{CS}}$ is low.                              |

| 24                 | 24      | 18      | CS               | Active-Low Chip-Select Input. $\overline{CS}$ is used to select the active device in systems with more than one device on the serial bus. Data will not be clocked into DIN unless $\overline{CS}$ is low. When $\overline{CS}$ is high, DOUT is three-stated. |

| 25                 | 25      | 19      | DGND             | Digital Ground. Reference point for digital circuitry.                                                                                                                                                                                                         |

| 26                 | 26      | 20      | DV <sub>DD</sub> | Digital Supply Voltage                                                                                                                                                                                                                                         |

| 27                 | 27      | _       | IN3              | Analog Input. Analog input to both the positive and negative mux.                                                                                                                                                                                              |

| 28                 | _       | _       | OUT2             | Force/Sense DAC2 Output                                                                                                                                                                                                                                        |

|                    | 28      |         | IN5              | Analog Input. Analog input to the positive mux only.                                                                                                                                                                                                           |

## **Detailed Information**

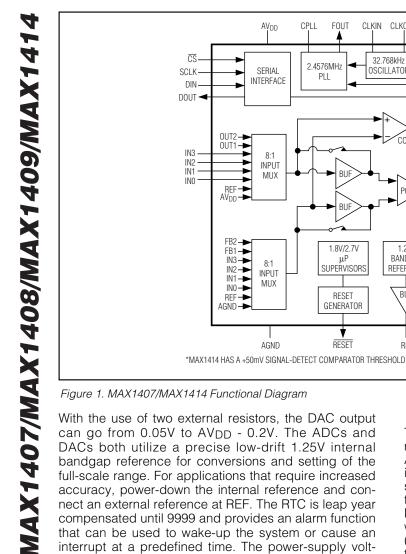

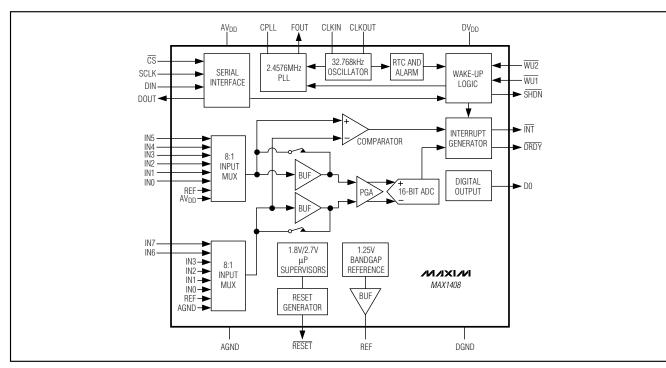

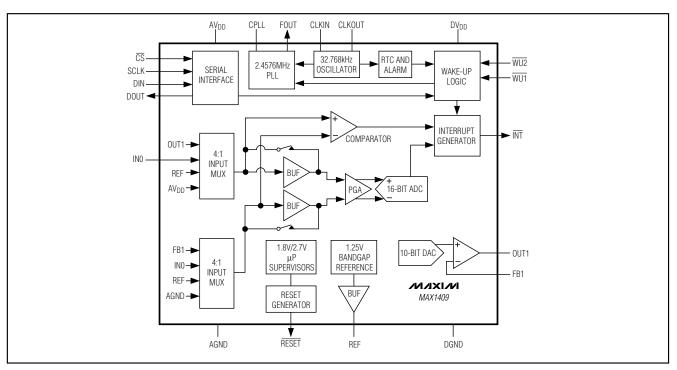

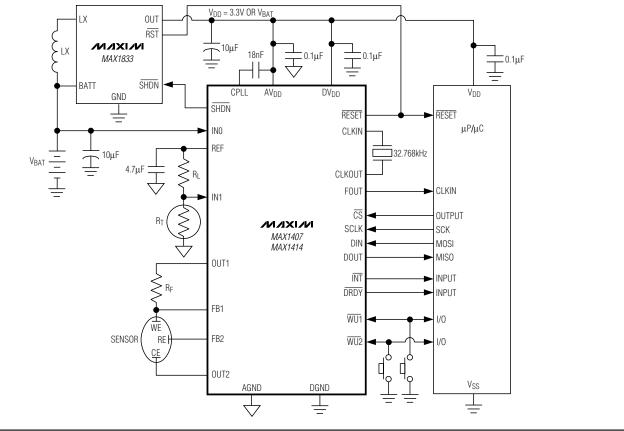

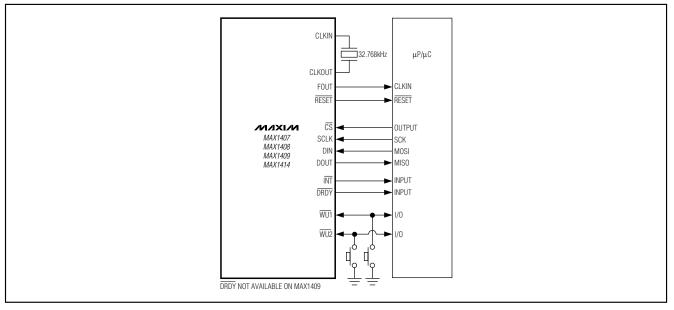

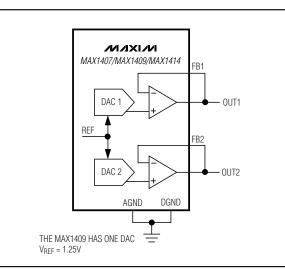

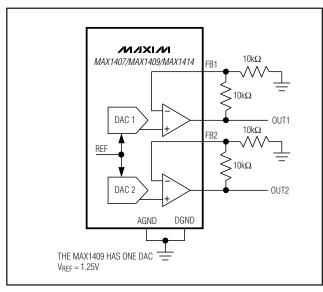

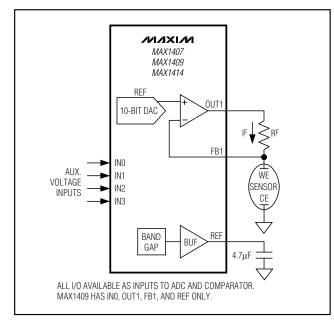

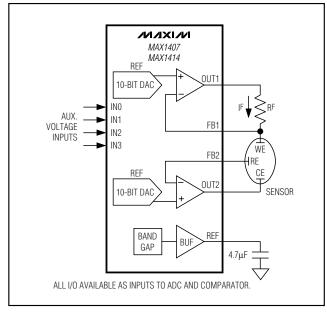

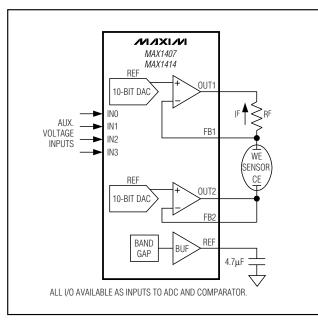

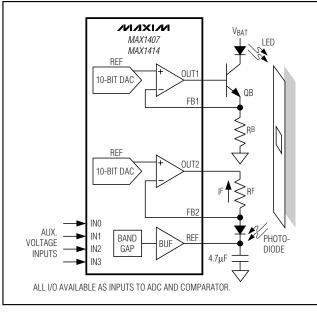

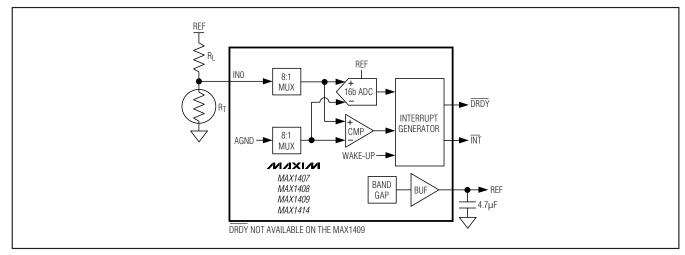

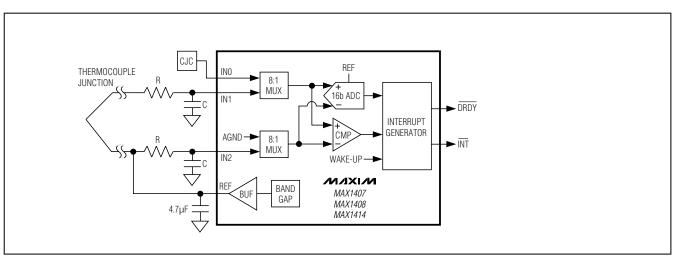

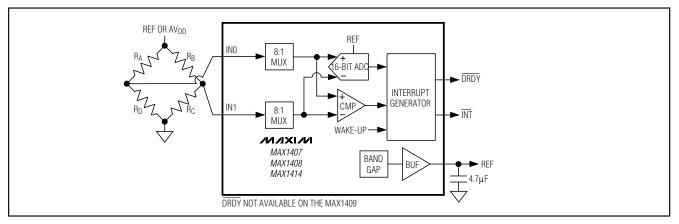

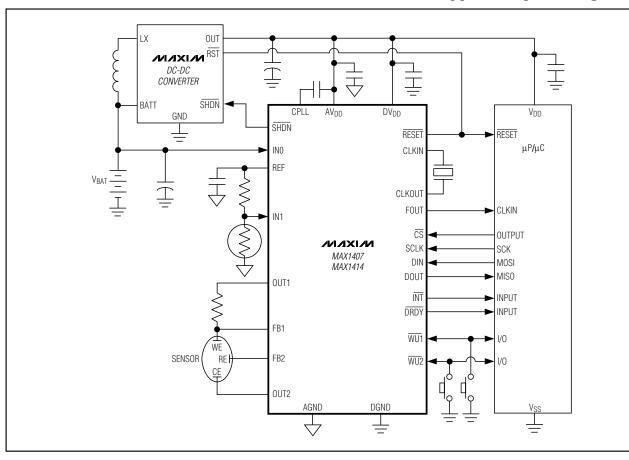

The MAX1407/MAX1408/MAX1409/MAX1414 are lowpower, general-purpose, multichannel DAS featuring a multiplexed fully differential 16-bit  $\Sigma \Delta$  analog-to-digital converter (ADC), 10-bit force/sense digital-to-analog converters (DAC), a real-time clock (RTC) with an alarm, a bandgap voltage reference, a signal detect comparator, two power-supply voltage monitors, wakeup control circuitry, and a high-frequency phase-locked loop (PLL) clock output all controlled by a 3-wire serial interface. (See Table 1 for the MAX1407/MAX1408/ MAX1409/MAX1414 feature sets and Figures 1, 2, 3 for the *Functional Diagrams*). These DAS directly interface to various sensor outputs and once configured provide the stimulus, conditioning, and data conversion, as well as microprocessor support. Figure 4 is a *Typical Application Circuit* for the MAX1407/MAX1414.

The 16-bit  $\sum \Delta$  ADC is capable of programmable continuous conversion rates of 30Hz or 60Hz and gains of 1/3, 1, and 2V/V to suit applications with different power and dynamic range constraints. The force/sense DACs provide 10-bit linearity for precise sensor applications.

| PART    | ADC<br>AUXILIARY<br>ANALOG<br>INPUTS | FORCE/<br>SENSE<br>DAC | THREE-<br>STATE<br>DIGITAL<br>OUTPUT | COMPARATOR<br>THRESHOLD<br>(mV) | RTC | ADC DATA<br>READY<br>(DRDY) | EXTERNAL<br>POWER-<br>SUPPLY<br>SHUTDOWN<br>CONTROL | ADC<br>DIFFERENTIAL<br>INPUT MUX |  |  |  |  |

|---------|--------------------------------------|------------------------|--------------------------------------|---------------------------------|-----|-----------------------------|-----------------------------------------------------|----------------------------------|--|--|--|--|

| MAX1407 | 4                                    | 2                      | Yes                                  | 0                               | Yes | Yes                         | Yes                                                 | 8                                |  |  |  |  |

| MAX1414 | 4                                    | 2                      | Yes                                  | 50                              | Yes | Yes                         | Yes                                                 | 8                                |  |  |  |  |

| MAX1408 | 8                                    | 0                      | Yes                                  | 0                               | Yes | Yes                         | Yes                                                 | 8                                |  |  |  |  |

| MAX1409 | 1                                    | 1                      | No                                   | 0                               | Yes | No                          | No                                                  | 4                                |  |  |  |  |

## Table 1. MAX1407/MAX1408/MAX1409/MAX1414 Feature Sets

CLKIN CLKOUT

32.768kHz

OSCILLATOR

RTC AND

ALARM

MAXIM

MAX1407/MAX1414

16-BIT ADC

10-BIT DAC

10-BIT DAC

COMPARATOR

PGA

1.25V

BANDGAP

REFERENCE

BUF

RFF

DVDD

WAKE-UP

LOGIC

¥

INTERRUPT

GENERATOR

DIGITAL

OUTPUT

DGND

WU2

WU1

SHDN

► ĪNT

DRDY

► D0

OUT1

FB1

OUT2

FB2

DACs both utilize a precise low-drift 1.25V internal bandgap reference for conversions and setting of the full-scale range. For applications that require increased accuracy, power-down the internal reference and connect an external reference at REF. The RTC is leap year compensated until 9999 and provides an alarm function that can be used to wake-up the system or cause an interrupt at a predefined time. The power-supply voltage monitors detect when AVDD falls below a trip threshold voltage at either +1.8V or +2.7V causing the reset to be asserted. The 4-wire serial interface is used to communicate directly between SPI, QSPI, and MICROWIRE devices for system configuration and readback functions.

#### **Analog Input Protection**

Internal protection diodes clamp the analog input to AV<sub>DD</sub> and AGND, which allow the channel input pins to swing from AGND - 0.3V to AV<sub>DD</sub> + 0.3V without damage. However, for accurate conversions near full scale, the inputs must not exceed AV<sub>DD</sub> by more than 50mV or be lower than AGND by 50mV.

#### Analog Mux

The MAX1407/MAX1408/MAX1414 include a dual 8 to 1 multiplexer for the positive and negative inputs of the ADC. The MAX1409 has a dual 4 to 1 multiplexer at the inputs of the ADC. Figures 1, 2, and 3 illustrate which signals are present at the inputs of each multiplexer for the MAX1407/MAX1408/MAX1409/MAX1414. The MUXP and MUXN bits of the MUX register choose which inputs will be seen at the input to the ADC (Tables 4 and 5) and the signal-detect comparator. See the MUX Register description under the *On-Chip Registers* section for multiplexer functionality.

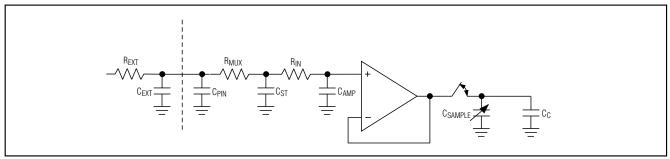

#### Input Buffers

The MAX1407/MAX1408/MAX1409/MAX1414 provide input buffers to isolate the analog inputs from the capacitive load presented by the ADC modulator (Figure 5 and 6). The buffers are chopper stabilized to reduce the effect of their DC offsets and low-frequency noise. Since the buffers can represent more than 25% of the total analog power dissipation (typically 220µA), they may be shut down in applications where minimum power dissipation is required and the capacitive input load is not a concern (see ADC and Power1 Registers). Disable the buffers in applications where the inputs must operate close to AGND or above +1.4V. The buffers are individually enabled or disabled.

Figure 2. MAX1408 Functional Diagram

Figure 3. MAX1409 Functional Diagram

MAX1407/MAX1408/MAX1409/MAX1414

Figure 4. MAX1407/MAX1414 Typical Application Circuit

Figure 5. Analog Input—Buffered Mode

#### **Buffered Mode**

When used in buffered mode, the buffers isolate the inputs from the sampling capacitors. The samplingrelated gain error is dramatically reduced since only a small dynamic load is present from the chopper. The multiplexer exhibits an input leakage current of 0.5nA (typ). With high-source resistances, this leakage current may result in a large DC offset error.

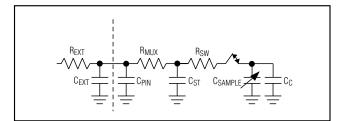

Figure 6. Analog Input—Unbuffered Mode

#### Unbuffered Mode

When used in unbuffered mode, the switched capacitor sampling front end of the modulator presents a dynamic load to the driving circuitry. The size of the internal sampling capacitor and the input sampling frequency (Figure 6) determines the dynamic load (see *Dynamic Input Impedance* section). As the gain increases, the input sampling capacitance also increases. Since the MAX1407/MAX1408/MAX1409/MAX1414 sample at a constant rate for all gain settings, the dynamic load presented by the inputs varies with the gain setting.

#### PGA Gain

An integrated programmable-gain amplifier (PGA) provides three user-selectable gains: +1/3V/V, +1V/V, and +2V/V to maximize the dynamic range of the ADC. Bits GAIN1 and GAIN0 set the desired gain (see *ADC Register*). The gain of +1/3V/V allows the direct measurement of the supply voltage through an internal multiplexer input or through an auxillary input.

#### **ADC Modulator**

The MAX1407/MAX1408/MAX1409/MAX1414 perform analog-to-digital conversions using a single-bit, second-order, switched-capacitor delta-sigma modulator. The delta-sigma modulation converts the input signal into a digital pulse train whose average duty cycle represents the digitized signal information. The pulse train is then processed by a digital decimation filter.

The modulator provides 2nd-order frequency shaping of the quantization noise resulting from the single bit quantizer. The modulator is fully differential for maximum signal-to-noise ratio and minimum susceptibility to power-supply noise. The modulator operates at one of two different sampling rates resulting in an output data rate of either 30Hz or 60Hz (see *ADC Register*).

#### **ADC Offset Calibration**

The MAX1407/MAX1408/MAX1409/MAX1414 are capable of performing digital offset correction to eliminate changes due to power-supply voltage or system temperature. At the end of a calibration cycle, a 16-bit calibration value is stored in the Offset register in two's compliment format. After completing a conversion, the MAX1407/MAX1408/MAX1409/MAX1414 subtract the calibration value from the ADC conversion result and write the offset compensated data to the Data register (see Offset Register section). Either a positive or negative offset can be calibrated. During offset calibration, DRDY will go high. DRDY goes low after calibration is complete. The offset register can be programmed to skew the ADC offset with a maximum range from -2<sup>15</sup> to (+2<sup>15</sup> - 1)LSBs, e.g., if the programmed 2's complement value is +2LSB (-2LSB), this translates to a -2LSB (+2LSB) shift in bipolar mode or a -4LSB (+4LSB) shift in unipolar mode. To maintain optimum performance, recalibrate the ADC if the temperature changes by more than 20°C. Offset calibration should also be performed after any changes in PGA gain, bipolar/unipolar input range, buffered/unbuffered mode, or conversion speed. During calibration, the two mulitplexers will be disabled and the inputs to the ADC will internally be shorted to a common-mode voltage.

#### **ADC Digital Filter**

The on-chip digital filter processes the 1-bit data stream from the modulator using a SINC<sup>3</sup> filter function. The SINC<sup>3</sup> filters settle in three data word periods. The settling time is 3/60Hz or 50ms (for RATE bit in ADC register set to 1) and 3/30Hz or 100ms (for RATE bit set to "0").

#### **ADC Digital Filter Characteristics**

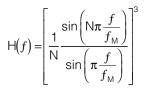

The transfer function for a SINC<sup>3</sup> filter function is that of three cascaded SINC<sup>1</sup> filters. This can be described in the Z-domain by:

$$H(z) = \left[\frac{1}{N} \frac{(1 - z^{-N})}{(1 - z^{-1})}\right]^{2}$$

and in the frequency domain by:

where N, the decimation factor, is the ratio of the modulator frequency  $f_M$  to the output frequency  $f_N$ .

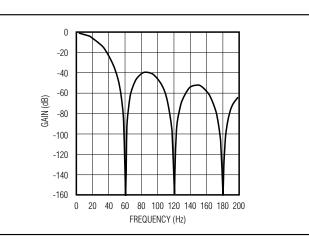

Figure 7. Frequency Response of the SINC<sup>3</sup> Filter (Notch at 60Hz)

Figure 7 shows the filter frequency response. The SINC<sup>3</sup> characteristic cutoff frequency is 0.262 times the first notch frequency. This results in a cutoff frequency of 15.72Hz for a first filter notch frequency of 60Hz (output data rate of 60Hz). The response shown in Figure 7 is repeated at either side of the digital filter's sample frequency (f<sub>M</sub>) (f<sub>M</sub> = 15.36kHz for 30Hz and f<sub>M</sub> = 30.72kHz for 60Hz) and at either side of the related harmonics (2f<sub>M</sub>, 3f<sub>M</sub>,....).

The output data rate for the digital filter corresponds with the positioning of the first notch of the filter's frequency response. Therefore, for the plot of Figure 7 where the first notch of the filter is at 60Hz, the output data rate is 60Hz. The notches of this  $(sinx/x)^3$  filter are repeated at multiples of the first notch frequency. The SINC<sup>3</sup> filter provides an attenuation of better than 100dB at these notches.

For step changes at the input, enough settling time must be allowed before valid data can be read. The settling time depends upon the output data rate chosen for the filter. The settling time of the SINC<sup>3</sup> filter to a fullscale step input can be up to four times the output data period, or three times if the step change is synchrozied with FSYNC.

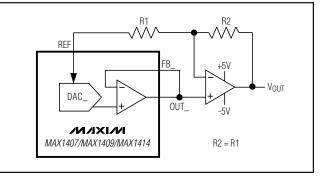

#### Force/Sense DAC (MAX1407/MAX1409/MAX1414)

The MAX1407/MAX1414 incorporate two 10-bit force/ sense DACs while the MAX1409 has one. The DACs use a precise 1.25V internal bandgap reference for setting the full-scale range. Program the DAC1 and DAC2 registers through the serial interface to set the output voltages of the DACs seen at OUT1 and OUT2. Shorting FB1(2) and OUT1(2) configures the DAC in a unity-gain setting. Connecting resistors in a voltagedivider configuration between OUT1(2), FB1(2), and GND sets a different closed-loop gain for the output amplifier (see the *Applications Information* section).

The DAC output amplifier typically settles to  $\pm 1/2$ LSB from a full-scale transition within 65µs, when it is connected in unity gain and loaded with 12k $\Omega$  in parallel with 200pF. Loads less than 2k $\Omega$  may degrade performance. See the *Typical Operating Characteristics* section for the source-and-sink capability of the DAC output.

The MAX1407/MAX1409/MAX1414 feature a softwareprogrammable shutdown mode for the DACs that reduce the total power consumption when they are not used. The two DACs can be powered-down independently or simultaneously by clearing the DA1E and DA2E bits (see *Power1 Register*). DAC outputs OUT1 and OUT2 go high impedance when powered down. The DACs are automatically powered up and ready for a conversion when Idle or Run mode is entered.

#### **Voltage Monitors**

The MAX1407/MAX1408/MAX1409/MAX1414 include two on-board voltage monitors. When AV<sub>DD</sub> is below the RESET trip threshold, RESET goes low and the RST bit of the Status register is set to "1". When AV<sub>DD</sub> is below the Low V<sub>DD</sub> trip threshold, the LVD bit of the Status register is set to 1.

#### **RESET** Voltage Monitor

The RESET voltage monitor is powered up at all times (provided that VM = 0 and LVDE = 1 or VM = 1 and LSDE = 1). A threshold voltage of either +1.8V or +2.7V may be selected for the RESET voltage monitor (see *Power2 Register*). At initial power-up, the RESET trip threshold is set to 2.7V. If the RESET voltage monitor is tripped, the RST bit of the status register is set to "1" and RESET goes low. RESET is held low for 1.54 seconds (typ) after AV<sub>DD</sub> rises above the RESET voltage monitor threshold. If AV<sub>DD</sub> is no longer below the RESET threshold, reading the Status register will clear RST.

#### Low VDD Voltage Monitor

/N / X | /V

When the device is operating in Run, Idle, or Standby mode (see *Power Modes*) and AV<sub>DD</sub> goes below +2.7V, the low V<sub>DD</sub> monitor trips, indicating that the supply voltage is below the safe minimum for proper operation. When tripped, the Low V<sub>DD</sub> Voltage Monitor sets the LVD bit of the Status register to 1. If AV<sub>DD</sub> is no longer below +2.7V, reading the Status register will clear LVD. The low V<sub>DD</sub> monitor is powered down in Sleep mode. When it is powered down, the LVD bit stays unchanged. The LVD is cleared if it is read in Sleep mode.

#### Internal/External Reference

The MAX1407/MAX1408/MAX1409/MAX1414 have an internal low-drift +1.25V reference used for both ADC and DAC conversion. The buffered reference output can be used as a reference source for other devices in the system. The internal reference requires a  $4.7\mu$ F low-ESR ceramic capacitor or tantalum capacitor connected between REF and AGND. For applications that require increased accuracy, power-down the internal reference by writing a 0 to the REFE bit of the Power1 register and connect an external reference source to REF. The valid external reference voltage range is 1.25V ±100mV.

#### **Crystal Oscillator**

The on-chip oscillator requires an external crystal (or resonator) connected between CLKIN and CLKOUT with an operating frequency of 32.768kHz. This oscillator is used for the RTC, alarm, signal-detect comparator, and PLL. The oscillator is operational down to 1.8V. In any crystal-based oscillator circuit, the oscillator frequency is based on the characteristics of the crystal. It is important to select a crystal that meets the design requirements, especially the capacitive load ( $C_L$ ) that must be placed across the crystal pins in order for the crystal to oscillate at its specified frequency. C<sub>1</sub> is the capacitance that the crystal needs to "see" from the oscillator circuit; it is not the capacitance of the crystal itself. The MAX1407/MAX1408/MAX1409/MAX1414 have 6pF of capacitance across the CLKIN and CLK-OUT pins. Choose a crystal with a 32.768kHz oscillation frequency and a 6pF capacitive load such as the C-002RX32-E from Epson Crystal. Using a crystal with a CL that is larger than the load capacitance of the oscillator circuit will cause the oscillator to run faster than the specified nominal frequency of the crystal. Conversely, using a crystal with a CL that is smaller than the load capacitance of the oscillator circuit will cause the oscillator to run slower than the specified nominal frequency of the crystal.

#### **Phase-Locked Loop (PLL) and FOUT**

An on-board phase-locked loop generates a 2.4576MHz clock at FOUT from the 32.768kHz crystal oscillator. FOUT can be used to clock a  $\mu$ P or other digital circuitry. Connect an 18nF ceramic capacitor from CPLL to AVDD to create the 2.4576MHz clock signal at FOUT. To power down the PLL, clear PLLE in the Power2 register (see *Power2 Register*) or write to the Sleep register. FOUT will be active for 1.95ms (tDFOF) after receiving either power-down command and then go low. This provides extra clock signals to the  $\mu$ P to complete a shutdown sequence. The PLL is active in all

modes except the sleep mode (see *Power Modes*). To reactivate the PLL, the following conditions must be met:  $AV_{DD}$  is greater than the low  $V_{DD}$  voltage monitor threshold, RESET is deasserted, and the PLLE bit is equal to "1". FOUT is enabled 31.25ms (tDFON) after the PLL is activated. At initial power-up, the PLL is enabled. If RESET is asserted while the PLL is running, the PLL does not shut down.

#### **Real-Time Clock (RTC)**

The integrated RTC provides the current second, minute, hour, date, month, day, year, century, and millenium information. An internally generated reference clock of 1.024kHz (derived from the 32.768kHz crystal) drives the RTC. The RTC operates in either 24-hour or 12-hour format with an AM/PM indicator (see *RTC\_Hour Register*). An internal calendar compensates for months with less than 31 days and includes leap year correction through the year 9999. The RTC operates from a supply voltage of +1.8V to +3.6V and consumes less than 1µA current.

#### Time of Day Alarm

The MAX1407/MAX1408/MAX1409/MAX1414 offer a time of day alarm which generates an interrupt when the RTC reaches a preset combination of seconds, minutes, hours, and day (see *Alarm Registers*). In addition to setting a "single-shot" alarm, the Time of Day Alarm can also be programmed to generate an alarm every second, minute, hour, day, or week. "Don't care" states can be inserted into one or more fields if it is desired for them to be ignored for the alarm condition. The Time of Day Alarm wakes up the device into Standby mode if it is in Sleep mode. The Time of Day Alarm operates from a supply voltage of +1.8V to +3.6V.

#### Interrupt (INT)

INT indicates one of three conditions. After receiving a valid interrupt (INT goes low), read the Status register and the Al\_Status register (if the alarm is enabled) to identify the source of the interrupt. The three sources of interrupts are from the CLK, SDC, and ALIRQ bits.

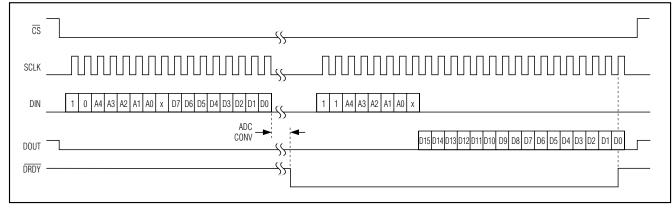

#### PLL Ready