# Single-Phase Energy Measurement IC with 8052 MCU, RTC, and LCD Driver

# ADE7116/ADE7156/ADE7166/ADE7169/ADE7566/ADE7569

#### **GENERAL FEATURES**

Wide supply voltage operation: 2.4 V to 3.7 V

Internal bipolar switch between regulated and battery inputs Ultralow power operation with power saving modes (PSM)

Full operation: 4 mA to 1.6 mA (PLL clock dependent) Battery mode: 3.2 mA to 400  $\mu$ A (PLL clock dependent) Sleep mode

Real-time clock (RTC) mode: 1.5 μA

RTC and LCD mode: 38 µA (LCD charge pump enabled)

Reference: 1.2 V ± 0.1% (10 ppm/°C drift)

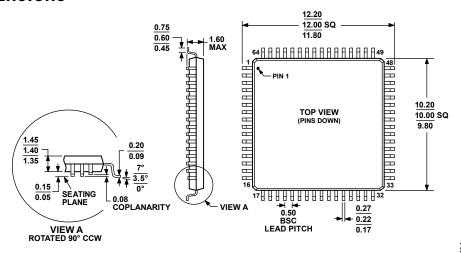

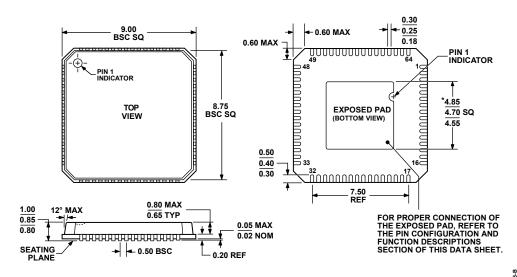

64-lead RoHS package options

Lead frame chip scale package (LFCSP)

Low profile quad flat package (LQFP)

Operating temperature range: -40°C to +85°C

#### **ENERGY MEASUREMENT FEATURES**

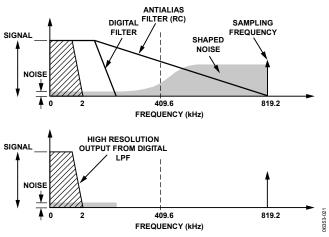

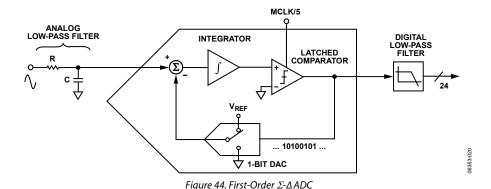

Proprietary analog-to-digital converters (ADCs) and digital signal processing (DSP) provide high accuracy active (watt), reactive (var), and apparent energy (volt-ampere (VA)) measurement

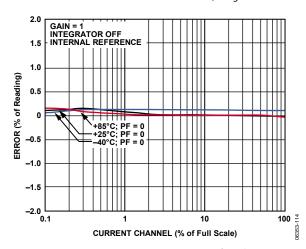

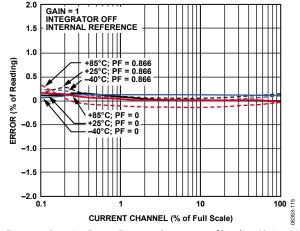

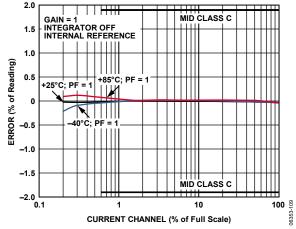

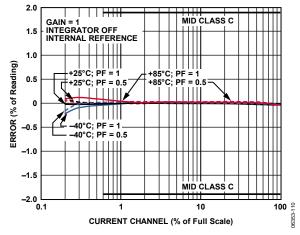

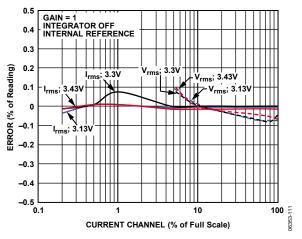

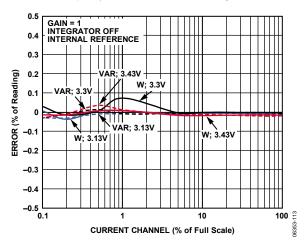

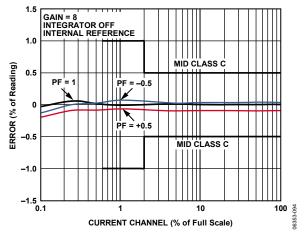

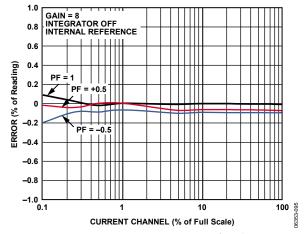

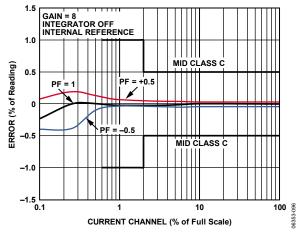

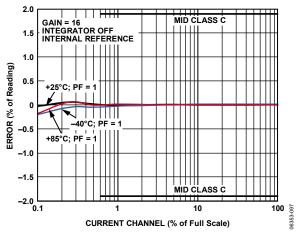

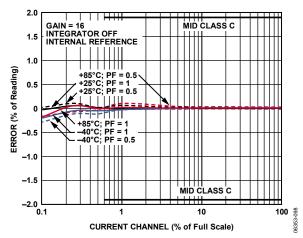

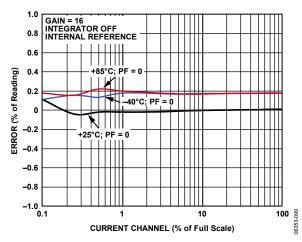

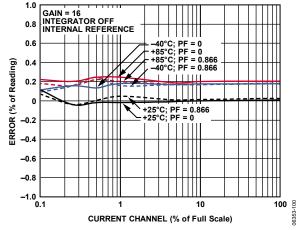

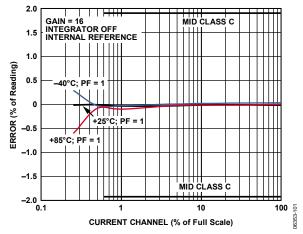

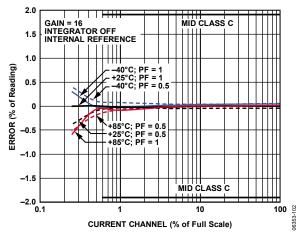

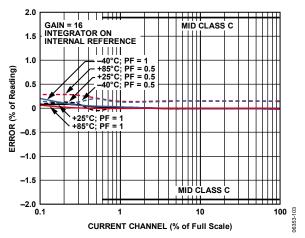

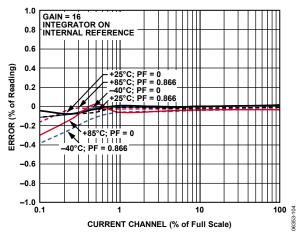

- <0.1% error on active energy over a dynamic range of 1000 to 1 @ 25°C

- <0.5% error on reactive energy over a dynamic range of 1000 to 1 @ 25°C (ADE7169 and ADE7569 only)

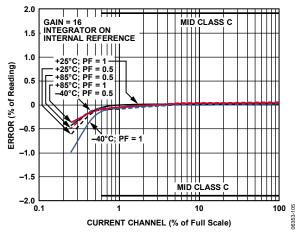

- <0.5% error on root mean square (rms) measurements over a dynamic range of 500 to 1 for current (I<sub>rms</sub>) and 100 to 1 for voltage (V<sub>rms</sub>) @ 25°C

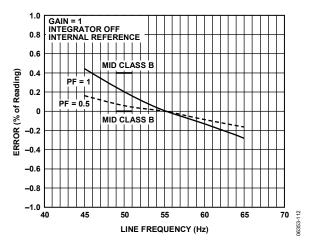

Supports IEC 62053-21, IEC 62053-22, and IEC 62053-23; EN 50470-3 Class A, Class B, and Class C; and ANSI C12-16

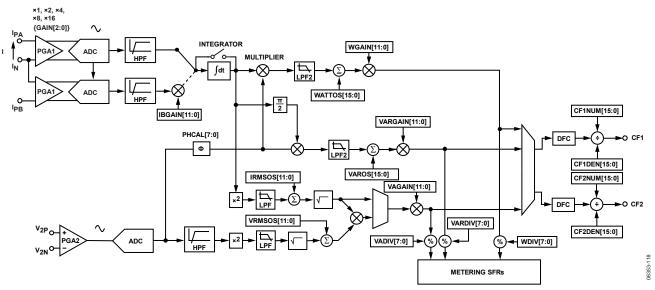

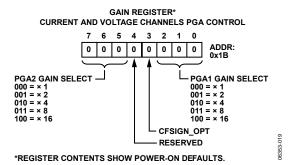

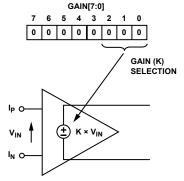

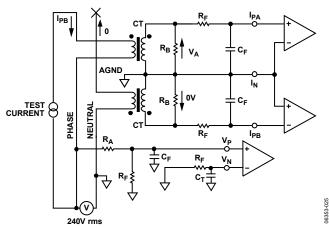

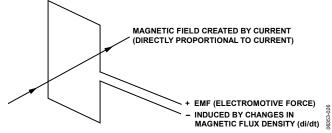

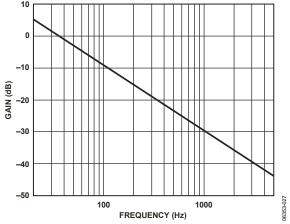

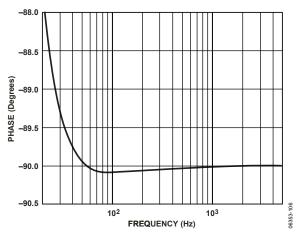

Differential input with programmable gain amplifiers (PGAs) supports shunts, current transformers, and di/dt current sensors (ADE7169 and ADE7569 only)

2 current inputs for antitamper detection in the ADE7116/ADE7156/ADE7166/ADE7169

High frequency outputs proportional to I<sub>rms</sub>, active, reactive, or apparent power (AP)

Table 1. Features Available on Each Part

| Feature                                       | Part No.                                                |

|-----------------------------------------------|---------------------------------------------------------|

| Antitamper                                    | ADE7116, ADE7156, ADE7166, ADE7169                      |

| Watt, VA, I <sub>rms</sub> , V <sub>rms</sub> | ADE7116, ADE7156, ADE7166, ADE7169,<br>ADE7566, ADE7569 |

| Var                                           | ADE7169, ADE7569                                        |

| di/dt Sensor                                  | ADE7169, ADE7569                                        |

#### MICROPROCESSOR FEATURES

8052-based core

Single-cycle 4 MIPS 8052 core 8052-compatible instruction set

32.768 kHz external crystal with on-chip PLL

2 external interrupt sources

External reset pin

Low power battery mode

Wake-up from I/O, temperature change<sup>1</sup>, alarm, and universal asynchronous receiver/transmitter (UART)

LCD driver operation

**Temperature measurement**

Real-time clock (RTC)

Counter for seconds, minutes, and hours

Automatic battery switchover for RTC backup

Operation down to 2.4 V

Ultralow battery supply current: 1.5  $\mu A$

Selectable output frequency: 1 Hz to 16 kHz

Embedded digital crystal frequency compensation for calibration and temperature variation of 2 ppm resolution

**Integrated LCD driver**

108-segment driver for the ADE7566/ADE7569 and 104-segment driver for the ADE7116/ADE7156/ADE7169

$2\times$ ,  $3\times$ , or  $4\times$  multiplexing

LCD voltages generated internally<sup>2</sup> or with external resistors Internal adjustable drive voltages up to 5 V independent of power supply level<sup>2</sup>

**On-chip peripherals**

**UART** interface

SPI or I<sup>2</sup>C

**Watchdog timer**

Power supply management with user-selectable levels

Memory: 16 kB flash memory, 512 bytes RAM

**Development tools**

Single-pin emulation

IDE-based assembly and C-source debugging

<sup>&</sup>lt;sup>1</sup> Not available in the ADE7116.

<sup>&</sup>lt;sup>2</sup> Not available in the ADE7116 or ADE7156.

# **TABLE OF CONTENTS**

| General Features                                       | Fault Detection.   |

|--------------------------------------------------------|--------------------|

| Energy Measurement Features                            | di/dt Current Sei  |

| Microprocessor Features                                | ADE7169/ADE7       |

| Revision History                                       | Power Quality M    |

| General Description4                                   | Phase Compensa     |

| Functional Block Diagrams4                             | RMS Calculation    |

| Specifications6                                        | Active Power Ca    |

| Energy Metering6                                       | Active Energy Ca   |

| Analog Peripherals7                                    | Reactive Power (   |

| Digital Interface8                                     | Reactive Energy    |

| Timing Specifications                                  | Apparent Power     |

| Absolute Maximum Ratings15                             | Apparent Energy    |

| Thermal Resistance                                     | Ampere-Hour A      |

| ESD Caution                                            | Energy-to-Frequ    |

| Pin Configurations and Function Descriptions           | Energy Register    |

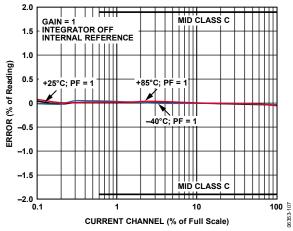

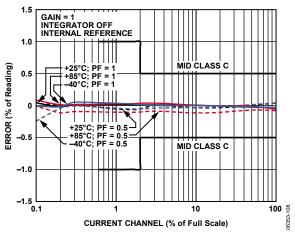

| Typical Performance Characteristics                    | Energy Measure     |

| Performance Curves for the ADE7169 and ADE7569 Only 25 | Temperature, Batte |

| Terminology                                            | Temperature Me     |

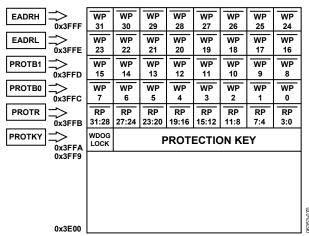

| Special Function Register (SFR) Mapping27              | Battery Measure    |

| Power Management                                       | External Voltage   |

| Power Management Register Details                      | 8052 MCU Core A    |

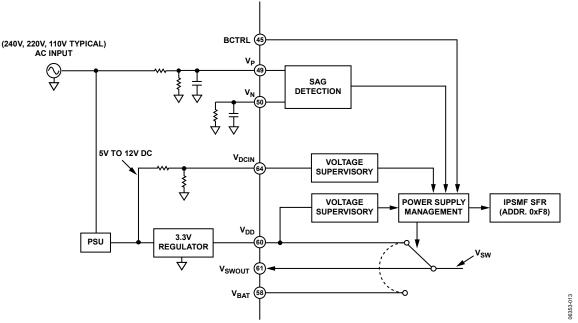

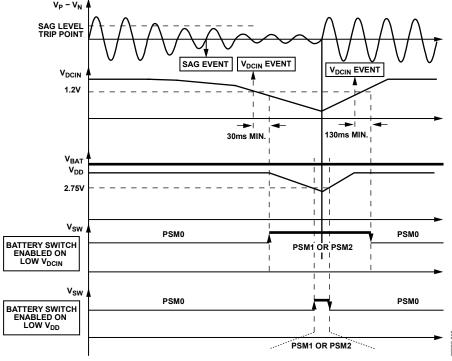

| Power Supply Architecture                              | MCU Registers      |

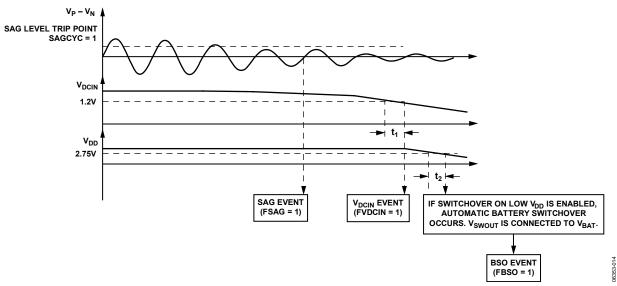

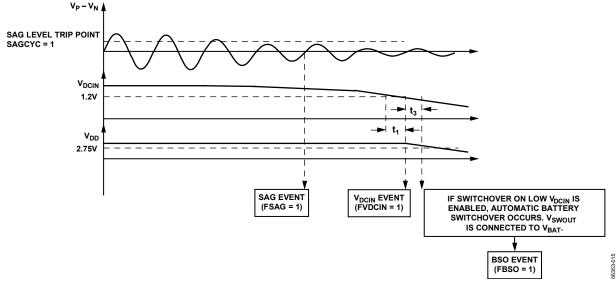

| Battery Switchover                                     | Basic 8052 Regis   |

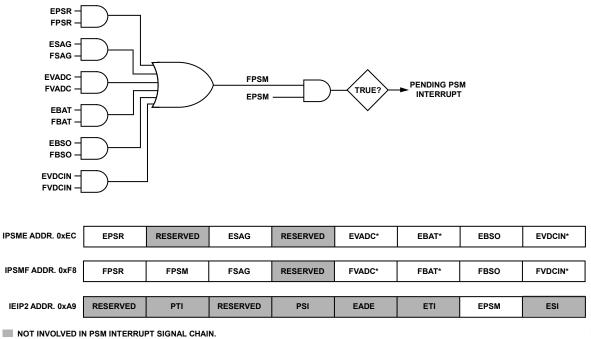

| Power Supply Management (PSM) Interrupt                | Standard 8052 Sl   |

| Using the Power Supply Features                        | Memory Overvi      |

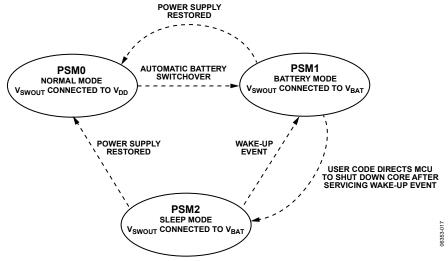

| Operating Modes                                        | Addressing Mod     |

| PSM0 (Normal Mode)                                     | Instruction Set    |

| PSM1 (Battery Mode)                                    | Read-Modify-W      |

|                                                        | Instructions Tha   |

| PSM2 (Sleep Mode)                                      | Dual Data Pointers |

| 3.3 V Peripherals and Wake-Up Events                   | Interrupt System   |

| Transitioning Between Operating Modes                  | Standard 8052 Ir   |

| Using the Power Management Features                    | Interrupt Archite  |

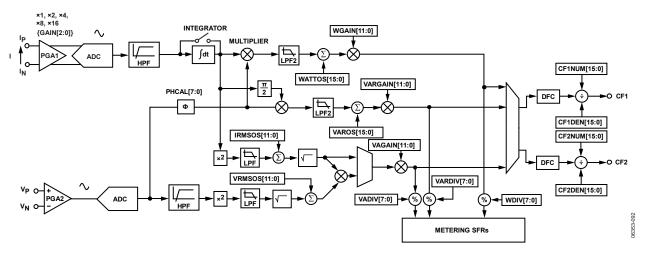

| Energy Measurement                                     | Interrupt Registe  |

| Access to Energy Measurement SFRs                      | Interrupt Priorit  |

| Access to Internal Energy Measurement Registers40      | Interrupt Flags    |

| Energy Measurement Registers43                         |                    |

| Energy Measurement Internal Register Details44         | Interrupt Vectors  |

| Interrupt Status/Enable SFRs47                         | Interrupt Latence  |

| Analog Inputs                                          | Context Saving     |

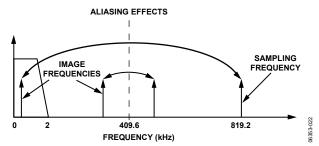

| Analog-to-Digital Conversion50                         | Watchdog Timer     |

| Fault Detection                                                     | . 54 |

|---------------------------------------------------------------------|------|

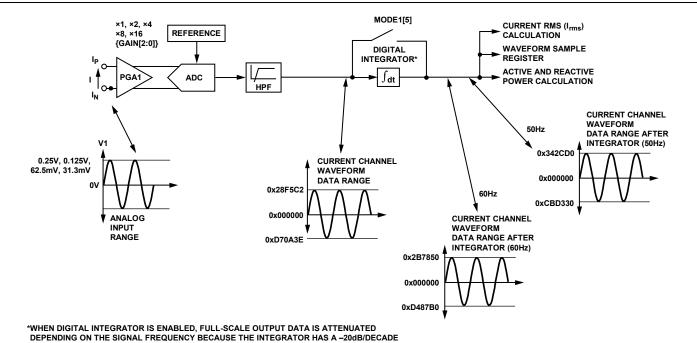

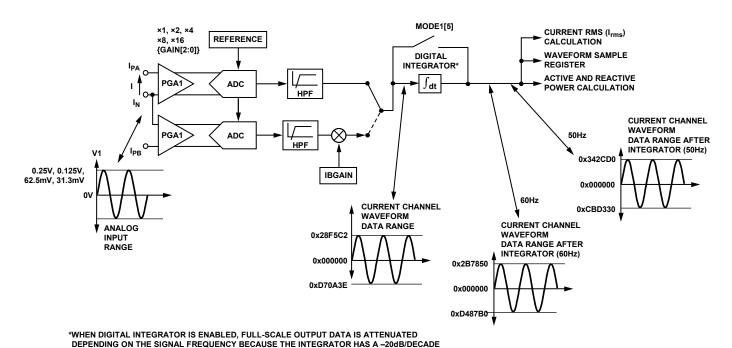

| di/dt Current Sensor and Digital Integrator for the ADE7169/ADE7569 | . 55 |

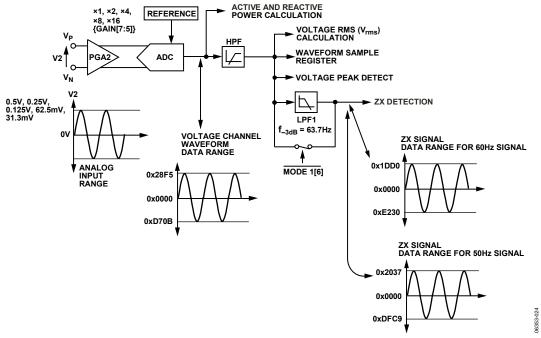

| Power Quality Measurements                                          | 57   |

| Phase Compensation                                                  | . 59 |

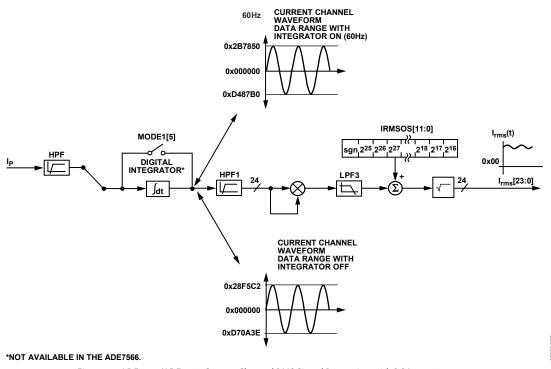

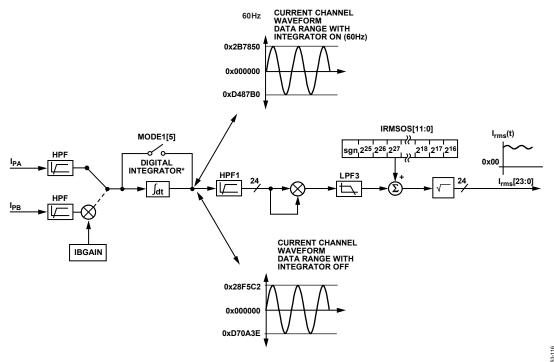

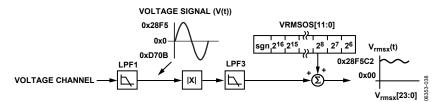

| RMS Calculation                                                     | . 59 |

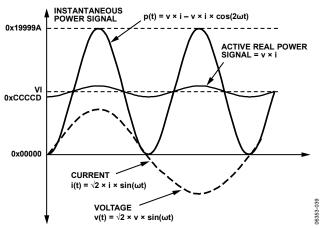

| Active Power Calculation                                            | 62   |

| Active Energy Calculation                                           | 64   |

| Reactive Power Calculation (ADE7169/ADE7569)                        | 67   |

| Reactive Energy Calculation (ADE7169/ADE7569)                       | 68   |

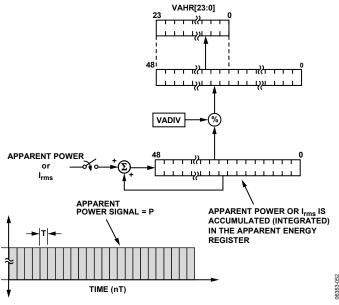

| Apparent Power Calculation                                          | 72   |

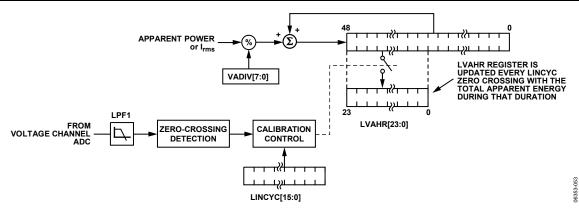

| Apparent Energy Calculation                                         | . 73 |

| Ampere-Hour Accumulation                                            | 74   |

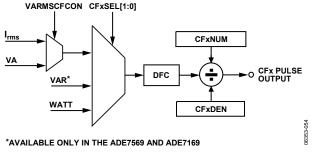

| Energy-to-Frequency Conversion                                      | 75   |

| Energy Register Scaling                                             | .76  |

| Energy Measurement Interrupts                                       | 76   |

| mperature, Battery, and Supply Voltage Measurements                 | 77   |

| Temperature Measurement                                             | . 79 |

| Battery Measurement                                                 | . 79 |

| External Voltage Measurement                                        | 80   |

| 52 MCU Core Architecture                                            | 82   |

| MCU Registers                                                       | 82   |

| Basic 8052 Registers                                                | 84   |

| Standard 8052 SFRs                                                  | 85   |

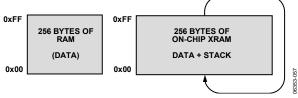

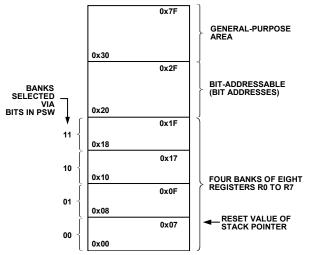

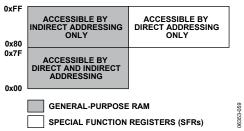

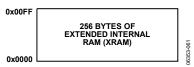

| Memory Overview                                                     | 85   |

| Addressing Modes                                                    | 86   |

| Instruction Set                                                     | 88   |

| Read-Modify-Write Instructions                                      | 90   |

| Instructions That Affect Flags                                      | 90   |

| ual Data Pointers                                                   | 92   |

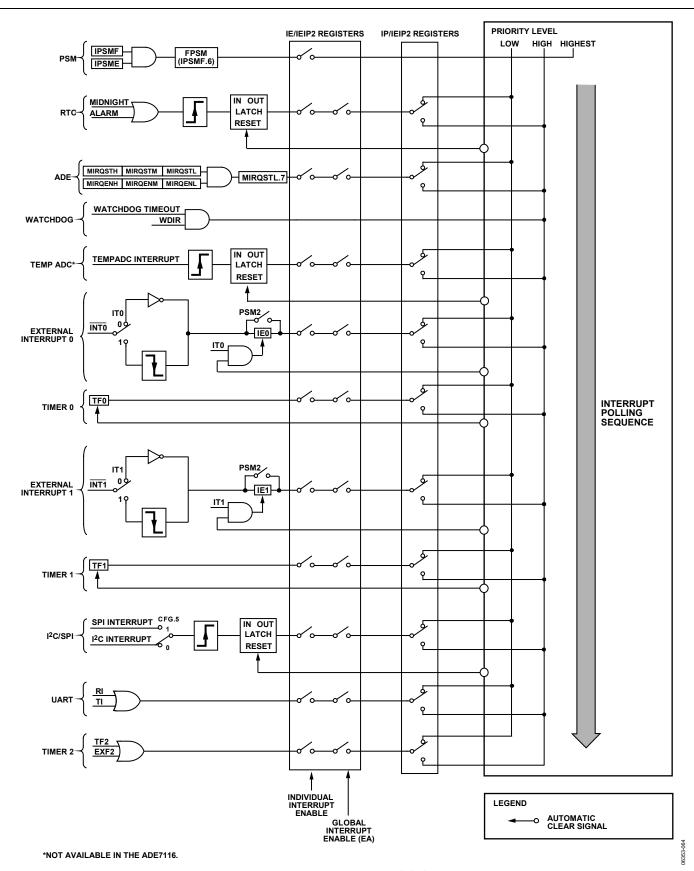

| terrupt System                                                      | 93   |

| Standard 8052 Interrupt Architecture                                | 93   |

| Interrupt Architecture                                              | 93   |

| Interrupt Registers                                                 | 93   |

| Interrupt Priority                                                  | 94   |

| Interrupt Flags                                                     | 95   |

| Interrupt Vectors                                                   | 97   |

| Interrupt Latency                                                   | 97   |

| Context Saving                                                      | 97   |

| atchdog Timer                                                       | 98   |

| LCD Driver                      | RTC Calibration                             | 125 |

|---------------------------------|---------------------------------------------|-----|

| LCD Registers                   | UART Serial Interface                       | 126 |

| LCD Setup                       | UART SFRs                                   | 126 |

| LCD Timing and Waveforms 103    | UART Operation Modes                        | 129 |

| Blink Mode 104                  | UART Baud Rate Generation                   | 130 |

| Display Element Control104      | UART Additional Features                    | 132 |

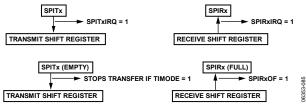

| Voltage Generation 105          | Serial Peripheral Interface (SPI)           | 133 |

| LCD External Circuitry106       | SPI Registers                               | 133 |

| LCD Function in PSM2 Mode 106   | SPI Pins                                    | 136 |

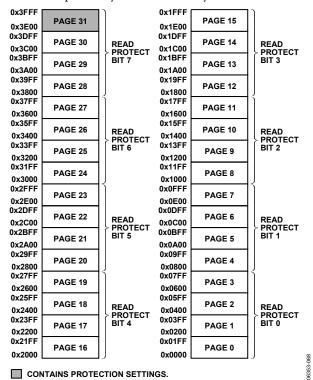

| Flash Memory                    | SPI Master Operating Modes                  | 137 |

| Flash Memory Overview           | SPI Interrupt and Status Flags              | 138 |

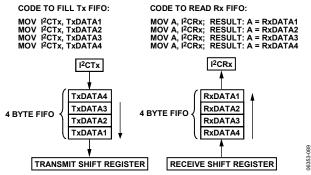

| Flash Memory Organization 109   | I <sup>2</sup> C-Compatible Interface       | 139 |

| Using the Flash Memory109       | Serial Clock Generation                     | 139 |

| Protecting the Flash Memory113  | Slave Addresses                             | 139 |

| In-Circuit Programming114       | I <sup>2</sup> C Registers                  | 139 |

| Timers                          | Read and Write Operations                   | 140 |

| Timer Registers 115             | I <sup>2</sup> C Receive and Transmit FIFOs | 141 |

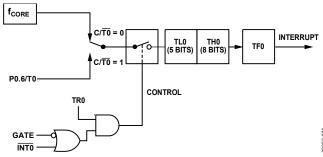

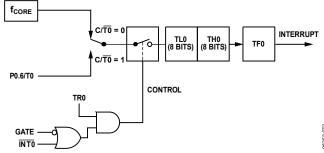

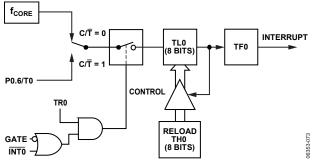

| Timer 0 and Timer 1             | I/O Ports                                   | 142 |

| Timer 2                         | Parallel I/O                                | 142 |

| PLL                             | I/O Registers                               | 143 |

| PLL Registers                   | Port 0                                      | 146 |

| Real-Time Clock (RTC)           | Port 1                                      | 146 |

| RTC SFRs 121                    | Port 2                                      | 146 |

| Read and Write Operations 124   | Determining the Version of the Part         | 147 |

| RTC Modes 124                   | Outline Dimensions                          | 148 |

| RTC Interrupts                  | Ordering Guide                              | 149 |

| REVISION HISTORY                |                                             |     |

| 11/08—Rev. A to Rev. B          |                                             |     |

| Added ADE7116/ADE7156           |                                             |     |

| 12/07—Rev. 0 to Rev. A          |                                             |     |

| Added ADE7166/ADE7169 Universal |                                             |     |

11/07—Revision 0: Initial Version

### **GENERAL DESCRIPTION**

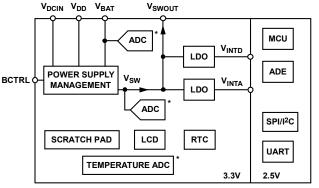

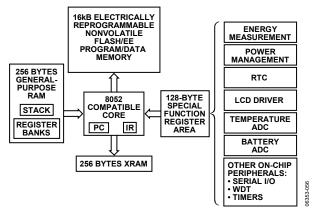

The ADE7116/ADE7156/ADE7166/ADE7169/ADE7566/ADE7569¹ integrate the Analog Devices, Inc., energy (ADE) metering IC analog front end and fixed function DSP solution with an enhanced 8052 MCU core, an RTC, an LCD driver, and all the peripherals to make an electronic energy meter with an LCD display in a single part.

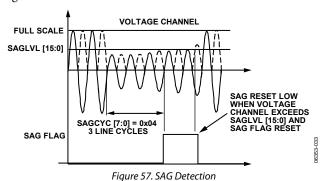

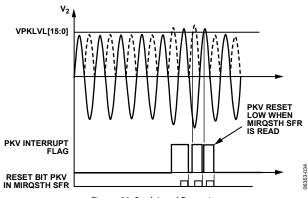

The ADE measurement core includes active, reactive, and apparent energy calculations, as well as voltage and current rms measurements. This information is accessible for energy billing by using the built-in energy scalars. Many power line supervisory features such as SAG, peak, and zero crossing are included in the energy measurement DSP to simplify energy meter design.

The microprocessor functionality includes a single-cycle 8052 core, a real-time clock with a power supply backup pin, an SPI or  $I^2C^*$  interface, and a UART interface. The ready-to-use information from the ADE core reduces the program memory size requirement, making it easy to integrate complicated design into 16~kB of flash memory.

The ADE7116/ADE7156/ADE7166/ADE7169/ADE7566/ADE7569 also include a 108-/104-segment LCD driver. In the ADE7166/ADE7169/ADE7566/ADE7569, this driver generates voltages capable of driving LCDs up to 5 V.

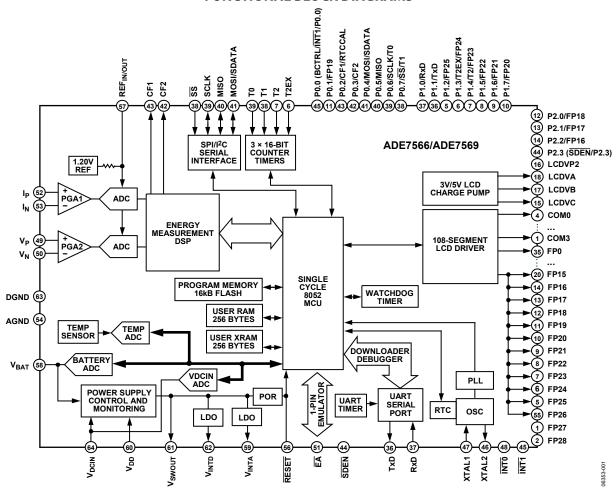

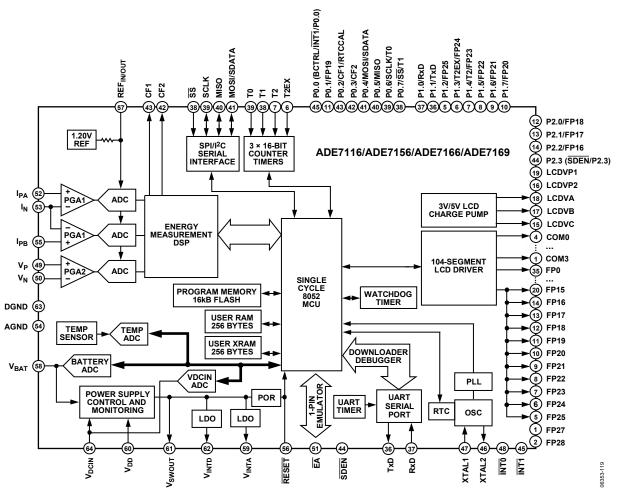

#### **FUNCTIONAL BLOCK DIAGRAMS**

Figure 1. ADE7566/ADE7569 Functional Block Diagram

<sup>&</sup>lt;sup>1</sup> Patents pending.

Figure 2. ADE7116/ADE7156/ADE7166/ADE7169 Functional Block Diagram

### **SPECIFICATIONS**

$V_{DD} = 3.3 \ V \pm 5\%, AGND = DGND = 0 \ V, on\text{-chip reference XTALx} = 32.768 \ kHz, T_{MIN} \ to \ T_{MAX} = -40 ^{\circ}C \ to \ +85 ^{\circ}C, unless \ otherwise \ noted.$

#### **ENERGY METERING**

Table 2.

| Parameter                                           | Min | Тур   | Max  | Unit         | Test Conditions/Comments                                          |

|-----------------------------------------------------|-----|-------|------|--------------|-------------------------------------------------------------------|

| MEASUREMENT ACCURACY <sup>1</sup>                   |     |       |      |              |                                                                   |

| Phase Error Between Channels <sup>2</sup>           |     |       |      |              |                                                                   |

| PF = 0.8 Capacitive                                 |     | ±0.05 |      | Degrees      | Phase lead: 37°                                                   |

| PF = 0.5 Inductive                                  |     | ±0.05 |      | Degrees      | Phase lag: 60°                                                    |

| Active Energy Measurement Error <sup>2</sup>        |     | 0.1   |      | % of reading | Over a dynamic range of 1000 to 1 at 25°C                         |

| AC Power Supply Rejection <sup>2</sup>              |     |       |      |              | $V_{DD} = 3.3 \text{ V} + 100 \text{ mV rms}/120 \text{ Hz}$      |

| Output Frequency Variation                          |     | 0.01  |      | %            | $I_{Px} = V_P = \pm 100 \text{ mV rms}$                           |

| DC Power Supply Rejection <sup>2</sup>              |     |       |      |              | $V_{DD} = 3.3 \text{ V} \pm 117 \text{ mV dc}$                    |

| Output Frequency Variation                          |     | 0.01  |      | %            |                                                                   |

| Active Energy Measurement Bandwidth <sup>1</sup>    |     | 8     |      | kHz          |                                                                   |

| Reactive Energy Measurement Error <sup>2, 3</sup>   |     | 0.5   |      | % of reading | Over a dynamic range of 1000 to 1 at 25°C                         |

| V <sub>rms</sub> Measurement Error <sup>2</sup>     |     | 0.5   |      | % of reading | Over a dynamic range of 100 to 1 at 25°C                          |

| V <sub>rms</sub> Measurement Bandwidth <sup>1</sup> |     | 3.9   |      | kHz          |                                                                   |

| I <sub>rms</sub> Measurement Error <sup>2</sup>     |     | 0.5   |      | % of reading | Over a dynamic range of 500 to 1 at 25°C                          |

| I <sub>rms</sub> Measurement Bandwidth <sup>1</sup> |     | 3.9   |      | kHz          |                                                                   |

| ANALOG INPUTS                                       |     |       |      |              |                                                                   |

| Maximum Signal Levels                               |     |       | ±400 | mV peak      | V <sub>P</sub> – V <sub>N</sub> differential input                |

| ADE7566/ADE7569                                     |     |       | ±400 | mV peak      | $I_P - I_N$ differential input                                    |

| ADE7116/ADE7156/ADE7166/ADE7169                     |     |       | ±250 | mV peak      | $I_{PA} - I_{N}$ and $I_{PB} - I_{N}$ differential inputs         |

| Input Impedance (DC)                                |     | 770   |      | kΩ           | ·                                                                 |

| ADC Offset Error <sup>2</sup>                       |     | ±10   |      | mV           | PGA1 = PGA2 = 1                                                   |

|                                                     |     | ±1    |      | mV           | PGA1 = 16                                                         |

| Gain Error <sup>2</sup>                             |     |       |      |              |                                                                   |

| Current Channel                                     |     | ±3    |      | %            | $I_{PA} = I_{PB} = 0.4 \text{ V dc or } I_P = 0.4 \text{ V dc}$   |

| Voltage Channel                                     |     | ±3    | +3   | %            | $V_P - V_N = 0.4 \text{ V dc}$                                    |

| Gain Error Match                                    |     | ±0.2  |      | %            |                                                                   |

| CF1 AND CF2 PULSE OUTPUT                            |     |       |      |              |                                                                   |

| Maximum Output Frequency                            |     | 13.5  |      | kHz          | $V_P - V_N = 400 \text{ mV peak}, I_{PA} - I_N = 250 \text{ mV},$ |

|                                                     |     |       |      |              | PGA1 = 2 sine wave                                                |

| Duty Cycle                                          |     | 50    |      | %            | If CF1 or CF2 frequency, >5.55 Hz                                 |

| Active High Pulse Width                             |     | 90    |      | ms           | If CF1 or CF2 frequency, <5.55 Hz                                 |

| FAULT DETECTION⁴                                    |     |       |      |              |                                                                   |

| Fault Detection Threshold                           |     |       |      |              |                                                                   |

| Inactive Input ≠ Active Input                       |     | 6.25  |      | % of active  | I <sub>PA</sub> or I <sub>PB</sub> active                         |

| Input Swap Threshold                                |     |       |      |              |                                                                   |

| Inactive Input > Active Input                       |     | 6.25  |      | % of active  | I <sub>PA</sub> or I <sub>PB</sub> active                         |

| Accuracy Fault Mode Operation                       |     |       |      |              |                                                                   |

| $I_{PA}$ Active, $I_{PB} = AGND$                    |     | 0.1   |      | % of reading | Over a dynamic range of 500 to 1                                  |

| $I_{PB}$ Active, $I_{PA} = AGND$                    |     | 0.1   |      | % of reading | Over a dynamic range of 500 to 1                                  |

| Fault Detection Delay                               |     | 3     |      | Seconds      | -                                                                 |

| Swap Delay                                          |     | 3     |      | Seconds      |                                                                   |

<sup>&</sup>lt;sup>1</sup> These specifications are not production tested but are guaranteed by design and/or characterization data on production release.

$<sup>^{\</sup>rm 2}$  See the Terminology section for definition.

<sup>&</sup>lt;sup>3</sup> This function is not available in the ADE7166 or ADE7566.

<sup>&</sup>lt;sup>4</sup> This function is not available in the ADE7566 or ADE7569.

### **ANALOG PERIPHERALS**

Table 3.

| Parameter                                                             | Min         | Тур  | Max   | Unit     | Test Conditions/Comments                                                        |

|-----------------------------------------------------------------------|-------------|------|-------|----------|---------------------------------------------------------------------------------|

| INTERNAL ADCs (BATTERY, TEMPERATURE, V <sub>DCIN</sub> ) <sup>1</sup> |             |      |       |          |                                                                                 |

| Power Supply Operating Range                                          | 2.4         |      | 3.7   | ٧        | Measured on V <sub>swout</sub>                                                  |

| No Missing Codes <sup>2</sup>                                         | 8           |      |       | Bits     |                                                                                 |

| Conversion Delay <sup>3</sup>                                         |             | 38   |       | μs       |                                                                                 |

| ADC Gain                                                              |             |      |       |          |                                                                                 |

| V <sub>DCIN</sub> Measurement                                         |             | 15.3 |       | mV/LSB   |                                                                                 |

| V <sub>BAT</sub> Measurement                                          |             | 14.6 |       | mV/LSB   |                                                                                 |

| Temperature Measurement                                               |             | 0.78 |       | °C/LSB   |                                                                                 |

| ADC Offset                                                            |             |      |       |          |                                                                                 |

| V <sub>DCIN</sub> Measurement at 3 V                                  |             | 206  |       | LSB      |                                                                                 |

| V <sub>BAT</sub> Measurement at 3.7 V                                 |             | 205  |       | LSB      |                                                                                 |

| Temperature Measurement at 25°C                                       |             | 129  |       | LSB      |                                                                                 |

| V <sub>DCIN</sub> Analog Input                                        |             |      |       |          |                                                                                 |

| Maximum Signal Levels                                                 | 0           |      | 3.3   | ٧        |                                                                                 |

| Input Impedance (DC)                                                  | 1           |      |       | ΜΩ       |                                                                                 |

| Low V <sub>DCIN</sub> Detection Threshold                             | 1.09        | 1.2  | 1.27  | V        |                                                                                 |

| POWER-ON RESET (POR)                                                  | 1           |      |       | <u> </u> |                                                                                 |

| V <sub>DD</sub> POR                                                   |             |      |       |          |                                                                                 |

| Detection Threshold                                                   | 2.5         |      | 2.95  | ٧        |                                                                                 |

| POR Active Timeout Period                                             |             | 33   |       | ms       |                                                                                 |

| V <sub>SWOUT</sub> POR                                                |             | 33   |       | 1113     |                                                                                 |

| Detection Threshold                                                   | 1.8         |      | 2.2   | V        |                                                                                 |

| POR Active Timeout Period                                             | 1.0         | 20   | 2.2   | ms       |                                                                                 |

| V <sub>INTD</sub> POR                                                 |             | 20   |       | 1113     |                                                                                 |

| Detection Threshold                                                   | 2.0         |      | 2.25  | V        |                                                                                 |

| POR Active Timeout Period                                             | 2.0         | 16   | 2.23  | ms       |                                                                                 |

| V <sub>INTA</sub> POR                                                 |             | 10   |       | 1113     |                                                                                 |

| Detection Threshold                                                   | 2.05        |      | 2.25  | V        |                                                                                 |

| POR Active Timeout Period                                             | 2.03        | 120  | 2.23  | ms       |                                                                                 |

| BATTERY SWITCHOVER                                                    |             | 120  |       | 1113     |                                                                                 |

| Voltage Operating Range (V <sub>SWOUT</sub> )                         | 2.4         |      | 3.7   | V        |                                                                                 |

| V <sub>DD</sub> to V <sub>BAT</sub> Switching                         | 2.4         |      | 3.7   | V        |                                                                                 |

| Switching Threshold (V <sub>DD</sub> )                                | 2.5         |      | 2.95  | V        |                                                                                 |

| Switching Delay                                                       | 2.5         | 10   | 2.93  |          | When V <sub>DD</sub> to V <sub>BAT</sub> switch activated by V <sub>DD</sub>    |

| Switching Delay                                                       |             | 30   |       | ns       | When V <sub>DD</sub> to V <sub>BAT</sub> switch activated by V <sub>DCI</sub>   |

| V <sub>BAT</sub> to V <sub>DD</sub> Switching                         |             | 30   |       | ms       | When vod to vear switch activated by vecil                                      |

| Switching Threshold (V <sub>DD</sub> )                                | 2.5         |      | 2.95  | V        |                                                                                 |

|                                                                       | 2.5         | 20   | 2.95  |          | Board on V > 2.75 V                                                             |

| Switching Delay                                                       |             | 30   |       | ms<br>A  | Based on $V_{DD} > 2.75 \text{ V}$                                              |

| V <sub>SWOUT</sub> to V <sub>BAT</sub> Leakage Current                |             | 10   |       | nA       | $V_{BAT} = 0 \text{ V, } V_{SWOUT} = 3.43 \text{ V, } T_A = 25^{\circ}\text{C}$ |

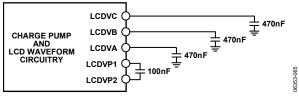

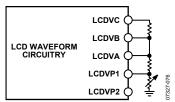

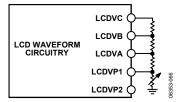

| LCD, CHARGE PUMP ACTIVE <sup>4</sup>                                  | 100         |      |       | _        |                                                                                 |

| Charge Pump Capacitance Between LCDVP1 and LCDVP2                     | 100         |      |       | nF       |                                                                                 |

| LCDVA, LCDVB, LCDVC Decoupling Capacitance                            | 470         |      |       | nF       |                                                                                 |

| LCDVA                                                                 | 0           |      | 1.75  | V        |                                                                                 |

| LCDVB                                                                 | 0           |      | 3.5   | V        | 1/3 bias mode                                                                   |

| LCDVC                                                                 | 0           |      | 5.3   | V        | 1/3 bias mode                                                                   |

| V1 Segment Line Voltage                                               | LCDVA – 0.1 |      | LCDVA | V        | Current on segment line = $-2 \mu A$                                            |

| V2 Segment Line Voltage                                               | LCDVB - 0.1 |      | LCDVB | V        | Current on segment line = $-2 \mu A$                                            |

| V3 Segment Line Voltage                                               | LCDVC - 0.1 |      | LCDVC | V        | Current on segment line = $-2 \mu A$                                            |

| DC Voltage Across Segment and COMx Pin                                |             |      | 50    | mV       | LCDVC – LCDVB, LCDVC – LCDVA, or<br>LCDVB – LCDVA                               |

| Parameter                            | Min         | Тур | Max   | Unit   | Test Conditions/Comments             |

|--------------------------------------|-------------|-----|-------|--------|--------------------------------------|

| LCD, RESISTOR LADDER ACTIVE          |             |     |       |        |                                      |

| Leakage Current                      |             | ±20 |       | nA     | 1/2 and 1/3 bias modes, no load      |

| V1 Segment Line Voltage              | LCDVA - 0.1 |     | LCDVA | V      | Current on segment line = $-2 \mu A$ |

| V2 Segment Line Voltage              | LCDVB - 0.1 |     | LCDVB | V      | Current on segment line = $-2 \mu A$ |

| V3 Segment Line Voltage              | LCDVC - 0.1 |     | LCDVC | V      | Current on segment line = $-2 \mu A$ |

| ON-CHIP REFERENCE                    |             |     |       |        |                                      |

| Reference Error                      |             |     | ±0.9  | mV     | $T_A = 25$ °C                        |

| Power Supply Rejection               |             | 80  |       | dB     |                                      |

| Temperature Coefficient <sup>2</sup> |             | 10  | 50    | ppm/°C |                                      |

#### **DIGITAL INTERFACE**

Table 4.

| Parameter                                                | Min    | Тур    | Max  | Unit   | Test Conditions/Comments                                          |

|----------------------------------------------------------|--------|--------|------|--------|-------------------------------------------------------------------|

| LOGIC INPUTS <sup>1</sup>                                |        |        |      |        |                                                                   |

| All Inputs Except XTAL1, XTAL2, BCTRL, INTO, INT1, RESET |        |        |      |        |                                                                   |

| Input High Voltage, V <sub>INH</sub>                     | 2.0    |        |      | V      |                                                                   |

| Input Low Voltage, V <sub>INL</sub>                      |        |        | 0.8  | V      |                                                                   |

| BCTRL, INTO, INT1, RESET                                 |        |        |      |        |                                                                   |

| Input High Voltage, V <sub>INH</sub>                     | 1.3    |        |      | V      |                                                                   |

| Input Low Voltage, V <sub>INL</sub>                      |        |        | 8.0  | V      |                                                                   |

| Input Currents                                           |        |        |      |        |                                                                   |

| RESET                                                    |        |        | 100  | nA     | $\overline{\text{RESET}} = V_{\text{SWOUT}} = 3.3 \text{ V}$      |

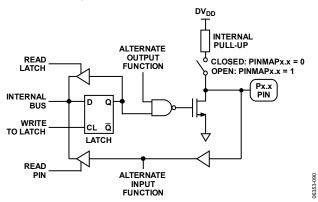

| Port 0, Port 1, Port 2                                   |        |        | ±100 | nA     | Internal pull-up disabled, input = 0 V or V <sub>SWOUT</sub>      |

|                                                          | -3.75  |        | -8.5 | μΑ     | Internal pull-up enabled, input = 0 V, V <sub>SWOUT</sub> = 3.3 V |

| Input Capacitance                                        |        | 10     |      | pF     | All digital inputs                                                |

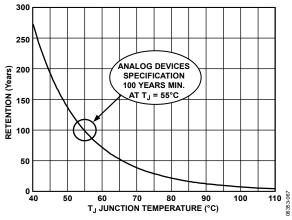

| FLASH MEMORY                                             |        |        |      |        |                                                                   |

| Endurance <sup>2</sup>                                   | 20,000 |        |      | Cycles |                                                                   |

| Data Retention <sup>3</sup>                              | 20     |        |      | Years  | T <sub>J</sub> = 85°C                                             |

| CRYSTAL OSCILLATOR <sup>4</sup>                          |        |        |      |        |                                                                   |

| Crystal Equivalent Series Resistance                     | 30     |        | 50   | kΩ     |                                                                   |

| Crystal Frequency                                        | 32     | 32.768 | 33.5 | kHz    |                                                                   |

| XTAL1 Input Capacitance                                  |        | 12     |      | pF     |                                                                   |

| XTAL2 Output Capacitance                                 |        | 12     |      | pF     |                                                                   |

| MCU CLOCK RATE (f <sub>CORE</sub> )                      |        | 4.096  |      | MHz    | Crystal = 32.768 kHz and CD bits = 000                            |

|                                                          |        | 32     |      | kHz    | Crystal = 32.768 kHz and CD bits = 111                            |

| LOGIC OUTPUTS                                            |        |        |      |        |                                                                   |

| Output High Voltage, V <sub>OH</sub>                     | 2.4    |        |      | V      | $V_{DD} = 3.3 \text{ V} \pm 5\%$                                  |

| Isource                                                  |        |        | 80   | μΑ     |                                                                   |

| Output Low Voltage, V <sub>OL</sub> <sup>5</sup>         |        |        | 0.4  | V      | $V_{DD} = 3.3 \text{ V} \pm 5\%$                                  |

| Isink                                                    |        |        | 2    | mA     |                                                                   |

| START-UP TIME <sup>6</sup>                               |        |        |      |        |                                                                   |

| PSM0 Power-On Time                                       |        | 880    |      | ms     | V <sub>DD</sub> at 2.75 V to PSM0 code execution                  |

| From Power Saving Mode 1 (PSM1)                          |        |        |      |        |                                                                   |

| PSM1 to PSM0                                             |        | 130    |      | ms     | V <sub>DD</sub> at 2.75 V to PSM0 code execution                  |

| From Power Saving Mode 2 (PSM2)                          |        |        |      |        |                                                                   |

| PSM2 to PSM1                                             |        | 48     |      | ms     | Wake-up event to PSM1 code execution                              |

| PSM2 to PSM0                                             |        | 186    |      | ms     | V <sub>DD</sub> at 2.75 V to PSM0 code execution                  |

<sup>&</sup>lt;sup>1</sup> This function is not available in the ADE7116. <sup>2</sup> These specifications are not production tested but are guaranteed by design and/or characterization data on production release. <sup>3</sup> Delay between ADC conversion request and interrupt set.

<sup>&</sup>lt;sup>4</sup> This function is not available in the ADE7116 or ADE7156.

| Parameter                                                    | Min  | Тур | Max  | Unit | Test Conditions/Comments                                                                |

|--------------------------------------------------------------|------|-----|------|------|-----------------------------------------------------------------------------------------|

| POWER SUPPLY INPUTS                                          |      |     |      |      |                                                                                         |

| $V_{DD}$                                                     | 3.13 | 3.3 | 3.46 | V    |                                                                                         |

| $V_{BAT}$                                                    | 2.4  | 3.3 | 3.7  | V    |                                                                                         |

| INTERNAL POWER SUPPLY SWITCH (V <sub>SWOUT</sub> )           |      |     |      |      |                                                                                         |

| V <sub>BAT</sub> to V <sub>SWOUT</sub> On Resistance         |      |     | 22   | Ω    | $V_{BAT} = 2.4 \text{ V}$                                                               |

| V <sub>DD</sub> to V <sub>SWOUT</sub> On Resistance          |      |     | 10.2 | Ω    | $V_{DD} = 3.13 \text{ V}$                                                               |

| V <sub>BAT</sub> to/from V <sub>DD</sub> Switching Open Time |      | 40  |      | ns   |                                                                                         |

| BCTRL State Change and Switch Delay                          |      | 18  |      | μs   |                                                                                         |

| V <sub>SWOUT</sub> Output Current Drive                      |      |     | 6    | mA   |                                                                                         |

| POWER SUPPLY OUTPUTS                                         |      |     |      |      |                                                                                         |

| $V_{INTA}$                                                   | 2.3  |     | 2.70 | V    |                                                                                         |

| $V_{INTD}$                                                   | 2.3  |     | 2.70 | V    |                                                                                         |

| V <sub>INTA</sub> Power Supply Rejection                     |      | 60  |      | dB   |                                                                                         |

| V <sub>INTD</sub> Power Supply Rejection                     |      | 50  |      | dB   |                                                                                         |

| POWER SUPPLY CURRENTS                                        |      |     |      |      |                                                                                         |

| Current in Normal Mode (PSM0)                                |      | 4   | 5.3  | mA   | $f_{CORE} = 4.096$ MHz, LCD and meter active                                            |

|                                                              |      | 2.1 |      | mA   | $f_{CORE} = 1.024$ MHz, LCD and meter active                                            |

|                                                              |      | 1.6 |      | mA   | f <sub>CORE</sub> = 32.768 kHz, LCD and meter active                                    |

|                                                              |      | 3   | 3.9  | mA   | $f_{CORE}$ = 4.096 MHz, metering ADC and DSP powered down                               |

| Current in PSM1                                              |      | 3.2 | 5.05 | mA   | $f_{CORE} = 4.096$ MHz, LCD active, $V_{BAT} = 3.7$ V                                   |

|                                                              |      | 880 |      | μΑ   | f <sub>CORE</sub> = 1.024 MHz, LCD active                                               |

| Current in PSM2                                              |      | 38  |      | μΑ   | LCD active with charge pump at $3.3 \text{ V} + \text{RTC}$ , $V_{BAT} = 3.3 \text{ V}$ |

|                                                              |      | 1.5 |      | μΑ   | RTC only, $T_A = 25$ °C, $V_{BAT} = 3.3 \text{ V}$                                      |

<sup>&</sup>lt;sup>1</sup> Specifications guaranteed by design. <sup>2</sup> Endurance is qualified as per JEDEC Standard 22 Method A117 and measured at –40°C, +25°C, +85°C, and +125°C.

<sup>&</sup>lt;sup>3</sup> Retention lifetime equivalent at junction temperature (T<sub>J</sub>) = 85°C as per JEDEC Standard 22 Method A117. Retention lifetime derates with junction temperature.

<sup>&</sup>lt;sup>4</sup> Recommended crystal specifications.

<sup>&</sup>lt;sup>5</sup> Test carried out with all the I/Os set to a low output level.

<sup>6</sup> Delay between power supply valid and execution of first instruction by 8052 core.

#### **TIMING SPECIFICATIONS**

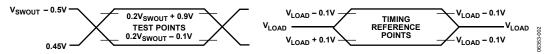

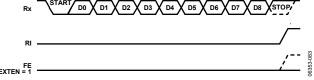

AC inputs during testing were driven at  $V_{\text{SWOUT}}-0.5~V$  for Logic 1 and at 0.45 V for Logic 0. Timing measurements were made at  $V_{\text{IH}}$  minimum for Logic 1 and at  $V_{\text{IL}}$  maximum for Logic 0, as shown in Figure 3.

For timing purposes, a port pin is no longer floating when a 100 mV change from load voltage occurs. A port pin begins to

float when a 100 mV change from the loaded  $V_{\text{OH}}/V_{\text{OL}}$  level occurs, as shown in Figure 3.

$C_{\text{LOAD}}$  for all outputs is equal to 80 pF, unless otherwise noted.  $V_{\text{DD}}$  = 2.7 V to 3.6 V; all specifications  $T_{\text{MIN}}$  to  $T_{\text{MAX}}$ , unless otherwise noted.

Figure 3. Timing Waveform Characteristics

Table 5. Clock Input (External Clock Driven XTAL1) Parameter

| Parameter           |                                   | 32.768 kHz External Crystal |       |     |      |  |  |  |

|---------------------|-----------------------------------|-----------------------------|-------|-----|------|--|--|--|

|                     | Description                       | Min                         | Тур   | Max | Unit |  |  |  |

| t <sub>CK</sub>     | XTAL1 period                      |                             | 30.52 |     | μs   |  |  |  |

| <b>t</b> ckl        | XTAL1 width low                   |                             | 6.26  |     | μs   |  |  |  |

| t <sub>CKH</sub>    | XTAL1 width high                  |                             | 6.26  |     | μs   |  |  |  |

| t <sub>CKR</sub>    | XTAL1 rise time                   |                             | 9     |     | ns   |  |  |  |

| t <sub>CKF</sub>    | XTAL1 fall time                   |                             | 9     |     | ns   |  |  |  |

| 1/t <sub>CORE</sub> | Core clock frequency <sup>1</sup> |                             | 1.024 |     | MHz  |  |  |  |

<sup>&</sup>lt;sup>1</sup> The internal PLL locks onto a multiple (512×) of the 32.768 kHz external crystal frequency to provide a stable 4.096 MHz internal clock for the system. The core can operate at this frequency or at a binary submultiple defined by the CD bits of the POWCON SFR, Address 0xC5[2:0] (see Table 26).

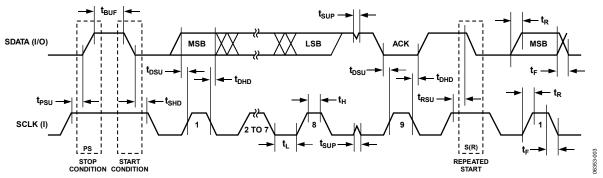

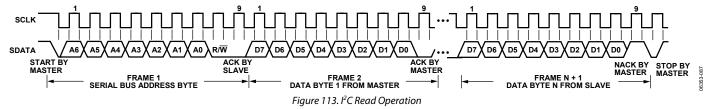

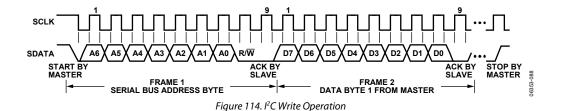

Table 6. I<sup>2</sup>C-Compatible Interface Timing Parameters (400 kHz)

| Parameter               | Description                                              | Тур    | Unit |

|-------------------------|----------------------------------------------------------|--------|------|

| t <sub>BUF</sub>        | Bus-free time between stop condition and start condition | 1.3    | μs   |

| t <sub>L</sub>          | SCLK low pulse width                                     | 1.36   | μs   |

| tн                      | SCLK high pulse width                                    | 1.14   | μs   |

| <b>t</b> <sub>SHD</sub> | Start condition hold time                                | 251.35 | μs   |

| t <sub>DSU</sub>        | Data setup time                                          | 740    | ns   |

| <b>t</b> <sub>DHD</sub> | Data hold time                                           | 400    | ns   |

| <b>t</b> <sub>RSU</sub> | Setup time for repeated start                            | 12.5   | ns   |

| t <sub>PSU</sub>        | Stop condition setup time                                | 400    | ns   |

| t <sub>R</sub>          | Rise time of both SCLK and SDATA                         | 200    | ns   |

| t <sub>F</sub>          | Fall time of both SCLK and SDATA                         | 300    | ns   |

| t <sub>SUP</sub> 1      | Pulse width of spike suppressed                          | 50     | ns   |

<sup>&</sup>lt;sup>1</sup> Input filtering on both the SCLK and SDATA inputs suppresses noise spikes of <50 ns.

Figure 4. I<sup>2</sup>C-Compatible Interface Timing

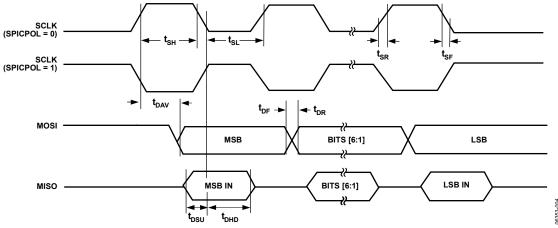

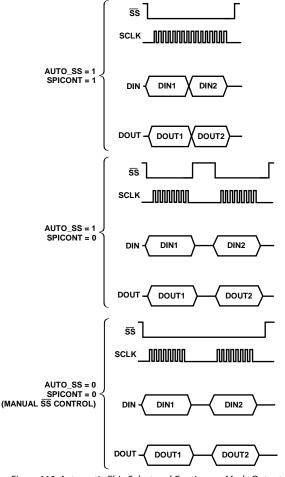

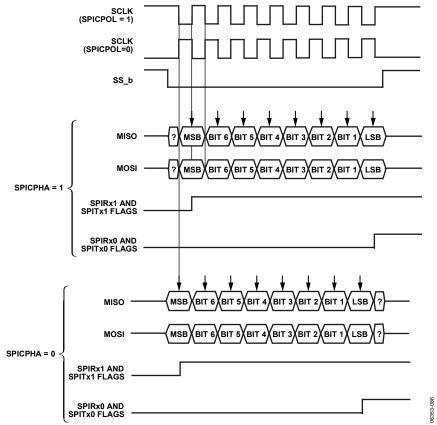

Table 7. SPI Master Mode Timing (SPICPHA = 1) Parameters

| Parameter        | Description                            | Min                                                | Тур | Max                     | Unit |

|------------------|----------------------------------------|----------------------------------------------------|-----|-------------------------|------|

| t <sub>SL</sub>  | SCLK low pulse width                   | 2 <sup>SPIR</sup> × t <sub>CORE</sub> <sup>1</sup> |     |                         | ns   |

| $t_{SH}$         | SCLK high pulse width                  | $2^{SPIR} \times t_{CORE}^{1}$                     |     |                         | ns   |

| t <sub>DAV</sub> | Data output valid after SCLK edge      |                                                    |     | $3 \times t_{CORE}^{1}$ | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge | 0                                                  |     |                         | ns   |

| t <sub>DHD</sub> | Data input hold time after SCLK edge   | t <sub>CORE</sub> 1                                |     |                         | ns   |

| t <sub>DF</sub>  | Data output fall time                  |                                                    | 19  |                         | ns   |

| t <sub>DR</sub>  | Data output rise time                  |                                                    | 19  |                         | ns   |

| t <sub>SR</sub>  | SCLK rise time                         |                                                    | 19  |                         | ns   |

| t <sub>SF</sub>  | SCLK fall time                         |                                                    | 19  |                         | ns   |

$<sup>^1</sup>$  t<sub>CORE</sub> depends on the clock divider or CD[2:0] bits of the POWCON SFR, Address 0xC5 (see Table 26); t<sub>CORE</sub> =  $2^{\text{CD}}/4.096$  MHz.

Figure 5. SPI Master Mode Timing (SPICPHA = 1)

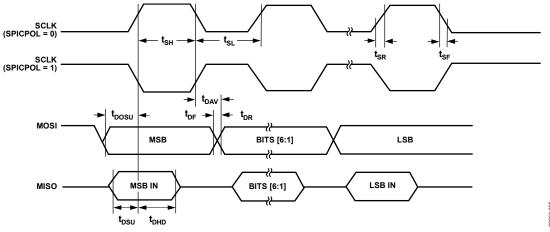

Table 8. SPI Master Mode Timing (SPICPHA = 0) Parameters

| Parameter         | Description                            | Min                            | Тур                            | Max                          | Unit |

|-------------------|----------------------------------------|--------------------------------|--------------------------------|------------------------------|------|

| t <sub>SL</sub>   | SCLK low pulse width                   | $2^{SPIR} \times t_{CORE}^{1}$ | $(SPIR + 1) \times t_{CORE^1}$ |                              | ns   |

| t <sub>SH</sub>   | SCLK high pulse width                  | $2^{SPIR} \times t_{CORE}^{1}$ | $(SPIR + 1) \times t_{CORE^1}$ |                              | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLK edge      |                                |                                | $3 \times t_{\text{CORE}^1}$ | ns   |

| t <sub>DOSU</sub> | Data output setup before SCLK edge     |                                |                                | 75                           | ns   |

| t <sub>DSU</sub>  | Data input setup time before SCLK edge | 0                              |                                |                              | ns   |

| t <sub>DHD</sub>  | Data input hold time after SCLK edge   | t <sub>CORE</sub> 1            |                                |                              | ns   |

| t <sub>DF</sub>   | Data output fall time                  |                                | 19                             |                              | ns   |

| t <sub>DR</sub>   | Data output rise time                  |                                | 19                             |                              | ns   |

| $t_{SR}$          | SCLK rise time                         |                                | 19                             |                              | ns   |

| t <sub>SF</sub>   | SCLK fall time                         |                                | 19                             |                              | ns   |

$<sup>^1</sup>$  t<sub>CORE</sub> depends on the clock divider or CD[2:0] bits of the POWCON SFR, Address 0xC5 (see Table 26); t<sub>CORE</sub> =  $2^{\text{CD}}/4.096$  MHz.

Figure 6. SPI Master Mode Timing (SPICPHA = 0)

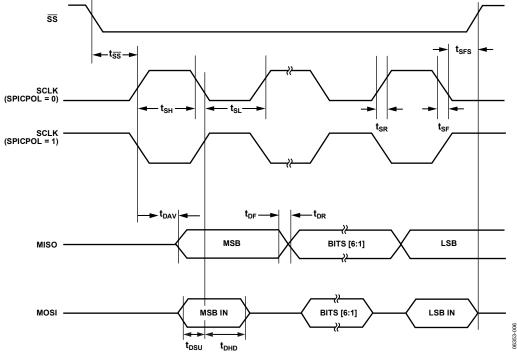

Table 9. SPI Slave Mode Timing (SPICPHA = 1) Parameters

| Parameter        | Description                            | Min                               | Тур | Max | Unit |

|------------------|----------------------------------------|-----------------------------------|-----|-----|------|

| t <sub>ss</sub>  | SS to SCLK edge                        | 145                               |     |     | ns   |

| t <sub>SL</sub>  | SCLK low pulse width                   | $6 \times t_{CORE}^{1}$           |     |     | ns   |

| t <sub>SH</sub>  | SCLK high pulse width                  | $6 \times t_{CORE}^{1}$           |     |     | ns   |

| t <sub>DAV</sub> | Data output valid after SCLK edge      |                                   |     | 25  | ns   |

| t <sub>DSU</sub> | Data input setup time before SCLK edge | 0                                 |     |     | ns   |

| $t_{DHD}$        | Data input hold time after SCLK edge   | $2 \times t_{CORE}^1 + 0.5 \mu s$ |     |     | μs   |

| $t_{DF}$         | Data output fall time                  |                                   | 19  |     | ns   |

| $t_{DR}$         | Data output rise time                  |                                   | 19  |     | ns   |

| t <sub>SR</sub>  | SCLK rise time                         |                                   | 19  |     | ns   |

| t <sub>SF</sub>  | SCLK fall time                         |                                   | 19  |     | ns   |

| t <sub>SFS</sub> | SS high after SCLK edge                | 0                                 |     |     | ns   |

$<sup>^{1}</sup>$   $t_{CORE}$  depends on the clock divider or CD[2:0] bits of the POWCON SFR, Address 0xC5 (see Table 26);  $t_{CORE} = 2^{CD}/4.096$  MHz.

Figure 7. SPI Slave Mode Timing (SPICPHA = 1)

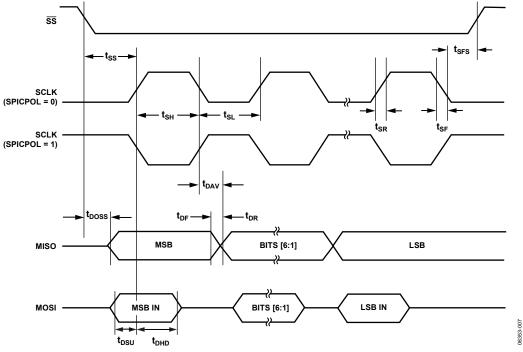

Table 10. SPI Slave Mode Timing (SPICPHA = 0) Parameters

| Parameter         | Description                            | Min                               | Тур | Max | Unit |

|-------------------|----------------------------------------|-----------------------------------|-----|-----|------|

| t <sub>ss</sub>   | SS to SCLK edge                        | 145                               |     |     | ns   |

| t <sub>SL</sub>   | SCLK low pulse width                   | $6 \times t_{CORE}^{1}$           |     |     | ns   |

| t <sub>SH</sub>   | SCLK high pulse width                  | $6 \times t_{CORE}^{1}$           |     |     | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLK edge      |                                   |     | 25  | ns   |

| $t_{DSU}$         | Data input setup time before SCLK edge | 0                                 |     |     | ns   |

| $t_{DHD}$         | Data input hold time after SCLK edge   | $2 \times t_{CORE}^1 + 0.5 \mu s$ |     |     | μs   |

| $t_{DF}$          | Data output fall time                  |                                   | 19  |     | ns   |

| $t_{DR}$          | Data output rise time                  |                                   | 19  |     | ns   |

| t <sub>SR</sub>   | SCLK rise time                         |                                   | 19  |     | ns   |

| t <sub>SF</sub>   | SCLK fall time                         |                                   | 19  |     | ns   |

| t <sub>DOSS</sub> | Data output valid after SS edge        | 0                                 |     |     | ns   |

| t <sub>SFS</sub>  | SS high after SCLK edge                | 0                                 |     |     | ns   |

$<sup>^{1}</sup>$  t<sub>CORE</sub> depends on the clock divider or CD[2:0] bits of the POWCON SFR, Address 0xC5 (see Table 26); t<sub>CORE</sub> =  $2^{\text{CD}}/4.096$  MHz.

Figure 8. SPI Slave Mode Timing (SPICPHA = 0)

### **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

Table 11.

| Parameter                                                                             | Rating                                        |

|---------------------------------------------------------------------------------------|-----------------------------------------------|

| V <sub>DD</sub> to DGND                                                               | -0.3 V to +3.7 V                              |

| V <sub>BAT</sub> to DGND                                                              | −0.3 V to +3.7 V                              |

| V <sub>DCIN</sub> to DGND                                                             | -0.3 V to V <sub>SWOUT</sub> + 0.3 V          |

| Input LCD Voltage to AGND, LCDVA,<br>LCDVB, LCDVC <sup>1</sup>                        | -0.3 V to V <sub>SWOUT</sub> + 0.3 V          |

| Analog Input Voltage to AGND, $V_P$ , $V_N$ , $I_P$ , $I_{PA}$ , $I_{PB}$ , and $I_N$ | -2 V to +2 V                                  |

| Digital Input Voltage to DGND                                                         | $-0.3 \text{ V to V}_{SWOUT} + 0.3 \text{ V}$ |

| Digital Output Voltage to DGND                                                        | -0.3 V to V <sub>SWOUT</sub> + 0.3 V          |

| Operating Temperature Range (Industrial)                                              | -40°C to +85°C                                |

| Storage Temperature Range                                                             | −65°C to +150°C                               |

| 64-Lead LQFP, Power Dissipation                                                       |                                               |

| Lead Temperature (Soldering, 30 sec)                                                  | 300°C                                         |

<sup>&</sup>lt;sup>1</sup> When used with external resistor divider.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

$\theta_{JA}$  is specified for the worst-case conditions, that is, a device soldered in a circuit board for surface-mount packages.

**Table 12. Thermal Resistance**

| Package Type  | θιΑ  | θις  | Unit |

|---------------|------|------|------|

| 64-Lead LQFP  | 60   | 20.5 | °C/W |

| 64-Lead LFCSP | 27.1 | 2.3  | °C/W |

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

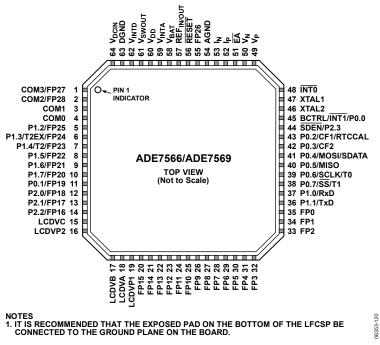

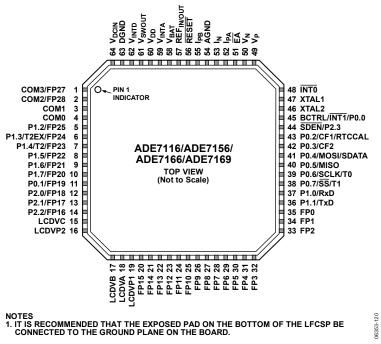

Figure 9. Pin Configuration for the ADE7566/ADE7569

**Table 13. Pin Function Descriptions**

| Pin No. | Mnemonic       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | COM3/FP27      | Common Output 3/LCD Segment Output 27. COM3 is used for the LCD backplane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2       | COM2/FP28      | Common Output 2/LCD Segment Output 28. COM2 is used for the LCD backplane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 3       | COM1           | Common Output 1. COM1 is used for the LCD backplane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 4       | COM0           | Common Output 0. COM0 is used for the LCD backplane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5       | P1.2/FP25      | General-Purpose Digital I/O Port 1.2/LCD Segment Output 25.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6       | P1.3/T2EX/FP24 | General-Purpose Digital I/O Port 1.3/Timer 2 Control Input/LCD Segment Output 24.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 7       | P1.4/T2/FP23   | General-Purpose Digital I/O Port 1.4/Timer 2 Input/LCD Segment Output 23.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 8       | P1.5/FP22      | General-Purpose Digital I/O Port 1.5/LCD Segment Output 22.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9       | P1.6/FP21      | General-Purpose Digital I/O Port 1.6/LCD Segment Output 21.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | P1.7/FP20      | General-Purpose Digital I/O Port 1.7/LCD Segment Output 20.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 11      | P0.1/FP19      | General-Purpose Digital I/O Port 0.1/LCD Segment Output 19.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 12      | P2.0/FP18      | General-Purpose Digital I/O Port 2.0/LCD Segment Output 18.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 13      | P2.1/FP17      | General-Purpose Digital I/O Port 2.1/LCD Segment Output 17.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 14      | P2.2/FP16      | General-Purpose Digital I/O Port 2.2/LCD Segment Output 16.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 15      | LCDVC          | This pin can be either an analog input when the LCD resistor driver is enabled or an analog output when the LCD charge pump is enabled. When this pin is an analog output, it should be decoupled with a 470 nF capacitor. When this pin is an analog input, it is internally connected to $V_{DD}$ . A resistor should be connected between this pin and LCDVB to generate the two highest voltages for the LCD waveforms (see the LCD Driver section).                                                                                                                                                  |

| 16      | LCDVP2         | This pin can be either an analog input when the LCD resistor driver is enabled or an analog output when the LCD charge pump is enabled. When this pin is an analog output, a 100 nF capacitor should be connected between this pin and LCDVP1. When this pin is an analog input, it is internally connected to LCDVP1 (see the LCD Driver section).                                                                                                                                                                                                                                                       |

| 17      | LCDVB          | This pin can be either an analog input when the LCD resistor driver is enabled or an analog output when the LCD charge pump is enabled. When this pin is an analog output, it should be decoupled with a 470 nF capacitor. When this pin is an analog input, a resistor should be connected between this pin and LCDVC to generate an intermediate voltage for the LCD driver. In 1/3 bias LCD mode, another resistor must be connected between this pin and LCDVA to generate another intermediate voltage. In 1/2 bias LCD mode, LCDVB and LCDVA are internally connected (see the LCD Driver section). |

| Pin No.  | Mnemonic                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18       | LCDVA                           | This pin can be either an analog input when the LCD resistor driver is enabled or an analog output when the LCD charge pump is enabled. When this pin is an analog output, it should be decoupled with a 470 nF capacitor. When this pin is an analog input, a resistor should be connected between this pin and LCDVP1 to generate an intermediate voltage for the LCD driver. In 1/3 bias LCD mode, another resistor must be connected between this pin and LCDVB to generate another intermediate voltage. In 1/2 bias LCD mode, LCDVA and LCDVB are internally connected (see the LCD Driver section). |

| 19       | LCDVP1                          | This pin can be either an analog input when the LCD resistor driver is enabled or an analog output when the LCD charge pump is enabled. When this pin is an analog output, a 100 nF capacitor should be connected between this pin and LCDVP2. When this pin is an analog input, a resistor should be connected between this pin and LCDVA to generate an intermediate voltage for the LCD driver. Another resistor must be connected between LCDVP1 and DGND to generate another intermediate voltage (see the LCD Driver section).                                                                       |

| 20 to 35 | FP15 to FP0                     | LCD Segment Output 15 to LCD Segment Output 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 36       | P1.1/TxD                        | General-Purpose Digital I/O Port 1.1/Transmitter Data Output (Asynchronous).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 37       | P1.0/RxD                        | General-Purpose Digital I/O Port 1.0/Receiver Data Input (Asynchronous).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

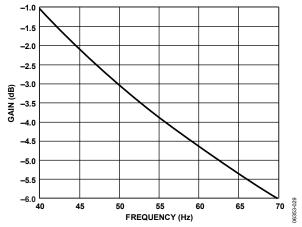

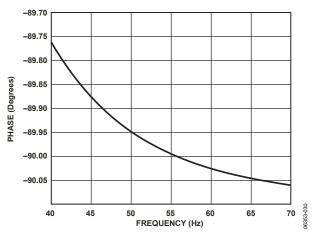

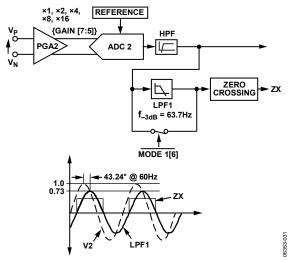

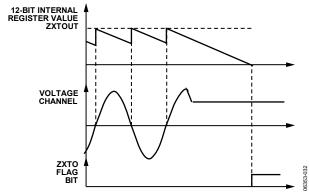

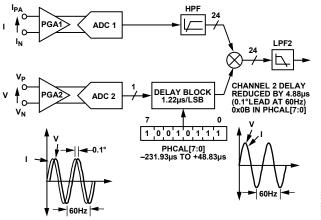

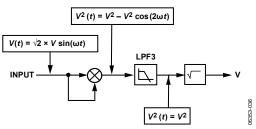

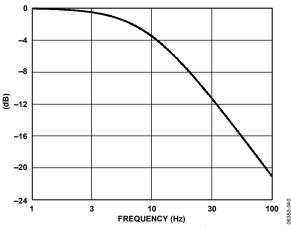

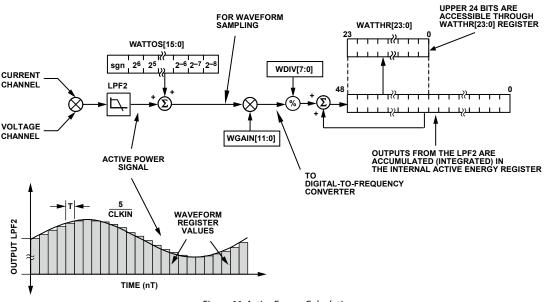

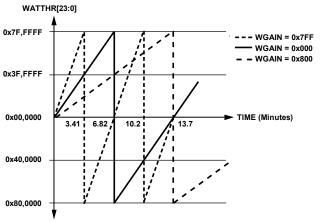

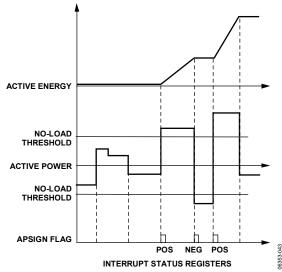

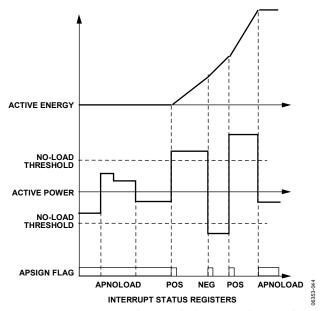

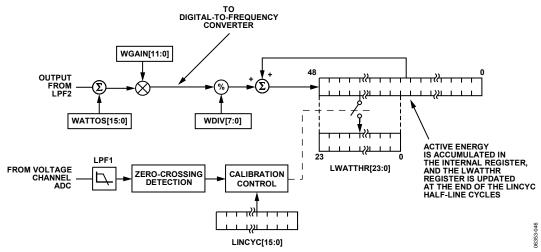

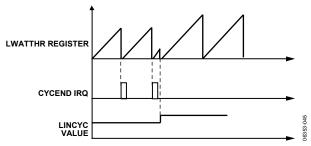

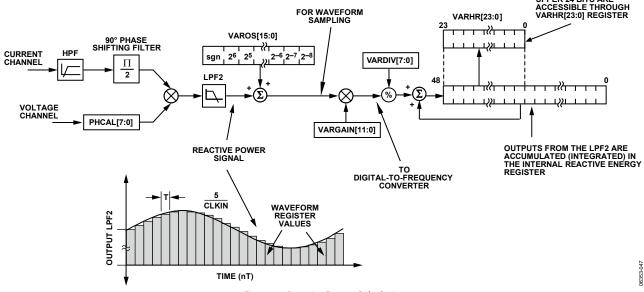

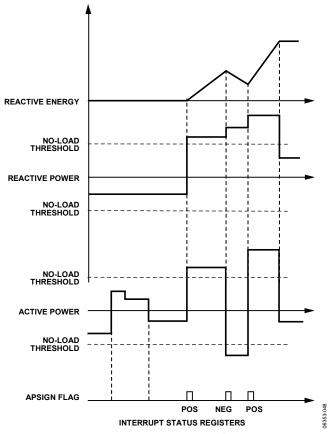

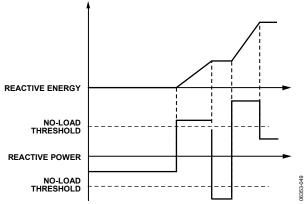

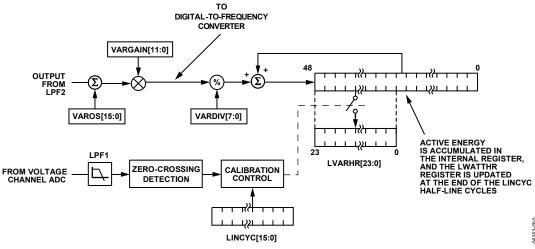

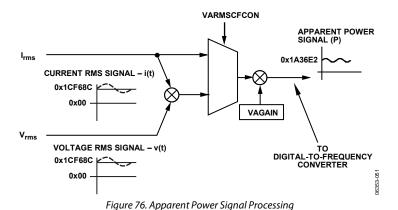

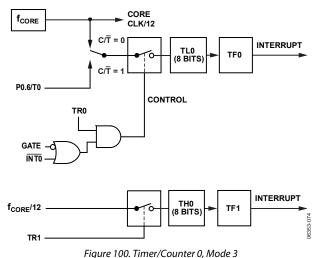

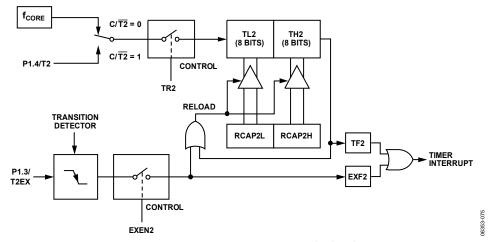

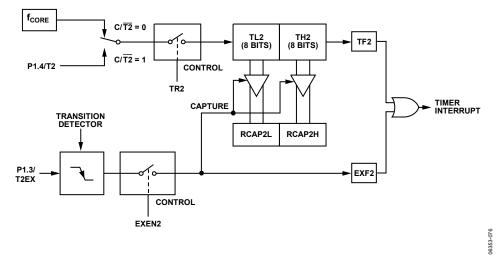

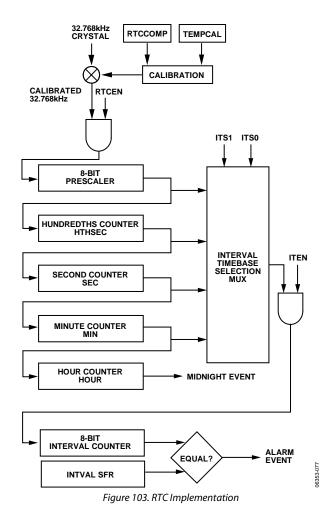

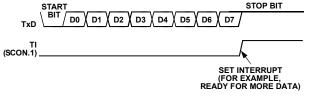

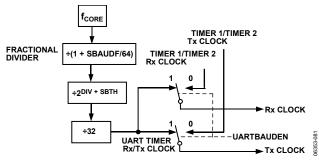

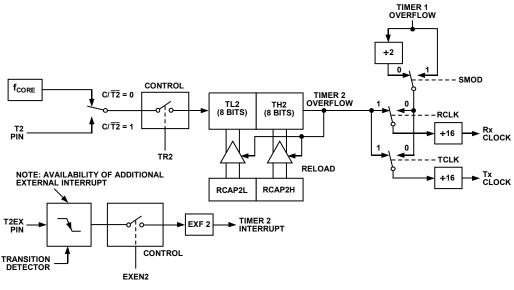

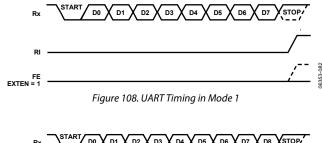

| 38       | P0.7/SS/T1                      | General-Purpose Digital I/O Port 0.7/Slave Select When SPI Is in Slave Mode/Timer 1 Input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |