# 16-bit Proprietary Microcontrollers

## F<sup>2</sup>MC-16LX MB90385 Series

## MB90387/387S/F387/F387S/MB90V495G

### ■ DESCRIPTION

MB90385 series devices are general-purpose high-performance 16-bit micro controllers designed for process control of consumer products, which require high-speed real-time processing. The devices of this series have the built-in full-CAN interface.

The system, inheriting the architecture of  $F^2MC^*$  family, employs additional instruction ready for high-level languages, expanded addressing mode, enhanced multiply-divide instructions, and enriched bit-processing instructions. Furthermore, employment of 32-bit accumulator achieves processing of long-word data (32 bits).

The peripheral resources of MB90385 series include the following:

8/10-bit A/D converter, UART (SCI), 8/16-bit PPG timer, 16-bit input-output timer (16-bit free-run timer, input capture 0, 1, 2, 3 (ICU)), and CAN controller.

\*: F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

### **■ FEATURES**

#### Clock

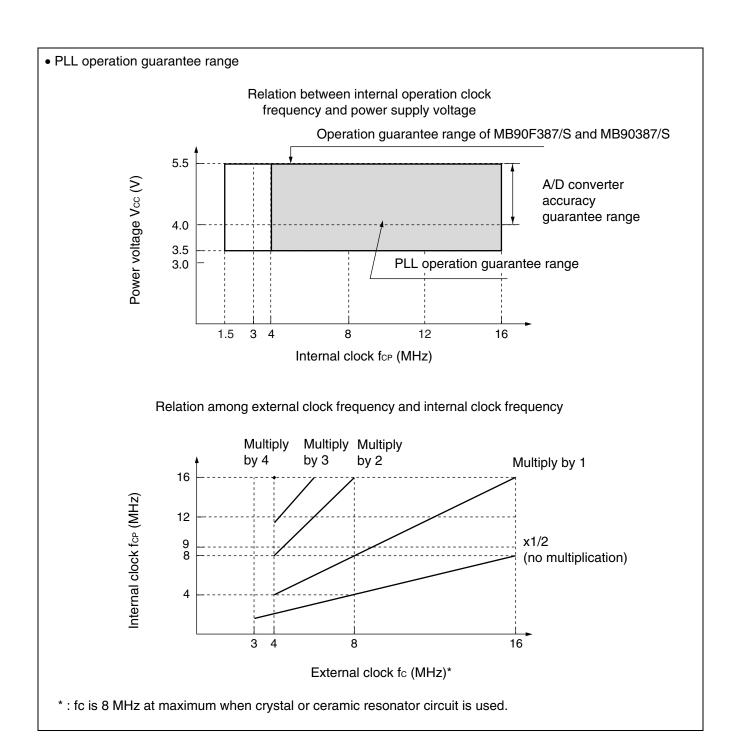

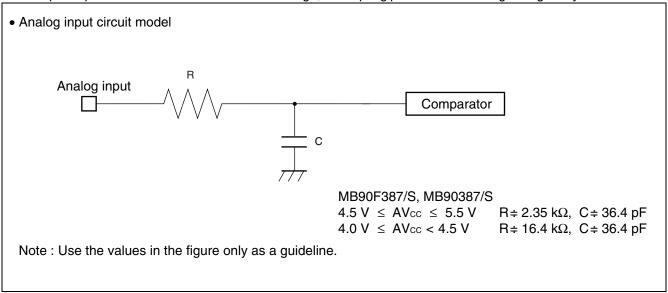

- · Built-in PLL clock frequency multiplication circuit

- Selection of machine clocks (PLL clocks) is allowed among frequency division by two on oscillation clock, and multiplication of 1 to 4 times of oscillation clock (for 4-MHz oscillation clock, 4 MHz to 16 MHz).

- Operation by sub-clock (8.192 kHz) is allowed. (MB90387, MB90F387)

- Minimum execution time of instruction: 62.5 ns (when operating with 4-MHz oscillation clock, and 4-time multiplied PLL clock).

(Continued)

For the information for microcontroller supports, see the following web site.

http://edevice.fujitsu.com/micom/en-support/

### • 16 Mbyte CPU memory space

· 24-bit internal addressing

### • Instruction system best suited to controller

- Wide choice of data types (bit, byte, word, and long word)

- Wide choice of addressing modes (23 types)

- Enhanced multiply-divide instructions and RETI instructions

- Enhanced high-precision computing with 32-bit accumulator

### • Instruction system compatible with high-level language (C language) and multitask

- · Employing system stack pointer

- Enhanced various pointer indirect instructions

- · Barrel shift instructions

### Increased processing speed

· 4-byte instruction queue

### • Powerful interrupt function with 8 levels and 34 factors

### • Automatic data transfer function independent of CPU

• Expanded intelligent I/O service function (EI2 OS): Maximum of 16 channels

### • Low power consumption (standby) mode

- Sleep mode (a mode that halts CPU operating clock)

- Time-base timer mode (a mode that operates oscillation clock, sub clock, time-base timer and watch timer only)

- Watch mode (a mode that operates sub clock and watch timer only)

- Stop mode (a mode that stops oscillation clock and sub clock)

- CPU blocking operation mode

### Process

CMOS technology

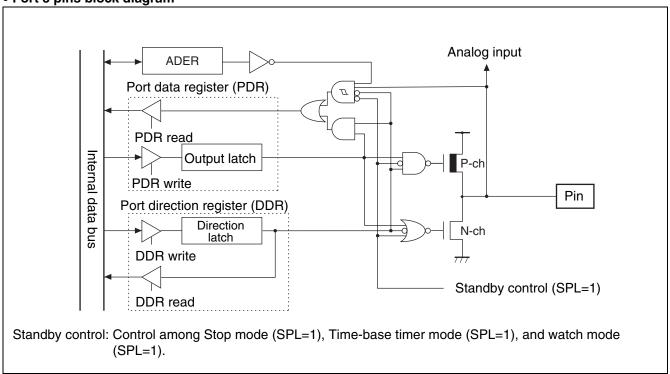

### • I/O port

• General-purpose input/output port (CMOS output) :

MB90387, MB90F387 : 34 ports (including 4 high-current output ports) MB90387S, MB90F387S : 36 ports (including 4 high-current output ports)

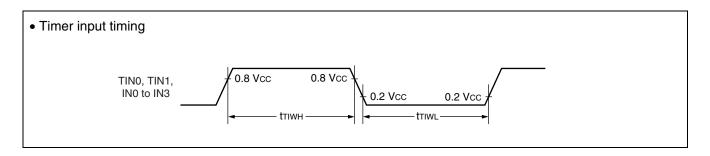

#### • Timer

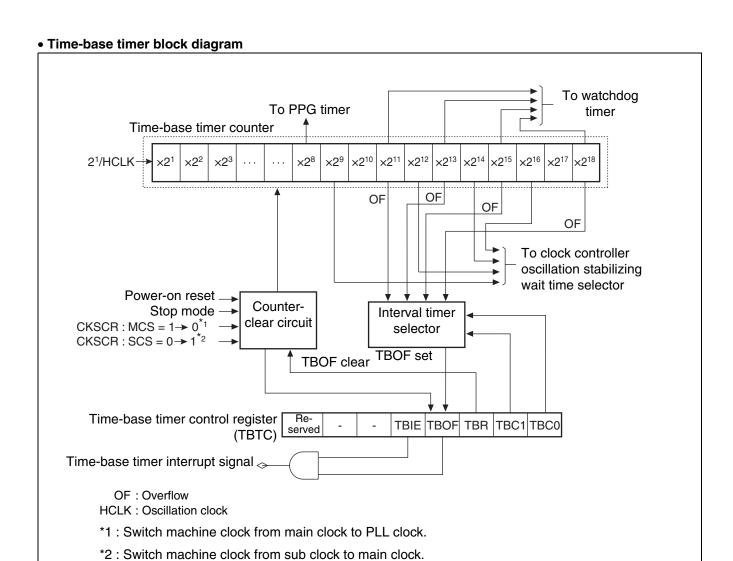

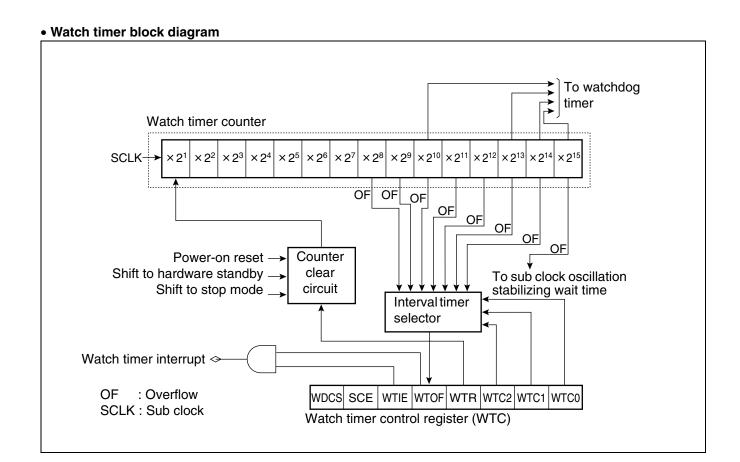

- Time-base timer, watch timer, watchdog timer: 1 channel

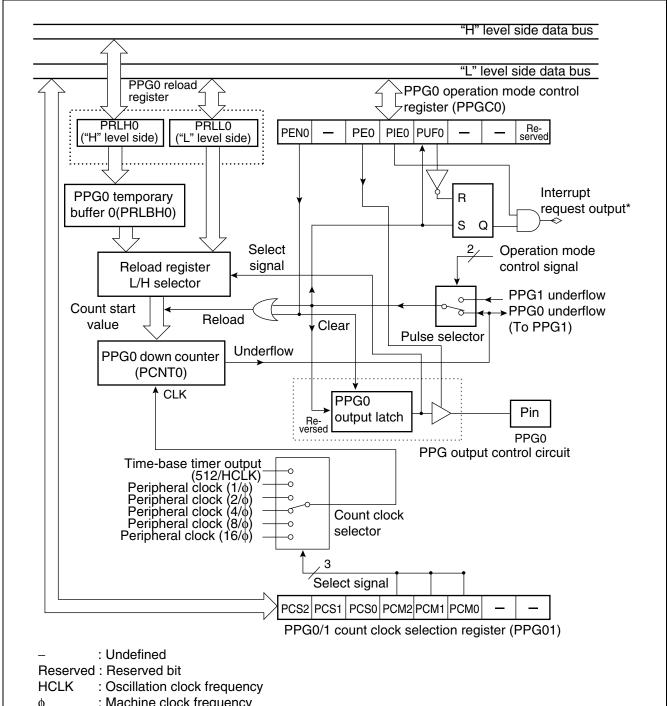

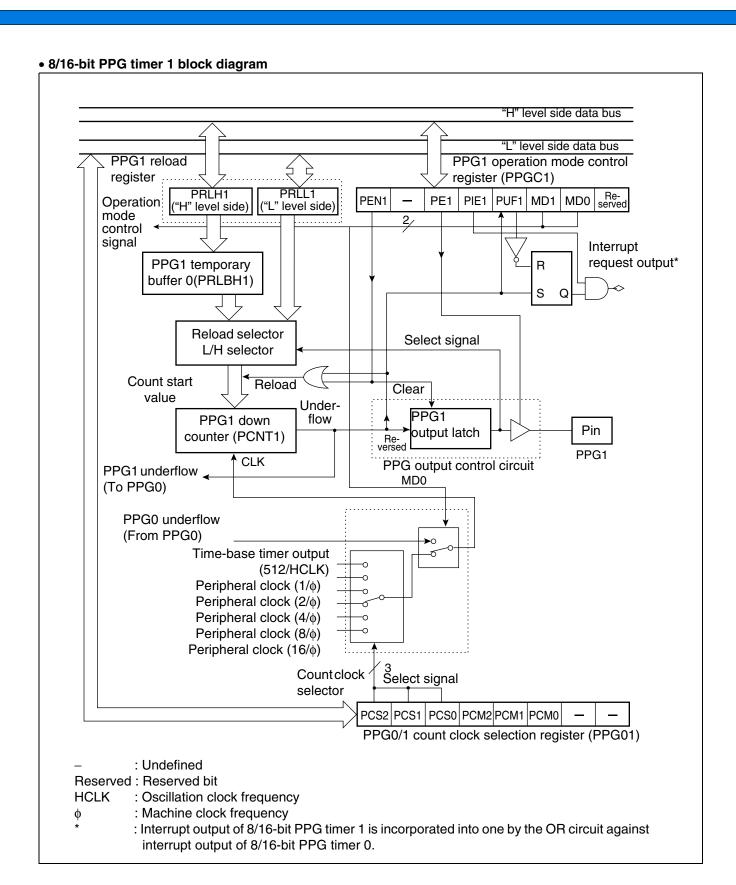

- 8/16-bit PPG timer: 8-bit x 4 channels, or 16-bit x 2 channels

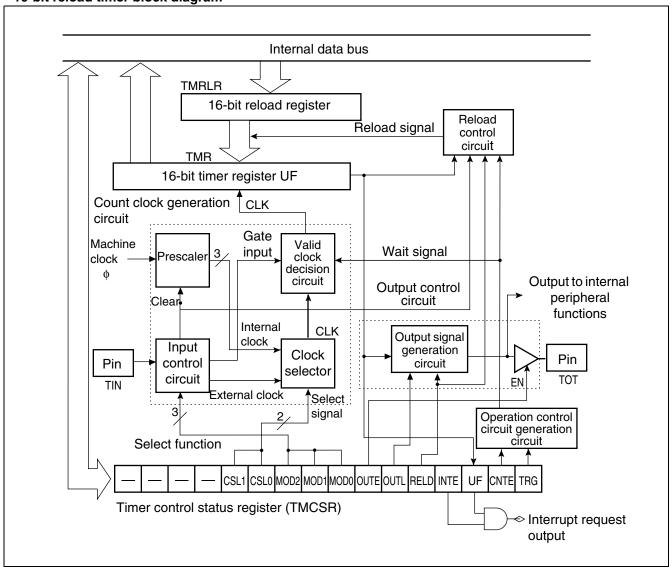

- 16-bit reload timer: 2 channels

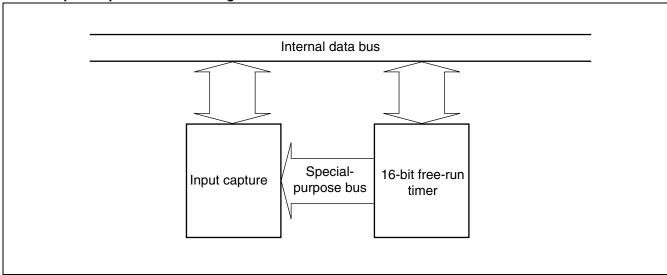

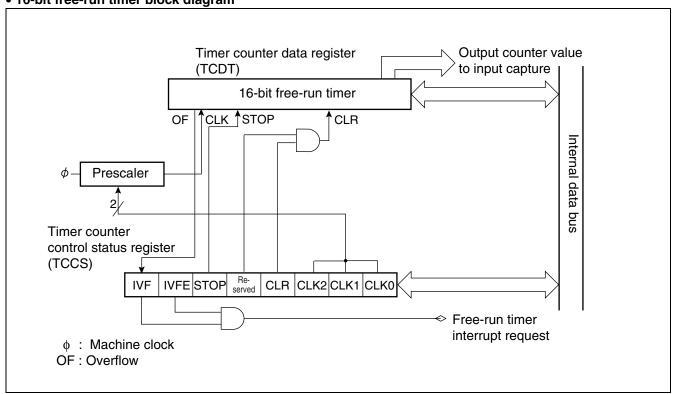

- 16-bit input/output timer

- 16-bit free run timer: 1 channel

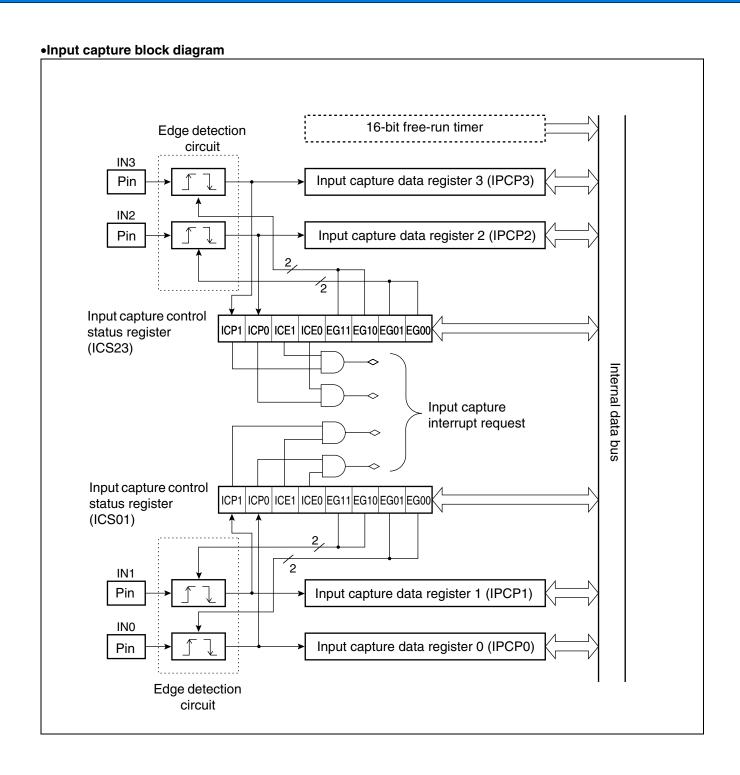

- 16-bit input capture: (ICU): 4 channels

Interrupt request is issued upon latching a count value of 16-bit free run timer by detection of an edge on pin input.

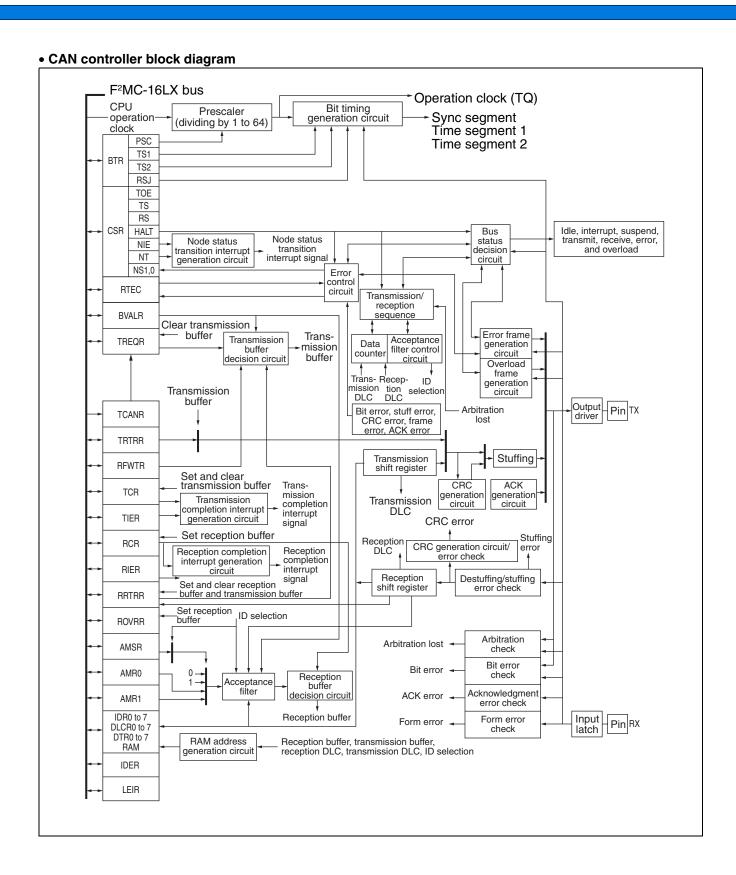

### • CAN controller: 1 channel

- Compliant with Ver2.0A and Ver2.0B CAN specifications

- 8 built-in message buffers

- Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock)

- CAN wake-up

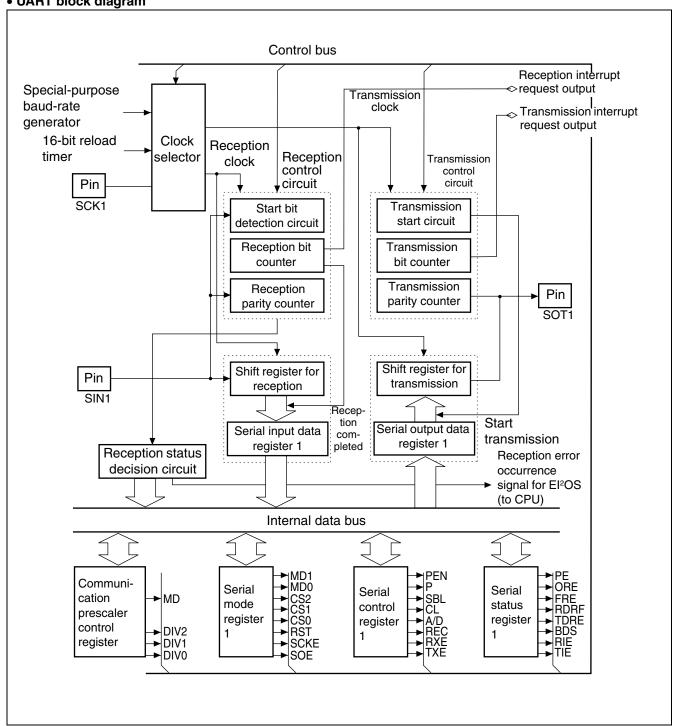

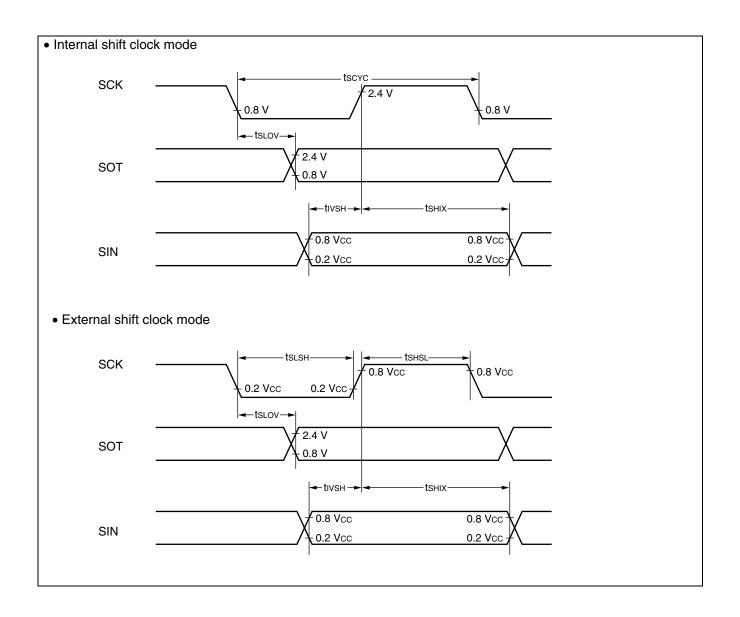

#### • UART (SCI): 1 channel

- Equipped with full-duplex double buffer

- Clock-asynchronous or clock-synchronous serial transmission is available.

### (Continued)

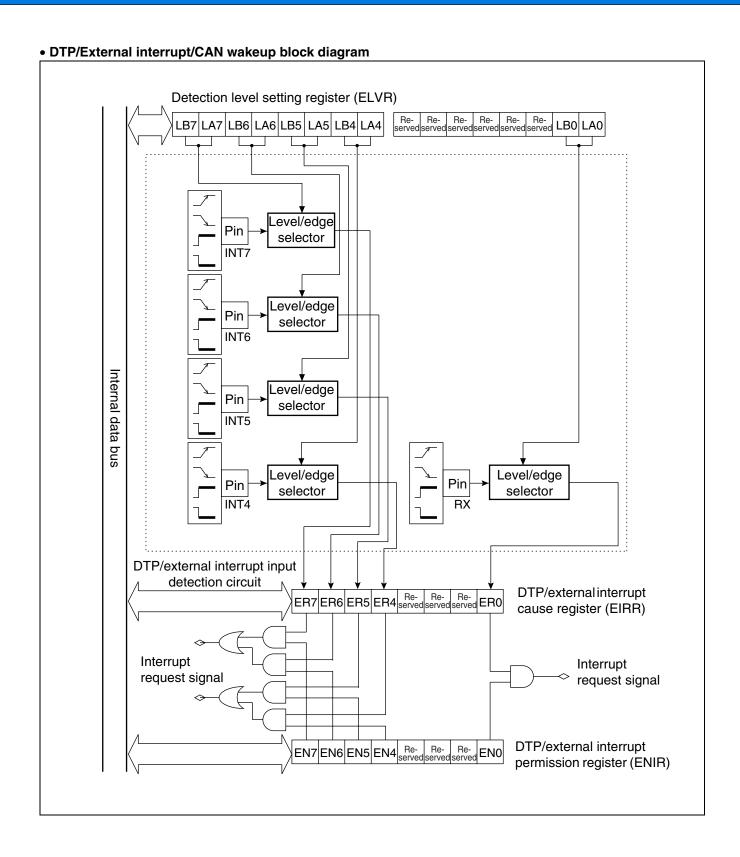

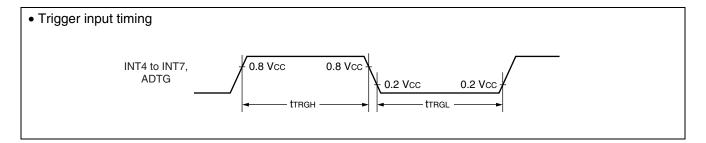

### • DTP/External interrupt: 4 channels, CAN wakeup: 1channel

• Module for activation of expanded intelligent I/O service (El<sup>2</sup>OS), and generation of external interrupt.

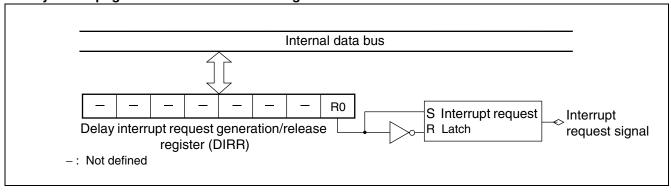

### • Delay interrupt generator module

• Generates interrupt request for task switching.

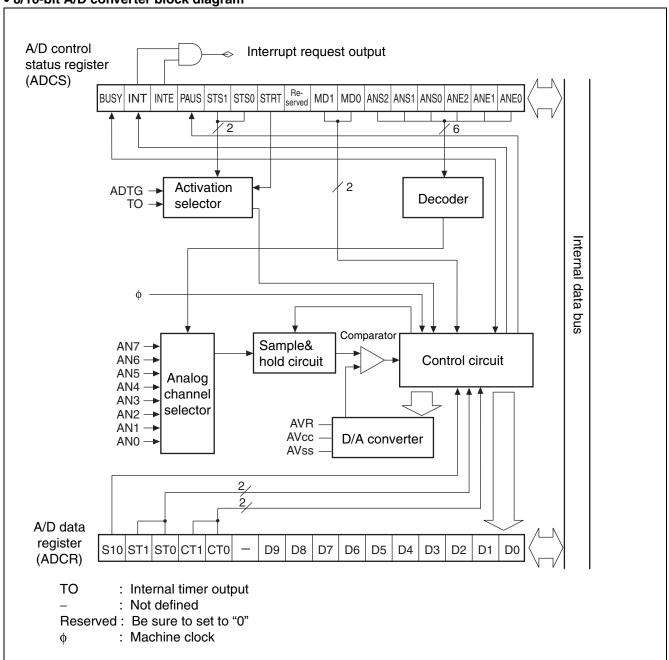

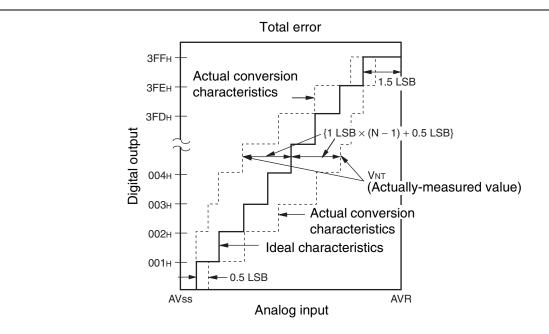

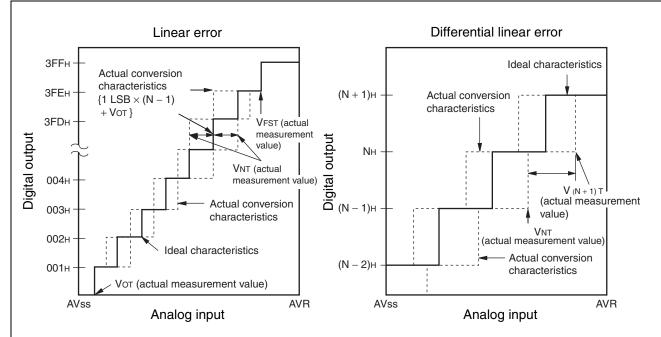

### • 8/10-bit A/D converter: 8 channels

- Resolution is selectable between 8-bit and 10-bit.

- Activation by external trigger input is allowed.

- Conversion time: 6.125 μs (at 16 MHz machine clock, including sampling time)

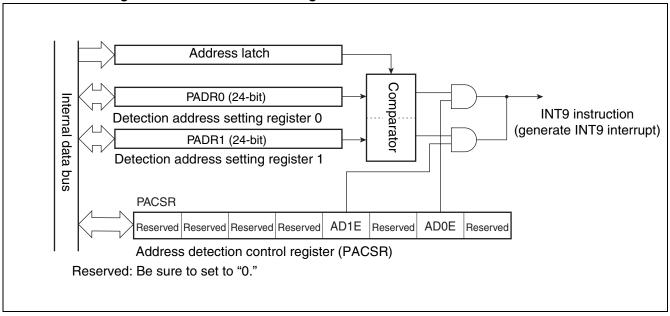

### • Program patch function

• Address matching detection for 2 address pointers.

### **■ PRODUCT LINEUP**

|                                | Part Number           | MB90F387                                                                                                                                                                                                                                                                  | MB90387                                                                                                                                                 | MB90V495G          |  |  |

|--------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|--|

| Parameter                      |                       | MB90F387S                                                                                                                                                                                                                                                                 | MB90387S                                                                                                                                                | WB304-30G          |  |  |

| Classification                 |                       | Flash ROM Mask ROM                                                                                                                                                                                                                                                        |                                                                                                                                                         | Evaluation product |  |  |

| ROM capacity                   |                       | 64 Kbyt                                                                                                                                                                                                                                                                   | tes                                                                                                                                                     | _                  |  |  |

| RAM capacity                   |                       | 2 Kbyte                                                                                                                                                                                                                                                                   | es                                                                                                                                                      | 6 Kbytes           |  |  |

| Process                        |                       |                                                                                                                                                                                                                                                                           | CMOS                                                                                                                                                    |                    |  |  |

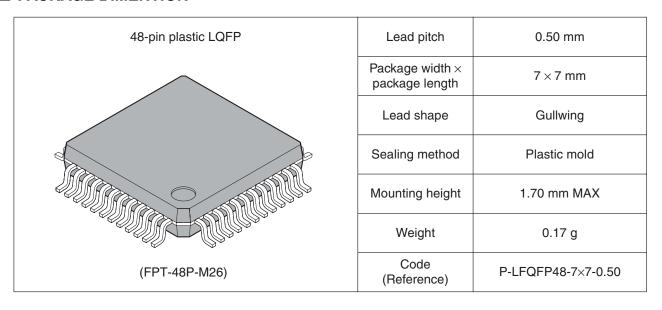

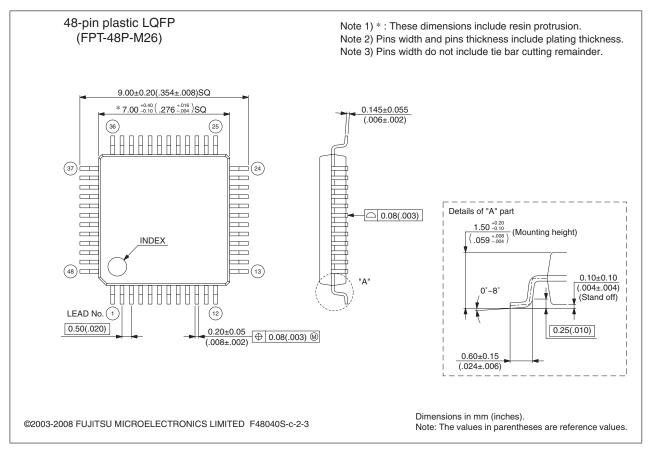

| Package                        |                       | LQFP-48 (pin pite                                                                                                                                                                                                                                                         | ch 0.50 mm)                                                                                                                                             | PGA-256            |  |  |

| Operating power                | er supply voltage     | 3.5 V to 5                                                                                                                                                                                                                                                                | 5.5 V                                                                                                                                                   | 4.5 V to 5.5 V     |  |  |

| Special power semulator*1      | supply for            | _                                                                                                                                                                                                                                                                         |                                                                                                                                                         | None               |  |  |

| CPU functions                  |                       | Instruction bit length Instruction length Data bit length                                                                                                                                                                                                                 | Instruction length : 1 byte to 7 bytes Data bit length : 1 bit, 8 bits, 16 bits  Minimum instruction execution time : 62.5 ns (at 16 MHz machine clock) |                    |  |  |

| Low power con<br>(standby) mod |                       | Sleep mode / Watch mode / Time-base timer mode / Stop mode / CPU intermittent                                                                                                                                                                                             |                                                                                                                                                         |                    |  |  |

| I/O port                       |                       | General-purpose input/output ports (CMOS output): 34 ports (36 ports*2) including 4 high-current output ports (P14 to P17)                                                                                                                                                |                                                                                                                                                         |                    |  |  |

| Time-base time                 | er                    | 18-bit free-run counter<br>Interrupt cycle: 1.024 ms, 4.096 ms, 16.834 ms, 131.072 ms<br>(with oscillation clock frequency at 4 MHz)                                                                                                                                      |                                                                                                                                                         |                    |  |  |

| Watchdog time                  | r                     | Reset generation cycle: 3.58 ms, 14.33 ms, 57.23 ms, 458.75 ms (with oscillation clock frequency at 4 MHz)                                                                                                                                                                |                                                                                                                                                         |                    |  |  |

| 16-bit input/                  | 16-bit free-run timer | Number of channels: 1 Interrupt upon occurrence of                                                                                                                                                                                                                        | overflow                                                                                                                                                |                    |  |  |

| output timer                   | Input capture         | Number of channels: 4 Retaining free-run timer value set by pin input (rising edge, falling edge, and both edges)                                                                                                                                                         |                                                                                                                                                         |                    |  |  |

| 16-bit reload timer            |                       | Number of channels: 2 16-bit reload timer operation Count clock cycle: 0.25 μs, 0.5 μs, 2.0 μs (at 16-MHz machine clock frequency) External event count is allowed.                                                                                                       |                                                                                                                                                         |                    |  |  |

| Watch timer                    |                       | 15-bit free-run counter<br>Interrupt cycle: 31.25 ms, 62.5 ms, 12 ms, 250 ms, 500 ms, 1.0 s, 2.0 s<br>(with 8.192 kHz sub clock)                                                                                                                                          |                                                                                                                                                         |                    |  |  |

| 8/16-bit PPG timer             |                       | Number of channels: 2 (four 8-bit channels are available also.) PPG operation is allowed with four 8-bit channels or two 16-bit channels. Outputting pulse wave of arbitrary cycle or arbitrary duty is allowed. Count clock: 62.5 ns to 1 µs (with 16 MHz machine clock) |                                                                                                                                                         |                    |  |  |

### (Continued)

| Part Number Parameter            | MB90F387<br>MB90F387S                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | MB90387<br>MB90387S                                           | MB90V495G        |  |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|--|

| Delay interrupt generator module | Interrupt generator modul                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | e for task switching. Used                                    | for realtime OS. |  |

| DTP/External interrupt           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | falling edge, "H" level or "L<br>nded intelligent I/O service |                  |  |

| 8/10-bit A/D converter           | Number of channels: 8 Resolution: Selectable 10-bit or 8-bit. Conversion time: 6.125 µs (at 16 MHz machine clock, including sampling time) Sequential conversion of two or more successive channels is allowed. (Setting a maximum of 8 channels is allowed.) Single conversion mode : Selected channel is converted only once. Sequential conversion mode: Selected channel is converted repetitively. Halt conversion mode : Conversion of selected channel is stopped and activated alternately. |                                                               |                  |  |

| UART(SCI)                        | Number of channels: 1 Clock-synchronous transfer: 62.5 kbps to 2 Mbps Clock-asynchronous transfer: 9,615 bps to 500 kbps Communication is allowed by bi-directional serial communication function and master/slave type connection.                                                                                                                                                                                                                                                                 |                                                               |                  |  |

| CAN                              | Compliant with Ver 2.0A and Ver 2.0B CAN specifications. 8 built-in message buffers. Transmission rate of 10 kbps to 1 Mbps (by 16 MHz machine clock) CAN wake-up                                                                                                                                                                                                                                                                                                                                   |                                                               |                  |  |

<sup>\*1 :</sup> Settings of DIP switch S2 for using emulation pod MB2145-507. For details, see MB2145-507 Hardware Manual (2.7 Power Pin solely for Emulator).

### ■ PACKAGES AND PRODUCT MODELS

| Package     | MB90F387, MB90F387S | MB90387, MB90387S |  |

|-------------|---------------------|-------------------|--|

| FPT-48P-M26 | $\circ$             | $\circ$           |  |

$\bigcirc$ : Yes  $\times$ : No

Note: Refer to "■ PACKAGE DIMENSION" for details of the package.

### **■ PRODUCT COMPARISON**

#### **Memory space**

When testing with test product for evaluation, check the differences between the product and a product to be used actually. Pay attention to the following points:

- The MB90V495G has no built-in ROM. However, a special-purpose development tool allows the operations as those of one with built-in ROM. ROM capacity depends on settings on a development tool.

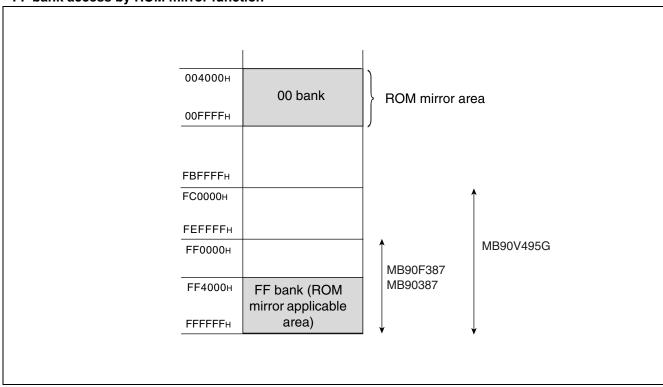

- On MB90V495G, an image from FF4000<sub>H</sub> to FFFFFF<sub>H</sub> is viewed on 00 bank and an image of FE0000<sub>H</sub> to FF3FFF<sub>H</sub> is viewed only on FE bank and FF bank. (Modified on settings of a development tool.)

- On MB90F387/F387S/387S, an image from FF4000<sub>H</sub> to FFFFFF<sub>H</sub> is viewed on 00 bank and an image of FE0000<sub>H</sub> to FF3FFF<sub>H</sub> is viewed only on FF bank.

<sup>\*2:</sup> MB90387S, MB90F387S

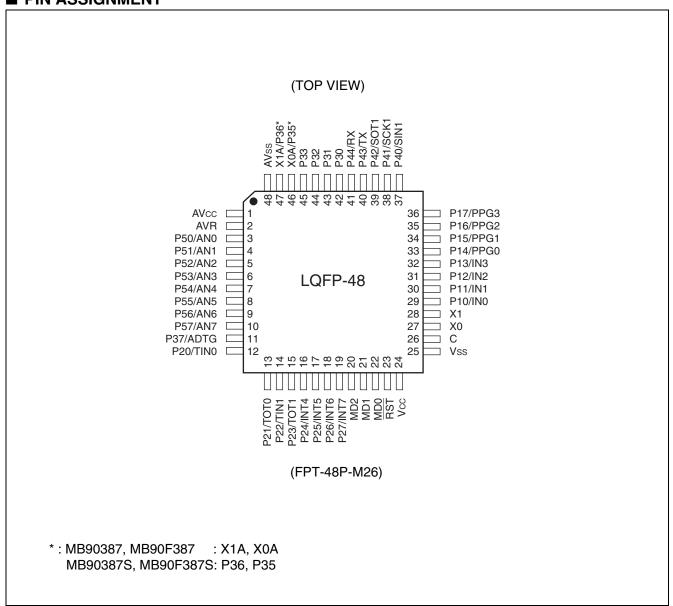

### **■ PIN ASSIGNMENT**

### **■ PIN DESCRIPTION**

| Pin No.  | Pin name     | Circuit<br>type | Function                                                                                                                   |

|----------|--------------|-----------------|----------------------------------------------------------------------------------------------------------------------------|

| 1        | AVcc         | _               | Vcc power input pin for A/D converter.                                                                                     |

| 2        | AVR          | _               | Power (Vref+) input pin for A/D converter. Use as input for Vcc or lower.                                                  |

|          | P50 to P57   |                 | General-purpose input/output ports.                                                                                        |

| 3 to 10  | AN0 to AN7   | E               | Functions as analog input pins for A/D converter. Valid when analog input setting is "enabled."                            |

|          | P37          |                 | General-purpose input/output port.                                                                                         |

| 11       | ADTG         | D               | Function as an external trigger input pin for A/D converter. Use the pin by setting as input port.                         |

|          | P20          |                 | General-purpose input/output port.                                                                                         |

| 12       | TIN0         | D               | Function as an event input pin for reload timer 0. Use the pin by setting as input port.                                   |

|          | P21          |                 | General-purpose input/output port.                                                                                         |

| 13       | ТОТ0         | D               | Function as an event output pin for reload timer 0. Valid only when output setting is "enabled."                           |

|          | P22          |                 | General-purpose input/output port.                                                                                         |

| 14       | TIN1         | D               | Function as an event input pin for reload timer 1. Use the pin by setting as input port.                                   |

| P23      |              |                 | General-purpose input/output port.                                                                                         |

| 15       | TOT1         | D               | Function as an event output pin for reload timer 1. Valid only when output setting is "enabled."                           |

| 16 to 19 | P24 to P27   | D               | General-purpose input/output ports.                                                                                        |

| 10 10 19 | INT4 to INT7 | D               | Functions as external interrupt input pins. Use the pins by setting as input port.                                         |

| 20       | MD2          | F               | Input pin for specifying operation mode. Connect directly to Vss.                                                          |

| 21       | MD1          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                                          |

| 22       | MD0          | С               | Input pin for specifying operation mode. Connect directly to Vcc.                                                          |

| 23       | RST          | В               | External reset input pin.                                                                                                  |

| 24       | Vcc          |                 | Power source (5 V) input pin.                                                                                              |

| 25       | Vss          | _               | Power source (0 V) input pin.                                                                                              |

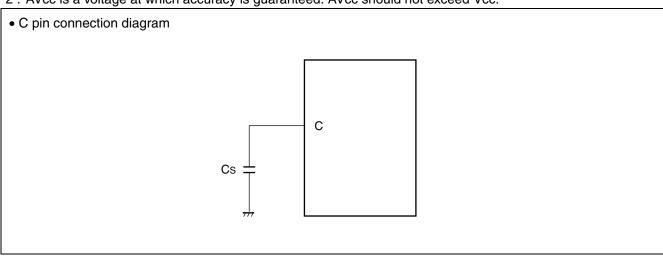

| 26       | С            | _               | Capacitor pin for stabilizing power source. Connect a ceramic capacitor of approximately 0.1 $\ensuremath{\mu F}\xspace$ . |

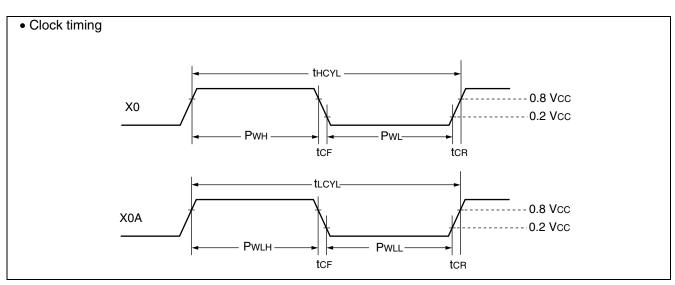

| 27       | X0           | А               | Pin for high-rate oscillation.                                                                                             |

| 28       | X1           | Α               | Pin for high-rate oscillation.                                                                                             |

|          | P10 to P13   |                 | General-purpose input/output ports.                                                                                        |

| 29 to 32 | IN0 to IN3   | D               | Functions as trigger input pins of input capture ch.0 to ch.3. Use the pins by setting as input ports.                     |

| Pin No.  | Pin name     | Circuit<br>type | Function                                                                                                 |  |

|----------|--------------|-----------------|----------------------------------------------------------------------------------------------------------|--|

|          | P14 to P17   |                 | General-purpose input/output ports. High-current output ports.                                           |  |

| 33 to 36 | PPG0 to PPG3 | G               | Functions as output pins of PPG timers 01 and 23. Valid when output setting is "enabled."                |  |

| 37       | P40          | D               | General-purpose input/output port.                                                                       |  |

| 31       | SIN1         | U               | Serial data input pin for UART. Use the pin by setting as input port.                                    |  |

|          | P41          |                 | General-purpose input/output port.                                                                       |  |

| 38       | SCK1         | D               | Serial clock input pin for UART. Valid only when serial clock input/output setting on UART is "enabled." |  |

|          | P42          |                 | General-purpose input/output port.                                                                       |  |

| 39       | SOT1         | D               | Serial data input pin for UART. Valid only when serial data input/output setting on UART is "enabled."   |  |

|          | P43          |                 | General-purpose input/output port.                                                                       |  |

| 40       | TX           | D               | Transmission output pin for CAN. Valid only when output setting is "enabled."                            |  |

|          | P44          |                 | General-purpose input/output port.                                                                       |  |

| 41       | RX           | D               | Transmission output pin for CAN. Valid only when output setting is "enabled."                            |  |

| 42 to 45 | P30 to P33   | D               | General-purpose input/output ports.                                                                      |  |

| 46       | X0A*         | Α               | Pin for low-rate oscillation.                                                                            |  |

| 40       | P35*         | Α               | General-purpose input/output port.                                                                       |  |

| 47       | X1A*         | Α               | Pin for low-rate oscillation.                                                                            |  |

| 41       | P36*         | Α               | General-purpose input/output port.                                                                       |  |

| 48       | AVss         | _               | Vss power source input pin for A/D converter.                                                            |  |

<sup>\*:</sup> MB90387, MB90F387 : X1A, X0A MB90387S, MB90F387S: P36, P35

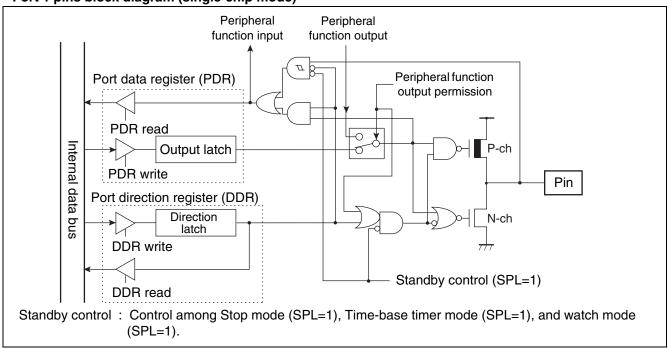

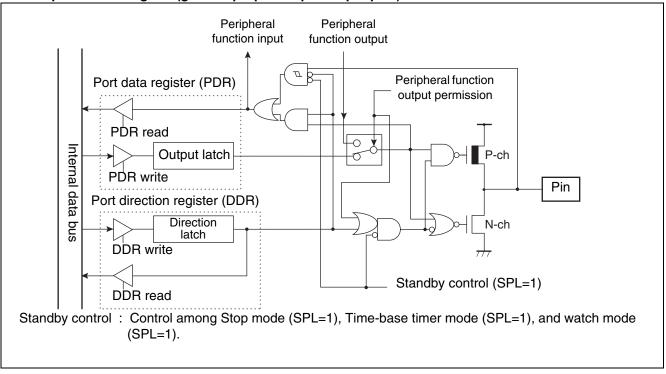

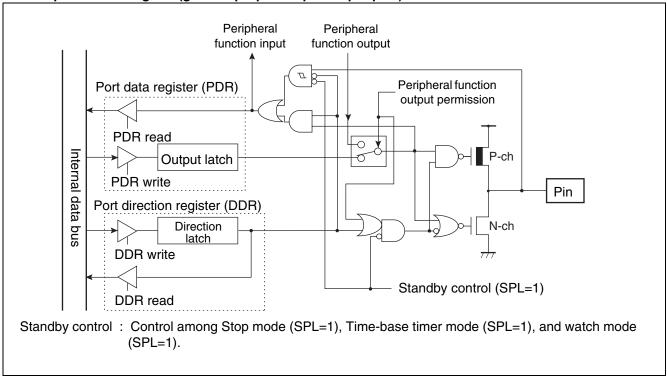

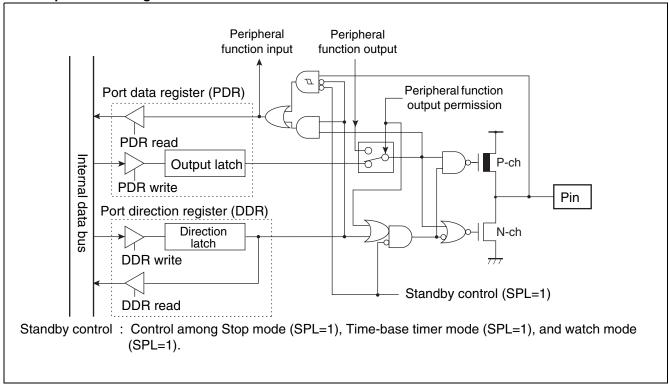

### ■ I/O CIRCUIT TYPE

| Туре | Circuit                                                                                                           | Remarks                                                                                                                                |

|------|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| А    | X1<br>X1A<br>X0<br>X0A Standby control signal                                                                     | <ul> <li>High-rate oscillation feedback resistor, approx.1 MΩ</li> <li>Low-rate oscillation feedback resistor, approx.10 MΩ</li> </ul> |

| В    | R N Nysteresis input                                                                                              | <ul> <li>Hysteresis input with pull-up resistor.</li> <li>Pull-up resistor, approx.50 kΩ</li> </ul>                                    |

| С    | R                                                                                                                 | Hysteresis input                                                                                                                       |

| D    | Vcc  P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control          | <ul> <li>CMOS hysteresis input</li> <li>CMOS level output</li> <li>Standby control provided</li> </ul>                                 |

| E    | P-ch Digital output  N-ch Digital output  N-ch Digital output  N-ch Digital output  Standby control  Analog input | CMOS hysteresis input CMOS level output Shared for analog input pin Standby control provided                                           |

| Type | Circuit                                                                                           | Remarks                                                                                                                                                                 |

|------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| F    | R<br>W → Hysteresis input                                                                         | <ul> <li>Hysteresis input with pull-down resistor</li> <li>Pull-down resistor, approx. 50 kΩ</li> <li>Flash product is not provided with pull-down resistor.</li> </ul> |

| G    | P-ch High-current output  High-current output  N-ch  Vss  CMOS  hysteresis input  Standby control | CMOS hysteresis input CMOS level output (high-current output) Standby control provided                                                                                  |

### **■ HANDLING DEVICES**

### • Do Not Exceed Maximum Rating (preventing "latch up")

- On a CMOS IC, latch-up may occur when applying a voltage higher than Vcc or a voltage lower than Vss to input or output pin, which has no middle or high withstand voltage. Latch-up may also occur when a voltage exceeding maximum rating is applied across Vcc pin and Vss pin.

- Latch-up causes drastic increase of power current, which may lead to destruction of elements by heat. Extreme caution must be taken not to exceed maximum rating.

- When turning on and off analog power source, take extra care not to apply an analog power voltages (AVcc and AVR) and analog input voltage that are higher than digital power voltage (Vcc).

### Handling Unused Pins

• Leaving unused input pins open may cause permanent destruction by malfunction or latch-up. Apply pull-up or pull-down process to the unused pins using resistors of 2 k $\Omega$  or higher. Leave unused input/output pins open under output status, or process as input pins if they are under input status.

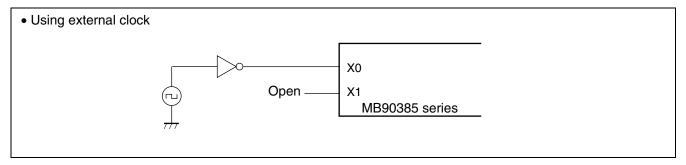

### Using External Clock

When using an external clock, drive only X0 pin and leave X1 pin open. An example of using an external clock is shown below.

### Notes When Using No Sub Clock

• If an oscillator is not connected to X0A and X1A pin, apply pull-down resistor to X0A pin and leave X1A pin open.

#### About Power Supply Pins

- If two or more Vcc and Vss pins exist, the pins that should be at the same potential are connected to each other inside the device. For reducing unwanted emissions and preventing malfunction of strobe signals caused by increase of ground level, however, be sure to connect the Vcc and Vss pins to the power source and the ground externally.

- Pay attention to connect a power supply to Vcc and Vss of MB90385 series device in a lowest-possible impedance.

- Near pins of MB90385 series device, connecting a bypass capacitor is recommended at 0.1  $\mu F$  across Vcc pin and Vss pin.

#### • Crystal Oscillator Circuit

- Noises around X0 and X1 pins cause malfunctions on a MB90385 series device. Design a print circuit so that X0 and X1 pins, an crystal oscillator (or a ceramic oscillator), and bypass capacitor to the ground become as close as possible to each other. Furthermore, avoid wires to X0 and X1 pins crossing each other as much as possible.

- Print circuit designing that surrounds X0 and X1 pins with grounding wires, which ensures stable operation, is strongly recommended.

#### • Caution on Operations during PLL Clock Mode

• If the PLL clock mode is selected, the microcontroller attempt to be working with the self-oscillating circuit even when there is no external oscillator or external clock input is stopped. Performance of this operation, however, cannot be guaranteed.

### • Sequence of Turning on Power of A/D Converter and Applying Analog Input

- Be sure to turn on digital power (Vcc) before applying signals to the A/D converter and applying analog input signals (AN0 to AN7 pins).

- Be sure to turn off the power of A/D converter and analog input before turning off the digital power source.

- Be sure not to apply AVR exceeding AVcc when turning on and off. (No problems occur if analog and digital power is turned on and off simultaneously.)

### • Handling Pins When A/D Converter is Not Used

• If the A/D converter is not used, connect the pins under the following conditions: "AVcc=AVR=Vcc," and "AVss=Vss"

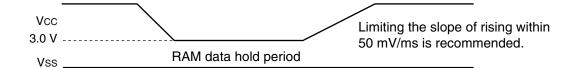

### • Note on Turning on Power

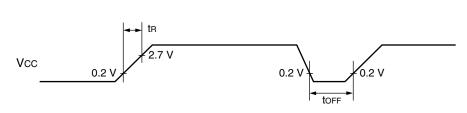

• For preventing malfunctions on built-in step-down circuit, maintain a minimum of 50 μs of voltage rising time (between 0.2 V and 2.7V) when turning on the power.

### Stabilization of supply voltage

• A sudden change in the supply voltage may cause the device to malfunction even within the specified Vcc supply voltage operating range. Therefore, the Vcc supply voltage should be stabilized.

For reference, the supply voltage should be controlled so that Vcc ripple variations (peak-to-peak values) at

commercial frequencies (50 Hz / 60 Hz) fall below 10% of the standard Vcc supply voltage and the coefficient of fluctuation does not exceed 0.1 V/ms at instantaneous power switching.

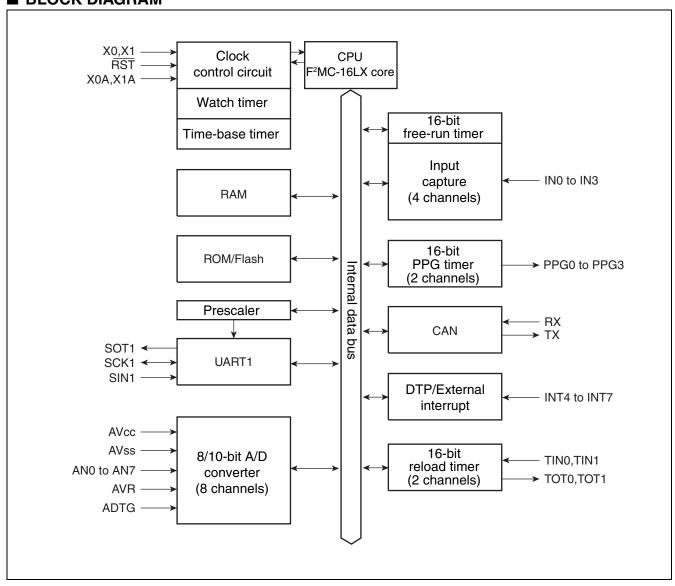

### **■ BLOCK DIAGRAM**

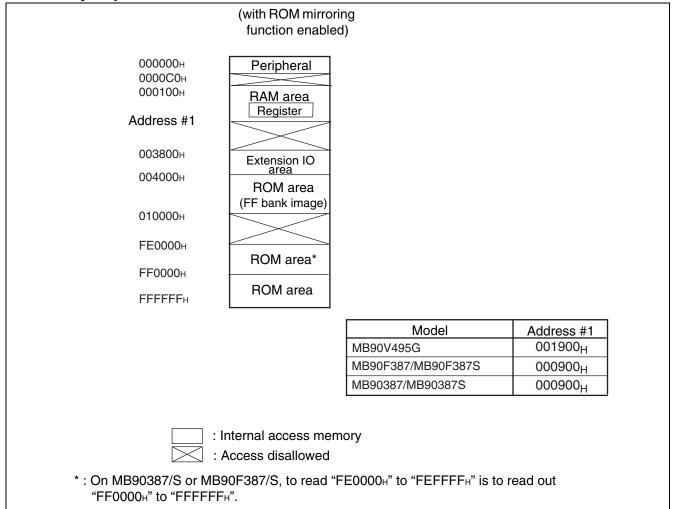

### **■ MEMORY MAP**

MB90385 series allows specifying a memory access mode "single chip mode."

### 1. Memory allocation of MB90385

MB90385 series model has 24-bit wide internal address bus and up to 24-bit bus of external address bus. A maximum of 16-Mbyte memory space of external access memory is accessible.

### 2. Memory map

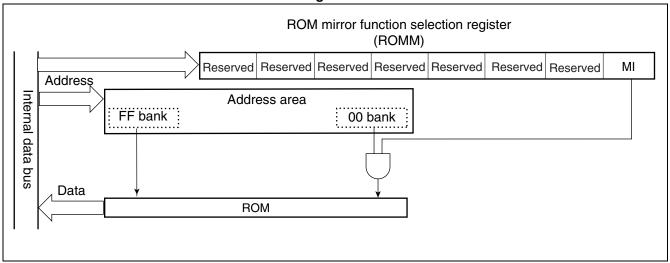

Note: When internal ROM is operating, F<sup>2</sup>MC-16LX allows viewing ROM data image on FF bank at upper-level of 00 bank. This function is called "mirroring ROM," which allows effective use of C compiler small model. F<sup>2</sup>MC-16LX assigns the same low order 16-bit address to FF bank and 00 bank, which allows referencing table in ROM without specifying "far" using pointer.

For example, when accessing to "00C000H", ROM data at "FFC000H" is accessed actually. However, because ROM area of FF bank exceeds 48 Kbytes, viewing all areas is not possible on 00 bank image. Because ROM data of "FF4000H" to "FFFFFFH" is viewed on "004000H" to "00FFFFH" image, store a ROM data table in area "FF4000H" to "FFFFFFHH."

### ■ I/O MAP

| Address                  | Register abbreviation | Register                                                    | Read/<br>Write | Resource                  | Initial value |  |

|--------------------------|-----------------------|-------------------------------------------------------------|----------------|---------------------------|---------------|--|

| 000000н                  |                       | (Reserv                                                     | ed area) *     |                           |               |  |

| 000001н                  | PDR1                  | Port 1 data register                                        | R/W            | Port 1                    | XXXXXXXXB     |  |

| 000002н                  | PDR2                  | Port 2 data register                                        | R/W            | Port 2                    | XXXXXXXX      |  |

| 000003н                  | PDR3                  | Port 3 data register                                        | R/W            | Port 3                    | XXXXXXXX      |  |

| 000004н                  | PDR4                  | Port 4 data register                                        | R/W            | Port 4                    | XXXXXXXX      |  |

| 000005н                  | PDR5                  | Port 5 data register                                        | R/W            | Port 5                    | XXXXXXXXB     |  |

| 000006н<br>to<br>000010н |                       | (Reserv                                                     | ed area) *     |                           |               |  |

| 000011н                  | DDR1                  | Port 1 direction data register                              | R/W            | Port 1                    | 0000000в      |  |

| 000012н                  | DDR2                  | Port 2 direction data register                              | R/W            | Port 2                    | 0000000В      |  |

| 000013н                  | DDR3                  | Port 3 direction data register                              | R/W            | Port 3                    | 000Х0000в     |  |

| 000014н                  | DDR4                  | Port 4 direction data register                              | R/W            | Port 4                    | ХХХ00000в     |  |

| 000015н                  | DDR5                  | Port 5 direction data register                              | R/W            | Port 5                    | 0000000в      |  |

| 000016н<br>to<br>00001Ан |                       | (Reserved area) *                                           |                |                           |               |  |

| 00001Вн                  | ADER                  | Analog input permission register                            | R/W            | 8/10-bit<br>A/D converter | 11111111В     |  |

| 00001Сн<br>to<br>000025н |                       | (Reserv                                                     | ed area) *     |                           |               |  |

| 000026н                  | SMR1                  | Serial mode register 1                                      | R/W            |                           | 0000000в      |  |

| 000027н                  | SCR1                  | Serial control register 1                                   | R/W, W         |                           | 00000100в     |  |

| 000028н                  | SIDR1/<br>SODR1       | Serial input data register 1/ Serial output data register 1 | R, W           | UART1                     | XXXXXXXXB     |  |

| 000029н                  | SSR1                  | Serial status data register 1                               | R, R/W         |                           | 00001000в     |  |

| 00002Ан                  |                       | (Reserv                                                     | ed area) *     | 1                         | -1            |  |

| 00002Вн                  | CDCR1                 | Communication prescaler control register 1                  | R/W            | UART1                     | 0ХХХ0000в     |  |

| 00002Сн<br>to<br>00002Fн |                       | (Reserv                                                     | ed area) *     |                           |               |  |

| 000030н                  | ENIR                  | DTP/External interrupt permission register                  | R/W            |                           | 0000000В      |  |

| 000031н                  | EIRR                  | DTP/External interrupt permission register                  | R/W            | DTP/External interrupt    | XXXXXXXXB     |  |

| 000032н                  | ELVD                  | Detection level cotting register                            | R/W            | 1                         | 0000000В      |  |

| 000033н                  | ELVR                  | Detection level setting register                            | R/W            | 1                         | 0000000в      |  |

16

| Address                  | Register abbreviation | Register                              | Read/<br>Write | Resource                  | Initial value         |

|--------------------------|-----------------------|---------------------------------------|----------------|---------------------------|-----------------------|

| 000034н                  | ADCS                  | A/D control status register           | R/W            |                           | 0000000В              |

| 000035н                  | ADCS                  | A/D control status register           | R/W, W         | 8/10-bit                  | 0000000В              |

| 000036н                  | ADCR                  | A/D data register                     | W, R           | A/D converter             | XXXXXXXXB             |

| 000037н                  | ADCR                  | A/D data register                     | R              | ]                         | 00101XXXв             |

| 000038н<br>to<br>00003Fн |                       | (Reserve                              | ed area) *     |                           |                       |

| 000040н                  | PPGC0                 | PPG0 operation mode control register  | R/W, W         |                           | 0X000XX1в             |

| 000041н                  | PPGC1                 | PPG1 operation mode control register  | R/W, W         | 8/16-bit<br>PPG timer 0/1 | 0Х00001в              |

| 000042н                  | PPG01                 | PPG0/1 count clock selection register | R/W            |                           | 000000XX <sub>B</sub> |

| 000043н                  |                       | (Reserve                              | ed area) *     |                           |                       |

| 000044н                  | PPGC2                 | PPG2 operation mode control register  | R/W, W         | 8/16-bit<br>PPG timer 2/3 | 0Х000ХХ1в             |

| 000045н                  | PPGC3                 | PPG3 operation mode control register  | R/W, W         |                           | 0Х00001в              |

| 000046н                  | PPG23                 | PPG2/3 count clock selection register | R/W            |                           | 000000XXв             |

| 000047н<br>to<br>00004Fн |                       | (Reserve                              | ed area) *     |                           |                       |

| 000050н                  | IPCP0                 | Input conture data register 0         | R              |                           | XXXXXXXXB             |

| 000051н                  | IPCPU                 | Input capture data register 0         | n              |                           | XXXXXXXXB             |

| 000052н                  | IPCP1                 | Input conture data register 1         | В              | ]                         | XXXXXXXXB             |

| 000053н                  | IPCPT                 | Input capture data register 1         | R              |                           | XXXXXXXXB             |

| 000054н                  | ICS01                 | Input conture control status register | DAM            | 16-bit input/output       | 0000000В              |

| 000055н                  | ICS23                 | Input capture control status register | R/W            |                           | 0000000в              |

| 000056н                  | TCDT                  | Timor countar data register           | R/W            | ]                         | 0000000В              |

| 000057н                  | וטטו                  | Timer counter data register           | □/ <b>VV</b>   |                           | 0000000в              |

| 000058н                  | TCCS                  | Timer counter control status register | R/W            | ]                         | 0000000в              |

| 000059н                  |                       | (Reserve                              | ed area) *     |                           |                       |

| 00005Ан                  | IPCP2                 | Input capture data register 2         | R              |                           | XXXXXXXX              |

| 00005Вн                  | 15052                 | Input capture data register 2         | ח              | 16-bit input/output       | XXXXXXXX              |

| 00005Сн                  | IPCP3                 | Input capture data register 2         | R              | timer                     | XXXXXXXX              |

| 00005Dн                  | IFUES                 | Input capture data register 3         | n              |                           | XXXXXXXXB             |

| Address                  | Register abbreviation | Register                                                | Read/<br>Write | Resource                                | Initial value         |

|--------------------------|-----------------------|---------------------------------------------------------|----------------|-----------------------------------------|-----------------------|

| 00005Eн<br>to<br>000065н |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 000066н                  | TMCSR0                |                                                         | R/W            | - 16-bit reload timer 0                 | 0000000В              |

| 000067н                  | TIVICONU              | Timer control status register                           | R/W            | To-bit reload timer of                  | XXXX0000 <sub>B</sub> |

| 000068н                  | TMCSR1                | Timer control status register                           | R/W            | - 16-bit reload timer 1                 | 0000000В              |

| 000069н                  | TIVICONT              |                                                         | R/W            | - 10-bit reload timer 1                 | XXXX0000 <sub>B</sub> |

| 00006Ан<br>to<br>00006Ен |                       | (Reserv                                                 | red area) *    |                                         |                       |

| 00006Fн                  | ROMM                  | ROM mirroring function selection register               | W              | ROM mirroring function selection module | XXXXXXX1 <sub>B</sub> |

| 000070н<br>to<br>00007Fн |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 000080н                  | BVALR                 | Message buffer enabling register                        | R/W            | CAN controller                          | 0000000В              |

| 000081н                  |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 000082н                  | TREQR                 | Send request register                                   | R/W            | CAN controller                          | 0000000В              |

| 000083н                  |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 000084н                  | TCANR                 | Send cancel register                                    | W              | CAN controller                          | 0000000В              |

| 000085н                  |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 000086н                  | TCR                   | Send completion register                                | R/W            | CAN controller                          | 0000000В              |

| 000087н                  |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 000088н                  | RCR                   | Receive completion register                             | R/W            | CAN controller                          | 0000000В              |

| 000089н                  |                       | (Reserv                                                 | ed area) *     |                                         |                       |

| 00008Ан                  | RRTRR                 | Receive RTR register                                    | R/W            | CAN controller                          | 0000000В              |

| 00008Вн                  |                       | (Reserv                                                 | red area) *    |                                         |                       |

| 00008Сн                  | ROVRR                 | Receive overrun register                                | R/W            | CAN controller                          | 0000000В              |

| 00008Dн                  |                       | (Reserv                                                 | ed area) *     | ·                                       |                       |

| 00008Ен                  | RIER                  | Receive completion interrupt permission register        | R/W            | CAN controller                          | 00000000в             |

| 00008Fн<br>to<br>00009Dн | (Reserved area) *     |                                                         |                |                                         |                       |

| 00009Ен                  | PACSR                 | Address detection control register                      | R/W            | Address matching detection function     | 00000000в             |

| 00009Fн                  | DIRR                  | Delay interrupt request generation/<br>release register | R/W            | Delay interrupt generation module       | XXXXXXX0 <sub>B</sub> |

| Address                  | Register abbreviation | Register                                      | Read/<br>Write | Resource                     | Initial value         |

|--------------------------|-----------------------|-----------------------------------------------|----------------|------------------------------|-----------------------|

| 0000А0н                  | LPMCR                 | Lower power consumption mode control register | W,R/W          | Lower power consumption mode | 00011000в             |

| 0000А1н                  | CKSCR                 | Clock selection register                      | R,R/W          | Clock                        | 11111100в             |

| 0000A2н<br>to<br>0000A7н |                       | (Reserv                                       | red area) *    |                              |                       |

| 0000А8н                  | WDTC                  | Watchdog timer control register               | R,W            | Watchdog timer               | XXXXX111 <sub>B</sub> |

| 0000А9н                  | TBTC                  | Time-base timer control register              | R/W,W          | Time-base timer              | 1XX00100 <sub>B</sub> |

| 0000ААн                  | WTC                   | Watch timer control register                  | R,R/W          | Watch timer                  | 1Х001000в             |

| 0000ABн<br>to<br>0000ADн |                       | (Reserv                                       | ved area) *    |                              |                       |

| 0000АЕн                  | FMCS                  | Flash memory control status register          | R,W,R/W        | 512k-bit<br>Flash memory     | 000Х0000в             |

| 0000АГн                  |                       | (Reserv                                       | ved area) *    |                              |                       |

| 0000В0н                  | ICR00                 | Interrupt control register 00                 |                |                              | 00000111в             |

| 0000В1н                  | ICR01                 | Interrupt control register 01                 |                |                              | 00000111в             |

| 0000В2н                  | ICR02                 | Interrupt control register 02                 |                |                              | 00000111в             |

| 0000ВЗн                  | ICR03                 | Interrupt control register 03                 |                |                              | 00000111в             |

| 0000В4н                  | ICR04                 | Interrupt control register 04                 |                |                              | 00000111в             |

| 0000В5н                  | ICR05                 | Interrupt control register 05                 |                |                              | 00000111в             |

| 0000В6н                  | ICR06                 | Interrupt control register 06                 |                |                              | 00000111в             |

| 0000В7н                  | ICR07                 | Interrupt control register 07                 | R/W            | Interrupt controller         | 00000111в             |

| 0000В8н                  | ICR08                 | Interrupt control register 08                 |                | TitleTupt Controller         | 00000111в             |

| 0000В9н                  | ICR09                 | Interrupt control register 09                 |                |                              | 00000111в             |

| 0000ВАн                  | ICR10                 | Interrupt control register 10                 | ]              |                              | 00000111в             |

| 0000ВВн                  | ICR11                 | Interrupt control register 11                 | ]              |                              | 00000111в             |

| 0000ВСн                  | ICR12                 | Interrupt control register 12                 |                |                              | 00000111в             |

| 0000ВДн                  | ICR13                 | Interrupt control register 13                 | ]              |                              | 00000111в             |

| 0000ВЕн                  | ICR14                 | Interrupt control register 14                 | ]              |                              | 00000111в             |

| 0000ВГн                  | ICR15                 | Interrupt control register 15                 | ]              |                              | 00000111в             |

| 0000С0н<br>to<br>0000FFн |                       | (Reserv                                       | ved area) *    |                              | (Continue)            |

| Address                  | Register abbreviation     | Register                                            | Read/<br>Write | Resource              | Initial value |

|--------------------------|---------------------------|-----------------------------------------------------|----------------|-----------------------|---------------|

| 001FF0н                  |                           | Detection address setting register 0 (low-order)    |                |                       | XXXXXXXXB     |

| 001FF1н                  | PADR0                     | Detection address setting register 0 (middle-order) | R/W            | Address matching      | XXXXXXXXB     |

| 001FF2н                  |                           | Detection address setting register 0 (high-order)   |                |                       | XXXXXXXXB     |

| 001FF3н                  |                           | Detection address setting register 1 (low-order)    |                | detection function    | XXXXXXXXB     |

| 001FF4н                  | PADR1                     | Detection address setting register 1 (middle-order) | R/W            |                       | XXXXXXXXB     |

| 001FF5н                  |                           | Detection address setting register 1 (high-order)   |                |                       | XXXXXXXXB     |

| 003900н                  | TMR0/                     | 16-bit timer register 0/16-bit reload               | R,W            | 16-bit reload timer 0 | XXXXXXXX      |

| 003901н                  | TMRLR0                    | register                                            | 11, VV         |                       | XXXXXXXX      |

| 003902н                  | TMR1/                     | 16-bit timer register 1/16-bit reload               | R,W            | 16-bit reload timer 1 | XXXXXXXX      |

| 003903н                  | TMRLR1                    | register R, W TO-bit Teload timer 1                 |                |                       | XXXXXXXX      |

| 003904н                  |                           |                                                     |                |                       |               |

| to<br>00390Fн            |                           | (Reserve                                            | d area) *      |                       |               |

| 003910н                  | PRLL0                     | PPG0 reload register L                              | R/W            |                       | XXXXXXXX      |

| 003911н                  | PRLH0                     | PPG0 reload register H                              | R/W            | 1                     | XXXXXXXX      |

| 003912н                  | PRLL1                     | PPG1 reload register L                              | R/W            | 1                     | XXXXXXXX      |

| 003913н                  | PRLH1                     | PPG1 reload register H                              | R/W            | - 8/16-bit PPG timer  | XXXXXXXX      |

| 003914н                  | PRLL2                     | PPG2 reload register L                              | R/W            |                       | XXXXXXXX      |

| 003915н                  | PRLH2                     | PPG2 reload register H                              | R/W            |                       | XXXXXXXX      |

| 003916н                  | PRLL3                     | PPG3 reload register L                              | R/W            |                       | XXXXXXXX      |

| 003917н                  | PRLH3                     | PPG3 reload register H                              | R/W            |                       | XXXXXXXX      |

| 003918н<br>to<br>00392Fн |                           | (Reserve                                            | d area) *      |                       |               |

| 003930н<br>to<br>003BFFн |                           | (Reserve                                            | d area) *      |                       |               |

| 003С00н<br>to<br>003С0Fн | RAM (General-purpose RAM) |                                                     |                |                       |               |

| Address                  | Register abbreviation | Register                                                 | Read/<br>Write              | Resource       | Initial value                                    |  |  |

|--------------------------|-----------------------|----------------------------------------------------------|-----------------------------|----------------|--------------------------------------------------|--|--|

| 003С10н<br>to<br>003С13н | IDR0                  | ID register 0                                            | ID register 0 R/W           |                |                                                  |  |  |

| 003С14н<br>to<br>003С17н | IDR1                  | ID register 1                                            | R/W                         |                | XXXXXXXXB<br>to<br>XXXXXXXXXB                    |  |  |

| 003С18н<br>to<br>003С1Вн | IDR2                  | ID register 2                                            | R/W                         |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |

| 003С1Сн<br>to<br>003С1Fн | IDR3                  | ID register 3                                            | R/W                         |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |

| 003С20н<br>to<br>003С23н | IDR4                  | ID register 4                                            | R/W                         | _              | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |

| 003С24н<br>to<br>003С27н | IDR5                  | D register 5 R/W                                         | XXXXXXXB<br>to<br>XXXXXXXXB |                |                                                  |  |  |

| 003С28н<br>to<br>003С2Вн | IDR6                  | ID register 6                                            | R/W                         | CAN controller | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |

| 003С2Сн<br>to<br>003С2Fн | IDR7                  | ID register 7                                            | R/W                         |                | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |

| 003С30н,<br>003С31н      | DLCR0                 | DLC register 0                                           | R/W                         |                | XXXXXXXXB,<br>XXXXXXXXB                          |  |  |

| 003С32н,<br>003С33н      | DLCR1                 | DLC register 1                                           | R/W                         |                | XXXXXXXXB,<br>XXXXXXXXB                          |  |  |

| 003С34н,<br>003С35н      | DLCR2                 | DLC register 2 R/W DLC register 3 R/W DLC register 4 R/W |                             | _              | XXXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub> |  |  |

| 003С36н,<br>003С37н      | DLCR3                 |                                                          |                             |                | XXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub>  |  |  |

| 003С38н,<br>003С39н      | DLCR4                 |                                                          |                             |                | XXXXXXXXB,<br>XXXXXXXXB                          |  |  |

| 003С3Ан,<br>003С3Вн      | DLCR5                 | DLC register 5                                           | R/W                         |                | XXXXXXXB,<br>XXXXXXXB                            |  |  |

| Address                  | Register abbreviation | Register                    | Read/<br>Write | Resource       | Initial value                |  |  |  |  |  |

|--------------------------|-----------------------|-----------------------------|----------------|----------------|------------------------------|--|--|--|--|--|

| 003С3Сн,<br>003С3Dн      | DLCR6                 | DLC register 6              | R/W            |                | XXXXXXXXB,<br>XXXXXXXXB      |  |  |  |  |  |

| 003С3Ен,<br>003С3Fн      | DLCR7                 | DLC register 7              | R/W            |                | XXXXXXXXB,<br>XXXXXXXXB      |  |  |  |  |  |

| 003С40н<br>to<br>003С47н | DTR0                  | Data register 0             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С48н<br>to<br>003С4Fн | DTR1                  | Data register 1             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С50н<br>to<br>003С57н | DTR2                  | Data register 2             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С58н<br>to<br>003С5Fн | DTR3                  | Data register 3             | R/W            | CAN controller | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С60н<br>to<br>003С67н | DTR4                  | Data register 4             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С68н<br>to<br>003С6Fн | DTR5                  | Data register 5             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С70н<br>to<br>003С77н | DTR6                  | Data register 6             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С78н<br>to<br>003С7Fн | DTR7                  | Data register 7             | R/W            |                | XXXXXXXXB<br>to<br>XXXXXXXXB |  |  |  |  |  |

| 003С80н<br>to<br>003СFFн |                       | (Reserv                     | ed area) *     |                |                              |  |  |  |  |  |

| 003D00н,<br>003D01н      | CSR                   | Control status register     | R/W, R         | CAN controller | 0XXXX001в,<br>00XXX000в      |  |  |  |  |  |

| 003D02н                  | LEIR                  | Last event display register | R/W            |                | 000ХХ000в                    |  |  |  |  |  |

| 003D03н                  |                       | (Reserv                     | ed area) *     |                |                              |  |  |  |  |  |

| 003D04н,<br>003D05н      | RTEC                  | Send/receive error counter  | R              |                | 0000000в,<br>0000000в        |  |  |  |  |  |

| 003D06н,<br>003D07н      | BTR                   | Bit timing register         | R/W            | CAN controller | 11111111в,<br>X1111111в      |  |  |  |  |  |

| 003D08н                  | IDER                  | IDE register                | R/W            | <u> </u>       | XXXXXXXX                     |  |  |  |  |  |

| 003D09н                  |                       | (Reserved area) *           |                |                |                              |  |  |  |  |  |

| 003D0Ан                  | TRTRR                 | Send RTR register           | R/W            | CAN controller | 0000000B                     |  |  |  |  |  |

### (Continued)

| Address                  | Register abbreviation | Register                                      | Read/<br>Write | Resource         | Initial value                                    |  |  |  |  |  |

|--------------------------|-----------------------|-----------------------------------------------|----------------|------------------|--------------------------------------------------|--|--|--|--|--|

| 003D0Вн                  |                       | (Reserve                                      | ed area) *     |                  |                                                  |  |  |  |  |  |

| 003D0Сн                  | RFWTR                 | Remote frame receive wait register            | R/W            | CAN controller   | XXXXXXXX                                         |  |  |  |  |  |

| 003D0Dн                  |                       | (Reserve                                      | ed area) *     |                  |                                                  |  |  |  |  |  |

| 003D0Eн                  | TIER                  | Send completion interrupt permission register | R/W            | CAN controller   | 0000000В                                         |  |  |  |  |  |

| 003D0Fн                  |                       | (Reserve                                      |                |                  |                                                  |  |  |  |  |  |

| 003D10н,<br>003D11н      | AMSR                  | Acceptance mask selection register            | R/W            | CAN controller   | XXXXXXXX <sub>B</sub> ,<br>XXXXXXXX <sub>B</sub> |  |  |  |  |  |

| 003D12н,<br>003D13н      |                       | (Reserve                                      | ed area) *     |                  |                                                  |  |  |  |  |  |

| 003D14н<br>to<br>003D17н | AMR0                  | Acceptance mask register 0                    | R/W            | - CAN controller | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |  |  |  |

| 003D18н<br>to<br>003D1Вн | AMR1                  | Acceptance mask register 1                    | R/W            | CAN controller   | XXXXXXXB<br>to<br>XXXXXXXXB                      |  |  |  |  |  |

| 003D1Сн<br>to<br>003DFFн |                       | (Reserve                                      | ed area) *     |                  |                                                  |  |  |  |  |  |

| 003E00н<br>to<br>003EFFн |                       | (Reserved area) *                             |                |                  |                                                  |  |  |  |  |  |

| 003FF0н<br>to<br>003FFFн | (Reserved area) *     |                                               |                |                  |                                                  |  |  |  |  |  |

### Initial values:

0 : Initial value of this bit is "0."1 : Initial value of this bit is "1."

X: Initial value of this bit is undefined.

\*: "Reserved area" should not be written anything. Result of reading from "Reserved area" is undefined.

### ■ INTERRUPT SOURCES, INTERRUPT VECTORS, AND INTERRUPT CONTROL REGISTERS

| Intowers a compa                                                         | El <sup>2</sup> OS | lr  | nterrup         | t vector            | Interrupt c    | ontrol register              | Dul a ultr +2 |

|--------------------------------------------------------------------------|--------------------|-----|-----------------|---------------------|----------------|------------------------------|---------------|

| Interrupt source                                                         | readiness          | Nun | nber            | Address             | ICR            | Address                      | Priority*3    |

| Reset                                                                    | ×                  | #08 | 08н             | FFFFDC⊢             | _              | _                            | High          |

| INT 9 instruction                                                        | ×                  | #09 | 09н             | FFFFD8 <sub>H</sub> | _              | _                            | $\uparrow$    |

| Exceptional treatment                                                    | ×                  | #10 | ОАн             | FFFFD4 <sub>H</sub> | _              | _                            |               |

| CAN controller reception completed (RX)                                  | ×                  | #11 | 0Вн             | FFFFD0 <sub>H</sub> |                |                              |               |

| CAN controller transmission completed (TX) / Node status transition (NS) | ×                  | #12 | 0Сн             | FFFFCCH             | ICR00          | 0000В0н*1                    |               |

| Reserved                                                                 | ×                  | #13 | 0Дн             | FFFFC8 <sub>H</sub> | ICD04          | 000001                       |               |

| Reserved                                                                 | ×                  | #14 | 0Ен             | FFFFC4 <sub>H</sub> | ICR01          | 0000В1н                      |               |

| CAN wakeup                                                               | Δ                  | #15 | 0Fн             | FFFFC0 <sub>H</sub> | ICDOO          | 000000 *1                    | 1             |

| Time-base timer                                                          | ×                  | #16 | 10н             | FFFFBCH             | ICR02          | 0000B2н*1                    |               |

| 16-bit reload timer 0                                                    | Δ                  | #17 | 11н             | FFFFB8 <sub>H</sub> | IODOO          | 000000 *1                    |               |

| 8/10-bit A/D converter                                                   | Δ                  | #18 | 12н             | FFFFB4 <sub>H</sub> | ICR03          | 0000ВЗн*1                    |               |

| 16-bit free-run timer overflow                                           | Δ                  | #19 | 13н             | FFFFB0 <sub>H</sub> | ICD04          | 0000004 *1                   |               |

| Reserved                                                                 | ×                  | #20 | 14н             | FFFFAC⊦             | ICR04          | 0000В4н*1                    |               |

| Reserved                                                                 | ×                  | #21 | 15н             | FFFFA8 <sub>H</sub> | IODOF          | 000005 *1                    |               |

| PPG timer ch0, ch1 underflow                                             | ×                  | #22 | 16н             | FFFFA4 <sub>H</sub> | ICR05          | 0000В5н*1                    |               |

| Input capture 0-input                                                    | Δ                  | #23 | 17н             | FFFFA0 <sub>H</sub> | ICDOC          | 0000DC *1                    |               |

| External interrupt (INT4/INT5)                                           | Δ                  | #24 | 18н             | FFFF9C <sub>H</sub> | ICR06          | 0000В6н*1                    |               |

| Input capture 1-input                                                    | Δ                  | #25 | 19н             | FFFF98 <sub>H</sub> | ICR07          | 0000D7*2                     |               |

| PPG timer ch2, ch3 underflow                                             | ×                  | #26 | 1Ан             | FFFF94 <sub>H</sub> | ICHU/          | 0000В7н*2                    |               |

| External interrupt (INT6/INT7)                                           | Δ                  | #27 | 1Вн             | FFFF90 <sub>H</sub> | ICR08          | 0000B8н*1                    |               |

| Watch timer                                                              | Δ                  | #28 | 1Сн             | FFFF8C <sub>H</sub> | ICHU           | ООООВОН .                    |               |

| Reserved                                                                 | ×                  | #29 | 1Dн             | FFFF88 <sub>H</sub> |                |                              |               |

| Input capture 2-input<br>Input capture 3-input                           | ×                  | #30 | 1Ен             | FFFF84 <sub>H</sub> | ICR09          | 0000В9н*1                    |               |

| Reserved                                                                 | ×                  | #31 | 1F <sub>H</sub> | FFFF80 <sub>H</sub> | ICR10          | 0000BAн*1                    |               |

| Reserved                                                                 | ×                  | #32 | 20н             | FFFF7C <sub>H</sub> |                | UUUUDAH '                    |               |

| Reserved                                                                 | ×                  | #33 | 21н             | FFFF78⊦             | ICD11          | OD44 0000DD #1               |               |

| Reserved                                                                 | ×                  | #34 | 22н             | FFFF74 <sub>H</sub> | IUNII          | ICR11 0000BB <sub>H</sub> *1 |               |

| Reserved                                                                 | ×                  | #35 | 23н             | FFFF70 <sub>H</sub> | 10040 20000 #1 |                              | $\downarrow$  |