## Buffered Quad, 18-Bit, 350ksps/Ch Differential ±10.24V ADC with 30V<sub>P-P</sub> Common Mode Range

### **FEATURES**

- Simultaneous Sampling of 4 Buffered Channels

- 350ksps per Channel Throughput

- 500pA/12nA Max Input Leakage at 85°C/125°C

- ±3.5LSB INL (Maximum, ±10.24V Range)

- Guaranteed 18-Bit, No Missing Codes

- Differential, Wide Common Mode Range Inputs

- Per-Channel SoftSpan Input Ranges:

- ±10.24V, 0V to 10.24V, ±5.12V, 0V to 5.12V

- ±12.5V, 0V to 12.5V, ±6.25V, 0V to 6.25V

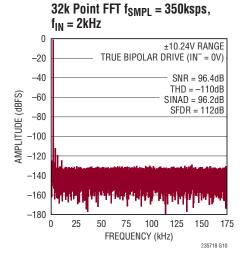

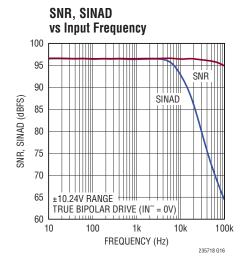

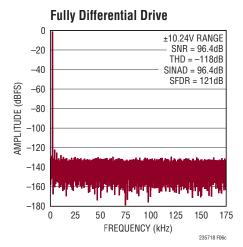

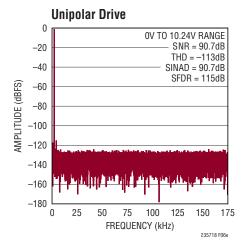

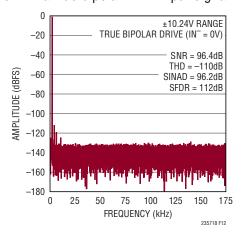

- 96.4dB Single-Conversion SNR (Typical)

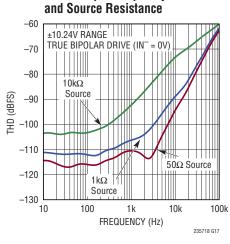

- -110dB THD (Typical) at f<sub>IN</sub> = 2kHz

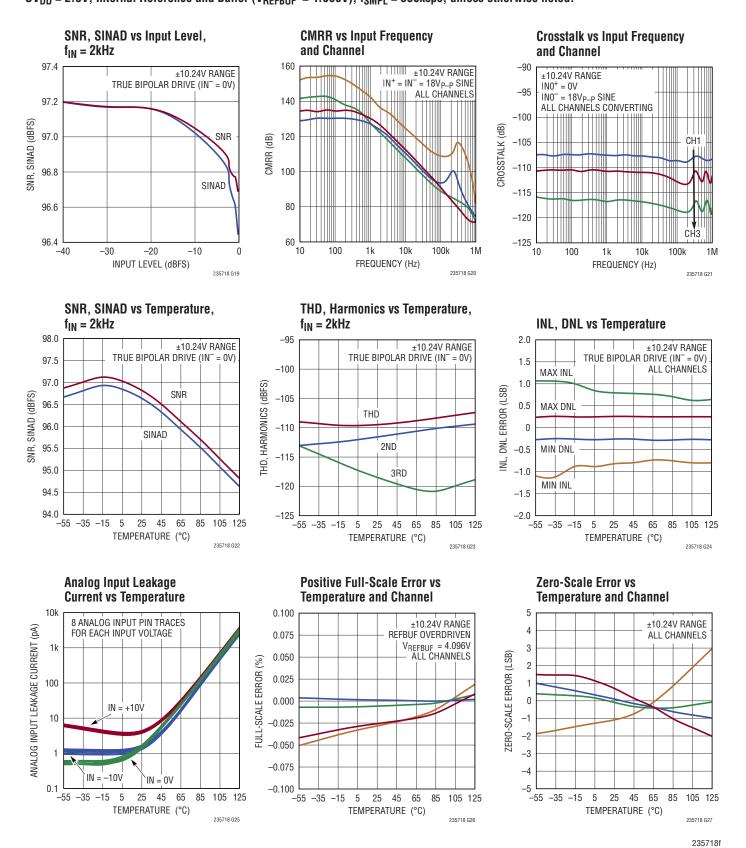

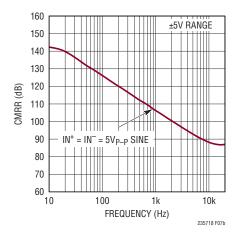

- 128dB CMRR (Typical) at f<sub>IN</sub> = 200Hz

- Rail-to-Rail Input Overdrive Tolerance

- Integrated Reference and Buffer (4.096V)

- SPI CMOS (1.8V to 5V) and LVDS Serial I/O

- Internal Conversion Clock, No Cycle Latency

- 175mW Power Dissipation (44mW/Ch Typical)

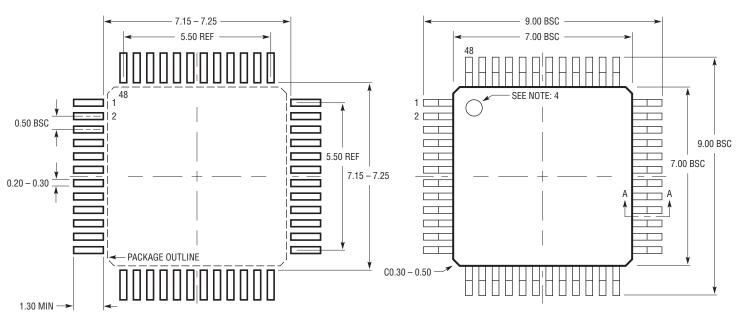

- 48-Lead (7mm x 7mm) LQFP Package

## **APPLICATIONS**

- Programmable Logic Controllers

- Industrial Process Control

- Power Line Monitoring

- Test and Measurement

## DESCRIPTION

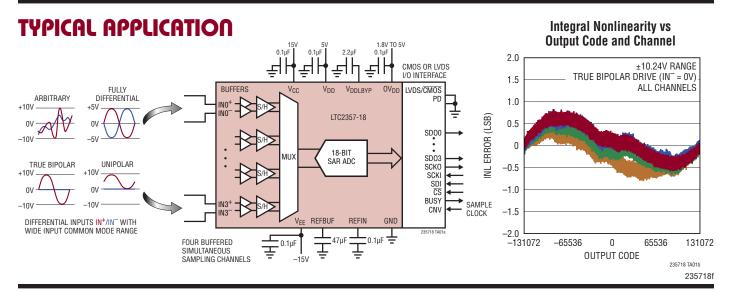

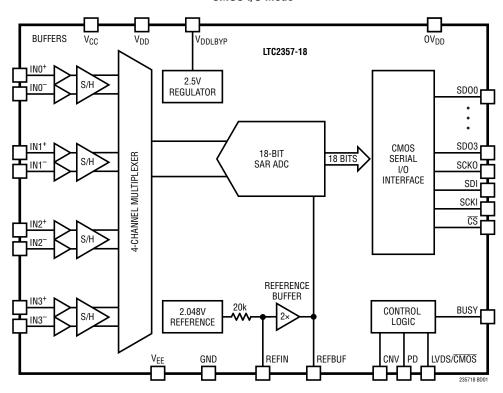

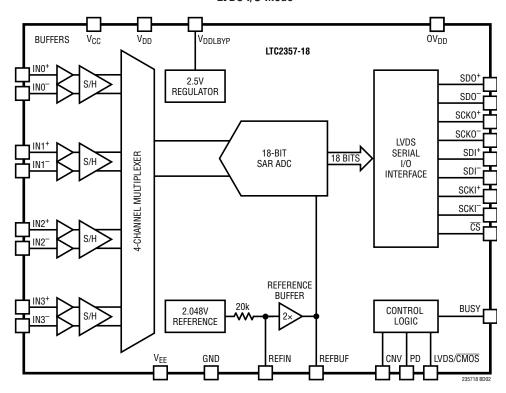

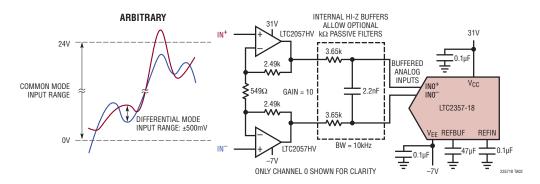

The LTC®2357-18 is an 18-bit, low noise 4-channel simultaneous sampling successive approximation register (SAR) ADC with buffered differential, wide common mode range picoamp inputs. Operating from a 5V low voltage supply, flexible high voltage supplies, and using the internal reference and buffer, each channel of this SoftSpan™ ADC can be independently configured on a conversion-by-conversion basis to accept ±10.24V, 0V to 10.24V, ±5.12V, or 0V to 5.12V signals. Individual channels may also be disabled to increase throughput on the remaining channels.

The integrated picoamp-input analog buffers, wide input common mode range and 128dB CMRR of the LTC2357-18 allow the ADC to directly digitize a variety of signals using minimal board space and power. This input signal flexibility, combined with ±3.5LSB INL, no missing codes at 18 bits, and 96.4dB SNR, makes the LTC2357-18 an ideal choice for many high voltage applications requiring wide dynamic range.

The LTC2357-18 supports pin-selectable SPI CMOS (1.8V to 5V) and LVDS serial interfaces. Between one and four lanes of data output may be employed in CMOS mode, allowing the user to optimize bus width and throughput.

All registered trademarks and trademarks are the property of their respective owners. Protected by U.S. Patents, including 7705765, 7961132, 8319673, 9197235.

## **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1, 2)

| Supply Voltage ( $V_{CC}$ )                                                              |

|------------------------------------------------------------------------------------------|

| Supply Voltage Difference (V <sub>CC</sub> – V <sub>EE</sub> )40V                        |

| Supply Voltage (V <sub>DD</sub> )6V                                                      |

| Supply Voltage (OV <sub>DD</sub> )6V                                                     |

| Internal Regulated Supply Bypass (V <sub>DDLBYP</sub> ) (Note 3)                         |

| Analog Input Voltage                                                                     |

| INO+ to IN3+,                                                                            |

| INO <sup>-</sup> to IN3 <sup>-</sup> (Note 4) ( $V_{EE} - 0.3V$ ) to ( $V_{CC} + 0.3V$ ) |

| REFIN0.3V to 2.8V                                                                        |

| REFBUF, CNV (Note 5) –0.3V to (V <sub>DD</sub> + 0.3V)                                   |

| Digital Input Voltage (Note 5) –0.3V to (OV <sub>DD</sub> + 0.3V)                        |

| Digital Output Voltage (Note 5) $-0.3V$ to $(OV_{DD} + 0.3V)$                            |

| Power Dissipation 500mW                                                                  |

| Operating Temperature Range                                                              |

| LTC2357C0°C to 70°C                                                                      |

| LTC2357I40°C to 85°C                                                                     |

| LTC2357H40°C to 125°C                                                                    |

| Storage Temperature Range65°C to 150°C                                                   |

|                                                                                          |

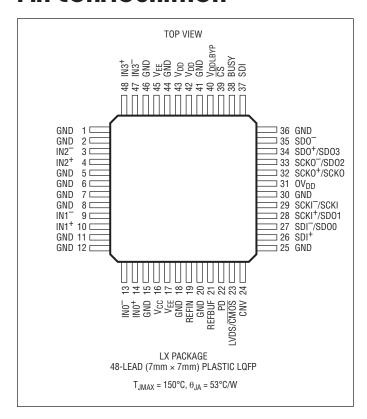

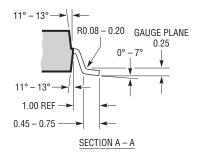

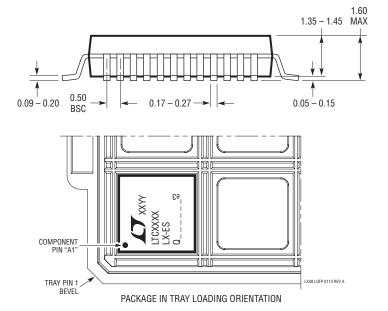

## PIN CONFIGURATION

## ORDER INFORMATION http://www.linear.com/product/LTC2357-18#orderinfo

| TRAY              | PART MARKING* | PACKAGE DESCRIPTION              | TEMPERATURE RANGE |

|-------------------|---------------|----------------------------------|-------------------|

| LTC2357CLX-18#PBF | LTC2357LX-18  | 48-Lead (7mm × 7mm) Plastic LQFP | 0°C to 70°C       |

| LTC2357ILX-18#PBF | LTC2357LX-18  | 48-Lead (7mm × 7mm) Plastic LQFP | –40°C to 85°C     |

| LTC2357HLX-18#PBF | LTC2357LX-18  | 48-Lead (7mm × 7mm) Plastic LQFP | -40°C to 125°C    |

Consult ADI Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

## **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 6)

| SYMBOL                                           | PARAMETER                                                       | CONDITIONS                                                                                                                                                                                                                                                                                                                                                                                                                                         |   | MIN                                                                                                                               | TYP   | MAX                                                                                                                                                                                                                     | UNITS                 |

|--------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------------------------------------------------------------------------------------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| V <sub>IN</sub> +                                | Absolute Input Range<br>(INO+ to IN3+)                          | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | V <sub>EE</sub> + 4                                                                                                               |       | V <sub>CC</sub> – 4                                                                                                                                                                                                     | V                     |

| V <sub>IN</sub> -                                | Absolute Input Range<br>(INO <sup>-</sup> to IN3 <sup>-</sup> ) | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | V <sub>EE</sub> + 4                                                                                                               |       | V <sub>CC</sub> – 4                                                                                                                                                                                                     | V                     |

| $V_{IN}$ + $-V_{IN}$ -                           | Input Differential<br>Voltage Range                             | SoftSpan 7: ±2.5 • V <sub>REFBUF</sub> Range (Note 7)<br>SoftSpan 6: ±2.5 • V <sub>REFBUF</sub> /1.024 Range (Note 7)<br>SoftSpan 5: 0V to 2.5 • V <sub>REFBUF</sub> Range (Note 7)<br>SoftSpan 4: 0V to 2.5 • V <sub>REFBUF</sub> /1.024 Range (Note 7)<br>SoftSpan 3: ±1.25 • V <sub>REFBUF</sub> Range (Note 7)<br>SoftSpan 2: ±1.25 • V <sub>REFBUF</sub> /1.024 Range (Note 7)<br>SoftSpan 1: 0V to 1.25 • V <sub>REFBUF</sub> Range (Note 7) | • | -2.5 • V <sub>REFBUF</sub> /1.024<br>0<br>0<br>-1.25 • V <sub>REFBUF</sub> /1.024<br>0<br>-1.25 • V <sub>REFBUF</sub> /1.024<br>0 |       | 2.5 • V <sub>REFBUF</sub> /1.024<br>2.5 • V <sub>REFBUF</sub> /1.024<br>2.5 • V <sub>REFBUF</sub> /1.024<br>1.25 • V <sub>REFBUF</sub> /1.024<br>1.25 • V <sub>REFBUF</sub> /1.024<br>1.25 • V <sub>REFBUF</sub> /1.024 | V<br>V<br>V<br>V<br>V |

| V <sub>CM</sub>                                  | Input Common Mode<br>Voltage Range                              | (Note 7)                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | V <sub>EE</sub> + 4                                                                                                               |       | V <sub>CC</sub> – 4                                                                                                                                                                                                     | V                     |

| $V_{IN}$ + $-V_{IN}$ $-$                         | Input Differential<br>Overdrive Tolerance                       | (Note 8)                                                                                                                                                                                                                                                                                                                                                                                                                                           | • | -(V <sub>CC</sub> - V <sub>EE</sub> )                                                                                             |       | (V <sub>CC</sub> - V <sub>EE</sub> )                                                                                                                                                                                    | V                     |

| I <sub>OVERDRIVE</sub>                           | Input Overdrive<br>Current Tolerance                            | $V_{IN+} > V_{CC}$ , $V_{IN-} > V_{CC}$ (Note 8)<br>$V_{IN+} < V_{EE}$ , $V_{IN-} < V_{EE}$ (Note 8)                                                                                                                                                                                                                                                                                                                                               | • | 0                                                                                                                                 |       | 10                                                                                                                                                                                                                      | mA<br>mA              |

| I <sub>IN</sub>                                  | Analog Input Leakage<br>Current                                 | C-Grade and I-Grade<br>H-Grade                                                                                                                                                                                                                                                                                                                                                                                                                     | • |                                                                                                                                   | 5     | 500<br>12                                                                                                                                                                                                               | pA<br>pA<br>nA        |

| I <sub>IN</sub> + – I <sub>IN</sub> <sup>–</sup> | Analog Input Leakage<br>Offset Current                          | $V_{IN}^+ = V_{IN}^-$<br>$V_{IN}^+ = V_{IN}^-$ , C-Grade and I-Grade<br>$V_{IN}^+ = V_{IN}^-$ , H-Grade                                                                                                                                                                                                                                                                                                                                            | • | -100<br>-1.2                                                                                                                      | ±1    | 100<br>1.2                                                                                                                                                                                                              | pA<br>pA<br>nA        |

| R <sub>IN</sub>                                  | Analog Input Resistance                                         | For Each Pin                                                                                                                                                                                                                                                                                                                                                                                                                                       |   | >                                                                                                                                 | >1000 |                                                                                                                                                                                                                         | GΩ                    |

| C <sub>IN</sub>                                  | Analog Input<br>Capacitance                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                    |   |                                                                                                                                   | 3     |                                                                                                                                                                                                                         | pF                    |

| CMRR                                             | Input Common Mode<br>Rejection Ratio                            | $V_{IN}$ + = $V_{IN}$ - = 18 $V_{P-P}$ 200Hz Sine                                                                                                                                                                                                                                                                                                                                                                                                  | • | 105                                                                                                                               | 128   |                                                                                                                                                                                                                         | dB                    |

| V <sub>IHCNV</sub>                               | CNV High Level Input<br>Voltage                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • | 1.3                                                                                                                               |       |                                                                                                                                                                                                                         | V                     |

| V <sub>ILCNV</sub>                               | CNV Low Level Input<br>Voltage                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                    | • |                                                                                                                                   |       | 0.5                                                                                                                                                                                                                     | V                     |

| I <sub>INCNV</sub>                               | CNV Input Current                                               | V <sub>IN</sub> = 0V to V <sub>DD</sub>                                                                                                                                                                                                                                                                                                                                                                                                            | • | -10                                                                                                                               |       | 10                                                                                                                                                                                                                      | μA                    |

## **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 9)

| SYMBOL | PARAMETER CONDITIONS         |                                                                                                                                                                                                                |       |                        | TYP                      | MAX                | UNITS                                                          |

|--------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|--------------------------|--------------------|----------------------------------------------------------------|

|        | Resolution                   |                                                                                                                                                                                                                | •     | 18                     |                          |                    | Bits                                                           |

|        | No Missing Codes             |                                                                                                                                                                                                                | •     | 18                     |                          |                    | Bits                                                           |

|        | Transition Noise             | SoftSpans 7 and 6: ±10.24V and ±10V Ranges SoftSpans 5 and 4: 0V to 10.24V and 0V to 10V Ranges SoftSpans 3 and 2: ±5.12V and ±5V Ranges SoftSpan 1: 0V to 5.12V Range                                         |       |                        | 1.4<br>2.8<br>2.1<br>4.2 |                    | LSB <sub>RMS</sub><br>LSB <sub>RMS</sub><br>LSB <sub>RMS</sub> |

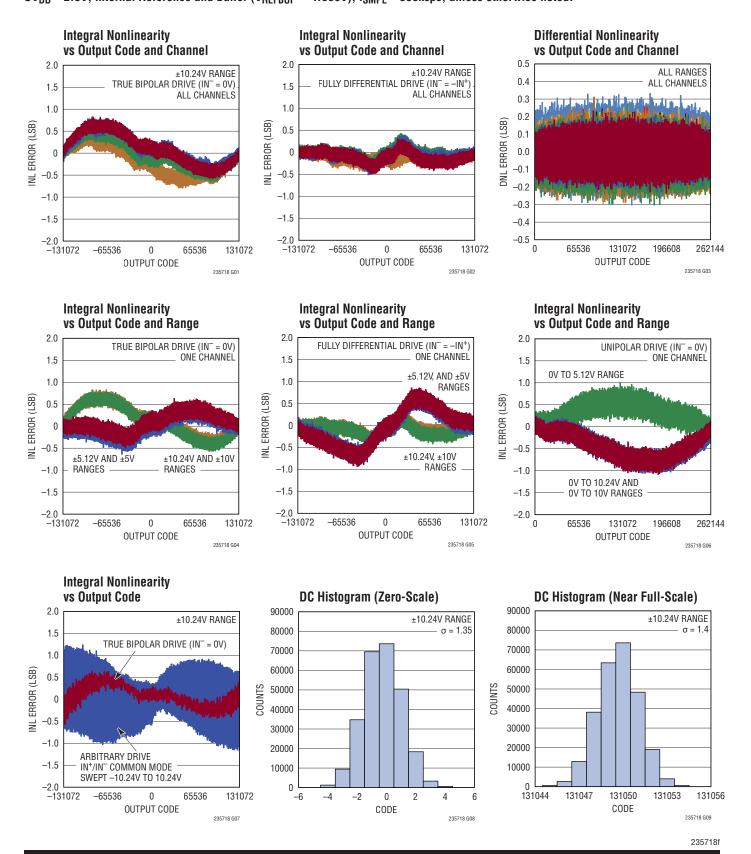

| INL    | Integral Linearity Error     | SoftSpans 7 and 6: ±10.24V and ±10V Ranges (Note 10) SoftSpans 5 and 4: 0V to 10.24V and 0V to 10V Ranges (Note 10) SoftSpans 3 and 2: ±5.12V and ±5V Ranges (Note 10) SoftSpan 1: 0V to 5.12V Range (Note 10) | • • • | -3.5<br>-5<br>-4<br>-6 | ±1<br>±1<br>±1.5<br>±1   | 3.5<br>5<br>4<br>6 | LSB<br>LSB<br>LSB<br>LSB                                       |

| DNL    | Differential Linearity Error | (Note 11)                                                                                                                                                                                                      | •     | -0.9                   | ±0.2                     | 0.9                | LSB                                                            |

## **CONVERTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25 \,^{\circ}\text{C}$ . (Note 9)

| SYMBOL | PARAMETER              | CONDITIONS                                                 |   | MIN  | TYP    | MAX | UNITS  |

|--------|------------------------|------------------------------------------------------------|---|------|--------|-----|--------|

| ZSE    | Zero-Scale Error       | (Note 12)                                                  | • | -900 | ±80    | 900 | μV     |

|        | Zero-Scale Error Drift |                                                            |   |      | ±4     |     | μV/°C  |

| FSE    | Full-Scale Error       | V <sub>REFBUF</sub> = 4.096V (REFBUF Overdriven) (Note 12) | • | -0.1 | ±0.025 | 0.1 | %FS    |

|        | Full-Scale Error Drift | V <sub>REFBUF</sub> = 4.096V (REFBUF Overdriven) (Note 12) |   |      | ±2.5   |     | ppm/°C |

## **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $A_{IN} = -1 dBFS$ . (Notes 9, 13)

| SYMBOL | PARAMETER                               | CONDITIONS                                                                                                                                                                                                                                                             |       | MIN                          | TYP                          | MAX                        | UNITS                |

|--------|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------------------------|------------------------------|----------------------------|----------------------|

| SINAD  | Signal-to-(Noise +<br>Distortion) Ratio | SoftSpans 7 and 6: $\pm 10.24$ V and $\pm 10$ V Ranges, $f_{IN} = 2$ kHz SoftSpans 5 and 4: 0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2$ kHz SoftSpans 3 and 2: $\pm 5.12$ V and $\pm 5$ V Ranges, $f_{IN} = 2$ kHz SoftSpan 1: 0V to 5.12V Range, $f_{IN} = 2$ kHz | •     | 92.7<br>86.9<br>89.3<br>83.6 | 96.2<br>90.3<br>92.5<br>86.6 |                            | dB<br>dB<br>dB<br>dB |

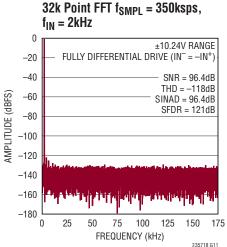

| SNR    | Signal-to-Noise Ratio                   | SoftSpans 7 and 6: $\pm 10.24$ V and $\pm 10$ V Ranges, $f_{IN} = 2$ kHz SoftSpans 5 and 4: 0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2$ kHz SoftSpans 3 and 2: $\pm 5.12$ V and $\pm 5$ V Ranges, $f_{IN} = 2$ kHz SoftSpan 1: 0V to 5.12V Range, $f_{IN} = 2$ kHz | • • • | 92.8<br>87.0<br>89.5<br>83.6 | 96.4<br>90.4<br>92.5<br>86.6 |                            | dB<br>dB<br>dB<br>dB |

| THD    | Total Harmonic Distortion               | SoftSpans 7 and 6: $\pm 10.24$ V and $\pm 10$ V Ranges, $f_{IN} = 2$ kHz SoftSpans 5 and 4: 0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2$ kHz SoftSpans 3 and 2: $\pm 5.12$ V and $\pm 5$ V Ranges, $f_{IN} = 2$ kHz SoftSpan 1: 0V to 5.12V Range, $f_{IN} = 2$ kHz | • • • |                              | -110<br>-111<br>-112<br>-113 | -101<br>-99<br>-102<br>-99 | dB<br>dB<br>dB<br>dB |

| SFDR   | Spurious Free Dynamic<br>Range          | SoftSpans 7 and 6: $\pm 10.24$ V and $\pm 10$ V Ranges, $f_{IN} = 2$ kHz SoftSpans 5 and 4: 0V to 10.24V and 0V to 10V Ranges, $f_{IN} = 2$ kHz SoftSpans 3 and 2: $\pm 5.12$ V and $\pm 5$ V Ranges, $f_{IN} = 2$ kHz SoftSpan 1: 0V to 5.12V Range, $f_{IN} = 2$ kHz | • • • | 101<br>99<br>103<br>99       | 112<br>113<br>114<br>114     |                            | dB<br>dB<br>dB<br>dB |

|        | Channel-to-Channel<br>Crosstalk         | One Channel Converting 18V <sub>P-P</sub> 200Hz Sine in ±10.24V Range, Crosstalk to All Other Channels                                                                                                                                                                 |       |                              | -109                         |                            | dB                   |

|        | -3dB Input Bandwidth                    |                                                                                                                                                                                                                                                                        |       |                              | 6                            |                            | MHz                  |

|        | Aperture Delay                          |                                                                                                                                                                                                                                                                        |       |                              | 1                            |                            | ns                   |

|        | Aperture Delay Matching                 |                                                                                                                                                                                                                                                                        |       |                              | 150                          |                            | ps                   |

|        | Aperture Jitter                         |                                                                                                                                                                                                                                                                        |       |                              | 3                            |                            | ps <sub>RMS</sub>    |

|        | Transient Response                      | Full-Scale Step, 0.005% Settling                                                                                                                                                                                                                                       |       |                              | 420                          |                            | ns                   |

## INTERNAL REFERENCE CHARACTERISTICS The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 9)

| SYMBOL             | PARAMETER                                  | CONDITIONS                       |   | MIN   | ТҮР   | MAX   | UNITS  |

|--------------------|--------------------------------------------|----------------------------------|---|-------|-------|-------|--------|

| OTHIDOL            |                                            | CONDITIONS                       |   |       |       | ШАХ   | OMITO  |

| $V_{REFIN}$        | Internal Reference Output Voltage          |                                  |   | 2.043 | 2.048 | 2.053 | V      |

|                    | Internal Reference Temperature Coefficient | (Note 14)                        | • |       | 5     | 20    | ppm/°C |

|                    | Internal Reference Line Regulation         | V <sub>DD</sub> = 4.75V to 5.25V |   |       | 0.1   |       | mV/V   |

|                    | Internal Reference Output Impedance        |                                  |   |       | 20    |       | kΩ     |

| V <sub>REFIN</sub> | REFIN Voltage Range                        | REFIN Overdriven (Note 7)        |   | 1.25  |       | 2.2   | V      |

## REFERENCE BUFFER CHARACTERISTICS

The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25$ °C. (Note 9)

| SYMBOL              | PARAMETER                       | CONDITIONS                                                                                                                 |   | MIN   | TYP         | MAX   | UNITS    |

|---------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------|---|-------|-------------|-------|----------|

| V <sub>REFBUF</sub> | Reference Buffer Output Voltage | REFIN Overdriven, V <sub>REFIN</sub> = 2.048V                                                                              | • | 4.091 | 4.096       | 4.101 | V        |

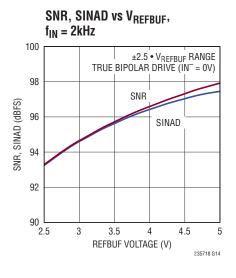

|                     | REFBUF Voltage Range            | REFBUF Overdriven (Notes 7, 15)                                                                                            | • | 2.5   |             | 5     | V        |

|                     | REFBUF Input Impedance          | V <sub>REFIN</sub> = 0V, Buffer Disabled                                                                                   |   |       | 13          |       | kΩ       |

| I <sub>REFBUF</sub> | REFBUF Load Current             | V <sub>REFBUF</sub> = 5V, 4 Channels Enabled (Notes 15, 16)<br>V <sub>REFBUF</sub> = 5V, Acquisition or Nap Mode (Note 15) | • |       | 1.4<br>0.36 | 1.5   | mA<br>mA |

## **DIGITAL INPUTS AND DIGITAL OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 9)

| SYMBOL                          | PARAMETER                               | CONDITIONS                                                                           |   | MIN                    | TYP       | MAX                    | UNITS   |  |  |

|---------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|---|------------------------|-----------|------------------------|---------|--|--|

| CMOS Digital Inputs and Outputs |                                         |                                                                                      |   |                        |           |                        |         |  |  |

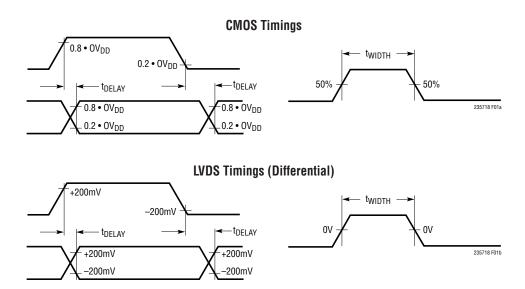

| $\overline{V_{IH}}$             | High Level Input Voltage                |                                                                                      | • | 0.8 • OV <sub>DD</sub> |           |                        | V       |  |  |

| $V_{IL}$                        | Low Level Input Voltage                 |                                                                                      | • |                        |           | 0.2 • OV <sub>DD</sub> | V       |  |  |

| I <sub>IN</sub>                 | Digital Input Current                   | V <sub>IN</sub> = 0V to 0V <sub>DD</sub>                                             | • | -10                    |           | 10                     | μA      |  |  |

| C <sub>IN</sub>                 | Digital Input Capacitance               |                                                                                      |   |                        | 5         |                        | pF      |  |  |

| $V_{OH}$                        | High Level Output Voltage               | I <sub>OUT</sub> = -500μA                                                            | • | 0V <sub>DD</sub> - 0.2 |           |                        | V       |  |  |

| $V_{0L}$                        | Low Level Output Voltage                | I <sub>OUT</sub> = 500μA                                                             | • |                        |           | 0.2                    | V       |  |  |

| I <sub>OZ</sub>                 | Hi-Z Output Leakage Current             | V <sub>OUT</sub> = 0V to OV <sub>DD</sub>                                            | • | -10                    |           | 10                     | μА      |  |  |

| I <sub>SOURCE</sub>             | Output Source Current                   | $V_{OUT} = 0V$                                                                       |   |                        | -50       |                        | mA      |  |  |

| I <sub>SINK</sub>               | Output Sink Current                     | $V_{OUT} = OV_{DD}$                                                                  |   |                        | 50        |                        | mA      |  |  |

|                                 |                                         | LVDS Digital Inputs and Outputs                                                      |   |                        |           |                        |         |  |  |

| $V_{ID}$                        | Differential Input Voltage              |                                                                                      | • | 200                    | 350       | 600                    | mV      |  |  |

| R <sub>ID</sub>                 | On-Chip Input Termination<br>Resistance | $\frac{\overline{CS}}{\overline{CS}} = 0V, V_{ICM} = 1.2V$ $\overline{CS} = 0V_{DD}$ | • | 90                     | 106<br>10 | 125                    | Ω<br>ΜΩ |  |  |

| V <sub>ICM</sub>                | Common-Mode Input Voltage               |                                                                                      | • | 0.3                    | 1.2       | 2.2                    | V       |  |  |

| I <sub>ICM</sub>                | Common-Mode Input Current               | $V_{IN}$ + = $V_{IN}$ - = 0V to $OV_{DD}$                                            | • | -10                    |           | 10                     | μА      |  |  |

| $\overline{V_{OD}}$             | Differential Output Voltage             | $R_L = 100\Omega$ Differential Termination                                           | • | 275                    | 350       | 425                    | mV      |  |  |

| V <sub>OCM</sub>                | Common-Mode Output Voltage              | $R_L = 100\Omega$ Differential Termination                                           | • | 1.1                    | 1.2       | 1.3                    | V       |  |  |

| I <sub>OZ</sub>                 | Hi-Z Output Leakage Current             | $V_{OUT} = 0V \text{ to } 0V_{DD}$                                                   | • | -10                    |           | 10                     | μА      |  |  |

## **POWER REQUIREMENTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25\,^{\circ}$ C. (Note 9)

| SYMBOL                       | PARAMETER                 | CONDITIONS                                                                                                                                                                                                                   |   | MIN                       | ТҮР                                    | MAX                                    | UNITS                      |

|------------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---------------------------|----------------------------------------|----------------------------------------|----------------------------|

| V <sub>CC</sub>              | Supply Voltage            |                                                                                                                                                                                                                              | • | 7.5                       |                                        | 38                                     | V                          |

| V <sub>EE</sub>              | Supply Voltage            |                                                                                                                                                                                                                              | • | -16.5                     |                                        | 0                                      | V                          |

| $\overline{V_{CC} - V_{EE}}$ | Supply Voltage Difference |                                                                                                                                                                                                                              | • | 10                        |                                        | 38                                     | V                          |

| $V_{DD}$                     | Supply Voltage            |                                                                                                                                                                                                                              | • | 4.75                      | 5.00                                   | 5.25                                   | V                          |

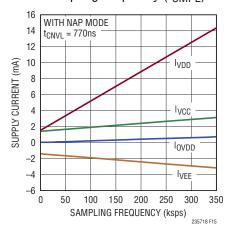

| I <sub>VCC</sub>             | Supply Current            | 350ksps Sample Rate, 4 Channels Enabled (Note 17)<br>Acquisition Mode (Note 17)<br>Nap Mode<br>Power Down Mode                                                                                                               | • |                           | 3.4<br>5.7<br>1.5<br>5                 | 3.9<br>6.9<br>1.8<br>15                | mA<br>mA<br>mA<br>μA       |

| I <sub>VEE</sub>             | Supply Current            | 350ksps Sample Rate, 4 Channels Enabled (Note 17)<br>Acquisition Mode (Note 17)<br>Nap Mode<br>Power Down Mode                                                                                                               | • | -4.1<br>-7.1<br>-2<br>-15 | -3.2<br>-5.6<br>-1.4<br>-4             |                                        | mA<br>mA<br>mA<br>μA       |

| CMOS I/O                     | Mode                      |                                                                                                                                                                                                                              |   |                           |                                        |                                        |                            |

| $OV_{DD}$                    | Supply Voltage            |                                                                                                                                                                                                                              | • | 1.71                      |                                        | 5.25                                   | V                          |

| I <sub>VDD</sub>             | Supply Current            | 350ksps Sample Rate, 4 Channels Enabled<br>350ksps Sample Rate, 4 Channels Enabled, V <sub>REFBUF</sub> = 5V (Note 15)<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade) | • |                           | 14.3<br>12.6<br>1.8<br>1.6<br>84<br>84 | 16<br>14.3<br>2.5<br>2.2<br>275<br>500 | mA<br>mA<br>mA<br>mA<br>μA |

| I <sub>OVDD</sub>            | Supply Current            | 350ksps Sample Rate, 4 Channels Enabled (C <sub>L</sub> = 25pF)<br>Acquisition or Nap Mode<br>Power Down Mode                                                                                                                | • |                           | 1.8<br>1<br>1                          | 2.6<br>20<br>20                        | mA<br>μΑ<br>μΑ             |

| P <sub>D</sub>               | Power Dissipation         | 350ksps Sample Rate, 4 Channels Enabled<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade)                                                                                | • |                           | 175<br>179<br>52<br>0.56<br>0.56       | 207<br>223<br>68<br>1.9<br>3           | mW<br>mW<br>mW<br>mW       |

| LVDS I/O I                   | Mode                      |                                                                                                                                                                                                                              |   |                           |                                        |                                        |                            |

| $OV_{DD}$                    | Supply Voltage            |                                                                                                                                                                                                                              | • | 2.375                     |                                        | 5.25                                   | V                          |

| I <sub>VDD</sub>             | Supply Current            | 350ksps Sample Rate, 4 Channels Enabled<br>350ksps Sample Rate, 4 Channels Enabled, V <sub>REFBUF</sub> = 5V (Note 15)<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade) | • |                           | 16.4<br>14.9<br>3.4<br>3.2<br>84<br>84 | 18.1<br>16.7<br>4.2<br>4<br>275<br>500 | mA<br>mA<br>mA<br>mA<br>μΑ |

| I <sub>OVDD</sub>            | Supply Current            | 350ksps Sample Rate, 4 Channels Enabled ( $R_L$ = 100Ω) Acquisition or Nap Mode ( $R_L$ = 100Ω) Power Down Mode                                                                                                              | • |                           | 7.5<br>7<br>1                          | 8.7<br>8.2<br>20                       | mA<br>mA<br>μA             |

| P <sub>D</sub>               | Power Dissipation         | 350ksps Sample Rate, 4 Channels Enabled<br>Acquisition Mode<br>Nap Mode<br>Power Down Mode (C-Grade and I-Grade)<br>Power Down Mode (H-Grade)                                                                                | • |                           | 200<br>204<br>77<br>0.56<br>0.56       | 232<br>252<br>98<br>1.9<br>3           | mW<br>mW<br>mW<br>mW       |

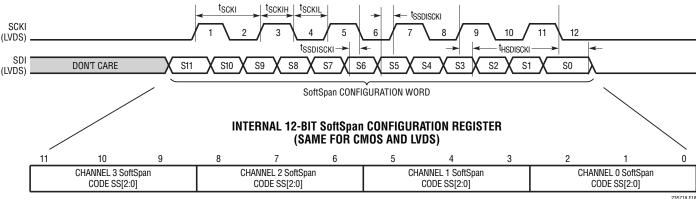

# **RDC TIMING CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . (Note 9)

| SYMBOL                 | PARAMETER                                                      | CONDITIONS                                                                                                                                                                                              |   | MIN                          | ТҮР                      | MAX                      | UNITS                        |

|------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------------------------|--------------------------|--------------------------|------------------------------|

| f <sub>SMPL</sub>      | Maximum Sampling Frequency                                     | 4 Channels Enabled<br>3 Channels Enabled<br>2 Channels Enabled<br>1 Channel Enabled                                                                                                                     | • |                              |                          | 350<br>425<br>550<br>800 | ksps<br>ksps<br>ksps<br>ksps |

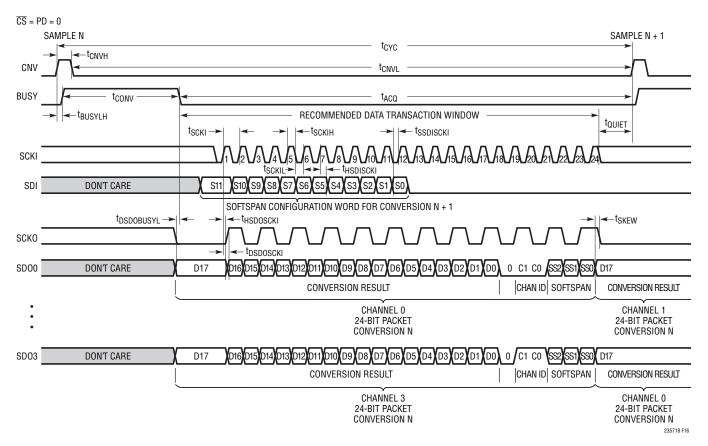

| t <sub>CYC</sub>       | Time Between Conversions                                       | 4 Channels Enabled, f <sub>SMPL</sub> = 350ksps<br>3 Channels Enabled, f <sub>SMPL</sub> = 425ksps<br>2 Channels Enabled, f <sub>SMPL</sub> = 550ksps<br>1 Channel Enabled, f <sub>SMPL</sub> = 800ksps | • | 2855<br>2350<br>1815<br>1250 |                          |                          | ns<br>ns<br>ns<br>ns         |

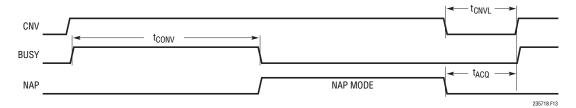

| t <sub>CONV</sub>      | Conversion Time                                                | N Channels Enabled, $1 \le N \le 4$                                                                                                                                                                     | • | 450•N                        | 500•N                    | 550•N                    | ns                           |

| t <sub>ACQ</sub>       | Acquisition Time $(t_{ACQ} = t_{CYC} - t_{CONV} - t_{BUSYLH})$ | 4 Channels Enabled, f <sub>SMPL</sub> = 350ksps<br>3 Channels Enabled, f <sub>SMPL</sub> = 425ksps<br>2 Channels Enabled, f <sub>SMPL</sub> = 550ksps<br>1 Channel Enabled, f <sub>SMPL</sub> = 800ksps | • | 625<br>670<br>685<br>670     | 835<br>830<br>795<br>730 |                          | ns<br>ns<br>ns               |

| t <sub>CNVH</sub>      | CNV High Time                                                  |                                                                                                                                                                                                         | • | 40                           |                          |                          | ns                           |

| t <sub>CNVL</sub>      | CNV Low Time                                                   |                                                                                                                                                                                                         | • | 750                          |                          |                          | ns                           |

| t <sub>BUSYLH</sub>    | CNV↑ to BUSY Delay                                             | C <sub>L</sub> = 25pF                                                                                                                                                                                   | • |                              |                          | 30                       | ns                           |

| t <sub>QUIET</sub>     | Digital I/O Quiet Time from CNV↑                               |                                                                                                                                                                                                         | • | 20                           |                          |                          | ns                           |

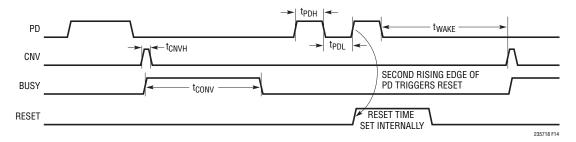

| t <sub>PDH</sub>       | PD High Time                                                   |                                                                                                                                                                                                         | • | 40                           |                          |                          | ns                           |

| t <sub>PDL</sub>       | PD Low Time                                                    |                                                                                                                                                                                                         | • | 40                           |                          |                          | ns                           |

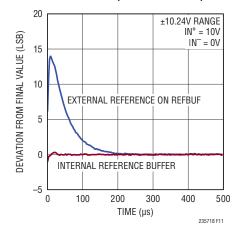

| t <sub>WAKE</sub>      | REFBUF Wake-Up Time                                            | $C_{REFBUF} = 47\mu F$ , $C_{REFIN} = 0.1\mu F$                                                                                                                                                         |   |                              | 200                      |                          | ms                           |

| CMOS I/O I             | Node                                                           |                                                                                                                                                                                                         |   |                              |                          |                          |                              |

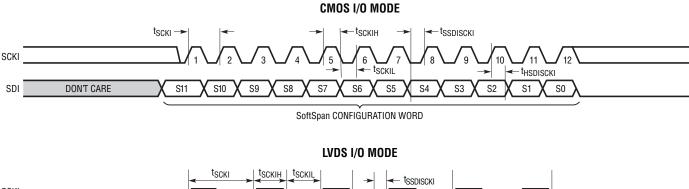

| t <sub>SCKI</sub>      | SCKI Period                                                    | (Notes 18, 19)                                                                                                                                                                                          | • | 10                           |                          |                          | ns                           |

| t <sub>SCKIH</sub>     | SCKI High Time                                                 |                                                                                                                                                                                                         | • | 4                            |                          |                          | ns                           |

| tsckil                 | SCKI Low Time                                                  |                                                                                                                                                                                                         | • | 4                            |                          |                          | ns                           |

| tssdiscki              | SDI Setup Time from SCKI↑                                      | (Note 18)                                                                                                                                                                                               | • | 2                            |                          |                          | ns                           |

| thsdiscki              | SDI Hold Time from SCKI↑                                       | (Note 18)                                                                                                                                                                                               | • | 1                            |                          |                          | ns                           |

| t <sub>DSDOSCKI</sub>  | SDO Data Valid Delay from SCKI↑                                | C <sub>L</sub> = 25pF (Note 18)                                                                                                                                                                         | • |                              |                          | 7.5                      | ns                           |

| t <sub>HSDOSCKI</sub>  | SDO Remains Valid Delay from SCKI↑                             | C <sub>L</sub> = 25pF (Note 18)                                                                                                                                                                         | • | 1.5                          |                          |                          | ns                           |

| t <sub>SKEW</sub>      | SDO to SCKO Skew                                               | (Note 18)                                                                                                                                                                                               | • | -1                           | 0                        | 1                        | ns                           |

| t <sub>DSDOBUSYL</sub> | SDO Data Valid Delay from BUSY↓                                | C <sub>L</sub> = 25pF (Note 18)                                                                                                                                                                         | • | 0                            |                          |                          | ns                           |

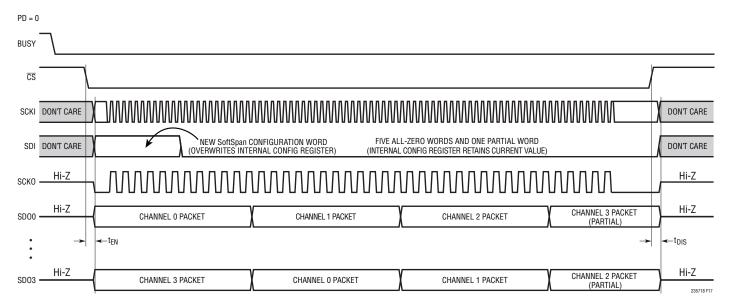

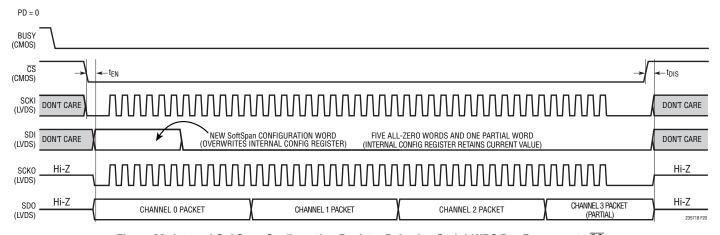

| t <sub>EN</sub>        | Bus Enable Time After CS↓                                      | (Note 18)                                                                                                                                                                                               | • |                              |                          | 15                       | ns                           |

| t <sub>DIS</sub>       | Bus Relinquish Time After CS↑                                  | (Note 18)                                                                                                                                                                                               | • |                              |                          | 15                       | ns                           |

| LVDS I/O M             | ode                                                            |                                                                                                                                                                                                         |   |                              |                          |                          |                              |

| t <sub>SCKI</sub>      | SCKI Period                                                    | (Note 20)                                                                                                                                                                                               | • | 4                            |                          |                          | ns                           |

| t <sub>SCKIH</sub>     | SCKI High Time                                                 | (Note 20)                                                                                                                                                                                               | • | 1.5                          |                          |                          | ns                           |

| t <sub>SCKIL</sub>     | SCKI Low Time                                                  | (Note 20)                                                                                                                                                                                               | • | 1.5                          |                          |                          | ns                           |

| t <sub>SSDISCKI</sub>  | SDI Setup Time from SCKI                                       | (Notes 11, 20)                                                                                                                                                                                          | • | 1.2                          |                          |                          | ns                           |

| t <sub>HSDISCKI</sub>  | SDI Hold Time from SCKI                                        | (Notes 11, 20)                                                                                                                                                                                          | • | -0.2                         |                          |                          | ns                           |

| t <sub>DSDOSCKI</sub>  | SDO Data Valid Delay from SCKI                                 | (Notes 11, 20)                                                                                                                                                                                          | • |                              |                          | 6                        | ns                           |

| thsdoscki              | SDO Remains Valid Delay from SCKI                              | (Notes 11, 20)                                                                                                                                                                                          | • | 1                            |                          |                          | ns                           |

| t <sub>SKEW</sub>      | SDO to SCKO Skew                                               | (Note 11)                                                                                                                                                                                               | • | -0.4                         | 0                        | 0.4                      | ns                           |

| t <sub>DSDOBUSYL</sub> | SDO Data Valid Delay from BUSY↓                                | (Note 11)                                                                                                                                                                                               | • | 0                            |                          |                          | ns                           |

| t <sub>EN</sub>        | Bus Enable Time After CS↓                                      |                                                                                                                                                                                                         | • |                              |                          | 50                       | ns                           |

| t <sub>DIS</sub>       | Bus Relinquish Time After CS↑                                  |                                                                                                                                                                                                         | • |                              |                          | 15                       | ns                           |

## **ADC TIMING CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

Note 2: All voltage values are with respect to GND.

**Note 3:**  $V_{DDLBYP}$  is the output of an internal voltage regulator, and should only be connected to a  $2.2\mu F$  ceramic capacitor to bypass the pin to GND, as described in the Pin Functions section. Do not connect this pin to any external circuitry.

**Note 4:** When these pin voltages are taken below  $V_{EE}$  or above  $V_{CC}$ , they will be clamped by internal diodes. This product can handle input currents of up to 100mA below  $V_{EE}$  or above  $V_{CC}$  without latch-up.

**Note 5:** When these pin voltages are taken below GND or above  $V_{DD}$  or  $OV_{DD}$ , they will be clamped by internal diodes. This product can handle currents of up to 100mA below GND or above  $V_{DD}$  or  $OV_{DD}$  without latch-up.

Note 6:  $-16.5V \le V_{EE} \le 0V$ ,  $7.5V \le V_{CC} \le 38V$ ,  $10V \le (V_{CC} - V_{EE}) \le 38V$ ,  $V_{DD} = 5V$ , unless otherwise specified.

Note 7: Recommended operating conditions.

**Note 8:** Exceeding these limits on any channel may corrupt conversion results on other channels. Driving an analog input above  $V_{CC}$  on any channel up to 10mA will not affect conversion results on other channels. Driving an analog input below  $V_{EE}$  may corrupt conversion results on other channels. Refer to Applications Information section for further details. Refer to Absolute Maximum Ratings section for pin voltage limits related to device reliability.

**Note 9:**  $V_{CC} = 15V$ ,  $V_{EE} = -15V$ ,  $V_{DD} = 5V$ ,  $OV_{DD} = 2.5V$ ,  $f_{SMPL} = 350$ ksps, internal reference and buffer, true bipolar input signal drive in bipolar SoftSpan ranges, unipolar signal drive in unipolar SoftSpan ranges, unless otherwise specified.

**Note 10:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

Note 11: Guaranteed by design, not subject to test.

**Note 13:** All specifications in dB are referred to a full-scale input in the relevant SoftSpan input range, except for crosstalk, which is referred to the crosstalk injection signal amplitude.

**Note 14:** Temperature coefficient is calculated by dividing the maximum change in output voltage by the specified temperature range.

**Note 15:** When REFBUF is overdriven, the internal reference buffer must be disabled by setting REFIN = 0V.

Note 16:  $I_{REFBUF}$  varies proportionally with sample rate and the number of active channels.

**Note 17:** Portions of the analog input circuitry are powered down during conversion, reducing  $I_{VCC}$  and  $I_{VEE}$ . Refer to Applications Information section for more details.

**Note 18:** Parameter tested and guaranteed at  $OV_{DD} = 1.71V$ ,  $OV_{DD} = 2.5V$ , and  $OV_{DD} = 5.25V$ .

Note 19: A  $t_{SCKI}$  period of 10ns minimum allows a shift clock frequency of up to 100MHz for rising edge capture.

**Note 20:**  $V_{ICM} = 1.2V$ ,  $V_{ID} = 350 \text{mV}$  for LVDS differential input pairs.

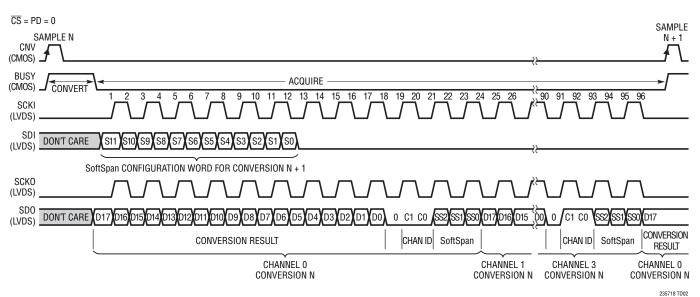

Figure 1. Voltage Levels for Timing Specifications

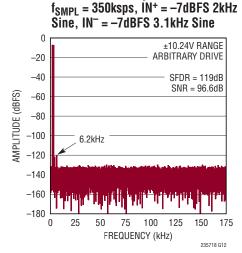

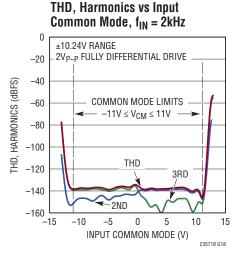

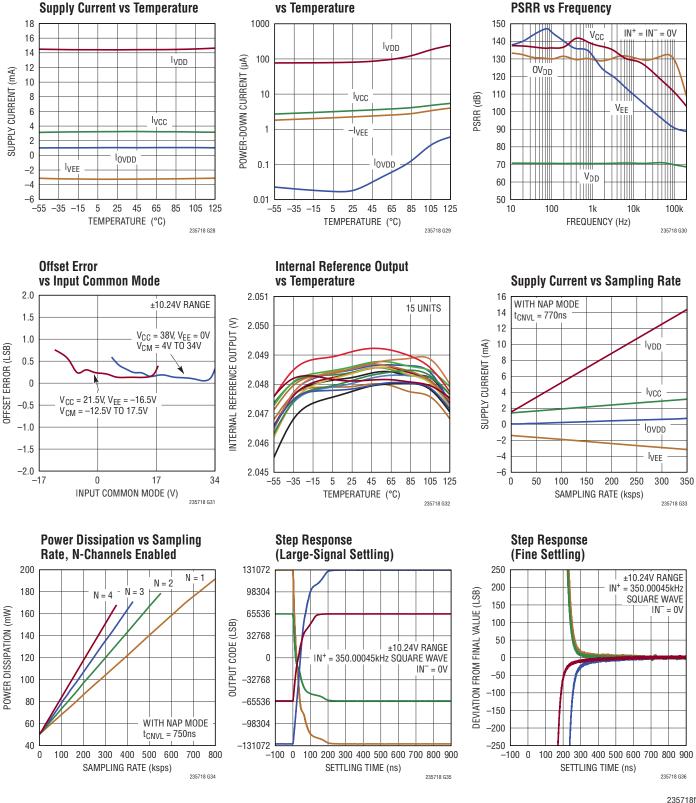

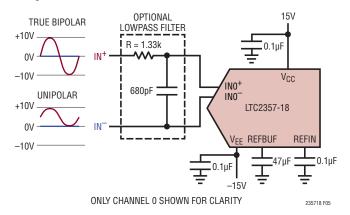

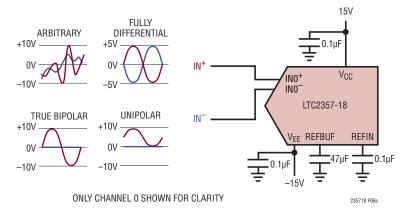

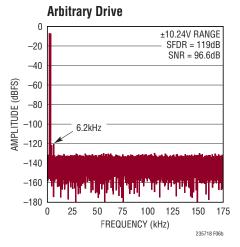

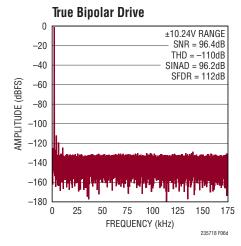

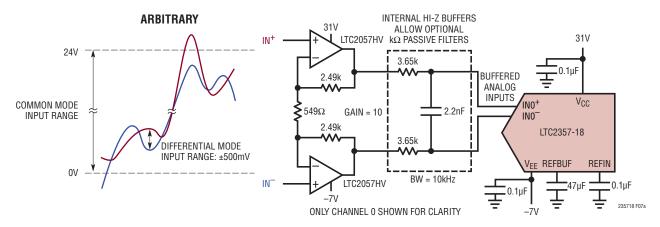

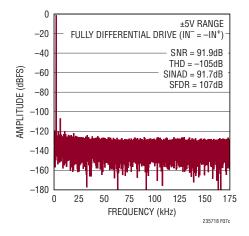

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC} = +15V$ , $V_{EE} = -15V$ , $V_{DD} = 5V$ , $OV_{DD} = 2.5V$ , Internal Reference and Buffer ( $V_{REFBUF} = 4.096V$ ), $f_{SMPL} = 350ksps$ , unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC} = +15V$ , $V_{EE} = -15V$ , $V_{DD} = 5V$ , $OV_{DD} = 2.5V$ , Internal Reference and Buffer ( $V_{REFBUF} = 4.096V$ ), $f_{SMPL} = 350ksps$ , unless otherwise noted.

32k Point Arbitrary Two-Tone FFT

32k Point FFT  $f_{SMPL} = 350ksps$ ,  $f_{IN} = 2kHz$ 0 ±5.12V RANGE TRUE BIPOLAR DRIVE (IN = 0V) -20 -40 SNR = 92.7dB THD = -111dBAMPLITUDE (dBFS) -60 SINAD = 92.6dB SFDR = 115dB -80 -100 -120-140-160-1800 25 75 100 125 150 175 FREQUENCY (kHz) 235718 G13

**THD vs Input Frequency**

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC} = +15V$ , $V_{EE} = -15V$ , $V_{DD} = 5V$ , $0V_{DD} = 2.5V$ , Internal Reference and Buffer ( $V_{REFBUF} = 4.096V$ ), $f_{SMPL} = 350ksps$ , unless otherwise noted.

## **TYPICAL PERFORMANCE CHARACTERISTICS** $T_A = 25^{\circ}C$ , $V_{CC} = +15V$ , $V_{EE} = -15V$ , $V_{DD} = 5V$ , $0V_{DD} = 2.5V$ , Internal Reference and Buffer ( $V_{REFBUF} = 4.096V$ ), $f_{SMPL} = 350ksps$ , unless otherwise noted.

**Power-Down Current**

### PIN FUNCTIONS

Pins that are the Same for All Digital I/O Modes

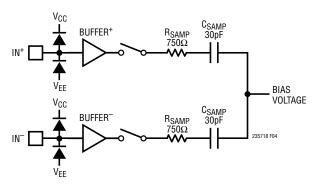

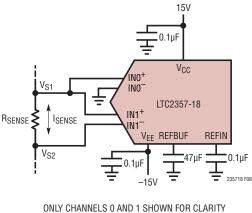

**INO**+/**INO**- **to IN3**+/**IN3**- **(Pins 14/13, 10/9, 4/3, and 48/47):** Positive and Negative Analog Inputs, Channels 0 to 3. The converter simultaneously samples and digitizes  $(V_{IN}+-V_{IN}-)$  for all channels. Wide input common mode range  $(V_{EE}+4V \leq V_{CM} \leq V_{CC}-4V)$  and high common mode rejection allow the inputs to accept a wide variety of signal swings. Full-scale input range is determined by the channel's SoftSpan configuration.

**GND** (Pins 1, 2, 5, 6, 7, 8, 11, 12, 15, 18, 20, 25, 30, 36, 41, 44, 46): Ground. Solder all GND pins to a solid ground plane.

**V<sub>CC</sub>** (**Pin 16**): Positive High Voltage Power Supply. The range of  $V_{CC}$  is 7.5V to 38V with respect to GND and 10V to 38V with respect to  $V_{EE}$ . Bypass  $V_{CC}$  to GND close to the pin with a 0.1µF ceramic capacitor.

$V_{EE}$  (Pins 17, 45): Negative High Voltage Power Supply. The range of  $V_{EE}$  is 0V to -16.5V with respect to GND and -10V to -38V with respect to  $V_{CC}$ . Connect Pins 17 and 45 together and bypass the  $V_{EE}$  network to GND close to Pin 17 with a 0.1μF ceramic capacitor. In applications where  $V_{EE}$  is shorted to GND, this capacitor may be omitted.

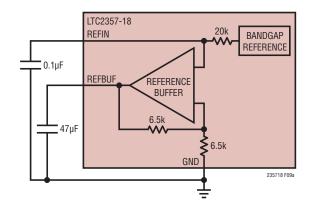

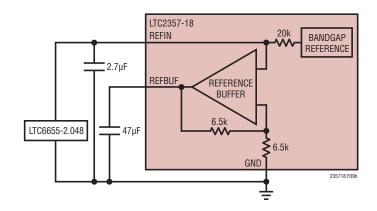

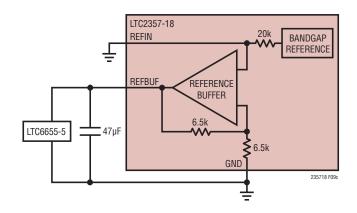

**REFIN (Pin 19):** Bandgap Reference Output/Reference Buffer Input. An internal bandgap reference nominally outputs 2.048V on this pin. An internal reference buffer amplifies  $V_{REFIN}$  to create the converter master reference voltage  $V_{REFBUF} = 2 \cdot V_{REFIN}$  on the REFBUF pin. When using the internal reference, bypass REFIN to GND (Pin 20) close to the pin with a 0.1µF ceramic capacitor to filter the bandgap output noise. If more accuracy is desired, overdrive REFIN with an external reference in the range of 1.25V to 2.2V. Do not load this pin when internal reference is used.

**REFBUF (Pin 21):** Internal Reference Buffer Output. An internal reference buffer amplifies  $V_{REFIN}$  to create the converter master reference voltage  $V_{REFBUF} = 2 \cdot V_{REFIN}$  on this pin, nominally 4.096V when using the internal bandgap reference. Bypass REFBUF to GND (Pin 20) close

to the pin with a  $47\mu F$  ceramic capacitor. The internal reference buffer may be disabled by grounding its input at REFIN. With the buffer disabled, overdrive REFBUF with an external reference voltage in the range of 2.5V to 5V. When using the internal reference buffer, limit the loading of any external circuitry connected to REFBUF to less than 200 $\mu A$ . Using a high input impedance amplifier to buffer  $V_{REFBUF}$  to any external circuits is recommended.

**PD** (**Pin 22**): Power Down Input. When this pin is brought high, the LTC2357-18 is powered down and subsequent conversion requests are ignored. If this occurs during a conversion, the device powers down once the conversion completes. If this pin is brought high twice without an intervening conversion, an internal global reset is initiated, equivalent to a power-on-reset event. Logic levels are determined by  $OV_{DD}$ .

**LVDS/CMOS** (Pin 23): I/O Mode Select. Tie this pin to OV<sub>DD</sub> to select LVDS I/O mode, or to ground to select CMOS I/O mode. Logic levels are determined by OV<sub>DD</sub>.

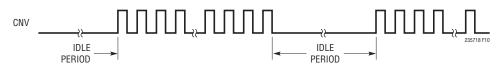

**CNV** (**Pin 24**): Conversion Start Input. A rising edge on this pin puts the internal sample-and-holds into the hold mode and initiates a new conversion. CNV is not gated by  $\overline{CS}$ , allowing conversions to be initiated independent of the state of the serial I/O bus.

**BUSY (Pin 38):** Busy Output. The BUSY signal indicates that a conversion is in progress. This pin transitions low-to-high at the start of each conversion and stays high until the conversion is complete. Logic levels are determined by OV<sub>DD</sub>.

$V_{DDLBYP}$  (Pin 40): Internal 2.5V Regulator Bypass Pin. The voltage on this pin is generated via an internal regulator operating off of  $V_{DD}$ . This pin must be bypassed to GND close to the pin with a 2.2μF ceramic capacitor. Do not connect this pin to any external circuitry.

$V_{DD}$  (Pins 42, 43): 5V Power Supply. The range of  $V_{DD}$  is 4.75V to 5.25V. Connect Pins 42 and 43 together and bypass the  $V_{DD}$  network to GND with a shared 0.1 $\mu$ F ceramic capacitor close to the pins.

### PIN FUNCTIONS

#### CMOS I/O Mode

**SDI**<sup>+</sup>, **SDO**<sup>-</sup> (**Pins 26 and 35**): LVDS Input and Output. In CMOS I/O mode these pins are Hi-Z.

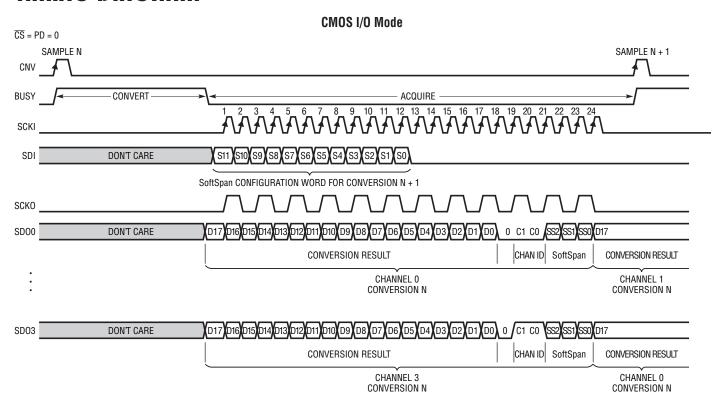

**SD00 to SD03 (Pins 27, 28, 33, and 34):** CMOS Serial Data Outputs, Channels 0 to 3. The most recent conversion result along with channel configuration information is clocked out onto the SD0 pins on each rising edge of SCKI. Output data formatting is described in the Digital Interface section. Leave unused SD0 outputs unconnected. Logic levels are determined by  $OV_{DD}$ .

**SCKI (Pin 29):** CMOS Serial Clock Input. Drive SCKI with the serial I/O clock. SCKI rising edges latch serial data in on SDI and clock serial data out on SD00 to SD03. For standard SPI bus operation, capture output data at the receiver on rising edges of SCKI. SCKI is allowed to idle either high or low. Logic levels are determined by OV<sub>DD</sub>.

**OV**<sub>DD</sub> (**Pin 31**): I/O Interface Power Supply. In CMOS I/O mode, the range of  $OV_{DD}$  is 1.71V to 5.25V. Bypass  $OV_{DD}$  to GND (Pin 30) close to the pin with a 0.1µF ceramic capacitor.

**SCKO** (Pin 32): CMOS Serial Clock Output. SCKI rising edges trigger transitions on SCKO that are skew-matched to the serial output data streams on SDO0 to SDO3. The resulting SCKO frequency is half that of SCKI. Rising and falling edges of SCKO may be used to capture SDO data at the receiver (FPGA) in double data rate (DDR) fashion. For standard SPI bus operation, SCKO is not used and should be left unconnected. SCKO is forced low at the falling edge of BUSY. Logic levels are determined by OV<sub>DD</sub>.

**SDI (Pin 37):** CMOS Serial Data Input. Drive this pin with the desired 12-bit SoftSpan configuration word (see Table 1a), latched on the rising edges of SCKI. If all channels will be configured to operate only in SoftSpan 7, tie SDI to  $OV_{DD}$ . Logic levels are determined by  $OV_{DD}$ .

$\overline{\text{CS}}$  (Pin 39): Chip Select Input. The serial data I/O bus is enabled when  $\overline{\text{CS}}$  is low and is disabled and Hi-Z when  $\overline{\text{CS}}$  is high.  $\overline{\text{CS}}$  also gates the external shift clock, SCKI. Logic levels are determined by OV<sub>DD</sub>.

#### LVDS I/O Mode

**SDI**<sup>+</sup>/**SDI**<sup>-</sup> (**Pins 26/27**): LVDS Positive and Negative Serial Data Input. Differentially drive SDI<sup>+</sup>/SDI<sup>-</sup> with the desired 12-bit SoftSpan configuration word (see Table 1a), latched on both the rising and falling edges of SCKI<sup>+</sup>/SCKI<sup>-</sup>. The SDI<sup>+</sup>/SDI<sup>-</sup> input pair is internally terminated with a  $100\Omega$  differential resistor when  $\overline{\text{CS}}$  is low.

**SCKI**<sup>+</sup>/**SCKI**<sup>-</sup> (**Pins 28/29**): LVDS Positive and Negative Serial Clock Input. Differentially drive SCKI<sup>+</sup>/SCKI<sup>-</sup> with the serial I/O clock. SCKI<sup>+</sup>/SCKI<sup>-</sup> rising and falling edges latch serial data in on SDI<sup>+</sup>/SDI<sup>-</sup> and clock serial data out on SDO<sup>+</sup>/SDO<sup>-</sup>. Idle SCKI<sup>+</sup>/SCKI<sup>-</sup> low, including when transitioning  $\overline{\text{CS}}$ . The SCKI<sup>+</sup>/SCKI<sup>-</sup> input pair is internally terminated with a  $100\Omega$  differential resistor when  $\overline{\text{CS}}$  is low.

$0V_{DD}$  (Pin 31): I/O Interface Power Supply. In LVDS I/O mode, the range of  $0V_{DD}$  is 2.375V to 5.25V. Bypass  $0V_{DD}$  to GND (Pin 30) close to the pin with a 0.1µF ceramic capacitor.

**SCKO**+/**SCKO**- (**Pins 32/33**): LVDS Positive and Negative Serial Clock Output. SCKO+/SCKO- outputs a copy of the input serial I/O clock received on SCKI+/SCKI-, skew-matched with the serial output data stream on SDO+/SDO-. Use the rising and falling edges of SCKO+/SCKO- to capture SDO+/SDO- data at the receiver (FPGA). The SCKO+/SCKO- output pair must be differentially terminated with a  $100\Omega$  resistor at the receiver (FPGA).

**SDO**<sup>+</sup>/**SDO**<sup>-</sup> (Pins 34/35): LVDS Positive and Negative Serial Data Output. The most recent conversion result along with channel configuration information is clocked out onto SDO<sup>+</sup>/SDO<sup>-</sup> on both rising and falling edges of SCKI<sup>+</sup>/SCKI<sup>-</sup>, beginning with channel 0. The SDO<sup>+</sup>/SDO<sup>-</sup> output pair must be differentially terminated with a  $100\Omega$  resistor at the receiver (FPGA).

**SDI (Pin 37):** CMOS Serial Data. In LVDS I/O mode, this pin is Hi-Z.

$\overline{\text{CS}}$  (Pin 39): Chip Select Input. The serial data I/O bus is enabled when  $\overline{\text{CS}}$  is low, and is disabled and Hi-Z when  $\overline{\text{CS}}$  is high.  $\overline{\text{CS}}$  also gates the external shift clock, SCKI<sup>+</sup>/SCKI<sup>-</sup>. The internal 100Ω differential termination resistors on the SCKI<sup>+</sup>/SCKI<sup>-</sup> and SDI<sup>+</sup>/SDI<sup>-</sup> input pairs are disabled when  $\overline{\text{CS}}$  is high. Logic levels are determined by OV<sub>DD</sub>.

## **CONFIGURATION TABLES**

Table 1a. SoftSpan Configuration Table. Use This Table with Table 1b to Choose Independent Binary SoftSpan Codes SS[2:0] for Each Channel Based on Desired Analog Input Range. Combine SoftSpan Codes to Form 12-Bit SoftSpan Configuration Word S[11:0]. Use Serial Interface to Write SoftSpan Configuration Word to LTC2357-18, as shown in Figure 18

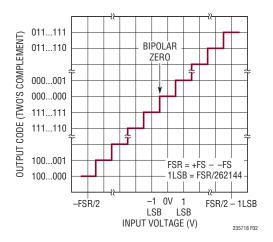

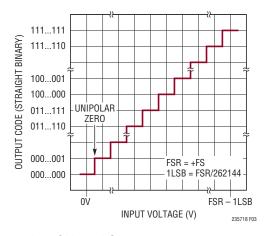

| BINARY SoftSpan CODE<br>SS[2:0] | ANALOG INPUT RANGE                     | FULL SCALE RANGE                 | BINARY FORMAT OF CONVERSION RESULT |

|---------------------------------|----------------------------------------|----------------------------------|------------------------------------|

| 111                             | ±2.5 • V <sub>REFBUF</sub>             | 5 • V <sub>REFBUF</sub>          | Two's Complement                   |

| 110                             | ±2.5 • V <sub>REFBUF</sub> /1.024      | 5 • V <sub>REFBUF</sub> /1.024   | Two's Complement                   |

| 101                             | 0V to 2.5 • V <sub>REFBUF</sub>        | 2.5 • V <sub>REFBUF</sub>        | Straight Binary                    |

| 100                             | 0V to 2.5 • V <sub>REFBUF</sub> /1.024 | 2.5 • V <sub>REFBUF</sub> /1.024 | Straight Binary                    |

| 011                             | ±1.25 • V <sub>REFBUF</sub>            | 2.5 • V <sub>REFBUF</sub>        | Two's Complement                   |

| 010                             | ±1.25 • V <sub>REFBUF</sub> /1.024     | 2.5 • V <sub>REFBUF</sub> /1.024 | Two's Complement                   |

| 001                             | 0V to 1.25 • V <sub>REFBUF</sub>       | 1.25 • V <sub>REFBUF</sub>       | Straight Binary                    |

| 000                             | Channel Disabled                       | Channel Disabled                 | All Zeros                          |

Table 1b. Reference Configuration Table. The LTC2357-18 Supports Three Reference Configurations. Analog Input Range Scales with the Converter Master Reference Voltage, V<sub>REFBUF</sub>

| REFERENCE CONFIGURATION                    | V <sub>REFIN</sub>   | V <sub>REFBUF</sub> | BINARY SoftSpan CODE<br>SS[2:0] | ANALOG INPUT RANGE |

|--------------------------------------------|----------------------|---------------------|---------------------------------|--------------------|

| Internal Reference with<br>Internal Buffer | 2.048V               | 4.096V              | 111                             | ±10.24V            |

|                                            |                      |                     | 110                             | ±10V               |

|                                            |                      |                     | 101                             | 0V to 10.24V       |

|                                            |                      |                     | 100                             | 0V to 10V          |

|                                            |                      |                     | 011                             | ±5.12V             |