# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### **General Description**

The MAX15112 high-efficiency, current-mode step-down regulator with integrated power switches operates from 2.7V to 5.5V and delivers up to 12A of output current in a small 2mm x 3mm package. The MAX15112 offers excellent efficiency with skip mode capability at light-load conditions, yet provides unmatched efficiency under heavy load conditions. The combination of small size and high efficiency makes this device suitable for both portable and nonportable applications.

The MAX15112 utilizes a current-mode control architecture with a high-gain transconductance error amplifier, which allows a simple compensation scheme and enables a cycle-by-cycle current limit with fast response to line and load transients. A factory-trimmed switching frequency of 1MHz (PWM operation) allows for a compact, all-ceramic capacitor design.

Integrated switches with low on-resistance ensure high efficiency at heavy loads while minimizing critical inductances. The MAX15112's simple layout and footprint assure first-pass success in new designs.

Other features of the MAX15112 include a capacitorprogrammable soft-start to reduce inrush current, safe startup into a prebiased output, an enable input, and a power-good output for power sequencing.

The regulator is available in a 24-bump (4 x 6), 2.10mm x 3.05mm WLP package, and is fully specified over the  $-40^{\circ}$ C to  $+85^{\circ}$ C extended temperature range.

### Features

- Continuous 12A Output Current

- ♦ ±1% Feedback Accuracy Over Load, Line, and Temperature

- ♦ Operates from 2.7V to 5.5V Supply

- Input Undervoltage Lockout

- ♦ Adjustable Output Range from 0.6V Up to 0.94 x VIN

- Programmable Soft-Start

- Factory-Trimmed 1MHz Switching Frequency

- Stable with Low-ESR Ceramic Output Capacitors

- ♦ Safe-Startup into a Prebiased Output

- External Reference Input

- Selectable Skip Mode Option for Improved Efficiency at Light Loads

- Enable Input/PGOOD Output Allows Sequencing

- Remote Ground Sense for Improved Accuracy

- Thermal and Overcurrent Protection

- Tiny 2.10mm x 3.05mm, 24-Bump WLP Package

### **Applications**

| Notebooks                 | DDR Memory    |

|---------------------------|---------------|

| Servers                   | Base Stations |

| Distributed Power Systems |               |

Ordering Information appears at end of data sheet.

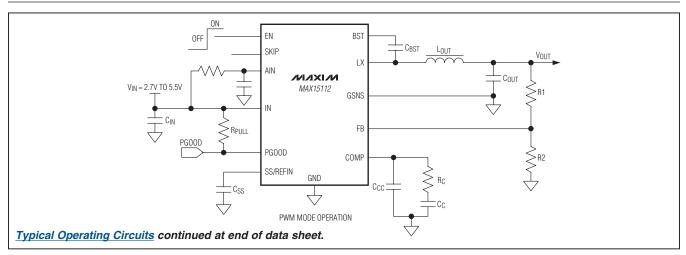

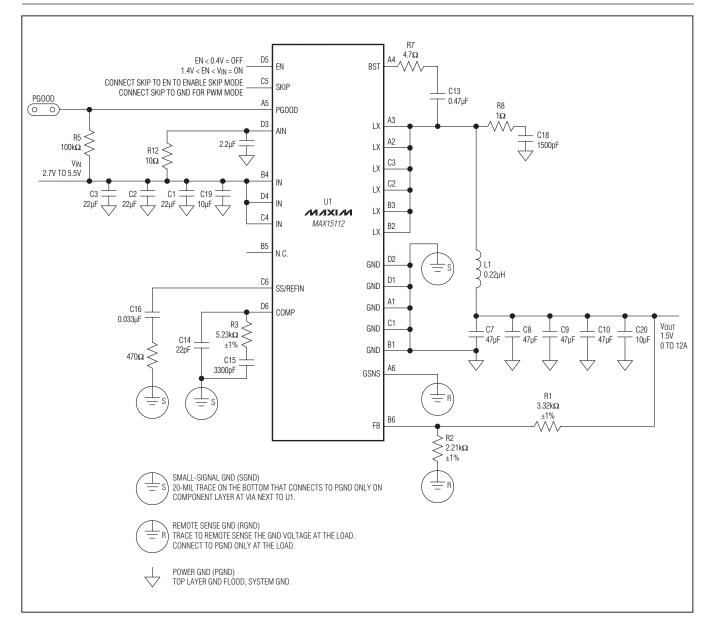

### **Typical Operating Circuits**

For related parts and recommended products to use with this part, refer to: www.maxim-ic.com/MAX15112.related

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### **ABSOLUTE MAXIMUM RATINGS**

| IN, PGOOD to GND                        | 0.3V to +6V                      | LX Continuous Current (Note 1)±20A                            |

|-----------------------------------------|----------------------------------|---------------------------------------------------------------|

| EN, COMP, FB, SS/REFIN, GSNS, SKIP,     |                                  | Output Short-Circuit Duration                                 |

| LX to GND                               | 0.3V to (V <sub>IN</sub> + 0.3V) | Continuous Power Dissipation                                  |

| LX to GND (for 10ns)                    | 2V to (V <sub>IN</sub> + 2V)     | WLP (derate 53.85mW/°C above +70°C)2.15W                      |

| LX to GND (for 50ns)                    | 1V to (V <sub>IN</sub> + 1V)     | Operating Temperature Range40°C to +85°C                      |

| BST to LX.                              | -0.3V to +6V                     | Junction Temperature (Note 2)+110°C                           |

| BST to GND                              | 0.3V to +12V                     | Storage Temperature Range65°C to +150°C                       |

| BST to IN                               | 0.3V to +6V                      | Bump Reflow Temperature (Note 3)+260°C                        |

| Note 1: LX has internal clamp diodes to | GND and IN. Application          | s that forward bias these diodes must take care not to exceed |

**Note 1:** LX has internal clamp diodes to GND and IN. Applications that forward bias these diodes must take care not to exceed the IC's package power dissipation limits.

Note 2: Limit the junction temperature to +110°C for continuous operation at maximum output current.

**Note 3:** The WLP package is constructed using a unique set of package techniques that impose a limit on the thermal profile the device can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and convection reflow. Preheating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### PACKAGE THERMAL CHARACTERISTICS (Note 4)

WLP

Note 4: Package thermal resistances were obtained using the MAX15112 evaluation board.

### DC ELECTRICAL CHARACTERISTICS

$(V_{IN} = 5V, \text{ see the } Typical Operating Circuits, T_A = -40^{\circ}C \text{ to } +85^{\circ}C.$  Typical values are at  $T_A = +25^{\circ}C, \text{ unless otherwise noted.})$  (Note 5)

| PARAMETER                                       | SYMBOL             | CONDITIONS                                       | MIN   | ТҮР   | MAX   | UNITS |

|-------------------------------------------------|--------------------|--------------------------------------------------|-------|-------|-------|-------|

| IN Voltage Range                                | V <sub>IN</sub>    |                                                  | 2.7   |       | 5.5   | V     |

| IN Supply Current                               | I <sub>IN</sub>    | $V_{EN} = V_{IN}, V_{FB} = 0.65V$ , no switching |       | 4.6   | 7     | mA    |

| IN Shutdown Current                             | I <sub>SHDN</sub>  | V <sub>EN</sub> = 0V                             |       | 0.01  | 3     | μA    |

| IN Undervoltage Lockout<br>Threshold            | V <sub>UVLO</sub>  | V <sub>IN</sub> rising, LX starts switching      |       | 2.6   | 2.68  | V     |

| IN Undervoltage Lockout<br>Threshold Hysteresis |                    | V <sub>IN</sub> falling, LX stops switching      |       | 200   |       | mV    |

| ERROR AMPLIFIER                                 | •                  |                                                  |       |       |       |       |

| Transconductance                                | Ям                 |                                                  |       | 1.1   |       | mS    |

| Voltage Gain                                    | A <sub>VEA</sub>   |                                                  |       | 90    |       | dB    |

| FB Setpoint Voltage                             | V <sub>FB</sub>    | Over line, load, and temperature                 | 0.594 | 0.600 | 0.606 | V     |

| FB Input Bias Current                           | I <sub>FB</sub>    | $V_{FB} = 0.6V$                                  | -500  |       | +500  | nA    |

| COMP to Current-Sense<br>Transconductance       | 9MC                |                                                  |       | 80    |       | A/V   |

| COMP Clamp Low Voltage                          |                    | $V_{FB} = 0.65V, V_{SS/REFIN} = 0.6V$            |       | 0.91  |       | V     |

| Slope Compensation Ramp<br>Amplitude            | V <sub>SLOPE</sub> |                                                  |       | 130   |       | mV    |

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = 5V, \text{see the } Typical Operating Circuits, T_A = -40^{\circ}C \text{ to } +85^{\circ}C. Typical values are at T_A = +25^{\circ}C, unless otherwise noted.) (Note 5)$

| PARAMETER                                                     | SYMBOL              | CONDITIONS                            | MIN | ТҮР  | MAX                      | UNITS           |

|---------------------------------------------------------------|---------------------|---------------------------------------|-----|------|--------------------------|-----------------|

| GROUND SENSE                                                  |                     |                                       | I   |      |                          |                 |

| GSNS Output Current                                           |                     | $V_{SS/REFIN} = 0.6V, V_{GSNS} = 0V$  |     | 52   |                          | μA              |

| POWER SWITCHES                                                |                     |                                       |     |      |                          |                 |

|                                                               |                     | High-side switch                      |     | 18   |                          |                 |

| Current-Limit Threshold                                       |                     | Low-side switch, sinking              |     | 18   |                          | A               |

|                                                               |                     | Low-side switch, sourcing             |     | 18   |                          |                 |

| LX Leakage Current                                            |                     | $V_{EN} = 0V$                         |     |      | 3                        | μΑ              |

| BST Leakage Current                                           |                     | $V_{EN} = 0V$                         |     |      | 3                        | μA              |

| BST On-Resistance                                             | R <sub>ON_BST</sub> | I <sub>BST</sub> = 50mA               |     | 0.63 |                          | Ω               |

| LX RMS Output Current                                         |                     |                                       | 12  |      |                          | A               |

| OSCILLATOR                                                    |                     |                                       |     |      |                          |                 |

| Switching Frequency                                           | f <sub>SW</sub>     |                                       | 850 | 1000 | 1150                     | kHz             |

| Maximum Duty Cycle                                            |                     | PWM mode                              |     | 94   |                          | %               |

| Maximum Duty Cycle                                            | D <sub>MAX</sub>    | Skip mode                             |     | 85   |                          | /0              |

| Minimum Controllable On-Time                                  | t <sub>ON</sub>     |                                       |     | 70   |                          | ns              |

| ENABLE FUNCTIONALITY                                          |                     |                                       |     |      |                          |                 |

| EN Input High Threshold                                       | VIH                 | V <sub>EN</sub> rising                |     |      | 1.4                      | V               |

| EN Input Low Threshold                                        | VIL                 | V <sub>EN</sub> falling               | 0.4 |      |                          | V               |

| EN Input Leakage Current                                      |                     |                                       | -1  |      | +1                       | μΑ              |

| SKIP FUNCTIONALITY (Note 6)                                   |                     |                                       |     |      |                          |                 |

| SKIP Input High Threshold                                     |                     | V <sub>SKIP</sub> rising              |     |      | 1.4                      | V               |

| SKIP Input Low Threshold                                      |                     | V <sub>SKIP</sub> falling             | 0.4 |      |                          | V               |

| SKIP Pulldown Resistor                                        |                     |                                       |     | 230  |                          | kΩ              |

| Minimum LX On-Current in Skip<br>Mode                         |                     |                                       |     | 3    |                          | A               |

| Zero-Crossing LX Threshold                                    |                     |                                       |     | 0.5  |                          | A               |

| SOFT-START AND PREBIAS FU                                     | NCTIONALI           | ГҮ                                    |     |      |                          |                 |

| Soft-Start Current                                            | I <sub>SS</sub>     | $V_{SS/REFIN} = 0.45V$ , sourcing     | 6.8 | 10   | 12.5                     | μA              |

| SS/REFIN Discharge Resistance                                 | R <sub>SS</sub>     | I <sub>SS/REFIN</sub> = 10mA, sinking |     | 7    |                          | Ω               |

| SS/REFIN Prebias Mode Stop<br>Voltage                         |                     | V <sub>SS/REFIN</sub> rising          |     | 0.58 |                          | V               |

| SS/REFIN External Reference<br>Input Range                    |                     |                                       |     |      | V <sub>IN</sub> -<br>2.5 | V               |

| HICCUP MODE                                                   |                     |                                       |     |      |                          |                 |

| Number of Consecutive Current-<br>Limit Events to Hiccup Mode | N <sub>HIC</sub>    |                                       |     | 8    |                          | Events          |

| Hiccup Mode Timeout                                           |                     |                                       |     | 1024 |                          | Clock<br>Cycles |

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### DC ELECTRICAL CHARACTERISTICS (continued)

$(V_{IN} = 5V)$ , see the <u>Typical Operating Circuits</u>,  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ . Typical values are at  $T_A = +25^{\circ}C$ , unless otherwise noted.) (Note 5)

| PARAMETER                   | SYMBOL             | CONDITIONS                                     | MIN   | ТҮР   | МАХ   | UNITS |

|-----------------------------|--------------------|------------------------------------------------|-------|-------|-------|-------|

| POWER-GOOD OUTPUT           |                    |                                                |       |       |       |       |

| PGOOD Threshold             |                    | V <sub>FB</sub> falling, PGOOD deasserts       | 0.514 | 0.529 | 0.542 | V     |

| PGOOD Threshold Hysteresis  |                    | V <sub>FB</sub> rising                         |       | 25    |       | mV    |

| PGOOD Output Voltage Low    | V <sub>PG_OL</sub> | I <sub>PGOOD</sub> = 5mA, V <sub>EN</sub> = 0V |       | 18    | 50    | mV    |

| PGOOD Leakage Current       | IPG_LK             | $V_{PGOOD} = 5.5V, V_{FB} = 0.65V$             |       |       | 1     | μA    |

| THERMAL SHUTDOWN            |                    |                                                |       |       |       |       |

| Thermal Shutdown Threshold  | T <sub>SHDN</sub>  | Die temperature rising                         |       | +150  |       | °C    |

| Thermal Shutdown Hysteresis |                    |                                                |       | 20    |       | °C    |

**Note 5:** All devices are 100% production tested at  $T_A = +25^{\circ}$ C. Limits over the operating temperature range are guaranteed by design. **Note 6:** Connect SKIP to EN for skip mode functionality. Leave SKIP unconnected or connect to GND for PWM mode functionality.

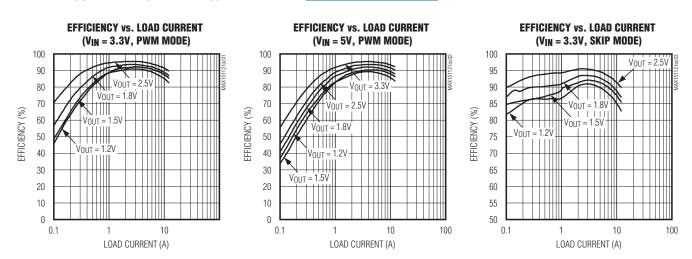

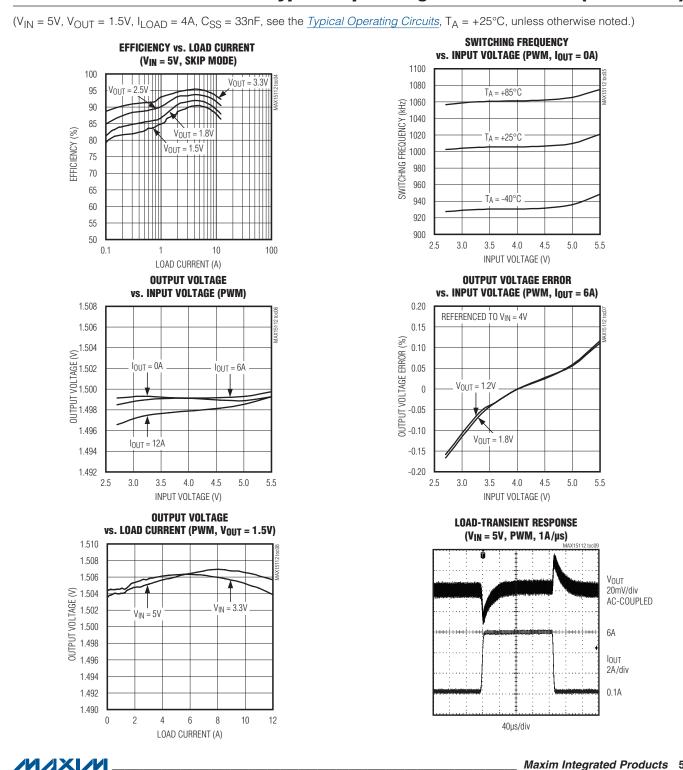

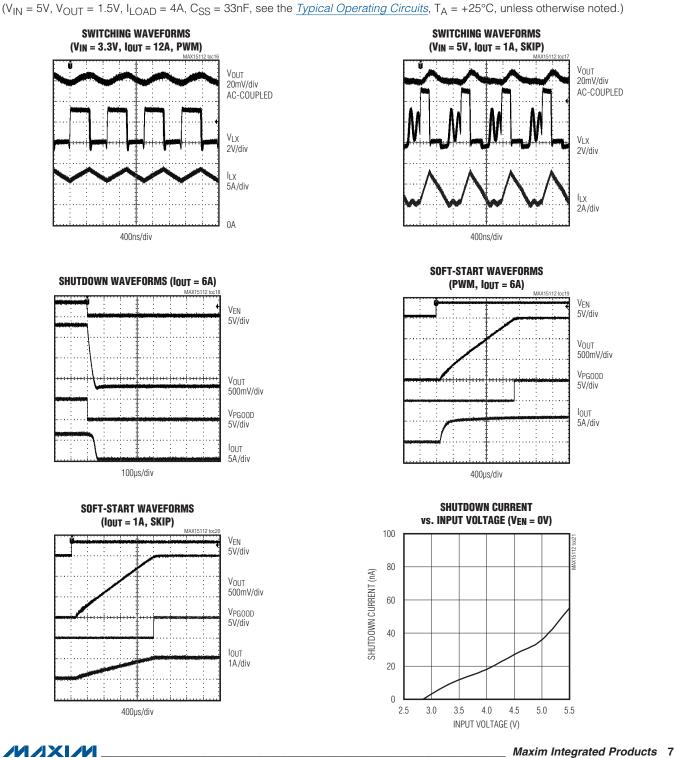

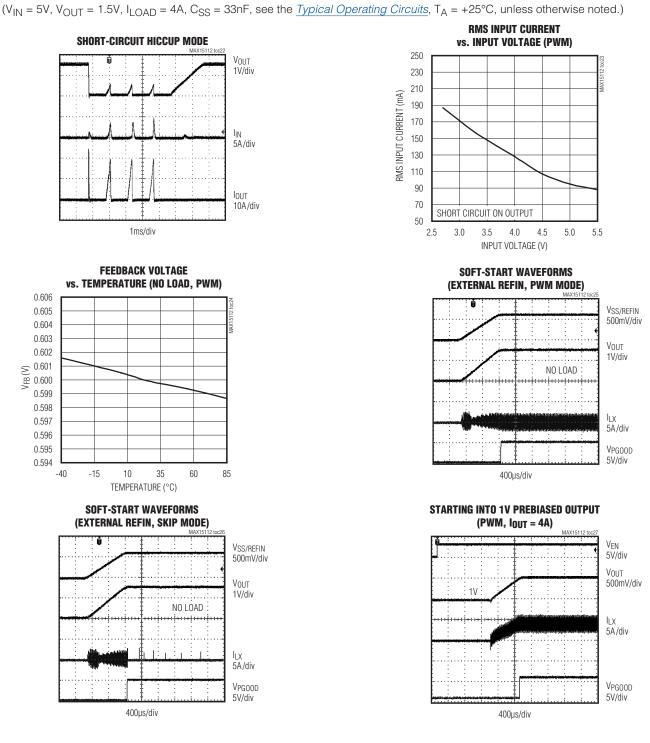

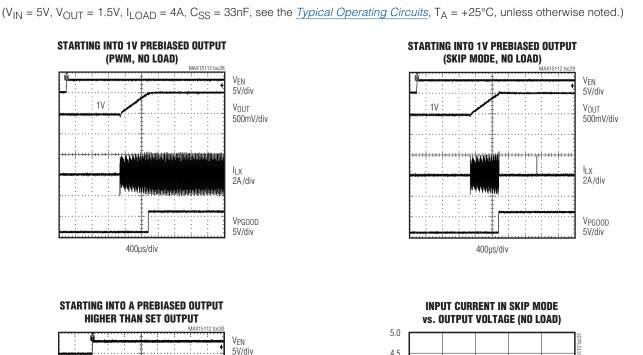

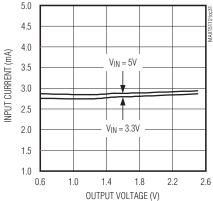

### **Typical Operating Characteristics**

(VIN = 5V, VOUT = 1.5V, ILOAD = 4A, CSS = 33nF, see the Typical Operating Circuits, TA = +25°C, unless otherwise noted.)

## **High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches**

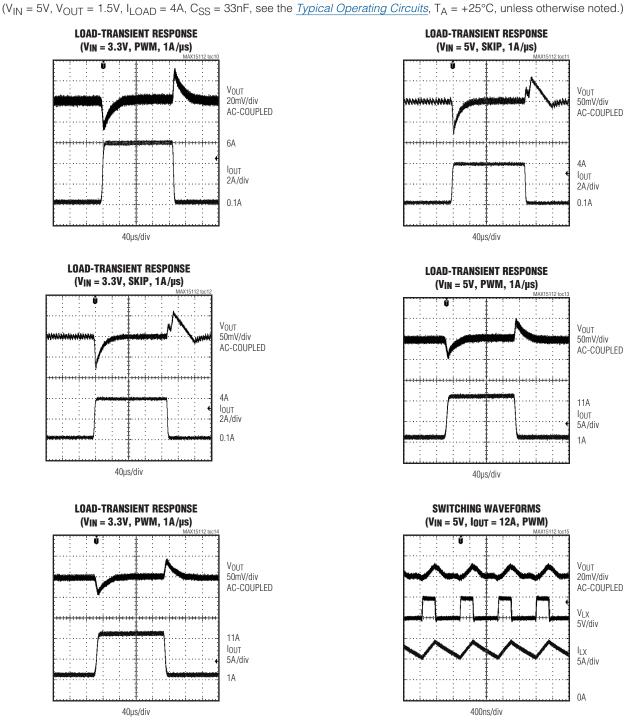

**Typical Operating Characteristics (continued)**

## **High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches**

### **Typical Operating Characteristics (continued)**

# **High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches**

### **Typical Operating Characteristics (continued)**

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

**Typical Operating Characteristics (continued)**

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

**Typical Operating Characteristics (continued)**

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### **Pin Configuration**

| TOP VIEW<br>(BUMP ON THE BOT | TOM)                             |                                  |                  | <b>XI///</b><br>15112 |               |                                                   |

|------------------------------|----------------------------------|----------------------------------|------------------|-----------------------|---------------|---------------------------------------------------|

|                              | + GND<br>(A1)                    | LX<br>(A2)                       | LX<br>(A3)       | BST<br>(A4)           | PG00D<br>(A5) | $\operatorname{GSNS}_{\left(\widehat{A6}\right)}$ |

|                              | $\frac{\text{GND}}{\text{(B1)}}$ | LX<br>(B2)                       | LX<br>(B3)       | IN<br>(B4)            | N.C.<br>(B5)  | FB<br>(B6)                                        |

|                              | $\frac{\text{GND}}{(01)}$        | LX<br>(C2)                       | LX<br>(03)       | (04)                  | SKIP<br>(C5)  | SS/REFIN                                          |

|                              | (D1)                             | $\frac{\text{GND}}{\text{(D2)}}$ | $(\widehat{D3})$ | (D4)                  | EN<br>(D5)    | COMP<br>(D6)                                      |

|                              |                                  |                                  | W                | LP                    |               |                                                   |

### **Pin Description**

| PIN                       | NAME     | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1, B1, C1,<br>D1, D2     | GND      | Ground Connection. GND is the source terminal of the internal low-side switch. Connect all GND bumps to a component-side PCB copper ground plane at a single point near the input bypass capacitor return terminal.                                                                                                                                                                       |

| A2, A3, B2,<br>B3, C2, C3 | LX       | Inductor Connection. Connect LX to the switching side of the inductor. LX is high impedance when the MAX15112 is in shutdown mode.                                                                                                                                                                                                                                                        |

| A4                        | BST      | Boost Input for the High-Side Switch Driver. Connect a capacitor from BST to LX.                                                                                                                                                                                                                                                                                                          |

| A5                        | PGOOD    | Power-Good Open-Drain Output. PGOOD asserts high when $V_{FB}$ is above 0.554V (typ) and deasserts when $V_{FB}$ falls below 0.529V (typ).                                                                                                                                                                                                                                                |

| A6                        | GSNS     | Remote Ground-Sense Input. Connect GSNS to the ground terminal of the load and to the bottom of the feedback resistors.                                                                                                                                                                                                                                                                   |

| B4, C4, D4                | IN       | Input Power Supply. Bypass IN to GND with at least two 22µF low-ESR ceramic capacitors with sufficient ripple current ratings.                                                                                                                                                                                                                                                            |

| B5                        | N.C      | No Connection. Do not connect.                                                                                                                                                                                                                                                                                                                                                            |

| B6                        | FB       | Feedback Input. Connect FB to the center tap of an external resistor divider from the output to the output capacitor return terminal to set the output voltage from 0.6V to $0.94 \times V_{IN}$ .                                                                                                                                                                                        |

| C5                        | SKIP     | Skip-Mode Selector Input. Connect SKIP to EN for skip-mode operation. Connect SKIP to GND or leave unconnected for continuous mode operation. Do not change the state of SKIP when EN is high.                                                                                                                                                                                            |

| C6                        | SS/REFIN | Soft-Start and External Voltage Reference Input. Connect a capacitor from SS/REFIN to GND to set the soft-start delay. See the <u>Setting the Soft-Start Time</u> section for more information. To use SS/REFIN as an external voltage reference, apply a voltage ranging from 0V to (V <sub>IN</sub> - 2.5V) to SS/REFIN to externally control the soft-start time and feedback voltage. |

| D3                        | AIN      | Filtered Input Voltage                                                                                                                                                                                                                                                                                                                                                                    |

| D5                        | EN       | Enable Input. Drive EN high to enable the MAX15112. Connect EN to IN for always-on operation.                                                                                                                                                                                                                                                                                             |

| D6                        | COMP     | Error Amplifier Output. Connect the compensation network from COMP to GND. See the<br><u>Compensation Design Guidelines</u> section for more information.                                                                                                                                                                                                                                 |

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

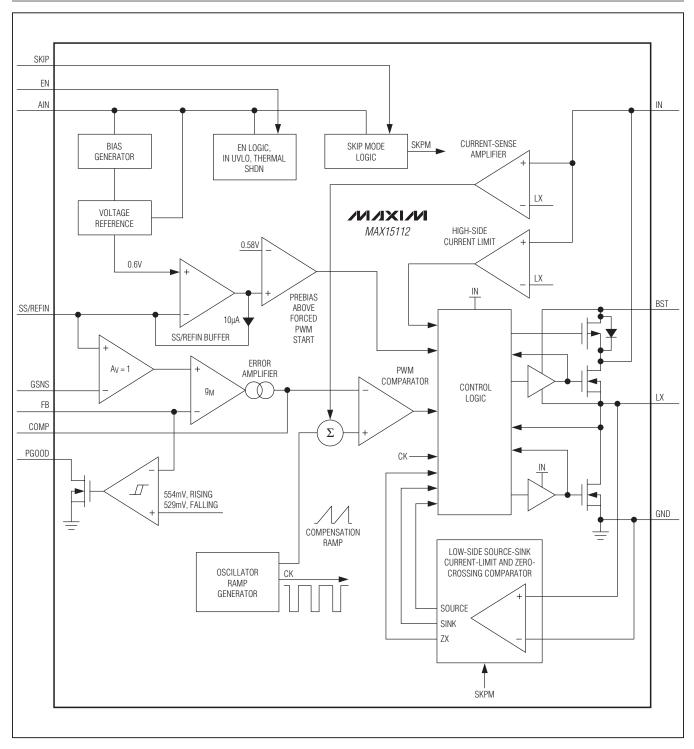

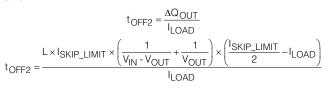

**Functional Diagram**

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### **Detailed Description**

The MAX15112 high-efficiency, current-mode switching regulator delivers up to 12A of output current. The regulator provides output voltages from 0.6V up to  $0.94 \times V_{IN}$  from 2.7V to 5.5V input supplies, making the device ideal for on-board point-of-load applications.

The MAX15112 delivers current-mode control architecture using a high-gain transconductance error amplifier. The current-mode control architecture facilitates easy compensation design and ensures cycle-by-cycle current limit with fast response to line and load transients.

The regulator features a 1MHz fixed switching frequency, allowing for all-ceramic capacitor designs and fast transient responses. The high operating frequency minimizes the size of external components.

The regulator offers a selectable skip mode functionality to reduce current consumption and achieve a higher efficiency at light output loads. Integrated switches ensure high efficiency at heavy loads while minimizing critical inductances.

The MAX15112 features PWM current-mode control, allowing for an all-ceramic capacitor solution. The regulator offers capacitor-programmable soft-start to reduce input inrush current. The device safely starts up into a prebiased output. The MAX15112 includes an enable input and open-drain PGOOD output for sequencing with other devices.

#### **Controller Function—PWM Logic**

The controller logic block is the central processor that determines the duty cycle of the high-side MOSFET under different line, load, and temperature conditions. Under normal operation, where the current-limit and temperature protection are not triggered, the controller logic block takes the output from the PWM comparator and generates the driver signals for both high-side and low-side MOSFETs. The control logic block controls the break-before-make logic and all the necessary timing.

The high-side MOSFET turns on at the beginning of the oscillator cycle and turns off when the COMP voltage crosses the internal current-mode ramp waveform. The internal ramp is the sum of the compensation ramp and the current-mode ramp derived from the inductor current (current-sense block). The high-side MOSFET also turns off if either the maximum duty cycle (94%, typ) or the current limit is reached. The low-side MOSFET turns on for the remainder of the oscillation cycle.

#### **Starting into a Prebiased Output**

The MAX15112 can soft-start into a prebiased output without discharging the output capacitor. In safe prebiased startup, both low-side and high-side MOSFETs remain off to avoid discharging the prebiased output. PWM operation starts when the voltage on SS/REFIN crosses the voltage on FB.

The MAX15112 can start into a prebiased voltage higher than the nominal set point without abruptly discharging the output. Forced PWM operation starts when the SS/REFIN voltage reaches 0.58V (typ), forcing the converter to start. The low-side current limit is increased over 350µs to the maximum from the first LX pulse. When the low-side sink current-limit threshold of 18A is reached, the low-side switch turns off before the end of the clock period and the high-side switch turns on until one of the following conditions is satisfied:

- High-side source current hits the reduced high-side current limit (18A, typ); in this case, the high-side switch is turned off for the remaining time of the clock period.

- The clock period ends.

Reduced high-side current limit is activated to recirculate the current into the high-side power switch rather than into the internal high-side body diode.

Low-side sink current limit is provided to protect the low-side switch from excessive reverse current during prebiased operation.

#### Enable Input and Power-Good (PGOOD) Output

The MAX15112 features independent enable control and a power-good signal that allows for flexible power sequencing. Drive the enable input (EN) high to enable the regulator, or connect EN to IN for always-on operation.

Power good (PGOOD) is an open-drain output that asserts when VFB is above 554mV (typ) and deasserts low if VFB is below 529mV (typ).

#### **Programmable Soft-Start (SS/REFIN)**

The MAX15112 utilizes a soft-start feature to slowly ramp up the regulated output voltage to reduce input inrush current during startup. Connect a capacitor from SS/REFIN to GND to set the startup time (see the <u>Setting</u> the Soft-Start Time section for capacitor selection details).

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

#### **Error Amplifier**

A high-gain transconductance error amplifier provides accuracy for the voltage-feedback loop regulation. Connect the necessary compensation network between COMP and GND (see the <u>Compensation Design</u> <u>Guidelines</u> section). The error-amplifier transconductance is 1.1mS (typ). COMP clamp low is set to 0.91V (typ), just below the slope ramp compensation valley, helping COMP to rapidly return to the correct set point during load and line transients.

#### **Ground-Sense Amplifier**

The MAX15112 features a ground-sense amplifier to prevent output voltage droop under heavy load conditions. Connect GSNS to the negative terminal of the load output capacitor to properly Kelvin-sense the output ground. Route the GSNS trace away from the switching nodes.

#### **PWM Comparator**

The PWM comparator compares the COMP voltage to the current-derived ramp waveform (COMP voltage to LX current transconductance value is 80A/V, typ). To avoid instability due to subharmonic oscillations when the duty cycle is around 50% or higher, a slope compensation ramp is added to the current-derived ramp waveform. The compensation ramp slope is designed to ensure stable operation at any duty cycle up to 94%.

**Overcurrent Protection and Hiccup Mode** When the converter output is shorted or the device is overloaded, each high-side MOSFET current-limit event turns off the high-side MOSFET and turns on the low-side MOSFET. On each current-limit event (either high-side or low-side) a 3-bit counter is incremented. The counter is reset after three consecutive switching cycles that do not reach the current limit. If the current-limit condition persists, the counter fills up reaching eight events. The control logic then keeps the low-side MOSFET turned on until the inductor current is fully discharged to avoid high currents circulating through the low-side body diode. The control logic turns off both high-side and low-side MOSFETs and waits for the hiccup period (1024 clock cycles, typ) before attempting a new soft-start sequence. The hiccup mode is also enabled during soft-start time.

#### **Thermal Shutdown Protection**

The MAX15112 contains an internal thermal sensor that limits the total power dissipation to protect the device in the event of an extended thermal fault condition. When the die temperature exceeds +150°C (typ), the thermal sensor shuts down the device, turning off the DC-DC converter to allow the die to cool. After the die temperature falls by 20°C (typ), the device restarts.

#### **Skip Mode Operation**

The MAX15112 features selectable skip mode operation when SKIP is connected to EN. When in skip mode, the LX output becomes high impedance when the inductor current falls below 0.5A (typ). The inductor current does not become negative. If during a clock cycle the inductor current falls below the 0.5A threshold (during off-time), the low-side turns off. At the next clock cycle, if the output voltage is above set point, the PWM logic keeps both high-side and low-side MOSFETs off. If instead the output voltage is below the set point, the PWM logic drives the high-side on until a reduced current limit threshold (3A, typ) is reached. In this way the system can skip cycles, reducing the frequency of operation, and switches only as needed to service load at the cost of an increase in output voltage ripple (see the Skip Mode Frequency and Output Ripple section). In skip mode, power dissipation is reduced and efficiency is improved at light loads because power MOSFETs do not switch at every clock cycle.

The MAX15112 automatically enters continuous mode regardless of the state of SKIP when the load current increases beyond the skip mode current limit.

Do not change the state of SKIP when EN is high.

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### **Applications Information**

#### Setting the Output Voltage

The MAX15112 output voltage is adjustable from 0.6V up to 94% of V<sub>IN</sub> by connecting FB to the center tap of a resistor-divider between the output and GND (see the *Typical Operating Circuits*). Choose R1 and R2 values so that the DC errors due to the FB input bias current ( $\pm$ 500nA) do not affect the output voltage accuracy. With lower value resistors the DC error is reduced, but the amount of power consumed in the resistor-divider increases. R2 values between 1k $\Omega$  and 20k $\Omega$  are acceptable (see Table 1 for typical values). Once R2 is chosen, calculate R1 using:

$$R1=R2 \times \left[ \left( V_{OUT} / V_{FB} \right) - 1 \right]$$

where the feedback threshold voltage  $V_{FB} = 0.6V$  (typ). When regulating for an output of 0.6V in skip mode, short FB to OUT and keep R2 connected from FB to GND.

#### **Inductor Selection**

A high-valued inductor results in reduced inductor-ripple current, leading to a reduced output-ripple voltage. However, a high-valued inductor results in either a larger physical size or a high series resistance (DCR) and a lower saturation current rating. Typically, choose an inductor value to produce a current ripple,  $\Delta IL$ , equal to 30% of load current. Choose the inductor with the following formula:

$$L = \frac{V_{OUT}}{f_{SW} \times LIR \times I_{LOAD}} \times \left(1 - \frac{V_{OUT}}{V_{IN}}\right)$$

where f<sub>SW</sub> is the fixed 1MHz switching frequency, and LIR is the desired inductor current ratio (typically 0.3). In addition, the peak inductor current, IL\_PK, must always be below the 18A high-side current-limit and the inductor saturation current rating, IL\_SAT. Ensure that the following relationship is satisfied:

$$I_{L_{PK}} = I_{LOAD} + \frac{1}{2} \Delta I_{L(P-P)} < \min(18A, I_{L_{SAT}})$$

where:

$$\Delta I_{L(P-P)} = \frac{\left(V_{IN} - V_{OUT}\right) \times \frac{V_{OUT}}{V_{IN}}}{L \times f_{SW}}$$

#### Input Capacitor Selection

For a step-down converter, the input capacitor, CIN, helps to keep the DC input voltage steady, in spite of discontinuous input AC current. Use low-ESR capacitors to minimize the voltage ripple due to ESR. Size CIN using the following formula:

$$C_{IN} = \frac{I_{LOAD}}{f_{SW} \times \Delta V_{IN} \text{ RIPPLE}} \times \frac{V_{OUT}}{V_{IN}}$$

where  $\Delta V_{IN\_RIPPLE}$  is the maximum-allowed input-ripple voltage across the input capacitors and is recommended to be less than 2% of the minimum input voltage, fSW is the switching frequency (1MHz), and I<sub>LOAD</sub> is the output load. The impedance of the input capacitor at the switching frequency should be less than that of the input source so high-frequency switching currents do not pass through the input source, but are instead shunted through the input capacitor.

Ensure that the input capacitor can accommodate the input-ripple current requirement imposed by the switching currents. The RMS input-ripple current is given by:

$$I_{RMS} = \left[\frac{\left[V_{OUT} \times (V_{IN} - V_{OUT})\right]^{1/2}}{V_{IN}}\right] \times I_{LOAD}$$

where IRMS is the input RMS ripple current.

Use multiple capacitors in parallel to meet the RMS current rating requirement.

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

#### **Output Capacitor Selection**

The key selection parameters for the output capacitor are capacitance, ESR, ESL, and voltage-rating requirements. These affect the overall stability, output-ripple voltage, and transient response of the DC-DC converter. The output ripple occurs due to variations in the charge stored in the output capacitor, the voltage drop due to the capacitor's ESR, and the voltage drop due to the capacitor's ESL. Estimate the output-voltage ripple due to the output capacitance, ESR, and ESL as follows:

$$V_{RIPPLE} = V_{RIPPLE(C)} + V_{RIPPLE(ESR)} + V_{RIPPLE(ESL)}$$

where the output ripple due to output capacitance, ESR, and ESL is:

$$V_{\text{RIPPLE}(\text{C})} = \frac{\Delta I_{\text{P}-\text{P}}}{8 \times C_{\text{OUT}} \times f_{\text{SW}}}$$

$$V_{\text{RIPPLE}(\text{ESR})} = \Delta I_{\text{P}-\text{P}} \times \text{ESR}$$

and  $\mathsf{VRIPPLE}(\mathsf{ESL})$  can be approximated as an inductive divider from LX to GND:

$$V_{\text{RIPPLE (ESL)}} = V_{LX} \times \frac{\text{ESL}}{L} = V_{IN} \times \frac{\text{ESL}}{L}$$

where  $V_{LX}$  swings from  $V_{IN}$  to GND.

The peak-to-peak inductor current ( $\Delta IP-P$ ) is:

$$\Delta I_{P-P} = \frac{\left(V_{IN} - V_{OUT}\right) \times \left(\frac{V_{OUT}}{V_{IN}}\right)}{L \times f_{SW}}$$

When using ceramic capacitors, which generally have low-ESR,  $\Delta V_{RIPPLE(C)}$  dominates. When using electrolytic capacitors,  $\Delta V_{RIPPLE(ESR)}$  dominates. Use ceramic capacitors for low ESR and low ESL at the switching frequency of the converter. The ripple voltage due to ESL is negligible when using ceramic capacitors.

As a general rule, a smaller inductor-ripple current results in less output-ripple voltage. Since inductor-ripple current depends on the inductor value and input voltage, the output-ripple voltage decreases with larger inductance and increases with higher input voltages. However, the inductor-ripple current also impacts transient-response performance, especially at low VIN to VOUT differentials. Low inductor values allow the inductor current to slew faster, replenishing charge removed from the output filter capacitors by a sudden load step. Load-transient response also depends on the selected output capacitance. During a load transient, the output instantly changes by ESR x  $\Delta I_{LOAD}$ . Before the controller can respond, the output deviates further, depending on the inductor and output capacitor values. After a short time, the controller responds by regulating the output voltage back to the predetermined value.

Use higher  $C_{OUT}$  values for applications that require light-load operation or transition between heavy load and light load, triggering skip mode, causing output undershooting or overshooting. When applying the load, limit the output undershooting by sizing  $C_{OUT}$  according to the following formula:

$$C_{OUT} = \frac{\Delta I_{LOAD}}{3f_{CO} \times \Delta V_{OUT}}$$

where  $\Delta I_{LOAD}$  is the total load change, f<sub>CO</sub> is the unitygain bandwidth (or zero-crossing frequency), and  $\Delta V_{OUT}$ is the desired output undershooting. When removing the load and entering skip mode, the device cannot control output overshooting, since it has no sink current capability; see the <u>Skip Mode Frequency and Output Ripple</u> section to properly size C<sub>OUT</sub> under this circumstance.

A worst-case analysis in sizing the minimum output capacitance takes the total energy stored in the inductor into account, as well as the allowable sag/soar (undershoot/overshoot) voltage as follows:

$$C_{OUT(MIN)} = \frac{L \times \left(I^2_{OUT(MAX)} - I^2_{OUT(MIN)}\right)}{\left(V_{FIN} + V_{SOAR}\right)^2 - V^2_{INIT}}, \text{voltage soar (overshoot)}$$

$$C_{OUT(MIN)} = \frac{L \times \left(l^2_{OUT(MAX)} - l^2_{OUT(MIN)}\right)}{V_{INIT}^2 - \left(V_{FIN} - V_{SAG}\right)^2}, \text{ voltage sag (undershoot)}$$

where IOUT(MAX) and IOUT(MIN) are the initial and final values of the load current during the worst-case load dump, VINIT is the initial voltage prior to the transient, VFIN is the steady-state voltage after the transient, VSOAR is the allowed voltage soar (overshoot) above VFIN, and VSAG is the allowable voltage sag below VFIN. The terms (VFIN + VSOAR) and (VFIN - VSAG) represent the maximum/minimum transient output voltage reached during the transient, respectively.

Use these equations for initial output-capacitor selection. Determine final values by testing a prototype or an evaluation circuit under the worst-case conditions.

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

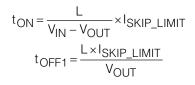

Skip Mode Frequency and Output Ripple

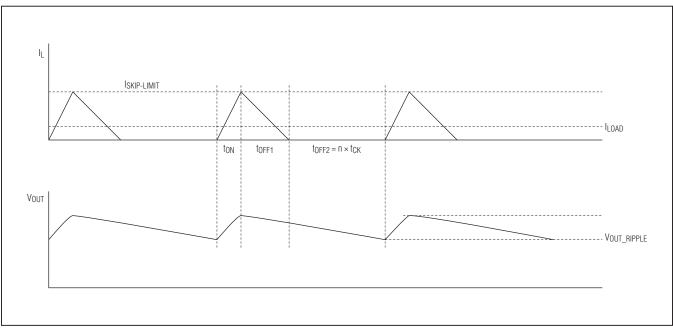

Enable skip mode in battery-powered systems for high efficiency at light loads. In skip mode the switching frequency ( $f_{SKIP}$ ), as illustrated in <u>Figure 1</u>, is calculated as follows:

$$f_{SKIP} = \frac{1}{t_{ON} + t_{OFF1} + t_{OFF2}}$$

where:

and:

Output ripple in skip mode is:

$$V_{OUT\_RIPPLE} = \left[\frac{L \times I_{SKIP\_LIMIT}}{C_{OUT} \times (V_{IN} - V_{OUT})} + R_{ESR\_COUT}\right]$$

$$\times \left(I_{SKIP\_LIMIT} - I_{LOAD}\right)$$

Figure 1. Skip Mode Waveform

## High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

#### **Compensation Design Guidelines**

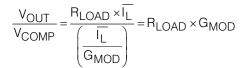

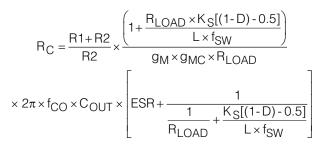

The MAX15112 uses a fixed-frequency, peak currentmode control scheme to provide easy compensation and fast transient response. The inductor peak current is monitored on a cycle-by-cycle basis and compared to the COMP voltage (output of the voltage error amplifier). The regulator's duty cycle is modulated based on the inductor's peak current value. This cycle-by-cycle control of the inductor current emulates a controlled current source. As a result, the inductor's pole frequency is shifted beyond the gain bandwidth of the regulator. System stability is provided with the addition of a simple series capacitor-resistor from COMP to GND. This pole-zero combination serves to tailor the desired response of the closed-loop system. The basic regulator loop consists of a power modulator (composed of the regulator's pulsewidth modulator, compensation ramp, control circuitry, MOSFETs, and inductor), the capacitive output filter and load, an output feedback divider, and a voltage-loop error amplifier with its associated compensation circuitry. See Figure 2 for a graphical representation. The power modulator's transfer function with respect to  $V_{COMP}$  is:

where  $\overline{I_L}$  is the average inductor current,  $G_{MOD}$  is the power modulator's transconductance, and  $R_{LOAD}$  is the equivalent load resistance value.

Figure 2. Peak Current-Mode Regulator Transfer Model

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

The peak current-mode controller's modulator gain is attenuated by the equivalent divider ratio of the load resistance and the current-loop gain.  $G_{MOD}$  becomes:

$$G_{MOD} = g_{MC} \times \frac{I}{1 + \frac{R_{LOAD}}{f_{SW} \times L} \times [K_S \times (1-D) - 0.5]}$$

where  $R_{LOAD} = V_{OUT}/I_{OUT(MAX)}$ , fSW is the switching frequency, L is the output inductance, D is the duty cycle ( $V_{OUT}/V_{IN}$ ), and KS is the slope compensation factor calculated as:

$$K_{S} = 1 + \frac{V_{SLOPE} \times f_{SW} \times L \times g_{MC}}{V_{IN} - V_{OUT}}$$

where  $V_{SLOPE} = 130 \text{mV}$  and  $g_{MC} = 80 \text{A/V}$ .

The power modulator's dominant pole is a function of the parallel effects of the load resistance and the current-loop gain's equivalent impedance. Assuming that ESR of the output capacitor is much smaller than the parallel combination of the load and the current loop,  $f_{PMOD}$  can be calculated as:

$$f_{PMOD} = \frac{1}{2\pi \times C_{OUT} \times R_{LOAD}} + \frac{[K_S \times (1-D) - 0.5]}{2\pi \times f_{SW} \times L \times C_{OUT}}$$

The power modulator zero is:

$$f_{ZMOD} = f_{ZESR} = \frac{1}{2\pi \times C_{OUT} \times ESR}$$

The total system transfer can be written as:

$$GAIN(s) = G_{FF}(s) \times G_{EA}(s) \times G_{MOD}(DC)$$

$$\times G_{FILTER}(s) \times G_{SAMPLING}(s)$$

where:

The dominant poles and zeros of the transfer loop gain are:

$$f_{P2} = \frac{g_M}{2\pi \times C_C \times 10^{AVEA(dB)/20}}$$

$$f_{P2} = \frac{1}{2\pi \times C_{OUT} \left(\frac{1}{R_{LOAD}} + \frac{K_S \times (1-D) - 0.5}{f_{SW} \times L}\right)^{-1}}$$

$$f_{P3} = \frac{f_{SW}}{2}$$

$$f_{Z1} = \frac{1}{2\pi \times C_C R_C}$$

$$f_{Z2} = \frac{1}{2\pi \times C_{OUT} ESR}$$

The order of pole occurrence is:

$$f_{P1} < f_{P2} < f_{Z1} < f_{CO} < f_{P3} < f_{Z2}$$

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

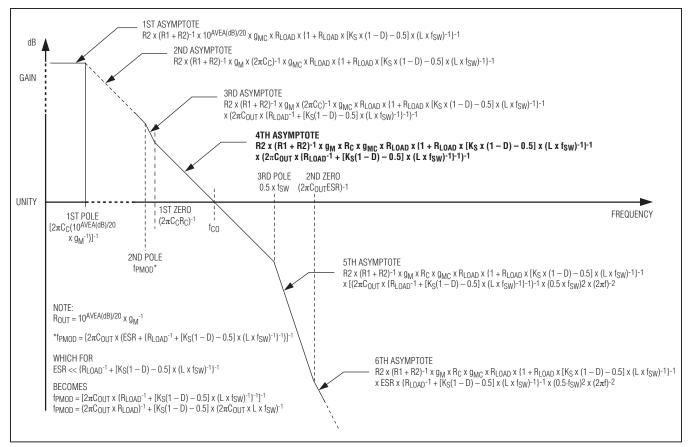

Figure 3 shows a graphical representation of the asymptotic system closed-loop response, including the dominant pole and zero locations.

The loop response's fourth asymptote (in bold, Figure 3) is the one of interest in establishing the desired crossover frequency (and determining the compensation component values). A lower crossover frequency provides for stable closed-loop operation at the expense of a slower load and line-transient response. Increasing the crossover frequency improves the transient response at the (potential) cost of system instability. A standard rule of thumb sets the crossover frequency  $\leq 1/5$  to 1/10 of the switching frequency.

# Closing the Loop: Designing the Compensation Circuitry

1) Select the desired crossover frequency. Choose  $f_{CO}$  equal to 1/10th of  $f_{SW},$  or  $f_{CO}\cong$  100kHz.

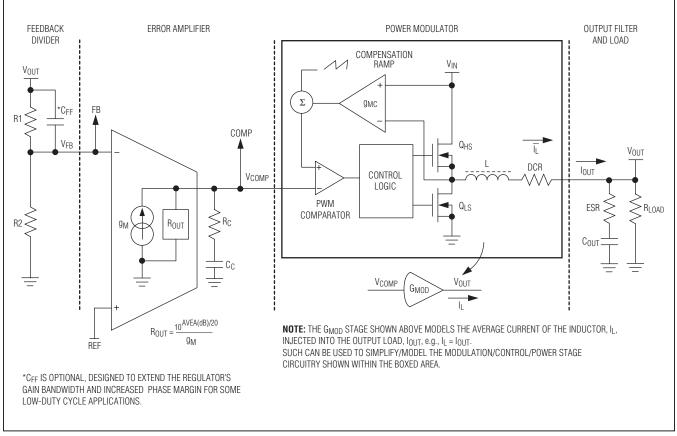

Select R<sub>C</sub> using the transfer-loop's fourth asymptote gain equal to unity (assuming f<sub>CO</sub> > f<sub>P1</sub>, f<sub>P2</sub>, and f<sub>Z1</sub>). R<sub>C</sub> becomes:

where Ks is calculated as:

$$K_{S} = 1 + \frac{V_{SLOPE} \times f_{SW} \times L \times g_{MC}}{V_{IN} - V_{OUT}}$$

and  $g_M = 1.1mS$ ,  $g_{MC} = 80A/V$ , and  $V_{SLOPE} = 130mV$ .

Figure 3. Asymptotic Loop Response of Peak Current-Mode Regulator

### High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

Select C<sub>C</sub>. C<sub>C</sub> is determined by selecting the desired first system zero, f<sub>Z1</sub>, based on the desired phase margin. Typically, setting f<sub>Z1</sub> below 1/5th of f<sub>CO</sub> provides sufficient phase margin.

$$C_{C} \ge \frac{5}{2\pi f_{CO} \times R_{C}}$$

Optionally, for low duty-cycle applications, the addition of a phase-leading capacitor ( $C_{FF}$  in Figure 2) helps mitigate the phase lag of the damped half-frequency double pole. Adding a second zero near to but below the desired crossover frequency increases both the closed-loop phase margin and the regulator's unity-gain bandwidth (crossover frequency). Select the capacitor as follows:

$$C_{FF} = \frac{1}{2\pi \times f_{CO} \times (R1 \parallel R2)}$$

Using C<sub>FF</sub>, the zero-pole order is adjusted as follows:

$$\begin{aligned} & f_{P1} < f_{P2} < f_{Z1} < 1 / \left[ 2\pi C_{FF} R_1 \right] \\ & < 1 / \left[ 2\pi C_{FF} \left( R_1 \| R2 \right) \right] < f_{P3} < f_{Z2} \end{aligned}$$

#### Setting the Soft-Start Time

The soft-start feature ramps up the output voltage slowly, reducing input inrush current during startup. Size the  $C_{SS}$  capacitor to achieve the desired soft-start time,  $t_{SS}$ , using:

$$C_{SS} = \frac{I_{SS} \times I_{SS}}{V_{FB}}$$

ISS, the soft-start current, is 10µA (typ) and V<sub>FB</sub> is the 0.6V (typ) output feedback voltage threshold. When using large  $C_{OUT}$  capacitance values, the high-side current limit can trigger during the soft-start period. To ensure the correct soft-start time, tSS, choose  $C_{SS}$  large enough to satisfy:

$$C_{SS} >> C_{OUT} \times \frac{V_{OUT} \times I_{SS}}{(18A - I_{LOAD}) \times V_{FB}}$$

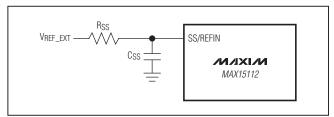

An external tracking reference with steady-state value between 0V and (V<sub>IN</sub> - 2.5V) can be applied to SS/REFIN. In this case, connect an RC network from the external tracking reference and SS/REFIN, as shown in Figure 4. The recommended value for RSS is approximately  $330\Omega$ . RSS is needed to ensure that, during hiccup period, SS/REFIN can be pulled down internally.

Figure 4. RC Network for External Reference at SS/REFIN

#### **Design Examples**

Table 1 provides values for various outputs based on the typical operating circuit.

#### Table 1. Suggested Component Values (see the <u>Typical Operating Circuits</u>)

| V <sub>OUT</sub> (V) | L (µH) | LIR (A/A)<br>(V <sub>IN</sub> = 3.3V) | LIR (A/A)<br>(V <sub>IN</sub> = 5V) | C15 (pF) | <b>R3 (k</b> Ω) | C14 (pF) | <b>R1 (k</b> Ω) | <b>R2 (k</b> Ω) |

|----------------------|--------|---------------------------------------|-------------------------------------|----------|-----------------|----------|-----------------|-----------------|

| 0.8                  | 0.18   | 0.28                                  | 0.31                                | 3300     | 5.23            | 22       | 0.74            | 2.21            |

| 1.2                  | 0.22   | 0.29                                  | 0.35                                | 3300     | 5.23            | 22       | 2.21            | 2.21            |

| 1.5                  | 0.22   | 0.31                                  | 0.40                                | 3300     | 5.23            | 22       | 3.32            | 2.21            |

| 1.8                  | 0.22   | 0.31                                  |                                     | 3300     | 5.23            | 22       | 4.42            | 2.21            |

| 1.8                  | 0.36   | —                                     | 0.27                                | 3300     | 5.23            | 22       | 4.42            | 2.21            |

| 2.5                  | 0.22   | 0.23                                  |                                     | 3300     | 5.23            | 22       | 6.98            | 2.21            |

| 2.5                  | 0.36   | —                                     | 0.29                                | 3300     | 5.23            | 22       | 6.98            | 2.21            |

| 3.3                  | 0.36   | —                                     | 0.26                                | 3300     | 5.23            | 22       | 9.95            | 2.21            |

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

#### **Power Dissipation**

The MAX15112 is available in a 24-bump WLP package and can dissipate up to 2.15W at +70°C board temperature. When the die temperature exceeds +150°C, the thermal shutdown protection is activated (see the *Thermal Shutdown Protection* section).

#### Layout Procedure

Careful PCB layout is critical to achieve clean and stable operation. It is highly recommended to duplicate the MAX15112 Evaluation Kit layout for optimum performance. The MAX15112 EV kit board has a small, quiet, ground-shape SGND on the back side below the IC. This ground is the return for the control circuitry, especially the return of the compensation components. This SGND is returned to the IC ground through vias close to the ground bumps of the IC. If deviation is necessary, follow these guidelines for good PCB layout:

- 1) Connect a single ground plane immediately adjacent to the GND bumps of the IC.

- 2) Place capacitors on IN and SS/REFIN as close as possible to the IC and the corresponding pad using direct traces.

- Keep the high-current paths as short and wide as possible. Keep the path of switching current short and minimize the loop area formed by LX, the output capacitors, and the input capacitors.

- 4) An electrolytic capacitor is strongly recommended for damping when there is significant distance between the input power supply and the MAX15112.

- 5) Connect IN, LX, and GND separately to a large copper area to help cool the IC to further improve efficiency.

- 6) Ensure all feedback connections are short and direct. Place the feedback resistors and compensation components as close as possible to the IC.

- Route high-speed switching nodes (such as LX and BST) away from sensitive analog areas (such as FB and COMP).

### **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE |

|--------------|----------------|-------------|

| MAX15112EWG+ | -40°C to +85°C | 24 WLP      |

+Denotes a lead(Pb)-free/RoHS-compliant package.

### **Chip Information**

PROCESS: BiCMOS

### **Package Information**

For the latest package outline information and land patterns (footprints), go to <u>www.maxim-ic.com/packages</u>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE                       | PACKAGE   | OUTLINE        | LAND                                               |

|-------------------------------|-----------|----------------|----------------------------------------------------|

| TYPE                          | CODE      | NO.            | PATTERN NO.                                        |

| 24 WLP<br>(2.1mm x<br>3.05mm) | W242A3Z+1 | <u>21-0538</u> | Refer to<br><u>Application</u><br><u>Note 1891</u> |

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

**Typical Operating Circuits (continued)**

# High-Efficiency, 12A, Current-Mode Synchronous Step-Down Regulator with Integrated Switches

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                                                                                                                                                                                                                 | PAGES<br>CHANGED    |

|--------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| 0                  | 6/11             | Initial release                                                                                                                                                                                                                             | —                   |

| 1                  | 9/11             | Updated the Features, Package Thermal Characteristics, Absolute<br>Maximum Ratings, DC Electrical Characteristics; Starting into a Prebiased<br>Output, Inductor Selection, Setting the Soft-Start Time, and Power<br>Dissipation sections. | 1–4, 12, 14, 20, 21 |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

#### Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_

Maxim is a registered trademark of Maxim Integrated Products, Inc.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.