# **GSM** Power Management System

# ADP3405

#### FEATURES

Handles all GSM Baseband Power Management Functions Four LDOS Optimized for Specific GSM Subsystems Charges Li-Mn Coin Cell for Real-Time Clock Charge Pump and Logic Level Translators for 3 V and 5 V GSM SIM Modules

Narrow Body 4.4 mm 28-Lead TSSOP Package

#### APPLICATIONS GSM/DCS/PCS Handsets TeleMatic Systems ICO/Iridium Terminals

#### **GENERAL DESCRIPTION**

The ADP3405 is a multifunction power management system IC optimized for GSM cell phones. The wide input voltage range of 3.0 V to 7.0 V makes the ADP3405 ideal for both single cell Li-Ion and three cell NiMH designs. The current consumption of the ADP3405 has been optimized for maximum battery life, featuring a ground current of only 150  $\mu$ A when the phone is in standby (digital LDO, and SIM card supply active). An undervoltage lock-out (UVLO) prevents the startup when there is not enough energy in the battery. All four integrated LDOs are optimized to power one of the critical sub-blocks of the phone. Their novel anyCAP<sup>®</sup> architecture requires only very small output capacitors for stability, and the LDOs are insensitive to the capacitors' equivalent series resistance (ESR). This makes them stable with any capacitor, including ceramic (MLCC) types for space-restricted applications.

A step-up converter is implemented to supply both the SIM module and the level translation circuitry to adapt logic signals for 3 V and 5 V SIM modules. Sophisticated controls are available for power-up during battery charging, keypad interface, and charging of an auxiliary backup battery for the real-time clock. These allow an easy interface between ADP3405, GSM processor, charger, and keypad. Furthermore, a reset circuit and a thermal shutdown function have been implemented to support reliable system design.

anyCAP is a registered trademark of Analog Devices, Inc.

#### **REV.0**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781/329-4700 World Wide Web Site:www.analog.com Fax: 781/326-8703 © Analog Devices, Inc., 2001

**ADP3405—SPECIFICATIONS**  $\begin{array}{l} (-20^{\circ}C \leq T_{A} \leq +85^{\circ}C, \ VBAT = 3 \ V \ to \ 7 \ V, \ C_{VBAT} = C_{SIMBAT} = C_{VSIM} = 10 \ \mu\text{F}, \ C_{VCC} = C_{VCCA} = 2.2 \ \mu\text{F}, \\ C_{VRTC} = 0.1 \ \mu\text{F}, \ C_{VTCX0} = 0.22 \ \mu\text{F}, \ C_{VCAP} = 0.1 \ \mu\text{F}, \ min. \ loads \ applied \ on \ all \ outputs, \ unless \ otherwise \ noted.) \end{array}$

# **ELECTRICAL CHARACTERISTICS<sup>1</sup>**

| Parameter                                                                                                                                | Symbol                                     | Conditions                                                                                                               | Min          | Тур                     | Max                | Unit                 |

|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------|-------------------------|--------------------|----------------------|

| SHUTDOWN SUPPLY CURRENT<br>VBAT = Low (UVLO Low)<br>VBAT = High (UVLO High)                                                              | $I_{BAT}$                                  | VBAT = 2.7 V<br>VBAT = 3.6 V, VRTC On                                                                                    |              | 3<br>12                 | 20<br>30           | μΑ<br>μΑ             |

| OPERATING GROUND CURRENT<br>VCC and VRTC On<br>VCC, VRTC and VSIM On<br>All LDOs and VSIM On<br>All LDOs and VSIM On                     | I <sub>GND</sub>                           | Minimum Loads, VBAT = 3.6 V<br>Minimum Loads, VBAT = 3.6 V<br>Minimum Loads, VBAT = 3.6 V<br>Maximum Loads, VBAT = 3.6 V |              | 100<br>150<br>260<br>15 | 140<br>240<br>400  | μA<br>μA<br>μA<br>mA |

| UVLO CHARACTERISTICS<br>UVLO On Threshold<br>UVLO Hysteresis                                                                             | VBAT <sub>UVLO</sub>                       |                                                                                                                          |              | 3.2<br>200              | 3.3                | V<br>mV              |

| INPUT CHARACTERISTICS<br>Input High Voltage<br>PWRONIN and ANALOGON<br>PWRONKEY<br>Input Low Voltage<br>PWRONIN and ANALOGON<br>PWRONKEY | V <sub>IH</sub><br>V <sub>IL</sub>         |                                                                                                                          | 2<br>0.7 × V | /BAT                    | 0.4<br>0.3 × VBAT  | V<br>V<br>V<br>V     |

| PWRONKEY INPUT PULL-UP<br>RESISTANCE TO VBAT                                                                                             |                                            |                                                                                                                          | 15           | 20                      | 25                 | kΩ                   |

| CHRON CHARACTERISTICS<br>CHRON Threshold<br>CHRON Hysteresis Resistance<br>CHRON Input Bias Current                                      | $V_{\rm T}$<br>$R_{\rm IN}$<br>$I_{\rm B}$ | 2.38 < CHRON < V <sub>T</sub><br>CHRON > V <sub>T</sub>                                                                  | 2.38<br>108  | 2.48<br>125             | 2.58<br>138<br>0.5 | V<br>kΩ<br>μA        |

| ROWX CHARACTERISTICS<br>ROWX Output Low Voltage<br>ROWX Output High Leakage<br>Current                                                   | V <sub>OL</sub><br>I <sub>IH</sub>         | PWRONKEY = Low<br>$I_{OL} = 200 \mu A$<br>PWRONKEY = High<br>V(ROWX) = 5 V                                               |              |                         | 0.4<br>1           | V<br>μA              |

| SHUTDOWN<br>Thermal Shutdown Threshold <sup>2</sup><br>Thermal Shutdown Hysteresis                                                       |                                            | Junction Temperature<br>Junction Temperature                                                                             |              | 160<br>35               |                    | °C<br>°C             |

| DIGITAL LDO (VCC)<br>Output Voltage<br>Line Regulation<br>Load Regulation                                                                | VCC<br>DVCC<br>DVCC                        | Line, Load, Temp<br>3 V < VBAT < 7 V, Min Load<br>50 μA < I <sub>LOAD</sub> < 100 mA,<br>VBAT = 3.6 V                    | 2.710        | 2.765<br>2<br>15        | 2.820              | V<br>mV<br>mV        |

| Output Capacitor <sup>3</sup><br>Dropout Voltage                                                                                         | C <sub>O</sub><br>V <sub>DO</sub>          | $V_{O} = V_{INITIAL} - 100 \text{ mV}$<br>$I_{LOAD} = 100 \text{ mA}$                                                    | 2.2          |                         | 215                | μF<br>mV             |

| ANALOG LDO (VCCA)<br>Output Voltage<br>Line Regulation<br>Load Regulation                                                                | VCCA<br>DVCCA<br>DVCCA                     | Line, Load, Temp<br>3 V < VBAT < 7 V, Min Load<br>200 µA < I <sub>LOAD</sub> < 130 mA,<br>VBAT = 3.6 V                   | 2.710        | 2.765<br>2<br>15        | 2.820              | V<br>mV<br>mV        |

| Output Capacitor <sup>3</sup><br>Dropout Voltage                                                                                         | C <sub>O</sub><br>V <sub>DO</sub>          | $V_0 = V_{INITIAL} - 100 \text{ mV}$<br>$I_{LOAD} = 130 \text{ mA}$                                                      | 2.2          |                         | 215                | μF<br>mV             |

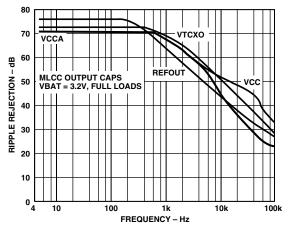

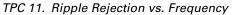

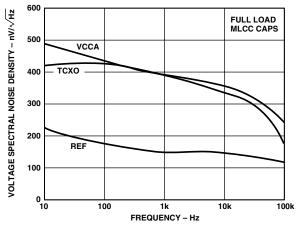

| Ripple Rejection<br>Output Noise Voltage                                                                                                 | DVBAT/<br>DVCCA<br>V <sub>NOISE</sub>      | f = 217 Hz (t = 4.6 ms)<br>VBAT = 3.6 V<br>f = 10 Hz to 100 kHz                                                          | 65           | 70<br>75                |                    | dB<br>µV rms         |

| Parameter                           | Symbol              | Conditions                                             | Min       | Тур   | Max   | Unit   |

|-------------------------------------|---------------------|--------------------------------------------------------|-----------|-------|-------|--------|

| CRYSTAL OSCILLATOR LDO (VTCXO)      |                     |                                                        |           |       |       |        |

| Output Voltage                      | VTCXO               | Line, Load, Temp                                       | 2.710     | 2.765 | 2.820 | V      |

| Line Regulation                     | ΔVTCXO              | 3  V < VBAT < 7  V, Min Load                           |           | 2     |       | mV     |

| Load Regulation                     | ΔVTCXO              | $100 \ \mu A < I_{LOAD} < 5 \ mA,$<br>VBAT = 3.6 V     |           | 1     |       | mV     |

| Output Capacitor <sup>3</sup>       | Co                  |                                                        | 0.22      |       |       | μF     |

| Dropout Voltage                     | V <sub>DO</sub>     | $V_{O} = V_{INITIAL} - 100 \text{ mV}$                 |           |       | 150   | mV     |

|                                     | 50                  | $I_{LOAD} = 5 \text{ mA}$                              |           |       |       |        |

| Ripple Rejection                    | ∆VBAT/              | f = 217  Hz (t = 4.6  ms),                             | 65        | 72    |       | dB     |

| ,                                   | ΔΥΤΟΧΟ              | VBAT = 3.6 V                                           |           |       |       |        |

| Output Noise Voltage                | V <sub>NOISE</sub>  | f = 10 Hz to 100 kHz                                   |           | 80    |       | μV rms |

| 1 0                                 | NOISE               | $I_{LOAD} = 5 \text{ mA}, \text{VBAT} = 3.6 \text{ V}$ |           |       |       | •      |

| VOLTAGE REFERENCE (REFOUT)          |                     |                                                        |           |       |       |        |

| Output Voltage                      | V <sub>REFOUT</sub> | Line, Load, Temp                                       | 1.192     | 1.210 | 1.228 | V      |

| Line Regulation                     | $\Delta V_{REFOUT}$ | 3 V < VBAT < 7 V, Min Load                             |           | 2     |       | mV     |

|                                     |                     |                                                        |           |       |       |        |

| Load Regulation                     | $\Delta V_{REFOUT}$ | $0 \ \mu A < I_{LOAD} < 50 \ \mu A$ ,                  |           | 0.5   |       | mV     |

|                                     |                     | VBAT = 3.6 V                                           |           |       |       |        |

| Ripple Rejection                    | $\Delta VBAT/$      | f = 217 Hz (t = 4.6 ms),                               | 65        | 75    |       | dB     |

|                                     | $\Delta V_{REFOUT}$ | VBAT = 3.6 V                                           |           |       |       | _      |

| Maximum Capacitive Load             | Co                  |                                                        | 100       |       |       | pF     |

| Output Noise Voltage                | V <sub>NOISE</sub>  | f = 10  Hz to  100  kHz                                |           | 40    |       | µV rms |

|                                     |                     | VBAT = 3.6 V                                           |           |       |       |        |

| REAL-TIME CLOCK LDO/                |                     |                                                        |           |       |       |        |

| BATTERY CHARGER (VRTC)              |                     |                                                        |           |       |       |        |

| Maximum Output Voltage              | VRTC                | $I_{LOAD} \leq 10 \ \mu A$                             | 2.810     | 2.850 | 2.890 | V      |

| Current Limit                       | I <sub>MAX</sub>    | 3.050 V < VBAT < 7 V                                   |           | 175   |       | μA     |

| Off Reverse Leakage Current         | IL                  | 2.0  V < VBAT < UVLO                                   |           |       | 1     | μA     |

| Dropout Voltage                     | V <sub>DO</sub>     | $V_{O} = V_{INITIAL} - 10 \text{ mV}$                  |           |       | 170   | mV     |

|                                     |                     | $I_{LOAD} = 10 \ \mu A$                                |           |       |       |        |

| SIM CHARGE PUMP (VSIM)              |                     |                                                        |           |       |       |        |

| Output Voltage for 5 V SIM Modules  | VSIM                | $0 \text{ mA} \le I_{\text{LOAD}} \le 10 \text{ mA}$   | 4.70      | 5.00  | 5.30  | V      |

|                                     |                     | SIMPROG = High                                         |           |       |       |        |

| Output Voltage for 3 V SIM Modules  | VSIM                | $0 \text{ mA} \leq I_{\text{LOAD}} \leq 6 \text{ mA}$  | 2.82      | 3.00  | 3.18  | V      |

|                                     |                     | SIMPROG = Low                                          |           |       |       |        |

| GSM/SIM LOGIC TRANSLATION           |                     |                                                        |           |       |       |        |

| (GSM INTERFACE)                     |                     |                                                        |           |       |       |        |

| Input High Voltage (SIMPROG, SIMON, | $V_{IH}$            |                                                        | VCC - 0.6 |       |       | V      |

| RESETIN, CLKIN)                     |                     |                                                        |           |       |       |        |

| Input Low Voltage (SIMPROG, SIMON,  | V <sub>IL</sub>     |                                                        |           |       | 0.6   | V      |

| RESETIN, CLKIN)                     |                     |                                                        |           |       |       |        |

| DATAIO                              | V <sub>IL</sub>     | $V_{OL}$ (I/O) = 0.4 V,                                |           |       | 0.230 | V      |

|                                     |                     | $I_{OL} (I/O) = 1 mA$                                  |           |       |       |        |

|                                     |                     | $V_{OL}$ (I/O) = 0.4 V,                                |           |       | 0.335 | V      |

|                                     |                     | $I_{OL}$ (I/O ) = 0 mA                                 |           |       |       |        |

|                                     | $V_{IH}$ , $V_{OH}$ | $I_{IH}$ , $I_{OH} = \pm 10 \ \mu A$                   | VCC-0.4   |       |       | V      |

|                                     | I <sub>IL</sub>     | $V_{IL} = 0 V$                                         |           |       | -0.9  | mA     |

|                                     | V <sub>OL</sub>     | $V_{IL}$ (I/O) = 0.4 V                                 |           |       | 0.420 | V      |

| DATAIO Pull-Up Resistance to VCC    | R <sub>IN</sub>     |                                                        | 16        | 20    | 24    | kΩ     |

| Parameter                         | Symbol                          | Conditions                           | Min            | Тур | Max            | Unit  |

|-----------------------------------|---------------------------------|--------------------------------------|----------------|-----|----------------|-------|

| SIM INTERFACE                     |                                 |                                      |                |     |                |       |

| VSIM = 5 V                        |                                 |                                      |                |     |                |       |

| RST                               | V <sub>OL</sub>                 | $I = +200 \mu A$                     |                |     | 0.6            | V     |

| RST                               | V <sub>OH</sub>                 | $I = -20 \mu \dot{A}$                | VSIM - 0.7     |     |                | V     |

| CLK                               | V <sub>OL</sub>                 | $I = +200 \mu A$                     |                |     | 0.5            | V     |

| CLK                               | V <sub>OH</sub>                 | $I = -20 \mu \dot{A}$                | 0.7 	imes VSIM |     |                | V     |

| I/O                               | V <sub>IL</sub>                 |                                      |                |     | 0.4            | V     |

| I/O                               | $V_{IH}, V_{OH}$                | $I_{IH}$ , $I_{OH} = \pm 20 \ \mu A$ | VSIM - 0.4     |     |                | V     |

| I/O                               | I <sub>IL</sub>                 | $V_{IL} = 0 V$                       |                |     | -0.9           | mA    |

| I/O                               | V <sub>OL</sub>                 | $I_{OL} = +1 \text{ mA}$             |                |     | 0.4            | V     |

|                                   |                                 | DATAIO $\leq 0.23$ V                 |                |     |                |       |

| VSIM = 3 V                        |                                 |                                      |                |     |                |       |

| RST                               | V <sub>OL</sub>                 | I = +200 μA                          |                |     | 0.2 	imes VSIM | V     |

| RST                               | V <sub>OH</sub>                 | I = -20 μA                           | 0.8 	imes VSIM |     |                | V     |

| CLK                               | V <sub>OL</sub>                 | $I = +20 \ \mu A$                    |                |     | 0.2 	imes VSIM | V     |

| CLK                               | V <sub>OH</sub>                 | $I = -20 \ \mu A$                    | 0.7 	imes VSIM |     |                | V     |

| I/O                               | V <sub>IL</sub>                 |                                      |                |     | 0.4            | V     |

| I/O                               | $V_{IH}, V_{OH}$                | $I_{IH}$ , $I_{OH}$ = ±20 $\mu$ A    | VSIM - 0.4     |     |                | V     |

| I/O                               | I <sub>IL</sub>                 | $V_{IL} = 0 V$                       |                |     | -0.9           | mA    |

| I/O                               | V <sub>OL</sub>                 | $I_{OL} = 1 \text{ mA}$              |                |     | 0.4            | V     |

|                                   |                                 | DATAIO $\leq 0.23$ V                 |                |     |                |       |

| I/O Pull-Up Resistance to VSIM    | R <sub>IN</sub>                 |                                      | 8              | 10  | 12             | kΩ    |

| Max Frequency (CLK)               | f <sub>MAX</sub>                | $C_L = 30 \text{ pF}$                | 5              |     |                | MHz   |

| Prop Delay (CLK)                  | t <sub>D</sub>                  |                                      |                | 30  | 50             | ns    |

| Output Rise/Fall Times (CLK)      | t <sub>R</sub> , t <sub>F</sub> | $C_L = 30 \text{ pF}$                |                | 9   | 18             | ns    |

| Output Rise/Fall Times (I/O, RST) | t <sub>R</sub> , t <sub>F</sub> | $C_L = 30 \text{ pF}$                |                |     | 1              | μs    |

| Duty Cycle (CLK)                  | D                               | D CLKIN = $50\%$                     | 47             |     | 53             | %     |

|                                   |                                 | f = 5 MHz                            |                |     |                |       |

| RESET GENERATOR (RESET)           |                                 |                                      |                |     |                |       |

| Output High Voltage               | V <sub>OH</sub>                 | I <sub>OH</sub> = -15 μA             | VCC - 0.3      |     |                | v     |

| Output Low Voltage                | VOH                             | $I_{OL} = -15 \mu A$                 |                |     | 0.3            | v     |

| Delay Time Per Unit Capacitance   | tD                              | -OL 15 Mil                           | 1.0            |     | 0.5            | ms/nF |

| Applied to RESCAP Pin             | U- U                            |                                      |                |     |                |       |

NOTES

<sup>1</sup>All limits at temperature extremes are guaranteed via correlation using standard Statistical Quality Control (SQC) methods .

<sup>2</sup>This feature is intended to protect against catastrophic failure of the device. Maximum allowed operating junction temperature is 125 °C. Operation beyond 125 °C could cause permanent damage to the device.

<sup>3</sup>Required for stability.

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Voltage on Any Pin with Respect                                   |

|-------------------------------------------------------------------|

| to Any GND Pin0.3 V, +10 V                                        |

| Voltage on Any Pin May Not Exceed VBAT,                           |

| with the Following Exceptions: VRTC, VSIM,                        |

| CAP+, PWRONIN, I/O, CLK, RST                                      |

| Storage Temperature Range65°C to +150°C                           |

| Operating Temperature Range20°C to +85°C                          |

| Maximum Junction Temperature                                      |

| $\theta_{JA}$ , Thermal Impedance (TSSOP-28) 4-Layer Board 68°C/W |

| $\theta_{JA}$ , Thermal Impedance (TSSOP-28) 6-Layer Board 62°C/W |

| Lead Temperature Range (Soldering, 60 sec)                        |

\*This is a stress rating only, operation beyond these limits can cause the device to be permanently damaged.

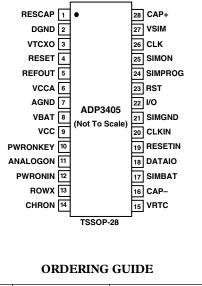

#### PIN CONFIGURATION

| Model      | Temperature    | Package       | Package |

|------------|----------------|---------------|---------|

|            | Range          | Description   | Option  |

| ADP3405ARU | –20°C to +85°C | 28-Lead TSSOP | RU-28   |

#### **PIN FUNCTION DESCRIPTIONS**

| Pin | Mnemonic | Function                                   |  |  |

|-----|----------|--------------------------------------------|--|--|

| 1   | RESCAP   | Reset Delay Timing Cap                     |  |  |

| 2   | DGND     | Digital Ground                             |  |  |

| 3   | VTCXO    | Crystal Oscillator Low Dropout             |  |  |

|     |          | Regulator                                  |  |  |

| 4   | RESET    | Main Reset                                 |  |  |

| 5   | REFOUT   | Reference Output                           |  |  |

| 6   | VCCA     | Analog Low Dropout Regulator               |  |  |

| 7   | AGND     | Analog Ground                              |  |  |

| 8   | VBAT     | Battery Input Voltage                      |  |  |

| 9   | VCC      | Digital Low Dropout Regulator              |  |  |

| 10  | PWRONKEY | Power-On/-Off Key                          |  |  |

| 11  | ANALOGON | VTCXO Enable                               |  |  |

| 12  | PWRONIN  | Power-On/-Off Signal from                  |  |  |

|     |          | Microprocessor                             |  |  |

| 13  | ROWX     | Microprocessor Keyboard Output             |  |  |

| 14  | CHRON    | Charger On/Off Input                       |  |  |

| 15  | VRTC     | Real-Time Clock Supply/Coin                |  |  |

|     |          | Cell Battery Charger                       |  |  |

| 16  | CAP-     | Negative Side of Boost Capacitor           |  |  |

| 17  | SIMBAT   | Battery Input for the SIM                  |  |  |

|     |          | Charge Pump                                |  |  |

| 18  | DATAIO   | Non-Level-Shifted Bidirectional            |  |  |

|     |          | Data I/O                                   |  |  |

| 19  | RESETIN  | Non-Level-Shifted SIM Reset                |  |  |

| 20  | CLKIN    | Non-Level-Shifted Clock                    |  |  |

| 21  | SIMGND   | Charge Pump Ground                         |  |  |

| 22  | I/O      | Level-Shifted Bidirectional SIM            |  |  |

|     |          | Data Input/Output                          |  |  |

| 23  | RST      | Level-Shifted SIM Reset                    |  |  |

| 24  | SIMPROG  | VSIM Programming:                          |  |  |

|     |          | Low = $3 \text{ V}$ , High = $5 \text{ V}$ |  |  |

| 25  | SIMON    | VSIM Enable                                |  |  |

| 26  | CLK      | Level-Shifted SIM Clock                    |  |  |

| 27  | VSIM     | SIM Supply                                 |  |  |

| 28  | CAP+     | Positive Side of Boost Capacitor           |  |  |

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADP3405 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

| Table I. L | DO Contro | l Logic |

|------------|-----------|---------|

|------------|-----------|---------|

| Inputs |       |          |         |          | Outputs | 5   |      |        |       |

|--------|-------|----------|---------|----------|---------|-----|------|--------|-------|

| UVLO   | CHRON | PWRONKEY | PWRONIN | ANALOGON | VRTC    | VCC | VCCA | REFOUT | VTCXO |

| L      | X     | Х        | Х       | X        | Off     | Off | Off  | Off    | Off   |

| Н      | н     | Х        | Х       | X        | On      | On  | On   | On     | On    |

| Н      | Х     | L        | Х       | X        | On      | On  | On   | On     | On    |

| Н      | L     | Н        | L       | X        | On      | Off | Off  | Off    | Off   |

| Н      | L     | Н        | н       | L        | On      | On  | Off  | Off    | Off   |

| Н      | L     | Н        | Н       | Н        | On      | On  | On   | On     | On    |

X = Don't care

Bold denotes the active control signal.

#### Table II. VSIM Control Logic

|     | Outputs |       |         |      |

|-----|---------|-------|---------|------|

| VCC | RESET   | SIMON | SIMPROG | VSIM |

| Off | L       | X     | X       | Off  |

| On  | L       | X     | X       | Off  |

| On  | Н       | L     | X       | Off  |

| On  | Н       | н     | L       | 3 V  |

| On  | Н       | Н     | Н       | 5 V  |

X = Don't care

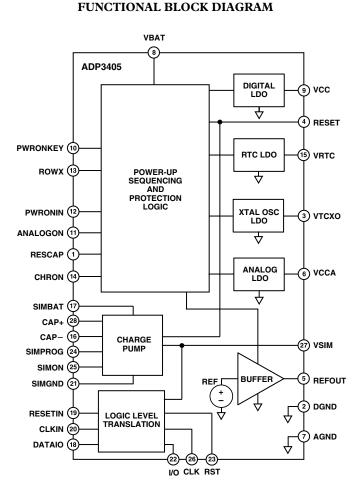

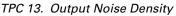

Figure 1. Functional Block Diagram

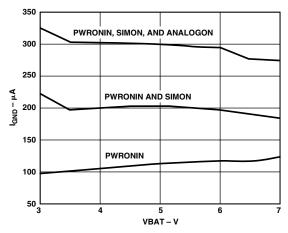

TPC 1. Ground Current vs. Battery Voltage

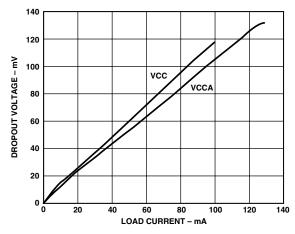

TPC 2. VCC, VCCA Dropout Voltage vs. Load Current

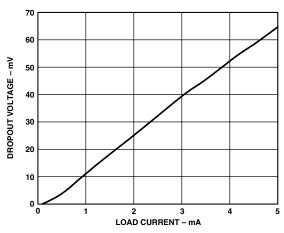

TPC 3. VTCXO Dropout Voltage vs. Load Current

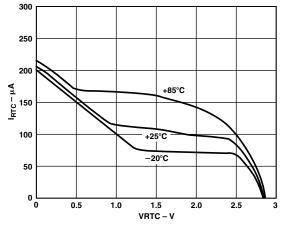

TPC 4. RTC I/V Characteristic

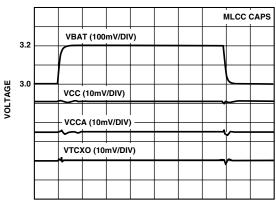

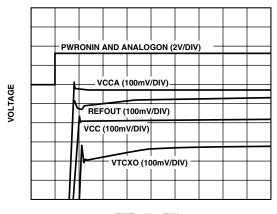

TIME – 100µs/DIV

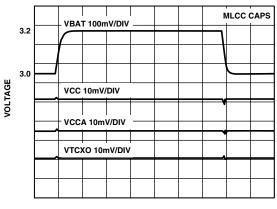

TPC 5. Line Transient Response, Maximum Loads

TIME – 100µs/DIV

TPC 6. Line Transient Response, Minimum Loads

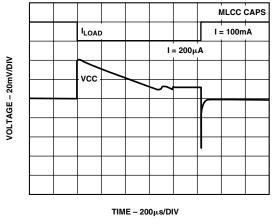

TPC 7. VCC Load Step

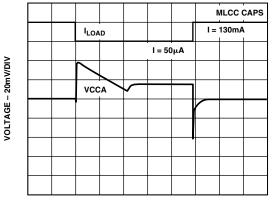

TIME – 100µs/DIV TPC 8. VCCA Load Step

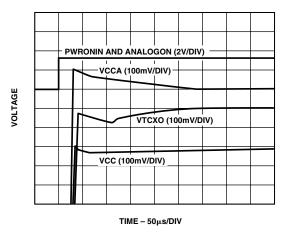

TPC 9. Turn-On Transients, Minimum Loads

TIME –  $50 \mu s/DIV$

TPC 10. Turn-On Transients, Maximum Loads

TPC 12. Ripple Rejection vs. Battery Voltage

#### THEORY OF OPERATION

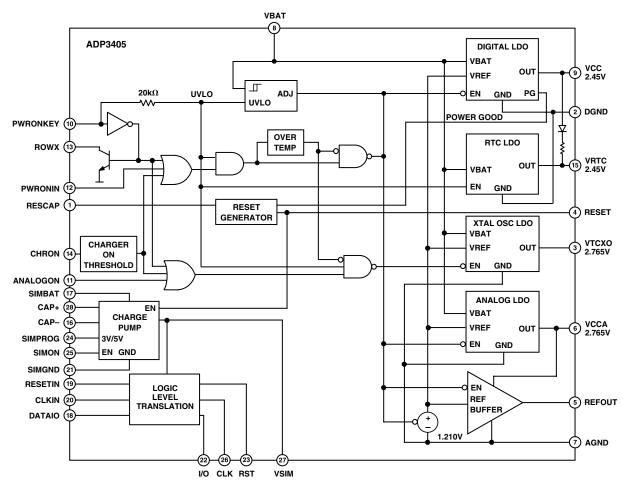

The ADP3405 is a power management chip optimized for use with the AD20msp425 GSM baseband chipsets in handset applications. Figure 1 shows a functional block diagram of the ADP3405.

The ADP3405 contains several blocks:

- Four Low Dropout Regulators (Digital, Analog, Crystal Oscillator, Real-Time Clock)

- Reset Generator

- Buffered Precision Reference

- SIM Interface Logic Level Translation (3 V/5 V)

- SIM Voltage Supply

- Power-On/-Off Logic

- Undervoltage Lockout

These functions have traditionally been done as either a discrete implementation or a custom ASIC design. ADP3405 combines the benefits of both worlds by providing an integrated standard product solution where every block is optimized to operate in a GSM environment while maintaining a cost-competitive solution.

Figure 2 shows the external circuitry associated with the ADP3405. Only a few support components, mainly decoupling capacitors, are required.

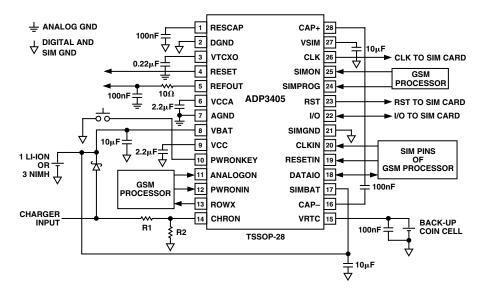

#### Input Voltage

The input voltage range for ADP3405 is 3 V to 7 V and optimized for a single Li-Ion cell or three NiMH/NiCd cells. The thermal impedance ( $\theta_{JA}$ ) of the ADP3405 is 62°C/W for 6-layer boards. The charging voltage for a high capacity NiMH cell can be as high as 5.5 V. Power dissipation should be calculated at maximum ambient temperatures and battery voltage in order not to exceed the 125°C maximum allowable junction temperature. Figure 3 shows the maximum total LDO output current as a function of ambient temperature and battery voltage.

However, high battery voltages normally occur only when the battery is being charged and the handset is not in conversation mode. In this mode there is a relatively light load on the LDOs. A fully charged Li-Ion battery is 4.25 V, where the LDOs deliver the maximum 240 mA up to the max 85°C ambient temperature.

Figure 2. Typical Application Circuit

Figure 3. Total LDO Load Current vs. Temperature and VBAT

#### Low Dropout Regulators (LDOs)

The ADP3405 high-performance LDOs are optimized for their given functions by balancing quiescent current, dropout voltage, line/load regulation, ripple rejection, and output noise. 2.2  $\mu$ F tantalum or MLCC ceramic capacitors are recommended for use with the digital and analog LDOs, and 0.22  $\mu$ F for the TCXO LDO.

#### Digital LDO (VCC)

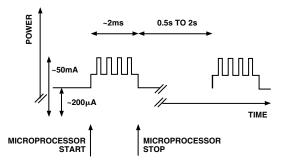

The digital LDO (VCC) supplies all the digital circuitry in the handset (baseband processor, baseband converter, external memory, display, etc.). The LDO has been optimized for very low quiescent current (30  $\mu$ A maximum) at light loads as this LDO is on at all times. This is due to both the structure of GSM and a new clocking scheme used in the AD20msp425. Figure 4 shows how the digital current varies as a function of time.

Figure 4. Digital Power as a Function of Time

#### Analog LDO (VCCA)

This LDO has the same features as the digital LDO. It has furthermore been optimized for good low frequency ripple rejection for use with analog sections in order to reject the ripple coming from the RF power amplifier. VCCA is rated to 130 mA load which is sufficient to supply the complete analog section of a baseband converter such as the AD6421/AD6425, including a 32  $\Omega$  earpiece. The analog LDO and the TCXO LDO can be controlled by ANALOGON.

#### TCXO LDO (VTCXO)

The TCXO LDO is intended as a supply for the temperaturecompensated crystal oscillator, which needs its own ultralow noise supply. The output current is rated to 5 mA for the TCXO LDO.

#### **RTC LDO (VRTC)**

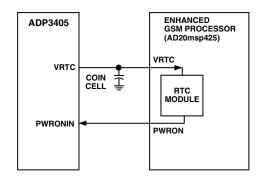

The RTC LDO charges a rechargable coin cell to run the realtime clock module. It has been targeted to charge Manganese Lithium batteries such as the ML series (ML621/ML1220) from Sanyo. The ML621 has a small physical size (6.8 mm diameter) and a nominal capacity of 2.5 mAh, which yields about 250 hours of backup time.

Figure 5 shows the use of VRTC with the Enhanced GSM Processor which is a part of the AD20msp425 chipset.

Figure 5. Connecting VRTC and PWRONIN to the AD20msp425 Chipset

The ADP3405 supplies current both for charging the coin cell and for the RTC module when the digital supply is off. The nominal charging voltage of 2.85 V ensures charging down to a main battery voltage of 3.0 V. The inherent current limit of VRTC ensures long cell life while the precise output voltage regulation charges the cell to more than 90% of its capacity. In addition, it features a very low quiescent current (10  $\mu$ A) since this LDO is running all the time, even when the handset is switched off. It also has reverse current protection with low leakage which is needed when the main battery is removed and the coin cell supplies the RTC module.

The RTC module has a built-in alarm which, when it expires, will pull PWRONIN high, allowing an alarm function even if the handset is switched off.

#### Reference Output (REFOUT)

The reference output is a low-noise, high-precision reference with a guaranteed accuracy of 1.5% over temperature. The reference can be fed to the baseband converter, such as the AD6425, improving the absolute accuracy of the converters from 5% to 1.5%. This significantly reduces calibration time needed for the baseband converter during production.

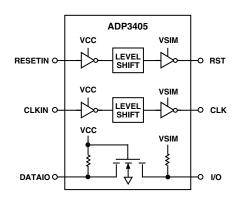

#### **SIM Interface**

The SIM interface generates the needed SIM voltage—either 3 V or 5 V, dependent on SIM type, and also performs the needed logic level translation. Quiescent current is low, as the SIM card will be powered all the time. Note that DATAIO and I/O have integrated pull-up resistors as shown in Figure 6. See Table II for the control logic of the charge pump output, VSIM.

Figure 6. Schematic for Level Translators

#### Power-On/-Off

ADP3405 handles all issues regarding power-on/-off of the handset. It is possible to turn on the ADP3405 in three different ways:

- Pulling PWRONKEY low

- Pulling PWRONIN high

- CHRON exceeds threshold

Pulling PWRONKEY key low is the normal way of turning on the handset. This will turn on all the LDOs as long as PWRONKEY is held low. The microprocessor then starts and pulls PWRONIN high after which PWRONKEY can be released. PWRONIN going high will also turn on the handset. This is the case when the alarm in the RTC module expires.

An external charger can also turn on the phone. The turn-on threshold and hysteresis can be programmed via external resistors to allow full flexibility with any external charger and battery chemistry. These resistors are referred to as R1 and R2 in Figure 2.

#### Undervoltage Lockout (UVLO)

The UVLO function in the ADP3405 prevents startup when the initial voltage of the main battery is below the 3.0 V threshold. If the battery is this low with no load, there will be little or no capacity left. When the battery is greater than 3.0 V, as with the insertion of a fresh battery, the UVLO comparator trips, the RTC LDO is enabled, and the threshold is reduced to 2.9 V. This allows the handset to start normally until the battery voltage decays to 2.9 V open circuit. Once the 3.0 V threshold is exceeded, the RTC LDO is enabled. If, however, the backup coin cell is not connected, or is damaged or discharged below 1.5 V, the RTC LDO will not start on its own. In this situation, the RTC LDO will be started by enabling the VCC LDO.

Once the system is started, i.e., the phone is turned on and the VCC LDO is up and running, the UVLO function is entirely disabled. The ADP3405 is then allowed to run down to very low battery voltages, typically around 2 V. The battery voltage is normally monitored by the microprocessor and usually shuts the phone off at around 3.0 V.

If the phone is off, i.e., the VCC LDO is off, and the battery voltage drops below 2.9 V, the UVLO circuit disables startup and the RTC LDO. This is implemented with very low quiescent current, typically 3  $\mu$ A, to protect the main battery against any damage. NiMH batteries can reverse polarity if the 3-cell battery voltage drops below 3.0 V and a current of more than about 40  $\mu$ A continues to flow. Lithium ion batteries will lose their capacity, although the built-in safety circuits normally present in these cells will most likely prevent any damage.

#### RESET

ADP3405 contains reset circuitry that is active both at power-up and at power-down. RESET is held low at power-up. An internal power-good signal starts the reset delay. The delay is set by an external capacitor on RESCAP:

$$t_{RESET} = 1.0 \quad \frac{ms}{nF} \times C_{RESCAP}$$

A 100 nF capacitor will produce a 100 ms reset time. At power-off, RESET will be kept low to prevent any spurious microprocessor starts. The current capability of RESET is low (a few hundred nA) when VCC is off, to minimize power consumption. Therefore, RESET should only be used to drive a single CMOS input. When VCC is on, RESET will drive about 15  $\mu$ A.

#### **Overtemperature Protection**

The maximum die temperature for ADP3405 is 125°C. If the die temperature exceeds 160°C, the ADP3405 will disable all the LDOs except the RTC LDO, which has very limited current capabilities. The LDOs will not be re-enabled before the die temperature is below 125°C, regardless of the state of PWRONKEY, PWRONIN, and CHRON. This ensures that the handset will always power-off before the ADP3405 exceeds its absolute maximum thermal ratings.

### APPLICATIONS INFORMATION

#### **Input Capacitor Selection**

For the input voltage, VBAT, of the ADP3405, a local bypass capacitor is recommended. Use a 5  $\mu$ F to 10  $\mu$ F, low ESR capacitor. Multilayer ceramic chip capacitors provide the best combination of low ESR and small size, but may not be cost-effective. A lower cost alternative may be to use a 5  $\mu$ F to 10  $\mu$ F tantalum capacitor with a small (1  $\mu$ F to 2  $\mu$ F) ceramic in parallel.

#### LDO Capacitor Selection

The performance of any LDO is a function of the output capacitor. The digital and analog LDOs require a 2.2  $\mu$ F capacitor and the TCXO LDO requires a 0.22  $\mu$ F capacitor. Larger values may be used, but the overshoot at startup will increase slightly. If a larger output capacitor is desired, be sure to check that the overshoot and settling time are acceptable for the application.

All the LDOs are stable with a wide range of capacitor types and ESR due to Analog Devices' anyCAP technology. The ADP3405 is stable with extremely low ESR capacitors (ESR  $\sim$  0), such as multilayer ceramic capacitors, but care should be taken in their selection. Note that the capacitance of some capacitor types shows wide variations over temperature or with dc voltage. A good quality dielectric, X7R or better, is recommended.

The RTC LDO has a rechargeable coin cell or an electric doublelayer capacitor as a load, but an additional 0.1  $\mu F$  ceramic capacitor is recommended for stability and best performance.

#### **Charge Pump Capacitor Selection**

For the input (SIMBAT) and output (VSIM) of the SIM charge pump, use 10  $\mu$ F low ESR capacitors. The use of low ESR capacitors improves the noise and efficiency of the SIM charge pump. Multilayer ceramic chip capacitors provide the best combination of low ESR and small size but may not be cost-effective. A lower cost alternative may be to use a 10  $\mu$ F tantalum capacitor with a small (1  $\mu$ F to 2  $\mu$ F) ceramic capacitor in parallel.

For the lowest ripple and best efficiency, use a 0.1  $\mu$ F, ceramic capacitor for the charge pump flying capacitor (CAP+ and CAP–). A good quality dielectric, such as X7R is recommended.

#### Setting the Charger Turn-On Threshold

The ADP3405 can be turned on when the charger input exceeds a programmable threshold voltage. The charger's threshold and hysteresis are set by selecting the values for R1 and R2 shown in Figure 2.

The turn-on threshold for the charger is calculated using:

$$V_{CHR} = \left[ \left( \frac{R2 + R_{HYS}}{R2 \times R_{HYS}} \times R1 \right) + 1 \right] \times V_T$$

Where  $V_T$  is the CHRON threshold voltage and  $R_{HYS}$  is the CHRON hysteresis resistance.

The hysteresis is determined using:

$$V_{HYS} = \frac{V_T}{R_{HYS}} \times R$$

Combining the above equations and solving for R1 and R2 gives the following formulas:

$$R1 = \frac{R_{HYS}}{V_T} \times V_{HYS}$$

$$R2 = \frac{R1 \times R_{HYS}}{\left(\frac{V_{CHR}}{V_T} - 1\right) \times R_{HYS} - R1}$$

Example:  $R1 = 10 \text{ k}\Omega$  and  $R2 = 30.2 \text{ k}\Omega$  gives a charger threshold (not counting the drop in the power Schottky diode) of 3.5 V ± 160 mV with a 200 mV ± 30 mV hysteresis.

#### **Charger Diode Selection**

The diode shown in Figure 2 is used to prevent the battery from discharging into the charger turn-on setting resistors, R1 and R2. A Schottky diode is recommended to minimize the voltage difference from the charger to the battery and the power dissipation. Choose a diode with a current rating high enough to handle both the battery charging current and the current the ADP3405 will draw if powered up during charging. The battery charging current is dependent on the battery chemistry and the charger circuit. The ADP3405 current will be dependent on the loading.

#### Printed Circuit Board Layout Considerations

Use the following general guidelines when designing printed circuit boards:

- 1. Split the battery connection to the VBAT and SIMBAT pins of the ADP3405. Use separate traces for each connection and locate the input capacitors as close to the pins as possible.

- 2. SIM input and output capacitors should be returned to the SIMGND and kept as close as possible to the ADP3405 to minimize noise. Traces to the SIM charge pump capacitor should be kept as short as possible to minimize noise.

- 3. VCCA and VTCXO capacitors should be returned to AGND.

- 4. VCC and VRTC capacitors should be returned to DGND.

- 5. Split the ground connections. Use separate traces or planes for the analog, digital, and power grounds, and tie them together at a single point, preferably close to the battery return.

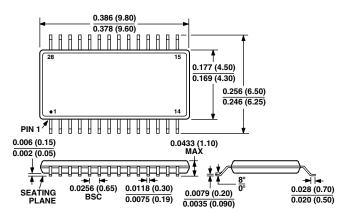

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 28-Lead Thin Shrink Small Outline (TSSOP) (RU-28)

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.