### Power management unit for LED drivers

Datasheet - production data

### **Features**

- Integrated high voltage startup

- 4 drivers for PFC, half-bridge and auxiliary **MOSFETs**

- 3.3 V microcontroller compatible

- Fully integrate power management for all operating modes

- Internal two point V<sub>CC</sub> regulator

- Overcurrent protection with digital output signal

- Cross conduction protection (interlocking)

- Undervoltage lockout

- Integrated bootstrap diode

### **Applications**

Dimmable / non-dimmable LED drivers

### **Description**

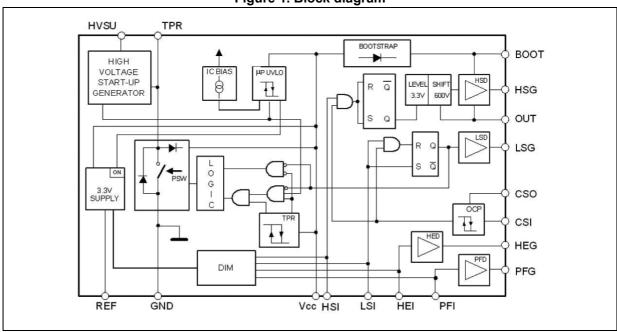

The L6382D device is suitable for LED drivers embedding a PFC stage and a half-bridge stage. The L6382D includes 4 MOSFET driving stages (for the PFC, for the half-bridge, and for the auxiliary MOSFET) plus a power management unit (PMU) featuring also a reference able to supply the microcontroller in any condition.

In addition to increasing application efficiency, the L6382D device reduces the bill of materials as different tasks (regarding drivers and power management) are performed by a single IC, which improves application reliability.

Figure 1. Block diagram

Contents L6382D

# **Contents**

| 1  | Devi  | ce description                                                           | 3  |

|----|-------|--------------------------------------------------------------------------|----|

| 2  | Pin s | settings                                                                 | 4  |

|    | 2.1   | Pin connection                                                           | 4  |

|    | 2.2   | Pin description                                                          | 4  |

| 3  | Max   | imum ratings                                                             | 6  |

|    | 3.1   | Absolute maximum ratings                                                 | 6  |

|    | 3.2   | Thermal data                                                             | 6  |

| 4  | Elec  | trical characteristics                                                   | 7  |

| 5  | Турі  | cal electrical performance                                               | 11 |

| 6  | Арр   | lication information                                                     | 12 |

|    | 6.1   | Power management                                                         | 12 |

|    | 6.2   | Startup mode 1                                                           | 12 |

|    |       | 6.2.1 Save mode                                                          | 13 |

|    |       | 6.2.2 Operating mode                                                     |    |

|    |       | 6.2.3 Shutdown                                                           | 14 |

| 7  | Bloc  | k description1                                                           | 16 |

|    | 7.1   | Supply section                                                           | 16 |

|    | 7.2   | 3.3 V reference voltage                                                  | 16 |

|    | 7.3   | Drivers                                                                  | 17 |

|    | 7.4   | Internal logic, overcurrent protection (OCP) and interlocking function 1 | 17 |

| 8  | Pacl  | rage information                                                         | 18 |

| 9  | Orde  | er codes                                                                 | 20 |

| 10 | Revi  | sion history                                                             | 20 |

L6382D Device description

## 1 Device description

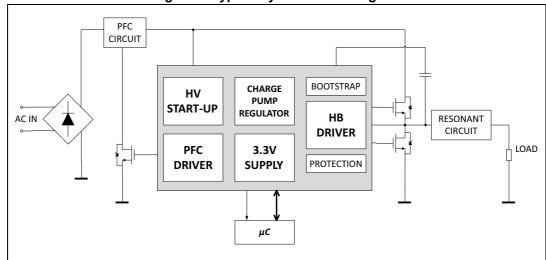

Designed in high voltage BCD off-line technology, the L6382D is a PFC and a half-bridge stage LED drivers controller equipped with 4 input pins and a high voltage startup generator conceived for applications managed by a microcontroller, providing maximum flexibility. It allows the designer to use the same LED drivers circuit for different lamp wattages/types simply by changing the mC software.

The digital input pins - capable of receiving signals up to 400 KHz - are connected to level shifters that provide the control signals to their relevant drivers. In particular, the L6382D embeds one driver for the PFC pre-regulator stage, two drivers for the LED drivers half-bridge stage (high voltage, and also including the bootstrap function) and the last one to provide supplementary features.

A precise reference voltage ( $\pm 3.3 \text{ V} \pm 1\%$ ) able to provide up to 30 mA is available to supply the mC: this current is obtained thanks to the on-chip high voltage startup generator which, moreover, keeps the consumption before startup below 150  $\mu$ A.

The chip was designed with advanced power management logic to minimize power losses and increase application reliability.

In the half-bridge section, a patented integrated bootstrap section replaces the external bootstrap diode.

The L6382D also integrates a function that regulates the IC supply voltage (without the need for an external charge pump) and optimizes the current consumption.

Figure 2. Typical system block diagram

Pin settings L6382D

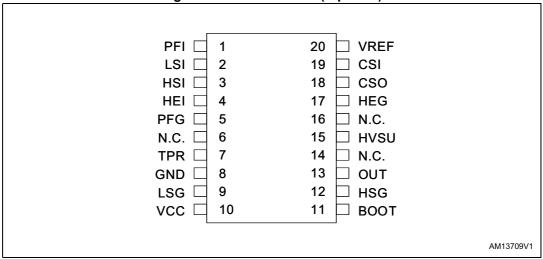

## 2 Pin settings

### 2.1 Pin connection

Figure 3. Pin connection (top view)

## 2.2 Pin description

Table 1. Pin description

| Name | Pin no. | Description                                                                                                                                                                                                                                                                                                                                                                                               |

|------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | PFI     | Digital input signal to control the PFC gate driver. This pin must be connected to a TTL compatible signal.                                                                                                                                                                                                                                                                                               |

| 2    | LSI     | Digital input signal to control the half-bridge low-side driver. This pin must be connected to a TTL compatible signal.                                                                                                                                                                                                                                                                                   |

| 3    | HSI     | Digital input signal to control the half-bridge high-side driver. This pin must be connected to a TTL compatible signal.                                                                                                                                                                                                                                                                                  |

| 4    | HEI     | Digital input signal to control the HEG output. This pin must be connected to a TTL compatible signal.                                                                                                                                                                                                                                                                                                    |

| 5    | PFG     | PFC driver output. This pin is intended to be connected to the PFC power MOSFET gate. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current. An internal 10 $k\Omega$ resistor toward ground avoids spurious and undesired MOSFET turn-on. The totem pole output stage is able to drive the power MOS with a peak current of 120 mA source and 250 mA sink. |

| 6    | N.C.    | Not connected.                                                                                                                                                                                                                                                                                                                                                                                            |

| 7    | TPR     | Input for two point regulator; by coupling the pin with a capacitor to a switching circuit, it is possible to implement a charge circuit for the Vcc.                                                                                                                                                                                                                                                     |

| 8    | GND     | Chip ground. Current return for both the low-side gate drive currents and the bias current of the IC. All of the ground connections of the bias components should be tied to a trace going to this pin and kept separate from any pulsed current return.                                                                                                                                                  |

L6382D Pin settings

Table 1. Pin description (continued)

| Name | Pin no. | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9    | LSG     | Low-side driver output. This pin must be connected to the gate of the half-bridge low-side power MOSFET. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current. An internal 20 $k\Omega$ resistor toward ground avoids spurious and undesired MOSFET turn-on. The totem pole output stage is able to drive power with a peak current of 120 mA source and 120 mA sink.                                                                                                                                        |

| 10   | Vcc     | Supply voltage for the signal part of the IC and for the drivers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 11   | BOOT    | High-side gate drive floating supply voltage. The bootstrap capacitor connected between this pin and pin 13 (OUT) is fed by an internal synchronous bootstrap diode driven in phase with the low-side gate drive. This patented structure normally replaces the external diode.                                                                                                                                                                                                                                                                             |

| 12   | HSG     | High-side driver output. This pin must be connected to the gate of the half bridge high-side power MOSFET. A resistor connected between this pin and the power MOS gate can be used to reduce the peak current. An internal 20 $k\Omega$ resistor toward OUT pin avoids spurious and undesired MOSFET turn-on The totem pole output stage is able to drive the power MOS with a peak current of 120 mA source and 120 mA sink.                                                                                                                              |

| 13   | OUT     | High-side gate drive floating ground. Current return for the high-side gate drive current. Layout carefully the connection of this pin to avoid too large spikes below ground.                                                                                                                                                                                                                                                                                                                                                                              |

| 14   | N.C.    | Not connected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 15   | HVSU    | High voltage startup. The current flowing into this pin charges the capacitor connected between pin Vcc and GND to start up the IC. While the chip is in save mode, the generator is cycled on-off between turn-on and <i>save</i> mode voltages. When the chip works in <i>operating</i> mode the generator is shut down and it is re-enabled when the Vcc voltage falls below the UVLO threshold. According to the required V <sub>REF</sub> pin current, this pin can be connected to the rectified mains voltage either directly or through a resistor. |

| 16   | N.C.    | High voltage spacer. The pin is not connected internally to isolate the high voltage pin and comply with safety regulations (creepage distance) on the PCB.                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17   | HEG     | Output for the HEI block; this driver can be used to drive the MOS. An internal 20 $\mbox{k}\Omega$ resistor toward ground avoids spurious and undesired MOSFET turnon.                                                                                                                                                                                                                                                                                                                                                                                     |

| 18   | CSO     | Output of current sense comparator, compatible with TTL logic signal; during operating mode, the pin is forced low whereas whenever the OC comparator is triggered (CSI > 0.5 V typ.) the pin latches high.                                                                                                                                                                                                                                                                                                                                                 |

| 19   | CSI     | Input of current sense comparator, it is enabled only during operating mode; when the pin voltage exceeds the internal threshold, the CSO pin is forced high and the half bridge drivers are disabled. It exits from this condition by either cycling the Vcc below the UVLO or with LGI = HGI = low simultaneously.                                                                                                                                                                                                                                        |

| 20   | VREF    | Voltage reference. During normal mode an internal generator provides an accurate voltage reference that can be used to supply up to 30 mA (during operating mode) to an external circuit. A small film capacitor (0.22 $\mu F$ min.), connected between this pin and GND is recommended to ensure the stability of the generator and to prevent noise from affecting the reference.                                                                                                                                                                         |

Maximum ratings L6382D

# 3 Maximum ratings

## 3.1 Absolute maximum ratings

Table 2. Absolute maximum ratings

| Symbol                | Pin        | Parameter                                    | Value                                    | Unit |

|-----------------------|------------|----------------------------------------------|------------------------------------------|------|

| V <sub>CC</sub>       | 10         | IC supply voltage (ICC = 20 mA)              | Self-limited                             |      |

| V <sub>HVSU</sub>     | 15         | High voltage startup generator voltage range | -0.3 to 600                              | V    |

| V <sub>BOOT</sub>     | 11         | Floating supply voltage                      | -1 to V <sub>HVSU</sub> +V <sub>CC</sub> | V    |

| V <sub>OUT</sub>      | 13         | Floating ground voltage                      | -1 to 600                                | V    |

| I <sub>TPR(RMS)</sub> | 7          | Maximum TPR RMS current                      | ± 200                                    | mA   |

| I <sub>TPR(PK)</sub>  | 7          | Maximum TPR peak current                     | ± 600                                    | mA   |

| V <sub>TPR</sub>      | 7          | Maximum TPR voltage <sup>(1)</sup>           | 14                                       | V    |

|                       | 19         | CSI input voltage                            | -0.3 to 7                                | V    |

|                       | 1, 2, 3, 4 | Logic input voltage                          | -0.3 to 7                                | V    |

|                       | 9, 12, 17  | Operating frequency                          | 15 to 400                                | KHz  |

|                       | 5          | Operating frequency                          | 15 to 600                                | KHz  |

| Tstg                  |            | Storage temperature                          | -40 to +150                              | °C   |

| $T_J$                 |            | Junction temperature operating range         | -40 to +150                              | °C   |

<sup>1.</sup> Excluding operating mode.

### 3.2 Thermal data

Table 3. Thermal data

| Symbol            | Parameter                                   | Value | Unit |

|-------------------|---------------------------------------------|-------|------|

| R <sub>thJA</sub> | Maximum thermal resistance junction ambient | 120   | °C/W |

## 4 Electrical characteristics

(T<sub>J</sub> = 25 °C, V<sub>CC</sub> = 13 V, C<sub>DRIVER</sub> = 1 nF unless otherwise specified).

**Table 4. Electrical characteristics**

| Symbol                | Pin    | Parameter                           | Test condition                                      | Min.  | Тур.  | Max.       | Unit                     |

|-----------------------|--------|-------------------------------------|-----------------------------------------------------|-------|-------|------------|--------------------------|

| Supply volta          | age    |                                     |                                                     |       |       |            |                          |

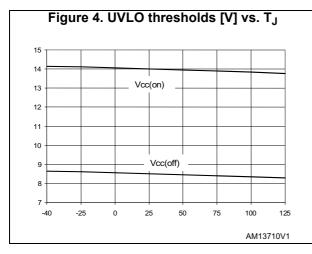

| V <sub>CCON</sub>     | 10     | Turn-on voltage                     |                                                     | 13    | 14    | 15         | V                        |

| V <sub>CCOFF</sub>    | 10     | Turn-off voltage                    |                                                     | 7.5   | 8.25  | 9.2        | ٧                        |

| V <sub>CCSM</sub>     | 10     | Save mode voltage                   |                                                     | 12.75 | 13.8  | 14.85      | V                        |

| VSMhys                | 10     | Save mode hysteresis                |                                                     | 0.12  | 0.16  | 0.2        | <b>\</b>                 |

| V <sub>REF(OFF)</sub> | 10     | Reference turn-off                  |                                                     | 5.7   | 6     | 6.4        | V                        |

| IvccON                | 10     | Startup current                     |                                                     |       |       | 150        | μА                       |

| IvccSM                | 10     | Save mode current consumption       | Tj = -40 °C to 150 °C                               |       | 150   | 190<br>230 | μ <b>Α</b><br>μ <b>Α</b> |

| lvcc                  | 10     | Quiescent current in operating mode | LGI = HGI = high;<br>no load on V <sub>REF</sub>    |       |       | 2          | mA                       |

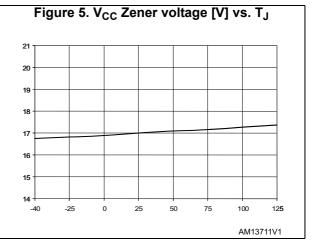

| Vz                    | 10     | Internal clamp voltage              |                                                     | 16.5  |       | 18         | ٧                        |

| High voltage          | startu | p                                   |                                                     |       |       |            |                          |

| IMSS                  | 15     | Maximum current                     | V <sub>HVSU</sub> > 50 V                            | 20    |       |            | mA                       |

| ILSS                  | 15     | Leakage current off state           | V <sub>HVSU</sub> = 600 V                           |       |       | 40         | μΑ                       |

| Two point re          | gulato | r (TPR) protection                  |                                                     |       |       |            |                          |

| TPR <sub>st</sub>     | 10     | Vcc protection level                | Operating mode                                      | 14.0  | 14.5  | 15.0       | ٧                        |

| TPR <sub>(ON)</sub>   | 10     | Vcc turn-on level                   | Operating mode; after the first falling edge on LSG | 12.5  | 13    | 13.5       | V                        |

| TPR <sub>(OFF)</sub>  | 10     | Vcc turn-off level                  | Operating mode; after the first falling edge on LSG | 12.45 | 12.95 | 13.48      | V                        |

|                       | 7      | Output voltage on state             | ITPR = 200 mA                                       |       |       | 2          | ٧                        |

|                       | 7      | Forward voltage drop diode          | At 600 mA forward current                           |       |       | 2.3        | V                        |

|                       | 7      | Leakage current off state           | VTPR = 13 V                                         |       |       | 5          | μΑ                       |

Electrical characteristics L6382D

Table 4. Electrical characteristics (continued)

| Symbol              | Pin      | Parameter                           | Test condition                   | Min. | Тур. | Max. | Unit |

|---------------------|----------|-------------------------------------|----------------------------------|------|------|------|------|

| LSG, HEG a          | nd PFG   | drivers                             |                                  |      |      |      |      |

| .,                  | 5, 9     |                                     | ILSG = IPFG = 10 mA              |      |      | 1    |      |

| $V_{OH(LS)}$        | 17       | HIGH output voltage                 | IHEG = 2.5 mA                    |      | 12.5 |      | V    |

| .,                  | 5, 9     |                                     | ILSG = IPFG = 10 mA              |      |      |      | .,   |

| $V_{OL(LS)}$        | 17       | LOW output voltage                  | IHEG = 2.5 mA                    |      | 0.5  |      | V    |

|                     |          | O                                   | LSG and PFG                      | 120  |      |      | mA   |

|                     |          | Source current capability           | HEG                              | 50   |      |      | mA   |

|                     |          |                                     | LSG                              | 120  |      |      | mA   |

|                     |          | Sink current capability             | HEG                              | 70   |      |      |      |

|                     |          |                                     | PFG                              | 250  |      |      |      |

|                     |          |                                     | LSG                              |      | 115  |      | ns   |

| T <sub>RISE</sub>   |          | Rise time                           | HEG                              |      | 300  |      | ns   |

|                     |          |                                     | PFG                              |      | 60   |      | ns   |

|                     |          |                                     | LSG                              |      | 75   |      | ns   |

| T <sub>FALL</sub>   |          | Fall time                           | HEG                              |      | 110  |      | ns   |

|                     |          |                                     | PFG                              |      | 40   |      | ns   |

|                     |          |                                     | LSG; high to low and low to high |      |      | 300  | ns   |

| T <sub>DELAY</sub>  |          | Propagation delay (input to output) | HEG; high to low and low to high |      |      | 200  | ns   |

|                     |          | . ,                                 | PFG; high to low                 |      |      | 250  | ns   |

|                     |          |                                     | PFG; low to high                 |      |      | 200  | ns   |

|                     |          |                                     | LSG                              |      | 20   |      | ΚΩ   |

| $R_B$               |          | Pull-down resistor                  | HEG                              |      | 50   |      | ΚΩ   |

|                     |          |                                     | PFG                              |      | 10   |      | ΚΩ   |

| HSG driver          | (voltage | es referred to OUT)                 | •                                | 1    | •    |      |      |

| V <sub>OH(HS)</sub> | 12       | HIGH output voltage                 | IHSG = 10 mA                     |      | 12.5 |      | V    |

| V <sub>OL(HS)</sub> | 12       | LOW output voltage                  | IHSG = 10 mA                     |      | 0.5  |      | V    |

|                     | 12       | Sink current capability             |                                  | 120  |      |      | mA   |

|                     | 12       | Source current capability           |                                  | 120  |      |      | mA   |

| T <sub>RISE</sub>   | 12       | Rise time                           | C <sub>load</sub> = 1 nF         |      | 115  |      | ns   |

| T <sub>FALL</sub>   | 12       | Fall time                           | C <sub>load</sub> = 1 nF         |      | 75   |      | ns   |

Table 4. Electrical characteristics (continued)

| Symbol                 | Pin      | Parameter                                 | Test condition                                                                                                                           | Min.                          | Тур. | Max.  | Unit |

|------------------------|----------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|------|-------|------|

| T <sub>DELAY</sub>     | 12       | Propagation delay (LGI to LSG)            | High to low and low to high                                                                                                              |                               |      | 300   | ns   |

| R <sub>B</sub>         | 12       | Pull-down resistor                        | To OUT                                                                                                                                   |                               | 20   |       | ΚΩ   |

| High-side flo          | oating ( | gate driver supply                        |                                                                                                                                          |                               |      |       |      |

| I <sub>LKBOOT</sub>    | 11       | V <sub>BOOT</sub> pin leakage current     | V <sub>BOOT</sub> = 580 V                                                                                                                |                               |      | 5     | μA   |

| I <sub>LKOUT</sub>     | 13       | OUT pin leakage current                   | V <sub>OUT</sub> = 562 V                                                                                                                 |                               |      | 5     | μA   |

| R <sub>DS(on)</sub>    |          | Synchronous bootstrap diode on-resistance | V <sub>LVG</sub> = HIGH                                                                                                                  |                               | 150  |       | Ω    |

|                        |          | Forward voltage drop                      | At 10 mA forward current                                                                                                                 |                               | 2.4  |       | ٧    |

|                        |          | Forward current                           | At 5 V forward voltage drop                                                                                                              | 20                            |      |       | mA   |

| V <sub>REF</sub>       |          | ,                                         |                                                                                                                                          | l                             | I    | ,     |      |

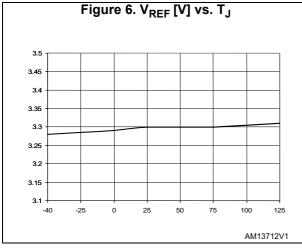

| V <sub>REF</sub>       | 20       | Reference voltage                         | 15 mA load                                                                                                                               | 3.267                         | 3.3  | 3.366 | ٧    |

|                        | 20       | Load regulation                           | I <sub>REF</sub> = -3 to +30 mA                                                                                                          | -20                           |      | 2     | mV   |

|                        | 20       | Voltage change                            | 15 mA load; Vcc = 9 V to 15 V                                                                                                            |                               |      | 15    | mV   |

| V <sub>REF_LATCH</sub> | 20       | V <sub>REF</sub> latched protection       |                                                                                                                                          |                               |      | 2     | ٧    |

|                        | 20       | V <sub>REF</sub> clamp at 3 mA            | V <sub>CC</sub> from 0 to V <sub>CCON</sub> during startup; Vcc from V <sub>REF</sub> (OFF) to 0 during shutdown; V <sub>REF</sub> < 2 V |                               | 1.2  | 1.4   | ٧    |

| I <sub>REF</sub>       | 20       | Current drive capability                  |                                                                                                                                          | -3                            |      | +30   | mA   |

| 'REF                   |          | Current unive capability                  | Save mode                                                                                                                                | -3                            |      | +10   | mA   |

| Overcurrent            | buffer   | stage                                     |                                                                                                                                          |                               |      |       |      |

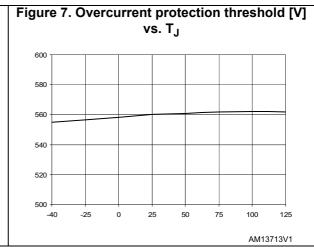

| V <sub>CSI</sub>       | 19       | Comparator level                          |                                                                                                                                          | 0.537                         | 0.56 | 0.582 | V    |

| I <sub>CSI</sub>       | 19       | Input bias current                        |                                                                                                                                          |                               |      | 500   | nA   |

|                        |          | Propagation delay                         | CSO turn off to LSG low                                                                                                                  |                               |      | 200   | ns   |

|                        | 18       | High output voltage                       | I <sub>CSO</sub> = 200 μA                                                                                                                | V <sub>REF</sub><br>-0.5<br>V |      |       |      |

|                        | 18       | Low output voltage                        | I <sub>CSO</sub> = -150 μA                                                                                                               |                               |      | 0.5   | V    |

Electrical characteristics L6382D

Table 4. Electrical characteristics (continued)

| Symbol          | Pin    | Parameter                         | Test condition | Min. | Тур. | Max. | Unit |

|-----------------|--------|-----------------------------------|----------------|------|------|------|------|

| DIM             |        |                                   |                |      |      |      |      |

|                 |        | Normal mode time out              |                | 70   | 100  | 130  | μs   |

|                 |        | V <sub>REF</sub> enabling drivers |                |      | 3.0  |      | V    |

| T <sub>ED</sub> |        | Time enabling drivers             |                |      | 10   |      | μs   |

| Logic input     |        |                                   |                |      |      |      |      |

|                 | 1 to 4 | Low level logic input voltage     |                |      |      | 0.8  | V    |

|                 | 1 to 4 | High level logic input voltage    |                | 2.2  |      |      | V    |

|                 | LGI    | Pull-down resistor                |                |      | 100  |      | ΚΩ   |

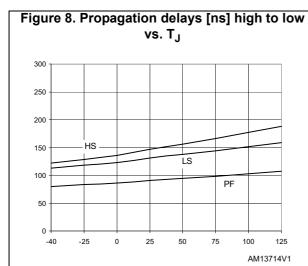

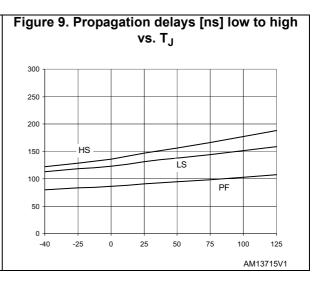

## 5 Typical electrical performance

577

## 6 Application information

### 6.1 Power management

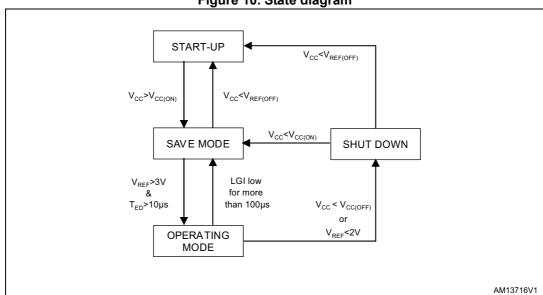

The L6382D has two stable states (save mode and operating mode) and two additional states that manage the startup and fault conditions (*Figure 10*): the overcurrent protection is a parallel asynchronous process enabled when in operating mode.

The following paragraphs describe each mode and the condition necessary to shift between them.

Figure 10. State diagram

## 6.2 Startup mode

With reference to the timing diagram in *Figure 11*, when power is first applied to the converter, the voltage on the bulk capacitor builds up and the HV generator is enabled to operate, drawing about 10 mA. This current, diminished by the IC consumption (less than 150  $\mu$ A), charges the bypass capacitor connected between pin Vcc and ground and makes its voltage rise almost linearly.

During this phase, all IC functions are disabled except for:

- the current sinking circuit on the V<sub>REF</sub> pin maintains the voltage low by keeping the microcontroller connected to this pin disabled;

- the high voltage startup (HVSU) that is ON (conductive) to charge the external capacitor on pin Vcc.

12/21 DocID10972 Rev 8

As the Vcc voltage reaches the startup threshold (14 V typ.) the chip starts operating and the HV generator is switched off.

#### To summarize:

- the high voltage startup generator is active

- VREF is disabled with an additional sinking circuit on pin V<sub>REF</sub> enabled

- TPR is disabled

- OCP is disabled

- the drivers are disabled

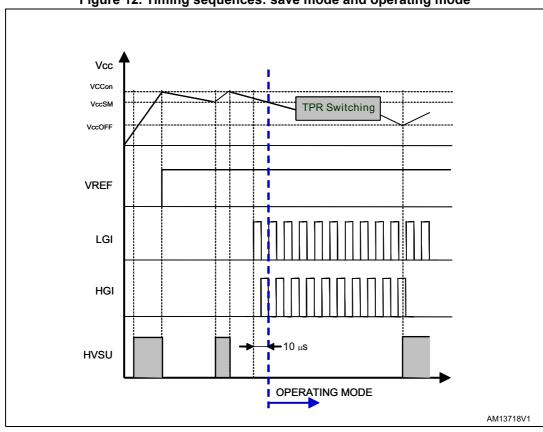

#### 6.2.1 Save mode

This mode is entered after the Vcc voltage reaches the turn-on threshold; the  $V_{REF}$  is enabled in low current source mode to supply the  $\mu C$  connected to it, the required wakeup current of which must be less than 10 mA: if no switching activity is detected at the LGI input, the high voltage startup generator cycles ON-OFF, keeping the Vcc voltage between VccON and VccSM.

#### Summarizing:

- the high voltage startup generator is cycling

- VREF is enabled in low source current capability (I<sub>REF</sub> ≤ 10 mA)

- TPR circuit is disabled

- OCP is disabled

the drivers are disabled.

If the Vcc voltage falls below the V<sub>REF(OFF)</sub> threshold, the device enters the startup mode.

#### 6.2.2 Operating mode

After 10  $\mu s$  in save mode and only if the voltage at  $V_{REF}$  is higher than 3.0 V, on the falling edge on the HGI input, the drivers are enabled as well as all the IC functions; this is the mode corresponding to the proper lamp behavior.

#### To summarize:

- HVSU is OFF

- VREF is enabled in high source current mode (I<sub>RFF</sub> < 30 mA)</li>

- TPR circuit is enabled

- OCP is enabled

- the drivers are enabled

If there is no switching activity on LGI for more than 100 μs, the IC returns to save mode.

#### 6.2.3 Shutdown

This state permits to manage the fault conditions in operating mode and it is entered by the occurrence on one of the following conditions:

- 1. Vcc < VccOff (undervoltage fault on supply)

- 2.  $V_{REF} < 2.0 \text{ V}$  (undervoltage fault on  $V_{REF}$ )

In this state the functions are:

- The HVSU generator is ON

- VREF is enabled in low source current mode (I<sub>REF</sub> < 10 mA)</li>

- TPR is disabled

- OCP is disabled

- the drivers are disabled

In this state if Vcc reaches VccOn, the device enters the save mode otherwise, if Vcc <  $V_{REF(OFF)}$ , also the  $\mu C$  is turned off and the device will be ready to execute the startup sequence.

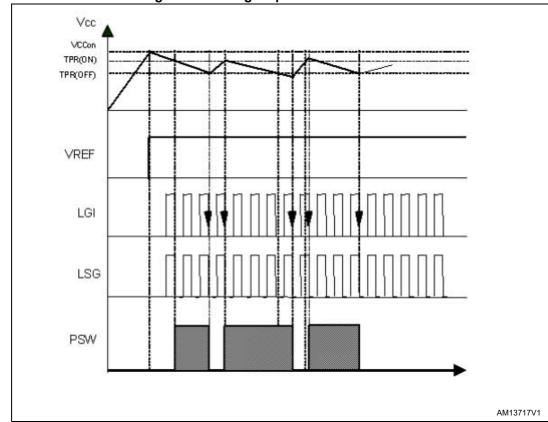

Figure 11. Timing sequences: TPR behavior

57

Figure 12. Timing sequences: save mode and operating mode

Block description L6382D

## 7 Block description

### 7.1 Supply section

**μPUVLO** (μpower undervoltage lockout): This block controls the power management of the L6382D, ensuring the correct current consumption in each operating state, the correct  $V_{REF}$  current capability, driver enabling and high voltage startup generator switching. During startup, the device sinks the current necessary to charge the external capacitor on pin  $V_{CC}$  from the high voltage bus. In this state, the other IC functions are disabled and the current consumption of the whole IC is less than 150 μA.

When the voltage on VCC pin reaches VccON, the IC enters the save mode where the  $\mu$ PUVLO block controls Vcc between VccON and VccSM by switching ON/OFF the high voltage startup generator.

- HVSU (high voltage startup generator): a 600 V internal MOS transistor structure

controls the Vcc supply voltage during startup and save mode conditions and it reduces

the power losses during operating Mode by switching OFF the MOS transistor. The

transistor has a source current capability of up to 30 mA.

- TPR (two point regulator) and PWS: during normal mode, the TPR block controls the PSW switch in order to regulate the IC supply voltage (VCC) to a value in the range between TPR(ON) and TPR(OFF) by switching ON and OFF the PSW transistor Figure 11.

- Vcc > TPRst: the PSW is switched ON immediately

- TPR(ON) < Vcc < TPRst: the PSW is switched ON at the following falling edge of LGI

- Vcc < TPR(OFF): the PSW is switched OFF at the following falling edge on LGI</li>

When the PSW switch is OFF, the diodes build a charge pump structure so that, connecting the TPR pin to a switching voltage (through a capacitor) it is possible to supply the low voltage section of the chip without adding any further external components. The diodes and the switch are designed to withstand a current of at least 200  $mA_{RMS}$ .

### 7.2 3.3 V reference voltage

This block is used to supply the microcontroller; this source is able to supply 10 mA in save mode and 30 mA in operating mode. Moreover, during startup when  $V_{REF}$  is not yet available, an additional circuit ensures that, even sinking 3 mA, the pin voltage will not exceed 1.2 V.

The reference is available until Vcc is above V<sub>REF(OFF)</sub>; below that it turns off and the additional sinking circuit is enabled again.

16/21 DocID10972 Rev 8

L6382D Block description

#### 7.3 Drivers

• LSD (low-side driver): it consists of a level shifter from 3.3 V logic signal (LSI) to Vcc MOS driving level; conceived for the half-bridge low-side power MOS, it is able to source and sink 120 mA (min).

- **HSD** (level shifter and high-side driver): it consists of a level shifter from 3.3 V logic signal (HGI) to the high-side gate driver input up to 600 V. Conceived for the half-bridge high-side power MOS, the HSG is able to source and sink 120 mA.

- PFD (power factor driver): it consists of a level shifter from 3.3 V logic signal (PFI) to Vcc MOS driving level: the driver is able to source 120 mA from Vcc to PFG (turn-on) and to sink 250 mA to GND (turn-off). It is suitable to drive the MOS of the PFC preregulator stage.

- HED (auxiliary driver): it consists of a level shifter from 3.3 V logic signal (HEI) to Vcc MOS driving level; the driver is able to source 30 mA from Vcc to HEG and to sink 75 mA to GND.

- Bootstrap circuit: it generates the supply voltage for the high-side driver (HSD).

A patented integrated bootstrap section replaces an external bootstrap diode. This section together with a bootstrap capacitor provides the bootstrap voltage to drive the high-side power MOSFET. This function is achieved using a high voltage DMOS driver which is driven synchronously with the low-side external power MOSFET. For safe operation, current flow between the BOOT pin and Vcc is always inhibited, even though ZVS operation may not be ensured.

# 7.4 Internal logic, overcurrent protection (OCP) and interlocking function

The DIM (digital input monitor) block manages the input signals delivered to the drivers ensuring that they are low during the described startup procedure; the DIM block controls the L6382D behavior during both save and operating modes.

When the voltage on pin CSI exceeds the internal reference of 0.5 V (typ.) the block latches the fault condition: in this state the OCP block forces low both HSG and LSG signals while CSO will be forced high. This condition remains latched until LSI and HSI are simultaneously low and CSI is below 0.5 V.

This function is suitable to implement overcurrent protection or hard-switching detection by using an external sense resistor.

As the voltage on pin CSI can go negative, the current must be limited below 2 mA by external components.

Another feature of the DIM block is the internal interlocking that prevents cross conduction in the half-bridge FETs. If by chance both HGI and LGI inputs are brought high at the same time, then LSG and HSG are forced low as long as this critical condition persists.

Package information L6382D

# 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

L6382D Package information

D hx45'

B B B

SEATING PLANE

C 0,25 mm

GAGE PLANE

O016022\_E

Figure 13. SO-20 package outline

Table 5. SO-20 package mechanical data

| Symbol   |       | Dimensions (mm) |       |

|----------|-------|-----------------|-------|

| - Symbol | Min.  | Тур.            | Max.  |

| А        | 2.35  |                 | 2.65  |

| A1       | 0.10  |                 | 0.30  |

| В        | 0.33  |                 | 0.51  |

| С        | 0.23  |                 | 0.32  |

| D (1)    | 12.60 |                 | 13.00 |

| E        | 7.40  |                 | 7.60  |

| е        |       | 1.27            |       |

| Н        | 10.0  |                 | 10.65 |

| h        | 0.25  |                 | 0.75  |

| L        | 0.40  |                 | 1.27  |

| k        | 0°    |                 | 8°    |

| ddd      |       |                 | 0.10  |

Order codes L6382D

## 9 Order codes

Table 6. Order codes

| Part number | Package | Packaging     |

|-------------|---------|---------------|

| L6382D      | SO-20   | Tube          |

| L6382DTR    | SO-20   | Tape and reel |

# 10 Revision history

Table 1. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-Nov-2004 | 1        | First Issue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 03-Jan-2005 | 2        | Changed from "Preliminary Data" to "Final Datasheet"                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 23-Oct-2005 | 3        | Many modified                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 19-Apr-2006 | 4        | New template                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 22-May-2006 | 5        | Typo error in block diagram, updated values in electrical characteristics <i>Table 6</i> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 21-Mar-2007 | 6        | Typo on Table 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 06-Jun-2013 | 7        | Updated Table 3: Thermal data, Table 4: Electrical characteristics, Table 5: SO-20 package mechanical data and Figure 9: Order codes. Minor text changes.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 01-Sep-2014 | 8        | Updated main title on page 1 (replaced "microcontrolled ballast" by "LED drivers").  Updated Section: Features on page 1 (replaced "preheating" by "auxiliary).  Updated Section: Applications on page 1 (replaced "ballast" by "LED drivers").  Updated Section: Description on page 1 (replaced "microcontrolled electronic ballast" by "LED drivers" and "preheating" by "auxiliary).  Updated Section 1: Device description on page 3 (replaced "ballast" by "LED drivers", added "half-bridge stage", removed "like preheating of filaments supplied through isolated windings in dimmable applications.", replaced Figure 2 by new figure).  Updated Table 1: Pin description on page 4 (removed "employed in preheating isolated filaments").  Updated Table 4: Electrical characteristics on page 7 (updated Min. value of Vz symbol, replaced "Zener" by "clamp voltage").  Updated Section 7.3: Drivers on page 17 (removed "and it is suitable for the filament heating when they are supplied by independent winding.", replaced "heat" by "auxiliary").  Updated Section 8: Package information on page 18 (updated titles, reversed order of Figure 13 on page 19 and Table 5 on page 19, minor modifications).  Minor modifications throughout document. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2014 STMicroelectronics - All rights reserved

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.