# DMOS driver for bipolar stepper motor

#### **Datasheet - production data**

PowerSO36

SO24 (20 + 2 + 2)

Ordering numbers:

L6208PD (PowerSO36) L6208D (SO24)

#### **Features**

- · Operating supply voltage from 8 to 52 V

- 5.6 A output peak current (2.8 A RMS)

- R<sub>DS(ON)</sub> 0.3 Ω typ. value at T<sub>i</sub> = 25 °C

- Operating frequency up to 100 KHz

- Non-dissipative overcurrent protection

- Dual independent constant t<sub>OFF</sub> PWM current controllers

- Fast/slow decay mode selection

- Fast decay quasi-synchronous rectification

- Decoding logic for stepper motor full and half step drive

- Cross conduction protection

- Thermal shutdown

- Undervoltage lockout

- Integrated fast freewheeling diodes

### **Applications**

· Bipolar stepper motor

### **Description**

The L6208 device is a DMOS fully integrated stepper motor driver with non-dissipative overcurrent protection, realized in BCD technology, which combines isolated DMOS power transistors with CMOS and bipolar circuits on the same chip. The device includes all the circuitry needed to drive a two phase bipolar stepper motor including: a dual DMOS full bridge, the constant off time PWM current controller that performs the chopping regulation and the phase sequence generator, that generates the stepping sequence. Available in PowerSO36 and SO24 (20 + 2 + 2) packages, the L6208 device features a non-dissipative overcurrent protection on the high-side power MOSFETs and thermal shutdown.

Contents L6208

# **Contents**

| 1  | Bloc  | Block diagram                                      |     |  |  |  |  |  |

|----|-------|----------------------------------------------------|-----|--|--|--|--|--|

| 2  | Max   | Maximum ratings                                    |     |  |  |  |  |  |

| 3  | Pin o | connections                                        | . 6 |  |  |  |  |  |

| 4  | Elec  | trical characteristics                             | . 8 |  |  |  |  |  |

| 5  | Circ  | uit description                                    | 12  |  |  |  |  |  |

|    | 5.1   | Power stages and charge pump                       | 12  |  |  |  |  |  |

|    | 5.2   | Logic inputs                                       | 13  |  |  |  |  |  |

| 6  | PWN   | /I current control                                 | 14  |  |  |  |  |  |

| 7  | Deca  | ay modes                                           | 18  |  |  |  |  |  |

|    | 7.1   | Stepping sequence generation                       | 19  |  |  |  |  |  |

|    | 7.2   | Half step mode                                     | 19  |  |  |  |  |  |

|    | 7.3   | Normal drive mode (full step two phase on)         | 19  |  |  |  |  |  |

|    | 7.4   | Wave drive mode (full step one phase on)           | 19  |  |  |  |  |  |

|    | 7.5   | Non-dissipative overcurrent protection             | 21  |  |  |  |  |  |

|    | 7.6   | Thermal protection                                 | 23  |  |  |  |  |  |

| 8  | App   | lication information                               | 24  |  |  |  |  |  |

|    | 8.1   | Output current capability and IC power dissipation | 25  |  |  |  |  |  |

|    | 8.2   | Thermal management                                 | 27  |  |  |  |  |  |

| 9  | Pack  | kage information                                   | 30  |  |  |  |  |  |

|    | 9.1   | PowerSO36 package information                      | 30  |  |  |  |  |  |

|    | 9.2   | SO24 package information                           | 32  |  |  |  |  |  |

| 10 | Revi  | sion history                                       | 33  |  |  |  |  |  |

L6208 **Block diagram**

# **Block diagram**

VBOOT  $V_{\mathsf{BOOT}}$ CHARGE PUMP VCP OVER-1 CURRENT DETECTION OCDB OUT1<sub>A</sub> OUT2<sub>A</sub> THERMAL PROTECTION GATE LOGIC CONTROL SENSEA HALF/FULL PWM STEPPING SEQUENCE GENERATION ONE SHOT MONOSTABLE CLOCK MASKING SENSE COMPARATOR VREFA RESET cw/ccw  $\mathsf{RC}_\mathsf{A}$ BRIDGE A  $VS_B$ OVER-CURRENT DETECTION OUT1<sub>B</sub> VOLTAGE REGULATOR  ${\rm OUT2_B}$  $\mathsf{SENSE}_\mathsf{B}$ GATE LOGIC VREFB 10 V 5 V  $RC_B$ BRIDGE B D01IN1225V2

Figure 1. Block diagram

Maximum ratings L6208

# 2 Maximum ratings

Table 1. Absolute maximum ratings

| Symbol                                       | Parameter                                                                                                                                                                                  | Test conditions                                                              | Value               | Unit |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------|------|

| V <sub>S</sub>                               | Supply voltage                                                                                                                                                                             | $V_{SA} = V_{SB} = V_{S}$                                                    | 60                  | V    |

| V <sub>OD</sub>                              | Differential voltage between VS <sub>A</sub> , OUT1 <sub>A</sub> , OUT2 <sub>A</sub> , SENSE <sub>A</sub> and VS <sub>B</sub> , OUT1 <sub>B</sub> , OUT2 <sub>B</sub> , SENSE <sub>B</sub> | $V_{SA} = V_{SB} = V_{S} = 60 \text{ V};$<br>$V_{SENSEA} = V_{SENSEB} = GND$ | 60                  | V    |

| $V_{BOOT}$                                   | Bootstrap peak voltage                                                                                                                                                                     | $V_{SA} = V_{SB} = V_{S}$                                                    | V <sub>S</sub> + 10 | V    |

| $V_{IN}, V_{EN}$                             | Input and enable voltage range                                                                                                                                                             | -                                                                            | -0.3 to +7          | V    |

| V <sub>REFA</sub> ,<br>V <sub>REFB</sub>     | Voltage range at pins V <sub>REFA</sub> and V <sub>REFB</sub>                                                                                                                              | -                                                                            | -0.3 to +7          | V    |

| V <sub>RCA,</sub><br>V <sub>RCB</sub>        | Voltage range at pins RC <sub>A</sub> and RC <sub>B</sub>                                                                                                                                  | -                                                                            | -0.3 to +7          | V    |

| V <sub>SENSEA</sub> ,<br>V <sub>SENSEB</sub> | Voltage range at pins SENSE <sub>A</sub> and SENSE <sub>B</sub>                                                                                                                            | -                                                                            | -1 to +4            | V    |

| I <sub>S(peak)</sub>                         | Pulsed supply current (for each V <sub>S</sub> pin), internally limited by the overcurrent protection                                                                                      | $V_{SA} = V_{SB} = V_S;$<br>$t_{PULSE} < 1 \text{ ms}$                       | 7.1                 | Α    |

| I <sub>S</sub>                               | RMS supply current (for each V <sub>S</sub> pin)                                                                                                                                           | $V_{SA} = V_{SB} = V_{S}$                                                    | 2.8                 | Α    |

| T <sub>stg</sub> , T <sub>OP</sub>           | Storage and operating temperature range                                                                                                                                                    | -                                                                            | -40 to 150          | °C   |

Table 2. Recommended operating conditions

| Symbol                                       | Parameter                                                                                                          | Test conditions                                                                                   | Min.     | Max.   | Unit   |

|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------|--------|--------|

| V <sub>S</sub>                               | Supply voltage                                                                                                     | $V_{SA} = V_{SB} = V_{S}$                                                                         | 8        | 52     | V      |

| V <sub>OD</sub>                              | Differential voltage between $VS_A$ , $OUT1_A$ , $OUT2_A$ , $SENSE_A$ and $VS_B$ , $OUT1_B$ , $OUT2_B$ , $SENSE_B$ | V <sub>SA</sub> = V <sub>SB</sub> = V <sub>S</sub> ;<br>V <sub>SENSEA</sub> = V <sub>SENSEB</sub> | -        | 52     | V      |

| V <sub>REFA</sub> ,<br>V <sub>REFB</sub>     | Voltage range at pins V <sub>REFA</sub> and V <sub>REFB</sub>                                                      | -                                                                                                 | -0.1     | 5      | V      |

| V <sub>SENSEA</sub> ,<br>V <sub>SENSEB</sub> | Voltage range at pins SENSE <sub>A</sub> and SENSE <sub>B</sub>                                                    | (pulsed t <sub>W</sub> < t <sub>rr</sub> )<br>(DC)                                                | -6<br>-1 | 6<br>1 | V<br>V |

| I <sub>OUT</sub>                             | RMS output current                                                                                                 | -                                                                                                 | -        | 2.8    | Α      |

| f <sub>sw</sub>                              | Switching frequency                                                                                                | -                                                                                                 |          | 100    | KHz    |

L6208 Maximum ratings

Table 3. Thermal data

| Symbol                 | Description                                                | SO24 | PowerSO36 | Unit |

|------------------------|------------------------------------------------------------|------|-----------|------|

| R <sub>th-j-pins</sub> | Maximum thermal resistance junction pins                   | 14   | -         | °C/W |

| R <sub>th-j-case</sub> | Maximum thermal resistance junction case                   | -    | 1         | °C/W |

| R <sub>th-j-amb1</sub> | Maximum thermal resistance junction ambient <sup>(1)</sup> | 51   | -         | °C/W |

| R <sub>th-j-amb1</sub> | Maximum thermal resistance junction ambient <sup>(2)</sup> | -    | 35        | °C/W |

| R <sub>th-j-amb1</sub> | Maximum thermal resistance junction ambient <sup>(3)</sup> | -    | 15        | °C/W |

| R <sub>th-j-amb2</sub> | Maximum thermal resistance junction ambient <sup>(4)</sup> | 77   | 62        | °C/W |

- 1. Mounted on a multilayer FR4 PCB with a dissipating copper surface on the bottom side of 6  $\text{cm}^2$  (with a thickness of 35  $\mu\text{m}$ ).

- 2. Mounted on a multilayer FR4 PCB with a dissipating copper surface on the top side of 6  $\text{cm}^2$  (with a thickness of 35  $\mu\text{m}$ ).

- 3. Mounted on a multilayer FR4 PCB with a dissipating copper surface on the top side of 6 cm $^2$  (with a thickness of 35  $\mu$ m), 16 via holes and a ground layer.

- 4. Mounted on a multilayer FR4 PCB without any heat sinking surface on the board.

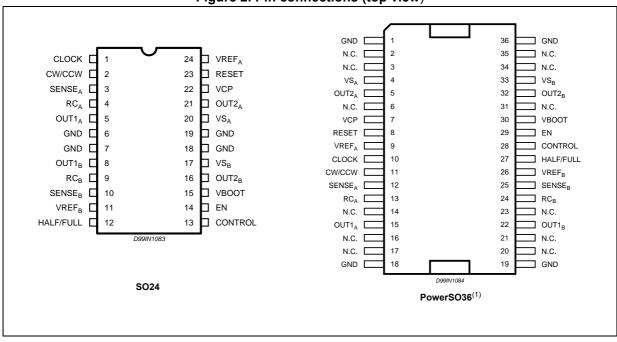

Pin connections L6208

# 3 Pin connections

Figure 2. Pin connections (top view)

1. The slug is internally connected to pins 1, 18, 19 and 36 (GND pins).

**Table 4. Pin description**

| Paci         | Package       |                   |              |                                                                                                                                                                                                 |

|--------------|---------------|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO24         | PowerSO36     | Name              | Туре         | Function                                                                                                                                                                                        |

| Pin no.      | Pin no.       |                   |              |                                                                                                                                                                                                 |

| 1            | 10            | CLOCK             | Logic input  | Step clock input. The state machine makes one step on each rising edge.                                                                                                                         |

| 2            | 11            | CW/CCW            | Logic input  | Selects the direction of the rotation. HIGH logic level sets clockwise direction, whereas LOW logic level sets counterclockwise direction.  If not used, it has to be connected to GND or +5 V. |

| 3            | 12            | SENSEA            | Power supply | Bridge A source pin. This pin must be connected to power ground through a sensing power resistor.                                                                                               |

| 4            | 13            | RC <sub>A</sub>   | RC pin       | RC network pin. A parallel RC network connected between this pin and ground sets the current controller OFF-time of the bridge A.                                                               |

| 5            | 15            | OUT1 <sub>A</sub> | Power output | Bridge A output 1.                                                                                                                                                                              |

| 6, 7, 18, 19 | 1, 18, 19, 36 | GND               | GND          | Ground terminals. In SO24 package, these pins are also used for heat dissipation toward the PCB. On PowerSO36 package the slug is connected to these pins.                                      |

L6208 Pin connections

Table 4. Pin description (continued)

| Package |           |                    |                            |                                                                                                                                                                                                                                                                                       |

|---------|-----------|--------------------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SO24    | PowerSO36 | Name               | Туре                       | Function                                                                                                                                                                                                                                                                              |

| Pin no. | Pin no.   |                    |                            |                                                                                                                                                                                                                                                                                       |

| 8       | 22        | OUT1 <sub>B</sub>  | Power output               | Bridge B output 1.                                                                                                                                                                                                                                                                    |

| 9       | 24        | RC <sub>B</sub>    | RC pin                     | RC network pin. A parallel RC network connected between this pin and ground sets the current controller OFF-time of the bridge B.                                                                                                                                                     |

| 10      | 25        | SENSE <sub>B</sub> | Power supply               | Bridge B source pin. This pin must be connected to power ground through a sensing power resistor.                                                                                                                                                                                     |

| 11      | 26        | VREFB              | Analog input               | Bridge B current controller reference voltage.  Do not leave this pin open or connected to GND.                                                                                                                                                                                       |

| 12      | 27        | HALF/FULL          | Logic input                | Step mode selector. HIGH logic level sets HALF STEP mode, LOW logic level sets FULL STEP mode. If not used, it has to be connected to GND or +5 V.                                                                                                                                    |

| 13      | 28        | CONTROL            | Logic input                | Decay mode selector. HIGH logic level sets SLOW DECAY mode. LOW logic level sets FAST DECAY mode.  If not used, it has to be connected to GND or +5 V.                                                                                                                                |

| 14      | 29        | EN                 | Logic input <sup>(1)</sup> | Chip enable. LOW logic level switches OFF all power MOSFETs of both bridge A and bridge B. This pin is also connected to the collector of the overcurrent and thermal protection to implement overcurrent protection. If not used, it has to be connected to +5 V through a resistor. |

| 15      | 30        | VBOOT              | Supply voltage             | Bootstrap voltage needed for driving the upper power MOSFETs of both bridge A and bridge B.                                                                                                                                                                                           |

| 16      | 32        | OUT2 <sub>B</sub>  | Power output               | Bridge B output 2.                                                                                                                                                                                                                                                                    |

| 17      | 33        | VS <sub>B</sub>    | Power supply               | Bridge B power supply voltage. It must be connected to the Supply Voltage together with pin VS <sub>A</sub> .                                                                                                                                                                         |

| 20      | 4         | VS <sub>A</sub>    | Power supply               | Bridge A power supply voltage. It must be connected to the supply voltage together with pin VS <sub>B</sub> .                                                                                                                                                                         |

| 21      | 5         | OUT2 <sub>A</sub>  | Power output               | Bridge A output 2.                                                                                                                                                                                                                                                                    |

| 22      | 7         | VCP                | Output                     | Charge pump oscillator output.                                                                                                                                                                                                                                                        |

| 23      | 8         | RESET              | Logic input                | Reset pin. LOW logic level restores the <i>home</i> state (state 1) on the phase sequence generator state machine.  If not used, it has to be connected to +5 V.                                                                                                                      |

| 24      | 9         | VREFA              | Analog input               | Bridge A current controller reference voltage. Do not leave this pin open or connected to GND.                                                                                                                                                                                        |

<sup>1.</sup> Also connected at the output drain of the overcurrent and thermal protection MOSFET. Therefore, it has to be driven putting in series a resistor with a value in the range of 2.2 K $\Omega$  - 180 K $\Omega$ , recommended 100 K $\Omega$ .

Electrical characteristics L6208

# 4 Electrical characteristics

Table 5. Electrical characteristics ( $T_{amb}$  = 25 °C,  $V_{s}$  = 48 V, unless otherwise specified)

| Symbol                 | Parameter                                           | Test conditions                                                     | Min.  | Тур. | Max. | Unit |

|------------------------|-----------------------------------------------------|---------------------------------------------------------------------|-------|------|------|------|

| V <sub>Sth(ON)</sub>   | Turn-on threshold                                   | -                                                                   | 6.6   | 7    | 7.4  | V    |

| V <sub>Sth(OFF)</sub>  | Turn-off threshold                                  | -                                                                   | 5.6   | 6    | 6.4  | V    |

| I <sub>S</sub>         | Quiescent supply current                            | All bridges OFF;<br>$T_j = -25 \text{ °C to } 125 \text{ °C}^{(1)}$ | -     | 5    | 10   | mA   |

| T <sub>j(OFF)</sub>    | Thermal shutdown temperature                        | -                                                                   | -     | 165  | -    | °C   |

| Output DM              | OS transistors                                      |                                                                     |       |      |      |      |

|                        | High side switch ON resistance                      | T <sub>j</sub> = 25 °C                                              | -     | 0.34 | 0.4  | W    |

| Б                      | High-side switch ON resistance                      | $T_j = 125  ^{\circ}C^{(1)}$                                        | -     | 0.53 | 0.59 | W    |

| R <sub>DS(ON)</sub>    | Low side switch ON resistance                       | T <sub>j</sub> = 25 °C                                              | -     | 0.28 | 0.34 | W    |

|                        | Low-side switch ON resistance                       | T <sub>j</sub> =125 °C <sup>(1)</sup>                               | -     | 0.47 | 0.53 | W    |

| ,                      | Lookogo gurrant                                     | EN = low; OUT = V <sub>S</sub>                                      | -     | -    | 2    | mA   |

| I <sub>DSS</sub>       | Leakage current                                     | EN = low; OUT = GND                                                 | -0.15 | -    | -    | mA   |

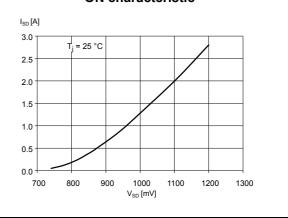

| Source dra             | in diodes                                           |                                                                     |       |      |      |      |

| V <sub>SD</sub>        | Forward ON voltage                                  | I <sub>SD</sub> = 2.8 A, EN = LOW                                   | -     | 1.15 | 1.3  | V    |

| t <sub>rr</sub>        | Reverse recovery time                               | I <sub>f</sub> = 2.8 A                                              | -     | 300  | -    | ns   |

| t <sub>fr</sub>        | Forward recovery time                               | -                                                                   | -     | 200  | -    | ns   |

| Logic inpu             | ts (EN, CONTROL, HALF/FULL, CLOCK,                  | RESET, CW/CCW)                                                      |       |      |      |      |

| V <sub>IL</sub>        | Low level logic input voltage                       | -                                                                   | -0.3  | -    | 0.8  | V    |

| V <sub>IH</sub>        | High level logic input voltage                      | -                                                                   | 2     | -    | 7    | V    |

| I <sub>IL</sub>        | Low level logic input current                       | GND logic input voltage                                             | -10   | -    | -    | μΑ   |

| I <sub>IH</sub>        | High level logic input current                      | 7 V logic input voltage                                             | -     | -    | 10   | μΑ   |

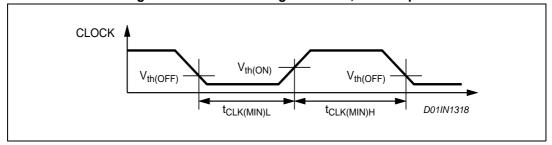

| V <sub>th(ON)</sub>    | Turn-on input threshold                             | -                                                                   | -     | 1.8  | 2.0  | V    |

| V <sub>th(OFF)</sub>   | Turn-off input threshold                            | -                                                                   | 0.8   | 1.3  | -    | ٧    |

| V <sub>th(HYS)</sub>   | Input threshold hysteresis                          | -                                                                   | 0.25  | 0.5  | -    | >    |

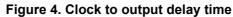

| Switching              | characteristics                                     |                                                                     |       |      |      |      |

| t <sub>D(ON)EN</sub>   | Enable to output turn-on delay time <sup>(2)</sup>  | I <sub>LOAD</sub> = 2.8 A, resistive load                           | 100   | 250  | 400  | ns   |

| t <sub>D(OFF)EN</sub>  | Enable to output turn-off delay time <sup>(2)</sup> | I <sub>LOAD</sub> = 2.8 A, resistive load                           | 300   | 550  | 800  | ns   |

| t <sub>RISE</sub>      | Output rise time <sup>(2)</sup>                     | I <sub>LOAD</sub> = 2.8 A, resistive load                           | 40    | -    | 250  | ns   |

| t <sub>FALL</sub>      | Output fall time <sup>(2)</sup>                     | I <sub>LOAD</sub> = 2.8 A, resistive load                           | 40    | -    | 250  | ns   |

| t <sub>DCLK</sub>      | Clock to output delay time <sup>(3)</sup>           | I <sub>LOAD</sub> = 2.8 A, resistive load                           | -     | 2    | -    | μs   |

| t <sub>CLK(min)L</sub> | Minimum clock time <sup>(4)</sup>                   | -                                                                   | -     | -    | 1    | μs   |

# Table 5. Electrical characteristics ( $T_{amb}$ = 25 °C, $V_s$ = 48 V, unless otherwise specified) (continued)

| Symbol                             | Parameter                                                  | Test conditions                                             | Min. | Тур. | Max. | Unit |

|------------------------------------|------------------------------------------------------------|-------------------------------------------------------------|------|------|------|------|

| t <sub>CLK(min)H</sub>             | Minimum clock time <sup>(4)</sup>                          | -                                                           | -    | -    | 1    | μs   |

| f <sub>CLK</sub>                   | Clock frequency                                            | -                                                           | -    | -    | 100  | KHz  |

| t <sub>S(MIN)</sub>                | Minimum setup time <sup>(5)</sup>                          | -                                                           | -    | -    | 1    | μs   |

| t <sub>H(MIN)</sub>                | Minimum hold time <sup>(5)</sup>                           | -                                                           | -    | -    | 1    | μs   |

| t <sub>R(MIN)</sub>                | Minimum reset time <sup>(5)</sup>                          | -                                                           | -    | -    | 1    | μs   |

| t <sub>RCLK(MIN)</sub>             | Minimum reset to clock delay time <sup>(5)</sup>           | -                                                           | -    | -    | 1    | μs   |

| t <sub>DT</sub>                    | Deadtime protection                                        |                                                             | 0.5  | 1    | -    | μs   |

| f <sub>CP</sub>                    | Charge pump frequency                                      | $T_j = -25 ^{\circ}\text{C to } 125 ^{\circ}\text{C}^{(1)}$ | -    | 0.6  | 1    | MHz  |

| PWM comp                           | parator and monostable                                     |                                                             |      |      |      |      |

| I <sub>RCA,</sub> I <sub>RCB</sub> | Source current at pins RC <sub>A</sub> and RC <sub>B</sub> | V <sub>RCA</sub> = V <sub>RCB</sub> = 2.5 V                 | 3.5  | 5.5  | -    | mA   |

| V <sub>offset</sub>                | Offset voltage on sense comparator                         | V <sub>REFA</sub> , V <sub>REFB</sub> = 0.5 V               | -    | ±5   | -    | mV   |

| t <sub>PROP</sub>                  | Turn OFF propagation delay <sup>(6)</sup>                  | -                                                           | -    | 500  | -    | ns   |

| t <sub>BLANK</sub>                 | Internal blanking time on SENSE pins                       | -                                                           | -    | 1    | -    | μs   |

| t <sub>ON(MIN)</sub>               | Minimum On time                                            | -                                                           | -    | 1.5  | 2    | μs   |

| t                                  | PWM recirculation time                                     | $R_{OFF}$ = 20 K $\Omega$ ; $C_{OFF}$ = 1 nF                | -    | 13   | -    | μs   |

| t <sub>OFF</sub>                   | 1 WWW recirculation time                                   | $R_{OFF}$ = 100 KΩ; $C_{OFF}$ = 1 nF                        | -    | 61   | -    | μs   |

| I <sub>BIAS</sub>                  | Input bias current at pins $VREF_A$ and $VREF_B$           | -                                                           | -    | -    | 10   | μA   |

| Overcurrer                         | nt protection                                              |                                                             |      |      |      |      |

| I <sub>SOVER</sub>                 | Input supply overcurrent protection threshold              | $T_j = -25 ^{\circ}\text{C to } 125 ^{\circ}\text{C}^{(1)}$ | 4    | 5.6  | 7.1  | Α    |

| R <sub>OPDR</sub>                  | Open drain ON resistance                                   | I = 4 mA                                                    | -    | 40   | 60   | W    |

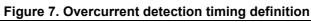

| t <sub>OCD(ON)</sub>               | OCD turn-on delay time <sup>(7)</sup>                      | I = 4 mA; C <sub>EN</sub> < 100 pF                          | -    | 200  | -    | ns   |

| t <sub>OCD(OFF)</sub>              | OCD turn-off delay time <sup>(7)</sup>                     | I = 4 mA; C <sub>EN</sub> < 100 pF                          | -    | 100  | -    | ns   |

- 1. Tested at 25 °C in a restricted range and guaranteed by characterization.

- 2. See Figure 3: Switching characteristic definition.

- 3. See Figure 4: Clock to output delay time.

- 4. See Figure 5: Minimum timing definition; clock input.

- 5. See Figure 6: Minimum timing definition; logic inputs.

- 6. Measured applying a voltage of 1 V to pin SENSE and a voltage drop from 2 V to 0 V to pin VREF.

- 7. See Figure 7: Overcurrent detection timing definition.

Electrical characteristics L6208

V<sub>th(OFF)</sub>

IOUT

90%

D01IN1316

t<sub>D(OFF)EN</sub>

t<sub>D(ON)EN</sub>

t<sub>RISE</sub>

Figure 3. Switching characteristic definition

Figure 5. Minimum timing definition; clock input

CLOCK

Vth(ON)

LOGIC INPUTS

ts(MIN)

th(MIN)

D01IN1319

Figure 6. Minimum timing definition; logic inputs

Circuit description L6208

# 5 Circuit description

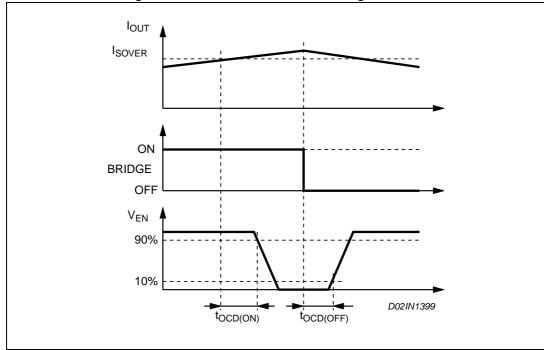

### 5.1 Power stages and charge pump

The L6208 integrates two independent power MOS full bridges. Each power MOS has an  $R_{\text{DS(ON)}}$  = 0.3  $\Omega$  (typical value at 25 °C), with intrinsic fast freewheeling diode. Switching patterns are generated by the PWM current controller and the phase sequence generator (see *Section 6: PWM current control*). Cross conduction protection is achieved using a deadtime ( $t_{\text{DT}}$  = 1  $\mu s$  typical value) between the switch off and switch on of two power MOSFETs in one leg of a bridge.

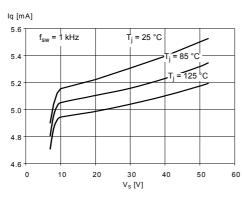

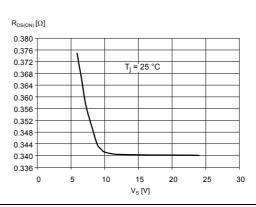

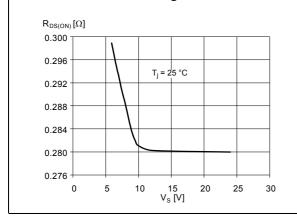

Pins  $VS_A$  and  $VS_B$  MUST be connected together to the supply voltage  $V_S$ . The device operates with a supply voltage in the range from 8 V to 52 V. It has to be noticed that the  $R_{DS(ON)}$  increases of some percents when the supply voltage is in the range from 8 V to 12 V (see *Figure 37: Typical low-side RDS(ON) vs. supply voltage on page 29* and *Figure 34: Typical high-side R\_{DS(ON)} vs. supply voltage on page 29*).

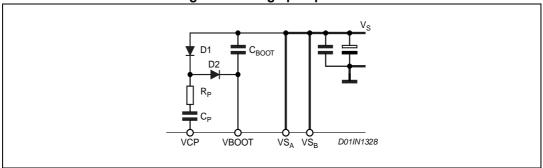

Using N-channel power MOS for the upper transistors in the bridge requires a gate drive voltage above the power supply voltage. The bootstrapped supply voltage  $V_{\text{BOOT}}$  is obtained through an internal oscillator and few external components to realize a charge pump circuit as shown in *Figure 8*. The oscillator output (VCP) is a square wave at 600 KHz (typical) with 10 V amplitude. Recommended values/part numbers for the charge pump circuit are shown in *Table 6*.

Component

Value

$C_{BOOT}$  220 nF

$C_P$  10 nF

$R_P$  100 Ω

D1

1N4148

D2

1N4148

Table 6. Charge pump external components values

12/34 DocID7514 Rev 3

L6208 Circuit description

## 5.2 Logic inputs

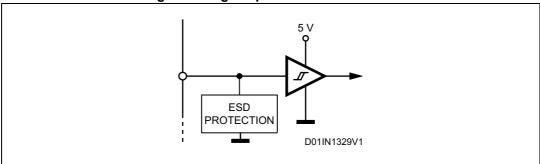

Pins CONTROL, HALF/FULL, CLOCK, RESET and CW/CCW are TTL/CMOS compatible logic inputs. The internal structure is shown in *Figure 9*. Typical value for turn-on and turn-off thresholds are respectively  $V_{th(ON)}$  = 1.8 V and  $V_{th(OFF)}$  = 1.3 V.

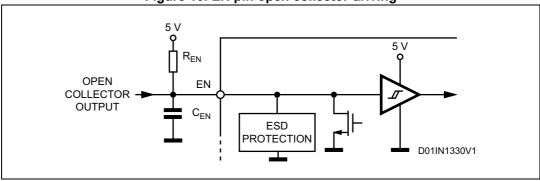

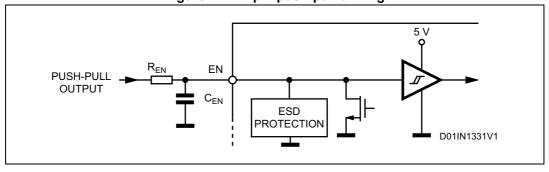

Pin EN ("Enable") has identical input structure with the exception that the drain of the overcurrent and thermal protection MOSFET is also connected to this pin. Due to this connection some care needs to be taken in driving this pin. The EN input may be driven in one of two configurations as shown in *Figure 10* or *Figure 11*. If driven by an open drain (collector) structure, a pull-up resistor  $R_{EN}$  and a capacitor  $C_{EN}$  are connected as shown in *Figure 10*. If the driver is a standard Push-Pull structure the resistor  $R_{EN}$  and the capacitor  $C_{EN}$  are connected as shown in *Figure 11*. The resistor  $R_{EN}$  should be chosen in the range from 2.2 K $\Omega$  to 180 K $\Omega$ . Recommended values for  $R_{EN}$  and  $C_{EN}$  are respectively 100 K $\Omega$  and 5.6 nF. More information on selecting the values is found in *Section 7.5: Non-dissipative overcurrent protection on page 21*.

Figure 9. Logic inputs internal structure

Figure 10. EN pin open collector driving

Figure 11. EN pin push-pull driving

PWM current control L6208

### 6 PWM current control

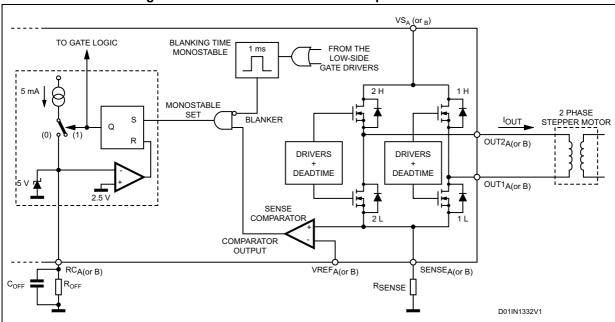

The L6208 device includes a constant off time PWM current controller for each of the two bridges. The current control circuit senses the bridge current by sensing the voltage drop across an external sense resistor connected between the source of the two lower power MOS transistors and ground, as shown in *Figure 12*. As the current in the motor builds up the voltage across the sense resistor increases proportionally. When the voltage drop across the sense resistor becomes greater than the voltage at the reference input (VREF<sub>A</sub> or VREF<sub>B</sub>) the sense comparator triggers the monostable switching the bridge off. The power MOS remains off for the time set by the monostable and the motor current recirculates as defined by the selected decay mode, described in *Section 7: Decay modes on page 18*. When the monostable times out the bridge will again turn on. Since the internal deadtime, used to prevent cross conduction in the bridge, delays the turn on of the power MOS, the effective off time is the sum of the monostable time plus the deadtime.

Figure 12. PWM current controller simplified schematic

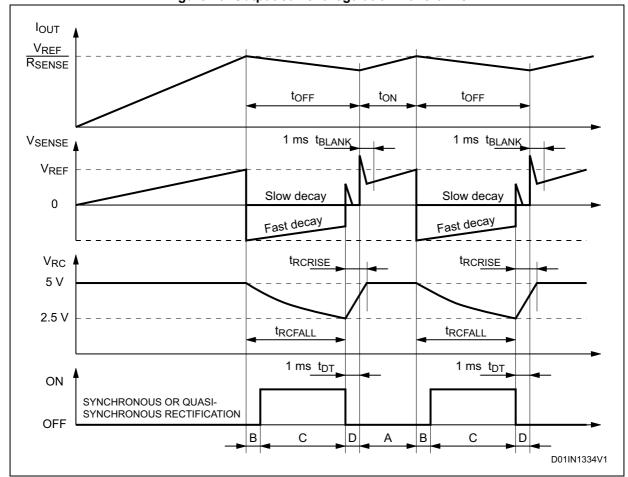

Figure 13 shows the typical operating waveforms of the output current, the voltage drop across the sensing resistor, the RC pin voltage and the status of the bridge. More details regarding the synchronous rectification and the output stage configuration are included in Section 7: Decay modes on page 18.

Immediately after the power MOS turns on, a high peak current flows through the sensing resistor due to the reverse recovery of the freewheeling diodes. The L6208 device provides a 1  $\mu$ s blanking time  $t_{BLANK}$  that inhibits the comparator output so that this current spike cannot prematurely retrigger the monostable.

14/34 DocID7514 Rev 3

L6208 PWM current control

Figure 13. Output current regulation waveforms

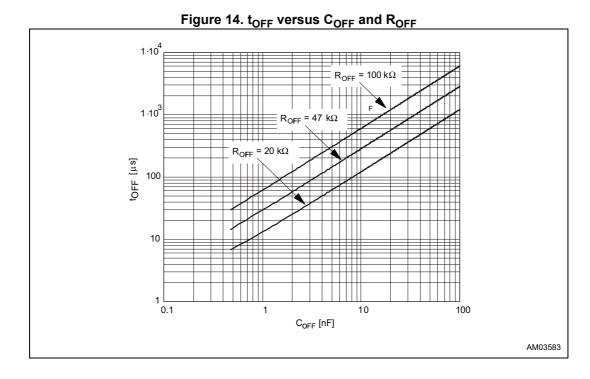

*Figure 14* shows the magnitude of the Off time  $t_{OFF}$  versus  $C_{OFF}$  and  $R_{OFF}$  values. It can be approximately calculated from the equations:

### **Equation 1**

$$t_{\mathsf{RCFALL}} = 0.6 \cdot \mathsf{R}_{\mathsf{OFF}} \cdot \mathsf{C}_{\mathsf{OFF}}$$

$$t_{\mathsf{OFF}} = t_{\mathsf{RCFALL}} + t_{\mathsf{DT}} = 0.6 \cdot \mathsf{R}_{\mathsf{OFF}} \cdot \mathsf{C}_{\mathsf{OFF}} + t_{\mathsf{DT}}$$

where  $R_{OFF}$  and  $C_{OFF}$  are the external component values and  $t_{DT}$  is the internally generated deadtime with:

#### **Equation 2**

20 KΩ

$$\leq$$

R<sub>OFF</sub>  $\leq$  100 KΩ

0.47 nF  $\leq$  C<sub>OFF</sub>  $\leq$  100 nF

t<sub>DT</sub> = 1 μs (typical value)

PWM current control L6208

Therefore:

#### **Equation 3**

$$t_{OFF(MIN)} = 6.6 \mu s$$

$t_{OFF(MAX)} = 6 ms$

These values allow a sufficient range of t<sub>OFF</sub> to implement the drive circuit for most motors.

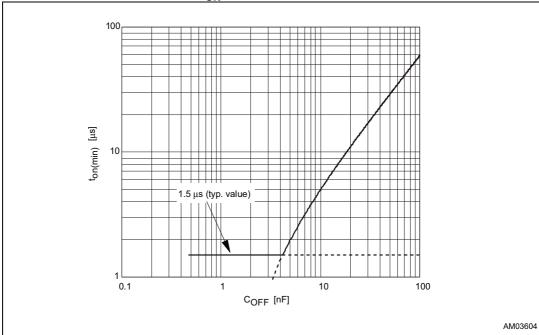

The capacitor value chosen for  $C_{OFF}$  also affects the rise time  $t_{RCRISE}$  of the voltage at the pin RCOFF. The rise time  $t_{RCRISE}$  will only be an issue if the capacitor is not completely charged before the next time the monostable is triggered. Therefore, the on time  $t_{ON}$ , which depends by motors and supply parameters, has to be bigger than  $t_{RCRISE}$  for allowing a good current regulation by the PWM stage. Furthermore, the on time  $t_{ON}$  can not be smaller than the minimum on time  $t_{ON(MIN)}$ .

#### **Equation 4**

$$\begin{cases} t_{ON} > t_{ON(MIN)} = 1.5 \mu s \text{ (typ. value)} \\ t_{ON} > t_{RCRISE} - t_{DT} \end{cases}$$

$$t_{RCRISE} = 600 \cdot C_{OFF}$$

Figure 15 shows the lower limit for the on time  $t_{ON}$  for having a good PWM current regulation capacity. It has to be said that  $t_{ON}$  is always bigger than  $t_{ON(MIN)}$  because the device imposes this condition, but it can be smaller than  $t_{RCRISE}$  -  $t_{DT}$ . In this last case the device continues to work but the off time  $t_{OFF}$  is not more constant.

So, small  $C_{\mathsf{OFF}}$  value gives more flexibility for the applications (allows smaller on time and, therefore, higher switching frequency), but, the smaller is the value for  $C_{\mathsf{OFF}}$ , the more influential will be the noises on the circuit performance.

L6208 PWM current control

Figure 15. Area where  $t_{\mbox{\scriptsize ON}}$  can vary maintaining the PWM regulation

L6208 **Decay modes**

#### 7 **Decay modes**

The CONTROL input is used to select the behavior of the bridge during the off time. When the CONTROL pin is low, the fast decay mode is selected and both transistors in the bridge are switched off during the off time. When the CONTROL pin is high, the slow decay mode is selected and only the low-side transistor of the bridge is switched off during the off time.

Figure 16 shows the operation of the bridge in the fast decay mode. At the start of the off time, both of the power MOS are switched off and the current recirculates through the two opposite freewheeling diodes. The current decays with a high di/dt since the voltage across the coil is essentially the power supply voltage. After the deadtime, the lower power MOS in parallel with the conducting diode is turned on in synchronous rectification mode. In applications where the motor current is low it is possible that the current can decay completely to zero during the off time. At this point if both of the power MOS were operating in the synchronous rectification mode, it would then be possible for the current to build in the opposite direction. To prevent this only the lower power MOS is operated in synchronous rectification mode. This operation is called "Quasi-synchronous rectification mode". When the monostable times out, the power MOS are turned on again after some delay set by the deadtime to prevent cross conduction.

Figure 17 shows the operation of the bridge in the slow decay mode. At the start of the off time, the lower power MOS is switched off and the current recirculates around the upper half of the bridge. Since the voltage across the coil is low, the current decays slowly. After the deadtime the upper power MOS is operated in the synchronous rectification mode. When the monostable times out, the lower power MOS is turned on again after some delay set by the deadtime to prevent cross conduction.

B) 1 μs DEADTIME C) QUASI-SYNCHRONOUS RECTIFICATION D) 1 μs SLOW DECAY A) ON TIME D01IN1335V1

Figure 16. Fast decay mode output stage configurations

Figure 17. Slow decay mode output stage configurations A) ON TIME B) 1  $\mu$ s DEADTIME C) SYNCHRONOUS RECTIFICATION D) 1 μs DEADTIME D01IN1336V1

L6208 Decay modes

### 7.1 Stepping sequence generation

The phase sequence generator is a state machine that provides the phase and enable inputs for the two bridges to drive a stepper motor in either full step or half step. Two full step modes are possible, the normal drive mode where both phases are energized each step and the wave drive mode where only one phase is energized at a time. The drive mode is selected by the HALF/FULL input and the current state of the sequence generator as described below. A rising edge of the CLOCK input advances the state machine to the next state. The direction of rotation is set by the CW/CCW input. The RESET input resets the state machine to state.

### 7.2 Half step mode

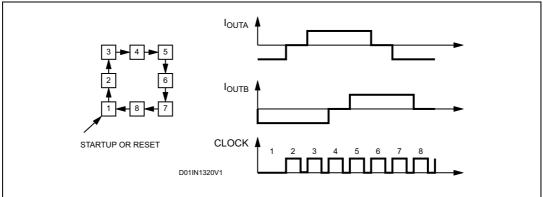

A HIGH logic level on the HALF/FULL input selects half step mode. *Figure 18* shows the motor current waveforms and the state diagram for the phase sequencer generator. At startup or after a RESET the phase sequencer is at state 1. After each clock pulse the state changes following the sequence 1, 2, 3, 4, 5, 6, 7, 8, etc. if CW/CCW is high (clockwise movement) or 1, 8, 7, 6, 5, 4, 3, 2, etc. if CW/CCW is low (counterclockwise movement).

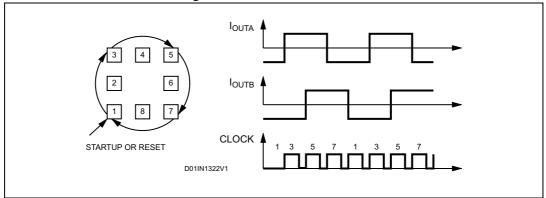

### 7.3 Normal drive mode (full step two phase on)

A LOW level on the HALF/FULL input selects the full step mode. When the low level is applied when the state machine is at an ODD numbered state the normal drive mode is selected. *Figure 19* shows the motor current waveform state diagram for the state machine of the phase sequencer generator. The normal drive mode can easily be selected by holding the HALF/FULL input low and applying a RESET. At startup or after a RESET the state machine is in state 1. While the HALF/FULL input is kept low, state changes following the sequence 1, 3, 5, 7, etc. if CW/CCW is high (clockwise movement) or 1, 7, 5, 3, etc. if CW/CCW is low (counterclockwise movement).

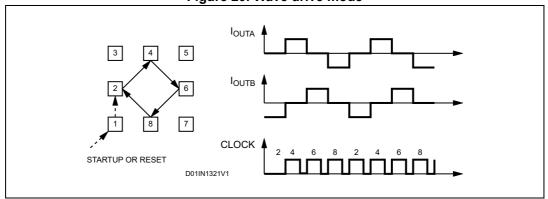

## 7.4 Wave drive mode (full step one phase on)

A LOW level on the pin HALF/FULL input selects the full step mode. When the low level is applied when the state machine is at an EVEN numbered state the wave drive mode is selected. *Figure 20* shows the motor current waveform and the state diagram for the state machine of the phase sequence generator. To enter the wave drive mode the state machine must be in an EVEN numbered state. The most direct method to select the wave drive mode is to first apply a RESET, then while keeping the HALF/FULL input high apply one pulse to the clock input then take the HALF/FULL input low. This sequence first forces the state machine to state 1. The clock pulse, with the HALF/FULL input high advances the state machine from state 1 to either state 2 or 8 depending on the CW/CCW input. Starting from this point, after each clock pulse (rising edge) will advance the state machine following the sequence 2, 4, 6, 8, etc. if CW/CCW is high (clockwise movement) or 8, 6, 4, 2, etc. if CW/CCW is low (counterclockwise movement).

Decay modes L6208

Figure 18. Half step mode

Figure 19. Normal drive mode

Figure 20. Wave drive mode

L6208 Decay modes

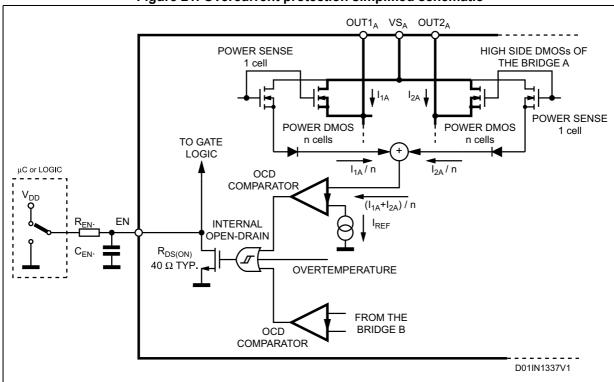

### 7.5 Non-dissipative overcurrent protection

The L6208 device integrates an "Overcurrent Detection" circuit (OCD). This circuit provides protection against a short-circuit to ground or between two phases of the bridge. With this internal overcurrent detection, the external current sense resistor normally used and its associated power dissipation are eliminated. *Figure 21* shows a simplified schematic of the overcurrent detection circuit.

To implement the overcurrent detection, a sensing element that delivers a small but precise fraction of the output current is implemented with each high-side power MOS. Since this current is a small fraction of the output current there is very little additional power dissipation. This current is compared with an internal reference current  $I_{REF}$ . When the output current reaches the detection threshold (typically 5.6 A), the OCD comparator signals a fault condition. When a fault condition is detected, the EN pin is pulled below the turn off threshold (1.3 V typical) by an internal open drain MOS with a pull down capability of 4 mA. By using an external R-C on the EN pin, the off time before recovering normal operation can be easily programmed by means of the accurate thresholds of the logic inputs.

Figure 21. Overcurrent protection simplified schematic

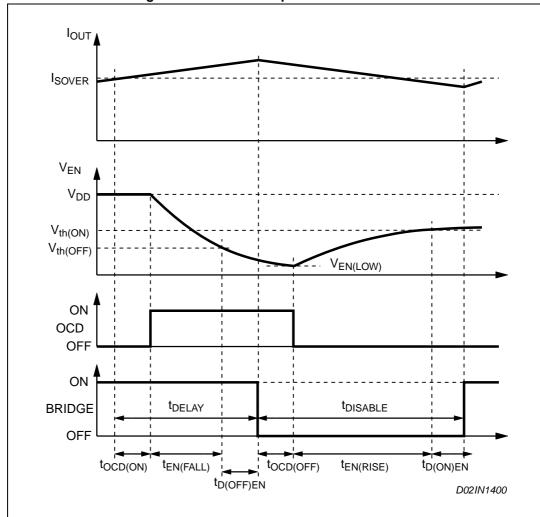

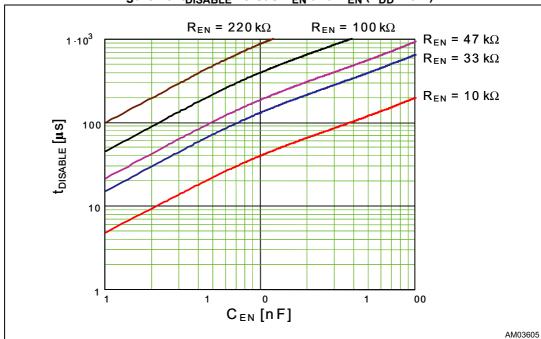

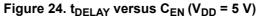

Figure 22 shows the overcurrent detection operation. The disable time  $t_{DISABLE}$  before recovering normal operation can be easily programmed by means of the accurate thresholds of the logic inputs. It is affected whether by  $C_{EN}$  and  $R_{EN}$  values and its magnitude is reported in Figure 23. The delay time  $t_{DELAY}$  before turning off the bridge when an overcurrent has been detected depends only by  $C_{EN}$  value. Its magnitude is reported in Figure 24.

$C_{\text{EN}}$  is also used for providing immunity to the pin EN against fast transient noises. Therefore the value of  $C_{\text{EN}}$  should be chosen as big as possible according to the maximum

DocID7514 Rev 3 21/34

Decay modes L6208

tolerable delay time and the  $R_{\text{EN}}$  value should be chosen according to the desired disable time

The resistor  $R_{EN}$  should be chosen in the range from 2.2 K $\Omega$  to 180 K $\Omega$ . Recommended values for  $R_{EN}$  and  $C_{EN}$  are respectively 100 K $\Omega$  and 5.6 nF that allow obtaining 200  $\mu s$  disable time.

Figure 22. Overcurrent protection waveforms

L6208 Decay modes

Figure 23.  $t_{DISABLE}$  versus  $C_{EN}$  and  $R_{EN}$  ( $V_{DD}$  = 5 V)

# 7.6 Thermal protection

In addition to the overcurrent protection, the L6208 device integrates a thermal protection for preventing the device destruction in case of junction overtemperature. It works sensing the die temperature by means of a sensible element integrated in the die. The device switches-off when the junction temperature reaches 165 °C (typ. value) with 15 °C hysteresis (typ. value).

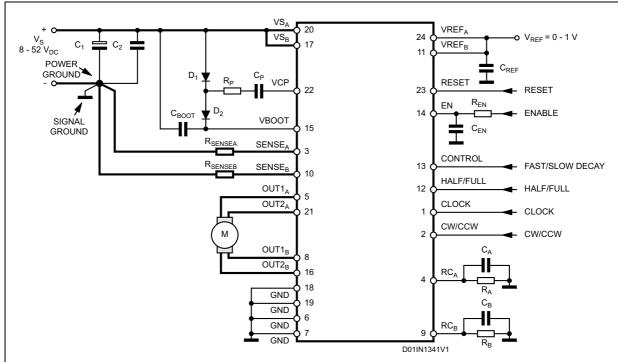

# 8 Application information

A typical bipolar stepper motor driver application using the L6208 device is shown in *Figure 25*. Typical component values for the application are shown in *Table 7*. A high quality ceramic capacitor in the range of 100 to 200 nF should be placed between the power pins ( $VS_A$  and  $VS_B$ ) and ground near the L6208 to improve the high frequency filtering on the power supply and reduce high frequency transients generated by the switching. The capacitor connected from the EN input to ground sets the shutdown time when an overcurrent is detected (see *Section 7.5: Non-dissipative overcurrent protection*. The two current sensing inputs ( $SENSE_A$  and  $SENSE_B$ ) should be connected to the sensing resistors with a trace length as short as possible in the layout. The sense resistors should be non-inductive resistors to minimize the di/dt transients across the resistor. To increase noise immunity, unused logic pins (except EN) are best connected to 5 V (high logic level) or GND (low logic level) (see *Table 4: Pin description on page 6*). It is recommended to keep power ground and signal ground separated on the PCB.

Table 7. Component values for typical application

| Component         | Value  | Component           | Value  |

|-------------------|--------|---------------------|--------|

| C <sub>1</sub>    | 100 μF | D <sub>1</sub>      | 1N4148 |

| C <sub>2</sub>    | 100 nF | D <sub>2</sub>      | 1N4148 |

| C <sub>A</sub>    | 1 nF   | R <sub>A</sub>      | 39 ΚΩ  |

| C <sub>B</sub>    | 1 nF   | R <sub>B</sub>      | 39 ΚΩ  |

| C <sub>BOOT</sub> | 220 nF | R <sub>EN</sub>     | 100 ΚΩ |

| C <sub>P</sub>    | 10 nF  | R <sub>P</sub>      | 100 Ω  |

| C <sub>EN</sub>   | 5.6 nF | R <sub>SENSEA</sub> | 0.3 Ω  |

| C <sub>REF</sub>  | 68 nF  | R <sub>SENSEB</sub> | 0.3 Ω  |

24/34 DocID7514 Rev 3

Figure 25. Typical application

### 8.1 Output current capability and IC power dissipation

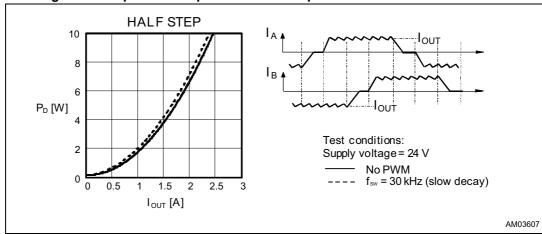

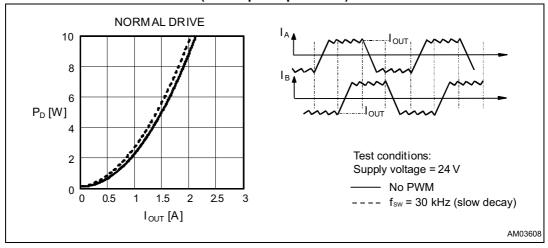

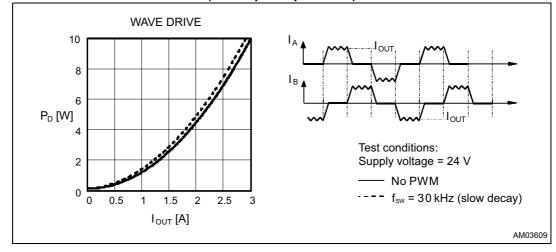

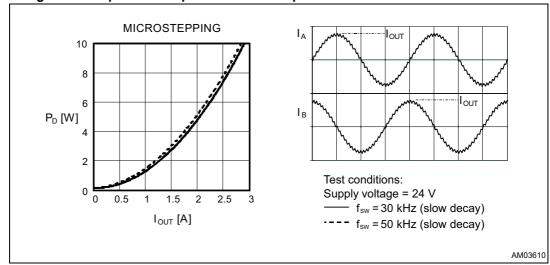

In *Figure 26*, *27*, *28* and *29* are shown the approximate relation between the output current and the IC power dissipation using PWM current control driving a two phase stepper motor, for different driving sequences:

- HALF STEP mode (*Figure 26*) in which alternately one phase / two phases are energized.

- NORMAL DRIVE (FULL STEP TWO PHASE ON) mode (Figure 27) in which two

phases are energized during each step.

- WAVE DRIVE (FULL STEP ONE PHASE ON) mode (Figure 28) in which only one phase is energized at each step.

- MICROSTEPPING mode (Figure 29), in which the current follows a sine wave profile, provided through the V<sub>ref</sub> pins.

For a given output current and driving sequence the power dissipated by the IC can be easily evaluated, in order to establish which package should be used and how large must be the on-board copper dissipating area to guarantee a safe operating junction temperature (125 °C maximum).

Figure 26. IC power dissipation versus output current in HALF STEP mode

Figure 27. IC power dissipation versus output current in NORMAL mode (full step two phase on)

Figure 28. IC power dissipation versus output current in WAVE mode (full step one phase on)

26/34 DocID7514 Rev 3

Figure 29. IC power dissipation versus output current in MICROSTEPPING mode

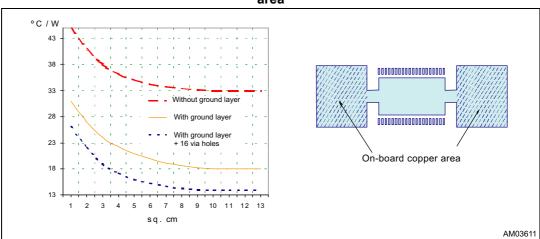

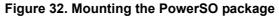

### 8.2 Thermal management

In most applications the power dissipation in the IC is the main factor that sets the maximum current that can be delivered by the device in a safe operating condition. Therefore, it has to be taken into account very carefully. Besides the available space on the PCB, the right package should be chosen considering the power dissipation. Heat sinking can be achieved using copper on the PCB with proper area and thickness. *Figure 30* and *31* show the junction to ambient thermal resistance values for the PowerSO36 and SO24 packages.

For instance, using a PowerSO package with a copper slug soldered on a 1.5 mm copper thickness FR4 board with a 6 cm² dissipating footprint (copper thickness of 35  $\mu$ m), the R<sub>th(j-amb)</sub> is about 35 °C/W. *Figure 32* shows mounting methods for this package. Using a multilayer board with vias to a ground plane, thermal impedance can be reduced down to 15 °C/W.

Figure 30. PowerSO36 junction ambient thermal resistance versus on-board copper area

5

\*\*C /W 68 66 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 64 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60 62 60

Figure 31. SO24 junction ambient thermal resistance versus on-board copper area

Figure 33. Typical quiescent current vs. supply | Figure 34. Typical high-side R<sub>DS(ON)</sub> vs. supply voltage

voltage

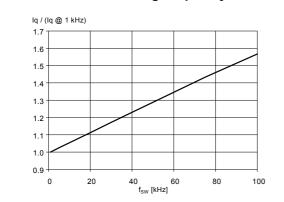

Figure 35. Normalized typical quiescent current vs. switching frequency

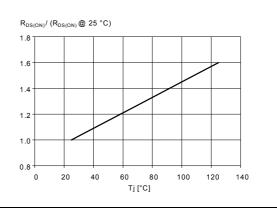

Figure 36. Normalized R<sub>DS(ON)</sub> vs. junction temperature (typical value)

Figure 37. Typical low-side R<sub>DS(ON)</sub> vs. supply voltage

Figure 38. Typical drain-source diode forward **ON** characteristic

Package information L6208

# 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: <a href="www.st.com">www.st.com</a>. ECOPACK is an ST trademark.

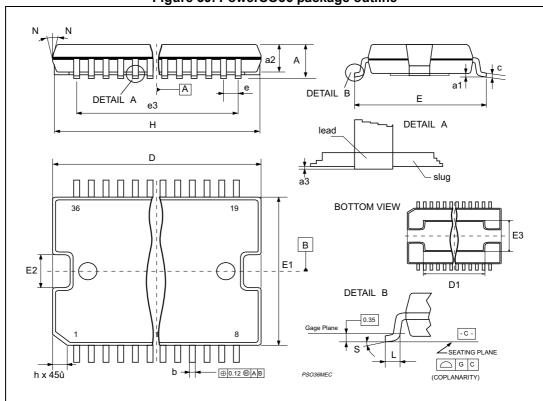

# 9.1 PowerSO36 package information

Figure 39. PowerSO36 package outline

L6208 Package information

Table 8. PowerSO36 package mechanical data

|                   | Dimensions |       |       |       |        |       |  |  |

|-------------------|------------|-------|-------|-------|--------|-------|--|--|

| Symbol            | mm         |       |       | inch  |        |       |  |  |

|                   | Min.       | Тур.  | Max.  | Min.  | Тур.   | Max.  |  |  |

| Α                 | -          | -     | 3.60  | -     | -      | 0.141 |  |  |

| a1                | 0.10       | -     | 0.30  | 0.004 | -      | 0.012 |  |  |

| a2                | -          | -     | 3.30  |       | -      | 0.130 |  |  |

| a3                | 0          | -     | 0.10  | 0     | -      | 0.004 |  |  |

| b                 | 0.22       | -     | 0.38  | 0.008 | -      | 0.015 |  |  |

| С                 | 0.23       | -     | 0.32  | 0.009 | -      | 0.012 |  |  |

| D <sup>(1)</sup>  | 15.80      | -     | 16.00 | 0.622 | -      | 0.630 |  |  |

| D1                | 9.40       | -     | 9.80  | 0.370 | -      | 0.385 |  |  |

| E                 | 13.90      | -     | 14.50 | 0.547 | -      | 0.570 |  |  |

| е                 | -          | 0.65  | -     | -     | 0.0256 | -     |  |  |

| e3                | -          | 11.05 | -     | -     | 0.435  | -     |  |  |

| E1 <sup>(1)</sup> | 10.90      | -     | 11.10 | 0.429 | -      | 0.437 |  |  |

| E2                | -          | -     | 2.90  | -     | -      | 0.114 |  |  |

| E3                | 5.80       | -     | 6.20  | 0.228 | -      | 0.244 |  |  |

| E4                | 2.90       | -     | 3.20  | 0.114 | -      | 0.126 |  |  |

| G                 | 0          | -     | 0.10  | 0     | -      | 0.004 |  |  |

| Н                 | 15.50      | -     | 15.90 | 0.610 | -      | 0.626 |  |  |

| h                 | -          | -     | 1.10  | -     | -      | 0.043 |  |  |

| L                 | 0.80       | -     | 1.10  | 0.031 | -      | 0.043 |  |  |

| N                 |            | •     | 10° ( | max.) | •      |       |  |  |

| S                 | 8° (max.)  |       |       |       |        |       |  |  |

<sup>1. &</sup>quot;D" and "E1" do not include mold flash or protrusions.

<sup>-</sup> Mold flash or protrusions shall not exceed 0.15 mm (0.006 inch).

<sup>-</sup> Critical dimensions are "a3", "E" and "G".

Package information L6208

# 9.2 SO24 package information

D hx45'

Add C

SEATING PLANE

C 0,25 mm

GAGE PLANE

12

0070769 C

Figure 40. SO24 package outline

Table 9. SO24 package mechanical data

|                  | Dimensions (mm)      |      |       | Dimensions (inch) |       |       |

|------------------|----------------------|------|-------|-------------------|-------|-------|

| Symbol           | Min.                 | Тур. | Max.  | Min.              | Тур.  | Max.  |

| Α                | 2.35                 | -    | 2.65  | 0.093             | -     | 0.104 |

| A1               | 0.10                 | -    | 0.30  | 0.004             | -     | 0.012 |

| В                | 0.33                 | -    | 0.51  | 0.013             | -     | 0.020 |

| С                | 0.23                 | -    | 0.32  | 0.009             | -     | 0.013 |

| D <sup>(1)</sup> | 15.20                | -    | 15.60 | 0.598             | -     | 0.614 |

| E                | 7.40                 | -    | 7.60  | 0.291             | -     | 0.299 |

| е                | -                    | 1.27 | -     | -                 | 0.050 | -     |

| Н                | 10.0                 | -    | 10.65 | 0.394             | -     | 0.419 |

| h                | 0.25                 | -    | 0.75  | 0.010             | -     | 0.030 |

| L                | 0.40                 | -    | 1.27  | 0.016             | -     | 0.050 |

| k                | 0° (min.), 8° (max.) |      |       |                   |       |       |

| ddd              | -                    | -    | 0.10  | -                 | -     | 0.004 |

<sup>&</sup>quot;D" dimension does not include mold flash, protrusions or gate burrs. Mold flash, protrusions or gate burrs shall not exceed 0.15 mm per side.

32/34 DocID7514 Rev 3

L6208 Revision history

# 10 Revision history

Table 10. Document revision history

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 03-Sep-2003 | 1        | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20-Feb-2014 | 2        | Updated Section: Description on page 1 (removed "MultiPower-" from "MultiPower-BCD technology").  Added Contents on page 2.  Updated Section 1: Block diagram (added section title, numbered and moved Figure 1: Block diagram from page 1 to page 3).  Added title to Section 2: Maximum ratings on page 4, added numbers and titles from Table 1: Absolute maximum ratings to Table 3: Thermal data.  Added title to Section 3: Pin connections on page 6, added number and title to Figure 2: Pin connections (top view), renumbered note 1 below Figure 2, added title to Table 4: Pin description, renumbered note 1 below Table 4.  Added title to Section 4: Electrical characteristics on page 8, added title and number to Table 5, renumbered notes 1 to 7 below Table 5.  Renumbered Figure 3 to Figure 7.  Added section numbers to Section 5: Circuit description on page 12, Section 5.1 and Section 5.2. Removed "and uC" from first sentence in Section 5.2. Renumbered Table 6, added header to Table 6.  Renumbered Figure 8 to Figure 11.  Added numbers to Section 6: PWM current control on page 14.  Renumbered Figure 12 to Figure 15. Added titles to Equation 1: on page 15 till Equation 4: on page 16.  Added section numbers to Section 7: Decay modes on page 18 and Section 7.1 to Section 7.6 on page 23). Renumbered Figure 16 to Figure 24.  Added section numbers to Section 8: Application information on page 24, Section 8.1 and Section 8: Application information on page 24, Section 8.1 and Section 8: Application information on page 24, Section 8.1 and Section 8: Application information on page 24, Section 8.1 and Section 8: Application information on page 24, Section 8.1 and Section 8: Application information on page 24, Section 8.1 and Section 8: Application information on page 30 (added main title and ECOPACK text. Added titles from Table 8: PowerSO36 package mechanical data and from Figure 40: PowerSO36 package outline to Figure 42: SO24 package outline, reversed order of named tables and figures. Removed 3D figures of packages, replaced 0.200 b |

| 03-Oct-2018 | 3        | Removed "T <sub>j</sub> " from <i>Table 2 on page 4</i> .  Minor modifications throughout document.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2018 STMicroelectronics - All rights reserved

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.