# RENESAS

# DATASHEET

# ISL62870 PWM DC/DC Voltage Regulator Controller

The ISL62870 IC is a Single-Phase Synchronous-Buck PWM voltage regulator featuring Intersil's Robust Ripple Regulator (R<sup>3</sup>) Technology™. The ISL62870 provides a low cost solution for compact high performance applications.The wide 3.3V to 25V input voltage range is ideal for systems that run on battery or AC adapter power sources. Resistor programmed output voltage setpoint and capacitor programmed soft-start delay allow for fast and easy implementation. Robust integrated MOSFET drivers and Schottky bootstrap diode reduce the implementation area and lower component cost.

Intersil's R<sup>3</sup> Technology<sup>™</sup> combines the best features of both fixed-frequency and hysteretic PWM control. The PWM frequency is 300kHz during static operation, becoming variable during changes in load, setpoint voltage, and input voltage when changing between battery and AC adapter power. The modulators ability to change the PWM switching frequency during these events in conjunction with external loop compensation produces superior transient response. For maximum efficiency, the converter automatically enters diode-emulation mode (DEM) during light-load conditions such as system standby.

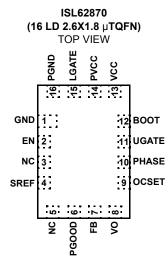

# Pinout

# **Ordering Information**

FN6708 Rev 0.00 August 14, 2008

## Features

- Input Voltage Range: 3.3V to 25V

- Output Voltage Range: 0.5V to 3.3V

- Output Load to 30A

- · Simple Resistor Programming for Output Voltage

- ±0.75% System Accuracy: -10°C to +100°C

- · Capacitor Programming for Soft-Start Delay

- Fixed 300kHz PWM Frequency in Continuous Conduction

- External Compensation Affords Optimum Control Loop Tuning

- · Automatic Diode Emulation Mode for Highest Efficiency

- Integrated High-Current MOSFET Drivers and Schottky Boot-Strap Diode for Optimal Efficiency

- Choice of Overcurrent Detection Schemes

- Lossless Inductor DCR Current Sensing

- Precision Resistive Current Sensing

- · Power-Good Monitor for Soft-Start and Fault Detection

- Fault Protection

- Undervoltage

- Overvoltage

- Overcurrent (DCR-Sense or Resistive-Sense Capability)

- Over-Temperature Protection

- Fault Identification by PGOOD Pull-Down Resistance

- Pb-Free (RoHS Compliant)

## Applications

- Mobile PC Graphical Processing Unit VCC Rail

- Mobile PC I/O Controller Hub (ICH) VCC Rail

- Mobile PC Memory Controller Hub (GMCH) VCC Rail

| PART NUMBER<br>(Note) | PART<br>MARKING | TEMP RANGE<br>(°C) | PACKAGE<br>(Pb-Free) | PKG.<br>DWG. # |

|-----------------------|-----------------|--------------------|----------------------|----------------|

| ISL62870HRUZ          | GAL             | -10 to +100        | 16 Ld 2.6x1.8 µTQFN  | L16.2.6x1.8A   |

| ISL62870HRUZ-T*       | GAL             | -10 to +100        | 16 Ld 2.6x1.8 µTQFN  | L16.2.6x1.8A   |

\*Please refer to TB347 for details on reel specifications.

NOTE: These Intersil Pb-free plastic packaged products employ special Pb-free material sets; molding compounds/die attach materials and NiPdAu plate - e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations. Intersil Pb-free products are MSL classified at Pb-free peak reflow temperatures that meet or exceed the Pb-free requirements of IPC/JEDEC J STD-020.

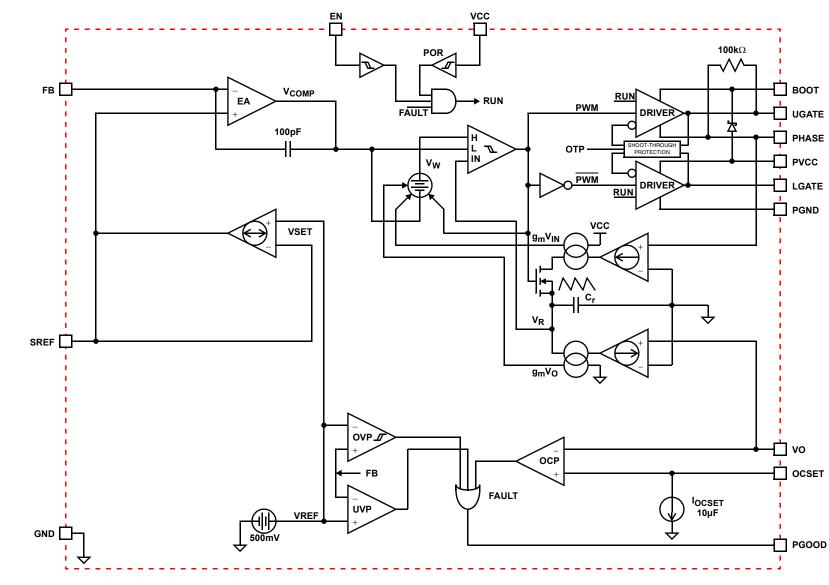

**Block Diagram**

FIGURE 1. SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM OF ISL62870

ISL62870

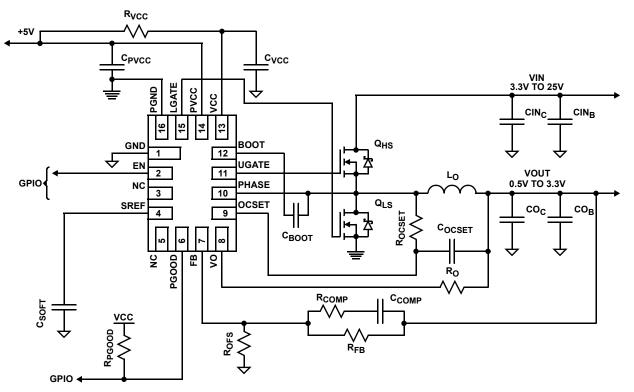

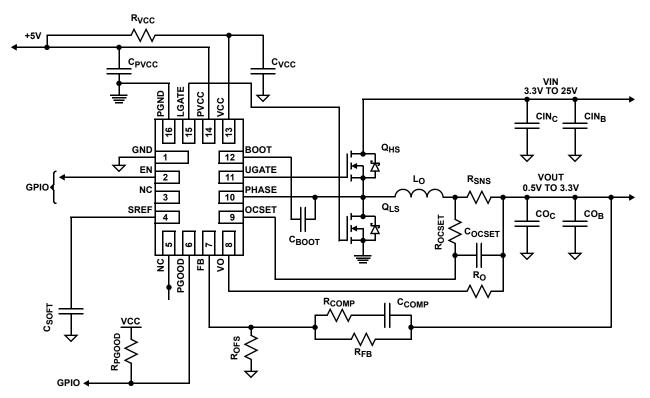

# **Application Schematics**

FIGURE 3. ISL62870 APPLICATION SCHEMATIC WITH RESISTOR CURRENT SENSE

#### Absolute Maximum Ratings

| VCC, PVCC, PGOOD to GND                                                                                               |

|-----------------------------------------------------------------------------------------------------------------------|

| GND to PGND                                                                                                           |

| BOOT Voltage (V <sub>BOOT-GND</sub> )                                                                                 |

| -0.3V to 9V (<10ns)<br>PHASE Voltage                                                                                  |

| GND -8V (<20ns Pulse Width, 10µJ)<br>UGATE Voltage V <sub>PHASE</sub> - 0.3V (DC) to V <sub>BOOT</sub>                |

| V <sub>PHASE</sub> - 5V (<20ns Pulse Width, 10µJ) to V <sub>BOOT</sub><br>LGATE Voltage GND - 0.3V (DC) to VCC + 0.3V |

| GND - 2.5V (<20ns Pulse Width, 5µJ) to VCC + 0.3V                                                                     |

#### Thermal Information

| Thermal Resistance (Typical, Note 1)             | θ <sub>JA</sub> (°C/W) |

|--------------------------------------------------|------------------------|

| 16 Ld µTQFN Package                              | . 84                   |

| Junction Temperature Range5                      |                        |

| Operating Temperature Range1                     | 0°C to +100°C          |

| Storage Temperature6                             | 5°C to +150°C          |

| Pb-Free Reflow Profile                           | .see link below        |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

| http://www.intersil.com/pbfree/Pb-FreeReflow.asp |                        |

#### **Recommended Operating Conditions**

| Ambient Temperature Range      | 10°C to +100°C |

|--------------------------------|----------------|

| Converter Input Voltage to GND | 3.3V to 25V    |

| VCC, PVCC to GND               | 5V ±5%         |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions may adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

1. θ<sub>JA</sub> is measured in free air with the component mounted on a high effective thermal conductivity test board with "direct attach" features. See Tech Brief TB379.

| Electrical Specifications | These specifications apply for $T_A = -10^{\circ}C$ to $+100^{\circ}C$ , unless otherwise stated. All typical specifications |

|---------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                           | $T_A = +25^{\circ}C$ , VCC = 5V. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise            |

|                           | specified. Temperature limits established by characterization and are not production tested.                                 |

| PARAMETER                         | SYMBOL                | TEST CONDITIONS                                                                                    | MIN   | TYP  | MAX   | UNIT |

|-----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------|-------|------|-------|------|

| VCC and PVCC                      |                       |                                                                                                    |       | 1    |       |      |

| VCC Input Bias Current            | IVCC                  | EN = 5V, VCC = 5V, FB = 0.55V, SREF <fb< td=""><td>-</td><td>1.1</td><td>1.5</td><td>mA</td></fb<> | -     | 1.1  | 1.5   | mA   |

| VCC Shutdown Current              | I <sub>VCCoff</sub>   | EN = GND, VCC = 5V                                                                                 | -     | 0.1  | 1.0   | μA   |

| PVCC Shutdown Current             | I <sub>PVCCoff</sub>  | EN = GND, PVCC = 5V                                                                                | -     | 0.1  | 1.0   | μA   |

| VCC POR THRESHOLD                 |                       |                                                                                                    | I     | L    |       |      |

| Rising VCC POR Threshold Voltage  | V <sub>VCC_THR</sub>  |                                                                                                    | 4.40  | 4.49 | 4.60  | V    |

| Falling VCC POR Threshold Voltage | V <sub>VCC_THF</sub>  |                                                                                                    | 4.10  | 4.22 | 4.35  | V    |

| REGULATION                        |                       | 1                                                                                                  | I     | 1    |       |      |

| Reference Voltage                 | V <sub>REF(int)</sub> |                                                                                                    | -     | 0.50 | -     | V    |

| System Accuracy                   |                       | PWM Mode = CCM                                                                                     | -0.75 | -    | +0.75 | %    |

| PWM                               |                       | 1                                                                                                  | I     | 1    |       |      |

| Switching Frequency               | F <sub>SW</sub>       | PWM Mode = CCM                                                                                     | 270   | 300  | 330   | kHz  |

| vo                                | L.                    | L                                                                                                  |       | 1    |       |      |

| VO Input Voltage Range            | V <sub>VO</sub>       |                                                                                                    | 0     | -    | 3.6   | V    |

| VO Input Impedance                | R <sub>VO</sub>       | EN = 5V                                                                                            | -     | 600  | -     | kΩ   |

| VO Reference Offset Current       | I <sub>VOSS</sub>     | V <sub>ENTHR</sub> < EN, SREF = Soft-Start Mode                                                    | -     | 10   | -     | μA   |

| VO Input Leakage Current          | I <sub>VOoff</sub>    | EN = GND, VO = 3.6V                                                                                | -     | .1   | -     | μA   |

| ERROR AMPLIFIER                   |                       | 1                                                                                                  | I     | 1    |       |      |

| FB Input Bias Current             | I <sub>FB</sub>       | EN = 5V, FB = 0.50V                                                                                | -20   | -    | +50   | nA   |

| SREF                              |                       |                                                                                                    | I     | 1    | 1     |      |

| SREF Voltage                      | V <sub>SREF</sub>     |                                                                                                    | -     | 0.5  | -     | V    |

| Soft-Start Current                | I <sub>SS</sub>       |                                                                                                    | 10    | 20   | 30    | μA   |

## Electrical Specifications

These specifications apply for  $T_A = -10^{\circ}$ C to  $+100^{\circ}$ C, unless otherwise stated. All typical specifications  $T_A = +25^{\circ}$ C, VCC = 5V. Parameters with MIN and/or MAX limits are 100% tested at +25°C, unless otherwise specified. Temperature limits established by characterization and are not production tested. (Continued)

| PARAMETER                                 | SYMBOL              | TEST CONDITIONS                        | MIN       | TYP  | MAX  | UNIT |

|-------------------------------------------|---------------------|----------------------------------------|-----------|------|------|------|

| POWER GOOD                                |                     |                                        | · · · · · |      |      |      |

| PGOOD Pull-down Impedance                 | R <sub>PG_SS</sub>  | PGOOD = 5mA Sink                       | 75        | 95   | 150  | Ω    |

|                                           | R <sub>PG_UV</sub>  | PGOOD = 5mA Sink                       | 75        | 95   | 150  | Ω    |

|                                           | R <sub>PG_OV</sub>  | PGOOD = 5mA Sink                       | 50        | 65   | 90   | Ω    |

|                                           | R <sub>PG_OC</sub>  | PGOOD = 5mA Sink                       | 25        | 35   | 50   | Ω    |

| PGOOD Leakage Current                     | I <sub>PG</sub>     | PGOOD = 5V                             | -         | 0.1  | 1.0  | μA   |

| PGOOD Maximum Sink Current (Note 2)       | I <sub>PG_max</sub> |                                        | -         | 5.0  | -    | mA   |

| GATE DRIVER                               |                     |                                        |           | L    | r.   |      |

| UGATE Pull-Up Resistance (Note 2)         | R <sub>UGPU</sub>   | 200mA Source Current                   | -         | 1.0  | 1.5  | Ω    |

| UGATE Source Current (Note 2)             | IUGSRC              | UGATE - PHASE = 2.5V                   | -         | 2.0  | -    | Α    |

| UGATE Sink Resistance (Note 2)            | R <sub>UGPD</sub>   | 250mA Sink Current                     | -         | 1.0  | 1.5  | Ω    |

| UGATE Sink Current (Note 2)               | IUGSNK              | UGATE - PHASE = 2.5V                   | -         | 2.0  | -    | Α    |

| LGATE Pull-Up Resistance (Note 2)         | R <sub>LGPU</sub>   | 250mA Source Current                   | -         | 1.0  | 1.5  | Ω    |

| LGATE Source Current (Note 2)             | ILGSRC              | LGATE - GND = 2.5V                     | -         | 2.0  | -    | Α    |

| LGATE Sink Resistance (Note 2)            | R <sub>LGPD</sub>   | 250mA Sink Current                     | -         | 0.5  | 0.9  | Ω    |

| LGATE Sink Current (Note 2)               | ILGSNK              | LGATE - PGND = 2.5V                    | -         | 4.0  | -    | Α    |

| UGATE to LGATE Deadtime                   | t <sub>UGFLGR</sub> | UGATE falling to LGATE rising, no load | -         | 21   | -    | ns   |

| LGATE to UGATE Deadtime                   | t <sub>LGFUGR</sub> | LGATE falling to UGATE rising, no load | -         | 21   | -    | ns   |

| PHASE                                     |                     | 1                                      |           | 1    | 1    |      |

| PHASE Input Impedance                     | R <sub>PHASE</sub>  |                                        | -         | 33   | -    | kΩ   |

| BOOTSTRAP DIODE                           |                     | 1                                      |           | 1    | 1    |      |

| Forward Voltage                           | VF                  | PVCC = 5V, I <sub>F</sub> = 2mA        | -         | 0.58 | -    | V    |

| Reverse Leakage                           | I <sub>R</sub>      | V <sub>R</sub> = 25V                   | -         | 0.2  | -    | μA   |

| CONTROL INPUTS                            |                     | 1                                      |           | 1    | 1    |      |

| EN High Threshold Voltage                 | V <sub>ENTHR</sub>  |                                        | 2.0       | -    | -    | V    |

| EN Low Threshold Voltage                  | V <sub>ENTHF</sub>  |                                        | -         | -    | 1.0  | V    |

| EN Input Bias Current                     | IEN                 | EN = 5V                                | 1.5       | 2.0  | 2.5  | μA   |

| EN Leakage Current                        | IENoff              | EN = GND                               | -         | 0.1  | 1.0  | μA   |

| PROTECTION                                |                     | 1                                      |           | 1    | 1    |      |

| OCP Threshold Voltage                     | V <sub>OCPTH</sub>  | V <sub>OCSET</sub> - V <sub>O</sub>    | -1.75     | -    | 1.75 | mV   |

| OCP Reference Current                     | IOCP                | EN = 5.0V                              | 9.0       | 10   | 11   | μA   |

| OCSET Input Resistance                    | R <sub>OCSET</sub>  | EN = 5.0V                              | -         | 600  | -    | kΩ   |

| OCSET Leakage Current                     | IOCSET              | EN = GND                               | -         | 0    | -    | μA   |

| UVP Threshold Voltage                     | V <sub>UVTH</sub>   | V <sub>FB</sub> = %V <sub>SREF</sub>   | 81        | 84   | 87   | %    |

| OVP Rising Threshold Voltage              | VOVRTH              | V <sub>FB</sub> = %V <sub>SREF</sub>   | 113       | 116  | 120  | %    |

| OVP Falling Threshold Voltage             | V <sub>OVFTH</sub>  | V <sub>FB</sub> = %V <sub>SREF</sub>   | 100       | 102  | 106  | %    |

| OTP Rising Threshold Temperature (Note 2) | TOTRTH              |                                        | -         | 150  | -    | °C   |

| OTP Hysteresis (Note 2)                   | TOTHYS              |                                        | -         | 25   | -    | °C   |

NOTE:

2. Limits established by characterization and are not production tested.

# Functional Pin Descriptions

## GND (Pin 1)

IC ground for bias supply and signal reference.

#### EN (Pin 2)

Enable input for the IC. Pulling EN above the  $V_{\mbox{ENTHR}}$  rising threshold voltage initializes the soft-start sequence.

## NC (Pins 3, 5)

No internal connection. Pins 3 and 5 should be connected to the GND pin.

# SREF (Pin 4)

Soft-start programming capacitor input. Connects internally to the inverting input of the  $V_{SET}$  voltage setpoint amplifier.

## PGOOD (Pin 6)

Power-good open-drain indicator output. This pin changes to high impedance when the converter is able to supply regulated voltage. The pull-down resistance between the PGOOD pin and the GND pin identifies which protective fault has shut down the regulator. See Table 1 on page 10.

## FB (Pin 7)

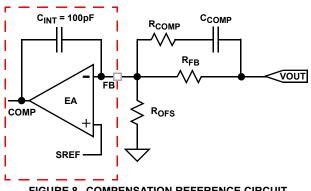

Voltage feedback sense input. Connects internally to the inverting input of the control-loop error amplifier. The converter is in regulation when the voltage at the FB pin equals the voltage on the SREF pin. The control loop compensation network connects between the FB pin and the converter output. See Figure 8 on page 10.

## VO (Pin 8)

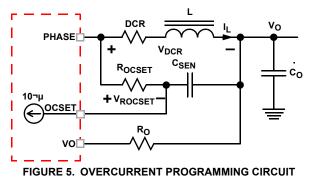

Output voltage sense input for the  $R^3$  modulator. The VO pin also serves as the reference input for the overcurrent detection circuit. See Figure 5 on page 7.

## OCSET (Pin 9)

Input for the overcurrent detection circuit. The overcurrent setpoint programming resistor R<sub>OCSET</sub> connects from this pin to the sense node. See "OVERCURRENT PROGRAMMING CIRCUIT" on page 7.

## PHASE (Pin 10)

Return current path for the UGATE high-side MOSFET driver. VIN sense input for the R<sup>3</sup> modulator. Inductor current polarity detector input. Connect to junction of output inductor, high-side MOSFET, and low-side MOSFET. See "Application Schematics" on page 3 (Figures 2 and 3).

## UGATE (Pin 11)

High-side MOSFET gate driver output. Connect to the gate terminal of the high-side MOSFET of the converter.

## BOOT (Pin 12)

Positive input supply for the UGATE high-side MOSFET gate driver. The BOOT pin is internally connected to the cathode of

the Schottky boot-strap diode. Connect an MLCC between the BOOT pin and the PHASE pin.

# VCC (Pin 13)

Input for the IC bias voltage. Connect +5V to the VCC pin and decouple with at least a  $1\mu$ F MLCC to the GND pin. See "Application Schematics" on page 3 (Figures 2 and 3).

# PVCC (Pin 14)

Input for the LGATE and UGATE MOSFET driver circuits. The PVCC pin is internally connected to the anode of the Schottky boot-strap diode. Connect +5V to the PVCC pin and decouple with a 10 $\mu$ F MLCC to the PGND pin. See "Application Schematics" on page 3 (Figures 2 and 3).

## LGATE (Pin 15)

Low-side MOSFET gate driver output. Connect to the gate terminal of the low-side MOSFET of the converter.

#### PGND (Pin 16)

Return current path for the LGATE MOSFET driver. Connect to the source of the low-side MOSFET.

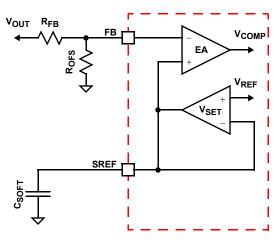

# Setpoint Reference Voltage

The 500mV output of the setpoint reference voltage (V<sub>SREF</sub>) appears at the SREF pin. This signal is the output of the current limited voltage follower that buffers an internal 500mV voltage reference (V<sub>REF</sub>.) The converter is in regulation when the voltage at the FB pin (V<sub>FB</sub>) equals the V<sub>SREF</sub> voltage at the SREF pin. Both of these pins are measured relative to the GND pin, not the PGND pin.

The feedback voltage-divider network consisting of offset resistor (R<sub>OFS</sub>) and loop-compensation resistor (R<sub>FB</sub>) scale down the converter output voltage (V<sub>OUT</sub>) such that the voltage V<sub>FB</sub> equals V<sub>SREF</sub> when V<sub>OUT</sub> equals the desired output voltage of the converter. The voltage-divider relation is given in Equation 1:

$$V_{FB} = V_{OUT} \cdot \frac{R_{OFS}}{R_{FB} + R_{OFS}}$$

(EQ. 1)

Where:

- $V_{FB} = V_{SREF}$

- R<sub>FB</sub> is the loop-compensation feedback resistor that connects from the FB pin to the converter output

- $R_{OFS}$  is the voltage-scaling programming resistor that connects from the FB pin to the GND pin

The value of offset resistor  $R_{OFS}$  must be recalculated whenever the value of loop-compensation resistor  $R_{FB}$  has been changed. Calculation of  $R_{OFS}$  is written as shown in Equation 2:

$$R_{OFS} = \frac{V_{SREF} \cdot R_{FB}}{V_{OUT} - V_{SREF}}$$

(EQ. 2)

FIGURE 4. ISL62870 VOLTAGE PROGRAMMING CIRCUIT

# Soft-Start Delay

#### **Circuit Description**

When the voltage on the VCC pin has ramped above the rising power-on reset voltage V<sub>VCC\_THR</sub>, and the voltage on the EN pin has increased above the rising enable threshold voltage V<sub>ENTHR</sub>, the SREF pin releases its discharge clamp, and enables the reference amplifier V<sub>SET</sub>. The soft-start current I<sub>SS</sub> is limited to 20µA and is sourced out of the SREF pin and charges capacitor C<sub>SOFT</sub> until V<sub>SREF</sub> equals V<sub>REF</sub>. The regulator controls the PWM such that the voltage on the FB pin tracks the rising voltage on the SREF pin. The elapsed time from when the EN pin is asserted to when V<sub>SREF</sub> has charged C<sub>SOFT</sub> to V<sub>REF</sub> is called the soft-start delay t<sub>SS</sub> which is given by Equation 3:

$$t_{SS} = \frac{V_{SREF} \cdot C_{SOFT}}{I_{SS}}$$

(EQ. 3)

Where:

- $\,I_{SS}$  is the soft-start current source at the 20  $\!\mu\text{A}$  limit

- V<sub>SREF</sub> is the buffered V<sub>REF</sub> reference voltage

The end of soft-start is detected by  $I_{SS}$  tapering off when capacitor  $C_{SOFT}$  charges to  $V_{REF}$ . The internal SSOK flag is set, the PGOOD pin goes high, and diode emulation mode (DEM) is enabled.

#### Component Selection For C<sub>SOFT</sub> Capacitor

Choosing the C<sub>SOFT</sub> capacitor to meet the requirements of a particular soft-start delay  $t_{SS}$  is calculated using Equation 4, which is written as follows:

$$C_{SOFT} = \frac{t_{SS} \cdot I_{SS}}{V_{SREF}}$$

(EQ. 4)

Where:

- t<sub>SS</sub> is the soft-start delay

- $I_{SS}$  is the 20µA soft-start current source at the 20µA limit

- $V_{SREF}$  is the buffered  $V_{REF}$  reference voltage

# Fault Protection

#### Overcurrent

The overcurrent protection (OCP) setpoint is programmed with resistor R<sub>OCSET</sub>, which is connected across the OCSET and PHASE pins. Resistor R<sub>O</sub> is connected between the VO pin and the actual output voltage of the converter. During normal operation, the VO pin is a high impedance path, therefore there is no voltage drop across R<sub>O</sub>. The value of resistor R<sub>O</sub> should always match the value of resistor R<sub>OCSET</sub>.

Figure 5 shows the overcurrent set circuit. The inductor consists of inductance L and the DC resistance DCR. The inductor DC current  $I_L$  creates a voltage drop across DCR, which is given by Equation 5:

$$V_{DCR} = I_{L} \cdot DCR$$

(EQ. 5)

The I<sub>OCSET</sub> current source sinks 10 $\mu$ A into the OCSET pin, creating a DC voltage drop across the resistor R<sub>OCSET</sub>, which is given by Equation 6:

$$V_{\text{ROCSET}} = 10 \mu A \cdot R_{\text{OCSET}}$$

(EQ. 6)

The DC voltage difference between the OCSET pin and the VO pin, which is given by Equation 7:

$$V_{OCSET} - V_{VO} = V_{DCR} - V_{ROCSET} = I_L \cdot DCR - I_{OCSET} \cdot R_{OCSET}$$

(EQ. 7)

The IC monitors the voltage of the OCSET pin and the VO pin. When the voltage of the OCSET pin is higher than the voltage of the VO pin for more than  $10\mu$ s, an OCP fault latches the converter off.

## Component Selection For ROCSET and CSEN

The value of  $\mathsf{R}_{OCSET}$  is calculated with Equation 8 which is written as follows:

$$R_{OCSET} = \frac{I_{OC} \cdot DCR}{I_{OCSET}}$$

(EQ. 8)

Where:

- $R_{OCSET}(\Omega)$  is the resistor used to program the overcurrent setpoint

- $I_{\mbox{\scriptsize OCP}}$  is the output DC load current that will activate the OCP fault detection circuit

- DCR is the inductor DC resistance

For example, if I<sub>OC</sub> is 20A and DCR is 4.5m $\Omega$ , the choice of R<sub>OCSET</sub> is = 20Ax4.5m $\Omega$ /10µA = 9k $\Omega$ .

Resistor R<sub>OCSET</sub> and capacitor C<sub>SEN</sub> form an R-C network to sense the inductor current. To sense the inductor current correctly not only in DC operation, but also during dynamic operation, the R-C network time constant R<sub>OCSET</sub> C<sub>SEN</sub> needs to match the inductor time constant L/DCR. The value of C<sub>SEN</sub> is then written as follows:

$$C_{SEN} = \frac{L}{R_{OCSET} \cdot DCR}$$

(EQ. 9)

For example, if L is 1.5µH, DCR is 4.5m $\Omega$ , and R<sub>OCSET</sub> is 9k $\Omega$ , the choice of C<sub>SEN</sub> = 1.5µH/(9k $\Omega$ x4.5m $\Omega$ ) = 0.037µF.

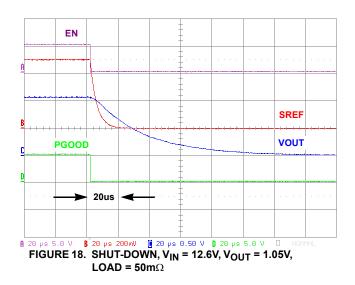

When an OCP fault is declared, the PGOOD pin will pull-down to 35 $\Omega$  and latch off the converter. The fault will remain latched until the EN pin has been pulled below the falling EN threshold voltage V<sub>ENTHF</sub> or if VCC has decayed below the falling POR threshold voltage V<sub>VCC THF</sub>

#### Overvoltage

The OVP fault detection circuit triggers after the FB pin voltage is above the rising overvoltage threshold V<sub>OVRTH</sub> for more than 2µs. For example, if the converter is programmed to regulate 1.0V at the FB pin, that voltage would have to rise above the typical V<sub>OVRTH</sub> threshold of 116% for more than 2µs in order to trip the OVP fault latch. In numerical terms, that would be 116% x 1.0V = 1.16V. When an OVP fault is declared, the PGOOD pin will pull-down to 65 $\Omega$  and latch-off the converter. The OVP fault will remain latched until VCC has decayed below the falling POR threshold voltage V<sub>VCC\_THF</sub>. An OVP fault cannot be reset by pulling the EN pin below the falling EN threshold voltage V<sub>ENTHF</sub>.

Although the converter has latched-off in response to an OVP fault, the LGATE gate-driver output will retain the ability to toggle the low-side MOSFET on and off, in response to the output voltage transversing the VOVRTH and VOVFTH thresholds. The LGATE gate-driver will turn-on the low-side MOSFET to discharge the output voltage, protecting the load. The LGATE gate-driver will turn-off the low-side MOSFET once the FB pin voltage is lower than the falling overvoltage threshold VOVRTH for more than 2µs. The falling overvoltage threshold VOVFTH is typically 102%. That means if the FB pin voltage falls below 102% x 1.0V = 1.02V, for more than 2µs, the LGATE gate-driver will turn off the low-side MOSFET. If the output voltage rises again, the LGATE driver will again turn on the low-side MOSFET when the FB pin voltage is above the rising overvoltage threshold VOVRTH for more than 2µs. By doing so, the IC protects the load when there is a consistent overvoltage condition.

#### Undervoltage

The UVP fault detection circuit triggers after the FB pin voltage is below the undervoltage threshold  $V_{UVTH}$  for more than 2µs. For example, if the converter is programmed to regulate 1.0V at the FB pin, that voltage would have to fall below the typical

$V_{UVTH}$  threshold of 84% for more than 2µs in order to trip the UVP fault latch. In numerical terms, that would be 84% x 1.0V = 0.84V. When a UVP fault is declared, the PGOOD pin will pull-down to 95 $\Omega$  and latch-off the converter. The fault will remain latched until the EN pin has been pulled below the falling EN threshold voltage  $V_{ENTHF}$  or if VCC has decayed below the falling POR threshold voltage  $V_{VCC}$  THF.

#### **Over-Temperature**

When the temperature of the IC increases above the rising threshold temperature  $T_{OTRTH}$ , it will enter the OTP state that suspends the PWM, forcing the LGATE and UGATE gate-driver outputs low. The status of the PGOOD pin does not change nor does the converter latch-off. The PWM remains suspended until the IC temperature falls below the hysteresis temperature  $T_{OTHYS}$ , at which time normal PWM operation resumes. The OTP state can be reset if the EN pin is pulled below the falling EN threshold voltage  $V_{ENTHF}$  or if VCC has decayed below the falling POR threshold voltage  $V_{VCC_THF}$ . All other protection circuits remain functional while the IC is in the OTP state. It is likely that the IC will detect an UVP fault because in the absence of PWM, the output voltage decays below the undervoltage threshold  $V_{UVTH}$ .

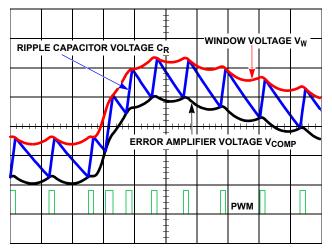

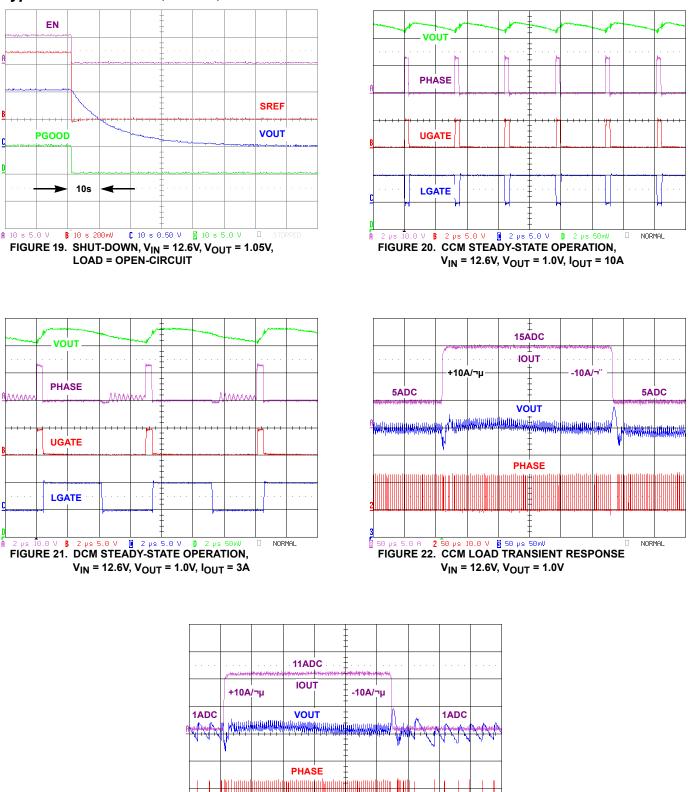

# Theory of Operation

The modulator features Intersil's R<sup>3</sup> Robust-Ripple Regulator technology, a hybrid of fixed frequency PWM control and variable frequency hysteretic control. The PWM frequency is maintained at 300kHz under static continuous conduction mode operation within the entire specified envelope of input voltage, output voltage, and output load. If the application should experience a rising load transient and/or a falling line transient such that the output voltage starts to fall, the modulator will extend the on-time and/or reduce the off-time of the PWM pulse in progress. Conversely, if the application should experience a falling load transient and/or a rising line transient such that the output voltage starts to rise, the modulator will truncate the on-time and/or extend the off-time of the PWM pulse in progress. The period and duty cycle of the ensuing PWM pulses are optimized by the R<sup>3</sup> modulator for the remainder of the transient and work in concert with the error amplifier V<sub>FRR</sub> to maintain output voltage regulation. Once the transient has dissipated and the control loop has recovered, the PWM frequency returns to the nominal static 300kHz.

#### Modulator

The R<sup>3</sup> modulator synthesizes an AC signal V<sub>R</sub>, which is an analog representation of the output inductor ripple current. The duty-cycle of V<sub>R</sub> is the result of charge and discharge current through a ripple capacitor C<sub>R</sub>. The current through C<sub>R</sub> is provided by a transconductance amplifier g<sub>m</sub> that measures the input voltage (V<sub>IN</sub>) at the PHASE pin and output voltage

$(V_{OUT})$  at the VO pin. The positive slope of  $V_R$  can be written as Equation 10:

$$V_{\text{RPOS}} = (g_{\text{m}}) \cdot (V_{\text{IN}} - V_{\text{OUT}}) / C_{\text{R}}$$

(EQ. 10)

The negative slope of  $V_R$  can be written as Equation 11:

$V_{RNEG} = g_{m} \cdot V_{OUT} / C_{R}$ (EQ. 11)

Where g<sub>m</sub> is the gain of the transconductance amplifier.

A window voltage  $V_W$  is referenced with respect to the error amplifier output voltage  $V_{COMP}$ , creating an envelope into which the ripple voltage  $V_R$  is compared. The amplitude of  $V_W$  is controlled internally by the IC. The  $V_R$ ,  $V_{COMP}$ , and  $V_W$  signals feed into a window comparator in which  $V_{COMP}$  is the lower threshold voltage and  $V_W$  is the higher threshold voltage. Figure 6 shows PWM pulses being generated as  $V_R$  traverses the  $V_W$  and  $V_{COMP}$  thresholds. The PWM switching frequency is proportional to the slew rates of the positive and negative slopes of  $V_R$ ; it is inversely proportional to the voltage between  $V_W$  and  $V_{COMP}$ .

FIGURE 6. MODULATOR WAVEFORMS DURING LOAD TRANSIENT

## Synchronous Rectification

A standard DC/DC buck regulator uses a free-wheeling diode to maintain uninterrupted current conduction through the output inductor when the high-side MOSFET switches off for the balance of the PWM switching cycle. Low conversion efficiency as a result of the conduction loss of the diode makes this an unattractive option for all but the lowest current applications. Efficiency is dramatically improved when the freewheeling diode is replaced with a MOSFET that is turned on whenever the high-side MOSFET is turned off. This modification to the standard DC/DC buck regulator is referred to as synchronous rectification, the topology implemented by the ISL62870 controller.

#### **Diode Emulation**

The polarity of the output inductor current is defined as positive when conducting *away* from the phase node, and defined as

negative when conducting *towards* the phase node. The DC component of the inductor current is positive, but the AC component known as the ripple current, can be either positive or negative. Should the sum of the AC and DC components of the inductor current remain positive for the entire switching period, the converter is in continuous-conduction-mode (CCM.) However, if the inductor current becomes negative or zero, the converter is in discontinuous-conduction-mode (DCM.)

Unlike the standard DC/DC buck regulator, the synchronous rectifier can sink current from the output filter inductor during DCM, reducing the light-load efficiency with unnecessary conduction loss as the low-side MOSFET sinks the inductor current. The ISL62870 controller avoids the DCM conduction loss by making the low-side MOSFET emulate the current blocking behavior of a diode. This smart-diode operation called diode-emulation-mode (DEM) is triggered when the negative inductor current produces a positive voltage drop across the  $r_{DS(ON)}$  of the low-side MOSFET for eight consecutive PWM cycles while the LGATE pin is high. The converter will exit DEM on the next PWM pulse after detecting a negative voltage across the  $r_{DS(ON)}$  of the low-side MOSFET.

It is characteristic of the  $R^3$  architecture for the PWM switching frequency to decrease while in DCM, increasing efficiency by reducing unnecessary gate-driver switching losses. The extent of the frequency reduction is proportional to the reduction of load current. Upon entering DEM, the PWM frequency is forced to fall approximately 30% by forcing a similar increase of the window voltage V<sub>W</sub>. This measure is taken to prevent oscillating between modes at the boundary between CCM and DCM. The 30% increase of V<sub>W</sub> is removed upon exit of DEM, forcing the PWM switching frequency to jump back to the nominal CCM value.

#### Power-On Reset

The IC is disabled until the voltage at the VCC pin has increased above the rising power-on reset (POR) threshold voltage V<sub>VCC\_THR</sub>. The controller will become disabled when the voltage at the VCC pin decreases below the falling POR threshold voltage V<sub>VCC\_THF</sub>. The POR detector has a noise filter of approximately 1µs.

#### VIN and PVCC Voltage Sequence

Prior to pulling EN above the  $V_{\mbox{ENTHR}}$  rising threshold voltage, the following criteria must be met:

- 1.  $V_{PVCC}$  is at least equivalent to the VCC rising power-on reset voltage  $V_{VCC\_THR}$

- 2.  $V_{\mbox{VIN}}$  must be 3.3V or the minimum required by the application.

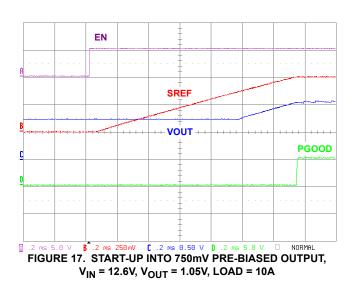

#### Start-Up Timing

Once VCC has ramped above  $V_{VCC_THR}$ , the controller can be enabled by pulling the EN pin voltage above the input high threshold  $V_{ENTHR}$ . Approximately 20µs later, the voltage at the SREF pin begins slewing to the designated VID set-point. The converter output voltage at the FB feedback pin follows the

voltage at the SREF pin. During soft-start, the regulator always operates in CCM until the soft-start sequence is complete.

#### **PGOOD Monitor**

The PGOOD pin indicates when the converter is capable of supplying regulated voltage. The PGOOD pin is an undefined impedance if the VCC pin has not reached the rising POR threshold  $V_{VCC}$  THR, or if the VCC pin is below the falling POR threshold  $V_{VCC}$  THF. The PGOOD pull-down resistance corresponds to a specific protective fault, thereby reducing troubleshooting time and effort. Table 1 maps the pull-down resistance of the PGOOD pin to the corresponding fault status of the controller.

| CONDITION                  | PGOOD RESISTANCE |

|----------------------------|------------------|

| VCC Below POR              | Undefined        |

| Soft-Start or Undervoltage | 95Ω              |

| Overvoltage                | 65Ω              |

| Overcurrent                | 35Ω              |

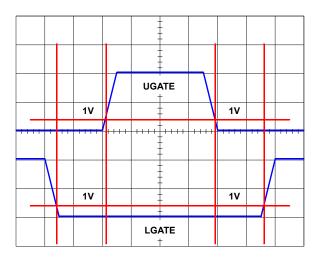

#### LGATE and UGATE MOSFET Gate-Drivers

The LGATE pin and UGATE pins are MOSFET driver outputs. The LGATE pin drives the low-side MOSFET of the converter while the UGATE pin drives the high-side MOSFET of the converter.

The LGATE driver is optimized for low duty-cycle applications where the low-side MOSFET experiences long conduction times. In this environment, the low-side MOSFETs require exceptionally low r<sub>DS(ON)</sub> and tend to have large parasitic charges that conduct transient currents within the devices in response to high dv/dt switching present at the phase node. The drain-gate charge in particular can conduct sufficient current through the driver pull-down resistance that the VGS(th) of the device can be exceeded and turned on. For this reason, the LGATE driver has been designed with low pull-down resistance and high sink current capability to ensure clamping the MOSFETs gate voltage below VGS(th).

## Adaptive Shoot-Through Protection

Adaptive shoot-through protection prevents a gate-driver output from turning on until the opposite gate-driver output has fallen below approximately 1V. The dead-time shown in Figure 7 is extended by the additional period that the falling gate voltage remains above the 1V threshold. The high-side gatedriver output voltage is measured across the UGATE and PHASE pins while the low-side gate-driver output voltage is measured across the LGATE and PGND pins. The power for the LGATE gate-driver is sourced directly from the PVCC pin. The power for the UGATE gate-driver is supplied by a bootstrap capacitor connected across the BOOT and PHASE pins. The capacitor is charged each time the phase node voltage falls a diode drop below PVCC, such as when the low-side MOSFET is turned on.

FIGURE 7. GATE DRIVER ADAPTIVE SHOOT-THROUGH

# Compensation Design

Figure 8 shows the recommended Type-II compensation circuit. The FB pin is the inverting input of the error amplifier. The COMP signal, the output of the error amplifier, is inside the chip and unavailable to users. CINT is a 100pF capacitor integrated inside the IC, connecting across the FB pin and the COMP signal. R<sub>FB</sub>, R<sub>COMP</sub>, C<sub>COMP</sub> and C<sub>INT</sub> form the Type-II compensator. The frequency domain transfer function is given by Equation 12:

$$G_{COMP}(s) = \frac{1 + s \cdot (R_{FB} + R_{COMP}) \cdot C_{COMP}}{s \cdot R_{FB} \cdot C_{INT} \cdot (1 + s \cdot R_{COMP} \cdot C_{COMP})}$$

(EQ. 12)

The LC output filter has a double pole at its resonant frequency that causes rapid phase change. The R<sup>3</sup> modulator used in the IC makes the LC output filter resemble a first order system in which the closed loop stability can be achieved with the recommended Type-II compensation network. Intersil provides a PC-based tool that can be used to calculate compensation network component values and help simulate the loop frequency response.

# General Application Design Guide

This design guide is intended to provide a high-level explanation of the steps necessary to design a single-phase power converter. It is assumed that the reader is familiar with many of the basic skills and techniques referenced in the following. In

addition to this guide, Intersil provides complete reference designs that include schematics, bills of materials, and example board layouts.

#### Selecting the LC Output Filter

The duty cycle of an ideal buck converter is a function of the input and the output voltage. This relationship is written as shown in Equation 13:

$$D = \frac{v_0}{V_{IN}}$$

(EQ. 13)

The output inductor peak-to-peak ripple current is written as shown in Equation 14:

$$I_{P-P} = \frac{V_{O} \cdot (1-D)}{F_{SW} \cdot L}$$

(EQ. 14)

A typical step-down DC/DC converter will have an  $I_{P-P}$  of 20% to 40% of the maximum DC output load current. The value of  $I_{P-P}$  is selected based upon several criteria, such as MOSFET switching loss, inductor core loss, and the resistive loss of the inductor winding. The DC copper loss of the inductor can be estimated using Equation 15:

$$P_{COPPER} = I_{LOAD}^{2} \cdot DCR$$

(EQ. 15)

Where ILOAD is the converter output DC current.

The copper loss can be significant so attention has to be given to the DCR selection. Another factor to consider when choosing the inductor is its saturation characteristics at elevated temperature. A saturated inductor could cause destruction of circuit components, as well as nuisance OCP faults.

A DC/DC buck regulator must have output capacitance  $C_O$  into which ripple current  $I_{P,P}$  can flow. Current  $I_{P,P}$  develops a corresponding ripple voltage  $V_{P,P}$  across  $C_{O_i}$  which is the sum of the voltage drop across the capacitor ESR and of the voltage change stemming from charge moved in and out of the capacitor. These two voltages are written as Equations 16 and

17:

$$\Delta V_{\text{ESR}} = I_{\text{P}-\text{P}} \cdot \text{ESR}$$

(EQ

and:

$$\Delta V_{\rm C} = \frac{I_{\rm P-P}}{8 \cdot C_{\rm O} \cdot F_{\rm SW}}$$

(EQ. 17)

If the output of the converter has to support a load with high pulsating current, several capacitors will need to be paralleled to reduce the total ESR until the required  $V_{P,P}$  is achieved. The inductance of the capacitor can cause a brief voltage dip if the load transient has an extremely high slew rate. Low inductance capacitors should be considered. A capacitor dissipates heat as a function of RMS current and frequency. Be sure that  $I_{P,P}$  is shared by a sufficient quantity of paralleled capacitors so that they operate below the maximum rated RMS current at  $F_{SW}$ . Take into account that the rated value of a capacitor can fade as much as 50% as the DC voltage across it increases.

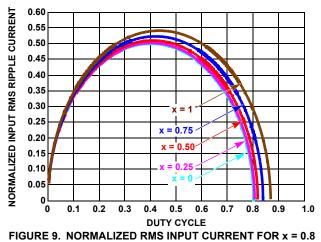

# Selection of the Input Capacitor

The important parameters for the bulk input capacitance are the voltage rating and the RMS current rating. For reliable operation, select bulk capacitors with voltage and current ratings above the maximum input voltage and capable of supplying the RMS current required by the switching circuit. Their voltage rating should be at least 1.25 times greater than the maximum input voltage, while a voltage rating of 1.5 times is a preferred rating. Figure 9 is a graph of the input RMS ripple current, normalized relative to output load current, as a function of duty cycle that is adjusted for converter efficiency. The ripple current calculation is written as expressed in Equation 18:

$$I_{IN\_RMS} = \frac{\sqrt{(I_{MAX}^2 \cdot (D - D^2)) + (x \cdot I_{MAX}^2 \cdot \frac{D}{12})}}{I_{MAX}}$$

(EQ. 18)

Where:

- I<sub>MAX</sub> is the maximum continuous I<sub>LOAD</sub> of the converter

- x is a multiplier (0 to 1) corresponding to the inductor peak-to-peak ripple amplitude expressed as a percentage of I<sub>MAX</sub> (0% to 100%)

- D is the duty cycle that is adjusted to take into account the efficiency of the converter

Duty cycle is written as expressed in Equation 19:

$$D = \frac{V_0}{V_{IN} \cdot EFF}$$

(EQ. 19)

In addition to the bulk capacitance, some low ESL ceramic capacitance is recommended to decouple between the drain of the high-side MOSFET and the source of the low-side MOSFET.

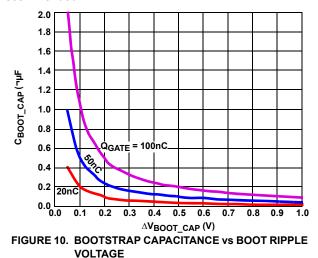

#### Selecting The Bootstrap Capacitor

Adding an external capacitor across the BOOT and PHASE pins completes the bootstrap circuit. We selected the bootstrap capacitor breakdown voltage to be at least 10V. Although the theoretical maximum voltage of the capacitor is PVCC -  $V_{DIODE}$  (voltage drop across the boot diode), large excursions below ground by the PHASE node requires that we select a capacitor

16)

with at least a breakdown rating of 10V. The bootstrap capacitor can be chosen from Equation 20:

$$C_{BOOT} \ge \frac{Q_{GATE}}{\Delta V_{BOOT}}$$

(EQ. 20)

Where:

- Q<sub>GATE</sub> is the amount of gate charge required to fully charge the gate of the upper MOSFET

- $\Delta V_{BOOT}$  is the maximum decay across the BOOT capacitor

As an example, suppose an upper MOSFET has a gate charge,  $Q_{GATE}$ , of 25nC at 5V and also assume the droop in the drive voltage over a PWM cycle is 200mV. One will find that a bootstrap capacitance of at least  $0.125\mu$ F is required. The next larger standard value capacitance is  $0.15\mu$ F. A good quality ceramic capacitor such as X7R or X5R is recommended.

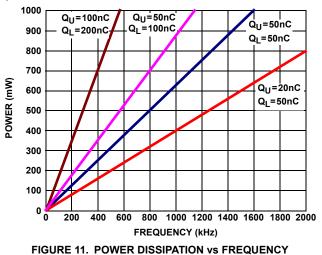

#### Driver Power Dissipation

Switching power dissipation in the driver is mainly a function of the switching frequency and total gate charge of the selected MOSFETs. Calculating the power dissipation in the driver for a desired application is critical to ensuring safe operation. Exceeding the maximum allowable power dissipation level will push the IC beyond the maximum recommended operating junction temperature of +125°C. When designing the application, it is recommended that the following calculation be performed to ensure safe operation at the desired frequency for the selected MOSFETs. The power dissipated by the drivers is approximated using Equation 21:

$$P = F_{sw}(1.5V_UQ_U + V_LQ_L) + P_L + P_U$$

(EQ. 21)

Where:

- Fsw is the switching frequency of the PWM signal

- VU is the upper gate driver bias supply voltage

- VL is the lower gate driver bias supply voltage

- $Q_U$  is the charge to be delivered by the upper driver into the gate of the MOSFET and discrete capacitors

- $\mathsf{Q}_\mathsf{L}$  is the charge to be delivered by the lower driver into the gate of the MOSFET and discrete capacitors

- PL is the quiescent power consumption of the lower driver

- PU is the quiescent power consumption of the upper driver

#### **MOSFET Selection and Considerations**

Typically, a MOSFET cannot tolerate even brief excursions beyond their maximum drain to source voltage rating. The MOSFETs used in the power stage of the converter should have a maximum  $V_{DS}$  rating that exceeds the sum of the upper voltage tolerance of the input power source and the voltage spike that occurs when the MOSFET switches off.

There are several power MOSFETs readily available that are optimized for DC/DC converter applications. The preferred high-side MOSFET emphasizes low switch charge so that the device spends the least amount of time dissipating power in the linear region. Unlike the low-side MOSFET, which has the drain-source voltage clamped by its body diode during turn-off, the high-side MOSFET turns off with V<sub>IN</sub>-V<sub>OUT</sub>, plus the spike, across it. The preferred low-side MOSFET emphasizes low r<sub>DS(ON)</sub> when fully saturated to minimize conduction loss.

For the low-side MOSFET, (LS), the power loss can be assumed to be conductive only and is written as Equation 22:

$$P_{\text{CON}_{\text{LS}}} = I_{\text{LOAD}}^{2} \cdot r_{\text{DS}(\text{ON})_{\text{LS}}} \cdot (1 - D)$$

(EQ. 22)

For the high-side MOSFET, (HS), its conduction loss is written as Equation 23:

$$P_{CON_{HS}} = I_{LOAD}^{2} \cdot r_{DS(ON_{HS})} \cdot D$$

(EQ. 23)

For the high-side MOSFET, its switching loss is written as Equation 24:

$$\mathsf{P}_{\mathsf{SW}_{\mathsf{HS}}} = \frac{\mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{VALLEY}} \cdot \mathsf{t}_{\mathsf{ON}} \cdot \mathsf{F}_{\mathsf{SW}}}{2} + \frac{\mathsf{V}_{\mathsf{IN}} \cdot \mathsf{I}_{\mathsf{PEAK}} \cdot \mathsf{t}_{\mathsf{OFF}} \cdot \mathsf{F}_{\mathsf{SW}}}{2}$$

(EQ. 24)

Where:

- I<sub>VALLEY</sub> is the difference of the DC component of the inductor current minus 1/2 of the inductor ripple current

- I<sub>PEAK</sub> is the sum of the DC component of the inductor current plus 1/2 of the inductor ripple current

- $t_{\mbox{ON}}$  is the time required to drive the device into saturation

- $t_{\mbox{\scriptsize OFF}}$  is the time required to drive the device into cut-off

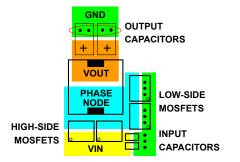

#### Layout Considerations

The IC, analog signals, and logic signals should all be on the same side of the PCB, located away from powerful emission sources. The power conversion components should be arranged in a manner similar to the example in Figure 12 where the area enclosed by the current circulating through the input capacitors, high-side MOSFETs, and low-side MOSFETs is as small as possible and all located on the same side of the PCB. The power components can be located on either side of the PCB relative to the IC.

#### FIGURE 12. TYPICAL POWER COMPONENT PLACEMENT

#### Signal Ground

The GND pin is the signal-common also known as analog ground of the IC. When laying out the PCB, it is very important that the connection of the GND pin to the bottom feedback voltage-divider resistor and the  $C_{SOFT}$  capacitor be made as close as possible to the GND pin on a conductor not shared by any other components.

In addition to the critical single point connection discussed in the previous paragraph, the ground plane layer of the PCB should have a single-point-connected island located under the area encompassing the IC, feedback voltage divider, compensation components, C<sub>SOFT</sub> capacitor, and the interconnecting traces among the components and the IC. The island should be connected using several filled vias to the rest of the ground plane layer at one point that is not in the path of either large static currents or high di/dt currents. The single connection point should also be where the VCC decoupling capacitor and the GND pin of the IC are connected.

#### **Power Ground**

Anywhere not within the analog-ground island is Power Ground.

#### VCC AND PVCC PINS

Place the decoupling capacitors as close as practical to the IC. In particular, the PVCC decoupling capacitor should have a very short and wide connection to the PGND pin. The VCC decoupling capacitor should not share any vias with the PVCC decoupling capacitor.

#### **EN AND PGOOD PINS**

These are logic signals that are referenced to the GND pin. Treat as a typical logic signal.

#### **OCSET AND VO PINS**

The current-sensing network consisting of  $R_{OCSET}$ ,  $R_O$ , and  $C_{SEN}$  needs to be connected to the inductor pads for accurate measurement of the DCR voltage drop. These components however, should be located physically close to the OCSET and VO pins with traces leading back to the inductor. It is critical that the traces are shielded by the ground plane layer all the way to the inductor pads. The procedure is the same for resistive current sense.

#### **FB AND SREF PINS**

The input impedance of these pins is high, making it critical to place the loop compensation components, feedback voltage divider resistors, and  $C_{\text{SOFT}}$  capacitor close to the IC, keeping the length of the traces short.

#### LGATE, PGND, UGATE, BOOT, AND PHASE PINS

The signals going through these traces are high dv/dt and high di/dt, with high peak charging and discharging current. The PGND pin can only flow current from the gate-source charge of the low-side MOSFETs when LGATE goes low. Ideally, route the trace from the LGATE pin in parallel with the trace from the PGND pin; route the trace from the UGATE pin in parallel with the trace from the PHASE pin, and route the trace from the BOOT pin in parallel with the trace from the trace from the PHASE pin. These pairs of traces should be short, wide, and away from other traces with high input impedance; weak signal traces should not be in proximity with these traces on any layer.

#### Copper Size for the Phase Node

The parasitic capacitance and parasitic inductance of the phase node should be kept very low to minimize ringing. It is best to limit the size of the PHASE node copper in strict accordance with the current and thermal management of the application. An MLCC should be connected directly across the drain of the upper MOSFET and the source of the lower MOSFET to suppress the turn-off voltage spike.

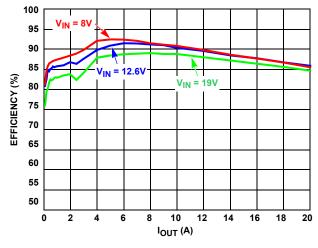

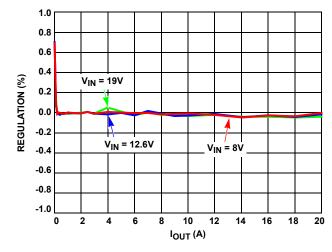

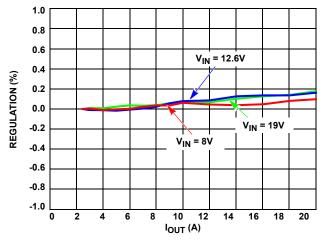

# **Typical Performance**

FIGURE 13. EFFICIENCY AT V<sub>OUT</sub> = 1.1V

FIGURE 14. LOAD REGULATION AT V<sub>OUT</sub> = 1.1V

FIGURE 15. SWITCHING FREQUENCY AT V<sub>OUT</sub> = 1.1V

FN6708 Rev 0.00 August 14, 2008

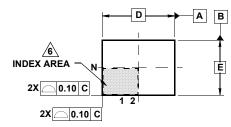

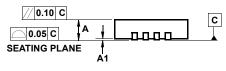

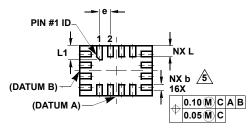

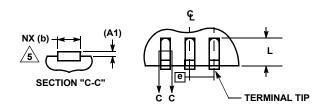

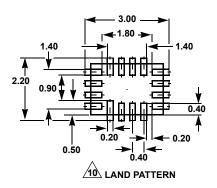

# Ultra Thin Quad Flat No-Lead Plastic Package (UTQFN)

BOTTOM VIEW

L16.2.6x1.8A

16 LEAD ULTRA THIN QUAD FLAT NO-LEAD PLASTIC PACKAGE

|        | MILLIMETERS |           |      |       |

|--------|-------------|-----------|------|-------|

| SYMBOL | MIN         | NOMINAL   | MAX  | NOTES |

| А      | 0.45        | 0.50      | 0.55 | -     |

| A1     | -           | -         | 0.05 | -     |

| A3     |             | 0.127 REF |      | -     |

| b      | 0.15        | 0.20      | 0.25 | 5     |

| D      | 2.55        | 2.60      | 2.65 | -     |

| E      | 1.75        | 1.80      | 1.85 | -     |

| е      | 0.40 BSC    |           |      | -     |

| L      | 0.35        | 0.40      | 0.45 | -     |

| L1     | 0.45        | 0.50      | 0.55 | -     |

| Ν      | 16          |           |      | 2     |

| Nd     | 4           |           |      | 3     |

| Ne     | 4           |           |      | 3     |

| θ      | 0           | -         | 12   | 4     |

NOTES:

1. Dimensioning and tolerancing conform to ASME Y14.5-1994.

Rev. 4 8/06

- 2. N is the number of terminals.

- 3. Nd and Ne refer to the number of terminals on D and E side, respectively.

- 4. All dimensions are in millimeters. Angles are in degrees.

- 5. Dimension b applies to the metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip.

- 6. The configuration of the pin #1 identifier is optional, but must be located within the zone indicated. The pin #1 identifier may be either a mold or mark feature.

- 7. Maximum package warpage is 0.05mm.

- 8. Maximum allowable burrs is 0.076mm in all directions.

- 9. JEDEC Reference MO-255.

- 10. For additional information, to assist with the PCB Land Pattern Design effort, see Intersil Technical Brief TB389.

© Copyright Intersil Americas LLC 2008. All Rights Reserved. All trademarks and registered trademarks are the property of their respective owners.

For additional products, see www.intersil.com/en/products.html

Intersil products are manufactured, assembled and tested utilizing ISO9001 quality systems as noted in the quality certifications found at <a href="http://www.intersil.com/en/support/qualandreliability.html">www.intersil.com/en/support/qualandreliability.html</a>

Intersil products are sold by description only. Intersil may modify the circuit design and/or specifications of products at any time without notice, provided that such modification does not, in Intersil's sole judgment, affect the form, fit or function of the product. Accordingly, the reader is cautioned to verify that datasheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see www.intersil.com

FN6708 Rev 0.00 August 14, 2008

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.