# ATWILC1000B-MUT IEEE® 802.11 b/g/n Link Controller SoC

### Introduction

The ATWILC1000B is a single chip IEEE® 802.11 b/g/n Radio/Baseband/MAC link controller optimized for low-power mobile applications. The ATWILC1000B supports single stream 1x1 802.11n mode providing up to 72 Mbps PHY rate. The ATWILC1000B features a fully integrated Power Amplifier (PA), Low Noise Amplifier (LNA), Switch, and Power Management. The ATWILC1000B offers very low-power consumption while simultaneously providing high performance and minimal bill of materials.

The ATWILC1000B provides multiple peripheral interfaces including Universal Asynchronous Receiver/ Transmitter (UART), Serial Peripheral Interface (SPI), Inter-Integrated Circuit (I<sup>2</sup>C), and Secure Digital Input Output (SDIO). The clock source for the ATWILC1000B is provided by an external crystal at 26 MHz. The ATWILC1000B is available in both QFN and Wafer Level Chip Scale Package (WLCSP) packaging.

### **Features**

- IEEE 802.1 b/g/n 20 MHz (1x1) Solution

- Single Spatial Stream in 2.4 GHz ISM Band

- · Integrated PA and T/R Switch

- Superior Sensitivity and Range via Advanced PHY Signal Processing

- Advanced Equalization and Channel Estimation

- · Advanced Carrier and Timing Synchronization

- Wi-Fi Direct<sup>®</sup> and Soft-AP Support

- Supports IEEE 802.11 WEP, WPA, WPA2 Security

- Superior MAC Throughput via Hardware Accelerated Two-Level A-MSDU/A-MPDU Frame Aggregation and Block Acknowledgment

- On-Chip Memory Management Engine to Reduce Host Load

- SPI, SDIO, and I<sup>2</sup>C Host Interfaces

- Operating Temperature Ranges from -40°C to +85°C

- Power Save Modes:

- <1 µA Deep Power-Down mode typical at 3.3V I/O</li>

- 280 µA Doze mode with chip settings preserved (used for beacon monitoring)

- On-chip low-power sleep oscillator

- Fast host wake up from Doze mode by a pin or host I/O transaction

**Datasheet** DS70005386A-page 1

## **Table of Contents**

| Int | roduc | tion                                               | 1  |

|-----|-------|----------------------------------------------------|----|

| Fe  | ature | S                                                  | 1  |

| 1.  | Orde  | ering Information and IC Marking                   | 4  |

| 2.  | Bloc  | k Diagram                                          | 5  |

| 3.  | Pino  | ut and Package Information                         | 6  |

|     | 3.1.  | Pin Description                                    |    |

|     | 3.2.  | Package Description                                | 13 |

| 4.  | Elec  | trical Specifications                              | 15 |

|     | 4.1.  | Absolute Ratings                                   | 15 |

|     | 4.2.  | Recommended Operating Conditions                   | 15 |

|     | 4.3.  | DC Electrical Characteristics                      | 16 |

| 5.  | Cloc  | king                                               | 17 |

|     | 5.1.  | Crystal Oscillator                                 | 17 |

|     | 5.2.  | Low-Power Oscillator                               | 18 |

| 6.  | CPU   | l and Memory Subsystem                             | 19 |

|     | 6.1.  | Processor                                          | 19 |

|     | 6.2.  | Memory Subsystem                                   | 19 |

|     | 6.3.  | Nonvolatile Memory (eFuse)                         | 19 |

| 7.  | WLA   | N Subsystem                                        | 21 |

|     | 7.1.  | MAC                                                | 21 |

|     | 7.2.  | PHY                                                | 22 |

|     | 7.3.  | Radio                                              | 22 |

| 8.  | Exte  | rnal Interfaces                                    | 27 |

|     | 8.1.  | I <sup>2</sup> C Slave Interface                   | 27 |

|     | 8.2.  | I <sup>2</sup> C Master Interface                  | 28 |

|     | 8.3.  | SPI Slave Interface                                |    |

|     | 8.4.  | SPI Master Interface                               |    |

|     | 8.5.  | SDIO Slave Interface                               |    |

|     | 8.6.  | UART Debug Interface                               |    |

|     | 8.7.  | GPIOs                                              | 35 |

| 9.  | Pow   | er Management                                      | 36 |

|     | 9.1.  | Power Architecture                                 | 36 |

|     | 9.2.  | Power Consumption                                  |    |

|     | 9.3.  | Power-Up/Down Sequence                             |    |

|     | 9.4.  | Digital I/O Pin Behavior During Power-up Sequences | 40 |

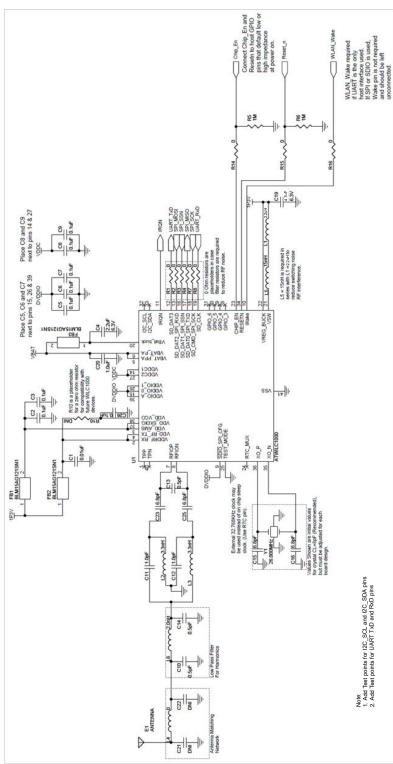

| 10. Reference Design                       | 41 |

|--------------------------------------------|----|

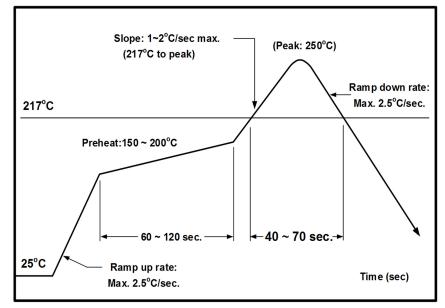

| 11. Reflow Profile Information             | 42 |

| 11.1. Storage Condition                    | 42 |

| 11.2. Solder Paste                         | 42 |

| 11.3. Stencil Design                       | 42 |

| 11.4. Printing Process                     | 42 |

| 11.5. Baking Conditions                    |    |

| 11.6. Soldering and Reflow Condition       | 43 |

| 12. Reference Documentation and Support    | 45 |

| 13. Document Revision History              | 46 |

| The Microchip Web Site                     | 47 |

| Customer Change Notification Service       | 47 |

| Customer Support                           | 47 |

| Microchip Devices Code Protection Feature  | 47 |

| Legal Notice                               | 48 |

| Trademarks                                 | 48 |

| Quality Management System Certified by DNV | 49 |

| Worldwide Sales and Service                | 50 |

## 1. Ordering Information and IC Marking

The following table provides the ordering details of the ATWILC1000B IC.

## Table 1-1. Ordering Details

| Ordering Code <sup>(1)</sup> | Package Type                          | IC Marking  |

|------------------------------|---------------------------------------|-------------|

| ATWILC1000B-MU-ABCD          | 5 x 5 QFN in Tape and Reel            | ATWILC1000B |

| ATWILC1000B-UU-ABCD          | 3.24 x 3.24 mm WLCSP in Tape and Reel | ATWILC1000B |

#### Note:

1. ABCD interprets as:

"A" can be "Y" indicating Tray, or "T" indicating Tape and Reel.

"BCD" equals to "042" for part assigned with MAC ID and blank for part with no MAC ID.

The following table lists possible combinations for ordering the ATWILC1000B-MU and ATWILC1000B-UU.

| Ordering Code       | Description                               |

|---------------------|-------------------------------------------|

| ATWILC1000B-MU-T    | No MAC ID and ship in Tape and Reel       |

| ATWILC1000B-MU-Y    | No MAC ID and ship in Tray                |

| ATWILC1000B-MU-Y042 | MAC ID assigned and ship in Tray          |

| ATWILC1000B-MU-T042 | MAC ID assigned and ship in Tape and Reel |

| ATWILC1000B-UU-T    | No MAC ID and ship in Tape and Reel       |

| ATWILC1000B-UU-Y    | No MAC ID and ship in Tray                |

| ATWILC1000B-UU-Y042 | MAC ID assigned and ship in Tray          |

| ATWILC1000B-UU-T042 | MAC ID assigned and ship in Tape and Reel |

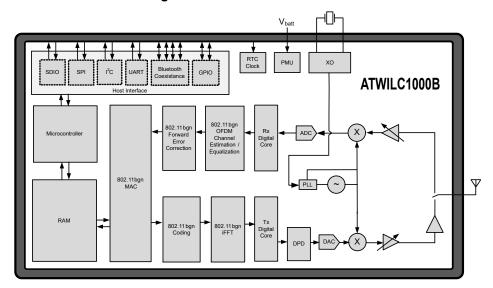

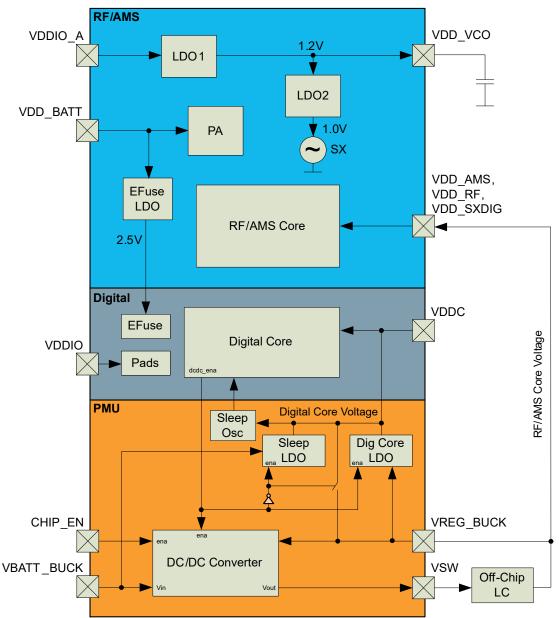

# 2. Block Diagram

The following figure provides a basic overview of the ATWILC1000B IC.

Figure 2-1. ATWILC1000B Block Diagram

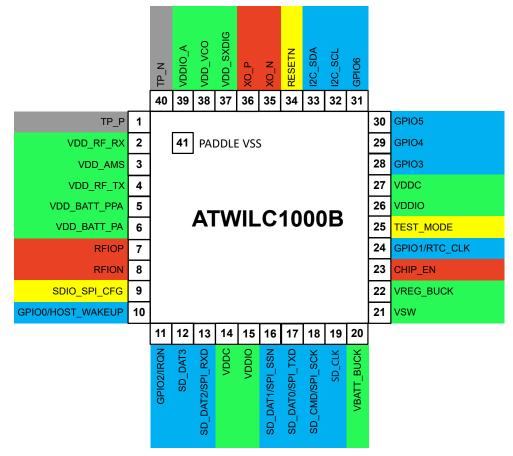

## 3. Pinout and Package Information

## 3.1 Pin Description

The ATWILC1000B is offered in an exposed pad 40-pin QFN package. This package has an exposed paddle that must be connected to the system board ground. The QFN package pin assignment and the WLCSP package pin assignment are shown in the following figures. The color shading is used to indicate the pin type as follows:

- · Green power

- Red analog

- · Blue digital I/O

- · Yellow digital input

- · Grey unconnected or reserved

Figure 3-1. Pin Assignment

Figure 3-2. WLCSP Package Pin Assignment

The ATWILC1000B pins are described in the following table.

Table 3-1. Pin Description

| QFN Pin Number | WLCSP Pin<br>Number | Pin Name  | Pin Type | Description                                                   |

|----------------|---------------------|-----------|----------|---------------------------------------------------------------|

| 1              | C6                  | TP_P      | Analog   | Test Pin/No<br>Connect                                        |

| 2              | B7                  | VDD_RF_RX | Power    | Tuner RF Supply<br>(see Section 9.1<br>Power<br>Architecture) |

| continued      |                     |                     |                                         |                                                                               |

|----------------|---------------------|---------------------|-----------------------------------------|-------------------------------------------------------------------------------|

| QFN Pin Number | WLCSP Pin<br>Number | Pin Name            | Pin Type                                | Description                                                                   |

| 3              | Н8                  | VDD_AMS             | Power                                   | Tuner BB Supply<br>(see Section 9.1<br>Power<br>Architecture)                 |

| 4              | -                   | VDD_RF_TX           | Power                                   | Tuner RF Supply<br>(see Section 9.1<br>Power<br>Architecture)                 |

| 5              | -                   | VDD_BATT_PPA        | Power                                   | PA 1 <sup>ST</sup> Stage<br>Supply (see<br>Section 9.1 Power<br>Architecture) |

| 6              | D7                  | VDD_BATT_PA         | Power                                   | PA 2 <sup>ND</sup> Stage<br>Supply (see<br>Section 9.1 Power<br>Architecture) |

| 7              | -                   | RFIOP               | Analog                                  | Positive RF<br>Differential I/O (see<br>Table 9-4)                            |

| 8              | -                   | RFION               | Analog                                  | Negative RF<br>Differential I/O (see<br>Table 9-4)                            |

| 9              | G7                  | SDIO_SPI_CFG        | Digital Input                           | Tie to 1 for SPI, 0 for SDIO                                                  |

| 10             | F6                  | GPIO0/<br>HOST_WAKE | Digital I/O,<br>Programmable<br>Pull-up | GPIO0/SLEEP<br>Mode Control                                                   |

| 11             | F5                  | GPIO2/IRQN          | Digital I/O,<br>Programmable<br>Pull-up | GPIO2/Device<br>Interrupt                                                     |

| 12             | F4                  | SD_DAT3             | Digital I/O,<br>Programmable<br>Pull-up | SDIO Data3                                                                    |

| 13             | G5                  | SD_DAT2/<br>SPI_RXD | Digital I/O,<br>Programmable<br>Pull-up | SDIO Data2/SPI<br>Data RX                                                     |

| 14             | C1                  | VDDC                | Power                                   | Digital Core Power<br>Supply (see<br>Section 9.1 Power<br>Architecture)       |

| continued      | continued           |                     |                                         |                                                                                     |  |  |  |

|----------------|---------------------|---------------------|-----------------------------------------|-------------------------------------------------------------------------------------|--|--|--|

| QFN Pin Number | WLCSP Pin<br>Number | Pin Name            | Pin Type                                | Description                                                                         |  |  |  |

| 15             | D1                  | VDDIO               | Power                                   | Digital I/O Power<br>Supply (see<br>Section 9.1 Power<br>Architecture)              |  |  |  |

| 16             | G4                  | SD_DAT1/<br>SPI_SSN | Digital I/O,<br>Programmable<br>Pull-up | SDIO Data1/SPI<br>Slave Select                                                      |  |  |  |

| 17             | G3                  | SD_DAT0/<br>SPI_TXD | Digital I/O,<br>Programmable<br>Pull-up | SDIO Data0/SPI<br>Data TX                                                           |  |  |  |

| 18             | Н3                  | SD_CMD/<br>SPI_SCK  | Digital I/O,<br>Programmable<br>Pull-up | SDIO<br>Command/SPI<br>Clock                                                        |  |  |  |

| 19             | G2                  | SD_CLK              | Digital I/O,<br>Programmable<br>Pull-up | SDIO Clock                                                                          |  |  |  |

| 20             | H2                  | VBATT_BUCK          | Power                                   | Battery Supply for<br>DC/DC Converter<br>(see Section 9.1<br>Power<br>Architecture) |  |  |  |

| 21             | H1                  | VSW                 | Power                                   | Switching output of DC/DC Converter (see Section 9.1 Power Architecture)            |  |  |  |

| 22             | F3                  | VREG_BUCK           | Power                                   | Core Power from DC/DC Converter (see Section 9.1 Power Architecture)                |  |  |  |

| 23             | F2                  | CHIP_EN             | Analog                                  | PMU Enable                                                                          |  |  |  |

| 24             | E2                  | GPIO1/RTC_CLK       | Digital I/O,<br>Programmable<br>Pull-up | GPIO1/32kHz<br>Clock Input                                                          |  |  |  |

| 25             | D2                  | TEST_MODE           | Digital Input                           | Test Mode – User<br>must tie this pin to<br>GND                                     |  |  |  |

| continued      |                     |           |                                         |                                                                         |

|----------------|---------------------|-----------|-----------------------------------------|-------------------------------------------------------------------------|

| QFN Pin Number | WLCSP Pin<br>Number | Pin Name  | Pin Type                                | Description                                                             |

| 26             | H5                  | VDDIO     | Power                                   | Digital I/O Power<br>Supply (see<br>Section 9.1 Power<br>Architecture)  |

| 27             | Н6                  | VDDC      | Power                                   | Digital Core Power<br>Supply (see<br>Section 9.1 Power<br>Architecture) |

| 28             | E3                  | GPIO3     | Digital I/O,<br>Programmable<br>Pull-up | GPIO3/<br>SPI_SCK_Flash                                                 |

| 29             | D3                  | GPIO4     | Digital I/O,<br>Programmable<br>Pull-up | GPIO4/<br>SPI_SSN_Flash                                                 |

| 30             | B2                  | GPIO5     | Digital I/O,<br>Programmable<br>Pull-up | GPIO5/<br>SPI_TXD_Flash                                                 |

| 31             | A1                  | GPIO6     | Digital I/O,<br>Programmable<br>Pull-up | GPIO6/<br>SPI_RXD_Flash                                                 |

| 32             | A2                  | I2C_SCL   | Digital I/O,<br>Programmable<br>Pull-up | I <sup>2</sup> C Slave Clock<br>(high-drive pad,<br>see Table 4-3)      |

| 33             | В3                  | I2C_SDA   | Digital I/O,<br>Programmable<br>Pull-up | I <sup>2</sup> C Slave Data<br>(high-drive pad,<br>see Table 4-3)       |

| 34             | A3                  | RESETN    | Digital Input                           | Active-Low Hard<br>Reset                                                |

| 35             | A4                  | XO_N      | Analog                                  | Crystal Oscillator N                                                    |

| 36             | B4                  | XO_P      | Analog                                  | Crystal Oscillator P                                                    |

| 37             | A6                  | VDD_SXDIG | Power                                   | SX Power Supply<br>(see Section 9.1<br>Power<br>Architecture)           |

| 38             | -                   | VDD_VCO   | Power                                   | VCO Power Supply<br>(see Section 9.1<br>Power<br>Architecture)          |

| continued         |                     |              |                                         |                                                               |

|-------------------|---------------------|--------------|-----------------------------------------|---------------------------------------------------------------|

| QFN Pin Number    | WLCSP Pin<br>Number | Pin Name     | Pin Type                                | Description                                                   |

| 39                | A7                  | VDDIO_A      | Power                                   | Tuner VDDIO Power Supply (see Section 9.1 Power Architecture) |

| 40                | B6                  | TP_N         | Analog                                  | Test Pin/No<br>Connect                                        |

| 41 <sup>(1)</sup> | -                   | PADDLE VSS   | Ground                                  | Connect to System Board Ground                                |

| -                 | A5                  | GND_SXDIG    | Ground                                  | SX Ground,<br>Connect to System<br>Board Ground               |

| -                 | B1                  | GPIO16       | Digital I/O,<br>Programmable<br>Pull-up | GPIO16                                                        |

| -                 | B5                  | GND_IO       | Ground                                  | I/O Ground,<br>Connect to System<br>Board Ground              |

| -                 | B8                  | NC           | None                                    | Reserved/No<br>Connect                                        |

| -                 | C2                  | GPIO15       | Digital I/O,<br>Programmable<br>Pull-up | GPIO15                                                        |

| -                 | C3                  | GPIO17       | Digital I/O,<br>Programmable<br>Pull-up | GPIO17                                                        |

| -                 | C4                  | GPIO18       | Digital I/O,<br>Programmable<br>Pull-up | GPIO18                                                        |

| -                 | C5                  | GPIO13       | Digital I/O,<br>Programmable<br>Pull-up | GPIO13                                                        |

| -                 | C7                  | GND_RF_RX    | Ground                                  | RF Rx Ground,<br>Connect to System<br>Board Ground            |

| -                 | D8                  | GND_BATT_PPA | Ground                                  | PA 2nd Stage<br>Ground, Connect<br>to System Board<br>Ground  |

## **Pinout and Package Information**

| continued      |                     |             |                                         |                                                                 |  |  |

|----------------|---------------------|-------------|-----------------------------------------|-----------------------------------------------------------------|--|--|

| QFN Pin Number | WLCSP Pin<br>Number | Pin Name    | Pin Type                                | Description                                                     |  |  |

| -              | E1                  | VSS         | Ground                                  | Connect to System<br>Board Ground                               |  |  |

| -              | E7                  | GND_BATT_PA | Ground                                  | PA 1st Stage<br>Ground, Connect<br>to System Board<br>Ground    |  |  |

| -              | F1                  | GND_BIAS    | Ground                                  | Bias Ground,<br>Connect to System<br>Board Ground               |  |  |

| -              | F7                  | GND_AMS     | Ground                                  | AMS Ground,<br>Connect to System<br>Board Ground                |  |  |

| -              | F8                  | TX_P        | Analog                                  | Positive RF<br>Differential I/O                                 |  |  |

| -              | G1                  | GND_BUCK    | Ground                                  | DC/DC Converter<br>Ground, Connect<br>to System Board<br>Ground |  |  |

| -              | G6                  | GPIO12      | Digital I/O,<br>Programmable<br>Pull-up | GPIO12                                                          |  |  |

| -              | G8                  | TX_N        | Analog                                  | Negative RF<br>Differential I/O                                 |  |  |

| -              | H4                  | VSS         | Ground                                  | Connect to System<br>Board Ground                               |  |  |

| -              | H7                  | GPIO11      | Digital I/O,<br>Programmable<br>Pull-up | GPIO11                                                          |  |  |

#### Note:

1. Applies to QFN package only. Pin 41, PADDLE\_VSS must be soldered to GND providing good RF grounding and good heat dissipation.

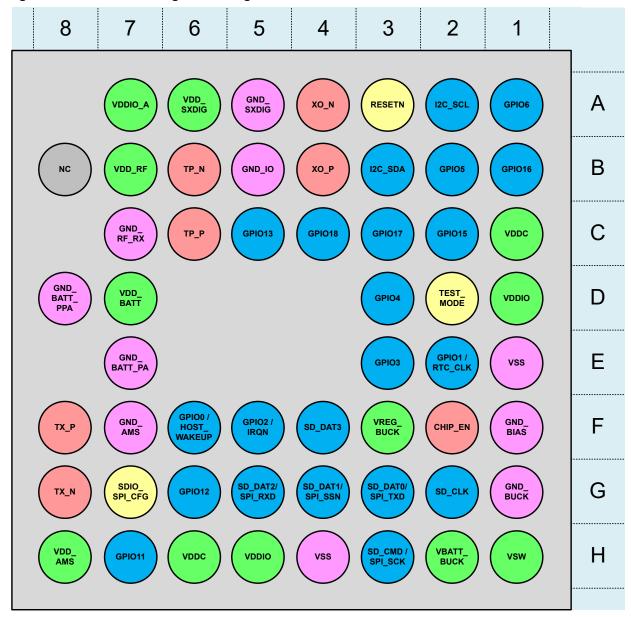

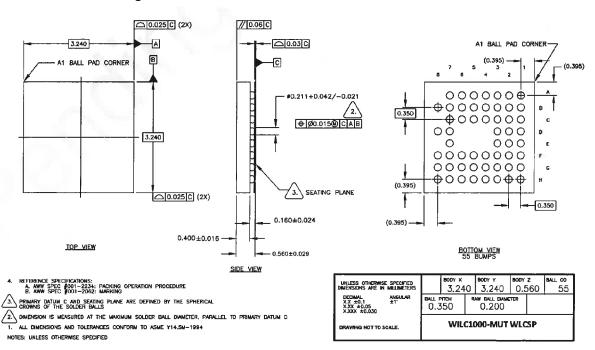

Figure 3-3. WLCSP ATWILC1000B UU

| 8           | 7            | 6           | 5        | 4       | 3               | 2          | 1        |   |

|-------------|--------------|-------------|----------|---------|-----------------|------------|----------|---|

|             | VDDA_IO      | VDDSXDIG    | GNDSXDIG | XON     | RESET           | I2C_SCL    | GPIO_6   | Α |

| NC          | VDDRF        | TPN         | GNDIO    | XOP     | I2C_SDA         | GPIO_5     | GPIO_16  | В |

|             | GNDRF_RX     | TPP         | GPIO_13  | GPIO_18 | GPIO_17         | GPIO_15    | VDD      | С |

| GNDBATT_PPA | VDDBATT      |             |          |         | GPIO_4          | TESTMODE   | VDDIO    | D |

|             | GNDBATT_PA   |             |          |         | GPIO_3          | RTC_CLK    | VSS      | Е |

| TXP         | GNDAMS       | HOST_WAKEUP | IRQN     | SD_DAT3 | VREGBUCK        | CHIPEN     | GND_BIAS | F |

| TXN         | SDIO_SPI_CFG | GPIO_12     | SD_DAT2  | SD_DAT1 | SD_DATO_SPI_TXD | SD_CLK     | GNDBUCK  | G |

| VDDAMS      | GPIO_11      | VDD         | VDDIO    | VSS     | SD_CMD_SPI_SCK  | VBATT_BUCK | VSW      | Н |

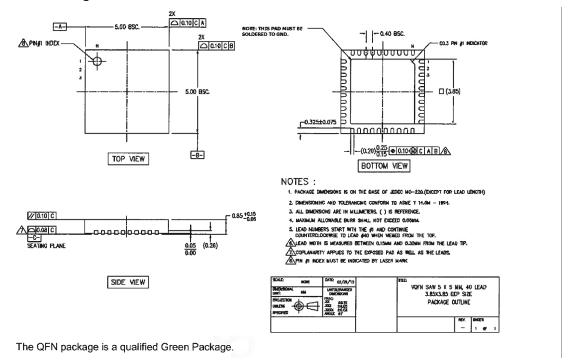

## 3.2 Package Description

The ATWILC1000B QFN package information is provided in the following table and the package view is shown in Figure 3-4.

Table 3-2. QFN Package Information

| Parameter        | Value     | Unit | Tolerance      |

|------------------|-----------|------|----------------|

| Package size     | 5 x 5     | mm   | ±0.1 mm        |

| QFN pad count    | 40        | _    | -              |

| Total thickness  | 0.85      | mm   | +/0.15/-0.05mm |

| QFN pad pitch    | 0.40      |      | -              |

| Pad width        | 0.20      |      | _              |

| Exposed pad size | 3.7 x 3.7 |      | _              |

The ATWILC1000B WLCSP package information is provided in the following table and the package view is shown in the Figure 3-5.

Table 3-3. WLCSP Package Information

| Parameter       | Value       | Unit | Tolerance |

|-----------------|-------------|------|-----------|

| Package size    | 3.24 x 3.24 |      | ±0.3 mm   |

| Total thickness | 0.56        | mm   | ±0.3 mm   |

| I/O Pitch       | 0.35        | mm   | _         |

| Ball diameter   | 0.20        |      | ±0.3 mm   |

Figure 3-4. QFN Package

Figure 3-5. WLCSP Package

## 4. Electrical Specifications

## 4.1 Absolute Ratings

The values listed in this section are the peaked excursions ratings that can be tolerated by the device, and if sustained will cause irreparable damage to the device.

Table 4-1. Absolute Maximum Ratings

| Characteristics        | Symbol                          | Min.                        | Max.                        | Unit |

|------------------------|---------------------------------|-----------------------------|-----------------------------|------|

| Core supply voltage    | VDDC                            | -0.3                        | 1.5                         |      |

| I/O supply voltage     | VDDIO                           | -0.3                        | 5.0                         |      |

| Battery supply voltage | VBATT                           | -0.3                        | 5.0                         | V    |

| Digital input voltage  | V <sub>IN</sub> <sup>(1)</sup>  | -0.3                        | VDDIO                       | V    |

| Analog input voltage   | V <sub>AIN</sub> <sup>(2)</sup> | -0.3                        | 1.5                         |      |

| ESD human body model   | V <sub>ESDHBM</sub> (3)         | -1000, -2000 <sup>(3)</sup> | +1000, +2000 <sup>(3)</sup> |      |

| Storage temperature    | T <sub>A</sub>                  | -65                         | 150                         | °C   |

| Junction temperature   | _                               | _                           | 125                         |      |

| RF input power max.    | _                               | _                           | 23                          | dBm  |

#### Note:

- 1. V<sub>IN</sub> corresponds to all the digital pins.

- 2. V<sub>AIN</sub> corresponds to the following analog pins: VDD\_RF\_RX, VDD\_RF\_TX, VDD\_AMS, RFIOP, RFION, XO\_N, XO\_P, VDD\_SXDIG, and VDD\_VCO.

- 3. For V<sub>ESDHBM</sub>, each pin is classified as Class 1, or Class 2, or both:

- The Class 1 pins include all the pins (both analog and digital).

- The Class 2 pins are all digital pins only.

- V<sub>ESDHBM</sub> is ±1 kV for Class 1 pins. V<sub>ESDHBM</sub> is ±2 kV for Class 2 pins.

## 4.2 Recommended Operating Conditions

The recommended operating conditions for the ATWILC1000B are listed in the following table.

**Table 4-2. Recommended Operating Conditions**

| Characteristics        | Symbol | Min. | Тур. | Max. | Unit |

|------------------------|--------|------|------|------|------|

| I/O supply voltage     | VDDIO  | 2.7  | 3.3  | 3.6  | V    |

| Battery supply voltage | VBATT  | 3.00 | 3.30 | 4.20 | V    |

| Operating temperature  | -      | -40  | _    | 85   | °C   |

#### Note:

- 1. The ATWILC1000B is functional across this range of voltages; however, optimal RF performance is ensured for VBATT in the range 3.0V < VBATT < 4.2V.

- 2. I/O supply voltage is applied to the VDDIO\_A, and VDDIO pins.

- 3. Battery supply voltage is applied to the VDD\_BATT\_PPA, VDD\_BATT\_PA, and VBATT\_BUCK pins.

- 4. See Table 9-4 for the details of power connections.

#### 4.3 DC Electrical Characteristics

The following table provides the DC characteristics for the ATWILC1000B digital pads.

Table 4-3. DC Electrical Characteristics

| Characteristic                                    | Min.       | Тур. | Max.       | Unit |

|---------------------------------------------------|------------|------|------------|------|

| Input Low Voltage (V <sub>IL</sub> )              | -0.30      | _    | 0.60       |      |

| Input High Voltage (V <sub>IH</sub> )             | VDDIO-0.60 | _    | VDDIO+0.30 | V    |

| Output Low<br>Voltage (V <sub>OL</sub> )          | _          | _    | 0.45       | V    |

| Output High<br>Voltage (OV <sub>OH</sub> )        | VDDIO-0.50 | _    | _          |      |

| Output Loading                                    | _          | _    | 20         | pF   |

| Digital Input Load                                | _          | _    | 6          | рг   |

| Pad Drive Strength (regular pads <sup>(1)</sup> ) | 10.6       | 13.5 | _          | mA   |

| Pad Drive Strength (high-drive pads (1))          | 21.2       | 27   | _          | IIIA |

### Note:

1. The following are high-drive pads: I2C\_SCL, I2C\_SDA; all other pads are regular.

## 5. Clocking

### 5.1 Crystal Oscillator

The following table provides the crystal oscillator parameters of the ATWILC1000B.

Table 5-1. Crystal Oscillator Parameters

| Parameter                                 | Min. | Тур. | Max. | Unit |

|-------------------------------------------|------|------|------|------|

| Crystal resonant frequency                | _    | 26   | _    | MHz  |

| Crystal equivalent series resistance      | _    | 50   | 150  | Ω    |

| Stability – Initial offset <sup>(1)</sup> | -100 | _    | 100  | nnm  |

| Stability - Temperature and aging         | -25  | _    | 25   | ppm  |

#### Note:

1. To ensure ±25 ppm under operating conditions, frequency offset calibration is required.

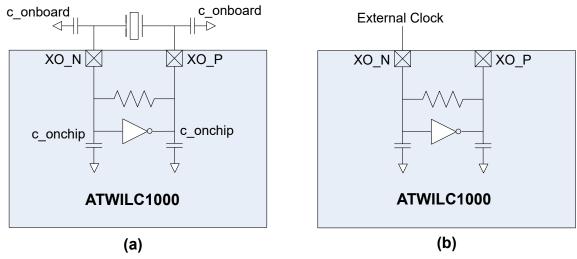

The following block diagram in figure "XO Connections - (a)" shows how the internal Crystal Oscillator (XO) is connected to the external crystal. The XO has 5 pF internal capacitance, (denoted as c\_onchip in the following figure) on each terminal XO\_P and XO\_N. To bypass the crystal oscillator with an external reference, an external signal capable of driving 5 pF can be applied to the XO\_N terminal as shown in following figure "XO Connections - (b)". The XO has 5 pF internal capacitance on each terminal XO\_P and XO\_N. This internal capacitance must be accounted for when calculating the external loading capacitance, c\_onboard, for the XTAL.

Figure 5-1. XO Connections: (a) The Crystal Oscillator is Used, (b) The Crystal Oscillator is Bypassed

The following table specifies the electrical and performance requirements for the external clock.

Table 5-2. Bypass Clock Specification

| Parameter                               | Min. | Тур. | Max. | Unit            | Comments                                                                 |

|-----------------------------------------|------|------|------|-----------------|--------------------------------------------------------------------------|

| Oscillation frequency                   | _    | 26   | -    | MHz             | Must drive 5 pF<br>load at desired<br>frequency                          |

| Voltage swing                           | 0.5  | _    | 1.2  | V <sub>PP</sub> | Must be AC coupled                                                       |

| Stability –<br>Temperature<br>and aging | -25  | _    | +25  | ppm             | _                                                                        |

| Phase noise                             | _    | _    | -130 | dBc/Hz          | At 10 kHz offset                                                         |

| Jitter (RMS)                            | _    | _    | <1   | psec            | Based on<br>integrated<br>phase noise<br>spectrum from<br>1 kHz to 1 MHz |

### 5.2 Low-Power Oscillator

The ATWILC1000B has an internally-generated 32 kHz clock to provide timing information for various sleep functions. Alternatively, the ATWILC1000B allows for an external 32kHz clock to be used for this purpose, which is provided through pin 24 (RTC\_CLK). Software selects whether the internal clock or external clock is used.

The internal low-power clock is ring oscillator-based and has accuracy within 10,000 ppm. When using the internal low-power clock, the advance wake-up time in the Beacon Monitoring mode has to be increased by about 1% of the sleep time to compensate for the oscillator inaccuracy. For example, for the DTIM interval value of 1, wake-up time has to be increased by 1 ms.

For any application targeting very low-power consumption, an external 32 kHz RTC clock must be used.

## 6. CPU and Memory Subsystem

#### 6.1 Processor

The ATWILC1000B has a Cortus APS3 32-bit processor. This processor performs many of the MAC functions, including but not limited to: association, authentication, power management, security key management, and MSDU aggregation/de-aggregation. In addition, the processor provides flexibility for various modes of operation, such as STA and AP modes.

## 6.2 Memory Subsystem

The APS3 core uses a 128 KB instruction/boot ROM along with a 160 KB instruction RAM and a 64 KB data RAM. In addition, the device uses a 128 KB shared RAM, accessible by the processor and MAC, which allows the APS3 core to perform various data management tasks on the TX and RX data packets.

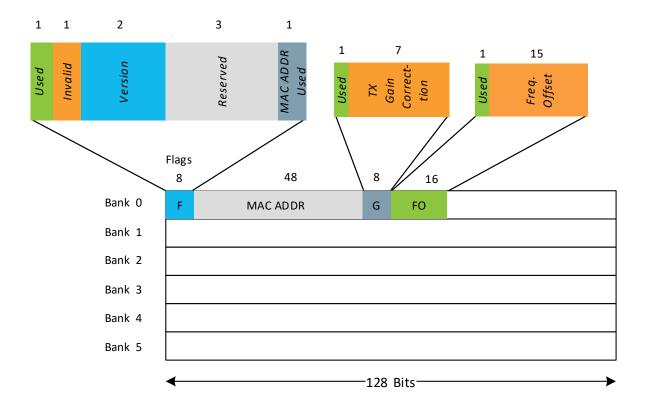

### 6.3 Nonvolatile Memory (eFuse)

The ATWILC1000B has 768 bits of nonvolatile eFuse memory that can be read by the CPU after device reset. This nonvolatile One-Time-Programmable (OTP) memory can be used to store customer-specific parameters, such as MAC address; various calibration information, such as TX power, crystal frequency offset, other software-specific configuration parameters, and so on. The eFuse is partitioned into six 128-bit banks. Each bank has the same bit map, which is shown in the following figure. The purpose of the first 80 bits in each bank is fixed, and the remaining 48 bits are general-purpose software dependent bits, or reserved for future use. Since each bank can be programmed independently, this allows for several updates of the device parameters following the initial programming, e.g., updating the MAC address. Refer to the ATWILC1000 Programming Guide for the eFuse programming instructions.

Figure 6-1. eFuse Bit Map

## 7. WLAN Subsystem

The WLAN subsystem is composed of the Media Access Controller (MAC) and the Physical Layer (PHY). The following two subsections describe the MAC and PHY in detail.

#### 7.1 MAC

#### 7.1.1 Features

The ATWILC1000B IEEE802.11 MAC supports the following functions:

- IEEE 802.11b/g/n

- IEEE 802.11e WMM QoS EDCA/PCF Multiple Access Categories Traffic Scheduling

- · Advanced IEEE 802.11n Features:

- Transmission and reception of aggregated MPDUs (A-MPDU)

- Transmission and reception of aggregated MSDUs (A-MSDU)

- Immediate Block Acknowledgment

- Reduced Interframe Spacing (RIFS)

- · Support for IEEE 802.11i and WFA Security with Key Management

- WEP 64/128

- WPA-TKIP

- 128-bit WPA2 CCMP (AES)

- · Support for WAPI Security

- · Advanced Power Management

- Standard 802.11 Power Save mode

- Wi-Fi Alliance<sup>®</sup> WMM-PS (U-APSD)

- RTS-CTS and CTS-Self Support

- Supports Either STA or AP Mode in the Infrastructure Basic Service Set Mode

- Supports Independent Basic Service Set (IBSS)

#### 7.1.2 Description

The ATWILC1000B MAC is designed to operate at low power while providing high data throughput. The IEEE 802.11 MAC functions are implemented with a combination of dedicated datapath engines, hardwired control logic, and a low-power, high-efficiency microprocessor. The combination of dedicated logic with a programmable processor provides optimal power efficiency and real-time response while providing the flexibility to accommodate evolving standards and future feature enhancements.

Dedicated datapath engines with heavy computational are used to implement datapath functions. For example, an FCS engine checks the CRC of the transmitting and receiving packets, and a cipher engine performs all the required encryption and decryption operations for the WEP, WPA-TKIP, WPA2 CCMP-AES, and WAPI security requirements.

Control functions which have real-time requirements are implemented using hardwired control logic modules. These logic modules offer real-time response while maintaining configurability via the processor. Examples of hardwired control logic modules are: the channel access control module (implements EDCA/HCCA, Beacon TX control, interframe spacing, and so on.), protocol timer module (responsible for the Network Access Vector, back-off timing, timing synchronization function, and slot management), MPDU handling module, aggregation/deaggregation module, block ACK controller

(implements the protocol requirements for burst block communication), and TX/RX control FSMs (coordinate data movement between PHY-MAC interface, cipher engine, and the DMA interface to the TX/RX FIFOs).

The MAC functions that are implemented in software on the microprocessor have the following characteristics:

- Functions with high memory requirements or complex data structures. Examples are association table management and power save queuing.

- Functions with low computational load or without critical real-time requirements. Examples are authentication and association.

- Functions which need flexibility and upgradeability. Examples are beacon frame processing and QoS scheduling.

#### 7.2 PHY

#### 7.2.1 Features

The ATWILC1000B IEEE 802.11 PHY supports the following functions:

- · Single Antenna 1x1 Stream in 20 MHz Channels

- Supports IEEE 802.11b DSSS-CCK Modulation: 1, 2, 5.5, and 11 Mbps

- Supports IEEE 802.11g OFDM Modulation: 6, 9, 12,18, 24, 36, 48, and 54 Mbps

- Supports IEEE 802.11n HT Modulations MCS0-7, 20 MHz, 800 and 400 ns guard interval: 6.5, 7.2, 13.0, 14.4, 19.5, 21.7, 26.0, 28.9, 39.0, 43.3, 52.0, 57.8, 58.5, 65.0, and 72.2 Mbps

- IEEE 802.11n Mixed Mode Operation

- Per Packet TX Power Control

- Advanced Channel Estimation/Equalization, Automatic Gain Control, CCA, Carrier/Symbol Recovery, and Frame Detection

#### 7.2.2 Description

The ATWILC1000B WLAN PHY is designed to achieve reliable and power-efficient physical layer communication specified by IEEE 802.11 b/g/n in Single Stream mode with 20 MHz bandwidth. Advanced algorithms are used to achieve maximum throughput in a real-world communication environment with impairments and interference. The PHY implements all the required functions such as FFT, filtering, FEC (Viterbi decoder), frequency and timing acquisition and tracking, channel estimation and equalization, carrier sensing and clear channel assessment, as well as the automatic gain control.

#### 7.3 Radio

This section describes the properties and characteristics of the ATWILC1000B and Wi-Fi radio transmit and receive performance capabilities of the device. The performance measurements are taken at the RF pin assuming  $50\Omega$  impedance; the RF performance is assured for room temperature of  $25^{\circ}$ C with a derating of 2-3dB at boundary conditions.

Measurements were taken under typical conditions: VBATT at 3.3V; VDDIO at 3.3V ,and temperature at +25°C.

**Table 7-1. Features and Properties**

| Feature                              | Description                                                               |

|--------------------------------------|---------------------------------------------------------------------------|

| Part Number                          | ATWILC1000B                                                               |

| WLAN Standard                        | IEEE 802.11b/g/n, Wi-Fi compliant                                         |

| Host Interface                       | SPI, SDIO                                                                 |

| Dimension                            | L x W x H: 21.7 x 14.7 x 2.1 (typical) mm                                 |

| Frequency range                      | 2.412 GHz ~ 2.472 GHz (2.4 GHz ISM band)                                  |

| Number of channels                   | 11 for North America, 13 for Europe                                       |

| Modulation                           | 802.11b: DQPSK, DBPSK, CCK                                                |

|                                      | 802.11g/n: OFDM/64-QAM,16-QAM, QPSK, BPSK                                 |

| Data rate                            | 802.11b: 1, 2, 5.5, 11 Mbps<br>802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps |

| Data rate                            | 802.11n: 7.2, 14.4, 21.7, 28.9, 43.3, 57.8, 65,72.2                       |

| (20 MHz ,short GI,400ns)             | Mbps                                                                      |

| Operating temperature <sup>(1)</sup> | -40°C to 85°C                                                             |

| Storage temperature                  | -40°C to 125°C                                                            |

| Humidity                             | Operating humidity 10% to 95% non-condensing                              |

|                                      | Storage humidity 5% to 95% non-condensing                                 |

#### Note:

1. RF performance is ensured at room temperature of 25°C with a 2-3db change at boundary conditions.

#### 7.3.1 Receiver Performance

The following are typical conditions for radio receiver performance:

VBATT at 3.3V; VDDIO at 3.3V; temperature at 25°C and WLAN Channel 6 (2437 MHz).

The table below provides the receiver performance characteristics for the ATWILC1000B.

Table 7-2. Receiver Performance

| Parameter           | Description   | Min.  | Тур. | Max.  | Unit |

|---------------------|---------------|-------|------|-------|------|

| Frequency           | -             | 2,412 | -    | 2,472 | MHz  |

| Sensitivity 802.11b | 1 Mbps DSSS   | -     | -94  | -     |      |

|                     | 2 Mbps DSSS   | -     | -91  | -     | dBm  |

|                     | 5.5 Mbps DSSS | -     | -89  | -     |      |

|                     | 11 Mbps DSSS  | -     | -86  | -     |      |

WLAN Subsystem

| continued                          |                                   |      |      |      |      |  |

|------------------------------------|-----------------------------------|------|------|------|------|--|

| Parameter                          | Description                       | Min. | Тур. | Max. | Unit |  |

| Sensitivity 802.11g                | 6 Mbps OFDM                       | -    | -88  | -    |      |  |

|                                    | 9 Mbps OFDM                       | -    | -87  | -    |      |  |

|                                    | 12 Mbps OFDM                      | -    | -86  | -    | dBm  |  |

|                                    | 18 Mbps OFDM                      | -    | -84  | -    |      |  |

|                                    | 24 Mbps OFDM                      | -    | -82  | -    | иын  |  |

|                                    | 36 Mbps OFDM                      | -    | -78  | -    |      |  |

|                                    | 48 Mbps OFDM                      | -    | -74  | -    |      |  |

|                                    | 54 Mbps OFDM                      | -    | -73  | -    |      |  |

| Sensitivity 802.11n (BW at 20 MHz) | MCS 0                             | -    | -87  | -    |      |  |

|                                    | MCS 1                             | -    | -85  | -    |      |  |

|                                    | MCS 2                             | -    | -83  | -    |      |  |

|                                    | MCS 3                             | -    | -80  | -    | dBm  |  |

|                                    | MCS 4                             | -    | -76  | -    | иын  |  |

|                                    | MCS 5                             | -    | -73  | -    |      |  |

|                                    | MCS 6                             | -    | -71  | -    |      |  |

|                                    | MCS 7                             | -    | -69  | -    |      |  |

| Maximum Receive Signal Level       | 1-11 Mbps DSSS                    | -    | 0    | -    |      |  |

|                                    | 6-54 Mbps OFDM                    | -    | -5   | -    | dBm  |  |

|                                    | MCS 0 - 7                         | -    | -5   | -    |      |  |

| Adjacent Channel Rejection         | 1 Mbps DSSS (30 MHz offset)       | -    | 50   | -    |      |  |

|                                    | 11 Mbps DSSS (25 MHz offset)      | -    | 43   | -    |      |  |

|                                    | 6 Mbps OFDM (25 MHz offset)       | -    | 40   | -    | dР   |  |

|                                    | 54 Mbps OFDM (25 MHz offset)      | -    | 25   | -    | dB   |  |

|                                    | MCS 0 – 20 MHz BW (25 MHz offset) | -    | 40   | -    |      |  |

|                                    | MCS 7 – 20 MHz BW (25 MHz offset) | -    | 20   | -    |      |  |

| continued                 |                     |      |      |      |      |  |  |

|---------------------------|---------------------|------|------|------|------|--|--|

| Parameter                 | Description         | Min. | Тур. | Max. | Unit |  |  |

| Cellular Blocker Immunity | 776-794 MHz CDMA    | -    | -14  | -    |      |  |  |

|                           | 824-849 MHz GSM     | -    | -10  | -    |      |  |  |

|                           | 880-915 MHz GSM     | -    | -10  | -    |      |  |  |

|                           | 1710-1785 MHz GSM   | -    | -15  | -    | dBm  |  |  |

|                           | 1850-1910 MHz GSM   | -    | -15  | -    |      |  |  |

|                           | 1850-1910 MHz WCDMA | -    | -24  | -    |      |  |  |

|                           | 1920-1980 MHz WCDMA | -    | -24  | -    |      |  |  |

### 7.3.2 Transmitter Performance

The following are typical conditions for radio transmitter performance:

VBAT=3.3V; VDDIO=3.3V; temperature at 25°C and WLAN Channel 6 (2437 MHz).

The following table provides the transmitter performance characteristics for the ATWILC1000B.

**Table 7-3. Transmitter Performance**

| Parameter                                     | Description    | Min.  | Тур.                | Max.  | Unit  |

|-----------------------------------------------|----------------|-------|---------------------|-------|-------|

| Frequency                                     | -              | 2,412 |                     | 2,472 | MHz   |

| Output power <sup>(1)-(2)</sup> , ON_Transmit | 802.11b 1Mbps  | -     | 17.6                | -     |       |

|                                               | 802.11b 11Mbps | -     | 18.2                | -     |       |

|                                               | 802.11g 6Mbps  | -     | 18.7                | -     | dBm   |

|                                               | 802.11g 54Mbps | -     | 16.7                | -     | UDIII |

|                                               | 802.11n MCS 0  | -     | 17.3                | -     |       |

|                                               | 802.11n MCS 7  | -     | 13.8                | -     |       |

| TX power accuracy                             | -              | -     | ±1.5 <sup>(2)</sup> |       | dB    |

| Carrier suppression                           | 802.11b mode   | -     | -19.4               | -     |       |

|                                               | 802.11g mode   | -     | -27.5               | -     | dBc   |

|                                               | 802.11n mode   | -     | -21.1               | -     |       |

| continued                            |                 |      |      |      |             |  |  |

|--------------------------------------|-----------------|------|------|------|-------------|--|--|

| Parameter                            | Description     | Min. | Тур. | Max. | Unit        |  |  |

| Out of band Transmit Power           | 76-108          | -    | -125 | -    |             |  |  |

|                                      | 776-794         | -    | -125 | -    |             |  |  |

|                                      | 869-960         | -    | -125 | -    |             |  |  |

|                                      | 925-960         | -    | -125 | -    | dBm/Hz      |  |  |

|                                      | 1570-1580       | -    | -125 | -    | UDIII/IIZ   |  |  |

|                                      | 1805-1880       | -    | -125 | -    |             |  |  |

|                                      | 1930-1990       | -    | -125 | -    |             |  |  |

|                                      | 2110-2170       | -    | -125 | -    |             |  |  |

| Harmonic output power <sup>(4)</sup> | 2 <sup>nd</sup> | -    | -28  | -    |             |  |  |

|                                      | 3 <sup>rd</sup> | -    | -33  | -    | dBm/MHz     |  |  |

|                                      | 4 <sup>th</sup> | -    | -40  | -    | UDIII/IVITZ |  |  |

|                                      | 5 <sup>th</sup> | -    | -28  | -    |             |  |  |

#### Note:

- 1. Measured at 802.11 specification compliant EVM/Spectral mask.

- 2. Measured after RF matching network.

- 3. Operating temperature range is -40°C to +85°C. RF performance is ensured at a room temperature range of 25°C with 2-3dB change at boundary conditions.

- 4. Measured at 11 Mbps, DG (Digital Gain) = -7, WLAN Channel 6 (2437 MHz).

- 5. With respect to TX power, different (higher/lower) RF output power settings may be used for specific antennas and/or enclosures, in which case re-certification may be required.

- 6. The availability of some specific channels and/or operational frequency bands are country dependent and should be programmed at the host product factory to match the intended destination. Regulatory bodies prohibit exposing the settings to the end user. This requirement needs to be taken care of via host implementation.

### 8. External Interfaces

The ATWILC1000B external interfaces include:

- I<sup>2</sup>C slave for control

- SPI slave and SDIO slave for control and data transfer

- · SPI master for external Flash

- I<sup>2</sup>C master for external EEPROM

- · UART Debug Interface

- · General Purpose Input/Output (GPIO) pins

### 8.1 I<sup>2</sup>C Slave Interface

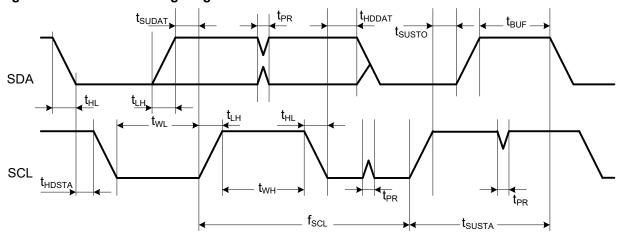

The I<sup>2</sup>C Slave interface, used primarily for control by the host processor, is a two-wire serial interface consisting of a serial data line (SDA, Pin 33) and a serial clock (SCL, pin 32). It responds to the seven bit address value 0x60. The ATWILC1000B I<sup>2</sup>C supports I<sup>2</sup>C bus Version 2.1 - 2000 and can operate in Standard mode (with data rates up to 100 Kb/s) and Fast mode (with data rates up to 400 Kb/s). The I<sup>2</sup>C Slave is a synchronous serial interface. The SDA line is a bidirectional signal and changes only while the SCL line is low, except for STOP, START, and RESTART conditions. The output drivers are open-drain to perform wire-AND functions on the bus. The maximum number of devices on the bus is limited by only the maximum capacitance specification of 400 pF. Data is transmitted in byte packages. For specific information, refer to the Philips Specification entitled "The I<sup>2</sup>C -Bus Specification, Version 2.1". The I<sup>2</sup>C Slave timing is provided in the following figure.

Figure 8-1. I<sup>2</sup>C Slave Timing Diagram

The I<sup>2</sup>C Slave timing parameters are provided in the following table.

Table 8-1. I<sup>2</sup>C Slave Timing Parameters

| Parameter            | Symbol           | Min. | Max. | Unit | Remarks |

|----------------------|------------------|------|------|------|---------|

| SCL clock frequency  | f <sub>SCL</sub> | 0    | 400  | kHz  | _       |

| SCL low pulse width  | t <sub>WL</sub>  | 1.3  | _    | 110  | _       |

| SCL high pulse width | t <sub>WH</sub>  | 0.6  | _    | μs   | _       |

| continued                            | continued          |         |      |      |                                                    |  |  |  |  |

|--------------------------------------|--------------------|---------|------|------|----------------------------------------------------|--|--|--|--|

| Parameter                            | Symbol             | Min.    | Max. | Unit | Remarks                                            |  |  |  |  |

| SCL, SDA fall time                   | t <sub>HL</sub>    | -       | 300  |      | -                                                  |  |  |  |  |

| SCL, SDA rise time                   | t <sub>LH</sub>    | _       | 300  | ns   | This is dictated by external components            |  |  |  |  |

| START setup time                     | t <sub>SUSTA</sub> | 0.6     | _    | μs   | _                                                  |  |  |  |  |

| START hold time                      | t <sub>HDSTA</sub> | 0.6     | _    | μο   | _                                                  |  |  |  |  |

| SDA setup time                       | t <sub>SUDAT</sub> | 100     | _    |      | _                                                  |  |  |  |  |

| SDA hold time                        | t <sub>HDDAT</sub> | 0<br>40 | _    | ns   | Slave and master default master programming option |  |  |  |  |

| STOP setup time                      | t <sub>SUSTO</sub> | 0.6     | _    |      | -                                                  |  |  |  |  |

| Bus free time between STOP and START | t <sub>BUF</sub>   | 1.3     | _    | μs   | _                                                  |  |  |  |  |

| Glitch pulse reject                  | t <sub>PR</sub>    | 0       | 50   | ns   | _                                                  |  |  |  |  |

### 8.2 I<sup>2</sup>C Master Interface

The ATWILC1000B provides an I<sup>2</sup>C bus master, which is intended primarily for accessing an external EEPROM memory through a software-defined protocol. The I<sup>2</sup>C Master is a two-wire serial interface consisting of a serial data line (SDA) and a serial clock line (SCL). SDA can be configured on one of the following pins: SD\_CLK (pin 19), GPIO1 (pin 24), GPIO6 (pin 31), or I2C\_SDA (pin 33). SCL can be configured on one of the following pins: GPIO0 (pin 10), SD\_DAT3 (pin 12), GPIO4 (pin 29), or I2C\_SCL (pin 32). For more specific instructions refer to the ATWILC1000 Programming Guide.

The I<sup>2</sup>C master interface supports three speeds:

- Standard mode (100 kb/s)

- Fast mode (400 kb/s)

- High-Speed mode (3.4 Mb/s)

The timing diagram of the I<sup>2</sup>C master interface is the same as that of the I<sup>2</sup>C slave interface (see Figure 8-1). The timing parameters of I<sup>2</sup>C master are shown in the following table.

Table 8-2. I<sup>2</sup>C Master Timing Parameters

| Parameter            | Symbol           | Standard Mode |      | Mode Fast Mode |      | High-Speed Mode |      | Unit |

|----------------------|------------------|---------------|------|----------------|------|-----------------|------|------|

|                      |                  | Min.          | Max. | Min.           | Max. | Min.            | Max. |      |

| SCL clock frequency  | f <sub>SCL</sub> | 0             | 100  | 0              | 400  | 0               | 3400 | kHz  |

| SCL high pulse width | t <sub>WH</sub>  | 4             | _    | 0.6            | _    | 0.06            | _    | ш    |

| SCL low pulse width  | t <sub>WL</sub>  | 4.7           | _    | 1.3            | _    | 0.16            | _    | μs   |

| continued                            |                    |        |         |           |      |                 |      |      |

|--------------------------------------|--------------------|--------|---------|-----------|------|-----------------|------|------|

| Parameter                            | Symbol             | Standa | rd Mode | Fast Mode |      | High-Speed Mode |      | Unit |

|                                      |                    | Min.   | Max.    | Min.      | Max. | Min.            | Max. |      |

| SCL fall time                        | t <sub>HLSCL</sub> | _      | 300     | _         | 300  | 10              | 40   |      |

| SDA fall time                        | t <sub>HLSDA</sub> | _      | 300     |           | 300  | 10              | 80   | ns   |

| SCL rise time                        | t <sub>LHSCL</sub> | _      | 1000    | _         | 300  | 10              | 40   | 115  |

| SDA rise time                        | t <sub>LHSDA</sub> | _      | 1000    | _         | 300  | 10              | 80   |      |

| START setup time                     | t <sub>SUSTA</sub> | 4.7    | _       | 0.6       | _    | 0.16            | _    | 110  |

| START hold time                      | t <sub>HDSTA</sub> | 4      | _       | 0.6       | _    | 0.16            | _    | μs   |

| SDA setup time                       | t <sub>SUDAT</sub> | 250    | _       | 100       | _    | 10              | _    | ns   |

| SDA hold time                        | t <sub>HDDAT</sub> | 5      | _       | 40        | _    | 0               | 70   | 115  |

| STOP setup time                      | t <sub>SUSTO</sub> | 4      | _       | 0.6       | _    | 0.16            | _    |      |

| Bus free time between STOP and START | t <sub>BUF</sub>   | 4.7    | _       | 1.3       | _    | _               | _    | μs   |

| Glitch pulse reject                  | t <sub>PR</sub>    | _      | _       | 0         | 50   | _               | _    |      |

### 8.3 SPI Slave Interface

The ATWILC1000B provides a Serial Peripheral Interface (SPI) that operates as an SPI slave. The SPI Slave interface can be used for control and for serial I/O of 802.11 data. The SPI Slave pins are mapped as shown in the the following table. The RXD pin is same as Master Output, Slave Input (MOSI), and the TXD pin is same as Master Input, Slave Output (MISO). The SPI Slave is a full-duplex slave-synchronous serial interface that is available immediately following reset when pin 9 (SDIO\_SPI\_CFG) is tied to VDDIO.

Table 8-3. SPI Slave Interface Pin Mapping

| Pin Number | SPI Function                     |

|------------|----------------------------------|

| 9          | CFG: Must be tied to VDDIO       |

| 16         | SSN: Active Low Slave Select     |

| 18         | SCK: Serial Clock                |

| 13         | RXD: Serial Data Receive (MOSI)  |

| 17         | TXD: Serial Data Transmit (MISO) |

When the SPI is not selected, i.e., when SSN is high, the SPI interface does not interfere with data transfers between the serial-master and other serial-slave devices. When the serial slave is not selected, its transmitted data output is buffered, resulting in a high impedance drive onto the serial master receive line.

The SPI Slave interface responds to a protocol that allows an external host to read or write any register in the chip as well as initiate DMA transfers. For more details of the SPI protocol and more specific instructions, refer to the ATWILC1000 Programming Guide.

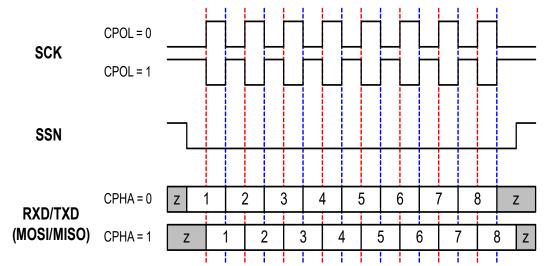

The SPI Slave interface supports four standard modes as determined by the Clock Polarity (CPOL) and Clock Phase (CPHA) settings. These modes are illustrated in table SPI Slave Modes and Figure 8-2. The red lines in this figure correspond to Clock Phase = 0 and the blue lines correspond to Clock Phase = 1.

Table 8-4. SPI Slave Modes

| Mode | CPOL | СРНА |

|------|------|------|

| 0    | 0    | 0    |

| 1    | 0    | 1    |

| 2    | 1    | 0    |

| 3    | 1    | 1    |

Figure 8-2. SPI Slave Clock Polarity and Clock Phase Timing

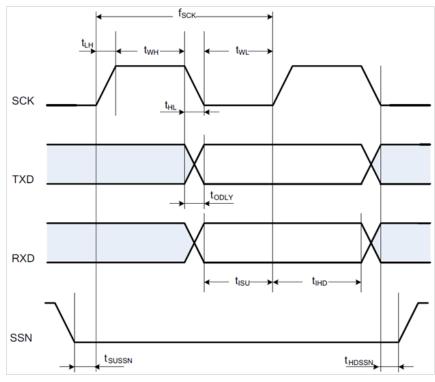

The SPI slave timing is provided in the following figure.

Figure 8-3. SPI Slave Timing Diagram

The SPI slave timing parameters are provided in the following table.

**Table 8-5. SPI Slave Timing Parameters**

| Parameter               | Symbol             | Min. | Max. | Unit |

|-------------------------|--------------------|------|------|------|

| Clock input frequency   | f <sub>SCK</sub>   | _    | 48   | MHz  |

| Clock low pulse width   | t <sub>WL</sub>    | 15   | _    |      |

| Clock high pulse width  | t <sub>WH</sub>    | 15   | _    |      |

| Clock rise time         | t <sub>LH</sub>    | _    | 10   |      |

| Clock fall time         | t <sub>HL</sub>    | _    | 10   |      |

| Input setup time        | t <sub>ISU</sub>   | 5    | _    | ns   |

| Input hold time         | t <sub>IHD</sub>   | 5    | _    |      |

| Output delay            | t <sub>ODLY</sub>  | 0    | 20   |      |

| Slave select setup time | t <sub>SUSSN</sub> | 5    | _    |      |

| Slave select hold time  | t <sub>HDSSN</sub> | 5    | _    |      |

## 8.4 SPI Master Interface

The ATWILC1000B provides an SPI master interface for accessing external Flash memory. The SPI master pins are mapped as shown in the following table. The TXD pin is same as Master Output, Slave Input (MOSI), and the RXD pin is same as Master Input, Slave Output (MISO). The SPI master interface supports all four standard modes of clock polarity and clock phase shown in Table 8-4. External SPI Flash

memory is accessed by a processor programming commands to the SPI master interface, which in turn initiates a SPI master access to the Flash. For more specific instructions, refer to the ATWILC1000 Programming Guide.

Table 8-6. SPI Master Interface Pin Mapping

| Pin Number | Pin Name | SPI Function                            |

|------------|----------|-----------------------------------------|

| 28         | GPIO3    | SCK: Serial Clock Output                |

| 29         | GPIO4    | SCK: Active-Low Slave Select Output     |

| 30         | GPIO5    | TXD: Serial Data Transmit Output (MOSI) |

| 31         | GPIO6    | RXD: Serial Data Receive Input (MISO)   |

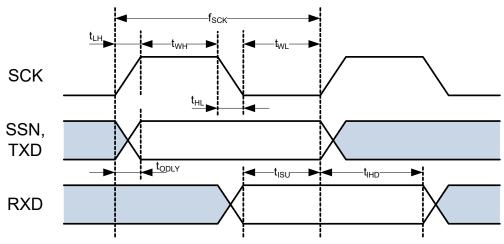

The SPI master timing is provided in the following figure.

Figure 8-4. SPI Master Timing Diagram

The SPI master timing parameters are provided in the following table.

**Table 8-7. SPI Master Timing Parameters**

| Parameter              | Symbol            | Min. | Max. | Unit |

|------------------------|-------------------|------|------|------|

| Clock output frequency | f <sub>SCK</sub>  | _    | 48   | MHz  |

| Clock low pulse width  | t <sub>WL</sub>   | 5    | _    |      |

| Clock high pulse width | t <sub>WH</sub>   | 5    | _    |      |

| Clock rise time        | t <sub>LH</sub>   | _    | 5    |      |

| Clock fall time        | t <sub>HL</sub>   | _    | 5    | ns   |

| Input setup time       | t <sub>ISU</sub>  | 5    | _    |      |

| Input hold time        | t <sub>IHD</sub>  | 5    | _    |      |

| Output delay           | t <sub>ODLY</sub> | 0    | 5    |      |

### 8.5 SDIO Slave Interface

The ATWILC1000B SDIO Slave is a full speed interface. The interface supports the 1-bit/4-bit SD Transfer mode at the clock range of 0 to 50 MHz. The host can use this interface to read and write from any register within the chip as well as configure the ATWILC1000B for data DMA. To use this interface, pin 9 (SDIO\_SPI\_CFG) must be grounded. The SDIO slave pins are mapped as shown in the following table.

Table 8-8. SDIO Interface Pin Mapping

| Pin Number | SPI Function                |

|------------|-----------------------------|

| 9          | CFG: Must be tied to ground |

| 12         | DAT3: Data 3                |

| 13         | DAT2: Data 2                |

| 16         | DAT1: Data 1                |

| 17         | DAT0: Data 0                |

| 18         | CMD: Command                |

| 19         | CLK: Clock                  |

When the SDIO card is inserted into an SDIO aware host, the detection of the card will be via the means described in SDIO specification. During the normal initialization and interrogation of the card by the host, the card identifies itself as an SDIO device. The host software obtains the card information in a tuple (linked list) format and determines if that card's I/O function(s) are acceptable to activate. If the card is acceptable, it is allowed to power-up fully and start the I/O function(s) built into it. The SD memory card communication is based on an advanced 9-pin interface (clock, command, four data and three power lines) designed to operate at a maximum operating frequency of 50 MHz. The SDIO slave interface has the following features:

- Meets SDIO card specification version 2.0

- Host clock rate variable between 0 to 50 MHz

- 1 bit/4-bit SD bus modes supported

- · Allows card to interrupt host

- · Responds to direct read/write (IO52) and extended read/write (IO53) transactions

- Supports Suspend/Resume operation

The SDIO slave interface timing is provided in the following figure.

SCK

tuh

twh

twh

today

today

ssn

Figure 8-5. SDIO Slave Timing Diagram

The SDIO slave timing parameters are provided in the following table.

t<sub>SUSSN</sub>

Table 8-9. SDIO Slave Timing Parameters

| Parameter              | Symbol            | Min. | Max. | Unit |

|------------------------|-------------------|------|------|------|

| Clock input frequency  | f <sub>PP</sub>   | 0    | 50   | MHz  |

| Clock low pulse width  | t <sub>WL</sub>   | 10   | _    |      |

| Clock high pulse width | t <sub>WH</sub>   | 10   | _    |      |

| Clock rise time        | t <sub>LH</sub>   | _    | 10   |      |

| Clock fall time        | t <sub>HL</sub>   | _    | 10   | ns   |

| Input setup time       | t <sub>ISU</sub>  | 5    | _    |      |

| Input hold time        | t <sub>IH</sub>   | 5    | _    |      |

| Output delay           | t <sub>ODLY</sub> | 0    | 14   |      |

t<sub>HDSSN</sub>

## 8.6 UART Debug Interface

ATWILC1000B has a Universal Asynchronous Receiver/Transmitter (UART) interface on pin 13, SD-DATA2/SPI-RxD and pin 17, SD-DATA0/SPI-TXD. This interface should be used only for debugging purposes. The UART is compatible with the RS-232 standard, where ATWILC1000B-MUT operates as Data Terminal Equipment (DTE). It has a two-pin RXD/TXD interface.

The default configuration for accessing the UART interface of ATWILC1000B-MUT is as follows:

Baud rate: 115200

Data: 8 bitParity: None

· Stop bit: 1 bit

· Flow control: None

It also has Rx and Tx FIFOs, which ensures reliable high speed reception and low software overhead transmission. FIFO size is 4x8 for both Rx and Tx direction. The UART has status registers that show the number of received characters available in the FIFO and various error conditions; in addition, it has the ability to generate interrupts based on these status bits.

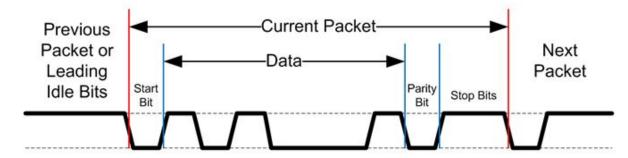

An example of UART receiving or transmitting a single packet is shown in the following figure. This example shows 7-bit data (0x45), odd parity, and two stop bits.

Figure 8-6. Example of UART RX or TX Packet

### 8.7 GPIOs

Nine General Purpose Input/Output (GPIO) pins, labeled GPIO 0-8, are available to allow for application specific functions. Each GPIO pin can be programmed as an input (the value of the pin can be read by the host or internal processor) or as an output (the output values can be programmed by the host or internal processor), where the default mode after power-up is input. GPIOs 7 and 8 are only available when the host does not use the SDIO interface, which shares two of its pins with these GPIOs. Therefore, for SDIO-based applications, seven GPIOs (0-6) are available. For more specific usage instructions refer to the ATWILC1000 Programming Guide.

## 9. Power Management

#### 9.1 Power Architecture

The ATWILC1000B uses an innovative power architecture to eliminate the need for external regulators and reduce the number of off-chip components. This architecture is shown in the following figure. The Power Management Unit (PMU) has a DC/DC Converter that converts VBATT to the core supply used by the digital and RF/AMS blocks. The PA and eFuse are supplied by dedicated LDOs, and the VCO is supplied by a separate LDO structure. The power connections in the following figure provide a conceptual framework for understanding the ATWILC1000B power architecture.

Figure 9-1. Power Architecture

The following table provides the typical values for the digital and RF/AMS core voltages.

Table 9-1. PMU Output Voltages

| Parameter                       | Typical |

|---------------------------------|---------|

| RF/AMS core voltage (VREG_BUCK) | 1.35V   |

| Digital core voltage (VDDC)     | 1.10V   |

Refer to the reference design for an example of power supply connections, including proper isolation of the supplies used by the digital and RF/AMS blocks.

## 9.2 Power Consumption

The ATWILC1000B has several device states:

- ON\_Transmit Device is actively transmitting an 802.11 signal

- ON Receive Device is actively receiving an 802.11 signal

- ON\_Doze Device is on but is neither transmitting nor receiving

- Power\_Down Device core supply off (leakage)

The following pins are used to switch between the ON and Power Down states:

- CHIP\_EN Device pin (pin 23) used to enable DC/DC Converter

- VDDIO I/O supply voltage from external supply

In the ON states, VDDIO is on and CHIP\_EN is high (at VDDIO voltage level). To switch between the ON states and Power\_Down state, CHIP\_EN has to change between high and low (GND) voltage. When VDDIO is off and CHIP\_EN is low, the chip is powered off with no leakage (also see 9.3 Power-Up/Down Sequence).

#### 9.2.1 Current Consumption in Various Device States

The following table provides the ATWILC1000B current consumption in various device states.

**Table 9-2. Current Consumption**

| Device State | Code Rate       | Output Power | Current Consumption <sup>(1)</sup> |                    |  |

|--------------|-----------------|--------------|------------------------------------|--------------------|--|

|              |                 | (dBm)        | I <sub>VBATT</sub>                 | I <sub>VDDIO</sub> |  |

| ON_Transmit  | 802.11b 1 Mbps  | 17.6         | 266 mA                             | 22 mA              |  |

|              | 802.11b 11 Mbps | 18.5         | 239 mA                             | 22 mA              |  |

|              | 802.11g 6 Mbps  | 18.6         | 249 mA                             | 22 mA              |  |

|              | 802.11g 54 Mbps | 16.9         | 173 mA                             | 22 mA              |  |

|              | 802.11n MCS 0   | 17.7         | 253 mA                             | 22 mA              |  |

|              | 802.11n MCS 7   | 14.0         | 164 mA                             | 22 mA              |  |

| continued    |                 |              |                                    |                    |  |

|--------------|-----------------|--------------|------------------------------------|--------------------|--|

| Device State | Code Rate       | Output Power | Current Consumption <sup>(1)</sup> |                    |  |

|              |                 | (dBm)        | I <sub>VBATT</sub>                 | I <sub>VDDIO</sub> |  |

| ON_Receive   | 802.11b 1 Mbps  | N/A          | 63 mA                              | 22 mA              |  |

|              | 802.11b 11 Mbps | N/A          | 63 mA                              | 22 mA              |  |

|              | 802.11g 6 Mbps  | N/A          | 63 mA                              | 22 mA              |  |

|              | 802.11g 54 Mbps | N/A          | 63 mA                              | 22 mA              |  |

|              | 802.11n MCS 0   | N/A          | 63 mA                              | 22 mA              |  |

|              | 802.11n MCS 7   | N/A          | 63 mA                              | 22 mA              |  |

| ON_Doze      | N/A             | N/A          | 380 μΑ                             | <10 µA             |  |

| Power_Down   | N/A             | N/A          | 1.25 µA <sup>(2)</sup>             |                    |  |

#### Note:

1. The power consumption values are measured when VBAT is 3.6V and VDDIO is 2.8V at 25°C.

## 9.2.2 Controlling the Device States

Table "Device States" shows how to switch between the device states using the following:

- CHIP EN Device pin (pin #23) used to enable DC/DC Converter

- VDDIO I/O supply voltage from external supply

Table 9-3. Device States

| Device State | CHIP_EN | VDDIO | Power Consumption <sup>(1), (2)</sup> |                    |

|--------------|---------|-------|---------------------------------------|--------------------|

|              |         |       | I <sub>VBATT</sub>                    | I <sub>VDDIO</sub> |

| ON_Transmit  | VDDIO   | On    | 172mA @ 18dBm (≤18Mbps)               | 2mA                |

|              |         |       | 230mA @ 18dBm (>18Mbps)               |                    |

| ON_Receive   | VDDIO   | On    | 60mA                                  | 2mA                |

| ON_Doze      | VDDIO   | ON    | 280μΑ                                 | <10µA              |

| Power_Down   | GND     | On    | <0.5μΑ                                | <0.2µA             |

#### Note:

- 1. Conditions: VBAT @ 3.6v, I/O@1.8V.

- 2. Power consumption numbers are preliminary.

## 9.2.3 Restrictions for Power States

When no power is supplied to the device, i.e., the DC/DC converter output and VDDIO are both off (at ground potential). In this case, a voltage cannot be applied to the device pins because each pin contains an ESD diode from the pin to supply. This diode turns on when voltage higher than one diode-drop is supplied to the pin.

If a voltage must be applied to the signal pads while the chip is in a low power state, the VDDIO supply must be on, so the SLEEP or Power\_Down state must be used.

Similarly, to prevent the pin-to-ground diode from turning on, do not apply a voltage that is more than one diode-drop below ground to any pin.

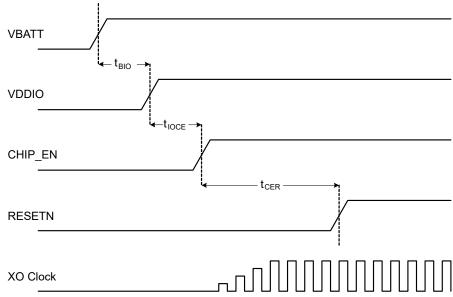

## 9.3 Power-Up/Down Sequence

The power-up/down sequence for the ATWILC1000B is shown in the following figure.

Figure 9-2. Power-Up/Down Sequence

The timing parameters are provided in the following table.

Table 9-4. Power-Up/Down Sequence Timing

| Parameter      | Min. | Max. | Unit | Description                    | Notes                                                                                                                             |

|----------------|------|------|------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| t <sub>A</sub> | 0    | _    |      | VBATT rise to VDDIO rise       | VBATT and VDDIO can rise simultaneously or can be tied together. VDDIO must not rise before VBATT.                                |

| t <sub>B</sub> | 0    | _    |      | VDDIO rise to CHIP_EN rise     | CHIP_EN must not rise before VDDIO. CHIP_EN must be driven high or low, not left floating.                                        |

| t <sub>C</sub> | 5    | _    | ms   | CHIP_EN rise to<br>RESETN rise | This delay is needed because XO clock must stabilize before RESETN removal. RESETN must be driven high or low, not left floating. |

| t <sub>A</sub> | 0    | _    |      | VDDIO fall to VBATT fall       | VBATT and VDDIO can fall simultaneously or can be tied together. VBATT must not fall before VDDIO.                                |

| t <sub>B</sub> | 0    | _    |      | CHIP_EN fall to VDDIO fall     | VDDIO must not fall before CHIP_EN. CHIP_EN and RESETN can fall simultaneously.                                                   |

| t <sub>C</sub> | 0    | _    |      | RESETN fall to VDDIO fall      | VDDIO must not fall before RESETN. RESETN and CHIP_EN can fall simultaneously.                                                    |

# 9.4 Digital I/O Pin Behavior During Power-up Sequences

The following table represents digital I/O pin states corresponding to device power modes.

Table 9-5. Digital I/O Pin Behavior in Different Device States

| Device State                                                                          | VDDIO | CHIP_EN | RESETN | Output Driver                                                        | Input<br>Driver                 | Pull-Up/Down<br>Resistor (96kΩ)                          |

|---------------------------------------------------------------------------------------|-------|---------|--------|----------------------------------------------------------------------|---------------------------------|----------------------------------------------------------|