# **MPQ2420-AEC1**

75V, 0.3A, Synchronous Step-Down Converter with Watchdog AEC-Q100 Qualified

## **DESCRIPTION**

The MPQ2420 is a step-down switching regulator with integrated high- and low-side, high-voltage power MOSFETs. It provides a highly efficient output of up to 0.3A. The integrated watchdog adds additional security redundancy to the system.

The wide 4.5V to 75V input range accommodates a variety of step-down applications in an automotive environment. A 5µA shutdown mode quiescent current in a full temperature range is ideal for battery-powered applications. It allows for high-power conversion efficiency over a wide load range by scaling down the switching frequency under a light-load condition to reduce switching and gate driver losses. The start-up switching frequency and short circuit can also be scaled down to prevent inductor current runaway.

Full protection features include under-voltage lockout (UVLO) and thermal shutdown. Thermal shutdown provides reliable, fault-tolerant operation.

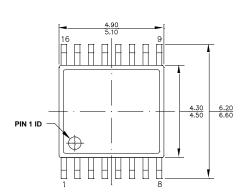

The MPQ2420 is available in a TSSOP-16 EP package.

#### **FEATURES**

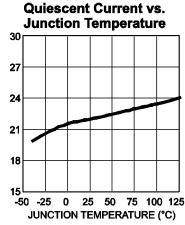

- 20µA Quiescent Current for Buck Only

- Wide 4.5V to 75V Operating Input Range (80V ABS MAX)

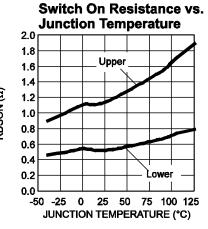

- 1.2Ω/0.45Ω Internal Power MOSFETs

- Programmable Soft Start

- FB Tolerance: 1% at Room Temperature,

2% at Full Temperature

- Adjustable Output Voltage

- Integrated Window Watchdog

- Power-On Reset during Power-Up

- Under-Voltage Lockout and Thermal Shutdown

- Programmable Short Window Mode or Long Window Mode

- Low Shutdown Mode Current of 5µA

- TSSOP-16 EP Package

- Available in AEC-Q100 Grade 1

## **APPLICATIONS**

- Automotive Systems

- Industrial Power Systems

- Distributed Power Systems

- Battery-Powered Systems

All MPS parts are lead-free, halogen-free, and adhere to the RoHS directive. For MPS green status, please visit the MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are registered trademarks of Monolithic Power Systems, Inc.

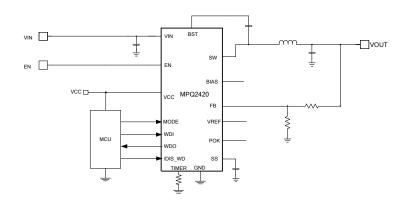

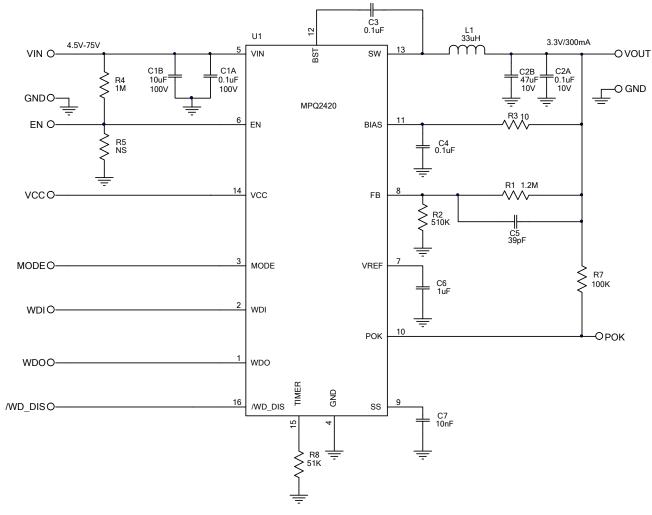

## TYPICAL APPLICATION

## ORDERING INFORMATION

| Part Number*   | Package     | Top Marking |  |

|----------------|-------------|-------------|--|

| MPQ2420GF      | TSSOP-16 EP | See Below   |  |

| MPQ2420GF-AEC1 | 1330F-10 EF | See Below   |  |

<sup>\*</sup> For Tape & Reel, add suffix -Z (e.g. MPQ2420GF-Z)

## **TOP MARKING**

MPSYYWW MP2420 LLLLLL

MPS: MPS prefix YY: Year code WW: Week code

MP2420: Part code of MPQ2420GF

LLLLL: Lot number

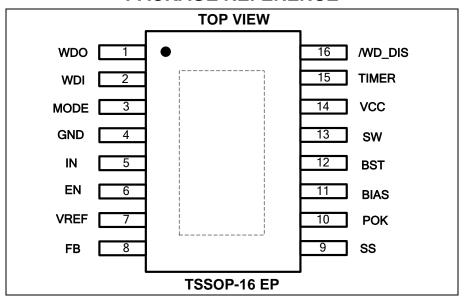

### PACKAGE REFERENCE

#

| Thermal Resistance (4) | $oldsymbol{	heta}_{JA}$ | $oldsymbol{	heta_{JC}}$ |

|------------------------|-------------------------|-------------------------|

| TSSOP-16 EP            | 45                      | 10°C/W                  |

#### NOTES:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature  $T_J$  (MAX), the junction-to-ambient thermal resistance  $\theta_{JA}$ , and the ambient temperature  $T_A$ . The maximum allowable continuous power dissipation at any ambient temperature is calculated by  $P_D$  (MAX) =  $(T_J$  (MAX)- $T_A$ )/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation produces an excessive die temperature, causing the regulator to go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 24V,  $V_{EN}$  = 2V,  $V_{CC}$  = 5V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

| Parameter                                  | Condition                                                | Min   | Тур  | Max   | Units |

|--------------------------------------------|----------------------------------------------------------|-------|------|-------|-------|

| DC/DC Converter                            |                                                          | •     |      | •     | •     |

| Supply quiescent current                   | No load, V <sub>FB</sub> = 1.2V                          |       | 20   | 30    | μA    |

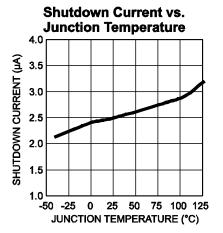

| Shutdown supply current                    | V <sub>EN</sub> < 0.3V                                   |       | 2.2  | 5     | μA    |

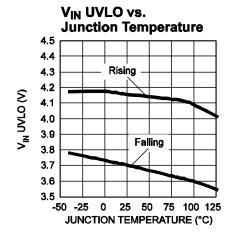

| V <sub>IN</sub> UVLO rising threshold      |                                                          | 3.9   | 4.2  | 4.4   | V     |

| V <sub>IN</sub> UVLO falling threshold     |                                                          | 3.45  | 3.75 | 3.95  |       |

| V <sub>IN</sub> UVLO hysteresis            |                                                          |       | 0.45 |       | V     |

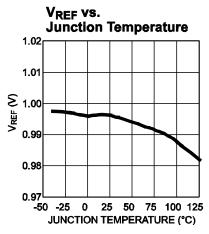

| Feedback voltage                           | $V_{IN} = 4.5 V \text{ to } 75 V, T_{J} = 25 ^{\circ} C$ | 0.99  | 1.0  | 1.01  | V     |

| reeuback vollage                           | V <sub>IN</sub> = 4.5V to 75V                            | 0.98  |      | 1.02  | V     |

| Feedback current                           | V <sub>FB</sub> = 1.2V                                   | -50   | 2    | 50    | nA    |

| V <sub>REF</sub> voltage                   | $V_{IN} = 4.5V$ to 75V, $I_{REF} = 100\mu A$             | 0.965 | 1    | 1.035 | V     |

| Upper switch on registance                 | $V_{BST}$ - $V_{SW}$ = 5V, $T_{J}$ = 25°C                | 0.9   | 1.2  | 1.5   | Ω     |

| Upper switch-on resistance                 | $V_{BST} - V_{SW} = 5V$                                  | 0.7   |      | 2.5   | Ω     |

| Lower switch-on resistance                 | $V_{BIAS} = 5V$ , $T_J = 25$ °C                          | 0.275 | 0.45 | 0.625 | Ω     |

| Lower Switch-on resistance                 | $V_{BIAS} = 5V$                                          | 0.2   |      | 0.9   | Ω     |

| Lower switch leakage                       | $V_{EN} = 0V, V_{SW} = 75V$                              |       |      | 1     | μA    |

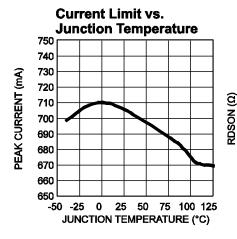

| Peak current limit                         |                                                          | 630   | 720  | 810   | mA    |

| Minimum switch-on time <sup>(5)</sup>      |                                                          |       | 120  |       | ns    |

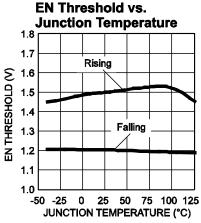

| Enable rising threshold                    |                                                          | 1.25  | 1.55 | 1.85  | V     |

| Enable falling threshold                   |                                                          | 1.152 | 1.2  | 1.248 | V     |

| Enable threshold hysteresis                |                                                          |       | 0.35 |       | V     |

| Enable current                             | $V_{EN} = 2.4V$                                          |       | 0.8  |       | μA    |

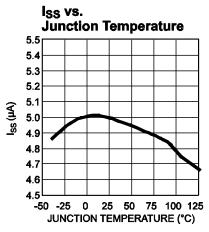

| Soft-start current                         |                                                          | 4     | 5.5  | 7     | μA    |

| POK upper trip threshold                   | FB respect to the nominal value                          | 86    | 90   | 94    | %     |

| POK lower trip threshold                   | FB respect to the nominal value                          | 81    | 85   | 89    | %     |

| POK threshold hysteresis                   | FB respect to the nominal value                          |       | 5    |       | %     |

| POK deglitch timer                         |                                                          |       | 40   |       | μs    |

| POK output voltage low                     | I <sub>SINK</sub> = 1mA                                  |       |      | 0.4   | V     |

| FB OVP rising threshold                    |                                                          |       | 1.05 | 1.1   | V     |

| FB OVP hysteresis                          |                                                          |       | 50   |       | mV    |

| Thermal shutdown <sup>(5)</sup>            |                                                          |       | 175  |       | °C    |

| Thermal shutdown hysteresis <sup>(5)</sup> |                                                          |       | 20   |       | °C    |

#### NOTE:

5) Derived from bench characterization. Not tested in production.

# **ELECTRICAL CHARACTERISTICS** (continued)

$V_{IN}$  = 24V,  $V_{EN}$  = 2V,  $V_{CC}$  = 5V,  $T_J$  = -40°C to +125°C, unless otherwise noted.

| Parameter                                              | Symbol                | Condition                                 | Min                  | Тур  | Max  | Units |  |

|--------------------------------------------------------|-----------------------|-------------------------------------------|----------------------|------|------|-------|--|

| Watchdog Power Suppl                                   | Watchdog Power Supply |                                           |                      |      |      |       |  |

| Timer voltage                                          |                       | R <sub>TIMER</sub> = 51k                  |                      | 0.3  |      | V     |  |

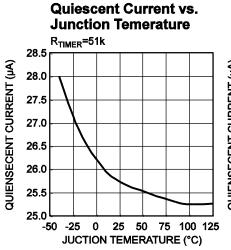

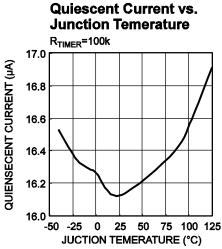

| Quiescent current                                      | IQ                    | R <sub>TIMER</sub> = 100k                 |                      | 16   | 19   | μΑ    |  |

|                                                        |                       | $R_{TIMER} = 51k$                         |                      | 25   | 32   | μA    |  |

| Power-on reset threshold                               | $V_{POR-HIGH}$        | WDO goes high with rising $V_{CC}$        | 4.4                  | 4.6  | 4.8  | V     |  |

| trii corioid                                           | $V_{POR\text{-}LOW}$  | WDO goes low with falling V <sub>CC</sub> | 4.3                  | 4.5  | 4.7  | V     |  |

| Watchdog Timing                                        |                       |                                           |                      |      |      |       |  |

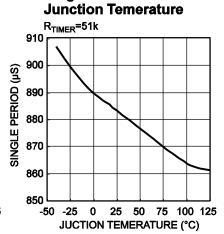

| Single period                                          | Т                     | $R_{TIMER} = 51k$                         | -10%                 | 880  | +10% | μs    |  |

| Power-on delay <sup>(6)</sup>                          | $t_0$                 | $R_{TIMER} = 51k$                         |                      | 10   |      | cycle |  |

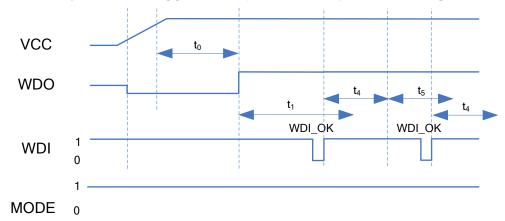

| Sync signal monitoring time <sup>(6)</sup>             | t <sub>1</sub>        | R <sub>TIMER</sub> = 51k                  |                      | 450  |      | cycle |  |

| Watchdog window close time (short mode) <sup>(6)</sup> | $t_2$                 | R <sub>TIMER</sub> = 51k, mode = low      |                      | 15   |      | cycle |  |

| Watchdog window open time (short mode) (6)             | t <sub>3</sub>        | R <sub>TIMER</sub> = 51k, mode = low      |                      | 10   |      | cycle |  |

| Watchdog window close time (long mode) (6)             | t <sub>4</sub>        | R <sub>TIMER</sub> = 51k, mode = high     |                      | 1500 |      | cycle |  |

| Watchdog window open time (long mode) (6)              | t <sub>5</sub>        | R <sub>TIMER</sub> = 51k, mode = high     |                      | 1000 |      | cycle |  |

| WDO reset pulse width <sup>(6)</sup>                   | t <sub>6</sub>        | R <sub>TIMER</sub> = 51k                  |                      | 4    |      | cycle |  |

| WDI_OK pulse width                                     |                       |                                           | 10                   |      | 5000 | μs    |  |

| Watchdog Input and Ou                                  | ıtput                 |                                           |                      |      |      |       |  |

| WDI logic high                                         |                       |                                           | 3.2                  |      |      | V     |  |

| WDI logic low                                          |                       |                                           |                      |      | 8.0  | V     |  |

| MODE logic high                                        |                       |                                           | 3.2                  |      |      | V     |  |

| MODE logic low                                         |                       |                                           |                      |      | 0.8  | V     |  |

| MODE input current                                     |                       | MODE = 5V                                 |                      | 0.1  | 1    | μA    |  |

| MODE input current                                     |                       | MODE = 0V                                 |                      | 5    | 8    | μA    |  |

| /WD_DIS logic high                                     |                       |                                           | 3.2                  |      |      | V     |  |

| /WD_DIS logic low                                      |                       |                                           |                      |      | 0.8  | ٧     |  |

| WD_DIS input current                                   |                       | WD_DIS = 5V                               |                      | 0.1  | 1    | μA    |  |

| /vvD_DIS illput current                                |                       | WD_DIS = 0V                               |                      | 5    | 8    | μA    |  |

| WDO high                                               |                       | VCC = 5V, I <sub>WDO</sub> = 1mA          | V <sub>CC</sub> -0.2 |      |      | V     |  |

| WDO low                                                |                       | VCC = 5V, I <sub>WDO</sub> = 1mA          |                      |      | 0.2  | V     |  |

| VVDO IOW                                               | _                     | VCC = 1V, I <sub>WDO</sub> = 300μA        |                      |      | 0.1  | V     |  |

#### NOTE:

6) Guaranteed by design.

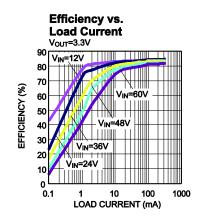

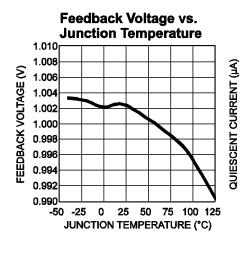

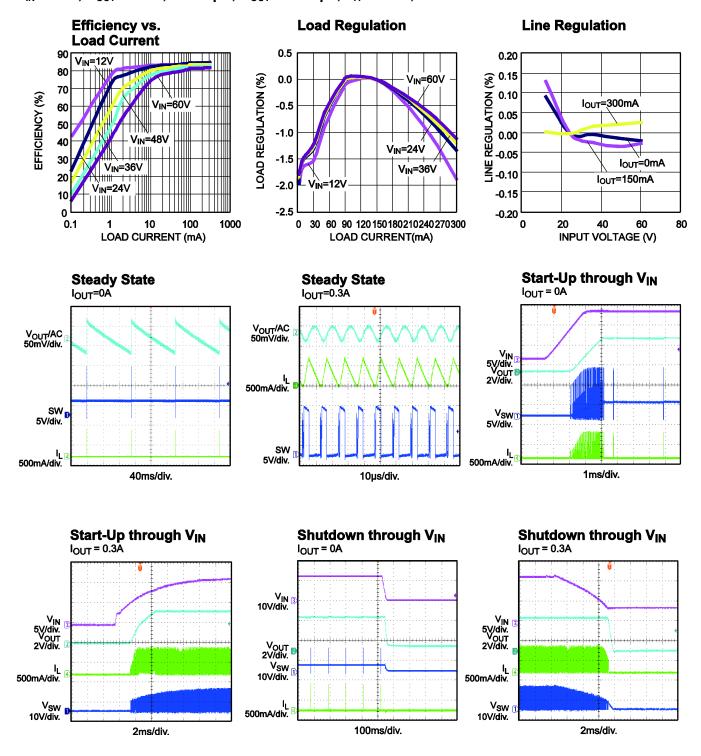

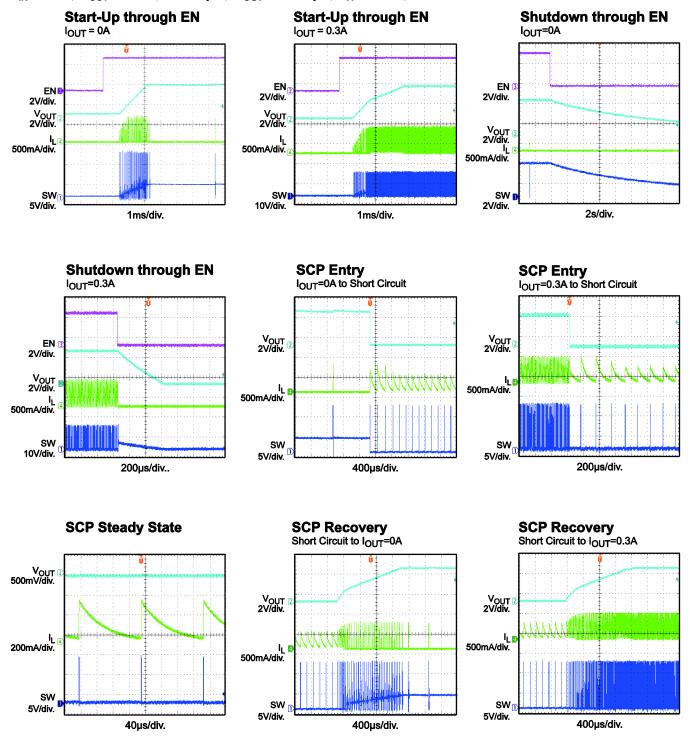

## TYPICAL CHARACTERISTICS

**DC/DC Converter**

$V_{IN}$  = 12V, unless otherwise noted.

# TYPICAL CHARACTERISTICS (continued)

## Watchdog

Single Period vs.

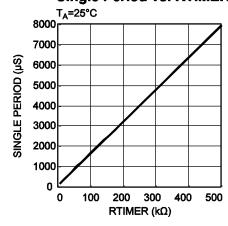

#### Single Period vs. RTIMER

## TYPICAL PERFORMANCE CHARACTERISTICS

#### **DC/DC Converter**

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V, L = 33 $\mu$ H,  $C_{OUT}$  = 2x22 $\mu$ F,  $T_A$  = 25°C, unless otherwise noted.

## TYPICAL PERFORMANCE CHARACTERISTICS (continued)

$V_{IN}$  = 12V,  $V_{OUT}$  = 3.3V, L = 33 $\mu$ H,  $C_{OUT}$  = 2x22 $\mu$ F,  $T_A$  = 25°C, unless otherwise noted.

# **PIN FUNCTIONS**

| Pin#     | Name        | Description                                                                                                                                                                                                                        |  |  |

|----------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Watchdog |             | •                                                                                                                                                                                                                                  |  |  |

| 1        | WDO         | Watchdog output. WDO outputs the reset signal to MCU.                                                                                                                                                                              |  |  |

| 2        | WDI         | Watchdog input. WDI receives the trigger signal from MCU.                                                                                                                                                                          |  |  |

| 3        | MODE        | <b>Mode switching.</b> Pull MODE high to make the watchdog work in a long window mode. Pull MODE low to make the watchdog work in a short window mode. MODE has a weak internal pull-up.                                           |  |  |

| 4        | GND         | <b>Ground.</b> Connect GND as close as possible to the output capacitor to avoid high-current switch paths.                                                                                                                        |  |  |

| 14       | VCC         | Power input.                                                                                                                                                                                                                       |  |  |

| 15       | TIMER       | Watchdog timer. Set the time out with an external resistor                                                                                                                                                                         |  |  |

| 16       | /WD_DIS     | <b>Watchdog disable.</b> Pull /WD_DIS low to disable the watchdog. Pull /WD_DIS high to enable the watchdog. /WD_DIS has a weak internal pull-up.                                                                                  |  |  |

| DC/DC    |             |                                                                                                                                                                                                                                    |  |  |

| 4        | GND         | Ground. Same as GND in Watchdog.                                                                                                                                                                                                   |  |  |

| 5        | IN          | <b>Input supply.</b> IN requires a decoupling capacitor connected to ground to reduce switching spikes.                                                                                                                            |  |  |

| 6        | EN          | <b>Enable input.</b> Pull EN below the low threshold to shut the chip down. Pull EN above the high threshold to enable the chip. Float EN to disable the chip.                                                                     |  |  |

| 7        | VREF        | Reference voltage output.                                                                                                                                                                                                          |  |  |

| 8        | FB          | Feedback input to the error amplifier (QFN-10 3mmx3mm package only). Connect FB to the tap of an external resistive divider between the output and GND. FB sets the regulation voltage when compared to the internal 1V reference. |  |  |

| 9        | SS          | <b>Soft-start control input.</b> Connect a capacitor from SS to GND to set the soft-start period.                                                                                                                                  |  |  |

| 10       | POK         | <b>Open-drain power-good output.</b> A high output indicates that $V_{\text{OUT}}$ is higher than 90% of the reference. POK is pulled down during shutdown.                                                                        |  |  |

| 11       | BIAS        | Controller bias input. BIAS supplies current to the internal circuit when $V_{\text{BIAS}} > 2.9 \text{V}$ and provides a feedback input for the SOIC8E package, which has a fixed output only.                                    |  |  |

| 12       | BST         | <b>Bootstrap.</b> BST provides a positive power supply for the internal floating high-side MOSFET driver. Connect a bypass capacitor between BST and SW.                                                                           |  |  |

| 13       | SW          | Switch node.                                                                                                                                                                                                                       |  |  |

|          | Exposed Pad | Connect exposed pad to GND plane for optimal thermal performance.                                                                                                                                                                  |  |  |

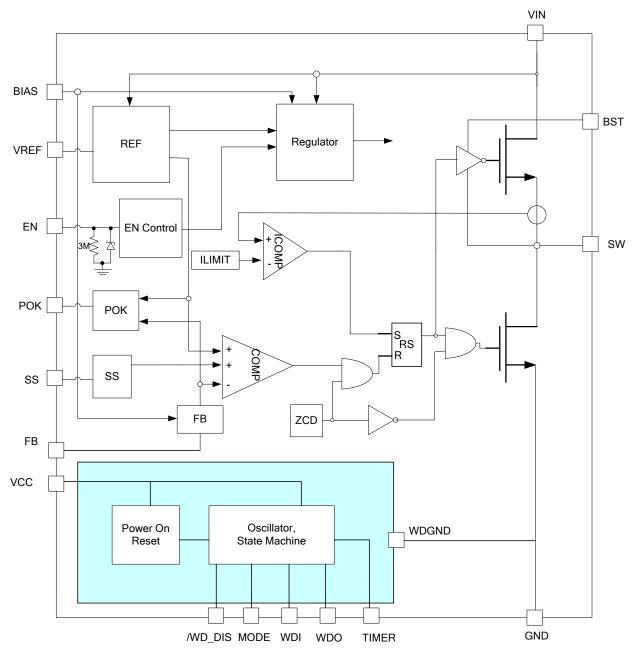

# **FUNCTIONAL BLOCK DIAGRAM**

**Figure 1: Functional Block Diagram**

#### DC/DC OPERATION

The MPQ2420 is a 75V, 0.3A, synchronous, step-down, switching regulator with integrated high-side and low-side, high-voltage power MOSFETs (HS-FET and LS-FET, respectively). It provides a highly efficient 0.3A output and features a wide input voltage range, external soft-start control, and precision current limit. It has a very low operational quiescent current, making it suitable for battery-powered applications.

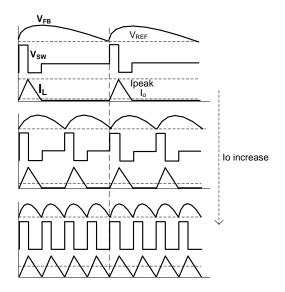

#### **Control Scheme**

The ILIM comparator, FB comparator, and zero current detector (ZCD) block control of the PWM (see Figure 2). If  $V_{FB}$  is below the 1V reference and the inductor current drops to zero, the HS-FET turns on, and the ILIM comparator begins sensing the HS-FET current. When the HS-FET current reaches its limit, the HS-FET turns off, and the LS-FET and the ZCD block turn on. The ILIM comparator turns off to reduce the quiescent current. The LS-FET and the ZCD block turn off after the inductor current drops to zero. If  $V_{FB}$  is below the 1V reference, the HS-FET turns on and begins another cycle. If  $V_{FB}$  remains higher than the 1V reference, the HS-FET remains off until  $V_{FB}$  drops below 1V.

Figure 2: Control Scheme

#### Internal Regulator and BIAS

The 2.6V internal regulator powers most of the internal circuitry. This regulator takes  $V_{\text{IN}}$  and operates in the full  $V_{\text{IN}}$  range. When  $V_{\text{IN}}$  is greater than 3.0V, the output of the regulator is in full

regulation. Lower values of  $V_{\text{IN}}$  result in lower output voltages. When  $V_{\text{BIAS}} > 2.9 \text{V}$ , the BIAS supply overrides the input voltage and supplies power to the internal regulator. When  $V_{\text{BIAS}} > 4.5 \text{V}$ , BIAS powers the LS-FET driver. Using BIAS to power the internal regulators improves efficiency. It is recommended to connect BIAS to the regulated output voltage when it is in the 2.9V to 5.5V range. When the output voltage is out of this range, BIAS can be powered using an external supply of >2.9V to >4.5V.

#### **Enable Control (EN)**

The MPQ2420 has a dedicated enable control (EN). When  $V_{\rm IN}$  goes high, EN enables and disables the chip (high logic). Its falling threshold is a consistent 1.2V, and its rising threshold is about 350mV. When floating, EN is pulled down internally to GND to disable the chip.

When EN = 0V, the chip enters the lowest shutdown current mode. When EN is higher than zero, but lower than its rising threshold, the chip remains in shutdown mode with a slightly larger shutdown current.

A Zener diode is connected internally from EN to GND. The typical clamping voltage of the Zener diode is 6.5V.  $V_{\text{IN}}$  can be connected to EN through a high ohm  $(\Omega)$  resistor if the system does not have another logic input acting as an EN signal. The resistor must be designed to limit the EN sink current to less than 150µA. Since there is an internal 3M resistor from EN to GND, the external pull-up resistor should be smaller

than

$$\frac{[V_{IN(MIN)} -1.55V] \times 3M}{1.55V}$$

to ensure that EN can

turn on at the lowest operational V<sub>IN</sub>.

#### **Under-Voltage Lockout (UVLO)**

Under-voltage lockout (UVLO) protects the chip from operating below the operational supply voltage range. The UVLO rising threshold is about 4.2V while its falling threshold is about 3.75V.

#### Soft Start (SS)

The MPQ2420 employs a soft-start (SS) mechanism to prevent the converter output voltage from overshooting during start-up. When the chip starts, the internal circuitry generates a constant current to charge an external soft-start capacitor. The SS voltage ramps up slowly from 0V at a slow pace set by the SS time. When  $V_{\rm SS}$  is less than  $V_{\rm REF},\,V_{\rm SS}$  overrides  $V_{\rm REF},\,$  and the FB comparator uses  $V_{\rm SS}$  as the reference instead of  $V_{\rm REF}.$  When  $V_{\rm SS}$  is higher than  $V_{\rm REF},\,V_{\rm REF}$  resumes control.

$V_{SS}$  can be much smaller than  $V_{FB}$ , but it can only barely exceed  $V_{FB}$ . If  $V_{FB}$  drops,  $V_{SS}$  tracks  $V_{FB}$ . This function prevents an output voltage overshoot during short-circuit recovery. When the short circuit is removed, a new SS process ramps up.

#### **Thermal Shutdown**

Thermal shutdown prevents the chip from operating at exceedingly high temperatures. When the silicon die reaches temperatures that exceed its upper threshold, the entire chip shuts down. When the temperature falls below its lower threshold, the chip is enabled again.

#### Floating Driver and Bootstrap Charging

An external bootstrap capacitor powers the floating HS-FET driver. This floating driver has its own UVLO protection. This UVLO's rising threshold is about 2.4V with a hysteresis of about 300mV. During the UVLO, the SS voltage resets to zero. When the UVLO is disabled, the regulator follows the soft-start process.

The dedicated internal bootstrap regulator charges and regulates the bootstrap capacitor to about 5V. When the voltage difference between BST and SW falls below its working parameters, a PMOS pass transistor connected from  $V_{\text{IN}}$  to BST turns on to charge the bootstrap capacitor. The current path runs from  $V_{\text{IN}}$  to BST to SW. The external circuit must have enough voltage headroom to accommodate charging.

If  $V_{\text{IN}}$  is sufficiently higher than SW, the bootstrap capacitor charges. When the HS-FET is on,  $V_{\text{IN}}$  is about equal to SW, and the bootstrap capacitor cannot charge. The optimal charging period occurs when the LS-FET is on and  $V_{\text{IN}}$  -  $V_{\text{SW}}$  is at its largest.  $V_{\text{SW}}$  is equal to  $V_{\text{OUT}}$  when there is no current in the inductor. The difference between  $V_{\text{IN}}$  and  $V_{\text{OUT}}$  charges the bootstrap capacitor.

If the internal circuit does not have sufficient voltage and time to charge the bootstrap capacitor, extra external circuitry can be used to ensure that the bootstrap voltage operates in its normal region.

#### Start-Up and Shutdown

If both  $V_{\text{IN}}$  and  $V_{\text{EN}}$  are higher than their appropriate thresholds, the chip starts up. The reference block starts first, generating stable reference voltages and currents, and then the internal regulator is enabled. The regulator provides a stable supply for the remaining circuitries.

If the internal supply rail is high, an internal timer keeps the power MOSFET off for about 50µs to clear any start-up glitches. When the soft-start block is enabled, the SS output is held low and ramps up slowly.

Three events can shut down the chip:  $V_{\text{EN}}$  low,  $V_{\text{IN}}$  low, and thermal shutdown. During the shutdown procedure, the signaling path is blocked first to avoid any fault triggering. The internal supply rail is then pulled down. The floating driver is not subject to this shutdown command, but its charging path is disabled.

#### Power OK (POK)

POK is an open-drain power good output. A high output indicates that  $V_{\text{OUT}}$  is higher than 90% of its nominal value. POK is pulled down in shutdown mode.

#### Reference Voltage Output (V<sub>REF</sub>)

$V_{\text{REF}}$  has an output reference voltage of 1V. It has up to 500 $\mu$ A of source current capability.

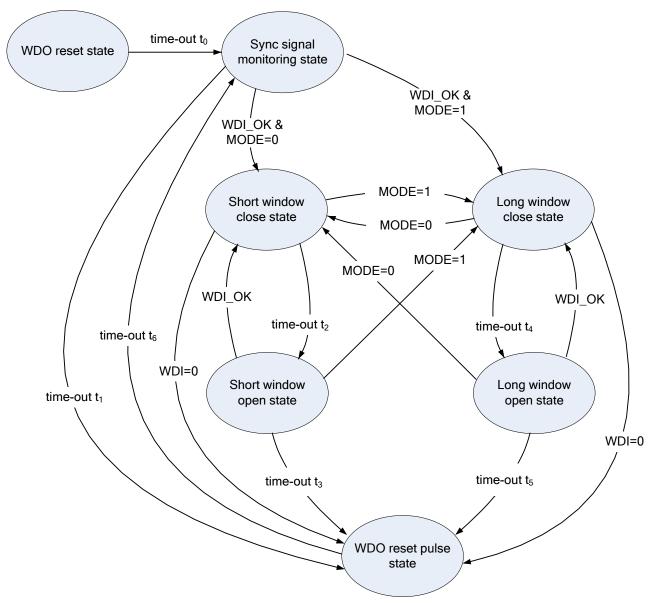

#### WATCHDOG OPERATION

### **Supply Voltage**

A supply voltage of  $V_{CC} = 5V$  +/-10% is recommended for normal operation. WDO is pulled low when  $V_{CC}$  rises to 1V or higher. When  $V_{CC}$  rises to 4.65V, WDO remains at a low level for  $t_0$  to reset the MCU.

#### **Timer**

Calculate Period T (µs) with Equation (1):

$$T(\mu s) = 15.75 \times R_{TIMER}(k\Omega) + 73.5 \qquad (1)$$

Calculate  $R_{TIMER}$  (k $\Omega$ ) with Equation (2):

$$R_{\text{TIMER}}(k\Omega) = 0.063 \times T(\mu s) - 4.67 \qquad (2)$$

For example, if  $R_{TIMER}$ =51k $\Omega$ , then T $\approx$ 0.88ms.

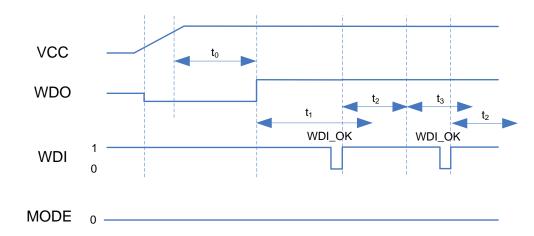

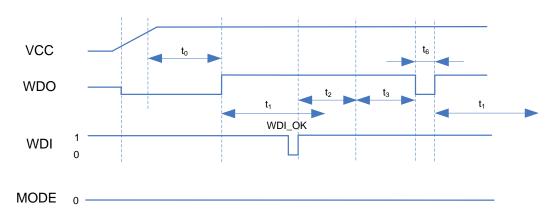

#### **Monitor MCU Synchronization Signal**

When the watchdog is in a sync signal monitoring state, the watchdog IC receives a WDI\_OK signal from the MCU within  $t_1$ , the timer resets and the watchdog enters normal operation (WDI remains low for  $10\mu s$  to 5ms). If the watchdog does not receive the WDI\_OK signal from the MCU during  $t_1$ , it generates a reset signal and enters the sync signal monitoring state again.

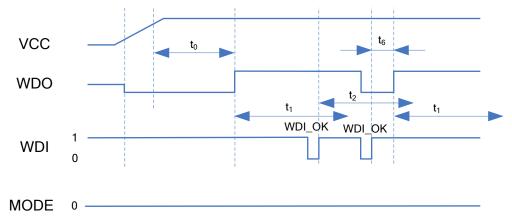

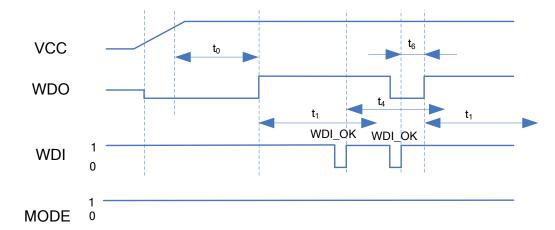

#### **Short Window Mode**

When the MCU and watchdog are synchronized correctly and MODE is low, the watchdog operates in short window mode if WDI\_OK is received in a window close state (t<sub>2</sub>). The watchdog then outputs a reset signal and enters the sync signal monitoring state.

If WDI\_OK is received in a window open state (t<sub>3</sub>), the watchdog enters a window close state. The MCU is in normal operation in this situation.

If WDI\_OK is not received in t<sub>2</sub>+t<sub>3</sub>, the watchdog outputs a reset signal and enters the sync signal monitoring state.

MODE is pulled high during the short window mode, and the watchdog enters a long window mode.

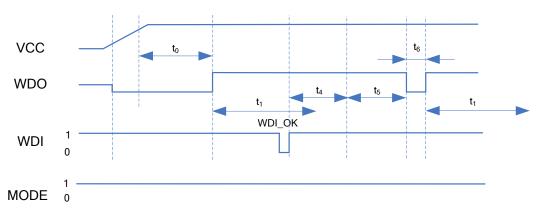

#### **Long Window Mode**

When the MCU and watchdog are synchronized correctly and MODE is high, the watchdog works in a long window mode if WDI\_OK is received in a window close state (t<sub>4</sub>). The watchdog then outputs a reset signal and enters the sync signal monitoring state.

If WDI\_OK is received in a window open state  $(t_5)$ , the watchdog enters a window close state. The MCU is in normal operation in this situation.

If WDI\_OK is not received in t<sub>4</sub>+t<sub>5</sub>, the watchdog then outputs a reset signal and enters the sync signal monitoring state.

MODE is pulled low during a long window mode, and the watchdog then enters a short window mode.

#### Watchdog Disable

Pull /WD\_DIS low to disable the watchdog. Pull /WD\_DIS high to enable the watchdog. It has a weak internal pull-up so leaving /WD\_DIS open enables the watchdog.

#### **WDI Error**

The WDI signal remaining at a low level for longer than the max WDI\_OK pulse width is regarded as an error. When this error occurs, WDO is pulled down until WDI rises to a high level again.

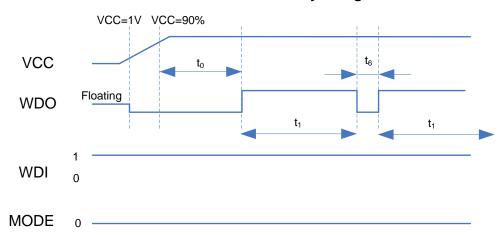

## **TIMING DIAGRAM**

## Power-On Reset and No-Sync Signal

## Synchronized by WDI and Triggered in Open Window (MODE=0, Short Window Mode)

## Synchronized by WDI and No-Trigger Signal (MODE=0, Short Window Mode)

#### Synchronized by WDI and Triggered in Closed Window (MODE=0, Short Window Mode)

**NOTE:** When the WDI\_OK rising edge approaches WDO when it is low, the  $t_6$  timer resets. In the above situation, the WDO reset signal keeps a  $t_6$ +WDI\_OK time.

## Synchronized by WDI and Triggered in Open Window (MODE=1, Long Window Mode)

# Synchronized by WDI and No-Trigger Signal (MODE=1, Long Window Mode)

## Synchronized by WDI and Triggered in Closed Window (MODE=1, Long Window Mode)

**NOTE:** When the WDI\_OK rising edge approaches WDO when it is low, the  $t_6$  timer resets. In the above situation, the WDO reset signal keeps a  $t_6$ +WDI\_OK time.

## **STATE DIAGRAM**

**NOTE:** The above state diagram does not show a WDI error situation.

#### **APPLICATION INFORMATION**

#### Selecting the Inductor

The  $I_{peak}$  is fixed, and the inductor value can be determined with Equation (3):

$$L = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{V_{IN} \times I_{peak} \times f_{s}}$$

(3)

Where  $f_{\text{S}}$  is the switching frequency at the maximum output current.

A larger inductor value results in a lower switching frequency and higher efficiency. However, the larger value inductor has a larger physical size, a higher series resistance, a lower saturation current, and/or a slow load transient dynamic performance. The inductor value has a lower limit, which is determined by the minimum on time. To keep the inductor functioning properly, choose an inductor value that is higher than L<sub>MIN</sub>, which is derived from Equation (4):

$$L_{MIN} = \frac{V_{IN(MAX)} \times t_{ON(MIN)}}{I_{peak}}$$

(4)

Where  $V_{\text{IN(MAX)}}$  is the maximum value of the input voltage, and  $t_{\text{ON(MIN)}}$  is the 115ns minimum switch on time.

#### **Switching Frequency**

The switching frequency can be estimated with Equation (5):

$$f_s = \frac{2 \times Io \times V_{OUT} \times (V_{IN} - V_{OUT})}{I_{pools}^2 \times V_{IN} \times L}$$

(5)

A larger inductor can produce a lower  $f_S$ .  $f_S$  increases as lo increases. When lo increases to its maximum value  $I_{peak}/2$ ,  $f_S$  also reaches its highest value. The maximum  $f_S$  value can be estimated with Equation (6):

$$f_{s(max)} = \frac{V_{OUT} \times (V_{IN} - V_{OUT})}{I_{peak} \times V_{IN} \times L}$$

(6)

#### **Setting the Output Voltage**

The output voltage is set using a resistive voltage divider from the output voltage to FB. To achieve the desired output voltage, select a resistor divider using Equation (7):

$$\frac{R1}{R2} = \frac{V_{\text{OUT}}}{V_{\text{REF}}} - 1 \tag{7}$$

Where  $V_{REF}$  is the FB reference voltage 1V.

The current flowing into the resistor divider increases the supply current, especially at no-load and light-load conditions. The  $V_{\rm IN}$  supply current caused by the feedback resistors can be calculated with Equation (8):

$$I_{IN\_FB} = \frac{V_{OUT}}{R1 + R2} \times \frac{V_{OUT}}{V_{IN}} \times \frac{1}{\eta}$$

(8)

Where  $\eta$  is the efficiency of the regulator.

To reduce this current, resistors in the  $M\Omega$  range are recommended. The recommended value of the feedback resistors are shown in Table 1.

Table 1: Resistor Selection for Common Output Voltages

| V <sub>OUT</sub> (V) | R1 (kΩ) | R2 (kΩ) |

|----------------------|---------|---------|

| 3.3                  | 1200    | 523     |

| 5                    | 1200    | 300     |

## **Under-Voltage Lockout Point Setting**

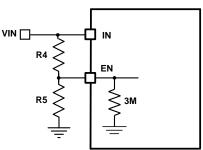

The MPQ2420 has an internal fixed undervoltage lockout (UVLO) threshold. The rising threshold is about 4.2V while the falling threshold is about 3.75V. An external resistor divider between EN and  $V_{\text{IN}}$  can be used to obtain a higher equivalent UVLO threshold (see Figure 3).

Figure 3: Adjustable UVLO Using EN

The UVLO threshold can be calculated with Equation (9) and Equation (10):

$$UVLO_{TH\_Rising} = (1 + \frac{R4}{3M/R5}) \times EN_{TH\_Rising}$$

(9)

$$UVLO_{TH\_Falling} = \left(1 + \frac{R4}{3M/R5}\right) \times EN_{TH\_Falling} \quad (10)$$

#### **Soft-Start Capacitor**

The soft-start time is the duration of an internal  $5\mu A$  current source charging the SS capacitor from 0 to the FB reference voltage (1V). The SS capacitor value can be determined with Equation (11):

$$C_{SS} = 5 \times t_{SS}(\mu F) \tag{11}$$

## **Feed-Forward Capacitor**

The HS-FET turns on when FB drops below the reference voltage, producing good load transient performance. However, this also causes the HS-FET to be sensitive to the FB voltage during turn-on. The HS-FET is easily affected by FB noise at turn-on, which can trigger a Fsw jitter. Fsw jitter occurs most often when the Vo ripple is very small. To improve jitter performance, it is recommended to use a small feed-forward capacitor of about 39pF between Vo and FB.

© 2016 MPS. All Rights Reserved.

# **TYPICAL APPLICATION CIRCUITS**

Figure 4: 3.3V Output Typical Application Circuit

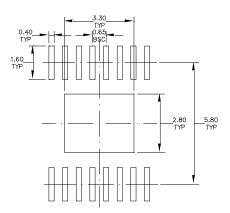

## PACKAGE INFORMATION

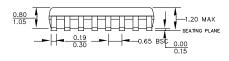

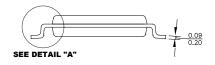

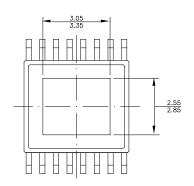

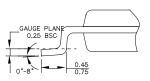

#### TSSOP-16 EP

**TOP VIEW**

**RECOMMENDED LAND PATTERN**

**FRONT VIEW**

**SIDE VIEW**

**BOTTOM VIEW**

**DETAIL "A"**

#### NOTE:

- 1) ALL DIMENSIONS ARE IN MILLIMETERS.

- 2) PACKAGE LENGTH DOES NOT INCLUDE MOLD

- FLASH, PROTRUSION OR GATE BURR.

- 3) PACKAGE WITDH DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION.

- 4) LEAD COPLANARITY (BOTTOM OF LEADS AFTER FORMING) SHALL BE 0.10 MILLIMETERS MAX.

- 5) DRAWING CONFORMS TO JEDEC MO-153, VARIATION ABT.

- 6) DRAWING IS NOT TO SCALE.

**NOTICE:** The information in this document is subject to change without notice. Please contact MPS for current specifications. Users should warrant and guarantee that third party Intellectual Property rights are not infringed upon when integrating MPS products into any application. MPS will not assume any legal responsibility for any said applications.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.