# 4-PLL Spread-Spectrum Clock Generator

#### **Features**

- Input frequencies

- □ Crystal input: 8 MHz to 48 MHz

- ☐ Reference clock: 8 MHz to 250 MHz LVCMOS

- □ Reference clock: 8 MHz to 700 MHz differential

- Output frequencies

- 25 MHz to 700 MHz LVDS, LVPECL, HCSL, CML

- 3 MHz to 250 MHz LVCMOS

- □ 1 kHz to 8 MHz for one LVCMOS output

- RMS phase jitter: 1-ps max at 12-kHz to 20-MHz offset

- PCIe 1.0/2.0/3.0 compliant

- SATA 2.0, USB 2.0/3.0, 1/10-GbE compliant

- Maximum 12 outputs split in two banks of six outputs each.

- □ Up to eight differential output pairs (HCSL, LVPECL, CML, or LVDS)

- □ Up to 12 LVCMOS outputs

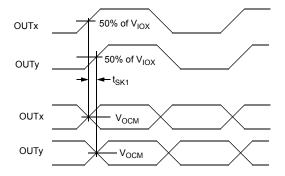

- Up to 75-ps skew for differential outputs within a bank

- Four fractional N-type phase-locked loops (PLLs) with □ VCXO (±120 ppm with steps of 0.23 ppm)

- □ Spread-spectrum capability (Logic SS and Lexmark profile 0.1% to 5% in 0.1% steps, down or center spread)

- Supply voltage: 1.8 V, 2.5 V, and 3.3 V

- Zero-delay buffer (ZDB) and non-zero delay buffer (NZDB) configurations

- I<sup>2</sup>C configurable with onboard programming

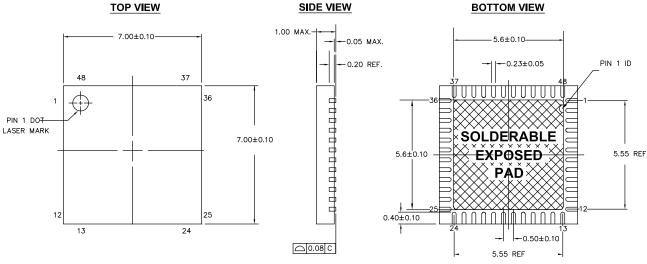

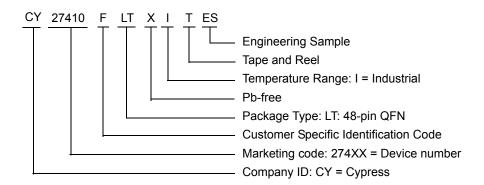

- Industrial-grade device, offered in 48-pin QFN (7 × 7 × 1.0 mm) package

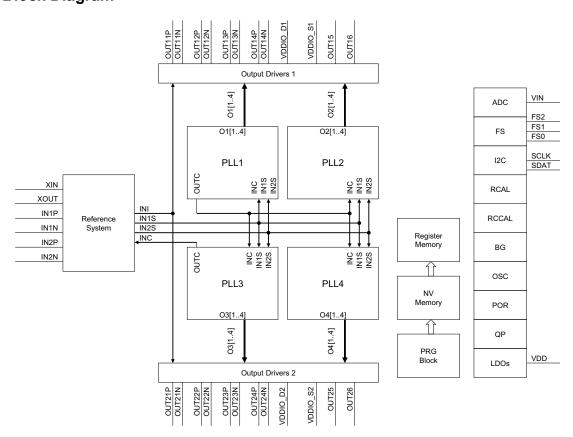

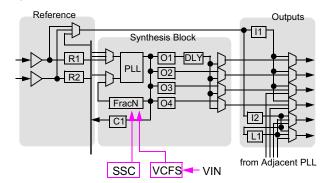

# Logic Block Diagram

Cypress Semiconductor Corporation Document Number: 001-89074 Rev. \*D

198 Champion Court

San Jose, CA 95134-1709 • 408-943-2600 Revised February 19, 2015

# Contents

| Functional Description         | 3  |

|--------------------------------|----|

| Input System                   | 3  |

| VCXO Input Block               |    |

| Frequency Select Input         | 3  |

| I2C Block (SCLK, SDAT)         | 4  |

| Synthesis Section              | 4  |

| Output Section                 | 4  |

| Onboard Programming            | 5  |

| Functional Features            |    |

| and Application Considerations | 5  |

| Pinouts                        | 10 |

| CY27410 Pinout                 | 10 |

| Electrical Specifications      | 13 |

| Absolute Maximum Ratings       | 13 |

| Operating Temperature          | 13 |

| Operating Power Supply         | 13 |

| DC Chip-Level Specifications   | 14 |

| DC Output Specifications       | 15 |

| AC Input Clock Specifications  | 16 |

| 16 |

|----|

| 22 |

| 23 |

| 25 |

| 25 |

| 26 |

| 26 |

| 27 |

| 27 |

| 27 |

| 28 |

| 31 |

| 31 |

| 31 |

| 31 |

| 31 |

| 31 |

|    |

# **Functional Description**

The CY27410 is a standard-performance programmable clock generator with four independent fractional PLLs, which generates any frequency with a zero-ppm synthesis error. Each PLL is followed by a set of four independent dividers to generate four different frequencies from a single PLL. All four dividers are synchronized to generate phase-aligned clock outputs with minimal skew. The PLLs also support the spread-spectrum feature to reduce EMI. All four PLLs are equipped with VCXO functionality to achieve ppm granularity of output frequency.

CY27410 is the master device with 12 outputs compared to CY27430 with 7, but the feature sets of the two devices are identical.

The CY27410 accepts a crystal clock or a single-ended/differential reference clock. The device supports up to 12 outputs, divided into two banks of six outputs each. Four outputs of PLL1 and PLL2 are multiplexed to output Bank1, and four clock outputs of PLL3 and PLL4 are multiplexed to output Bank2. The 12 outputs of the two banks are configurable as eight differential outputs, 12 single-ended outputs, or a combination of differential and single-ended outputs.

The CY27410 has an on-chip volatile and nonvolatile memory, composed of eight registers, which store the device configuration settings. These registers can be accessed and programmed onboard through the I<sup>2</sup>C interface. You can also configure the device on-the-fly to completely reprogram the device on the application board. Besides the I<sup>2</sup>C interface, external signals can be applied to multifunction pins for different functions such as the following:

- Dynamically change the output frequency

- Output enable/disable

- Power down

- Spread ON/OFF

One low-frequency clock output, in kilohertz, is provided to meet the need of widely used reference frequencies, such as 32.768 kHz. The jitter specs of CY27410 make it an ideal choice for the following communication protocols: PCIe 1.0/2.0/3.0, USB 2.0/3.0, SATA 1.0/2.0, and 1/10GbE.

#### Input System

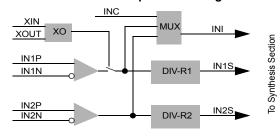

The input system supports the following (see Figure 1):

- XIN/XOUT supports crystal input.

- IN1 supports differential and single-ended clock inputs.

- IN2 supports differential and single-ended clock inputs.

Figure 1. Oscillator/Clock Input Block Diagram

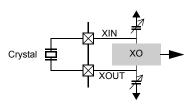

If a crystal is used, XIN and XOUT are connected to a crystal oscillator to generate the required internal frequency, as shown in Figure 2. The supported differential tuning capacitor range is 8 pF to 12 pF. To do this, there are two banks of capacitors – one coarse and the other fine.

Figure 2. Connecting a Crystal

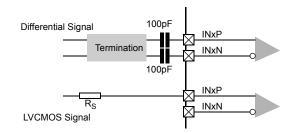

IN1 and IN2 are designed to accept either a single-ended or differential reference input. IN2 can be used to accept the feedback signal to implement the ZDB functionality of the device.

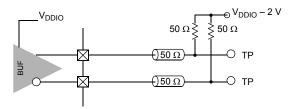

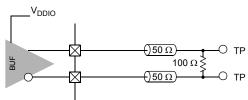

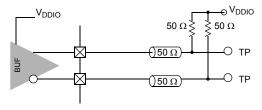

The differential inputs are capable of interfacing with multiple standards, such as LVPECL, LVDS, CML, and HCSL. The differential signals must be of AC-coupling, as shown in Figure 3.

Figure 3. Interfacing Differential and Single-Ended Signals

#### **VCXO Input Block**

The VIN input is used for the VCXO functionality of the device. In this functionality, the output can change with respect to an input voltage required for audio-visual applications. The output frequency can vary up to ±120 ppm. This input voltage directly controls the PLL1 fractional divider to provide the VCXO functionality.

#### Frequency Select Input

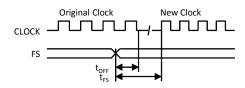

CY27410 supports frequency-select features with which the customer can change output frequencies on-the-fly. The device has eight configuration register sets, which can be preprogrammed or written through I<sup>2</sup>C. Changing the signal level of the FS pins (high and low) selects the appropriate configuration registers and changes the output frequency accordingly.

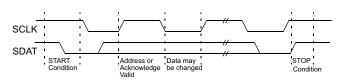

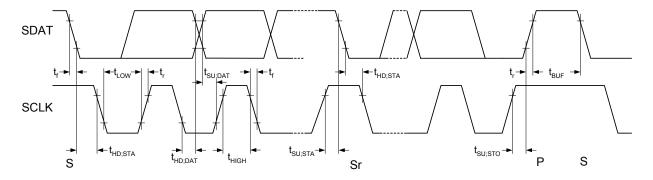

# I<sup>2</sup>C Block (SCLK, SDAT)

CY27410 supports I<sup>2</sup>C programming of internal registers, using which you can configure the device. CY27410 also supports user-profile programming to flash memory and allows partial updates. Read, Write, or Read/Write protection is also available. The device is compliant with the I<sup>2</sup>C-bus Specification, version 2.1 or later. The critical I<sup>2</sup>C specifications are as follows:

- 400 kb/s (Fast mode)

- 7-bit addressing support

- Selectable device address (programmable), default = 69 hex (7 bits)

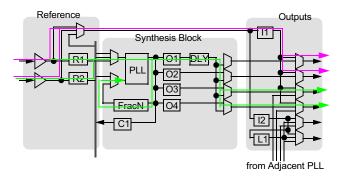

#### **Synthesis Section**

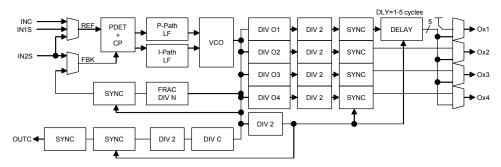

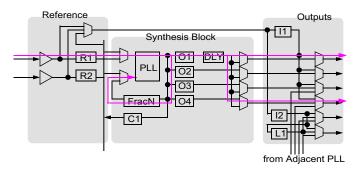

CY27410 consists of four PLLs, which are the core synthesis blocks of the chip. Each PLL has a fractional N capability, which supports output frequency generation based on an input reference frequency to an accuracy of 100 ppb. The output of the PLL is fed into four dividers and then moves to synchronizers to generate glitch-free clock transition features, variable delay generation circuits to support the programmable delay feature, and so on. The output dividers and multiplexers are also included as part of this subsystem. All the four PLLs have the same architecture, as shown in Figure 4.

Figure 4. PLL Architecture

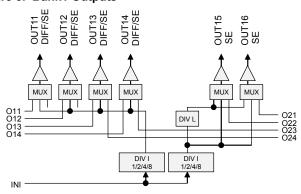

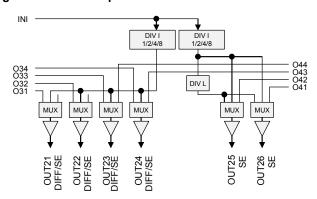

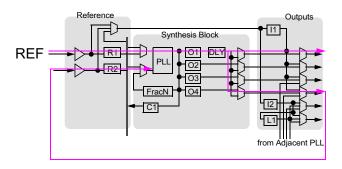

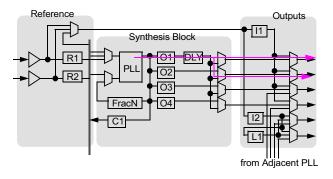

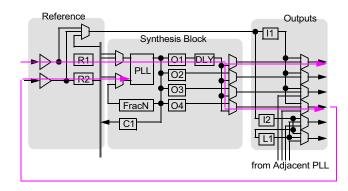

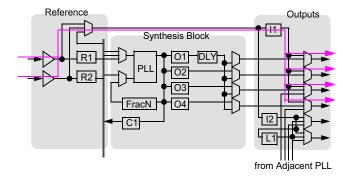

#### **Output Section**

CY27410 consists of two banks of outputs, which are located at the top and bottom of the device. Each bank consists of six outputs with OUT11–OUT14 and OUT21–OUT24 supporting both differential and single-ended outputs and OUT15–OUT16 and OUT25–OUT26 supporting only single-ended outputs.

Each output is fed from a PLL through a divider and then to a MUX, which helps in selecting the source for the output, as shown in Figure 5 and Figure 6.

Figure 5. Bank1 Outputs

Figure 6. Bank2 Outputs

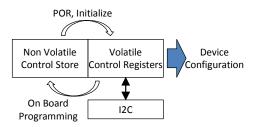

# **Onboard Programming**

You can write the device memory on the customer board, enabling the use of a blank device that is not preprogrammed. This helps you to use the same device across multiple projects and lets you program the device based on individual projects. Conceptual onboard programming is shown in Figure 7.

Figure 7. Onboard Programming

#### **Functional Features and Application Considerations**

CY27410 is a 4-PLL spread-spectrum clock generator targeted at consumer, industrial, and low-end networking applications. The key specifications of the part are differential inputs (2) and outputs (12), supporting frequencies up to 700 MHz. The device has a low RMS phase jitter of 1-ps max and value-added features, such as VCXO, Frequency Select, and PLL Bypass modes. This part is designed to support key standards, such as PCIe 1.0/2.0/3.0, USB 2.0/3.0, and 10GbE.

The product supports LVDS, LVPECL, CML, HCSL, and LVCMOS logic levels.

#### Clock Generator

The main feature of CY27410 is frequency generation from an external reference (IN1) or a crystal. There are four variables to determine the final output frequency. They are input REF, the DIV-R (R1), FracN (DIV-N) dividers, and the post dividers (DIV-O). The basic formula for determining the final output frequency is:

- Clock Generator mode

□ f<sub>OUT</sub> = ((REF x DIV-N) / DIV-R) / DIV-O

- PLL Bypass mode

□ f<sub>OUT</sub> = REF / DIV-I or REF / DIV-I / DIV-L

The basic PLL block diagram is shown in Figure 8. Each of the outputs from the PLL is fed to the output MUX through a Delay circuit that provides a certain delay to the individual clock, if needed.

Figure 8. PLL Block Diagram, Clock Generation

#### PCIE (HCSL) Clock Generation

For PCIe applications, CY27410 provides eight differential outputs that have the same spread on it at any particular point of time

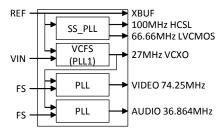

#### VCXO and Related Frequencies

CY27410 provides VCXO functionality and a cascading PLL option to generate critical frequencies with a fixed reference. Digital televisions have a requirement for the audio and video clocks to follow a 27-MHz VCXO signal so that they are synchronized. The architecture of the chip must ensure that this is met by cascading, as shown in Figure 9.

Figure 9. Cascading PLLs

Apart from having the audio and video clocks following the 27-MHz VCXO input, they also need complex divider ratios to generate the output frequencies. Commonly used divider ratios for audio and video signals are listed in Table 1.

Table 1. Audio and Video Frequencies

| Output Frequency | Ratios    |

|------------------|-----------|

| 74.17582418      | 91:250    |

| 33.8688          | 625:784   |

| 22.5792          | 1875:1568 |

| 16.9344          | 1250:784  |

| 11.2896          | 1875:784  |

| 5.6448           | 1875:392  |

| 36.864           | 375:512   |

#### Zero-Delay Buffer Functionality

CY27410 acts as a zero-delay buffer (ZDB) for one output from a single PLL block. To implement this feature, take one of the outputs and send it back as a feedback reference to the PLL. By providing a divider in the feedback loop, the device can also act as a frequency-multiplying ZDB (see Figure 10). This functionality is supported only when the PLL is in the integer N mode.

Figure 10. ZDB Configuration

CY27410 provides the frequency-multiplying ZDB by modulating the R1 and R2 values in the integer ratio. If both the values are identical, CY27410 acts as a simple ZDB.

#### Early/Late Output Phase

CY27410 supports a delay circuit in the divider to provide 0 to 5 × VCO/2 cycles. Therefore, an output has a certain lag phase or lead phase to other outputs when this feature is used. This functionality is also available in the ZDB mode and provides "early" phase or "delayed" phase to the Reference input. Refer to Figure 11 and Figure 12.

Figure 11. Early/Delayed Phase Output

Figure 12. Early/Late Phase in ZDB Configuration

#### Non-Zero Delay Buffer

CY27410 supports the PLL-bypass mode, which bypasses the entire synthesis block to act as a configurable non-zero delay buffer (NZDB) with level translation and selectable inputs, as shown in Figure 13.

Figure 13. NZDB Configuration

#### Combination Clock Generator and Buffer

CY27410 provides a combination of a clock generator and a buffer in one device. This is achieved by configuring the input and output selectors for the desired split configuration. An example of such an application is shown in Figure 14.

Figure 14. Clock Generator and NZDB

#### Low-Frequency Output

CY27410 integrates low-frequency generator counters for LVCMOS outputs that may be used for watchdog-time and/or kHz-order clocks for application, as shown in Figure 15.

Figure 15. Low-frequency Output Option

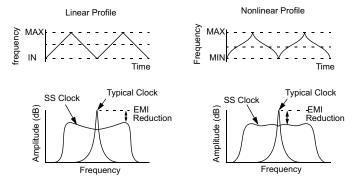

#### Spread Spectrum

To help reduce electromagnetic interference (EMI), CY27410 supports spread-spectrum modulation. The output clock frequencies can be modulated to spread energy across a broader range of frequencies and lower system EMI. CY27410 implements two types of spread profiles for modulation: linear and nonlinear.

The spread spectrum can be applied to any output clock, any frequency, and any spread amount ranging from 0.1% to 5% in 0.1% step. Center or down spread can be programmable.

The spread modulation rate is limited from 30 kHz to 60 kHz.

The spread spectrum is generated digitally in the FracN modulation, which means all the parameters are independent of process, voltage, and temperature variations. All the frequencies generating the same PLL have the same amount of modulation.

As shown in Figure 16, a harmonic of a modulated clock has a much lower amplitude than that of an unmodulated signal. The reduction in amplitude is dependent on the harmonic number and the frequency deviation or spread. The equation for the reduction in the nonlinear profile is:

$$dB = 6.5 + 9 * log_{10}(P) + 9 * log_{10}(F)$$

where P is the percentage of deviation and F is the frequency in megahertz where the reduction is measured.

Figure 16. Spread-Spectrum Profile

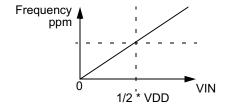

#### VCXO (VCFS) Functionality

CY27410 supports VCXO functionality without pulling the crystal frequency. This function is implemented by modulating the FracN counter according to the VIN level, as shown in Figure 17. Therefore, this is called voltage-controlled frequency shift (VCFS).

The VCFS function is implemented by modulating the FracN divider, which means all the parameters are independent of the process, voltage, and temperature variations.

It is not possible to combine the VCFS operation with spread spectrum (see Figure 18).

Figure 17. VCFS Profile

Figure 18. VCFS and Spread Spectrum

#### Crystal Oscillator

CY27410 supports various low-cost crystals as a reference oscillator at IN1 (XIN/XOUT) to generate multiple frequencies in a single chip. CY27410 supports a crystal with a nominal load capacitance specification from 8 pF to 12 pF. As shown in Figure 2 on page 3, CY27410 integrates all the components, such as a feedback resistor and tuning capacitor, to oscillate the clock with a particular crystal for the following specifications.

To enable proper operation, the crystal specification is divided into three ranges:

- Low range  $(F_{NOM})$  = 8 to 12 MHz

- Midrange = 12 to 20 MHz

- High range = 20 to 48 MHz

The corresponding crystal parameters are listed in Table 2.

**Table 2. Crystal Specifications**

| Range                  | Min Fre-<br>quency<br>(MHz) | Max Fre-<br>quency<br>(MHz) | Max R1<br>(ohms) | Max DL<br>(uW) |

|------------------------|-----------------------------|-----------------------------|------------------|----------------|

| Low                    | 8                           | 12                          | 150              | 100            |

| Mid                    | 12                          | 20                          | 70               | 100            |

| High                   | 20                          | 48                          | 50               | 100            |

| C <sub>L</sub> (pF) fo | r all Ranges                | Associated (pF)             |                  |                |

|                        | 8                           | 2                           |                  |                |

| 9 10                   |                             | 9 2                         |                  |                |

|                        |                             | 2                           |                  |                |

|                        | 12                          | 3                           |                  |                |

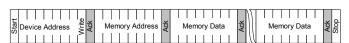

# Serial Programming Interface Protocol

The CY27410 uses the SDAT and SCLK pins for a 2-wire serial interface that operates up to 400 Kb/s in Read and Write modes. It complies with the I<sup>2</sup>C bus standard. The basic Write protocol is:

Start Bit; 7-bit Device Address; R/W Bit; Slave Clock Acknowledge (ACK); 8-bit Memory Address (MA); ACK; 8-bit Data; ACK; 8-bit Data in MA+1 if desired; ACK; 8-bit Data in MA+2; ACK; and more until STOP Bit.

The basic serial format is shown in Figure 19.

Figure 19. Data Transfer Sequence on the Serial Bus

A valid write operation must have a full 8-bit register address after the device address word from the master, which is followed by an acknowledge bit from the slave (SDAT = 0/LOW). The next eight bits must contain the data word intended for storage. After the data word is received, the slave responds with another acknowledge bit (SDAT = 0/LOW), and the master must end the write sequence with a STOP condition (see Figure 20).

Figure 20. Data Frame Architecture (Write)

Random Write

# Device Address X Memory Data X O

# **Sequential Write**

Read operations are initiated the same way as write operations, except that the R/W bit of the slave address is set to '1' (HIGH). There are two basic read operations: random read and sequential read. Figure 21 illustrates these operations.

Figure 21. Data Frame Architecture (Read)

# Random Read | Topological Address | Topolog

Through random read operations, the master may access any memory location. To perform this type of read operation, first set the word address. Send the address to CY27410 as part of a write operation. After the word address is sent, the master generates a START condition following the acknowledge. This terminates the write operation before any data is stored in the address, but not before the internal address pointer is set. Next, the master reissues the control byte with the R/W byte set to '1'.

Then, the CY27410 issues an acknowledge and transmits the 8-bit word. The master device does not acknowledge the transfer, but does generate a STOP condition, which causes the CY27410 to stop transmission.

Sequential read operations follow the same process as random reads, except that the master issues an acknowledge instead of a STOP condition after transmission of the first 8-bit data word. This action results in an incrementing of the internal address pointer, and subsequently output of the next 8-bit data word. By continuing to issue acknowledges instead of STOP conditions, the master may serially read the entire contents of the slave device memory.

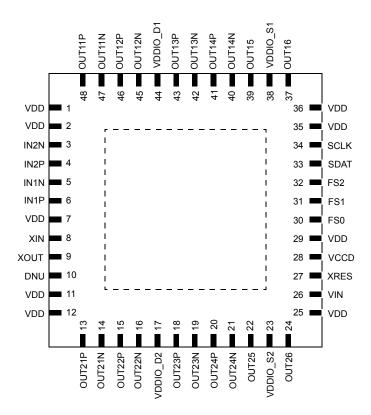

# **Pinouts**

The CY27410 devices are available in the 48-pin QFN package.

# CY27410 Pinout

The CY27410 is the master product that has the maximum number of outputs (12) with all the features including VCXO,  $I^2C$ , and Frequency Select options.

Table 3. 48-Pin QFN (CY27410) Pin Definitions

| Name   | I/O | Туре                     | # of Pins | Pin# | Function                                                                                                                                          |

|--------|-----|--------------------------|-----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| XIN    | I   | Crystal                  | 1         | 8    | XIN for crystal                                                                                                                                   |

| XOUT   | 0   | Crystal                  | 1         | 9    | XOUT for crystal                                                                                                                                  |

| IN1P   | I   | LVCMOS/<br>Differential  | 1         | 6    | True input for IN1 differential pair. IN1 for LVCMOS input. Need external series capacitor for differential input.                                |

| IN1N   | I   | Differential             | 1         | 5    | Complement input for IN1 differential pair. None for LVCMOS input. Need external series capacitor for differential input.                         |

| IN2P   | I   | LVCMOS /<br>Differential | 1         | 4    | Feedback input for ZDB mode. True input for IN2 differential pair. IN2 for LVCMOS input Need external series CAPS for differential input.         |

| IN2N   | I   | Differential             | 1         | 3    | Feedback input for ZDB mode. Complement input for IN2 differential pair. None for LVCMOS input. Need external series CAPS for differential input. |

| OUT15  | 0   | LVCMOS                   | 1         | 39   | LVCMOS clock output 15                                                                                                                            |

| OUT16  | 0   | LVCMOS                   | 1         | 37   | LVCMOS clock output 16                                                                                                                            |

| OUT11P | 0   | LVCMOS /<br>Differential | 1         | 48   | Output 11 true output (differential) or Output 11 LVCMOS                                                                                          |

| OUT11N | 0   | Differential             | 1         | 47   | Output 11 complement output (differential) connect to OUT11P for LVCMOS                                                                           |

| OUT12P | 0   | LVCMOS /<br>Differential | 1         | 46   | Output 12 true output (differential) or LVCMOS clock output 12                                                                                    |

| OUT12N | 0   | Differential             | 1         | 45   | Output 12 complement output (differential) connect to OUT12P for LVCMOS                                                                           |

| OUT13P | 0   | LVCMOS /<br>Differential | 1         | 43   | Output 13 complement output (differential) or Output 13 LVCMOS                                                                                    |

| OUT13N | 0   | Differential             | 1         | 42   | Output 13 complement output (differential) connect to OUT13P for LVCMOS                                                                           |

| OUT14P | 0   | LVCMOS /<br>Differential | 1         | 41   | Output 14 true output (differential) or Output 14 LVCMOS output                                                                                   |

| OUT14N | 0   | Differential             | 1         | 40   | Output 14 complement output (differential) connect to OUT14P for LVCMOS                                                                           |

| OUT21P | 0   | LVCMOS /<br>Differential | 1         | 13   | Output 21 true output (differential) or Output 21 LVCMOS output                                                                                   |

| OUT21N | 0   | Differential             | 1         | 14   | Output 21 complement output (differential) connect to OUT21P for LVCMOS                                                                           |

| OUT22P | 0   | LVCMOS /<br>Differential | 1         | 15   | Output 22 true output (differential) or Output 22 LVCMOS output                                                                                   |

| OUT22N | 0   | Differential             | 1         | 16   | Output 22 complement output (differential) connect to OUT22P for LVCMOS                                                                           |

| OUT23P | 0   | LVCMOS /<br>Differential | 1         | 18   | Output 23 true output (differential) or Output 23 LVCMOS output                                                                                   |

Table 3. 48-Pin QFN (CY27410) Pin Definitions (continued)

| Name     | I/O    | Туре                    | # of Pins | Pin#                        | Function                                                                                                                                       |

|----------|--------|-------------------------|-----------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|

| OUT23N   | 0      | Differential            | 1         | 19                          | Output 23 complement output (differential) connect to OUT23P for LVCMOS                                                                        |

| OUT24P   | 0      | LVCMOS/<br>Differential | 1         | 20                          | Output 24 true output (differential) or Output 24 LVCMOS output                                                                                |

| OUT24N   | 0      | Differential            | 1         | 21                          | Output 24 complement output (differential) connect to OUT24P for LVCMOS                                                                        |

| OUT25    | 0      | LVCMOS                  | 1         | 22                          | LVCMOS clock output 25                                                                                                                         |

| OUT26    | 0      | LVCMOS                  | 1         | 24                          | LVCMOS clock output 26                                                                                                                         |

| DNU      |        |                         | 1         | 10                          | Pin for test purpose                                                                                                                           |

| SDAT     | I/O    | LVCMOS/<br>Open Drain   | 1         | 33                          | I <sup>2</sup> C serial data pin                                                                                                               |

| SCLK     | I      | LVCMOS                  | 1         | 34                          | I <sup>2</sup> C clock pin                                                                                                                     |

| FS0      | I      | LVCMOS                  | 1         | 30                          | Frequency Select pin                                                                                                                           |

| FS1      | I      | LVCMOS                  | 1         | 31                          | Frequency Select pin                                                                                                                           |

| FS2      | I      | LVCMOS                  | 1         | 32                          | Frequency Select pin                                                                                                                           |

| VIN      | I      | Analog                  | 1         | 26                          | Voltage input for ADC                                                                                                                          |

| VDDIO_D1 | PWR    | PWR                     | 1         | 44                          | Output power supply for Bank1 differential outputs                                                                                             |

| VDDIO_S1 | PWR    | PWR                     | 1         | 38                          | Output power supply for Bank1 LVCMOS outputs                                                                                                   |

| VDDIO_D2 | PWR    | PWR                     | 1         | 17                          | Output power supply for Bank2 Differential outputs                                                                                             |

| VDDIO_S2 | PWR    | PWR                     | 1         | 23                          | Output power supply for Bank2 LVCMOS outputs                                                                                                   |

| VDD      | PWR    | PWR                     | 9         | 1,2,7,11,12,<br>25,29,35,36 | Core power supply                                                                                                                              |

| XRES     | I      | LVCMOS                  | 1         | 27                          | Active low RESET SIGNAL                                                                                                                        |

| GND      | GND    | GND                     | E-PAD     |                             | Supply ground                                                                                                                                  |

| VCCD     | Analog | Analog                  | 1         | 28                          | For 1.8-V operation, connect to VDD. For 2.5-V or 3.3-V operation, do not connect to VDD; connect a 100-nF capacitor between this pin and GND. |

Figure 22. 48-Pin QFN Pinout

# **Electrical Specifications**

Exceeding maximum ratings may shorten the useful life of the device.

# **Absolute Maximum Ratings**

# Table 4. Absolute Maximum Ratings

| Symbol             | Description                | Conditions                                        | Min  | Тур | Max                   | Units |

|--------------------|----------------------------|---------------------------------------------------|------|-----|-----------------------|-------|

| $V_{DD}$           | Core supply voltage        |                                                   | -0.5 | _   | 4.6                   | V     |

| V <sub>DDIOX</sub> | Output bank supply voltage |                                                   | -0.5 | _   | 4.6                   | V     |

| V <sub>IN</sub>    | Input voltage              | Relative to V <sub>SS</sub>                       | -0.5 | _   | V <sub>DD</sub> + 0.4 | V     |

| V <sub>INI2C</sub> | I2C Bus input voltage      | SCLK, SDAT pins                                   | -0.5 | _   | 6                     | V     |

| T <sub>S</sub>     | Storage temperature        | Non functional                                    | -55  | _   | +150                  | °C    |

| ESD <sub>HBM</sub> | ESD (human body model)     | JEDEC JS-001-2012                                 | 2000 | _   | _                     | V     |

| ESD <sub>CDM</sub> | ESD (charged device model) | JEDEC JESD22-C101E                                | 500  | _   | _                     | V     |

| ESD <sub>MM</sub>  | ESD (machine model)        | JEDEC JESD22-A115B                                | 200  | _   | -                     | V     |

| LU                 | Latchup                    | JEDEC JESD78D                                     | _    | _   | 140                   | mA    |

| UL-94              | Flammability rating        | V-0 at 1/8 in                                     | _    | _   | 10                    | ppm   |

| MSL                | Moisture sensitivity level |                                                   | -    | 3   | -                     |       |

| $\theta_{JA}$      | Package Thermal Resistance | PCB dimensions 76x114x1.6mm, 4 Layers, 0 air flow |      | 13  |                       | °C/W  |

# **Operating Temperature**

# Table 5. Operating Temperature

| Symbol         | Description          | Conditions | Min | Тур | Max  | Units |

|----------------|----------------------|------------|-----|-----|------|-------|

| T <sub>A</sub> | Ambient temperature  |            | -40 | _   | +85  | °C    |

| TJ             | Junction temperature |            | -40 | _   | +100 | °C    |

# **Operating Power Supply**

# **Table 6. Operating Power Supply**

| Symbol              | Description                        | Conditions                                                                             | Min  | Тур  | Max  | Units |

|---------------------|------------------------------------|----------------------------------------------------------------------------------------|------|------|------|-------|

| $V_{DD}$            | Core supply voltage                | 1.8-V range: ±5%                                                                       | 1.71 | 1.80 | 1.89 | V     |

|                     |                                    | 2.5-V range: ±10%                                                                      | 2.25 | 2.50 | 2.75 | V     |

|                     |                                    | 3.3-V range: 5%                                                                        | 3.13 | 3.3  | 3.46 | V     |

| V <sub>DDIO</sub>   | Output supply voltage              | 1.8-V range: ±5%                                                                       | 1.71 | 1.80 | 1.89 | V     |

|                     |                                    | 2.5-V range: ±10%                                                                      | 2.25 | 2.50 | 2.75 | V     |

|                     |                                    | 3.3-V range: 5%                                                                        | 3.13 | 3.30 | 3.46 | V     |

| I <sub>DDO</sub>    | Power supply current per pair      | LVPECL, output pair terminated 50 $\Omega$ to V <sub>TT</sub> (V <sub>DD</sub> -2 V)   | _    | _    | 38.0 | mA    |

|                     |                                    | LVPECL, output pair terminated 50 $\Omega$ to V <sub>TT</sub> (V <sub>DD</sub> -1.7 V) | _    | _    | 27.0 | mA    |

| I <sub>DDO</sub>    | Power supply current per pair      | LVDS, output pair terminated 100 $\Omega$                                              | _    | _    | 12.0 | mA    |

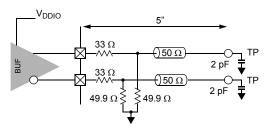

| I <sub>DDO</sub>    | Power supply current per pair      | HCSL, output pair terminated 33 $\Omega$ to 49.9 $\Omega$ to GND                       | _    | _    | 26.5 | mA    |

| I <sub>DDO</sub>    | Power supply current per pair      | CML, output pair terminated 50 $\Omega$ to $V_{DD}$                                    | _    | _    | 16.0 | mA    |

| I <sub>DDO</sub>    | Power supply current per pair      | CMOS, 10-pF load, 33 MHz                                                               | -    | _    | 6.0  | mA    |

| I <sub>DDPLL1</sub> | Current consumption per PLL        | Includes DIVC                                                                          | _    | _    | 26.5 | mA    |

| I <sub>DDXO</sub>   | XO/Input block current consumption | XO or IN1 input buffer on, IN2 input buffer off                                        | _    | _    | 3.5  | mA    |

**Table 6. Operating Power Supply** (continued)

| Symbol               | Description                                | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Min | Тур | Max | Units |

|----------------------|--------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|

| I <sub>DDPM</sub>    | Power management block current consumption |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _   | -   | 2.5 | mA    |

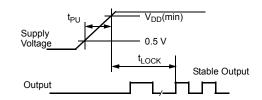

| t <sub>PLLLOCK</sub> | PLL lock time                              | Time from PLL enabled to PLL stable (PLL reaches at ±1-ppm accuracy)                                                                                                                                                                                                                                                                                                                                                                                                | _   | -   | 250 | μS    |

| t <sub>LOCK</sub>    | Device power-up time                       | Time from minimum specified $V_{DD}$ to Output Stable in XO-based clock gen mode. In the case of external clock input, $t_{LOCK}$ will reduce by the crystal oscillator startup time ( $t_{OSCSTART}$ ). This specification is valid when the reference is available and stable at startup. For supply ramps slower than the $t_{PU-SR}$ spec where customers use XRES during power up. Power-up time will be calculated from the release of XRES to output stable. | -   | -   | 8.0 | ms    |

| t <sub>PU_SR</sub>   | Power supply slew rate during power up     | Power-supply ramp rate for $V_{DD}$ to reach minimum specified voltage (power ramp must be monotonic). For supply ramps slower than 1 V/ms, use XRES to externally keep the part in RESET during power-up and release XRES after $V_{DD}$ reaches the minimum specification.                                                                                                                                                                                        | 1   | -   | 67  | V/ms  |

# **DC Chip-Level Specifications**

Table 7. DC Electrical Specifications Input

| Symbol               | Description                    | Conditions                                                 | Min  | Тур | Max  | Units |

|----------------------|--------------------------------|------------------------------------------------------------|------|-----|------|-------|

| V <sub>IH33</sub>    | Input high voltage             | LVCMOS and logic inputs, V <sub>DD</sub> = 3.3 V           | 2.0  | _   | _    | V     |

| V <sub>IH25</sub>    | Input high voltage             | LVCMOS and logic inputs, V <sub>DD</sub> = 2.5 V           | 1.7  | _   | _    | V     |

| V <sub>IH18</sub>    | Input high voltage             | LVCMOS and logic inputs, V <sub>DD</sub> = 1.8 V           | 1.1  | _   | _    | V     |

| V <sub>IL33</sub>    | Input low voltage              | LVCMOS and logic inputs, V <sub>DD</sub> = 3.3 V           | _    | _   | 0.8  | V     |

| V <sub>IL25</sub>    | Input low voltage              | LVCMOS and logic inputs, V <sub>DD</sub> = 2.5 V           | _    | _   | 0.7  | V     |

| V <sub>IL18</sub>    | Input low voltage              | LVCMOS and logic inputs, V <sub>DD</sub> = 1.8 V           | _    | _   | 0.5  | V     |

| $V_{DIFF}$           | Differential input             | LVDS, CML, PECL, HCSL. Differential amplitude, pk.         | 0.30 | -   | 1.45 | V     |

| DC <sub>DIFF</sub>   | Duty cycle, differential input | Measured at crossing point                                 | 40   | 50  | 60   | %     |

| DC <sub>LVCMOS</sub> | Duty cycle, LVCMOS input       | Measured at 1/2 V <sub>DD</sub>                            | 40   | 50  | 60   | %     |

| I <sub>IH</sub>      | Input high current             | Input = V <sub>DD</sub>                                    | _    | _   | 150  | μА    |

| I <sub>IL</sub>      | Input low current              | Input = GND                                                | -150 | _   | _    | μА    |

| C <sub>IN</sub>      | Input capacitance, IN1, IN2    | Measured at 10 MHz, differential                           | _    | _   | 3.0  | pF    |

| V <sub>PPSINE</sub>  | AC input swing pk              | Clipped sine wave, AC coupled through a 1000-pF capacitor. | 0.8  | 1.0 | 1.2  | V     |

| R <sub>P</sub>       | Input Pull-down resistance     | LVCMOS input                                               | 75   | 115 | 170  | kΩ    |

# **DC Output Specifications**

# Table 8. DC Specifications for LVCMOS Output

| Symbol          | Description         | Conditions | Min                    | Тур | Max | Units |

|-----------------|---------------------|------------|------------------------|-----|-----|-------|

| V <sub>OH</sub> | Output high voltage | 4-mA load  | V <sub>DDIO</sub> -0.3 | 1   | -   | V     |

| $V_{OL}$        | Output low voltage  | 4-mA load  | _                      | 1   | 0.3 | V     |

# Table 9. DC Specifications for LVDS Output ( $V_{\rm DDIO}$ = 2.5-V or 3.3-V range)

| Symbol           | Description                                                   | Conditions                                                        | Min   | Тур   | Max   | Units |

|------------------|---------------------------------------------------------------|-------------------------------------------------------------------|-------|-------|-------|-------|

| V <sub>PP</sub>  | LVDS output AC single-ended pk-pk,                            | 8 MHz to 325 MHz                                                  | 250   | _     | 470   | mV    |

| V <sub>PP</sub>  | LVDS output AC single-ended pk-pk                             | 325 MHz to 700 MHz                                                | 200   | _     | 470   | mV    |

| $\Delta V_{PP}$  | Change in V <sub>PP</sub> between complementary output states |                                                                   | -     | _     | 50    | mV    |

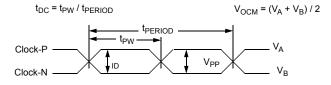

| V <sub>OCM</sub> | Output common-mode voltage                                    | Met only at 2.5 V and 3.3 V. Need AC coupling for 1.8-V operation | 1.125 | 1.200 | 1.375 | V     |

| $\Delta V_{OCM}$ | Change in VOCM between complementary output states            |                                                                   | -     | _     | 50    | mV    |

| I <sub>OZ</sub>  | Output leakage current                                        | Output off, V <sub>OUT</sub> = 0.75 V to 1.75 V                   | -20   | _     | 20    | μΑ    |

# Table 10. DC Specifications for LVPECL Output ( $V_{DDIO} = 2.5$ -V or 3.3-V range)

| Symbol          | Description             | Conditions                                                         | Min                         | Тур | Max                         | Units |

|-----------------|-------------------------|--------------------------------------------------------------------|-----------------------------|-----|-----------------------------|-------|

| V <sub>OH</sub> | Output high voltage     | R-term = 50 $\Omega$ to V <sub>TT</sub> (V <sub>DDIO</sub> -2.0 V) | V <sub>DDIO</sub><br>–1.165 | -   | V <sub>DDIO</sub><br>-0.850 | V     |

| V <sub>OL</sub> | Output low voltage      | R-term = 50 $\Omega$ to V <sub>TT</sub> (V <sub>DDIO</sub> –2.0 V) | V <sub>DDIO</sub> –2.0      | 1   | V <sub>DDIO</sub><br>-1.620 | V     |

| $V_{PP}$        | LVPECL output AC single | f <sub>OUT</sub> = 8 MHz to 150 MHz                                | 450                         | _   | _                           | mV    |

|                 | ended pk-pk,            | f <sub>OUT</sub> = 150 MHz to 700 MHz                              | 320                         | ı   | _                           | mV    |

# Table 11. DC Specifications for CML Output ( $V_{\rm DDIO}$ = 2.5-V or 3.3-V range)

| Symbol          | Description                      | Conditions                               | Min                   | Тур | Max                       | Units |

|-----------------|----------------------------------|------------------------------------------|-----------------------|-----|---------------------------|-------|

| V <sub>OH</sub> | Output high voltage              | R-term= 50 $\Omega$ to V <sub>DDIO</sub> | V <sub>DDIO</sub> -0. | _   | _                         | V     |

| V <sub>OL</sub> | Output low voltage               | R-term= 50 $\Omega$ to V <sub>DDIO</sub> | V <sub>DDIO</sub> -0. | _   | V <sub>DDIO</sub><br>-0.3 | V     |

| V <sub>PP</sub> | CML output AC single-ended pk-pk | f <sub>OUT</sub> = 8 MHz to150 MHz       | 250                   | _   | 700                       | mV    |

| V <sub>PP</sub> | CML output AC single-ended pk-pk | 150 < f <sub>OUT</sub> < 700 MHz         | 200                   | -   | 600                       | mV    |

Table 12. DC Specifications for HCSL Output ( $V_{DDIO} = 2.5$ -V or 3.3-V range)

| Symbol                  | Description                                                 | Conditions                                   | Min | Тур | Max         | Units |

|-------------------------|-------------------------------------------------------------|----------------------------------------------|-----|-----|-------------|-------|

| V <sub>OCM</sub>        | Output common mode voltage                                  | Common mode                                  | 350 | -   | 400         | mV    |

| V <sub>OHDIFF</sub>     | Differential output high voltage                            | Measurement taken from differential waveform | 150 | -   | -           | mV    |

| V <sub>OLDIFF</sub>     | Differential output low voltage                             | Measurement taken from differential waveform | -   | -   | <b>–150</b> | mV    |

| V <sub>CROSS</sub>      | Absolute crossing point voltage                             | Measurement taken from single-ended waveform | 250 | -   | 550         | mV    |

| V <sub>CROSSDELTA</sub> | Variation of V <sub>CROSS</sub> over all rising clock edges | Measurement taken from single-ended waveform | _   | -   | 140         | mV    |

# Table 13. Input Frequency Range

| Symbol                 | Description                        | Conditions                                      | Min | Тур | Max | Units |

|------------------------|------------------------------------|-------------------------------------------------|-----|-----|-----|-------|

| F <sub>CRYSTAL</sub>   | Crystal frequency                  | Fundamental AT CUT crystal                      | 8   | _   | 48  | MHz   |

| F <sub>REFERENCE</sub> | Reference frequency                | Internal reference to PLL                       | 8   | _   | 40  | MHz   |

| F <sub>INCMOS</sub>    | LVCMOS input frequency             | Buffer mode, all PLLs OFF                       | 8   | -   | 250 | MHz   |

| F <sub>INCMOS</sub>    | LVCMOS input frequency             | Buffer mode, one or more PLL active             | 8   | -   | 125 | MHz   |

| F <sub>INCMOS</sub>    | LVCMOS input frequency             | CLKGEN mode                                     | 8   | _   | 250 | MHz   |

| F <sub>INCMOS</sub>    | LVCMOS input frequency             | ZDB mode, PLL in integer N configuration        | 8   | _   | 250 | MHz   |

| F <sub>INDIFF</sub>    | Differential clock input frequency | Buffer mode, all PLLs OFF                       | 8   | _   | 700 | MHz   |

| F <sub>INDIFF</sub>    | Differential clock input frequency | Buffer mode, one or more PLL active             | 8   | _   | 125 | MHz   |

| F <sub>INDIFF</sub>    | Differential clock input frequency | CLKGEN mode                                     | 8   | _   | 300 | MHz   |

| F <sub>INDIFF</sub>    | Differential clock input frequency | ZDB mode, PLL in integer N configuration        | 8   | _   | 300 | MHz   |

| F <sub>INCAS</sub>     | Cascading clock frequency          | Internal cascading frequency in the Buffer mode | 8   | 1   | 125 | MHz   |

# **AC Input Clock Specifications**

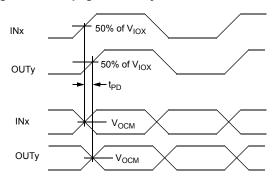

# Table 14. AC Input Clock Electrical Specification

| Symbol              | Description                   | Conditions                                         | Min | Тур | Max | Units |

|---------------------|-------------------------------|----------------------------------------------------|-----|-----|-----|-------|

| t <sub>CMOSDC</sub> | LVCMOS input duty cycle       | Measured at 1/2 V <sub>DD</sub> 20-80%, Functional | 40  | 50  | 60  | %     |

| t <sub>DIFFDC</sub> | Differential input duty cycle | Measured at V <sub>OCM</sub> 20-80%, Functional    | 40  | 50  | 60  | %     |

| t <sub>RFCMOS</sub> | LVCMOS input rise/fall time   | Measured between 20-80% of V <sub>DD</sub>         | _   | _   | 4   | ns    |

# **AC Output Specifications**

Table 15. AC Electrical Specifications LVCMOS Output. Load: 15 pF < 100MHz, 7.5 pF < 200 MHz, 5 pF > 200 MHz

| Symbol                              | Description           | Conditions                                                                               | Min | Тур | Max | Units |  |  |

|-------------------------------------|-----------------------|------------------------------------------------------------------------------------------|-----|-----|-----|-------|--|--|

| Common AC Electrical Specifications |                       |                                                                                          |     |     |     |       |  |  |

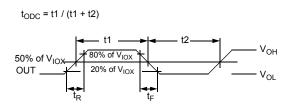

| t <sub>RFCMOS</sub>                 | Rise/fall time        | f <sub>OUT</sub> < 100MHz, 20%–80%                                                       | -   | _   | 2.0 | ns    |  |  |

| t <sub>RFCMOS</sub>                 | Rise/fall time        | f <sub>OUT</sub> < 200MHz, 20%–80%                                                       | -   | -   | 1.5 | ns    |  |  |

| t <sub>RFCMOS</sub>                 | Rise/fall time        | f <sub>OUT</sub> < 250MHz, 20%–80%                                                       | -   | -   | 1.3 | ns    |  |  |

| t <sub>SKEW</sub>                   | Output to output skew | Equally loaded, measured at 1/2 V <sub>IOX</sub> , in a bank, derived from the same PLL, | -   | _   | 100 | ps    |  |  |

| <b>Buffer Mod</b>                   | e                     |                                                                                          |     |     | •   |       |  |  |

| f <sub>OUT</sub>                    | Output frequency      | All PLLs off                                                                             | 8   |     | 250 | MHz   |  |  |

| f <sub>OUT</sub>                    | Output frequency      | With one or more PLL running                                                             | 8   |     | 125 | MHz   |  |  |

Table 15. AC Electrical Specifications LVCMOS Output. Load: 15 pF < 100MHz, 7.5 pF < 200 MHz, 5 pF > 200 MHz (continued)

| Symbol               | Description                      | Conditions                                                                                                                                                                                                                                           | Min   | Тур | Max | Units |

|----------------------|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-----|-------|

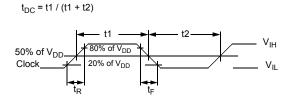

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 V <sub>IOX</sub> .<br>Input DC = 50%                                                                                                                                                                                                 | 40    | 50  | 60  | %     |

| t <sub>JIT_ADD</sub> | Additive RMS phase jitter        | f <sub>OUT</sub> = 156.25 MHz, 12k-20 MHz offset,<br>DIVI=1.Input slew rate 1.8 V/ns 20%–80%<br>V <sub>DD</sub>                                                                                                                                      | -     | 0.7 | 1.0 | ps    |

| t <sub>DELAY</sub>   | Propagation delay                | Input to output delay                                                                                                                                                                                                                                | -     | _   | 7.0 | ns    |

| ZDB Mode (           | IN1 = REF, Differential or LVCMO | OS feedback to IN2)                                                                                                                                                                                                                                  |       |     |     |       |

| $f_{OUT}$            | Output frequency                 |                                                                                                                                                                                                                                                      | 8     | _   | 250 | MHz   |

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 $V_{IOX}$ ,<br>$f_{OUT}$ > 200 MHz, $V_{DDIO}$ = 2.5 V or 3.3 V.<br>$f_{OUT}$ > 100MHz, $V_{DDIO}$ = 1.8 V                                                                                                                           | 40    | 50  | 60  | %     |

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 $V_{IOX}$ , $f_{OUT} \le 200$ MHz $V_{DDIO}$ = 2.5 V or 3.3 V. $f_{OUT} \le 100$ MHz, $V_{DDIO}$ = 1.8 V                                                                                                                             | 45    | 50  | 55  | %     |

| toccj                | Cycle-to-cycle jitter            | pk, measured at 1/2 $V_{\rm IOX}$ over 10-k cycle, $f_{\rm OUT}$ = 100 MHz.Input slew rate 1.8V/ns 20%–80% $V_{\rm DD}$ . Configuration dependent                                                                                                    | -     | _   | 50  | ps    |

| t <sub>PJ</sub>      | Period jitter                    | pk-pk, measured at 1/2 $V_{\rm IOX}$ over 10-k cycle, $f_{\rm OUT}$ = 100 MHz.Input slew rate 1.8 V/ns 20%–80% $V_{\rm DD}$ . Configuration dependent                                                                                                | -     | _   | 100 | ps    |

| t <sub>PDELAY</sub>  | Propagation delay                | Measured at 1/2 V <sub>IOX</sub> ±250 ps excludes any delay added onboard (from output to inputs). Delay onboard (t <sub>DELAY_BOARD</sub> ) must not exceed 2-ns max. Total delay in the ZDB mode is t <sub>DELAY_BOARD</sub> + t <sub>PDELAY</sub> | -250  | _   | 250 | ps    |

| CLKGEN Mo            | ode                              |                                                                                                                                                                                                                                                      |       |     |     |       |

| f <sub>OUT</sub>     | Output frequency                 |                                                                                                                                                                                                                                                      | 3     | _   | 250 | MHz   |

| f <sub>OUTL</sub>    | Low frequency output             | 1 kHz is supported when the max input frequency to DIVL is 48 MHz                                                                                                                                                                                    | 0.001 | _   | 50  | MHz   |

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 $V_{IOX}$ , $f_{OUT} > 200$ MHz, $V_{DDIO} = 2.5$ V or 3.3 V. $f_{OUT} > 100$ MHz, $V_{DDIO} = 1.8$ V                                                                                                                                | 40    | 50  | 60  | %     |

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 $V_{IOX}$ , $f_{OUT} \le 200$ MHz $V_{DDIO} = 2.5$ V or 3.3 V. $f_{OUT} \le 100$ MHz, $V_{DDIO} = 1.8$ V                                                                                                                             | 45    | _   | 55  | %     |

| t <sub>CCJ</sub>     | Cycle-to-cycle jitter            | pk, measured at 1/2 $V_{IOX}$ over 10-k cycle, $f_{OUT}$ =100 MHz. Configuration dependent                                                                                                                                                           | -     | _   | 50  | ps    |

| t <sub>PJ</sub>      | Period jitter                    | pk-pk, measured at 1/2 $V_{\rm IOX}$ over 10-k cycle, $f_{\rm OUT}$ = 100 MHz. Input reference 25-MHz crystal. Configuration dependent                                                                                                               | -     | _   | 100 | ps    |

| SSC Mode             |                                  |                                                                                                                                                                                                                                                      |       |     |     |       |

| f <sub>OUT</sub>     | Output frequency                 |                                                                                                                                                                                                                                                      | 3     |     | 250 | MHz   |

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 $V_{IOX}$ ,<br>$f_{OUT}$ > 200 MHz, $V_{DDIO}$ = 2.5 V or 3.3 V.<br>$f_{OUT}$ > 100 MHz, $V_{DDIO}$ = 1.8 V                                                                                                                          | 40    | 50  | 60  | %     |

| t <sub>DC</sub>      | Output duty cycle                | Measured at 1/2 $V_{IOX}$ , $f_{OUT} \le 200$ MHz $V_{DDIO} = 2.5$ V or 3.3 V. $f_{OUT} \le 100$ MHz, $V_{DDIO} = 1.8$ V                                                                                                                             | 45    | 50  | 55  | %     |

| t <sub>CCJ</sub>     | Cycle-to-cycle jitter            | pk, measured at 1/2 V <sub>IOX</sub> over 10-k cycle, f <sub>OUT</sub> = 100 MHz, with a spread of 0.5%. Input reference 25-MHz crystal. Configuration dependent                                                                                     | -     | _   | 100 | ps    |

|                      | _t                               | ı                                                                                                                                                                                                                                                    |       |     | ·   |       |

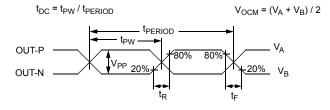

Table 16. AC Electrical Specifications, Differential Output (LVPECL, CML, LVDS) [1]

| Symbol               | Description                        | Conditions                                                                                                                                                                                                                                                                            | Min  | Тур | Max  | Units      |

|----------------------|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|------------|

| COMMON AC            | C Electrical Specifications        |                                                                                                                                                                                                                                                                                       |      |     |      |            |

| t <sub>RF</sub>      | PECL output rise/fall time         | 20%–80% of AC levels, measured at 622.08 MHz                                                                                                                                                                                                                                          | -    | _   | 450  | ps         |

| t <sub>RF</sub>      | CML output rise/fall time          | 20%–80% of AC levels, measured at 622.08 MHz                                                                                                                                                                                                                                          | -    | _   | 450  | ps         |

| t <sub>RF</sub>      | LVDS output rise/fall time         | 20%–80% of AC levels, measured at 622.08 MHz                                                                                                                                                                                                                                          | -    | _   | 450  | ps         |

| t <sub>SK1</sub>     | Output skew                        | Four differential output pairs in a bank, derived from the same PLL, with same standard and load conditions                                                                                                                                                                           | -    | _   | 75   | ps         |

| BUFFER Mod           | de                                 |                                                                                                                                                                                                                                                                                       |      |     |      |            |

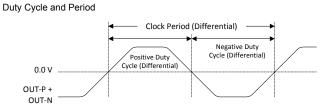

| t <sub>ODC</sub>     | Output duty cycle                  | Differential input signal at 50% duty cycle, differential signal, 622.08 MHz                                                                                                                                                                                                          | 45   | 50  | 55   | %          |

| t <sub>ODC</sub>     | Output duty cycle                  | LVCMOS input signal at 50% duty cycle, differential signal, 250 MHz                                                                                                                                                                                                                   | 40   | 50  | 60   | %          |

| t <sub>PD</sub>      | Propagation delay                  | Measured at differential signal,<br>156.25 MHz                                                                                                                                                                                                                                        | -    | _   | 4    | ns         |

| t <sub>JIT_ADD</sub> | Additive RMS phase jitter          | f <sub>OUT</sub> = 156.25 MHz, 12-k to 20-MHz offset,<br>DIV1 = 1. Input slew rate 4 V/ns differential<br>400-mV amplitude.                                                                                                                                                           | -    | _   | 400  | fs         |

| ZDB Mode (F          | REF=IN1, 1 pair of output is feedb | ack to IN2)                                                                                                                                                                                                                                                                           |      |     |      |            |

| t <sub>ODC</sub>     | Output duty cycle                  | Measured at differential signal, 100 MHz                                                                                                                                                                                                                                              | 45   | 50  | 55   | %          |

| t <sub>CCJ</sub>     | Cycle-to-cycle jitter              | pk, measured differential signal over 10-k cycle, f <sub>OUT</sub> =156.25 MHz. Input slew rate 4 V/ns differential 400-mV amplitude. (all differential outputs on)                                                                                                                   | -    | _   | 50   | ps         |

| t <sub>PJ</sub>      | Period jitter                      | pk-pk, measured differential signal over 10-k cycle, f <sub>OUT</sub> = 156.25 MHz. Input slew rate 4 V/ns differential 400-mV amplitude. (all differential outputs on)                                                                                                               | -    | _   | 50   | ps         |

| t <sub>PD</sub>      | Propagation delay                  | Measured differential signal, f <sub>OUT</sub> = 156.25 MHz, ±250 ps is excluding any delay added onboard (from output to inputs). Delay onboard (t <sub>DELAY_BOARD</sub> ) must not exceed 2-ns max.  Total delay in the ZDB mode is t <sub>DELAY_BOARD</sub> + t <sub>PDELAY</sub> | -200 |     | 200  | ps         |

| t <sub>JRMS</sub>    | RMS phase jitter                   | f <sub>IN</sub> = f <sub>OUT</sub> = 156.25 MHz, 12-k to 20-MHz offset. Input slew rate 4 V/ns differential 400-mV amplitude                                                                                                                                                          | -    | 0.7 | 1.0  | ps         |

| PNg10k               | Phase noise, offset10 kHz          | f <sub>IN</sub> = f <sub>OUT</sub> = 156.25 MHz. Input slew rate 4 V/ns differential 400-mV amplitude.                                                                                                                                                                                | -    | _   | -110 | dBc/<br>Hz |

| PNg100k              | Phase noise, offset = 100 kHz      | f <sub>IN</sub> = f <sub>OUT</sub> = 156.25 MHz. Input slew rate 4 V/ns differential 400-mV amplitude.                                                                                                                                                                                | -    | -   | -119 | dBc/<br>Hz |

| PNg1M                | Phase noise, offset = 1 MHz        | f <sub>IN</sub> = f <sub>OUT</sub> = 156.25 MHz. Input slew rate 4 V/ns differential 400-mV amplitude.                                                                                                                                                                                | _    | -   | -131 | dBc/<br>Hz |

| PNg10M               | Phase noise, offset = 10 MHz       | f <sub>IN</sub> = f <sub>OUT</sub> = 156.25 MHz. Input slew rate 4 V/ns differential 400-mV amplitude.                                                                                                                                                                                | -    | _   | -147 | dBc/<br>Hz |

#### Note

<sup>1.</sup> AC parameters for differential outputs are guaranteed for only differential outputs. LVCMOS is Off.

Table 16. AC Electrical Specifications, Differential Output (LVPECL, CML, LVDS) [1] (continued)

| Symbol            | Description                   | Conditions                                                                                                                                                                      | Min | Тур | Max  | Units      |

|-------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------------|

| PN-SPUR           | Spur                          | At frequency offsets equal to and greater than the update rate of the PLL. Input slew rate 4 V/ns differential 400-mV amplitude.                                                | -   | _   | -65  | dBc/<br>Hz |

| CLKGEN Mo         | de                            |                                                                                                                                                                                 |     | •   | •    | •          |

| t <sub>ODC</sub>  | Output duty cycle             | Measured at differential signal, 622.08 MHz                                                                                                                                     | 45  | 50  | 55   | %          |

| t <sub>CCJ</sub>  | Cycle-to-cycle jitter         | pk, measured at differential signal,<br>156.25 MHz, over 10-k cycles. Input<br>frequency (24 MHz to 40 MHz) crystal. (all<br>differential outputs on)                           | _   | -   | 50   | ps         |

| t <sub>PJ</sub>   | Period jitter                 | pk-pk, measured at differential signal<br>156.25 MHz, over 10-k cycles. Input<br>frequency (24 MHz to 40 MHz) crystal. (all<br>differential outputs on)                         | _   | -   | 50   | ps         |

| t <sub>JRMS</sub> | RMS phase jitter              | f <sub>OUT</sub> = 156.25 MHz, 12-k to 20-MHz offset                                                                                                                            | _   | 0.7 | 1.0  | ps         |

| PNg10k            | Phase noise, offset10 kHz     | f <sub>OUT</sub> =156.25 MHz. Input reference<br>25-MHz crystal                                                                                                                 | -   | _   | -110 | dBc/<br>Hz |

| PNg100k           | Phase noise, offset = 100 kHz | f <sub>OUT</sub> =156.25 MHz. Input reference<br>25-MHz crystal                                                                                                                 | _   | _   | -119 | dBc/<br>Hz |

| PNg1M             | Phase noise, offset = 1 MHz   | f <sub>OUT</sub> = 156.25 MHz. Input reference<br>25-MHz crystal                                                                                                                | _   | _   | -131 | dBc/<br>Hz |

| PNg10M            | Phase noise, offset = 10 MHz  | f <sub>OUT</sub> = 156.25 MHz. Input reference<br>25-MHz crystal                                                                                                                | _   | _   | -147 | dBc/<br>Hz |

| PN-SPUR           | Spur                          | At frequency offsets equal to and greater than the update rate of the PLL                                                                                                       | _   | _   | -65  | dBc/<br>Hz |

| SSC Mode          |                               |                                                                                                                                                                                 |     |     |      | u.         |

| t <sub>CCJ</sub>  | Cycle-to-cycle jitter         | pk, measured at differential signal,<br>156.25 MHz, over 10-k cycles. Input<br>frequency (24 MHz to 40 MHz) crystal,<br>with a spread of 0.5% (all differential<br>outputs on). | _   | -   | 70   | ps         |

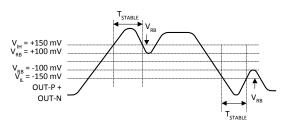

Table 17. AC Electrical Specification HSCL Output  $^{[2,\,3]}$

| Symbol                              | Description                            | Conditions                                                                         | Min   | Тур | Max    | Units |  |  |

|-------------------------------------|----------------------------------------|------------------------------------------------------------------------------------|-------|-----|--------|-------|--|--|

| Common AC Electrical Specifications |                                        |                                                                                    |       |     |        |       |  |  |

| $f_{OC}$                            | Output frequency                       | HCSL                                                                               | 96    | _   | 400    | MHz   |  |  |

| E <sub>R</sub>                      | Rising edge rate                       | Measurement taken from differential waveform, –150 mV to +150 mV                   | 0.6   | _   | 4      | V/ns  |  |  |

| E <sub>F</sub>                      | Falling edge rate                      | Measurement taken from differential waveform, –150 mV to +150 mV                   | 0.6   | _   | 4      | V/ns  |  |  |

| T <sub>STABLE</sub>                 | Time before V <sub>RB</sub> is allowed | Measurement taken from differential waveform, –150 mV to +150 mV                   | 500   | _   | _      | ps    |  |  |

| T <sub>PERIOD_AVG</sub>             | Average clock period accuracy, 100 MHz | Measurement taken from differential waveform, Spread Spectrum On, 0.5% down spread | -300  | -   | 2800   | ppm   |  |  |

| T <sub>PERIOD_ABS</sub>             | Absolute period                        | Measurement taken from differential waveform, Spread Spectrum On, 0.5% down spread | 9.874 | -   | 10.203 | ns    |  |  |

#### Notes

AC parameters for differential outputs are guaranteed for only differential outputs. LVCMOS is Off.

All output clocks 100MHz HCSL format. Jitter is from PCIE jitter filter combination that produces the highest jitter.

Table 17. AC Electrical Specification HSCL Output [2, 3] (continued)

| Symbol                  | Description                           | Conditions                                                                                                                                                  | Min  | Тур | Max | Units       |

|-------------------------|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|-------------|

| R-F <sub>MATCHING</sub> | Rise-fall matching                    | Measurement taken from single-ended waveform. Rising edge rate to falling edge rate matching 100 MHz                                                        | -20  | _   | +20 | %           |

| BUFFER Mode             | )                                     |                                                                                                                                                             |      |     |     |             |

| T <sub>DC</sub>         | Duty cycle                            | Measurement taken from differential waveform                                                                                                                | 45   | 50  | 55  | %           |

| t <sub>RMS_ADD</sub>    | Additive phase noise                  | Input slew rate 4 V/ns differential 400-mV amplitude.                                                                                                       | _    | _   | 0.4 | ps<br>(RMS) |

| ZDB Mode (RE            | F=IN1, 1 output pair fed back to I    | N2)                                                                                                                                                         |      |     |     |             |

| T <sub>DC</sub>         | Duty cycle                            | Measurement taken from differential waveform                                                                                                                | 45   | 50  | 55  | %           |

| T <sub>CCJITTER</sub>   | Cycle-to-cycle jitter                 | pk, measured at differential signal<br>100 MHz, over 10-k cycles. Input slew<br>rate 4 V/ns differential 400-mV amplitude<br>(all differential outputs on). | -    | _   | 50  | ps          |

| J <sub>RMS</sub>        | Random jitter_PCle 3.0 Common clocked | PCIe Gen3 filters. Input slew rate 4 V/ns differential 400-mV amplitude.                                                                                    | _    | 0.7 | 1.0 | ps<br>(RMS) |

| t <sub>PD</sub>         | Propagation delay                     | Early/Late option is OFF                                                                                                                                    | -200 | _   | 200 | ps          |