#### **DS3234**

#### **General Description**

The DS3234 is a low-cost, extremely accurate SPI bus real-time clock (RTC) with an integrated temperature-compensated crystal oscillator (TCXO) and crystal. The DS3234 incorporates a precision, temperature-compensated voltage reference and comparator circuit to monitor VCC. When VCC drops below the power-fail voltage (VPF), the device asserts the RST output and also disables read and write access to the part when VCC drops below both VPF and VBAT. The RST pin is monitored as a pushbutton input for generating a  $\mu P$  reset. The device switches to the backup supply input and maintains accurate timekeeping when main power to the device is interrupted. The integration of the crystal resonator enhances the long-term accuracy of the device as well as reduces the piece-part count in a manufacturing line. The DS3234 is available in commercial and industrial temperature ranges, and is offered in an industry-standard 300-mil, 20-pin SO package.

The DS3234 also integrates 256 bytes of battery-backed SRAM. In the event of main power loss, the contents of the memory are maintained by the power source connected to the  $V_{BAT}$  pin. The RTC maintains seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with  $\overline{AM}/PM$  indicator. Two programmable time-of-day alarms and a programmable square-wave output are provided. Address and data are transferred serially by an SPI bidirectional bus.

### **Applications**

Servers Utility Power Meters

Telematics GPS

Underwriters Laboratories Inc. is a registered certification mark of Underwriters Laboratories Inc.

# Extremely Accurate SPI Bus RTC with Integrated Crystal and SRAM

#### **Benefits and Features**

- Highly Accurate RTC with Integrated Crystal and SRAM Completely Manages All Timekeeping Functions

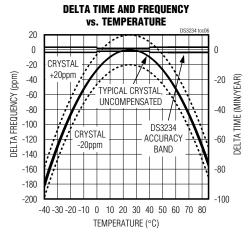

- Accuracy ±2ppm from 0°C to +40°C

- Accuracy ±3.5ppm from -40°C to +85°C

- Real-Time Clock Counts Seconds, Minutes, Hours, Day, Date, Month, and Year, with Leap Year Compensation Valid Up to 2099

- Digital Temp Sensor Output: ±3°C Accuracy

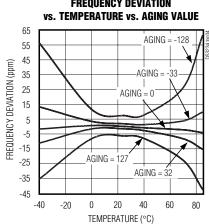

- Register for Aging Trim

- RST Input/Output

- Two Time-of-Day Alarms

- · Programmable Square-Wave Output

- Simple Serial Interface Connects to Most Microcontrollers

- · 4MHz SPI Bus Supports Modes 1 and 3

- Battery-Backup Input for Continuous Timekeeping

- Low Power Operation Extends Battery Backup Run Time

- Operating Temperature Ranges: Commercial: 0°C to +70°C, Industrial: -40°C to +85°C

- 300-Mil, 20-Pin SO Package

- Underwriters Laboratories® (UL) Recognized

### **Ordering Information**

| PART      | TEMP RANGE     | PIN-<br>PACKAGE | TOP<br>MARK |

|-----------|----------------|-----------------|-------------|

| DS3234S#  | 0°C to +70°C   | 20 SO           | DS3234S     |

| DS3234SN# | -40°C to +85°C | 20 SO           | DS3234SN    |

#Denotes an RoHS-compliant device that may include lead(Pb) that is exempt under the RoHS requirements. Lead finish is JESD97 Category e3, and is compatible with both lead-based and lead-free soldering processes. A "#" anywhere on the top mark denotes an RoHS-compliant device.

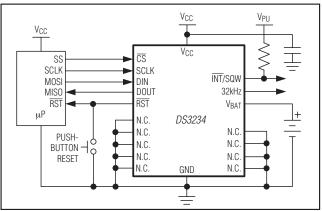

### **Typical Operating Circuit**

#### **Absolute Maximum Ratings**

Voltage Range on Any Pin Relative to Ground.....-0.3V to +6.0V Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) (Note 1) ...55°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ) (Note 1) ......24°C/W Operating Temperature Range (noncondensing) .....-40°C to  $+85^{\circ}$ C

| Junction Temperature                        | +125°C            |

|---------------------------------------------|-------------------|

| Storage Temperature Range                   | 40°C to +85°C     |

| Lead Temperature (soldering, 10s)           | +260°C            |

| Soldering Temperature (reflow, 2 times max) | +260°C            |

| (See the Handling, PC Board Layout, and     | Assembly section. |

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Recommended Operating Conditions**

$(T_A = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.})$  (Notes 2, 3)

| PARAMETER                    | SYMBOL           | CONDITIONS                     | MIN                      | TYP | MAX                       | UNITS |

|------------------------------|------------------|--------------------------------|--------------------------|-----|---------------------------|-------|

| Supply Voltage               | V <sub>CC</sub>  |                                | 2.0                      | 3.3 | 5.5                       | \/    |

| Supply Voltage               | V <sub>BAT</sub> |                                | 2.0                      | 3.0 | 3.8                       | V     |

| Logic 1 Input CS, SCLK, DIN  | V <sub>IH</sub>  |                                | 0.7 x<br>V <sub>CC</sub> |     | V <sub>CC</sub> + 0.3     | V     |

| Logic 0 Input CS, SCLK, DIN, | VIL              | 2.0V ≤ V <sub>CC</sub> ≤ 3.63V | -0.3                     |     | +0.2 x<br>V <sub>CC</sub> | V     |

|                              |                  | 3.63V < V <sub>CC</sub> ≤ 5.5V | -0.3                     |     | +0.7                      |       |

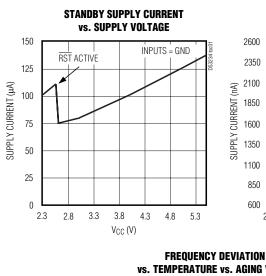

#### **Electrical Characteristics**

$(V_{CC} = 2.0 \text{V to } 5.5 \text{V}, V_{CC} = \text{active supply} \text{ (see Table 1)}, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted.)}$  (Typical values are at **V<sub>CC</sub> = 3.3V, V<sub>BAT</sub> = 3.0V**, and T<sub>A</sub> = +25 ^{\circ}\text{C}, unless otherwise noted. TCXO operation guaranteed from 2.3V to 5.5V on V<sub>CC</sub> and 2.3V to 3.8V on V<sub>BAT</sub>.) (Notes 2, 3)

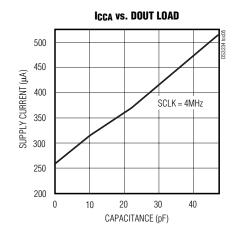

| PARAMETER                                                                                                 | SYMBOL      | CONDITIONS                  | MIN                    | TYP      | MAX   | UNITS |    |  |

|-----------------------------------------------------------------------------------------------------------|-------------|-----------------------------|------------------------|----------|-------|-------|----|--|

| Active Supply Current                                                                                     | look        | SCLK = 4MHz, BSY = 0        | $V_{CC} = 3.63V$       |          |       | 400   |    |  |

| Active Supply Current                                                                                     | ICCA        | (Notes 4, 5)                | $V_{CC} = 5.5V$        |          |       | 700   | μΑ |  |

| Standby Supply Current    CS = V <sub>IH</sub> , 32kHz output off, SQW output off                         |             | $V_{CC} = 3.63V$            |                        |          | 120   |       |    |  |

| Standby Supply Guilent                                                                                    | 1005        | (Note 5)                    | V <sub>CC</sub> = 5.5V |          |       | 160   | μΑ |  |

| Temperature Conversion Current                                                                            | Lacacan     | SPI bus inactive, 32kHz     | $V_{CC} = 3.63V$       |          |       | 500   | μΑ |  |

| Temperature Conversion Current                                                                            | ICCSCONV    | output off, SQW output off  | $V_{CC} = 5.5V$        |          |       | 600   |    |  |

| Power-Fail Voltage                                                                                        | VpF         |                             |                        | 2.45     | 2.575 | 2.70  | V  |  |

| V <sub>BAT</sub> Leakage Current                                                                          | IBATLKG     |                             |                        |          | 25    | 100   | nA |  |

| $(V_{CC} = 2.0V \text{ to } 5.5V, T_A = -40^{\circ}C \text{ to}$                                          | +85°C, unle | ss otherwise noted.) (Notes | 2 and 3)               |          |       |       |    |  |

| Logic 1 Output, 32kHz<br>I <sub>OH</sub> = -500µA<br>I <sub>OH</sub> = -250µA<br>I <sub>OH</sub> = -125µA | Vон         | V <sub>CC</sub> > 3.63V,    |                        | 0.85 x V | CC    |       | V  |  |

#### **Electrical Characteristics (continued)**

( $V_{CC}$  = 2.0V to 5.5V,  $V_{CC}$  = active supply (see Table 1),  $T_A$  = -40°C to +85°C, unless otherwise noted.) (Typical values are at **V<sub>CC</sub>** = **3.3V**, **V**<sub>BAT</sub> = **3.0V**, and  $T_A$  = +25°C, unless otherwise noted. TCXO operation guaranteed from 2.3V to 5.5V on  $V_{CC}$  and 2.3V to 3.8V on  $V_{BAT}$ .) (Notes 2, 3)

| PARAMETER                                              | SYMBOL              | CONDIT                                                   | CONDITIONS                         |                            | TYP      | MAX  | UNITS |  |

|--------------------------------------------------------|---------------------|----------------------------------------------------------|------------------------------------|----------------------------|----------|------|-------|--|

| Logic 0 Output, 32kHz                                  | VoL                 | I <sub>OL</sub> = 1mA                                    |                                    |                            |          | 0.4  | V     |  |

| Logic 1 Output, DOUT                                   | VoH                 | I <sub>OH</sub> = -1.0mA                                 |                                    | 0.85 x V                   | CC       |      | V     |  |

| Logic 0 Output, DOUT, INT/SQW                          | Vol                 | I <sub>OL</sub> = 3mA                                    |                                    |                            | 0.4      | V    |       |  |

| Logic 0 Output, RST                                    | V <sub>OL</sub>     | $I_{OL} = 1.0 \text{mA}$                                 |                                    |                            |          | 0.4  | V     |  |

| Output Leakage Current 32kHz, INT/SQW, DOUT            | ILO                 | Output high impedance                                    | Output high impedance              |                            |          |      | μΑ    |  |

| Input Leakage DIN, CS, SCLK                            | ILI                 |                                                          |                                    |                            |          |      | μΑ    |  |

| RST Pin I/O Leakage                                    | loL                 | RST high impedance (N                                    | RST high impedance (Note 6)        |                            |          |      | μΑ    |  |

| TCXO (V <sub>CC</sub> = 2.3V to 5.5V, V <sub>BAT</sub> | = 2.3V to 3.8       | V, T <sub>A</sub> = -40°C to +85°C, ι                    | ınless otherwise no                | ted.) (Note                | es 2 and | 3)   |       |  |

| Output Frequency                                       | fout                | $V_{CC} = 3.3V \text{ or } V_{BAT} = 3$                  | .3V                                |                            | 32.768   |      | kHz   |  |

| -                                                      | 1 AMOUT             |                                                          | 0°C to +40°C                       | -2                         |          | +2   |       |  |

| Frequency Stability vs. Temperature                    |                     | $V_{\text{CC}} = 3.3V \text{ or } V_{\text{BAT}} = 3.3V$ | -40°C to 0°C and<br>+40°C to +85°C | -3.5                       |          | +3.5 | ppm   |  |

| Frequency Stability vs. Voltage                        | Δf/V                |                                                          | -                                  |                            | 1        |      | ppm/V |  |

|                                                        |                     |                                                          | -40°C                              |                            | 0.7      |      |       |  |

| Trim Register Frequency                                | 4.(/I, O.D.         | 0                                                        | +25°C                              |                            | 0.1      |      |       |  |

| Sensitivity per LSB                                    | ∆f/LSB              | Specified at:                                            | +70°C                              |                            | 0.4      |      | ppm   |  |

|                                                        |                     |                                                          | +85°C                              |                            | 0.8      |      |       |  |

| Temperature Accuracy                                   | Temp                |                                                          |                                    | -3                         |          | +3   | °C    |  |

| Crystal Aging                                          | A f /f a            | After reflow, First year                                 |                                    | er reflow, First year ±1.0 |          |      | ppm   |  |

| Crystal Aging                                          | ∆f/f <sub>OUT</sub> | not production tested                                    | 0-10 years                         | ±5.0                       |          |      |       |  |

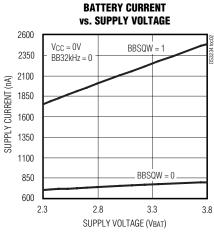

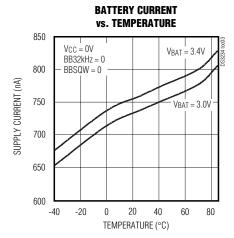

#### **Electrical Characteristics**

(VCC = 0V, VBAT = 2.0V to 3.8V,  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER SYMBOL CONDIT        |                    |                                           |                  | MIN | TYP | MAX | UNITS |

|--------------------------------|--------------------|-------------------------------------------|------------------|-----|-----|-----|-------|

| Timekeeping Battery Current    | ID 4 TT            | $\overline{\text{EOSC}} = 0$ , BBSQW = 0, | $V_{BAT} = 3.4V$ |     | 1.5 | 2.3 |       |

| (Note 5)                       | IBATT              | CRATE1 = CRATE0 = 0                       | $V_{BAT} = 3.8V$ |     | 1.5 | 2.5 | μΑ    |

| Temperature Conversion Current | I <sub>BATTC</sub> | $\overline{EOSC} = 0$ , BBSQW = 0         |                  |     |     | 400 | μΑ    |

| Data-Retention Current         | IBATTDR            | EOSC = 1                                  |                  |     |     | 100 | nA    |

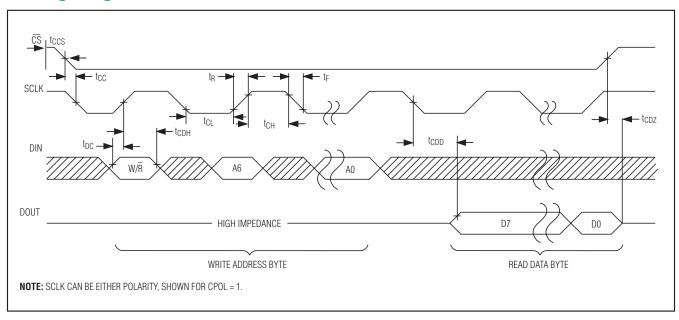

#### **Electrical Characteristics**

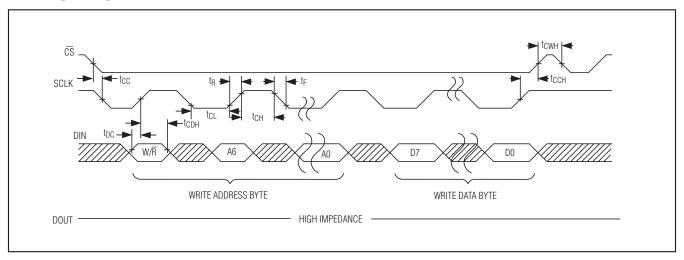

$(V_{CC} = 2.0V \text{ to } 5.5V, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.})$  (Note 2)

| PARAMETER                        | SYMBOL                          | CONDITIONS                    | MIN | TYP | MAX | UNITS  |  |

|----------------------------------|---------------------------------|-------------------------------|-----|-----|-----|--------|--|

| CCL // Clask Francisco           | f                               | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V |     |     | 4   | NAL I- |  |

| SCLK Clock Frequency             | fscl                            | 2.0V ≤ V <sub>CC</sub> < 2.7V |     |     | 2   | MHz    |  |

| Data to SCLK Setup               | tDC                             |                               | 30  |     |     | ns     |  |

| SCLK to Data Hold                | tCDH                            |                               | 30  |     |     | ns     |  |

| SCLK to CS Setup                 | tccs                            |                               | 30  |     |     | ns     |  |

| COLIV to Data Valid (Nata 7)     |                                 | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V |     |     | 80  |        |  |

| SCLK to Data Valid (Note 7)      | tCDD                            | $2.0V \le V_{CC} < 2.7V$      |     |     | 160 | ns     |  |

| COLIV Lour Times                 | <b>.</b>                        | $2.7V \le V_{CC} \le 5.5V$    | 110 |     |     |        |  |

| SCLK Low Time                    | tCL                             | 2.0V ≤ V <sub>CC</sub> < 2.7V | 220 |     |     | ns     |  |

| 0017717 1 7                      | tou                             | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V | 110 |     |     | no     |  |

| SCLK High Time                   | tСН                             | $2.0V \le V_{CC} < 2.7V$      | 220 |     |     | ns     |  |

| SCLK Rise and Fall               | t <sub>R</sub> , t <sub>F</sub> |                               |     |     | 200 | ns     |  |

| CS to SCLK Setup                 | tcc                             |                               | 400 |     |     | ns     |  |

| SCLK to CS Hold                  | 4                               | 2.7V ≤ V <sub>CC</sub> ≤ 5.5V | 100 |     |     | İ      |  |

| SCEN to CS Hold                  | tCCH                            | 2.0V ≤ V <sub>CC</sub> < 2.7V | 200 |     |     | ns     |  |

| CS Inactive Time                 | tcwh                            |                               | 400 |     |     | ns     |  |

| CS to Output High Impedance      | tCDZ                            | (Note 8)                      |     |     | 40  | ns     |  |

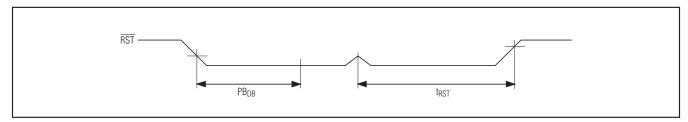

| Pushbutton Debounce              | PBDB                            |                               |     | 250 |     | ms     |  |

| Reset Active Time                | trst                            |                               |     | 250 |     | ms     |  |

| Oscillator Stop Flag (OSF) Delay | tosf                            | (Note 9)                      |     | 100 |     | ms     |  |

| Temperature Conversion Time      | tCONV                           |                               |     | 125 | 200 | ms     |  |

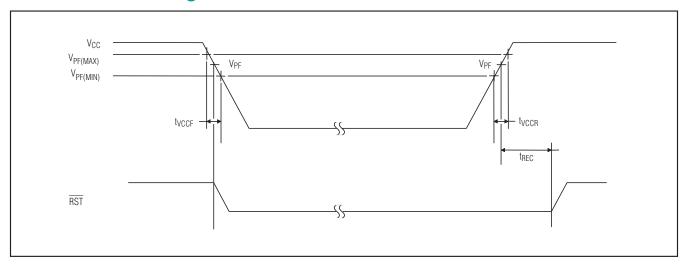

#### **Power-Switch Characteristics**

$5(T_A = -40^{\circ}C \text{ to } +85^{\circ}C)$

| PARAMETER                                                               | SYMBOL | CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------------------------------------------------------|--------|------------|-----|-----|-----|-------|

| V <sub>CC</sub> Fall Time; V <sub>PF(MAX)</sub> to V <sub>PF(MIN)</sub> | tvccf  |            | 300 |     |     | μs    |

| V <sub>CC</sub> Rise Time; V <sub>PF(MIN)</sub> to V <sub>PF(MAX)</sub> | tvccr  |            | 0   |     |     | μs    |

| Recovery at Power-Up                                                    | trec   | (Note 10)  |     | 125 | 300 | ms    |

## **Capacitance**

$(T_A = +25^{\circ}C)$

| PARAMETER                      | SYMBOL | CONDITIONS                       | MIN | TYP | MAX | UNITS |

|--------------------------------|--------|----------------------------------|-----|-----|-----|-------|

| Capacitance on All Input Pins  | CIN    | (Note 11)                        |     |     | 10  | рF    |

| Capacitance on All Output Pins | CIO    | Outputs high impedance (Note 11) |     | •   | 10  | рF    |

#### **Pushbutton Reset Timing**

### **Power-Switch Timing**

# WARNING: Negative undershoots below -0.3V while the part is in battery-backed mode may cause loss of data.

- Note 2: Limits at -40°C are guaranteed by design and not production tested.

- Note 3: All voltages are referenced to ground.

- Note 4: Measured at V<sub>IH</sub> = 0.8 x V<sub>CC</sub> or V<sub>IL</sub> = 0.2 x V<sub>CC</sub>, 10ns rise/fall time, DOUT = no load.

- Note 5: Current is the averaged input current, which includes the temperature conversion current. CRATE1 = CRATE0 = 0.

- **Note 6:** The  $\overline{RST}$  pin has an internal  $50k\Omega$  (nominal) pullup resistor to  $V_{CC}$ .

- Note 7: Measured at V<sub>OH</sub> = 0.8 x V<sub>CC</sub> or V<sub>OL</sub> = 0.2 x V<sub>CC</sub>. Measured from the 50% point of SCLK to the V<sub>OH</sub> minimum of DOUT.

- Note 8: With 50pF load.

- Note 9: The parameter t<sub>OSF</sub> is the period of time the oscillator must be stopped for the OSF flag to be set over the voltage range of 0V ≤ V<sub>CC</sub> ≤ V<sub>CC</sub>(MAX) and 2.3V ≤ V<sub>BAT</sub> ≤ V<sub>BAT</sub>(MAX).

- Note 10: This delay only applies if the oscillator is enabled and running. If the EOSC bit is 1, trec is bypassed and RST immediately goes high.

- Note 11: Guaranteed by design and not production tested.

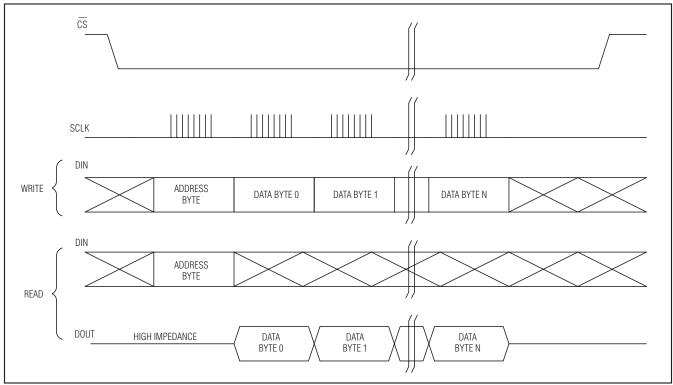

## **Timing Diagram—SPI Read Transfer**

## **Timing Diagram—SPI Write Transfer**

### **Typical Operating Characteristics**

$(V_{CC} = +3.3V, T_A = +25^{\circ}C, unless otherwise noted.)$

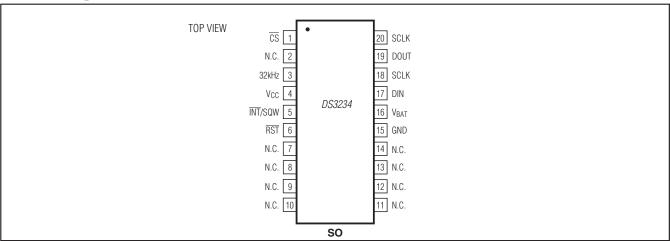

# **Pin Configuration**

# **Pin Description**

| PIN     | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | CS               | Active-Low Chip Select Input. Used to select or deselect the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2, 7–14 | N.C.             | No Connection. Not connected internally. Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 3       | 32kHz            | 32kHz Push-Pull Output. If disabled with either EN32kHz = 0 or BB32kHz = 0, the state of the 32kHz pin will be low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4       | Vcc              | DC Power Pin for Primary Power Supply. This pin should be decoupled using a 0.1µF to 1.0µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5       | ĪNT/SQW          | Active-Low Interrupt or Square-Wave Output. This open-drain pin requires an external pullup resistor. It can be left open if not used. This multifunction pin is determined by the state of the INTCN bit in the Control Register (0Eh). When INTCN is set to logic 0, this pin outputs a square wave and its frequency is determined by RS2 and RS1 bits. When INTCN is set to logic 1, then a match between the timekeeping registers and either of the alarm registers activates the INT/SQW pin (if the alarm is enabled). Because the INTCN bit is set to logic 1 when power is first applied, the pin defaults to an interrupt output with alarms disabled. The pullup voltage can be up to 5.5V, regardless of the voltage on V <sub>CC</sub> . If not used, this pin can be left unconnected. |

| 6       | RST              | Active-Low Reset. This pin is an open-drain input/output. It indicates the status of V <sub>CC</sub> relative to the V <sub>PF</sub> specification. As V <sub>CC</sub> falls below V <sub>PF</sub> , the RST pin is driven low. When V <sub>CC</sub> exceeds V <sub>PF</sub> , for t <sub>RST</sub> , the RST pin is driven high impedance. The active-low, open-drain output is combined with a debounced pushbutton input function. This pin can be activated by a pushbutton reset request. It has an internal 50k_ nominal value pullup resistor to V <sub>CC</sub> . No external pullup resistors should be connected. On first power-up, or if the crystal oscillator is disabled, t <sub>RST</sub> is bypassed and RST immediately goes high.                                                  |

| 15      | GND              | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 16      | V <sub>BAT</sub> | Backup Power-Supply Input. If V <sub>BAT</sub> is not used, connect to ground. Diodes placed in series between the V <sub>BAT</sub> pin and the battery can cause improper operation. UL recognized to ensure against reverse charging when used with a lithium battery. Go to <a href="https://www.maximintegrated.com/qa/info/ul">www.maximintegrated.com/qa/info/ul</a> .                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 17      | DIN              | SPI Data Input. Used to shift address and data into the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 18, 20  | SCLK             | SPI Clock Input. Used to control timing of data into and out of the device. Either clock polarity can be used. The clock polarity is determined by the device based on the state of SCLK when $\overline{\text{CS}}$ goes low. Pins 18 and 20 are electrically connected together internally.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 19      | DOUT             | SPI Data Output. Data is output on this pin when the device is in read mode; CMOS push-pull driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

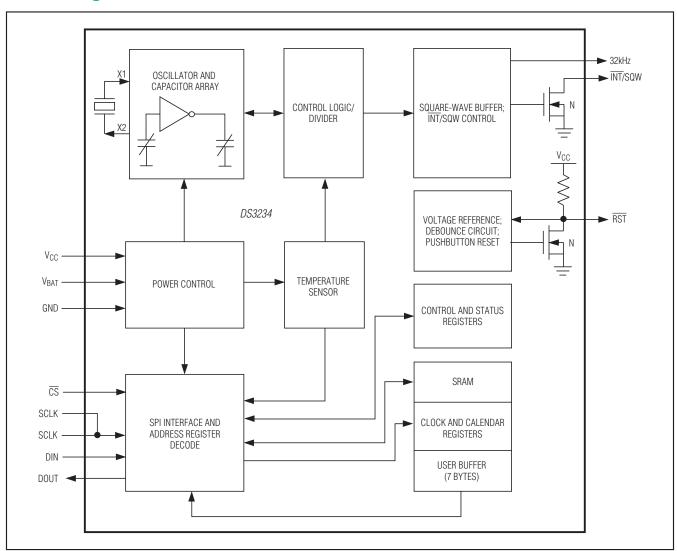

#### **Block Diagram**

## **Detailed Description**

The DS3234 is a TCXO and RTC with integrated crystal and 256 bytes of SRAM. An integrated sensor periodically samples the temperature and adjusts the oscillator load to compensate for crystal drift caused by temperature variations. The DS3234 provides user-selectable sample rates. This allows the user to select a temperature sensor sample rate that allows for various temperature rates of change, while minimizing current consumption by temperature sensor sampling. The user should select a sample rate based upon the

expected temperature rate of change, with faster sample rates for applications where the ambient temperature changes significantly over a short time. The TCXO provides a stable and accurate reference clock, and maintains the RTC to within ±2 minutes per year accuracy from -40°C to +85°C. The TCXO frequency output is available at the 32kHz pin. The RTC is a low-power clock/calendar with two programmable time-of-day alarms and a programmable square-wave output. The INT/SQW provides either an interrupt signal due to alarm conditions or a square-wave output. The clock/calendar provides seconds, minutes, hours, day,

date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with AM/PM indicator. Access to the internal registers is possible through an SPI bus interface.

A temperature-compensated voltage reference and comparator circuit monitors the level of  $V_{CC}$  to detect power failures and to automatically switch to the backup supply when necessary. When operating from the backup supply, access is inhibited to minimize supply current. Oscillator, time and date, and TCXO operations can continue while the backup supply powers the device. The  $\overline{\text{RST}}$  pin provides an external pushbutton function and acts as an indicator of a power-fail event.

#### **Operation**

The block diagram shows the main elements of the DS3234. The eight blocks can be grouped into four functional groups: TCXO, power control, pushbutton function, and RTC. Their operations are described separately in the following sections.

#### 32kHz TCXO

The temperature sensor, oscillator, and control logic form the TCXO. The controller reads the output of the on-chip temperature sensor and uses a lookup table to determine the capacitance required, adds the aging correction in the AGE register, and then sets the capacitance selection registers. New values, including changes to the AGE register, are loaded only when a change in the temperature value occurs. The temperature is read on initial application of VCC and once every 64 seconds (default, see the description for CRATE1 and CRATE0 in the *Control/Status Register* section) afterwards.

#### **Power Control**

The power control function is provided by a temperature-compensated voltage reference and a comparator circuit that monitors the V<sub>CC</sub> level. The device is fully accessible and data can be written and read when V<sub>CC</sub> is greater than V<sub>PF</sub>. However, when V<sub>CC</sub> falls below both V<sub>PF</sub> and V<sub>BAT</sub>, the internal clock registers are blocked from any access. If V<sub>PF</sub> is less than V<sub>BAT</sub>, the device power is switched from V<sub>CC</sub> to V<sub>BAT</sub> when V<sub>CC</sub> drops below V<sub>PF</sub>. If V<sub>PF</sub> is greater than V<sub>BAT</sub>, the device power is switched from V<sub>CC</sub> to V<sub>BAT</sub> when V<sub>CC</sub> drops below V<sub>BAT</sub>. After V<sub>CC</sub> returns above both V<sub>PF</sub> and V<sub>BAT</sub>, read and write access is allowed after RST goes high (Table 1).

To preserve the battery, the first time  $V_{BAT}$  is applied to the device, the oscillator does not start up until  $V_{CC}$

**Table 1. Power Control**

| SUPPLY CONDITION      | READ/WRITE<br>ACCESS | ACTIVE<br>SUPPLY | RST      |

|-----------------------|----------------------|------------------|----------|

| VCC < VPF, VCC < VBAT | No                   | V <sub>BAT</sub> | Active   |

| VCC < VPF, VCC > VBAT | Yes                  | Vcc              | Active   |

| VCC > VPF, VCC < VBAT | Yes                  | Vcc              | Inactive |

| VCC > VPF, VCC > VBAT | Yes                  | Vcc              | Inactive |

crosses VpF. After the first time  $V_{CC}$  is ramped up, the oscillator starts up and the  $V_{BAT}$  source powers the oscillator during power-down and keeps the oscillator running. When the DS3234 switches to  $V_{BAT}$ , the oscillator may be disabled by setting the  $\overline{EOSC}$  bit.

#### **VBAT Operation**

There are several modes of operation that affect the amount of VBAT current that is drawn. When the part is powered by VBAT, timekeeping current (IBATT), which includes the averaged temperature conversion current, IBATTC, is drawn (refer to Application Note 3644: *Power Considerations for Accurate Real-Time Clocks* for details). Temperature conversion current, IBATTC, is specified since the system must be able to support the periodic higher current pulse and still maintain a valid voltage level. Data retention current, IBATTDR, is the current drawn by the part when the oscillator is stopped ( $\overline{EOSC} = 1$ ). This mode can be used to minimize battery requirements for times when maintaining time and date information is not necessary, e.g., while the end system is waiting to be shipped to a customer.

#### **Pushbutton Reset Function**

The DS3234 provides for a pushbutton switch to be connected to the  $\overline{RST}$  output pin. When the DS3234 is not in a reset cycle, it continuously monitors the  $\overline{RST}$  signal for a low going edge. If an edge transition is detected, the DS3234 debounces the switch by pulling the  $\overline{RST}$  low. After the internal timer has expired (PBDB), the DS3234 continues to monitor the  $\overline{RST}$  line. If the line is still low, the DS3234 continuously monitors the line looking for a rising edge. Upon detecting release, the DS3234 forces the  $\overline{RST}$  pin low and holds it low for transfer in the line is still low for transfer in the line is still low for transfer in the line is still low for transfer in the line looking for a rising edge.

The same pin,  $\overline{RST}$ , is used to indicate a power-fail condition. When V<sub>CC</sub> is lower than V<sub>PF</sub>, an internal power-fail signal is generated, which forces the  $\overline{RST}$  pin low. When V<sub>CC</sub> returns to a level above V<sub>PF</sub>, the  $\overline{RST}$  pin is held low for t<sub>REC</sub> to allow the power supply to stabilize. If the  $\overline{EOSC}$  bit is set to logic 1 (to disable the oscillator in battery-backup mode), t<sub>REC</sub> is bypassed and  $\overline{RST}$  immediately goes high.

#### **DS3234**

# Extremely Accurate SPI Bus RTC with Integrated Crystal and SRAM

When RST is active due to a power-fail condition (see Table 1), SPI operations are inhibited while the TCXO and RTC continue to operate. When RST is active due to a pushbutton event, it does not affect the operation of the TCXO, SPI interface, or RTC functions.

#### **Real-Time Clock**

With the clock source from the TCXO, the RTC provides seconds, minutes, hours, day, date, month, and year information. The date at the end of the month is automatically adjusted for months with fewer than 31 days, including corrections for leap year. The clock operates in either the 24-hour or 12-hour format with an AM/PM indicator.

The clock provides two programmable time-of-day alarms and a programmable square-wave output. The INT/SQW pin either generates an interrupt due to alarm condition or outputs a square-wave signal and the selection is controlled by the bit INTCN.

#### SRAN

The DS3234 provides 256 bytes of general-purpose battery-backed read/write memory. The SRAM can be written or read whenever VCC is above either VPF or VBAT.

#### **Address Map**

Figure 1 shows the address map for the DS3234 timekeeping registers. During a multibyte access, when the address pointer reaches the end of the register space (13h read, 93h write), it wraps around to the beginning (00h read, 80h write). The DS3234 does not respond to a read or write to any reserved address, and the internal address pointer does not increment. Address pointer operation when accessing the 256-byte SRAM data is covered in the description of the SRAM address and data registers. On the falling edge of CS, or during a multibyte access when the address pointer increments to location 00h, the current time is transferred to a second set of registers. The time information is read from these secondary registers, while the internal clock registers continue to increment normally. If the time and date registers are read using a multibyte read, this eliminates the need to reread the registers in case the main registers update during a read.

#### **SPI Interface**

The DS3234 operates as a slave device on the SPI serial bus. Access is obtained by selecting the part by the  $\overline{\text{CS}}$  pin and clocking data into/out of the part using the SCLK and DIN/DOUT pins. Multiple byte transfers are supported within one  $\overline{\text{CS}}$  low period. The SPI on the DS3234 interface is accessible whenever V<sub>CC</sub> is above either V<sub>BAT</sub> or V<sub>PF</sub>.

#### **Clock and Calendar**

The time and calendar information is obtained by reading the appropriate register bytes. Figure 1 illustrates the RTC registers. The time and calendar data are set or initialized by writing the appropriate register bytes. The contents of the time and calendar registers are in binary-coded decimal (BCD) format. The DS3234 can be run in either 12-hour or 24-hour mode. Bit 6 of the hours register is defined as the 12- or 24-hour mode select bit. When high, 12-hour mode is selected. In 12-hour mode, bit 5 is the  $\overline{\text{AM}}/\text{PM}$  bit with logic-high being PM. In 24-hour mode, bit 5 is the 20-hour bit (20–23 hours). The century bit (bit 7 of the month register) is toggled when the years register overflows from 99 to 00.

The day-of-week register increments at midnight. Values that correspond to the day of week are user-defined but must be sequential (i.e., if 1 equals Sunday, then 2 equals Monday, and so on). Illogical time and date entries result in undefined operation.

When reading or writing the time and date registers, secondary (user) buffers are used to prevent errors when the internal registers update. When reading the time and date registers, the user buffers are synchronized to the internal registers on the falling edge of  $\overline{\text{CS}}$  or and when the register pointer rolls over to zero. The time information is read from these secondary registers, while the clock continues to run. This eliminates the need to reread the registers in case the main registers update during a read.

The countdown chain is reset whenever the seconds register is written. Write transfers occur when the last bit of a byte is clocked in. Once the countdown chain is reset, to avoid rollover issues the remaining time and date registers must be written within 1 second. The 1Hz square-wave output, if enabled, transitions high 500ms after the seconds data transfer.

Figure 1. Address Map for DS3234 Timekeeping Registers and SRAM

|         | RESS<br>/WRITE | MSB<br>BIT 7 | BIT 6   | BIT 5          | BIT 4     | BIT 3       | BIT 2       | E                           | BIT 1 | LSB<br>BIT 0           | FUNCTION                    | RANGE                 |

|---------|----------------|--------------|---------|----------------|-----------|-------------|-------------|-----------------------------|-------|------------------------|-----------------------------|-----------------------|

| 00h     | 80h            | 0            |         | 10 Seconds     |           |             | 9           | Seconds                     |       |                        | Seconds                     | 00–59                 |

| 01h     | 81h            | 0            |         | 10 Minutes     |           |             |             | Minutes                     |       |                        | Minutes                     | 00–59                 |

| 02h     | 82h            | 0            | 12/24   | AM/PM<br>20 hr | 10 hr     | Hour        |             |                             | Hours | 1-12 + AM /PM<br>00-23 |                             |                       |

| 03h     | 83h            | 0            | 0       | 0              | 0         | 0 Day       |             |                             | Day   | 1-7                    |                             |                       |

| 04h     | 84h            | 0            | 0       | 10 [           | Date      | Date        |             |                             |       | Date                   | 01-31                       |                       |

| 05h     | 85h            | Century      | 0       | 0              | 10 Mo     |             |             | Month                       |       |                        | Month/<br>Century           | 01-12 +<br>Century    |

| 06h     | 86h            |              | 10 `    | Year           |           |             |             | Year                        |       |                        | Year                        | 00-99                 |

| 07h     | 87h            | A1M1         |         | 10 Seconds     |           |             | 5           | Seconds                     |       |                        | Alarm 1<br>Seconds          | 00-59                 |

| 08h     | 88h            | A1M2         |         | 10 Minutes     |           |             | ı           | Minutes                     |       |                        | Alarm 1<br>Minutes          | 00-59                 |

| 09h     | 89h            | A1M3         | 12/24   | AM/PM<br>20 hr | 10 hr     |             |             | Hour                        |       |                        | Alarm 1 Hours               | 1-12 +AM /PM<br>00-23 |

| 0Ah     | 8Ah            | A1M4         | DY/DT   |                | 0<br>Date |             | Day<br>Date |                             |       |                        | Alarm 1 Day<br>Alarm 1 Date | 1-7<br>01-31          |

| 0Bh     | 8Bh            | A2M2         |         | 10 Minutes     |           |             | 1           | Minutes                     |       |                        | Alarm 2<br>Minutes          | 00-59                 |

| 0Ch     | 8Ch            | A2M3         | 12/24   | AM/PM<br>20 hr | 10 hr     |             |             | Hour                        |       |                        | Alarm 2 Hours               | 1-12 +AM /PM<br>00-23 |

| 0Dh     | 8Dh            | A2M4         | DY/DT   |                | 0<br>Date |             |             | Day<br>Date                 |       |                        | Alarm 2 Day<br>Alarm 2 Date | 1-7<br>01-31          |

| 0Eh     | 8Eh            | EOSC         | BBSQW   | CONV           | RS2       | RS1         | INTCN       | A2IE                        |       | A1IE                   | Control                     | _                     |

| 0Fh     | 8Fh            | OSF          | BB32kHz | CRATE1         | CRATE0    | EN32kHz     | BSY         | A2F                         |       | A1F                    | Control/<br>Status          | _                     |

| 10h     | 90h            | SIGN         | DATA    | DATA           | DATA      | DATA        | DATA        | DATA                        |       | DATA                   | Crystal Aging<br>Offset     | _                     |

| 11h     | 91h            | SIGN         | DATA    | DATA           | DATA      | DATA        | DATA        | DATA                        |       | DATA                   | Temp MSB                    | Read Only             |

| 12h     | 92h            | DATA         | DATA    | 0              | 0         | 0           | 0           | 0                           |       | 0                      | Temp LSB                    | Read Only             |

| 13h     | 93h            | 0            | 0       | 0              | 0         | 0 0 0 BB_TD |             | Disable Temp<br>Conversions | _     |                        |                             |                       |

| 14h–17h | 94h–97h        | _            | _       | _              | _         | _           | -           | _                           |       | _                      | Reserved                    | _                     |

| 18h     | 98h            | A7           | A6      | A5             | A4        | АЗ          | A2          | A1                          |       | A0                     | SRAM<br>Address             | _                     |

| 19h     | 99h            | D7           | D6      | D5             | D4        | D3          | D2          | D1                          |       | D0                     | SRAM Data                   | _                     |

**Note:** Unless otherwise specified, the registers' state is not defined when power is first applied. Bits defined as 0 cannot be written to 1 and will always read 0.

#### **Alarms**

The DS3234 contains two time-of-day/date alarms. Alarm 1 can be set by writing to registers 07h to 0Ah. Alarm 2 can be set by writing to registers 0Bh to 0Dh. The alarms can be programmed (by the alarm enable and INTCN bits of the control register) to activate the  $\overline{\rm INT}/\rm SQW$  output on an alarm match condition. Bit 7 of each of the time-of-day/date alarm registers are mask bits (Table 2). When all the mask bits for each alarm are logic 0, an alarm only occurs when the values in the time-keeping registers match the corresponding values stored in the time-of-day/date alarm registers. The alarms can also be programmed to repeat every second, minute, hour, day, or date. Table 2 shows the possible settings. Configurations not listed in the table will result in illogical operations.

The DY/DT bits (bit 6 of the alarm day/date registers) control whether the alarm value stored in bits 0 to 5 of that register reflects the day of the week or the date of the month. If DY/DT is written to logic 0, the alarm will be the result of a match with date of the month. If DY/DT is written to logic 1, the alarm will be the result of a match with day of the week.

When the RTC register values match alarm register settings, the corresponding Alarm Flag 'A1F' or 'A2F' bit is set to logic 1. If the corresponding Alarm Interrupt Enable 'A1IE' or 'A2IE' is also set to logic 1 and the INTCN bit is set to logic 1, the alarm condition activates the INT/SQW signal. The match is tested on the onceper-second update of the time and date registers.

Table 2. Alarm Mask Bits

| DV/DT | DY/DT ALARM 1 |               | R MASK BITS | (BIT 7) | ALARM RATE                                         |  |

|-------|---------------|---------------|-------------|---------|----------------------------------------------------|--|

| וטוזט | A1M4          | A1M3          | A1M2        | A1M1    | ALARW RATE                                         |  |

| Χ     | 1             | 1             | 1           | 1       | Alarm once per second                              |  |

| Χ     | 1             | 1             | 1           | 0       | Alarm when seconds match                           |  |

| Χ     | 1             | 1             | 0           | 0       | Alarm when minutes and seconds match               |  |

| Χ     | 1             | 0             | 0           | 0       | Alarm when hours, minutes, and seconds match       |  |

| 0     | 0             | 0             | 0           | 0       | Alarm when date, hours, minutes, and seconds match |  |

| 1     | 0             | 0             | 0           | 0       | Alarm when day, hours, minutes, and seconds match  |  |

|       |               |               |             |         |                                                    |  |

| DY/DT | ALARI         | VI 2 REGISTEI | R MASK BITS | (BIT 7) | ALADM DATE                                         |  |

| וט/זע | A2M4          | A2            | M3          | A2M2    | ALARM RATE                                         |  |

| Χ     | 1             |               | 1           | 1       | Alarm once per minute (00 seconds of every minute) |  |

| Χ     | 1             |               | 1           | 0       | Alarm when minutes match                           |  |

| Х     |               |               |             |         | , tiairii Wileir Illinatee Illateir                |  |

| Χ     | 1             | (             | )           | 0       | Alarm when hours and minutes match                 |  |

| 0     | 1 0           |               | )           | 0       |                                                    |  |

### Control Register (0Eh/8Eh)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | EOSC  | BBSQW | CONV  | RS2   | RS1   | INTCN | A2IE  | A1IE  |

| POR*: | 0     | 0     | 0     | 1     | 1     | 1     | 0     | 0     |

<sup>\*</sup>POR is defined as the first application of power to the device, either V<sub>BAT</sub> or V<sub>CC</sub>.

#### **Special-Purpose Registers**

The DS3234 has two additional registers (control and control/status) that control the real-time clock, alarms, and square-wave output.

#### Control Register (0Eh/8Eh)

Bit 7: Enable Oscillator (EOSC). When set to logic 0, the oscillator is started. When set to logic 1, the oscillator is stopped when the DS3234 switches to battery power. This bit is clear (logic 0) when power is first applied. When the DS3234 is powered by V<sub>CC</sub>, the oscillator is always on regardless of the status of the EOSC bit. When EOSC is disabled, all register data is static

**Bit 6: Battery-Backed Square-Wave Enable (BBSQW).** When set to logic 1 with INTCN = 0 and  $V_{CC}$  < VPF, this bit enables the square wave. When BBSQW is logic 0, the  $\overline{INT}/SQW$  pin goes high impedance when  $V_{CC} < V_{PF}$ . This bit is disabled (logic 0) when power is first applied.

Bit 5: Convert Temperature (CONV). Setting this bit to 1 forces the temperature sensor to convert the temperature into digital code and execute the TCXO algorithm to update the capacitance array to the oscillator. This can only happen when a conversion is not already in progress. The user should check the status bit BSY before forcing the controller to start a new TCXO execution. A user-initiated temperature conversion does not affect the internal 64-second (default interval) update cycle. This bit is disabled (logic 0) when power is first applied.

A user-initiated temperature conversion does not affect the BSY bit for approximately 2ms. The CONV bit remains at a 1 from the time it is written until the conversion is finished, at which time both CONV and BSY go to 0. The CONV bit should be used when monitoring the status of a user-initiated conversion. **Bits 4 and 3: Rate Select (RS2 and RS1).** These bits control the frequency of the square-wave output when the square wave has been enabled. The following table shows the square-wave frequencies that can be selected with the RS bits. These bits are both set to logic 1 (8.192kHz) when power is first applied.

#### **SQUARE-WAVE OUTPUT FREQUENCY**

| RS2 | RS1 | SQUARE-WAVE OUTPUT<br>FREQUENCY |

|-----|-----|---------------------------------|

| 0   | 0   | 1Hz                             |

| 0   | 1   | 1.024kHz                        |

| 1   | 0   | 4.096kHz                        |

| 1   | 1   | 8.192kHz                        |

Bit 2: Interrupt Control (INTCN). This bit controls the INT/SQW signal. When the INTCN bit is set to logic 0, a square wave is output on the INT/SQW pin. When the INTCN bit is set to logic 1, a match between the time-keeping registers and either of the alarm registers activates the INT/SQW (if the alarm is also enabled). The corresponding alarm flag is always set regardless of the state of the INTCN bit. The INTCN bit is set to logic 1 when power is first applied.

Bit 1: Alarm 2 Interrupt Enable (A2IE). When set to logic 1, this bit permits the alarm 2 flag (A2F) bit in the status register to assert  $\overline{\text{INT}}/\text{SQW}$  (when INTCN = 1). When the A2IE bit is set to logic 0 or INTCN is set to logic 0, the A2F bit does not initiate an interrupt signal. The A2IE bit is disabled (logic 0) when power is first applied.

Bit 0: Alarm 1 Interrupt Enable (A1IE). When set to logic 1, this bit permits the alarm 1 flag (A1F) bit in the status register to assert  $\overline{\text{INT}}/\text{SQW}$  (when INTCN = 1). When the A1IE bit is set to logic 0 or INTCN is set to logic 0, the A1F bit does not initiate the  $\overline{\text{INT}}/\text{SQW}$  signal. The A1IE bit is disabled (logic 0) when power is first applied.

### Control/Status Register (0Fh/8Fh)

|       | BIT 7 | BIT 6   | BIT 5  | BIT 4  | BIT 3   | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|---------|--------|--------|---------|-------|-------|-------|

| NAME: | OSF   | BB32kHz | CRATE1 | CRATE0 | EN32kHz | BSY   | A2F   | A1F   |

| POR*: | 1     | 1       | 0      | 0      | 1       | 0     | 0     | 0     |

<sup>\*</sup>POR is defined as the first application of power to the device, either V<sub>BAT</sub> or V<sub>CC</sub>.

#### Control/Status Register (0Fh/8Fh)

Bit 7: Oscillator Stop Flag (OSF). A logic 1 in this bit indicates that the oscillator either is stopped or was stopped for some period and may be used to judge the validity of the timekeeping data. This bit is set to logic 1 any time that the oscillator stops. The following are examples of conditions that can cause the OSF bit to be set:

- 1) The first time power is applied.

- 2) The voltages present on both V<sub>CC</sub> and V<sub>BAT</sub> are insufficient to support oscillation.

- 3) The EOSC bit is turned off in battery-backed mode.

- 4) External influences on the crystal (i.e., noise, leakage, etc.).

This bit remains at logic 1 until written to logic 0.

**Bit 6: Battery-Backed 32kHz Output (BB32kHz).** This bit enables the 32kHz output when powered from V<sub>BAT</sub> (provided EN32kHz is enabled). If BB32kHz = 0, the 32kHz output is low when the part is powered by V<sub>BAT</sub>. This bit is enabled (logic 1) when power is first applied.

Bits 5 and 4: Conversion Rate (CRATE1 and CRATE0). These two bits control the sample rate of the TCXO. The sample rate determines how often the temperature sensor makes a conversion and applies compensation to the oscillator. Decreasing the sample rate decreases the overall power consumption by decreasing the frequency at which the temperature sensor operates. However, significant temperature changes that occur between samples may not be completely compensated for, which reduce overall accuracy. These bits are set to logic 0 when power is first applied.

| CRATE1 | CRATE0 | SAMPLE RATE<br>(seconds) |

|--------|--------|--------------------------|

| 0      | 0      | 64                       |

| 0      | 1      | 128                      |

| 1      | 0      | 256                      |

| 1      | 1      | 512                      |

**Bit 3: Enable 32kHz Output (EN32kHz).** This bit indicates the status of the 32kHz pin. When set to logic 1, the 32kHz pin is enabled and outputs a 32.768kHz square-wave signal. When set to logic 0, the 32kHz pin is low. The initial power-up state of this bit is logic 1, and a 32.768kHz square-wave signal appears at the 32kHz pin after a power source is applied to the DS3234. This bit is enabled (logic 1) when power is first applied.

**Bit 2: Busy (BSY).** This bit indicates the device is busy executing TCXO functions. It goes to logic 1 when the conversion signal to the temperature sensor is asserted and then is cleared when the conversion is complete.

**Bit 1: Alarm 2 Flag (A2F).** A logic 1 in the alarm 2 flag bit indicates that the time matched the alarm 2 registers. If the A2IE bit and INTCN bit are set to logic 1, the INT/SQW pin is driven low while A2F is active. A2F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

**Bit 0: Alarm 1 Flag (A1F).** A logic 1 in the alarm 1 flag bit indicates that the time matched the alarm 1 registers. If the A1IE bit and the INTCN bit are set to logic 1, the INT/SQW pin is driven low while A1F is active. A1F is cleared when written to logic 0. This bit can only be written to logic 0. Attempting to write to logic 1 leaves the value unchanged.

### Aging Offset (10h/90h)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | SIGN  | DATA  |

| POR*: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### **Temperature Register (MSB) (11h)**

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | SIGN  | DATA  |

| POR*: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

#### **Temperature Register (LSB) (12h)**

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | DATA  | DATA  | 0     | 0     | 0     | 0     | 0     | 0     |

| POR*: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

<sup>\*</sup>POR is defined as the first application of power to the device, either V<sub>BAT</sub> or V<sub>CC</sub>.

### Aging Offset Register (10h/90h)

The aging offset register takes a user-provided value to add to or subtract from the oscillator capacitor array. The data is encoded in two's complement, with bit 7 representing the SIGN bit. One LSB represents the smallest capacitor to be switched in or out of the capacitance array at the crystal pins. The aging offset register capacitance value is added or subtracted from the capacitance value that the device calculates for each temperature compensation. The offset register is added to the capacitance array during a normal temperature conversion, if the temperature changes from the previous conversion, or during a manual user conversion (setting the CONV bit). To see the effects of the aging register on the 32kHz output frequency immediately, a manual conversion should be performed after each aging offset register change.

Positive aging values add capacitance to the array, slowing the oscillator frequency. Negative values remove capacitance from the array, increasing the oscillator frequency.

The change in ppm per LSB is different at different temperatures. The frequency vs. temperature curve is shifted by the values used in this register. At +25°C, one LSB typically provides about 0.1ppm change in fre-

quency. These bits are all set to logic 0 when power is first applied.

Use of the aging register is not needed to achieve the accuracy as defined in the EC tables, but could be used to help compensate for aging at a given temperature. See the *Typical Operating Characteristics* section for a graph showing the effect of the register on accuracy over temperature.

## **Temperature Registers (11h–12h)**

Temperature is represented as a 10-bit code with a resolution of 0.25°C and is accessible at location 11h and 12h. The temperature is encoded in two's complement format, with bit 7 in the MSB representing the SIGN bit. The upper 8 bits, the integer portion, are at location 11h and the lower 2 bits, the fractional portion, are in the upper nibble at location 12h. Example: 00011001 01b = +25.25°C. Upon power reset, the registers are set to a default temperature of 0°C and the controller starts a temperature conversion.

The temperature is read on initial application of VCC and once every 64 seconds afterwards. The temperature registers are updated after each user-initiated conversion and on every 64-second conversion. The temperature registers are read-only.

#### **Temperature Control (13h/93h)**

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | BB_TD |

| POR*: | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

<sup>\*</sup>POR is defined as the first application of power to the device, either VBAT or VCC.

### SRAM Address (18h/98h)

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | A7    | A6    | A5    | A4    | A2    | A1    | A1    | A0    |

#### **SRAM Data (19h/99h)**

|       | BIT 7 | BIT 6 | BIT 5 | BIT 4 | BIT 3 | BIT 2 | BIT 1 | BIT 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| NAME: | D7    | D6    | D5    | D4    | D2    | D1    | D1    | D0    |

Note: These registers do not default to any specific value.

# Temperature Control Register (13h/93h)

**Bit 0: Battery-Backed Temperature Conversion Disable (BB\_TD).** The battery-backed tempconv disable bit prevents automatic temperature conversions when the device is powered by the V<sub>BAT</sub> supply. This reduces the battery current at the expense of frequency accuracy.

### **SRAM Address Register (18h/98h)**

The SRAM address register provides the 8-bit address of the 256-byte memory array. The desired memory address should be written to this register before the data register is accessed. The contents of this register are incremented automatically if the data register is accessed more than once during a single transfer. When the contents of the address register reach 0FFh, the next access causes the register to roll over to 00h.

## SRAM Data Register (19h/99h)

The SRAM data register provides the data to be written to or the data read from the 256-byte memory array. During a read cycle, the data in this register is that found in the memory location in the SRAM address register (18h/98h). During a write cycle, the data in this register is placed in the memory location in the SRAM address register (18h/98h). When the SRAM data register is read or written, the internal register pointer remains at 19h/99h and the SRAM address register increments after each byte that is read or written, allowing multibyte transfers.

#### **SPI Serial Data Bus**

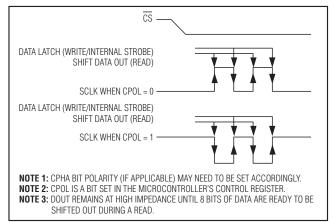

The DS3234 provides a 4-wire SPI serial data bus to communicate in systems with an SPI host controller. The DS3234 supports both single byte and multiple byte data transfers for maximum flexibility. The DIN and DOUT pins are the serial data input and output pins, respectively. The  $\overline{\text{CS}}$  input is used to initiate and terminate a data transfer. The SCLK pin is used to synchronize data movement between the master (microcontroller) and the slave devices (see Table 3). The shift clock (SCLK), which is generated by the microcontroller, is active only during address and data transfer to any device on the SPI bus. Input data (DIN) is latched on the internal strobe edge and output data (DOUT) is shifted out on the shift edge (Figure 2). There is one clock for each bit transferred. Address and data bits are transferred in groups of eight.

Figure 2. Serial Clock as a Function of Microcontroller Clock-Polarity Bit

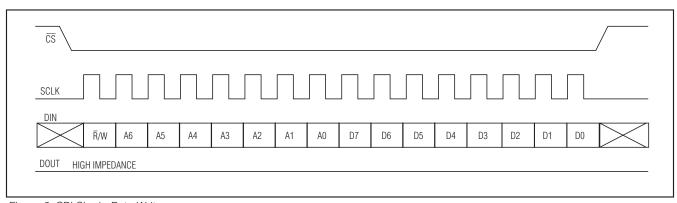

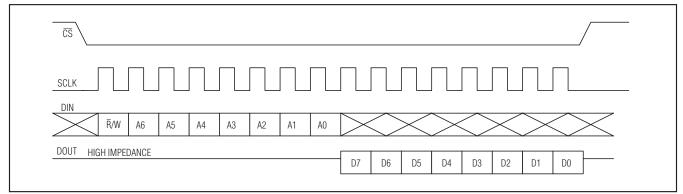

Address and data bytes are shifted MSB first into the serial data input (DIN) and out of the serial data output (DOUT). Any transfer requires the address of the byte to specify a write or read, followed by one or more bytes of data. Data is transferred out of the DOUT pin for a read operation and into the DIN for a write operation (Figures 3 and 4).

The address byte is always the first byte entered after  $\overline{\text{CS}}$  is driven low. The most significant bit of this byte determines if a read or write takes place. If the MSB is 0, one or more read cycles occur. If the MSB is 1, one or more write cycles occur.

#### **Table 3. SPI Pin Function**

| MODE                  | cs | SCLK                   | DIN                           | DOUT                  |  |

|-----------------------|----|------------------------|-------------------------------|-----------------------|--|

| Disable               | Н  | Input Disabled         | Input Disabled Input Disabled |                       |  |

| Muito                 | 1  | *CPOL = 1, SCLK Rising | Data Bit Latch                | High Impedance        |  |

| Write                 | L  | CPOL = 0, SCLK Falling | Dala Dil Lalon                |                       |  |

| Dood                  | 1  | CPOL = 1, SCLK Falling | V                             | Next Data Bit Shift** |  |

| Read                  | L  | CPOL = 0, SCLK Rising  | <b>^</b>                      |                       |  |

| Read Invalid Location | L  | Don't Care             | Don't Care                    | High Impedance        |  |

<sup>\*</sup>CPOL is the clock-polarity bit set in the control register of the host microprocessor.

<sup>\*\*</sup>DOUT remains at high impedance until 8 bits of data are ready to be shifted out during a read.

Figure 3. SPI Single-Byte Write

Figure 4. SPI Single-Byte Read

Figure 5. SPI Multiple-Byte Burst Transfer

Data transfers can occur one byte at a time or in multiple-byte burst mode. After CS is driven low, an address is written to the DS3234. After the address, one or more data bytes can be written or read. For a single-byte transfer, one byte is read or written and then CS is driven high. For a multiple-byte transfer, however, multiple bytes can be read or written after the address has been written (Figure 5). Each read or write cycle causes the RTC register address to automatically increment, which continues until the device is disabled. The address wraps to 00h after incrementing to 13h (during a read) and wraps to 80h after incrementing to 93h (during a write). An updated copy of the time is loaded into the user buffers upon the falling edge of  $\overline{\text{CS}}$  and each time the address pointer increments from 13h to 00h. Because the internal and user copies of the time are only synchronized on these two events, an alarm condition can occur internally and activate the INT/SQW pin independently of the user data.

If the SRAM is accessed by reading (address 19h) or writing (address 99h) the SRAM data register, the contents of the SRAM address register are automatically incremented after the first access, and all data cycles will use the SRAM data register.

# Handling, PC Board Layout, and Assembly

The DS3234 package contains a quartz tuning-fork crystal. Pick-and-place equipment can be used, but precautions should be taken to ensure that excessive shock and vibration are avoided. Exposure to reflow is limited to 2 times maximum. Ultrasonic cleaning should be avoided to prevent damage to the crystal.

Avoid running signal traces under the package, unless a ground plane is placed between the package and the signal line. All N.C. (no connect) pins must be connected to ground.

#### **DS3234**

# Extremely Accurate SPI Bus RTC with Integrated Crystal and SRAM

## **Chip Information**

SUBSTRATE CONNECTED TO GROUND PROCESS: CMOS

# **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/package">www.maximintegrated.com/package</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND           |  |

|---------|---------|---------|----------------|--|

| TYPE    | CODE    | NO.     | PATTERN NO.    |  |

| 20 SO   | W20#H2  | 21-0042 | <u>90-0108</u> |  |

### **Revision History**

| REVISION<br>NUMBER | REVISION<br>DATE                                  | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                          | PAGES<br>CHANGED          |

|--------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|

| 0                  | 2/06                                              | Initial release                                                                                                                                                                                                                                                                                                                                                                                                      | _                         |

| 1 7/07             | 7/07                                              | Clarified the behavior of t <sub>REC</sub> on initial power-up in the RST description of the <i>Pin Description</i>                                                                                                                                                                                                                                                                                                  | 8                         |

|                    | Corrected the POR for the BB32kHz bit from 0 to 1 | 15                                                                                                                                                                                                                                                                                                                                                                                                                   |                           |

| 2 10/0             |                                                   | Updated the Typical Operating Circuit                                                                                                                                                                                                                                                                                                                                                                                | 1                         |

|                    |                                                   | Removed the V <sub>PU</sub> parameter from the <i>Recommended DC Operating Conditions</i> table and added verbiage about the pullup to the <i>Pin Description</i> table for INT/SQW                                                                                                                                                                                                                                  | 2, 8                      |

|                    |                                                   | In the <i>Electrical Characteristics</i> table, added CRATE1 = CRATE0 = 0 to the I <sub>BATT</sub> parameter and changed the symbols for Timekeeping Battery Current, Temperature Conversion Current, and Data-Retention Current from I <sub>BAT</sub> , I <sub>TC</sub> , and I <sub>BATTC</sub> to I <sub>BATT</sub> , I <sub>BATTC</sub> , and I <sub>BATTDR</sub> , respectively                                 | 3                         |

|                    | 10/08                                             | In the AC Electrical Characteristics, changed the t <sub>CWH</sub> specification from 400ns (max) to 400ns (min)                                                                                                                                                                                                                                                                                                     | 4                         |

|                    |                                                   | Added the Delta Time and Frequency vs. Temperature graph in the <i>Typical Operating Characteristics</i> section                                                                                                                                                                                                                                                                                                     | 7                         |

|                    |                                                   | Updated the Block Diagram                                                                                                                                                                                                                                                                                                                                                                                            | 9                         |