#### **General Description**

The MAX8588 power-management IC is optimized for devices using Intel X-Scale<sup>™</sup> microprocessors, including smartphones, PDAs, internet appliances, and other portable devices requiring substantial computing and multimedia capability at low power.

The IC integrates seven high-performance, low-operatingcurrent power supplies along with supervisory and management functions. Included are three step-down DC-DC outputs, three linear regulators, and a seventh always-on output. DC-DC converters power I/O, memory, and the CPU core. The I/O supply can be preset to 3.3V or adjusted to other values. The DRAM supply is preset for 3.3V or 2.5V, or it can be adjusted with external resistors. The CPU core supply is serial programmed for dynamic voltage management and can supply up to 0.5A. Linear-regulated outputs are provided for SRAM, PLL, and USIM supplies.

To minimize quiescent current, critical power supplies have bypass "sleep" LDOs that can be activated when output current is very low. Other functions include separate on/off control for all DC-DC converters, low-battery and dead-battery detection, a reset and power-OK output, a backup-battery input, and a two-wire serial interface.

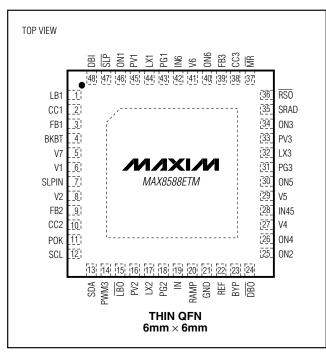

All DC-DC outputs use fast, 1MHz PWM switching and small external components. They operate with fixed-frequency PWM control and automatically switch from PWM to skip-mode operation at light loads to reduce operating current and extend battery life. The core output can be forced into PWM mode at all loads to minimize noise. A 2.6V to 5.5V input voltage range allows 1-cell lithium-ion (Li+), 3-cell NiMH, or a regulated 5V input. The MAX8588 is available in a tiny 6mm x 6mm, 48-pin thin QFN package.

#### **Applications**

PDA, Palmtop, and Wireless Handhelds Third-Generation Smart Cell Phones Internet Appliances and Web-Books

#### \_Features

Six Regulators in One Package Step-Down DC-DC for I/O at 1.3A Step-Down DC-DC for Memory at 0.9A Step-Down Serial-Programmed DC-DC for CORE Up to 0.5A Three LDO Outputs for SRAM, PLL, and USIM Always-On Output for VCC BATT

МЛХГМ

- Low Operating Current

60µA in Sleep Mode (Sleep LDOs On)

130µA with DC-DCs On (Core Off)

200µA All Regulators On, No Load

5µA Shutdown Current

- Optimized for X-Scale Processors

- Backup-Battery Input

- 1MHz PWM Switching Allows Small External Components

- Tiny 6mm x 6mm, 48-Pin Thin QFN Package

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE             |

|------------|----------------|-------------------------|

| MAX8588ETM | -40°C to +85°C | 48 Thin QFN (6mm x 6mm) |

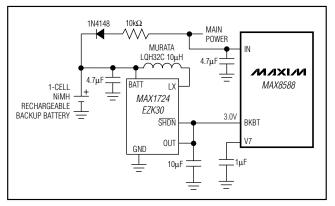

Pin Configuration appears at end of data sheet.

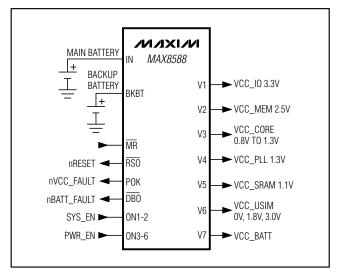

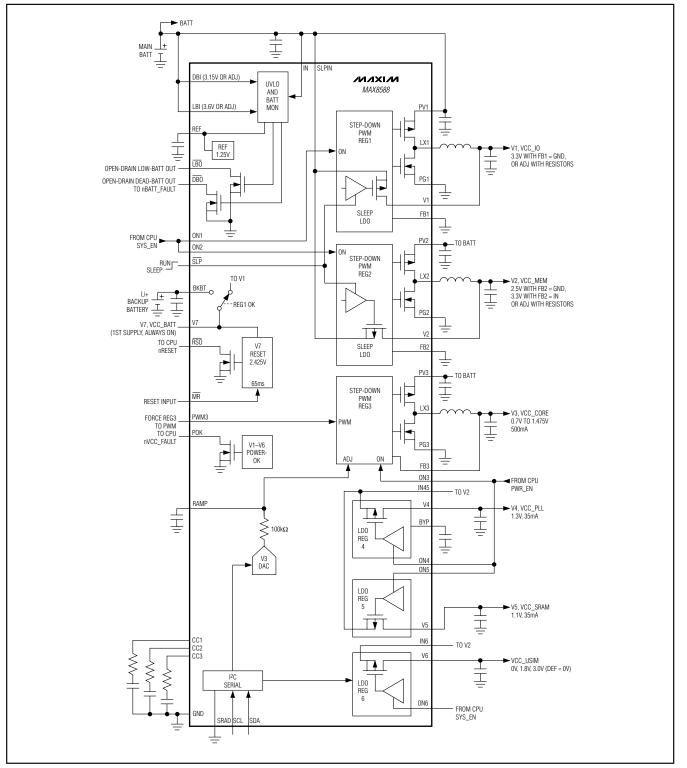

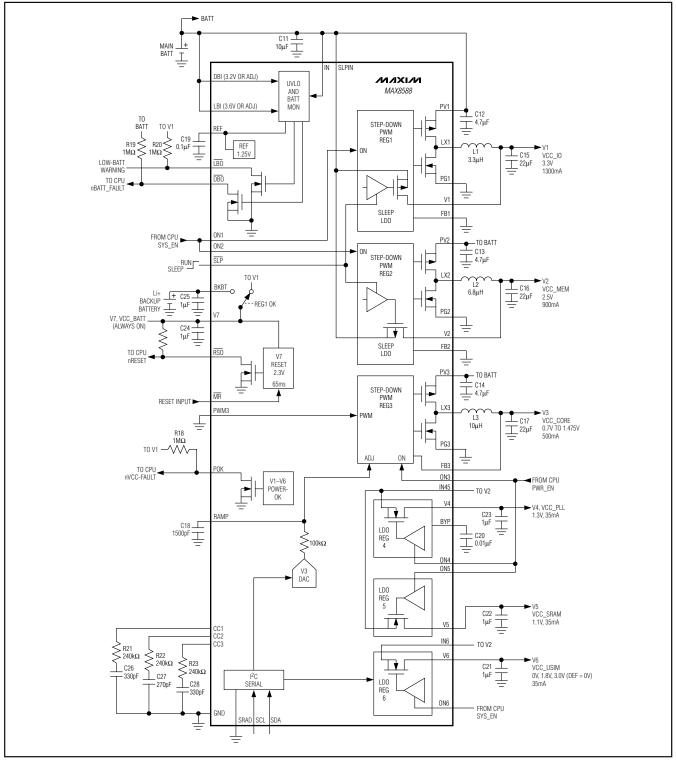

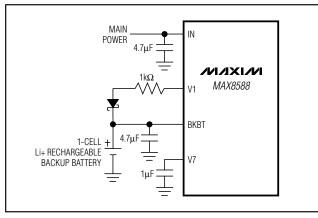

#### Simplified Diagram

X-Scale is a trademark of Intel Corp.

####

\_\_\_\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| IN, IN45, IN6, MR, LBO, DBO, F | RSO, POK, SCL, SDA,                | LX2 Continuo  |

|--------------------------------|------------------------------------|---------------|

| BKBT, V7, SLP, SRAD, PWN       | 13 to GND0.3V to +6V               | LX3 Continuo  |

| REF, CC_, ON_, FB_, DBI, LBI,  | V1, V2, RAMP, BYP,                 | PG1, PG2, PC  |

| MR to GND                      | 0.3V to (V <sub>IN</sub> + 0.3V)   | V1, V2, V4, V |

| PV1, PV2, PV3, SLPIN to IN     | -0.3V to +0.3V                     | Continuous P  |

| V4, V5 to GND                  | 0.3V to (V <sub>IN45</sub> + 0.3V) | 6mm x 6n      |

| V6 to GND                      | 0.3V to (V <sub>IN6</sub> + 0.3V)  | (derate 26    |

| PV1 to PG1                     | -0.3V to +6.0V                     | Operating Te  |

| PV2 to PG2                     | 0.3V to +6.0V                      | Junction Tem  |

| PV3 to PG3                     | 0.3V to +6.0V                      | Storage Temp  |

| LX1 Continuous Current         | 1.30A to +1.30A                    | Lead Temper   |

|                                |                                    |               |

| LX2 Continuous Current                                | 0.9A to +0.9A   |

|-------------------------------------------------------|-----------------|

| LX3 Continuous Current                                | 0.5A to +0.5A   |

| PG1, PG2, PG3 to GND                                  | 0.3V to +0.3V   |

| V1, V2, V4, V5, V6 Output Short-Circuit Dura          | ationContinuous |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                 |

| 6mm x 6mm 48-Pin Thin QFN                             |                 |

| (derate 26.3mW/°C above +70°C)                        | 2105mW          |

| Operating Temperature Range                           | 40°C to +85°C   |

| Junction Temperature                                  | +150°C          |

| Storage Temperature Range                             | 65°C to +150°C  |

| Lead Temperature (soldering, 10s)                     | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V$ , circuit of Figure 5, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                        |                                                                                       | CONDITIONS                                                    | MIN    | ТҮР  | МАХ    | UNITS |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------|---------------------------------------------------------------|--------|------|--------|-------|--|

| PV1, PV2, PV3, SLPIN, IN Supply<br>Voltage Range | PV1, PV2, PV3, IN, externally                                                         | PV1, PV2, PV3, IN, and SLPIN must connect together externally |        |      | 5.5    | V     |  |

| IN45, IN6 Supply Voltage Range                   |                                                                                       |                                                               | 2.4    |      | 5.5    | V     |  |

| IN Undervoltage-Lockout (UVLO)                   | V <sub>IN</sub> rising                                                                |                                                               |        | 2.40 | 2.55   | V     |  |

| Threshold                                        | V <sub>IN</sub> falling                                                               | V <sub>IN</sub> falling                                       |        | 2.35 | 2.525  | v     |  |

|                                                  |                                                                                       | Only V7 on, $V_{IN} = 3.0V$                                   |        | 32   |        |       |  |

| Quiescent Current                                | No load (Ipv1 +<br>Ipv2 + Ipv3 + I <sub>IN</sub> +                                    | REG1 and REG2 on in switch mode,<br>REG3 off                  |        | 130  |        |       |  |

| Quiescent Current                                | I <sub>SLPIN</sub> + I <sub>IN45</sub> +<br>I <sub>IN6</sub> )                        | REG1 and REG2 on in sleep mode,<br>REG3 off                   |        | 60   |        | μA    |  |

|                                                  |                                                                                       | All REGs on                                                   |        | 225  |        |       |  |

|                                                  | ON1 = 0                                                                               |                                                               |        | 4    |        |       |  |

| BKBT Input Current                               | ON1 = IN                                                                              |                                                               |        | 0.8  |        | μA    |  |

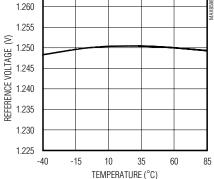

| REF Output Voltage                               | 0 to 10µA load                                                                        |                                                               | 1.2375 | 1.25 | 1.2625 | V     |  |

| SYNCHRONOUS-BUCK PWM REG                         | 1                                                                                     |                                                               |        |      |        |       |  |

| REG1 Voltage Accuracy                            | FB1 = GND, 3.6V ≤                                                                     | $V_{PV1} \le 5.5V$ , load = 0 to 1300mA                       | 3.25   | 3.3  | 3.35   | V     |  |

| FB1 Voltage Accuracy                             | FB1 used with external resistors, $3.6V \le V_{PV1} \le 5.5V$ ,<br>load = 0 to 1300mA |                                                               | 1.231  | 1.25 | 1.269  | V     |  |

| FB1 Input Current                                | FB1 used with external resistors                                                      |                                                               |        |      | 100    | nA    |  |

| Error-Amplifier Transconductance                 | Referred to FB                                                                        |                                                               |        | 87   |        | μS    |  |

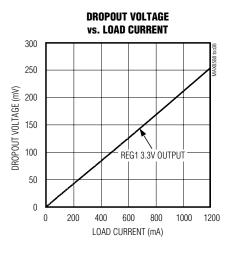

| Dropout Voltage (Note 1)                         | Load = 800mA                                                                          |                                                               |        | 180  | 280    | m\/   |  |

|                                                  | Load = 1300mA                                                                         | Load = 1300mA                                                 |        | 293  | 450    | mV    |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V$ , circuit of Figure 5, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                | CONE                                                                                 | CONDITIONS                                         |       | ΤΥΡ    | MAX   | UNITS |

|------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------|-------|--------|-------|-------|

| n Channel On Desistance                  | I <sub>LX1</sub> = -180mA                                                            |                                                    |       | 0.18   | 0.3   | 0     |

| p-Channel On-Resistance                  | I <sub>LX1</sub> = -180mA, V <sub>PV1</sub> = 2.6V                                   | I <sub>LX1</sub> = -180mA, V <sub>PV1</sub> = 2.6V |       | 0.21   | 0.35  | Ω     |

|                                          | I <sub>LX1</sub> = 180mA                                                             |                                                    |       | 0.13   | 0.225 | 0     |

| n-Channel On-Resistance                  | I <sub>LX1</sub> = 180mA, V <sub>PV1</sub> = 2.6V                                    |                                                    |       | 0.15   | 0.25  | Ω     |

| Current-Sense Transresistance            |                                                                                      |                                                    |       | 0.5    |       | V/A   |

| p-Channel Current-Limit Threshold        |                                                                                      |                                                    | -1.55 | -1.80  | -2.10 | А     |

| PWM Skip-Mode Transition Load<br>Current | Decreasing load current (No                                                          | Decreasing load current (Note 2)                   |       | 30     |       | mA    |

| OUT1 Maximum Output Current              | 2.6V ≤ V <sub>PV1</sub> ≤ 5.5V (Note 3)                                              |                                                    | 1.3   |        |       | А     |

| LX1 Leakage Current                      | V <sub>PV1</sub> = 5.5V, LX1 = GND or I                                              | PV1, V <sub>ON1</sub> = 0V                         | -20   | +0.1   | +20   | μΑ    |

| SYNCHRONOUS-BUCK PWM REG                 | 2                                                                                    |                                                    |       |        |       |       |

|                                          | FB2 = GND, $3.6V \le V_{PV2} \le 5.5V$ , load = 0 to 900mA                           |                                                    | 2.463 | 2.5    | 2.537 |       |

| REG2 Voltage Accuracy                    | FB2 = IN, $3.6V \le V_{PV2} \le 5.5V$ , load = 0 to 900mA                            |                                                    | 3.25  | 3.3    | 3.35  | V     |

| FB2 Voltage Accuracy                     | FB2 used with external resistors, $3.6V \le V_{PV2} \le 5.5V$ ,<br>load = 0 to 900mA |                                                    | 1.231 | 1.25   | 1.269 | V     |

| FB2 Input Current                        | FB2 used with external resist                                                        | tors, V <sub>FB2</sub> = 1.25V                     |       |        | 100   | nA    |

| Error-Amplifier Transconductance         | Referred to FB                                                                       |                                                    |       | 87     |       | μS    |

| Dropout Voltage                          | Load = 900mA (Note 1)                                                                |                                                    |       | 243    | 380   | mV    |

| p-Channel On-Resistance                  | I <sub>LX2</sub> = -180mA                                                            |                                                    |       | 0.225  | 0.375 | Ω     |

| p-channel on-nesistance                  | $I_{LX2} = -180 \text{mA}, V_{PV2} = 2.6 \text{V}$                                   |                                                    |       | 0.26   | 0.425 | 52    |

| n-Channel On-Resistance                  | I <sub>LX2</sub> = 180mA                                                             |                                                    |       | 0.15   | 0.25  | Ω     |

| n-channel on-nesistance                  | I <sub>LX2</sub> = 180mA, V <sub>PV2</sub> = 2.6V                                    |                                                    |       | 0.17   | 0.275 | 52    |

| Current-Sense Transresistance            |                                                                                      |                                                    |       | 0.7    |       | V/A   |

| p-Channel Current-Limit Threshold        |                                                                                      |                                                    | -1.10 | -1.275 | -1.50 | А     |

| PWM Skip-Mode Transition Load<br>Current | Decreasing load current (No                                                          | Decreasing load current (Note 2)                   |       | 30     |       | mA    |

| OUT2 Maximum Output Current              | $2.6V \le V_{PV2} \le 5.5V$ (Note 3)                                                 |                                                    | 0.9   |        |       | А     |

| LX2 Leakage Current                      | V <sub>PV2</sub> = 5.5V, LX2 = GND or PV2, V <sub>ON2</sub> = 0V                     |                                                    | -10   | +0.1   | +10   | μA    |

| SYNCHRONOUS-BUCK PWM REG                 | 3                                                                                    |                                                    |       |        |       |       |

| REG3 Voltage Accuracy                    | REG3 from 0.7V to 1.475V,<br>2.6V $\leq$ V <sub>PV3</sub> $\leq$ 5.5V                | Load = 0 to 500mA                                  | -1.5  |        | +1.5  | %     |

| Error-Amplifier Transconductance         |                                                                                      | •                                                  |       | 68     |       | μS    |

|                                          |                                                                                      |                                                    |       |        |       |       |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V$ , circuit of Figure 5, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                        | CONDITIONS                                                        | MIN   | TYP               | MAX   | UNITS             |  |

|--------------------------------------------------|-------------------------------------------------------------------|-------|-------------------|-------|-------------------|--|

|                                                  | I <sub>LX3</sub> = -180mA                                         |       | 0.225             | 0.375 |                   |  |

| p-Channel On-Resistance                          | $I_{LX2} = -180 \text{mA}, V_{PV3} = 2.6 \text{V}$                |       | 0.26              | 0.425 | Ω                 |  |

|                                                  | I <sub>LX3</sub> = 180mA                                          |       | 0.15              | 0.25  |                   |  |

| n-Channel On-Resistance                          | I <sub>LX3</sub> = 180mA, V <sub>PV3</sub> = 2.6V                 |       | 0.17              | 0.275 | Ω                 |  |

| Current-Sense Transresistance                    |                                                                   |       | 1.1               |       | V/A               |  |

| p-Channel Current-Limit Threshold                |                                                                   | -0.60 | -0.7              | -0.85 | Α                 |  |

| PWM Skip-Mode Transition Load<br>Current         | Decreasing load current (Note 2)                                  |       | 30                |       | mA                |  |

| OUT3 Maximum Output Current                      | 2.6V ≤ V <sub>PV3</sub> ≤ 5.5V (Note 3)                           | 0.5   |                   |       | А                 |  |

| LX3 Leakage Current                              | V <sub>PV3</sub> = 5.5V, LX3 = GND or PV2, V <sub>ON3</sub> = 0V  | -10   | +0.1              | +10   | μA                |  |

| LDOS V4, V5, V6, V1 SLEEP, V2 SL                 | EEP, AND V7 OUTPUT                                                |       |                   |       | •                 |  |

| V4, V5, V6, V1 SLEEP, V2 SLEEP<br>Output Current |                                                                   | 35    |                   |       | mA                |  |

| V7 Output Current                                |                                                                   | 30    |                   |       | mA                |  |

| REG4 Output Voltage                              | Load = 0.1mA to 35mA                                              | 1.261 | 1.3               | 1.339 | V                 |  |

| REG4 Noise                                       | With 1 $\mu$ F C <sub>OUT</sub> and 0.01 $\mu$ F C <sub>BYP</sub> |       | 15                |       | μV <sub>RMS</sub> |  |

| REG5 Output Voltage                              | Load = 0.1mA to 35mA                                              | 1.067 | 1.1               | 1.133 | V                 |  |

| IN45, IN6 Input Voltage Range                    |                                                                   | 2.4   |                   | 5.5   | V                 |  |

| REG6 Output Voltage (POR Default                 | 0V setting (either ON6 low or serial programmed)                  |       | 0                 |       |                   |  |

|                                                  | 1.8V setting, load = 0.1mA to 35mA                                | 1.746 | 1.8               | 1.854 |                   |  |

| to 0V, Set by Serial Input)                      | 2.5V setting, load = 0.1mA to 35mA                                | 2.425 | 2.5               | 2.575 |                   |  |

|                                                  | 3.0V setting, load = 0.1mA to 35mA                                | 2.91  | 3.0               | 3.09  |                   |  |

| VZ Output Valtage                                | V1 on and in regulation                                           |       | $V_{V1}$          |       | V                 |  |

| V7 Output Voltage                                | V1 off                                                            |       | V <sub>BKBT</sub> |       | v                 |  |

| V1 and V2 SLEEP Output Voltage<br>Accuracy       | Set to same output voltage as REG1 and REG2                       | -3.0  |                   | +3.0  | %                 |  |

| V1 and V2 SLEEP Dropout Voltage                  | Load = 20mA                                                       |       | 75                | 150   | mV                |  |

| V6 Dropout Voltage                               | 3V mode, load = 30mA, 2.5V mode, load = 30mA                      |       | 110               | 200   | mV                |  |

| V7 Switch Voltage Drop                           | Load = 20mA, $V_{BKBT} = V_{V1} = 3.0V$                           |       | 100               | 200   | mV                |  |

| V4, V5, V6 Output Current Limit                  |                                                                   | 40    | 90                |       | mA                |  |

| BKBT Leakage                                     |                                                                   |       |                   | 1     | μA                |  |

| OSCILLATOR                                       |                                                                   | •     |                   |       |                   |  |

| PWM Switching Frequency                          |                                                                   | 0.93  | 1                 | 1.07  | MHz               |  |

| SUPERVISORY/MANAGEMENT FU                        | NCTIONS                                                           |       |                   |       |                   |  |

| POK Trip Throshold (Note 4)                      | Rising                                                            | 92    | 94.75             | 97    | 0/                |  |

| OK Trip Threshold (Note 4)                       | old (Note 4) Falling                                              |       | 90.5              | 92.5  | %                 |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V$ , circuit of Figure 5, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                                                                                                    | CONDITIONS                       |                       | MIN   | ТҮР   | МАХ   | UNITS |  |

|--------------------------------------------------------------------------------------------------------------|----------------------------------|-----------------------|-------|-------|-------|-------|--|

|                                                                                                              |                                  | LBI = IN (for preset) | 3.51  | 3.6   | 3.69  | V     |  |

| LBI Threshold (Falling)                                                                                      | Hysteresis is 5% (typ)           | With resistors at LBI | 0.98  | 1.00  | 1.02  | V     |  |

|                                                                                                              | Libertana aia ia 50( (tura)      | DBI = IN (for preset) | 3.024 | 3.15  | 3.276 |       |  |

| DBI Threshold (Falling)                                                                                      | Hysteresis is 5% (typ)           | With resistors at LBI | 1.208 | 1.232 | 1.256 | V     |  |

| RSO Threshold (Falling)                                                                                      | Voltage on REG7, hystere         | esis is 5% (typ)      | 2.25  | 2.41  | 2.56  | V     |  |

| RSO Deassert Delay                                                                                           |                                  |                       | 61    | 65.5  | 70    | ms    |  |

| LBI Input Bias Current                                                                                       |                                  |                       | -50   | -5    |       | nA    |  |

| DBI Input Bias Current                                                                                       |                                  |                       |       | 15    | 50    | nA    |  |

| Thermal-Shutdown Temperature                                                                                 | T <sub>J</sub> rising            | rising                |       | +160  |       | °C    |  |

| Thermal-Shutdown Hysteresis                                                                                  |                                  |                       |       | 15    |       | °C    |  |

| LOGIC INPUTS AND OUTPUTS                                                                                     |                                  |                       |       |       |       |       |  |

| LBO, DBO, POK, RSO, SDA Output<br>Low Level                                                                  | $2.6V \le V7 \le 5.5V$ , sinking | 1mA                   |       |       | 0.4   | V     |  |

| LBO, DBO, POK, RSO Output Low<br>Level                                                                       | V7 = 1V, sinking 100µA           |                       |       |       | 0.4   | V     |  |

| LBO, DBO, POK, RSO Output-High<br>Leakage Current                                                            | Pin = 5.5V                       |                       |       |       | 0.2   | μΑ    |  |

| ON_, SCL, SDA, SLP, PWM3, MR,<br>SRAD Input High Level                                                       | $2.6V \le V_{IN} \le 5.5V$       |                       | 1.6   |       |       | V     |  |

| ON_, SCL, SDA, SLP, PWM3, MR,<br>SRAD Input Low Level                                                        | $2.6V \le V_{IN} \le 5.5V$       |                       |       |       | 0.4   | V     |  |

| ON_, SCL, SDA, SLP, PWM3, MR,<br>SRAD Input Leakage Current                                                  | Pin = GND, 5.5V                  |                       | -1    |       | +1    | μA    |  |

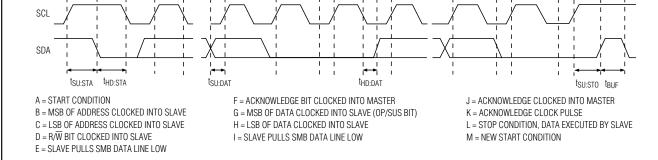

| SERIAL INTERFACE                                                                                             |                                  |                       | •     |       |       |       |  |

| Clock Frequency                                                                                              |                                  |                       |       |       | 400   | kHz   |  |

| Bus Free Time Between START and STOP                                                                         |                                  |                       | 1.3   |       |       | μs    |  |

| Hold Time Repeated START Condition                                                                           |                                  |                       | 0.6   |       |       | μs    |  |

| CLK Low Period                                                                                               |                                  |                       | 1.3   |       |       | μs    |  |

| CLK High Period                                                                                              |                                  |                       | 0.6   |       |       | μs    |  |

| Setup Time Repeated START Condition                                                                          |                                  |                       | 0.6   |       |       | μs    |  |

| DATA Hold Time                                                                                               |                                  |                       | 0     |       |       | μs    |  |

| DATA Setup Time                                                                                              |                                  |                       | 100   |       |       | ns    |  |

| Maximum Pulse Width of Spikes that<br>Must be Suppressed by the Input<br>Filter of Both DATA and CLK Signals |                                  |                       |       | 50    |       | ns    |  |

| Setup Time for STOP Condition                                                                                |                                  |                       | 0.6   |       |       | μs    |  |

## MAX8588

#### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V, circuit of Figure 5, T_{A} = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 5)$

| PARAMETER                                        | CONDITIONS                                                                            | MIN   | MAX   | UNITS  |  |

|--------------------------------------------------|---------------------------------------------------------------------------------------|-------|-------|--------|--|

| PV1, PV2, PV3, SLPIN, IN Supply<br>Voltage Range | PV1, PV2, PV3, IN, and SLPIN must connect together externally                         | 2.6   | 5.5   | V      |  |

| IN45, IN6 Supply Voltage Range                   |                                                                                       | 2.4   | 5.5   | V      |  |

| IN Undervoltage-Lockout (UVLO)                   | V <sub>IN</sub> rising                                                                | 2.25  | 2.55  | V      |  |

| Threshold                                        | V <sub>IN</sub> falling                                                               | 2.200 | 2.525 | v      |  |

| SYNCHRONOUS-BUCK PWM REG                         | 1                                                                                     |       |       |        |  |

| REG1 Voltage Accuracy                            | FB1 = GND, $3.6V \le V_{PV1} \le 5.5V$ , load = 0 to 1300mA                           | 3.25  | 3.35  | V      |  |

| FB1 Voltage Accuracy                             | FB1 used with external resistors, $3.6V \le V_{PV1} \le 5.5V$ ,<br>load = 0 to 1300mA | 1.231 | 1.269 | V      |  |

| FB1 Input Current                                | FB1 used with external resistors                                                      |       | 100   | nA     |  |

| Dropout Voltogo                                  | Load = 800mA (Note 1)                                                                 |       | 280   |        |  |

| Dropout Voltage                                  | Load = 1300mA (Note 1)                                                                |       | 450   | mV     |  |

| n Channel On Desistance                          | $I_{LX1} = -180 \text{mA}$                                                            |       | 0.3   | Ω      |  |

| p-Channel On-Resistance                          | $I_{LX1} = -180 \text{mA}, V_{PV1} = 2.6 \text{V}$                                    |       | 0.35  |        |  |

| n-Channel On-Resistance                          | I <sub>LX1</sub> = 180mA                                                              |       | 0.225 | 0      |  |

| n-Channel On-Resistance                          | I <sub>LX1</sub> = 180mA, V <sub>PV1</sub> = 2.6V                                     |       | 0.25  | Ω      |  |

| p-Channel Current-Limit Threshold                |                                                                                       | -1.55 | -2.10 | А      |  |

| OUT1 Maximum Output Current                      | $2.6V \le V_{PV1} \le 5.5V$ (Note 3)                                                  | 1.30  |       | А      |  |

| LX1 Leakage Current                              | $V_{PV1} = 5.5V$ , LX1 = GND or PV1, $V_{ON1} = 0V$                                   | -10   | +10   | μA     |  |

| SYNCHRONOUS-BUCK PWM REG                         | 2                                                                                     |       |       |        |  |

|                                                  | FB2 = GND, $3.6V \le V_{PV2} \le 5.5V$ , load = 0 to 900mA                            | 2.463 | 2.537 | V      |  |

| REG2 Voltage Accuracy                            | FB2 = IN, $3.6V \le V_{PV2} \le 5.5V$ , load = 0 to 900mA                             | 3.25  | 3.35  | v      |  |

| FB2 Voltage Accuracy                             | FB2 used with external resistors, $3.6V \le V_{PV2} \le 5.5V$ , load = 0 to 900mA     | 1.231 | 1.269 | V      |  |

| FB2 Input Current                                | FB2 used with external resistors, $V_{FB2} = 1.25V$                                   |       | 100   | nA     |  |

| Dropout Voltage                                  | Load = 900mA (Note 1)                                                                 |       | 380   | mV     |  |

| n Channel On Registeries                         | $I_{LX2} = -180 \text{mA}$                                                            |       | 0.375 | Ω      |  |

| p-Channel On-Resistance                          | $I_{LX2} = -180 \text{mA}, V_{PV2} = 2.6 \text{V}$                                    |       | 0.425 | 52     |  |

| n Channel On Desistance                          | $I_{LX2} = -180 \text{mA}$                                                            |       | 0.25  | 0      |  |

| n-Channel On-Resistance                          | I <sub>LX2</sub> = -180mA, V <sub>PV2</sub> = 2.6V                                    |       | 0.275 | .275 Ω |  |

| p-Channel Current-Limit Threshold                |                                                                                       | -1.1  | -1.50 | А      |  |

| OUT2 Maximum Output Current                      | $2.6V \le V_{PV2} \le 5.5V$ (Note 3)                                                  | 0.9   |       | А      |  |

| LX2 Leakage Current                              | $V_{PV2} = 5.5V$ , LX2 = GND or PV2, $V_{ON2} = 0V$                                   | -10   | +10   | μA     |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V, circuit of Figure 5, T_{A} = -40^{\circ}C to +85^{\circ}C, unless otherwise noted.) (Note 5)$

| PARAMETER                                                    | CONDITIONS                                                        |                                 | MIN   | MAX   | UNITS |  |

|--------------------------------------------------------------|-------------------------------------------------------------------|---------------------------------|-------|-------|-------|--|

| SYNCHRONOUS-BUCK PWM REG                                     | 3                                                                 |                                 |       |       | •     |  |

| REG3 Output Voltage Accuracy                                 | REG3 from 0.7V to 1.475V 2.6V $\leq$ V <sub>PV3</sub> $\leq$ 5.5V | <sup>/,</sup> Load = 0 to 500mA | -1.5  | +1.5  | %     |  |

| n Channel On Desistance                                      | I <sub>LX3</sub> = -180mA                                         |                                 |       | 0.375 | 0     |  |

| p-Channel On-Resistance                                      | I <sub>LX2</sub> = -180mA, V <sub>PV3</sub> = 2.6                 | SV                              |       | 0.425 | Ω     |  |

| n Channel On Resistance                                      | I <sub>LX3</sub> = 180mA                                          |                                 |       | 0.25  | 0     |  |

| n-Channel On-Resistance                                      | I <sub>LX3</sub> = 180mA, V <sub>PV3</sub> = 2.6                  | V                               |       | 0.275 | Ω     |  |

| p-Channel Current-Limit Threshold                            |                                                                   |                                 | -0.60 | -0.85 | А     |  |

| OUT3 Maximum Output Current                                  | 2.6V ≤ V <sub>PV3</sub> ≤ 5.5V (Note :                            | 3)                              | 0.5   |       | А     |  |

| LX3 Leakage Current                                          | V <sub>PV3</sub> = 5.5V, LX3 = GND                                | or PV2, V <sub>ON3</sub> = 0V   | -10   | +10   | μA    |  |

| LDOs V4, V5, V6, V1 SLEEP, V2 SL                             | EEP, AND V7 OUTPUT                                                |                                 |       |       |       |  |

| V4, V5, V6, V1 SLEEP, V2 SLEEP<br>Output Current             |                                                                   |                                 | 35    |       | mA    |  |

| V7 Output Current                                            |                                                                   | 30                              |       | mA    |       |  |

| REG4 Voltage Accuracy                                        | Load = 0.1mA to 35mA                                              | Load = 0.1mA to 35mA            |       | 1.346 | V     |  |

| REG5 Voltage Accuracy                                        | Load = 0.1mA to 35mA                                              | Load = 0.1mA to 35mA            |       | 1.139 | V     |  |

| IN45, IN6 Input Voltage Range                                |                                                                   |                                 |       | 5.5   | V     |  |

|                                                              | 1.8V setting, load = 0.1mA to 35mA                                |                                 | 1.737 | 1.863 |       |  |

| REG6 Output Voltage (POR Default to 0V, Set by Serial Input) | 2.5V setting, load = 0.1mA to 35mA                                |                                 | 2.412 | 2.588 | V     |  |

| to ov, set by senai input)                                   | 3.0V setting, load = 0.1mA to 35mA                                |                                 | 2.895 | 3.105 |       |  |

| V1 and V2 SLEEP Output Voltage<br>Accuracy                   | Set to same output voltag                                         | e as REG1 and REG2              | -3.5  | +3.5  | %     |  |

| V1 and V2 SLEEP Dropout Voltage                              | Load = 20mA                                                       |                                 |       | 150   | mV    |  |

| V6 Dropout Voltage                                           | 3V mode, load = 30mA; 2.                                          | 5V mode, load = 30mA            |       | 200   | mV    |  |

| V7 Switch Voltage Drop                                       | Load = 20mA, V <sub>BKBT</sub> = V                                | /1 = 3.0V                       |       | 200   | mV    |  |

| V4, V5, V6 Output Current Limit                              |                                                                   |                                 | 40    |       | mA    |  |

| BKBT Leakage                                                 |                                                                   |                                 |       | 1     | μA    |  |

| OSCILLATOR                                                   |                                                                   |                                 |       |       |       |  |

| PWM Switching Frequency                                      |                                                                   |                                 | 0.93  | 1.07  | MHz   |  |

| SUPERVISORY/MANAGEMENT FU                                    | NCTIONS                                                           |                                 |       |       |       |  |

| DOK Trip Threader's (Nets A)                                 | Rising                                                            |                                 | 92    | 97    | 0/    |  |

| POK Trip Threshold (Note 4)                                  | Falling                                                           |                                 | 88.5  | 92.5  | %     |  |

| DI Threadedd (Falling)                                       | Librataragia in EQ( (true)                                        | LBI = IN (for preset)           | 3.51  | 3.69  | V     |  |

| LBI Threshold (Falling)                                      | Hysteresis is 5% (typ)                                            | With resistors at LBI           | 0.98  | 1.02  | V     |  |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = 3.6V, V_{BKBT} = 3.0V, V_{LBI} = 1.1V, V_{DBI} = 1.35V, \text{ circuit of Figure 5}, \textbf{T_A} = -40^{\circ}C \text{ to } +85^{\circ}C, \text{ unless otherwise noted.}) (Note 5)$

| PARAMETER                                                                   | CO                               | NDITIONS                   | MIN   | MAX   | UNITS |

|-----------------------------------------------------------------------------|----------------------------------|----------------------------|-------|-------|-------|

|                                                                             |                                  | DBI = IN (for preset)      | 2.993 | 3.307 | N     |

| DBI Threshold (Falling)                                                     | Hysteresis is 5% (typ)           | With resistors at LBI      | 1.208 | 1.256 | V     |

| RSO Threshold (Falling)                                                     | Voltage on REG7, hystere         | esis is 5% (typ)           | 2.25  | 2.60  | V     |

| RSO Deassert Delay                                                          |                                  |                            | 62    | 69    | ms    |

| LBI Input Bias Current                                                      |                                  |                            | -50   |       | nA    |

| DBI Input Bias Current                                                      |                                  |                            |       | 75    | nA    |

| LOGIC INPUTS AND OUTPUTS                                                    |                                  |                            |       |       |       |

| LBO, DBO, POK, RSO, SDA Output<br>Low Level                                 | $2.6V \le V7 \le 5.5V$ , sinking | 1mA                        |       | 0.4   | V     |

| LBO, DBO, POK, RSO, SDA Output<br>Low Level                                 | V7 = 1V, sinking 100µA           | 7 = 1V, sinking 100µA      |       | 0.4   | V     |

| LBO, DBO, POK, RSO Output-High<br>Leakage Current                           | Pin = 5.5V                       | in = 5.5V                  |       | 0.2   | μA    |

| ON_, SCL, SDA, SLP, PWM3, MR,<br>SRAD Input High Level                      | $2.6V \le V_{IN} \le 5.5V$       | $2.6V \le V_{IN} \le 5.5V$ |       |       | V     |

| ON_, SCL, SDA, SLP, PWM3, MR,<br>SRAD Input Low Level                       | $2.6V \le V_{IN} \le 5.5V$       | $2.6V \le V_{IN} \le 5.5V$ |       | 0.4   | V     |

| ON_, SCL, SDA, <u>SLP</u> , PWM3, <u>MR</u> ,<br>SRAD Input Leakage Current | Pin = GND, 5.5V                  |                            | -1    | +1    | μA    |

| SERIAL INTERFACE                                                            |                                  |                            |       |       |       |

| Clock Frequency                                                             |                                  |                            |       | 400   | kHz   |

| Bus Free Time Between START and STOP                                        |                                  |                            | 1.3   |       | μs    |

| Hold Time Repeated START<br>Condition                                       |                                  |                            | 0.6   |       | μs    |

| CLK Low Period                                                              |                                  |                            | 1.3   |       | μs    |

| CLK High Period                                                             |                                  |                            | 0.6   |       | μs    |

| Setup Time Repeated START<br>Condition                                      |                                  |                            | 0.6   |       | μs    |

| DATA Hold Time                                                              |                                  |                            | 0     |       | μs    |

| DATA Setup Time                                                             |                                  |                            | 100   |       | ns    |

| Setup Time for STOP Condition                                               |                                  |                            | 0.6   |       | μs    |

M/IXI/M

#### **ELECTRICAL CHARACTERISTICS (continued)**

Note 1: Dropout voltage is guaranteed by the p-channel switch resistance and assumes a maximum inductor resistance of 45m Ω.

Note 2: The PWM-skip-mode transition has approximately 10mA of hysteresis.

Note 3: The maximum output current is guaranteed by the following equation:

$$I_{OUTmax} = \frac{I_{LIM} - \frac{V_{OUT} (1 - D)}{2 \times f \times L}}{1 + (R_N + R_L) \frac{(1 - D)}{2 \times f \times L}}$$

where:

$$\mathsf{D} = \frac{\mathsf{V}_{\mathsf{OUT}} + \mathsf{I}_{\mathsf{OUT}(\mathsf{MAX})} (\mathsf{R}_{\mathsf{N}} + \mathsf{R}_{\mathsf{L}})}{\mathsf{V}_{\mathsf{IN}} + \mathsf{I}_{\mathsf{OUT}(\mathsf{MAX})} (\mathsf{R}_{\mathsf{N}} - \mathsf{R}_{\mathsf{P}})}$$

and  $R_N = n$ -channel synchronous rectifier  $R_{DS(ON)}$

R<sub>P</sub> = p-channel power switch R<sub>DS(ON)</sub>

$R_L$  = external inductor ESR

IOUT(MAX) = maximum required load current

f = operating frequency minimum

L = external inductor value

$I_{LIM}$  can be substituted for  $I_{OUT(MAX)}$  (desired) when solving for D. This assumes that the inductor ripple current is small relative to the absolute value.

Note 4: POK only indicates the status of supplies that are enabled (except V7). When a supply is turned off, POK does not trigger low. When a supply is turned on, POK immediately goes low until that supply reaches regulation. POK is forced low when all supplies (except V7) are disabled.

Note 5: Specifications to -40°C are guaranteed by design, not production tested.

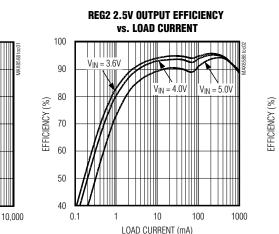

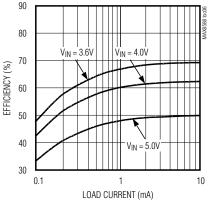

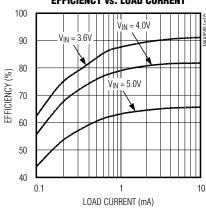

(Circuit of Figure 6,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

$V_{IN} = 5.0V$

vs. LOAD CURRENT

4.0V Vin =

10

100

LOAD CURRENT (mA)

## **MAX8588 REG1 3.3V OUTPUT EFFICIENCY** 100 $V_{IN} = 3.6V$ 90 80 EFFICIENCY (%)

70

60

50

40

0.1

1

#### **REG3 1.3V OUTPUT EFFICIENCY** vs. LOAD CURRENT 100 90 $V_{IN} = 3.6V$ 80 $V_{IN} = 5.0V$ $V_{IN} = 4.0V$ 70 60 50 40 10 0.1 1 100 1000 LOAD CURRENT (mA)

**REG3 1.3V OUTPUT WITH FORCED-PWM EFFICIENCY vs. LOAD CURRENT**

1000

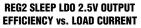

**REG1 SLEEP LDO 3.3V OUTPUT EFFICIENCY vs. LOAD CURRENT**

**Typical Operating Characteristics**

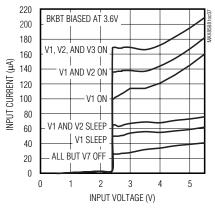

**OUIESCENT CURRENT** vs. SUPPLY VOLTAGE

1.265

#### **Typical Operating Characteristics (continued)**

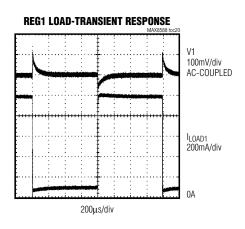

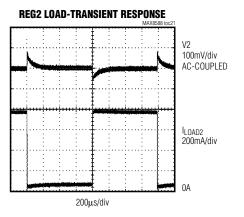

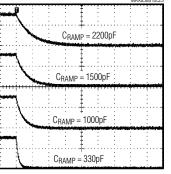

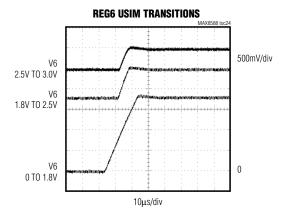

(Circuit of Figure 6,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

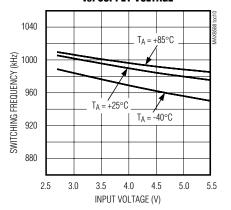

SWITCHING FREQUENCY vs. SUPPLY VOLTAGE

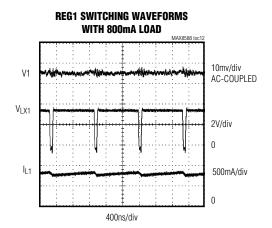

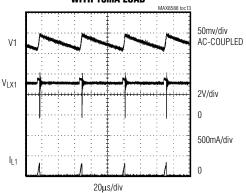

#### REG1 SWITCHING WAVEFORMS WITH 10mA LOAD

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 6,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

**MAX8588**

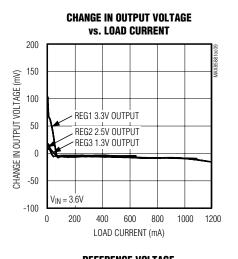

#### **Typical Operating Characteristics (continued)**

(Circuit of Figure 6,  $V_{IN}$  = 3.6V,  $T_A$  = +25°C, unless otherwise noted.)

# **MAX8588**

REG3 LOAD-TRANSIENT RESPONSE

REG3 OUTPUT VOLTAGE CHANGING FROM 1.3V TO 1.0V WITH DIFFERENT VALUES OF CRAMP

200µs/div

#### Pin Description

|     |       | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

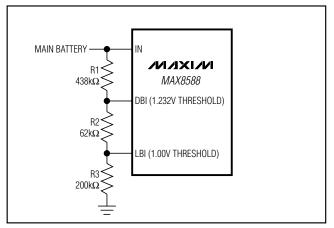

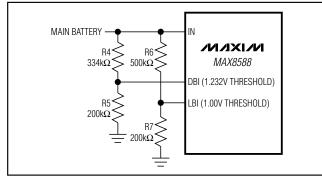

| 1   | LBI   | Dual-Mode <sup>™</sup> , Low-Battery Input. Connect to IN to set the low-battery threshold to 3.6V (no resistors needed).<br>Connect LBI to a resistor-divider for an adjustable LBI threshold. When IN is below the set threshold, <u>LBO</u> output switches low. <u>LBO</u> is deactivated and forced low when IN is below the dead-battery (DBI) threshold and when all REGs are disabled.                                                                                                                                                                                                     |

| 2   | CC1   | REG1 Compensation Node. Connect a series resistor and capacitor from CC1 to GND to compensate the regulation loop. See the <i>Compensation and Stability</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 3   | FB1   | REG1 Feedback Input. Connect FB1 to GND to set V1 to 3.3V. Connect FB1 to external feedback resistors for other output voltages.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

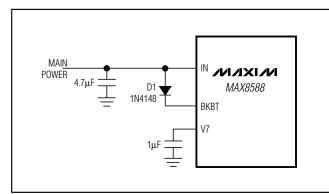

| 4   | BKBT  | Input Connection for Backup Battery. This input can also accept the output of an external boost converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 5   | V7    | <ul> <li>Also known as VCC_BATT. V7 is always active if main or backup power is present. It is the first regulator that powers up. V7 has two states:</li> <li>1) V7 tracks V1 if ON1 is high and V1 is in regulation.</li> <li>2) V7 tracks V<sub>BKBT</sub> when ON1 is low or V1 is out of regulation.</li> </ul>                                                                                                                                                                                                                                                                               |

| 6   | V1    | REG1 Voltage-Sense Input. Connect directly to the REG1 output voltage. The output voltage is set by FB1 to either 3.3V or adjustable with resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 7   | SLPIN | Input to V1 and V2 Sleep Regulators. The input to the standby regulators at V1 and V2. Connect SLPIN to IN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8   | V2    | REG2 Voltage-Sense Input. Connect directly to the REG2 output voltage. The output voltage is set by FB2 to either 3.3V/2.5V or adjustable with resistors.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 9   | FB2   | REG2 Feedback Input. Connect to GND to set V2 to 2.5V on all devices. Connect FB2 to IN to set V2 to 3.3V. Connect FB2 to external feedback resistors for other voltages.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10  | CC2   | REG2 Compensation Node. Connect a series resistor and capacitor from CC2 to GND to compensate the regulation loop. See the <i>Compensation and Stability</i> section.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11  | РОК   | Power-OK Output. Open-drain output that is low when any of the V1–V6 outputs are below their regulation threshold. When all activated outputs are in regulation, POK is high impedance. POK maintains a valid low output with V7 as low as 1V. POK does not flag an out-of-regulation condition while REG3 is transitioning between voltages set by serial programming. POK also does not flag for any REG channel that has been turned off; however, if <i>all</i> REG channels are off (V1–V6), then POK is forced low. If IN < UVLO, then POK is low. POK is expected to connect to nVCC_FAULT. |

| 12  | SCL   | Serial Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 13  | SDA   | Serial Data Input. Serial data programs the REG3 (core) and REG6 (VCC_USIM) voltage. REG3 and REG6 can be programmed even when off, but at least one of the ON_ pins must be logic-high to activate the serial interface. On power-up, REG3 defaults to 1.3V and REG6 defaults to 0V.                                                                                                                                                                                                                                                                                                              |

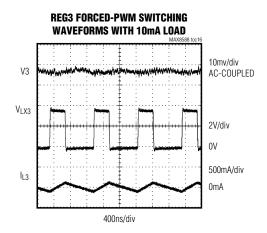

| 14  | PWM3  | Force V3 to PWM at All Loads. Connect PWM3 to GND for normal operation (skip mode at light loads). Drive or connect high for forced-PWM operation at all loads for V3 only.                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 15  | LBO   | Low-Battery Output. Open-drain output that goes low when IN is below the threshold set by LBI.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Dual Mode is a trademark of Maxim Integrated Products, Inc.

#### \_Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                     |

|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16  | PV2  | REG2 Power Input. Bypass to PG2 with a 4.7µF or greater low-ESR capacitor. PV1, PV2, PV3, and IN must connect together externally.                                                                                                                           |

| 17  | LX2  | REG2 Switching Node. Connects to REG2 inductor.                                                                                                                                                                                                              |

| 18  | PG2  | REG2 Power Ground. Connect directly to a power-ground plane. Connect PG1, PG2, PG3, and GND together at a single point as close to the IC as possible.                                                                                                       |

| 19  | IN   | Main Battery Input. This input provides power to the IC.                                                                                                                                                                                                     |

| 20  | RAMP | V3 Ramp-Rate Control. A capacitor connected from RAMP to GND sets the rate-of-change when V3 is changed. The output impedance of RAMP is $100k\Omega$ . FB3 regulates to $1.28 \times V_{RAMP}$ .                                                            |

| 21  | GND  | Analog Ground                                                                                                                                                                                                                                                |

| 22  | REF  | Reference Output. Output of the 1.25V reference. Bypass to GND with a 0.1µF or greater capacitor.                                                                                                                                                            |

| 23  | BYP  | Low-Noise LDO Bypass. Low-noise bypass pin for V4 LDO. Connect a 0.01µF capacitor from BYP to GND.                                                                                                                                                           |

| 24  | DBO  | Dead or Missing Battery Output. DBO is an open-drain output that goes low when IN is below the threshold set by DBI. DBO does not deactivate any regulator outputs. DBO is expected to connect to nBATT_FAULT on Intel CPUs.                                 |

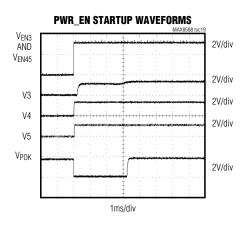

| 25  | ON2  | On/Off Input for REG2. Drive high to turn on. When enabled, the REG2 output soft-starts. ON2 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. It is expected that ON1, ON2, and ON6 are connected to SYS_EN. |

| 26  | ON4  | On/Off Input for REG4. Drive high to turn on. When enabled, the REG4 output activates. ON4 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. It is expected that ON4 is connected to PWR_EN.                  |

| 27  | V4   | Also Known as VCC_PLL. 1.3V, 35mA linear-regulator output for PLL. Regulator input is IN45.                                                                                                                                                                  |

| 28  | IN45 | Power Input to V4 and V5 LDOs. Typically connected to V2, but can also connect to IN or another voltage from 2.5V to VIN.                                                                                                                                    |

| 29  | V5   | Also Known as VCC_SRAM. 1.1V, 35mA linear-regulator output for CPU SRAM. Regulator input is IN45.                                                                                                                                                            |

| 30  | ON5  | On/Off Input for REG5. Drive high to turn on. When enabled, the MAX8588 soft-starts the REG5 output. ON5 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. It is expected that ON5 is connected to PWR_EN.    |

| 31  | PG3  | REG3 Power Ground. Connect directly to a power-ground plane. Connect PG1, PG2, PG3, and GND together at a single point as close to the IC as possible.                                                                                                       |

| 32  | LX3  | REG3 Switching Node. Connects to the REG3 inductor.                                                                                                                                                                                                          |

| 33  | PV3  | REG3 Power Input. Bypass to PG3 with a 4.7µF or greater low-ESR ceramic capacitor. PV1, PV2, PV3, and IN must connect together externally.                                                                                                                   |

| 34  | ON3  | On/Off Input for REG3 (Core). Drive high to turn on. When enabled, the REG3 output ramps up. ON3 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. It is expected that ON3 is driven from CPU SYS_EN.         |

#### \_\_\_\_\_Pin Description (continued)

| PIN | NAME | FUNCTION                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 35  | SRAD | Serial Address Bit. SRAD allows the serial address to be changed in case it conflicts with another serial device. If SRAD = GND, A1 = 0. If SRAD = IN, A1 = 1.                                                                                                                                                 |  |  |  |  |

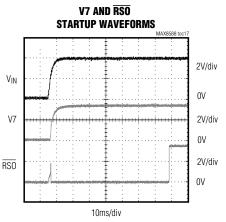

| 36  | RSO  | Open-Drain Reset Output. Deasserts when V7 exceeds 2.55V (typ rising). Has 65ms delay before release. RSO is expected to connect to nRESET on the CPU.                                                                                                                                                         |  |  |  |  |

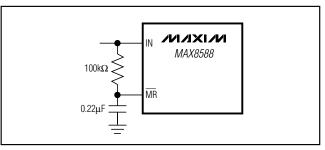

| 37  | MR   | Manual Reset Input. A low input at $\overline{\text{MR}}$ causes the $\overline{\text{RSO}}$ output to go low and also resets the V3 output to its default 1.3V setting. $\overline{\text{MR}}$ impacts no other functions.                                                                                    |  |  |  |  |

| 38  | CC3  | REG 3 Compensation Node. Connect a series resistor and capacitor from CC3 to GND to compensate the regulation loop. See the <i>Compensation and Stability</i> section.                                                                                                                                         |  |  |  |  |

| 39  | FB3  | REG3 Feedback-Sense Input. Connect directly to the REG3 output voltage. Output voltage is set by the serial interface.                                                                                                                                                                                         |  |  |  |  |

| 40  | ON6  | On/Off Input for REG6. Drive high to turn on. When enabled, the REG6 output activates. ON6 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. It is expected that ON1, ON2, and ON6 are connected to SYS_EN.                                                     |  |  |  |  |

| 41  | V6   | Also known as VCC_USIM. Linear-regulator output. This voltage is programmable through the I <sup>2</sup> C interf 0V, 1.8V, 2.5V, or 3.0V. The default voltage is 0V. REG6 is activated when ON6 is high.                                                                                                      |  |  |  |  |

| 42  | IN6  | Power Input to the V6 LDO. Typically connected to V1, but can also connect to IN.                                                                                                                                                                                                                              |  |  |  |  |

| 43  | PG1  | REG1 Power Ground. Connect directly to a power-ground plane. Connect PG1, PG2, PG3, and GND together at a single point as close to the IC as possible.                                                                                                                                                         |  |  |  |  |

| 44  | LX1  | REG1 Switching Node. Connects to the REG1 inductor.                                                                                                                                                                                                                                                            |  |  |  |  |

| 45  | PV1  | REG1 Power Input. Bypass to PG2 with a 4.7µF or greater low-ESR ceramic capacitor. PV1, PV2, PV3, and IN must connect together externally.                                                                                                                                                                     |  |  |  |  |

| 46  | ON1  | On/Off Input for REG1. Drive high to turn on REG1. When enabled, the REG1 output soft-starts. ON1 has hysteresis so an RC can be used to implement manual sequencing with respect to other inputs. It is expected that ON1, ON2, and ON6 connect to SYS_EN.                                                    |  |  |  |  |

| 47  | SLP  | Sleep Input. $\overline{\text{SLP}}$ selects which regulators ON1 and ON2 turn on. $\overline{\text{SLP}}$ = high is normal operation (ON1 and ON2 are the enables for the V1 and V2 DC-DC converters). $\overline{\text{SLP}}$ = low is sleep operation (ON1 and ON2 are the enables for the V1 and V2 LDOs). |  |  |  |  |

| 48  | DBI  | Dual-Mode, Dead-Battery Input. Connect DBI to IN to set the dead-battery falling threshold to 3.15V (no resistors needed). Connect DBI to a resistor-divider for an adjustable DBI threshold.                                                                                                                  |  |  |  |  |

| EP  | EP   | Exposed Metal Pad. Connect the exposed pad to ground. Connecting the exposed pad to ground does not remove the requirement for proper ground connections to the appropriate ground pins.                                                                                                                       |  |  |  |  |

Figure 1. MAX8588 Functional Diagram

M/X/M

**MAX8588**

#### **Detailed Description**

The MAX8588 power-management IC is optimized for devices using Intel X-Scale microprocessors, including third-generation smart cell phones, PDAs, internet appliances, and other portable devices requiring substantial computing and multimedia capability at low power. The MAX8588 complies with Intel Processor Power specifications.

The IC integrates seven high-performance, low-operating-current power supplies along with supervisory and management functions. Regulator outputs include three step-down DC-DC outputs (V1, V2, and V3), three linear regulators (V4, V5, and V6), and one always-on output, V7 (Intel VCC\_BATT). The V1 step-down DC-DC converter provides 3.3V or adjustable output voltage for I/O and peripherals. The V2 step-down DC-DC converter is preset for 3.3V or 2.5V. V2 can also be adjusted with external resistors on all parts. The V3 step-down DC-DC converter provides a serial-programmed output for powering microprocessor cores. The three linear regulators (V4, V5, and V6) provide power for PLL, SRAM, and USIM.

To minimize sleep-state quiescent current, V1 and V2 have bypass "sleep" LDOs that can be activated to minimize battery drain when output current is very low. Other functions include separate on/off control for all DC-DC converters, low-battery and dead-battery detection, a power-OK output, a backup-battery input, and a two-wire serial interface.

All DC-DC outputs use fast, 1MHz PWM switching and small external components. They operate with fixed-frequency PWM control and automatically switch from PWM to skip-mode operation at light loads to reduce operating current and extend battery life. The V3 core output is capable of forced-PWM operation at all loads. The 2.6V to 5.5V input voltage range allows 1-cell Li+, 3-cell NiMH, or a regulated 5V input.

The following power-supply descriptions include the Intel terms for the various voltages in parenthesis. For example, the V1 output is referred to as VCC\_IO in Intel documentation. See Figure 1.

#### V1 and V2 (VCC\_IO, VCC\_MEM) Step-Down DC-DC Converters

V1 is a 1MHz current-mode step-down converter. The V1 output voltage can be preset to 3.3V or adjusted using a resistor voltage-divider. V1 supplies loads up to 1300mA.

V2 is also a 1MHz current-mode step-down converter. The V2 step-down DC-DC converter is preset for 3.3V or 2.5V. V2 can also be adjusted with external resistors on all parts. V2 supplies loads up to 900mA.

Under moderate to heavy loading, the converters operate in a low-noise PWM mode with constant frequency and modulated pulse width. Switching harmonics generated by fixed-frequency operation are consistent and easily filtered. Efficiency is enhanced under light loading (<30mA typ), by assuming an Idle Mode<sup>™</sup> during which the converter switches only as needed to service the load.

#### Synchronous Rectification

Internal n-channel synchronous rectifiers eliminate the need for external Schottky diodes and improve efficiency. The synchronous rectifier turns on during the second half of each cycle (off-time). During this time, the voltage across the inductor is reversed, and the inductor current falls. In normal operation (not forced PWM), the synchronous rectifier turns off at the end of the cycle (at which time another on-time begins) or when the inductor current approaches zero.

#### 100% Duty-Cycle Operation

If the inductor current does not rise sufficiently to supply the load during the on-time, the switch remains on, allowing operation up to 100% duty cycle. This allows the output voltage to maintain regulation while the input voltage approaches the regulation voltage. Dropout voltage is approximately 180mV for an 800mA load on V1 and 220mV for an 800mA load on V2. During dropout, the high-side p-channel MOSFET turns on, and the controller enters a low-current-consumption mode. The device remains in this mode until the regulator channel is no longer in dropout.

#### Sleep LDOs

In addition to the high-efficiency step-down converters, V1 and V2 can also be supplied with low-quiescent current, low-dropout (LDO) linear regulators that can be used in sleep mode or at any time when the load current is very low. The sleep LDOs can source up to 35mA. To enable the sleep LDOs, drive SLP low. When SLP is high, the switching step-down converters are active. The output voltage of the sleep LDOs is set to be the same as the switching step-down converters as described in the *Setting the Output Voltages* section. SLPIN is the input to the V1 and V2 sleep LDOs and must connect to IN.

Idle Mode is a trademark of Maxim Integrated Products, Inc.

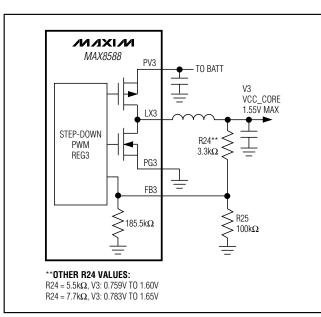

#### V3 (VCC\_CORE) Step-Down DC-DC Converter

V3 is a 1MHz current-mode step-down converter. It supplies loads up to 500mA.

The V3 output is set by the I<sup>2</sup>C serial interface to between 0.7V and 1.475V in 25mV increments. The default output voltage on power-up, and after a reset, is 1.3V. See the *Serial Interface* section for programming details. See the *Applications Information* for instructions on how to increase the V3 output voltage.

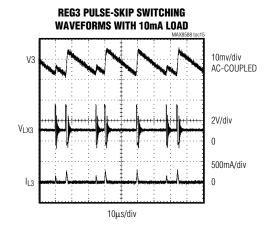

#### Forced PWM on REG3

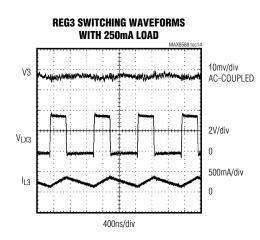

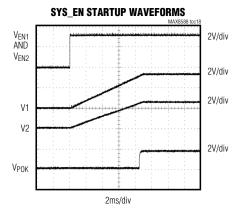

Under moderate to heavy loading, the V3 always operates in a low-noise PWM mode with constant frequency and modulated pulse width. Switching harmonics generated by fixed-frequency operation are consistent and easily filtered.