# 24-Bit Capacitance-to-Digital Converter with Temperature Sensor

**AD7747**

#### **FEATURES**

Capacitance-to-digital converter

New standard in single chip solutions

Interfaces to single or differential grounded sensors

Resolution down to 20 aF (that is, up to 19.5-bit ENOB)

Accuracy: 10 fF Linearity: 0.01%

Common-mode (not changing) capacitance up to 17 pF

Full-scale (changing) capacitance range ±8 pF

Update rate: 5 Hz to 45 Hz

Simultaneous 50 Hz and 60 Hz rejection at 8.1 Hz update

Active shield for shielding sensor connection

Temperature sensor on-chip

Resolution: 0.1°C, accuracy: ±2°C

Voltage input channel Internal clock oscillator

2-wire serial interface (I<sup>2</sup>C® compatible)

Power

2.7 V to 5.25 V single-supply operation

0.7 mA current consumption

Operating temperature: -40°C to +125°C

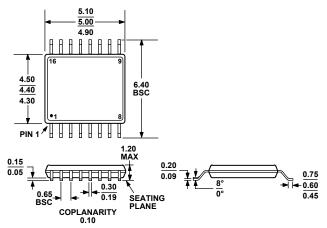

16-lead TSSOP package

### **APPLICATIONS**

Automotive, industrial, and medical systems for

**Pressure measurement**

**Position sensing**

**Proximity sensing**

Level sensing

Flow metering

Impurity detection

#### **GENERAL DESCRIPTION**

The AD7747 is a high-resolution,  $\Sigma$ - $\Delta$  capacitance-to-digital converter (CDC). The capacitance to be measured is connected directly to the device inputs. The architecture features inherent high resolution (24-bit no missing codes, up to 19.5-bit effective resolution), high linearity ( $\pm$ 0.01%), and high accuracy ( $\pm$ 10 fF factory calibrated). The AD7747 capacitance input range is  $\pm$ 8 pF (changing), and it can accept up to 17 pF common-mode capacitance (not changing), which can be balanced by a programmable on-chip digital-to-capacitance converter (CAPDAC).

The AD7747 is designed for single-ended or differential capacitive sensors with one plate connected to ground. For floating (not grounded) capacitive sensors, the AD7745 or AD7746 are recommended.

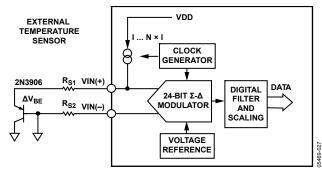

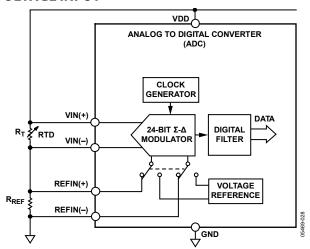

The part has an on-chip temperature sensor with a resolution of  $0.1^{\circ}$ C and accuracy of  $\pm 2^{\circ}$ C. The on-chip voltage reference and the on-chip clock generator eliminate the need for any external components in capacitive sensor applications. The part has a standard voltage input that, together with the differential reference input, allows easy interface to an external temperature sensor, such as an RTD, thermistor, or diode.

The AD7747 has a 2-wire,  $I^2C$ -compatible serial interface. The part can operate with a single power supply of 2.7 V to 5.25 V. It is specified over the automotive temperature range of  $-40^{\circ}C$  to  $+125^{\circ}C$  and is housed in a 16-lead TSSOP package.

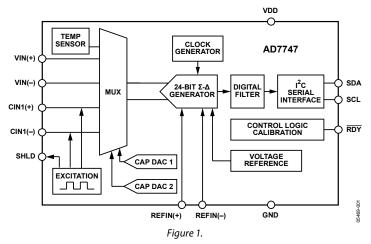

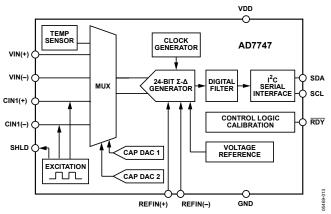

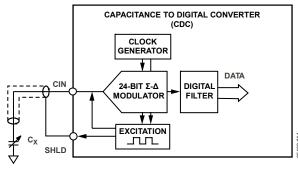

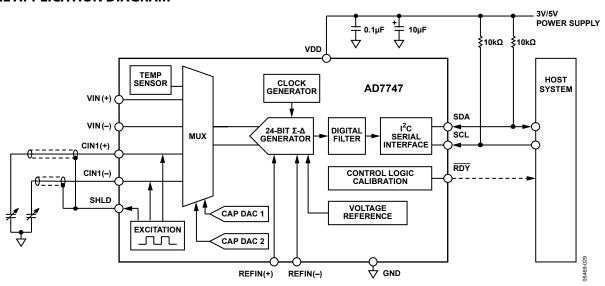

#### **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| Specifications                              | 3  |

| Timing Specifications                       | 5  |

| Absolute Maximum Ratings                    | 6  |

| ESD Caution                                 | 6  |

| Pin Configuration and Function Descriptions | 7  |

| Typical Performance Characteristics         | 8  |

| Output Noise and Resolution Specifications  | 11 |

| Serial Interface                            | 12 |

| Read Operation                              | 12 |

| Write Operation                             | 12 |

| AD7747 Reset                                | 13 |

| General Call                                | 13 |

| Register Descriptions                       | 14 |

| Status Register                             | 15 |

| Cap Data Register                           | 15 |

| VT Data Register                            | 15 |

| Cap Setup Register                          | 16 |

| VT Setup Register                           | 16 |

| EXC Setup Register                          | 17 |

| Configuration Register                      | 18 |

| Cap DAC A Register                    |

|---------------------------------------|

| Cap DAC B Register19                  |

| Cap Offset Calibration Register       |

| Cap Gain Calibration Register20       |

| Volt Gain Calibration Register        |

| Circuit Description                   |

| Overview                              |

| Capacitance-to-Digital Converter21    |

| Active AC Shield Concept              |

| CAPDAC21                              |

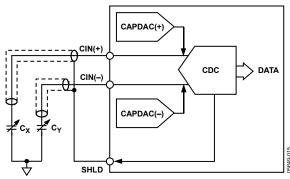

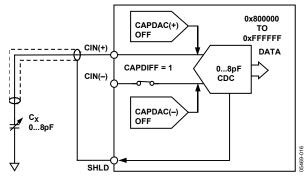

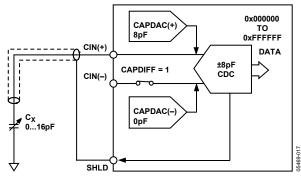

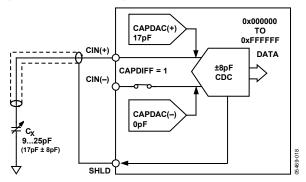

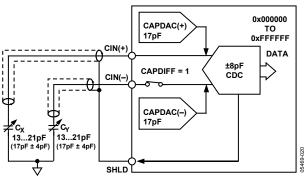

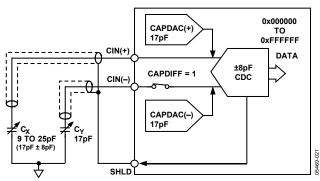

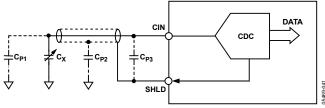

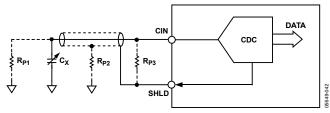

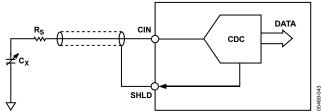

| Single-Ended Capacitive Configuration |

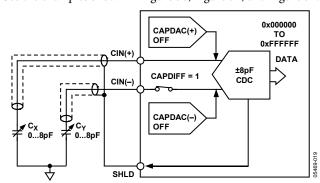

| Differential Capacitive Configuration |

| Parasitic Capacitance                 |

| Parasitic Resistance                  |

| Parasitic Serial Resistance           |

| Capacitive Gain Calibration           |

| Capacitive System Offset Calibration  |

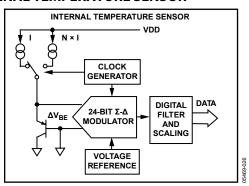

| Internal Temperature Sensor           |

| External Temperature Sensor           |

| Voltage Input                         |

| V <sub>DD</sub> Monitor               |

| Typical Application Diagram26         |

| Outline Dimensions                    |

| Ordering Guide                        |

### **REVISION HISTORY**

1/07—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_{DD}$  = 2.7 V to 3.6 V or 4.75 V to 5.25 V; GND = 0 V; EXC =  $\pm V_{DD} \times 3/8$ ;  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

Table 1.

| Parameter                                      | Min        | Тур                     | Max             | Unit                  | Test Conditions/Comments                                                |

|------------------------------------------------|------------|-------------------------|-----------------|-----------------------|-------------------------------------------------------------------------|

| CAPACITIVE INPUT                               |            |                         |                 |                       |                                                                         |

| Conversion Input Range                         |            | ±8.192                  |                 | pF <sup>1</sup>       | Factory calibrated                                                      |

| Integral Nonlinearity (INL) <sup>2</sup>       |            |                         | ±0.01           | % of FSR <sup>1</sup> |                                                                         |

| No Missing Codes <sup>2</sup>                  | 24         |                         |                 | Bit                   | Conversion time ≥ 124 ms                                                |

| Resolution, p-p                                |            | 16.5                    |                 | Bit                   | Conversion time 124 ms, see Table 5                                     |

| Resolution Effective                           |            | 19.1                    |                 | Bit                   | Conversion time 124 ms, see Table 5                                     |

| Output Noise, rms                              |            | 11.0                    |                 | aF/√Hz                | Conversion time 124 ms, see Table 5                                     |

| Absolute Error <sup>3</sup>                    |            |                         | ±10             | fF <sup>1</sup>       | $25^{\circ}$ C, $V_{DD} = 5$ V, after offset calibration                |

| Offset Error <sup>4,5</sup>                    |            |                         | 32              | aF¹                   | After system offset calibration, excluding effect of noise <sup>4</sup> |

| System Offset Calibration Range⁵               |            |                         | ±1              | pF                    |                                                                         |

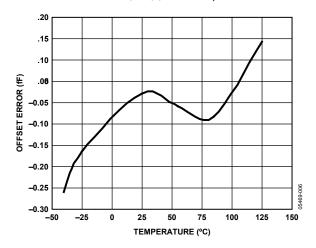

| Offset Deviation over Temperature <sup>2</sup> |            | 0.4                     |                 | fF                    | See Figure 6                                                            |

| Gain Error <sup>6</sup>                        |            | 0.02                    | 0.11            | % of FS <sup>1</sup>  | 25°C, V <sub>DD</sub> = 5 V                                             |

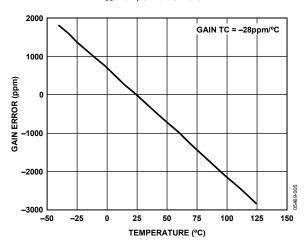

| Gain Drift vs. Temperature <sup>2</sup>        | -23        | -26                     | -29             | ppm of FS/°C          | 25 5, 125 5 1                                                           |

| Power Supply Rejection <sup>2</sup>            |            | 0.5                     | 4               | fF/V                  |                                                                         |

| Normal Mode Rejection <sup>5</sup>             |            | 72                      | •               | dB                    | 50 Hz $\pm$ 1%, conversion time 124 ms                                  |

|                                                |            | 60                      |                 | dB                    | $60 \text{ Hz} \pm 1\%$ , conversion time 124 ms                        |

| CAPDAC                                         |            |                         |                 | 0.0                   | 001122170, 001170131011 111110 1211113                                  |

| Full Range                                     | 17         | 21                      |                 | pF                    | 6-bit CAPDAC                                                            |

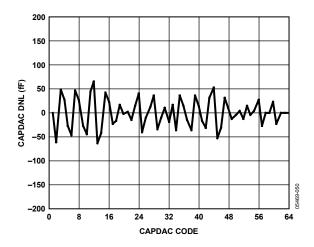

| Differential Nonlinearity (DNL)                | ''         | 0.3                     |                 | LSB                   | See Figure 16                                                           |

| Drift vs. Temperature <sup>2</sup>             |            | 26                      |                 | ppm of FS/°C          | See Figure 10                                                           |

| EXCITATION                                     |            |                         |                 | рриготта, с           |                                                                         |

| Frequency                                      |            | 16                      |                 | kHz                   |                                                                         |

| AC Voltage Across Capacitance                  |            | $\pm V_{DD} \times 3/8$ |                 | V                     | To be configured via digital interface                                  |

| Average DC Voltage Across Capacitance          |            | V <sub>DD</sub> /2      |                 | ľv                    | 10 be configured via digital interface                                  |

| TEMPERATURE SENSOR <sup>7</sup>                |            | V DD/ Z                 |                 | •                     | V <sub>REF</sub> internal                                               |

| Resolution                                     |            | 0.1                     |                 | °C                    | VREF IIICCITIAI                                                         |

| Error <sup>2</sup>                             |            | ±0.5                    | ±2              | ℃                     | Internal temperature sensor                                             |

| LITOI                                          |            | ±0.5<br>±2              | 12              | ℃                     | External sensing diode8                                                 |

| VOLTAGE INPUT <sup>7</sup>                     |            |                         |                 |                       | $V_{REF}$ internal or $V_{REF} = 2.5 \text{ V}$                         |

| Differential VIN Voltage Range                 |            | $\pm V_{REF}$           |                 | V                     | VREF IIILEITIAI OI VREF — 2.3 V                                         |

| Absolute VIN Voltage <sup>2</sup>              | GND - 0.03 | <b>±V</b> REF           | $V_{DD} + 0.03$ | V                     |                                                                         |

|                                                | GND - 0.03 | L-3                     | ±15             | _                     |                                                                         |

| Integral Nonlinearity (INL)                    | 24         | ±3                      | ±15             | ppm of FS             | Conversion time - 122.1 ms                                              |

| No Missing Codes <sup>2</sup>                  | 24         | 1.0                     |                 | Bit                   | Conversion time = 122.1 ms                                              |

| Resolution, p-p                                |            | 16                      |                 | Bits                  | Conversion time = 62 ms, see Table 6 and Table 7                        |

| Output Noise                                   |            | 3                       |                 | μV rms                | Conversion time = 62 ms, see Table 6 and Table 7                        |

| Offset Error                                   |            | ±3                      |                 | μV                    |                                                                         |

| Offset Drift vs. Temperature                   |            | 15                      |                 | nV/°C                 |                                                                         |

| Full-Scale Error <sup>2,9</sup>                |            | 0.025                   | 0.1             | % of FS               |                                                                         |

| Full-Scale Drift vs. Temperature               |            | 5                       |                 | ppm of FS/°C          | Internal reference                                                      |

|                                                |            | 0.5                     |                 | ppm of FS/°C          | External reference                                                      |

| Average VIN Input Current                      |            | 300                     |                 | nA/V                  |                                                                         |

| Analog VIN Input Current Drift                 |            | ±50                     |                 | pA/V/°C               |                                                                         |

| Power Supply Rejection                         |            | 80                      |                 | dB                    | Internal reference, V <sub>IN</sub> = V <sub>REF</sub> /2               |

|                                                |            | 90                      |                 | dB                    | External reference, V <sub>IN</sub> = V <sub>REF</sub> /2               |

| Parameter                                | Min            | Тур  | Max             | Unit    | Test Conditions/Comments                             |

|------------------------------------------|----------------|------|-----------------|---------|------------------------------------------------------|

| Normal Mode Rejection⁵                   |                | 75   |                 | dB      | $50 \text{ Hz} \pm 1\%$ , conversion time = 122.1 ms |

|                                          |                | 50   |                 | dB      | $60 \text{ Hz} \pm 1\%$ , conversion time = 122.1 ms |

| Common-Mode Rejection <sup>2</sup>       |                | 95   |                 | dB      | $V_{IN} = 1 V$                                       |

| INTERNAL VOLTAGE REFERENCE               |                |      |                 |         |                                                      |

| Voltage                                  | 1.169          | 1.17 | 1.171           | V       | T <sub>A</sub> = 25°C                                |

| Drift vs. Temperature                    |                | 5    |                 | ppm/°C  |                                                      |

| EXTERNAL VOLTAGE REFERENCE INPUT         |                |      |                 |         |                                                      |

| Differential REFIN Voltage <sup>2</sup>  | 0.1            | 2.5  | $V_{DD}$        | V       |                                                      |

| Absolute REFIN Voltage <sup>2</sup>      | GND - 0.03     |      | $V_{DD} + 0.03$ | V       |                                                      |

| Average REFIN Input Current              |                | 400  |                 | nA/V    |                                                      |

| Average REFIN Input Current Drift        |                | ±50  |                 | pA/V/°C |                                                      |

| Common-Mode Rejection                    |                | 80   |                 | dB      |                                                      |

| SERIAL INTERFACE LOGIC INPUTS (SCL, SDA) |                |      |                 |         |                                                      |

| V <sub>H</sub> Input High Voltage        | 2.1            |      |                 | V       |                                                      |

| V <sub>IL</sub> Input Low Voltage        |                |      | 0.8             | V       |                                                      |

| Hysteresis                               |                | 150  |                 | mV      |                                                      |

| Input Leakage Current (SCL)              |                | ±0.1 | ±1              | μΑ      |                                                      |

| OPEN-DRAIN OUTPUT (SDA)                  |                |      |                 |         |                                                      |

| Vo∟ Output Low Voltage                   |                |      | 0.4             | V       | $I_{SINK} = -6.0 \text{ mA}$                         |

| Iон Output High Leakage Current          |                | 0.1  | 1               | μΑ      | $V_{OUT} = V_{DD}$                                   |

| LOGIC OUTPUT (RDY)                       |                |      |                 |         |                                                      |

| V <sub>OL</sub> Output Low Voltage       |                |      | 0.4             | V       | $I_{SINK} = 1.6 \text{ mA}, V_{DD} = 5 \text{ V}$    |

| V <sub>OH</sub> Output High Voltage      | 4.0            |      |                 | V       | $I_{SOURCE} = 200  \mu A,  V_{DD} = 5  V$            |

| V <sub>OL</sub> Output Low Voltage       |                |      | 0.4             | V       | $I_{SINK} = 100  \mu A, V_{DD} = 3  V$               |

| V <sub>OH</sub> Output High Voltage      | $V_{DD} - 0.6$ |      |                 | V       | $I_{SOURCE} = 100  \mu A,  V_{DD} = 3  V$            |

| POWER REQUIREMENTS                       |                |      |                 |         |                                                      |

| V <sub>DD</sub> -to-GND Voltage          | 4.75           |      | 5.25            | V       | $V_{DD} = 5 \text{ V, nominal}$                      |

| -                                        | 2.7            |      | 3.6             | V       | $V_{DD} = 3.3 \text{ V, nominal}$                    |

| I <sub>DD</sub> Current                  |                |      | 850             | μΑ      | Digital inputs equal to VDD or GND                   |

|                                          |                | 750  |                 | μA      | $V_{DD} = 5 \text{ V}$                               |

|                                          |                | 700  |                 | μA      | $V_{DD} = 3.3 \text{ V}$                             |

| IDD Current Power-Down Mode              |                | 0.5  | 2               | μA      | Digital inputs equal to V <sub>DD</sub> or GND       |

<sup>&</sup>lt;sup>1</sup> Capacitance units: 1 pF =  $10^{-12}$  F; 1 fF =  $10^{-15}$  F; 1 aF =  $10^{-18}$  F. Full scale (FS) = 8.192 pF; full-scale range (FSR) =  $\pm 8.192$  pF.

<sup>&</sup>lt;sup>2</sup> Specification is not production tested, but is supported by characterization data at initial product release.

<sup>&</sup>lt;sup>3</sup> Factory calibrated. The absolute error includes factory gain calibration error, integral nonlinearity error, and offset error after system offset calibration, all at 25°C. At different temperatures, compensation for gain drift over temperature is required.

<sup>&</sup>lt;sup>4</sup> The capacitive input offset can be eliminated using a system offset calibration. The accuracy of the system offset calibration is limited by the offset calibration register LSB size (32 aF) or by converter + system p-p noise during the system capacitive offset calibration, whichever is greater. To minimize the effect of the converter + system noise, longer conversion times should be used for system capacitive offset calibration. The system capacitance offset calibration range is ±1 pF; the larger offset can be removed using CAPDACs.

<sup>&</sup>lt;sup>5</sup> Specification is not production tested, but guaranteed by design.

<sup>&</sup>lt;sup>6</sup> The gain error is factory calibrated at 25°C. At different temperatures, compensation for gain drift over temperature is required.

<sup>&</sup>lt;sup>7</sup> The VTCHOP bit in the VT SETUP register must be set to 1 for the specified temperature sensor and voltage input performance.

$<sup>^8</sup>$  Using an external temperature sensing diode 2N3906, with nonideality factor  $n_f = 1.008$ , connected as in Figure 37, with total serial resistance <100  $\Omega$ .

<sup>&</sup>lt;sup>9</sup> Full-scale error applies to both positive and negative full scale.

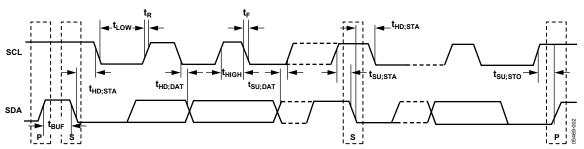

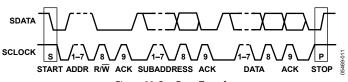

### **TIMING SPECIFICATIONS**

$V_{DD} = 2.7 \text{ V}$  to 3.6 V, or 4.75 V to 5.25 V; GND = 0 V; Input Logic 0 = 0 V; Input Logic 1 =  $V_{DD}$ ;  $-40^{\circ}$ C to  $+125^{\circ}$ C, unless otherwise noted.

Table 2.

| Parameter                                                           | Min | Тур | Max | Unit | Test Conditions/Comments                        |

|---------------------------------------------------------------------|-----|-----|-----|------|-------------------------------------------------|

| SERIAL INTERFACE <sup>1, 2</sup>                                    |     |     |     |      | See Figure 2                                    |

| SCL Frequency                                                       | 0   |     | 400 | kHz  |                                                 |

| SCL High Pulse Width, t <sub>HIGH</sub>                             | 0.6 |     |     | μs   |                                                 |

| SCL Low Pulse Width, t <sub>LOW</sub>                               | 1.3 |     |     | μs   |                                                 |

| SCL, SDA Rise Time, t <sub>R</sub>                                  |     |     | 0.3 | μs   |                                                 |

| SCL, SDA Fall Time, t <sub>F</sub>                                  |     |     | 0.3 | μs   |                                                 |

| Hold Time (Start Condition), thD;STA                                | 0.6 |     |     | μs   | After this period, the first clock is generated |

| Setup Time (Start Condition), tsu;sta                               | 0.6 |     |     | μs   | Relevant for repeated start condition           |

| Data Setup Time, t <sub>SU;DAT</sub>                                | 0.1 |     |     | μs   |                                                 |

| Setup Time (Stop Condition), tsu;sto                                | 0.6 |     |     | μs   |                                                 |

| Data Hold Time, t <sub>HD;DAT</sub> (Master)                        | 0   |     |     | μs   |                                                 |

| Bus-Free Time (Between Stop and Start Condition, t <sub>BUF</sub> ) | 1.3 |     |     | μs   |                                                 |

<sup>&</sup>lt;sup>1</sup> Sample tested during initial release to ensure compliance. <sup>2</sup> All input signals are specified with input rise/fall times = 3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs. Output load = 10 pF.

Figure 2. Serial Interface Timing Diagram

# **ABSOLUTE MAXIMUM RATINGS**

$T_A = 25$ °C, unless otherwise noted.

#### Table 3.

| Parameter                                              | Rating                                     |

|--------------------------------------------------------|--------------------------------------------|

| Positive Supply Voltage VDD to GND                     | -0.3 V to +6.5 V                           |

| Voltage on any Input or Output Pin to<br>GND           | $-0.3 \text{ V to V}_{DD} + 0.3 \text{ V}$ |

| ESD Rating (ESD Association Human Body<br>Model, S5.1) | 2000 V                                     |

| Operating Temperature Range                            | -40°C to +125°C                            |

| Storage Temperature Range                              | −65°C to +150°C                            |

| Junction Temperature                                   | 150°C                                      |

| TSSOP Package θ <sub>JA</sub>                          | 128°C/W                                    |

| (Thermal Impedance-to-Air)                             |                                            |

| TSSOP Package θ <sub>JC</sub>                          | 14°C/W                                     |

| (Thermal Impedance-to-Case)                            |                                            |

| Peak Reflow Soldering Temperature                      |                                            |

| Pb Free (20 sec to 40 sec)                             | 260°C                                      |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

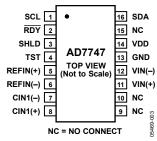

# PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

## **Table 4. Pin Function Descriptions**

| Pin No. | Mnemonic              | Description                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | SCL                   | Serial Interface Clock Input. Connects to the master clock line. Requires pull-up resistor if not already provided in the system.                                                                                                                                                                                                                        |

| 2       | RDY                   | Logic Output. A falling edge on this output indicates that a conversion on enabled channel(s) has been finished and the new data is available. Alternatively, the status register can be read via the 2-wire serial interface and the relevant bit(s) decoded to query the finished conversion. If not used, this pin should be left as an open circuit. |

| 3       | SHLD                  | Capacitive Input Active AC Shielding. To eliminate the CIN parasitic capacitance to ground, the SHLD signal can be used for shielding the connection between the sensor and CIN. If not used, this pin should be left as an open circuit.                                                                                                                |

| 4       | TST                   | This pin must be left as an open circuit for proper operation.                                                                                                                                                                                                                                                                                           |

| 5, 6    | REFIN(+),<br>REFIN(-) | Differential Voltage Reference Input for the Voltage Channel (ADC). Alternatively, the on-chip internal reference can be used for the voltage channel. These reference input pins are not used for conversion on capacitive channel(s) (CDC). If not used, these pins can be left as an open circuit or connected to GND.                                |

| 7       | CIN1(-)               | CDC Negative Capacitive Input. The measured capacitance is connected between the CIN1(–) pin and GND. If not used, this pin should be left as an open circuit.                                                                                                                                                                                           |

| 8       | CIN1(+)               | CDC Positive Capacitive Input. The measured capacitance is connected between the CIN1(+) pin and GND. If not used, this pin should be left as an open circuit.                                                                                                                                                                                           |

| 9, 10   | NC                    | Not Connected. These pins should be left as an open circuit.                                                                                                                                                                                                                                                                                             |

| 11, 12  | VIN(+), VIN(-)        | Differential Voltage Input for the Voltage Channel (ADC). These pins are also used to connect an external temperature sensing diode. If not used, these pins can be left as an open circuit or connected to GND.                                                                                                                                         |

| 13      | GND                   | Ground Pin.                                                                                                                                                                                                                                                                                                                                              |

| 14      | VDD                   | Power Supply Voltage. This pin should be decoupled to GND, using a low impedance capacitor, for example in combination with a 10 µF tantalum and a 0.1 µF multilayer ceramic.                                                                                                                                                                            |

| 15      | NC                    | Not Connected. This pin should be left as an open circuit.                                                                                                                                                                                                                                                                                               |

| 16      | SDA                   | Serial Interface Bidirectional Data. Connects to the master data line. Requires a pull-up resistor if not provided elsewhere in the system.                                                                                                                                                                                                              |

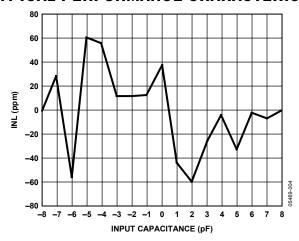

# TYPICAL PERFORMANCE CHARACTERISTICS

Figure 4. Capacitance Input Integral Nonlinearity;  $V_{DD} = 5 V$ , CAPDAC = 0x3F

Figure 5. Capacitance Input Gain Drift vs. Temperature;  $V_{DD} = 5 V$ , CIN(+) to GND = 8 pF

Figure 6. Capacitance Input Offset Drift vs. Temperature;  $V_{DD} = 5 V$ , CIN(+) Open

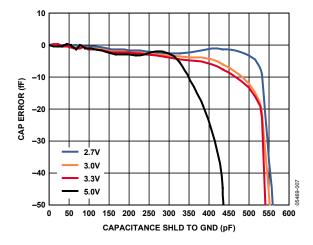

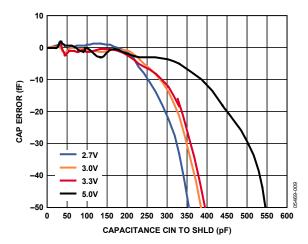

Figure 7. Capacitance Input Error vs. Capacitance Between SHLD and GND; CIN(+) to GND = 8 pF,  $V_{DD} = 2.7$  V, 3 V, 3.3 V, and 5 V

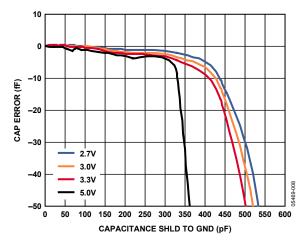

Figure 8. Capacitance Input Error vs. Capacitance Between SHLD and GND; CIN(+) to GND = 25 pF,  $V_{DD} = 2.7$  V, 3 V, 3.3 V, and 5 V

Figure 9. Capacitance Input Error vs. Capacitance Between CIN(+) and SHLD; CIN(+) to GND=8 pF,  $V_{DD}=2.7$  V, 3 V, 3.3 V, and 5V

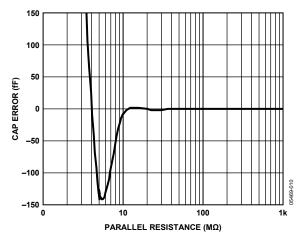

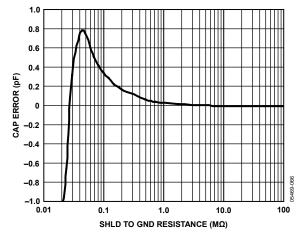

Figure 10. Capacitance Input Error vs. Parallel Resistance; CIN(+) to GND=8 pF,  $V_{DD}=5$  V

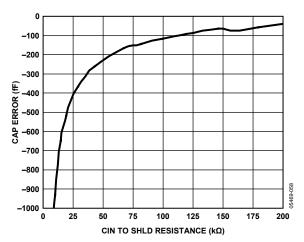

Figure 11. Capacitance Input Error vs. Resistance Between CIN1(+) and SHLD;  $CIN(+) \ to \ GND = 8 \ pF, \ V_{DD} = 5 \ V$

Figure 12. Capacitance Input Error vs. Resistance Between CIN(+) and SHLD; CIN(+) to GND=25 pF,  $V_{DD}=5$  V

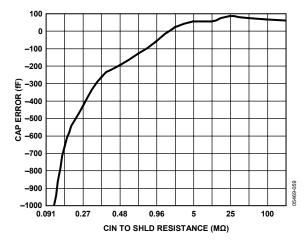

Figure 13. Capacitance Input Error vs. Resistance Between SHLD and GND; CIN(+) to GND = 8 pF;  $V_{DD} = 5$  V

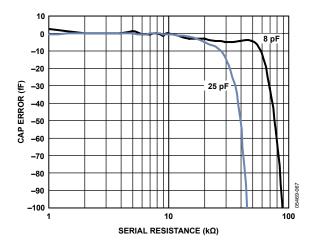

Figure 14. Capacitance Input Error vs. Serial Resistance; CIN(+) to GND = 8 pF and 25pF,  $V_{DD} = 5$  V

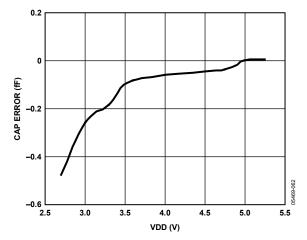

Figure 15. Capacitance Input Power Supply Rejection (PSR); CIN(+) to GND = 8 pF

Figure 16. CAPDAC Differential Nonlinearity (DNL)

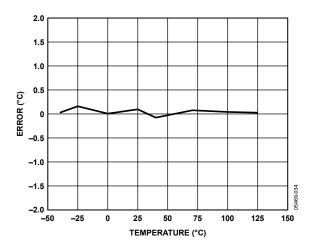

Figure 17. Internal Temperature Sensor Error vs. Temperature

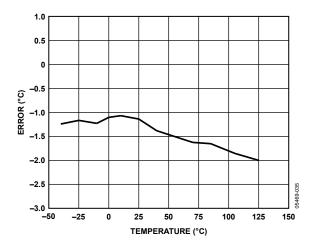

Figure 18. External Temperature Sensor Error vs. Temperature

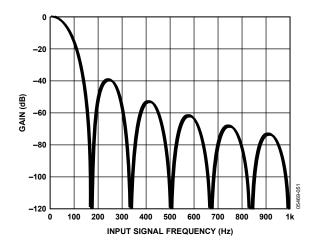

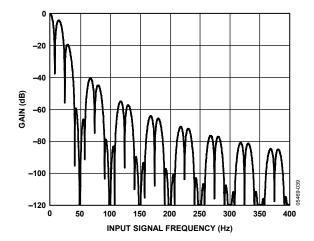

Figure 19. Capacitive Channel Frequency Response; Conversion Time = 22 ms

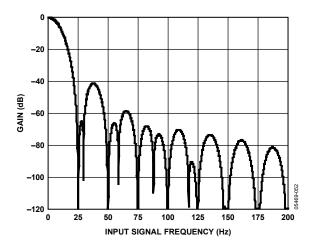

Figure 20. Capacitive Channel Frequency Response; Conversion Time = 124 ms

Figure 21. Voltage Channel Frequency Response; Conversion Time = 122.1 ms

# **OUTPUT NOISE AND RESOLUTION SPECIFICATIONS**

The AD7747 resolution is limited by noise. The noise performance varies with the selected conversion time.

Table 5 shows typical noise performance and resolution for the capacitive channel. These numbers were generated from 1000 data samples acquired in continuous conversion mode, at an excitation of 16 kHz,  $\pm V_{DD} \times 3/8$ , and with all CIN and SHLD pins connected only to the evaluation board (no external capacitors).

Table 6 and Table 7 show typical noise performance and resolution for the voltage channel. These numbers were generated from 1000 data samples acquired in continuous conversion mode with VIN pins shorted to ground.

RMS noise represents the standard deviation and p-p noise represents the difference between minimum and maximum results in the data. Effective resolution is calculated from rms noise, and p-p resolution is calculated from p-p noise.

Table 5. Typical Capacitive Input Noise and Resolution vs. Conversion Time (Bold line represents default setting)

| Conversion<br>Time (ms) | Output Data<br>Rate (Hz) | -3 dB Frequency<br>(Hz) | RMS Noise<br>(aF/√Hz) | RMS<br>Noise (aF) | P-P<br>Noise (aF) | Effective Resolution (Bits) | P-P Resolution<br>(Bits) |

|-------------------------|--------------------------|-------------------------|-----------------------|-------------------|-------------------|-----------------------------|--------------------------|

| 22.0                    | 45.5                     | 43.6                    | 28.8                  | 190               | 821               | 16.4                        | 14.3                     |

| 23.9                    | 41.9                     | 39.5                    | 23.2                  | 146               | 725               | 16.8                        | 14.5                     |

| 40.0                    | 25.0                     | 21.8                    | 11.1                  | 52                | 411               | 18.3                        | 15.3                     |

| 76.0                    | 13.2                     | 10.9                    | 11.2                  | 37                | 262               | 18.7                        | 15.9                     |

| 124.0                   | 8.1                      | 6.9                     | 11.0                  | 29                | 174               | 19.1                        | 16.5                     |

| 154.0                   | 6.5                      | 5.3                     | 10.4                  | 24                | 173               | 19.3                        | 16.5                     |

| 184.0                   | 5.4                      | 4.4                     | 10.0                  | 21                | 141               | 19.6                        | 16.8                     |

| 219.3                   | 4.6                      | 4.0                     | 9.0                   | 18                | 126               | 19.9                        | 17.0                     |

Table 6. Typical Voltage Input Noise and Resolution vs. Conversion Time, Internal Voltage Reference

| Conversion<br>Time (ms) | Output Data<br>Rate (Hz) | –3 dB Frequency<br>(Hz) | RMS Noise<br>(μV) | P-P Noise<br>(μV) | Effective Resolution (Bits) | P-P Resolution<br>(Bits) |

|-------------------------|--------------------------|-------------------------|-------------------|-------------------|-----------------------------|--------------------------|

| 20.1                    | 49.8                     | 26.4                    | 11.4              | 62                | 17.6                        | 15.2                     |

| 32.1                    | 31.2                     | 15.9                    | 7.1               | 42                | 18.3                        | 15.7                     |

| 62.1                    | 16.1                     | 8.0                     | 4.0               | 28                | 19.1                        | 16.3                     |

| 122.1                   | 8.2                      | 4.0                     | 3.0               | 20                | 19.5                        | 16.8                     |

Table 7. Typical Voltage Input Noise and Resolution vs. Conversion Time, External 2.5 V Voltage Reference

| Conversion<br>Time (ms) | Output Data<br>Rate (Hz) | -3 dB Frequency<br>(Hz) | RMS Noise<br>(μV) | P-P Noise<br>(μV) | Effective Resolution (Bits) | P-P Resolution<br>(Bits) |

|-------------------------|--------------------------|-------------------------|-------------------|-------------------|-----------------------------|--------------------------|

| 20.1                    | 49.8                     | 26.4                    | 14.9              | 95                | 18.3                        | 15.6                     |

| 32.1                    | 31.2                     | 15.9                    | 6.3               | 42                | 19.6                        | 16.8                     |

| 62.1                    | 16.1                     | 8.0                     | 3.3               | 22                | 20.5                        | 17.7                     |

| 122.1                   | 8.2                      | 4.0                     | 2.1               | 15                | 21.1                        | 18.3                     |

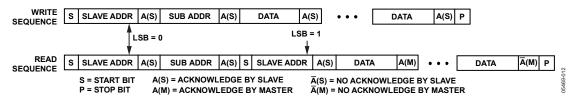

# SERIAL INTERFACE

The AD7747 supports an I<sup>2</sup>C-compatible 2-wire serial interface. The two wires on the I<sup>2</sup>C bus are called SCL (clock) and SDA (data). These two wires carry all addressing, control, and data information one bit at a time over the bus to all connected peripheral devices. The SDA wire carries the data, while the SCL wire synchronizes the sender and receiver during the data transfer. I<sup>2</sup>C devices are classified as either master or slave devices. A device that initiates a data transfer message is called a master, while a device that responds to this message is called a slave.

To control the AD7747 device on the bus, the following protocol must be followed. First, the master initiates a data transfer by establishing a start condition, defined by a high-to-low transition on SDA while SCL remains high. This indicates that the start byte follows. This 8-bit start byte is made up of a 7-bit address plus an R/W bit indicator.

All peripherals connected to the bus respond to the start condition and shift in the next 8 bits (7-bit address + R/W bit). The bits arrive MSB first. The peripheral that recognizes the transmitted address responds by pulling the data line low during the ninth clock pulse. This is known as the acknowledge bit. All other devices withdraw from the bus at this point and maintain an idle condition. An exception to this is the general call address, which is described later in this document. The idle condition is where the device monitors the SDA and SCL lines waiting for the start condition and the correct address byte. The R/W bit determines the direction of the data transfer. A Logic 0 LSB in the start byte means that the master writes information to the addressed peripheral. In this case, the AD7747 becomes a slave receiver. A Logic 1 LSB in the start byte means that the master reads information from the addressed peripheral. In this case, the AD7747 becomes a slave transmitter. In all instances, the AD7747 acts as a standard slave device on the I2C bus.

The start byte address for the AD7747 is 0x90 for a write and 0x91 for a read.

### **READ OPERATION**

When a read is selected in the start byte, the register that is currently addressed by the address pointer is transmitted on to the SDA line by the AD7747. This is then clocked out by the master device and the AD7747 awaits an acknowledge from the master.

If an acknowledge is received from the master, the address auto-incrementer automatically increments the address pointer register and outputs the next addressed register content on to the SDA line for transmission to the master. If no acknowledge is received, the AD7747 returns to the idle state and the address pointer is not incremented.

The address pointer's auto-incrementer allows block data to be written or read from the starting address and subsequent incremental addresses.

In continuous conversion mode, the address pointer's auto-incrementer should be used for reading a conversion result. That means the three data bytes should be read using one multibyte read transaction rather than three separate single byte transactions. The single byte data read transaction may result in the data bytes from two different results being mixed. The same applies for six data bytes if both the capacitive and the voltage/temperature channel are enabled.

The user can also access any unique register (address) on a one-to-one basis without having to update all the registers. The address pointer register's contents cannot be read.

If an incorrect address pointer location is accessed, or if the user allows the auto-incrementer to exceed the required register address, the following applies:

- In read mode, the AD7747 continues to output various internal register contents until the master device issues a no acknowledge, start, or stop condition. The address pointer auto-incrementer's contents are reset to point to the status register at Address 0x00 when a stop condition is received at the end of a read operation. This allows the status register to be read (polled) continually without having to constantly write to the address pointer.

- In write mode, the data for the invalid address is not loaded into the AD7747 registers, but an acknowledge is issued by the AD7747.

#### WRITE OPERATION

When a write is selected, the byte following the start byte is always the register address pointer (subaddress) byte, which points to one of the internal registers on the AD7747. The address pointer byte is automatically loaded into the address pointer register and acknowledged by the AD7747. After the address pointer byte acknowledge, a stop condition, a repeated start condition, or another data byte can follow from the master.

A stop condition is defined by a low-to-high transition on SDA while SCL remains high. If a stop condition is ever encountered by the AD7747, it returns to its idle condition and the address pointer is reset to Address 0x00.

If a data byte is transmitted after the register address pointer byte, the AD7747 loads this byte into the register that is currently addressed by the address pointer register, sends an acknowledge, and the address pointer auto-incrementer automatically increments the address pointer register to the next internal register address. Thus, subsequent transmitted data bytes are loaded into sequentially incremented addresses.

If a repeated start condition is encountered after the address pointer byte, all peripherals connected to the bus respond exactly as outlined above for a start condition, that is, a repeated start condition is treated the same as a start condition. When a master device issues a stop condition, it relinquishes control of

the bus, allowing another master device to take control of the bus. Therefore, a master wanting to retain control of the bus issues successive start conditions known as repeated start conditions.

### **AD7747 RESET**

To reset the AD7747 without having to reset the entire  $I^2C$  bus, an explicit reset command is provided. This uses a particular address pointer word as a command word to reset the part and upload all default settings. The AD7747 does not respond to the  $I^2C$  bus commands (do not acknowledge) during the default values upload for approximately 150  $\mu$ s (max 200  $\mu$ s).

The reset command address word is 0xBF.

#### **GENERAL CALL**

When a master issues a slave address consisting of seven 0s with the eighth bit (R/W bit) set to 0, this is known as the general call address. The general call address is for addressing every device connected to the  $\rm I^2C$  bus. The AD7747 acknowledges this address and read in the following data byte.

If the second byte is 0x06, the AD7747 is reset, completely uploading all default values. The AD7747 does not respond to the  $I^2C$  bus commands (do not acknowledge) during the default values upload for approximately 150  $\mu s$  (200  $\mu s$  maximum).

The AD7747 does not acknowledge any other general call commands.

Figure 22. Bus Data Transfer

Figure 23. Write and Read Sequences

# **REGISTER DESCRIPTIONS**

The master can write to or read from all of the AD7747 registers except the address pointer register, which is a write-only register. The address pointer register determines which register the next read or write operation accesses. All communications with the part through the bus start with an access to the address pointer register. After the part has been accessed over the bus

and a read/write operation is selected, the address pointer register is set up. The address pointer register determines from or to which register the operation takes place. A read/write operation is performed from/to the target address, which then increments to the next address until a stop command on the bus is performed.

**Table 8. Register Summary**

|               | Addres<br>Pointe |       |     | Bit 7         | Bit 6 | Bit 5         | Bit 4          | Bit 3          | Bit 2         | Bit 1   | Bit 0   |

|---------------|------------------|-------|-----|---------------|-------|---------------|----------------|----------------|---------------|---------|---------|

| Register      | (Dec)            | (Hex) | Dir | Default Value |       |               |                |                |               |         | -1      |

| Status        | 0                | 0x00  | R   | _             | _     | _             | -              | -              | RDY           | RDYVT   | RDYCAP  |

|               |                  |       |     | 0             | 0     | 0             | 0              | 0              | 1             | 1       | 1       |

| Cap Data H    | 1                | 0x01  | R   |               | •     | Capaciti      | ve channel c   | lata—high b    | yte, 0x00     | •       | •       |

| Cap Data M    | 2                | 0x02  | R   |               |       | Capacitiv     | e channel da   | ta—middle      | byte, 0x00    |         |         |

| Cap Data L    | 3                | 0x03  | R   |               |       | Capacit       | ive channel o  | data—low by    | /te, 0x00     |         |         |

| VT Data H     | 4                | 0x04  | R   |               | V     | oltage/temp   | erature char   | nnel data—h    | igh byte, 0x  | 00      |         |

| VT Data M     | 5                | 0x05  | R   |               | Vo    | ltage/tempe   | rature chani   | nel data—mi    | iddle byte, 0 | x00     |         |

| VT Data L     | 6                | 0x06  | R   |               | 1     | /oltage/temp  | oerature cha   | nnel data—l    | ow byte, 0x0  | 00      |         |

| Cap Setup     | 7                | 0x07  | R/W | CAPEN         | _     | CAPDIFF       | -              | -              | _             | _       | -       |

|               |                  |       |     | 0             | 0     | 0             | 0              | 0              | 0             | 0       | 0       |

| VT Setup      | 8                | 0x08  | R/W | VTEN          | VTMD1 | VTMD0         | EXTREF         | -              | -             | VTSHORT | VTCHOP  |

|               |                  |       |     | 0             | 0     | 0             | 0              | 0              | 0             | 0       | 0       |

| EXC Setup     | 9                | 0x09  | R/W | _             | _     | _             | -              | EXCDAC         | EXCEN         | EXCLVL1 | EXCLVL0 |

|               |                  |       |     | 0             | 0     | 0             | 0              | 0              | 0             | 1       | 1       |

| Configuration | 10               | 0x0A  | R/W | VTFS1         | VTFS0 | CAPFS2        | CAPFS1         | CAPFS0         | MD2           | MD1     | MD0     |

|               |                  |       |     | 1             | 0     | 1             | 0              | 0              | 0             | 0       | 0       |

| Cap DAC A     | 11               | 0x0B  | R/W | DACAENA       | -     |               |                | DACA—          | 6-Bit Value   |         |         |

|               |                  |       |     | 0             | 0     |               |                | 0>             | k00           |         |         |

| Cap DAC B     | 12               | 0x0C  | R/W | DACBENB       | -     |               |                | DACB—6         | 6-Bit Value   |         |         |

|               |                  |       |     | 0             | 0     |               |                | 0:             | x00           |         |         |

| Cap Offset H  | 13               | 0x0D  | R/W |               |       | Capacitive    | offset calibi  | ation—high     | byte, 0x80    |         |         |

| Cap Offset L  | 14               | 0x0E  | R/W |               |       | Capacitiv     | e offset calib | ration—low     | byte, 0x00    |         |         |

| Cap Gain H    | 15               | 0x0F  | R/W |               | Cap   | acitive gain  | calibration—   | -high byte, fa | actory calibr | rated   |         |

| Cap Gain L    | 16               | 0x10  | R/W |               | Cap   | oacitive gain | calibration-   | –low byte, fa  | ctory calibra | ated    |         |

| Volt Gain H   | 17               | 0x11  | R/W |               | Vo    | ltage gain c  | alibration—l   | nigh byte, fac | tory calibra  | ted     |         |

| Volt Gain L   | 18               | 0x12  | R/W |               | Vo    | oltage gain o | alibration—    | low byte, fac  | tory calibrat | ed      |         |

#### **STATUS REGISTER**

### Address Pointer 0x00, Read Only, Default Value 0x07

This register indicates the status of the converter. The status register can be read via the 2-wire serial interface to query a finished conversion.

The  $\overline{RDY}$  pin reflects the status of the RDY bit. Therefore, the  $\overline{RDY}$  pin high-to-low transition can be used as an alternative indication of the finished conversion.

Table 9. Status Register Bit Map

| Bit      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0  |

|----------|-------|-------|-------|-------|-------|-------|-------|--------|

| Mnemonic | -     | -     | -     | -     | -     | RDY   | RDYVT | RDYCAP |

| Default  | 0     | 0     | 0     | 0     | 0     | 1     | 1     | 1      |

#### Table 10.

| Bit    | Mnemonic | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|--------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7 to 3 | -        | Not used, always read 0.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 2      | RDY      | RDY = 0 indicates that conversion on the enabled channel(s) is complete and new unread data is available. If both capacitive and voltage/temperature channels are enabled, the RDY bit is changed to 0 after conversion on both channels is complete. The RDY bit returns to 1 either when data is read or prior to finishing the next conversion. If, for example, only the capacitive channel is enabled, then the RDY bit reflects the RDYCAP bit. |

| 1      | RDYVT    | RDYVT = 0 indicates that a conversion on the voltage/temperature channel is complete and new unread data is available.                                                                                                                                                                                                                                                                                                                                |

| 0      | RDYCAP   | RDYCAP = 0 indicates that a conversion on the capacitive channel is complete and new unread data is available.                                                                                                                                                                                                                                                                                                                                        |

### **CAP DATA REGISTER**

# 24 Bits, Address Pointer 0x01, 0x02, 0x03, Read-Only, Default Value 0x000000

This register contains the capacitive channel output data. The register is updated after finished conversion on the capacitive channel, with one exception: When the serial interface read operation from the Cap Data register is in progress, the data register is not updated and the new capacitance conversion result is lost.

The stop condition on the serial interface is considered to be the end of the read operation. Therefore, to prevent data corruption, all three bytes of the data register should be read sequentially using the register address pointer auto-increment feature of the serial interface.

To prevent losing some of the results, the Cap Data register should be read before the next conversion on the capacitive channel is finished.

The 0x000000 code represents negative full scale (-8.192 pF), the 0x800000 code represents zero scale (0 pF), and the 0xFFFFFF code represents positive full scale (+8.192 pF).

#### **VT DATA REGISTER**

# 24 Bits, Address Pointer 0x04, 0x05, 0x06, Read-Only, Default Value 0x000000

This register contains the voltage/temperature channel output data. The register is updated after finished conversion on the voltage channel or temperature channel, with one exception: When the serial interface read operation from the VT Data register is in progress, the data register is not updated and the new voltage/temperature conversion result is lost.

The stop condition on the serial interface is considered to be the end of the read operation. Therefore, to prevent data corruption, all three bytes of the data register should be read sequentially using the register address pointer auto-increment feature of the serial interface.

For voltage input, Code 0 represents negative full scale ( $-V_{REF}$ ), the 0x800000 code represents zero scale (0 V), and the 0xFFFFFF code represents positive full scale ( $+V_{REF}$ ).

To prevent losing some of the results, the VT Data register should be read before the next conversion on the voltage/ temperature channel is complete.

For the temperature sensor, the temperature can be calculated from code using the following equation:

*Temperature* ( $^{\circ}$ C) = (Code/2048) – 4096

# **CAP SETUP REGISTER**

# Address Pointer 0x07, Default Value 0x00

Capacitive channel setup.

# Table 11. Cap Setup Register Bit Map

| Bit      | Bit 7 | Bit 6 | Bit 5   | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|---------|-------|-------|-------|-------|-------|

| Mnemonic | CAPEN | -     | CAPDIFF | -     | -     | -     | -     | _     |

| Default  | 0     | 0     | 0       | 0     | 0     | 0     | 0     | 0     |

### Table 12.

| Bit    | Mnemonic | Description                                                                                        |

|--------|----------|----------------------------------------------------------------------------------------------------|

| 7      | CAPEN    | CAPEN = 1 enables capacitive channel for single conversion, continuous conversion, or calibration. |

| 6      | -        | This bit must be 0 for proper operation.                                                           |

| 5      | CAPDIFF  | This bit must be set to 1 for proper operation.                                                    |

| 4 to 0 | _        | These bits must be 0 for proper operation.                                                         |

### **VT SETUP REGISTER**

### Address Pointer 0x08, Default Value 0x00

Voltage/Temperature channel setup.

# Table 13. VT Setup Register Bit Map

| Bit      | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1   | Bit 0  |

|----------|-------|-------|-------|--------|-------|-------|---------|--------|

| Mnemonic | VTEN  | VTMD1 | VTMD0 | EXTREF | -     | -     | VTSHORT | VTCHOP |

| Default  | 0     | 0     | 0     | 0      | 0     | 0     | 0       | 0      |

## Table 14.

| Bit    | Mnemonic   | Descripti                         | on                   |                                                                                                                                                                                                  |

|--------|------------|-----------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | VTEN       | VTEN = 1                          | enables volt         | age/temperature channel for single conversion, continuous conversion, or calibration.                                                                                                            |

| 6      | VTMD1      | Voltage/t                         | emperature           | channel input configuration.                                                                                                                                                                     |

| 5      | VTMD0      | VTMD1                             | VTMD0                | Channel Input                                                                                                                                                                                    |

|        |            | 0                                 | 0                    | Internal temperature sensor                                                                                                                                                                      |

|        |            | 0                                 | 1                    | External temperature sensor diode                                                                                                                                                                |

|        |            | 1                                 | 0                    | V <sub>DD</sub> monitor                                                                                                                                                                          |

|        |            | 1                                 | 1                    | External voltage input (VIN)                                                                                                                                                                     |

| 4      | EXTREF     | V <sub>DD</sub> monit<br>EXTREF = | or.<br>0 selects the | external reference voltage connected to REFIN(+), REFIN(–) for the voltage input or the e on-chip internal reference. The internal reference must be used with the internal or proper operation. |

| 3 to 2 | _          | These bits                        | s must be 0 f        | or proper operation.                                                                                                                                                                             |

| 1      | VTSHORT    | VTSHORT                           | = 1 internal         | ly shorts the voltage/temperature channel input for test purposes.                                                                                                                               |

| 0      | VTCHOP = 1 |                                   |                      | nal chopping on the voltage/temperature channel.<br>be set to 1 for the specified voltage/temperature channel performance.                                                                       |

# **EXC SETUP REGISTER**

# Address Pointer 0x09, Default Value 0x03

Capacitive channel excitation setup.

# Table 15. EXC Setup Bit Map

| Bit      | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1   | Bit 0   |

|----------|-------|-------|-------|-------|--------|-------|---------|---------|

| Mnemonic | -     | _     | _     | _     | EXCDAC | EXCEN | EXCLVL1 | EXCLVL0 |

| Default  | 0     | 0     | 0     | 0     | 0      | 0     | 1       | 1       |

### Table 16.

| Bit    | Mnemonic | Description                                                                                                    | Description                                                                                        |                        |                       |                       |  |  |  |  |

|--------|----------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|------------------------|-----------------------|-----------------------|--|--|--|--|

| 7 to 4 | _        | These bits m                                                                                                   | These bits must be 0 for proper operation.                                                         |                        |                       |                       |  |  |  |  |

| 3      | EXCDAC   | CAPDAC exc                                                                                                     | CAPDAC excitation. This bit must be set to 1 for the proper capacitive channel operation.          |                        |                       |                       |  |  |  |  |

| 2      | EXCEN    | CIN and AC S                                                                                                   | CIN and AC SHLD excitation. This bit must be set to 1 for the proper capacitive channel operation. |                        |                       |                       |  |  |  |  |

| 1      | EXCLVL1, | Excitation Voltage Level. Must be set to $\pm V_{DD} \times 3/8$ to allow operation for specified performance. |                                                                                                    |                        |                       |                       |  |  |  |  |

| 0      | EXCLVL0  | EXCLVL1                                                                                                        | EXCLVL0                                                                                            | Voltage on Cap         | EXC Low Level         | EXC High Level        |  |  |  |  |

|        |          | 0                                                                                                              | 0                                                                                                  | ±V <sub>DD</sub> /8    | V <sub>DD</sub> × 3/8 | V <sub>DD</sub> × 5/8 |  |  |  |  |

|        |          | 0                                                                                                              | 1                                                                                                  | ±V <sub>DD</sub> /4    | $V_{DD} \times 1/4$   | $V_{DD} \times 3/4$   |  |  |  |  |

|        |          | 1                                                                                                              | 0                                                                                                  | ±V <sub>DD</sub> × 3/8 | $V_{DD} \times 1/8$   | $V_{DD} \times 7/8$   |  |  |  |  |

|        |          | 1                                                                                                              | 1                                                                                                  | ±V <sub>DD</sub> /2    | 0                     | $V_{DD}$              |  |  |  |  |

# **CONFIGURATION REGISTER**

# Address Pointer 0x0A, Default Value 0xA0

Converter update rate and mode of operation setup.

Table 17. Configuration Register Bit Map

| Bit      | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3  | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|--------|--------|--------|-------|-------|-------|

| Mnemonic | VTFS1 | VTFS0 | CAPFS2 | CAPFS1 | CAPFS0 | MD2   | MD1   | MD0   |

| Default  | 0     | 0     | 0      | 0      | 0      | 0     | 0     | 0     |

Table 18.

| Bit    | Mnemonic | Description | on              |              |                             |                        |                      |  |  |  |

|--------|----------|-------------|-----------------|--------------|-----------------------------|------------------------|----------------------|--|--|--|

| 7      | VTFS1    | Voltage/te  | mperature       | channel digi | tal filter setup—conversior | n time/update rate set | up.                  |  |  |  |

| 6      | VTFS0    |             |                 |              | VTCHOP = 1                  |                        |                      |  |  |  |

|        |          | VTFS1       | VTFS1 VTFS0     |              | Conversion Time (ms)        | Update Rate (Hz)       | −3 dB Frequency (Hz) |  |  |  |

|        |          | 0           | 0               |              | 20.1                        | 49.8                   | 26.4                 |  |  |  |

|        |          | 0           | 1               |              | 32.1                        | 31.2                   | 15.9                 |  |  |  |

|        |          | 1           | 0               |              | 62.1                        | 16.1                   | 8.0                  |  |  |  |

|        |          | 1           | 1               |              | 122.1                       | 8.2                    | 4.0                  |  |  |  |

| 5      | CAPFS2   | Capacitive  | ate rate setup. |              |                             |                        |                      |  |  |  |

| 4      | CAPES1   | CAPFS2      | CAPFS1          | CAPFS0       | Conversion Time (ms)        | Update Rate            | −3 dB Frequency (Hz) |  |  |  |

| 3      | CAPFS0   | 0           | 0               | 0            | 22.0                        | 45.5                   | 43.6                 |  |  |  |

|        |          | 0           | 0               | 1            | 23.9                        | 41.9                   | 39.5                 |  |  |  |

|        |          | 0           | 1               | 0            | 40.0                        | 25.0                   | 21.8                 |  |  |  |

|        |          | 0           | 1               | 1            | 76.0                        | 13.2                   | 10.9                 |  |  |  |

|        |          | 1           | 0               | 0            | 124.0                       | 8.1                    | 6.9                  |  |  |  |

|        |          | 1           | 0               | 1            | 154.0                       | 6.5                    | 5.3                  |  |  |  |

|        |          | 1           | 1               | 0            | 184.0                       | 5.5                    | 4.4                  |  |  |  |

|        |          | 1           | 1               | 1            | 219.3                       | 4.6                    | 4.0                  |  |  |  |

| 2      | MD2      | Converter   | mode of op      | eration setu | p.                          |                        |                      |  |  |  |

| 1<br>0 | MD1      | MD2         | MD1             | MD0          | Mode                        |                        |                      |  |  |  |

| U      | MD0      | 0           | 0               | 0            | Idle                        |                        |                      |  |  |  |

|        |          | 0           | 0               | 1            | Continuous conversion       |                        |                      |  |  |  |

|        |          | 0           | 1               | 0            | Single conversion           |                        |                      |  |  |  |

|        |          | 0           | 1               | 1            | Power-down                  | Power-down             |                      |  |  |  |

|        |          | 1           | 0               | 0            | _                           |                        |                      |  |  |  |

|        |          | 1           | 0               | 1            | Capacitance system offse    | et calibration         |                      |  |  |  |

|        |          | 1           | 1               | 0            | Capacitance or voltage s    | ystem gain calibratior | l                    |  |  |  |

|        |          | 1           | 1               | 1            | _                           |                        |                      |  |  |  |

### **CAP DAC A REGISTER**

# Address Pointer 0x0B, Default Value 0x00

Capacitive DAC setup.

# Table 19. Cap DAC A Register Bit Map

| Bit      | Bit 7   | Bit 6 | Bit 5            | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|---------|-------|------------------|-------|-------|-------|-------|-------|

| Mnemonic | DACAENA | _     | DACA—6-Bit Value |       |       |       |       |       |

| Default  | 0       | 0     | 0x00             |       |       |       |       |       |

### Table 20.

| Bit    | Mnemonic                                                                        | Description                                           |  |  |  |  |

|--------|---------------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| 7      | DACAENA DACAENA = 1 connects capacitive DACA to the positive capacitance input. |                                                       |  |  |  |  |

| 6      | -                                                                               | This bit must be 0 for proper operation.              |  |  |  |  |

| 5 to 1 | DACA                                                                            | DACA value, Code 0x00 ≈ 0 pF, Code 0x3F ≈ full range. |  |  |  |  |

### **CAP DAC B REGISTER**

# Address Pointer 0x0C, Default Value 0x00

Capacitive DAC setup.

# Table 21. Cap DAC B Register Bit Map

| Bit      | Bit 7   | Bit 6 | Bit 5            | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|---------|-------|------------------|-------|-------|-------|-------|-------|

| Mnemonic | DACBENB | -     | DACB—6-Bit Value |       |       |       |       |       |

| Default  | 0       | 0     | 0x00             |       |       |       |       |       |

### Table 22.

| Bit    | Mnemonic | Description                                                             |

|--------|----------|-------------------------------------------------------------------------|

| 7      | DACBENB  | DACBENB = 1 connects capacitive DACB to the negative capacitance input. |

| 6      | -        | This bit must be 0 for proper operation.                                |

| 5 to 1 | DACB     | DACB value, Code 0x00 ≈ 0 pF, Code 0x3F ≈ full range.                   |

#### **CAP OFFSET CALIBRATION REGISTER**

### 16 Bits, Address Pointer 0x0D, 0x0E, Default Value 0x8000

The capacitive offset calibration register holds the capacitive channel zero-scale calibration coefficient. The coefficient is used to digitally remove the capacitive channel offset. The register value is updated automatically following the execution of a capacitance offset calibration. The capacitive offset calibration resolution (cap offset register LSB) is less than 32 aF; the full range is  $\pm 1$  pF.

### **CAP GAIN CALIBRATION REGISTER**

16 Bits, Address Pointer 0x0F, 0x10, Default Value 0xXXXX

Capacitive gain calibration register. The register holds the capacitive channel full-scale factory calibration coefficient.

### **VOLT GAIN CALIBRATION REGISTER**

16 Bits, Address Pointer 0x11,0x12, Default Value 0xXXXX

Voltage gain calibration register. The register holds the voltage channel full-scale factory calibration coefficient.

# CIRCUIT DESCRIPTION

Figure 24. AD7747 Block Diagram

### **OVERVIEW**

The AD7747 core is a high precision converter consisting of a second-order ( $\Sigma$ - $\Delta$  or charge balancing) modulator and a third-order digital filter. It works as a CDC for the capacitive inputs and as a classic ADC for the voltage input or for the voltage from a temperature sensor.

In addition to the converter, the AD7747 integrates a multiplexer, an excitation source and CAPDACs for the capacitive inputs, a temperature sensor and a voltage reference for the voltage and temperature inputs, a complete clock generator, a control and calibration logic, and an I<sup>2</sup>C-compatible serial interface.

### **CAPACITANCE-TO-DIGITAL CONVERTER**