# Intel<sup>®</sup> 5000P/5000V/5000Z Chipset Memory Controller Hub (MCH)

Datasheet

September 2006

Document Number: 313071-003

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL® PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

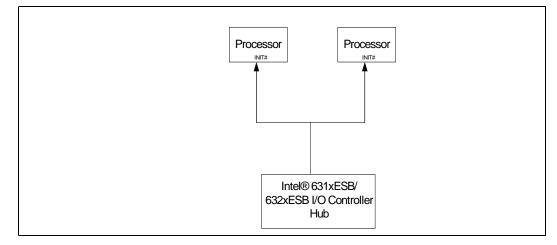

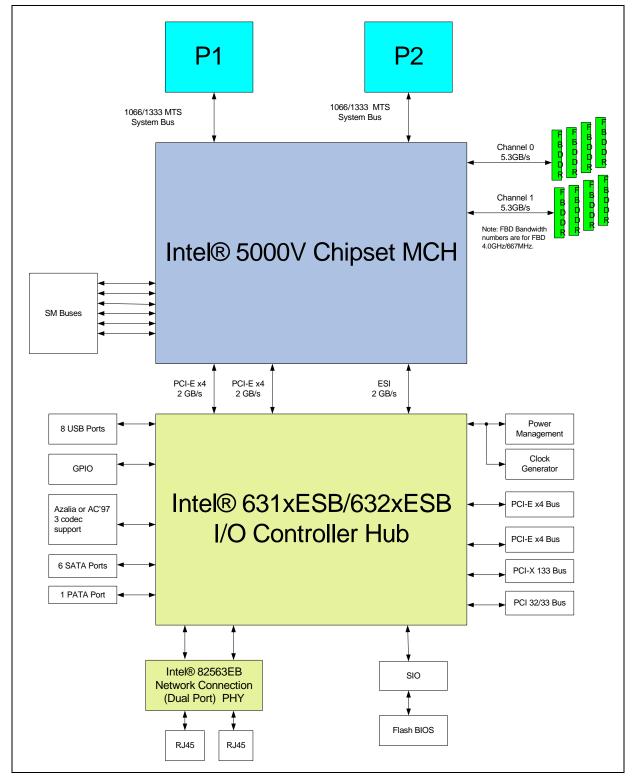

The Intel<sup>®</sup> 5000 Series Chipsets, Dual Core Intel<sup>®</sup> Xeon<sup>®</sup> Processor 5000 sequence and Intel<sup>®</sup> 631xESB/632xESB I/O Controller Hub may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

64-bit Intel<sup>®</sup> Xeon<sup>®</sup> processors with Intel<sup>®</sup> EM64T requires a computer system with a processor, chipset, BIOS, OS, device drivers and applications enabled for Intel EM64T. Processor will not operate (including 32-bit operation) without an Intel EM64T-enabled BIOS. Performance will vary depending on your hardware and software configurations. Intel EM64T-enabled OS, BIOS, device drivers and applications may not be available. Check with your vendor for more information.Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

I<sup>2</sup>C is a two-wire communications bus/protocol developed by Philips. SMBus is a subset of the I<sup>2</sup>C bus/protocol and was developed by Intel. Implementations of the I<sup>2</sup>C bus/protocol may require licenses from various entities, including Philips Electronics N.V. and North American Philips Corporation.

Intel, Pentium, and Xeon are trademarks or registered trademarks of Intel Corporation or its subsidiaries in the United States and other countries.

\*Other brands and names are the property of their respective owners.

Copyright © 2005-2006, Intel Corporation.

# Contents

| 1 | Introd      | duction                                                                   | . 15 |

|---|-------------|---------------------------------------------------------------------------|------|

|   | 1.1         | Terminology                                                               | . 15 |

|   | 1.2         | Related Documents and Materials                                           | . 21 |

|   |             | 1.2.1 BIOS Self-test Utility                                              | . 21 |

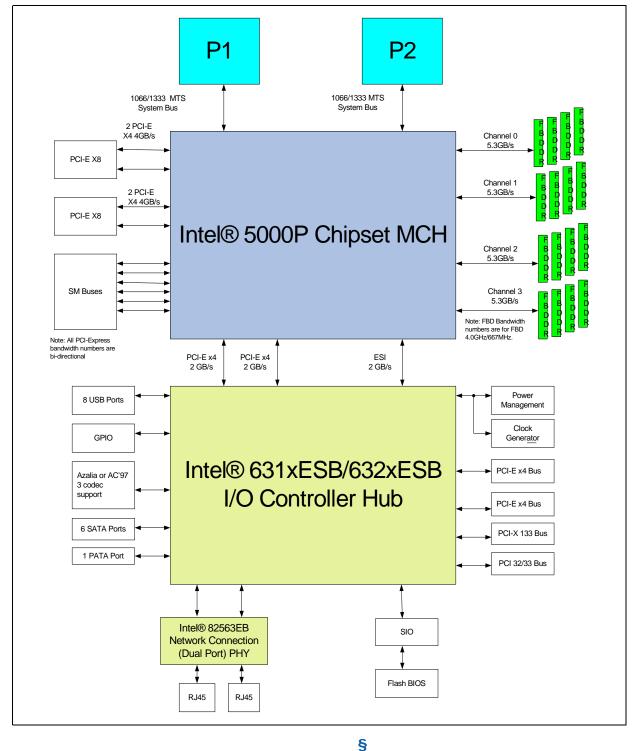

|   | 1.3         | Intel 5000P Chipset Overview                                              | . 21 |

| 2 | Signa       | I Description                                                             | . 25 |

| - | 2.1         | Processor Front Side Bus Signals                                          |      |

|   | 2.1         | 2.1.1 Processor Front Side Bus 0                                          |      |

|   |             | 2.1.2 Processor Front Side Bus 1                                          |      |

|   | 2.2         | Fully Buffered DIMM Memory Channels                                       |      |

|   | 2.2         | 2.2.1 FB-DIMM Branch 0                                                    |      |

|   |             | 2.2.2 FB-DIMM Branch 1                                                    |      |

|   | 2.3         |                                                                           |      |

|   | 2.3         | PCI Express* Signal List                                                  |      |

|   |             |                                                                           |      |

|   |             |                                                                           |      |

|   |             | 2.3.3 PCI Express Port 2.                                                 |      |

|   |             | 2.3.4 PCI Express Port 3.                                                 |      |

|   |             | 2.3.5 PCI Express Port 4                                                  |      |

|   |             | 2.3.6 PCI Express Port 5                                                  |      |

|   |             | 2.3.7 PCI Express Port 6                                                  |      |

|   | ~ .         | 2.3.8 PCI Express Port 7                                                  |      |

|   | 2.4         | System Management Bus Interfaces                                          |      |

|   | 2.5         | XD Port Signal List                                                       |      |

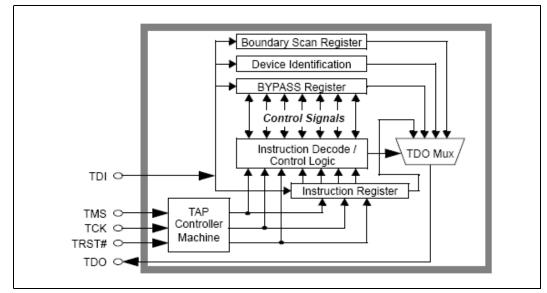

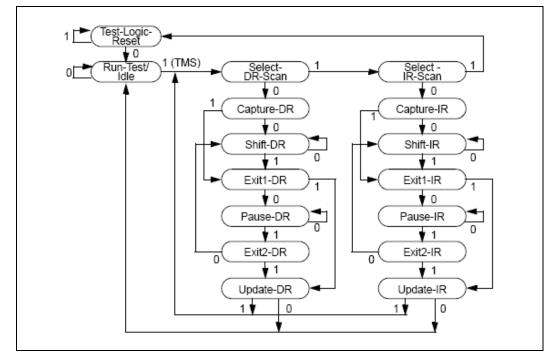

|   | 2.6         | JTAG Bus Signal List                                                      |      |

|   | 2.7         | Clocks, Reset and Miscellaneous                                           |      |

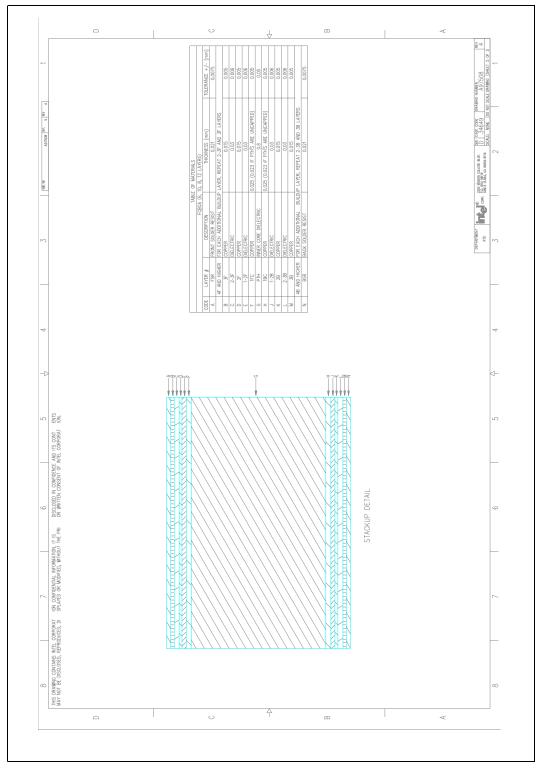

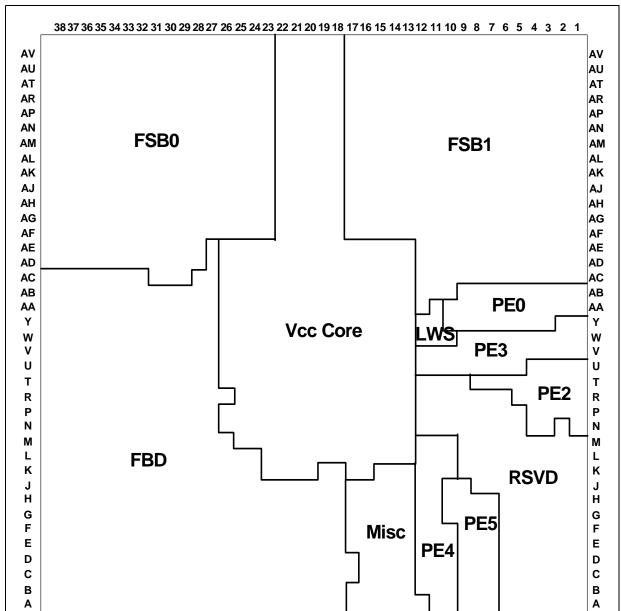

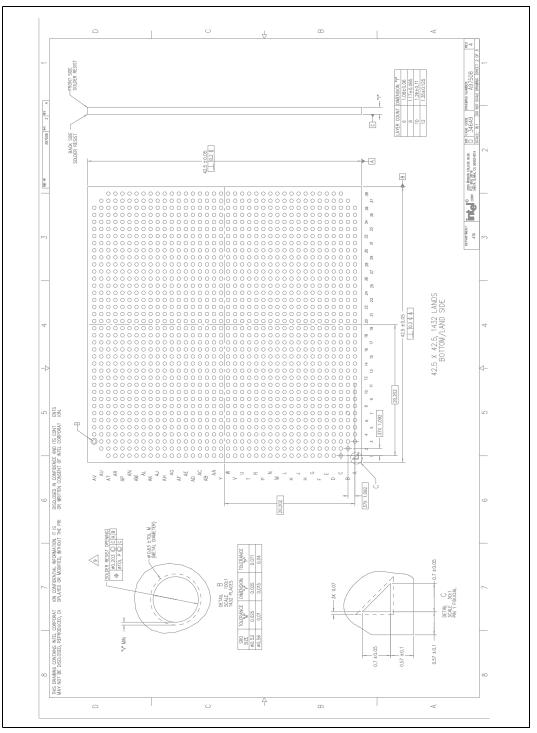

|   | 2.8         | Power and Ground Signals                                                  |      |

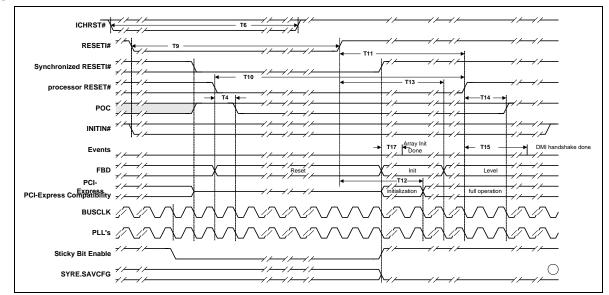

|   | 2.9         | MCH Sequencing Requirements                                               |      |

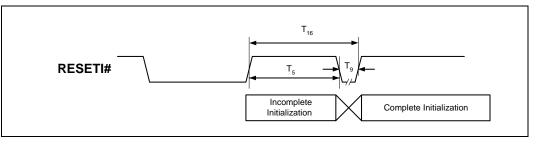

|   | 2.10        | Reset Requirements                                                        |      |

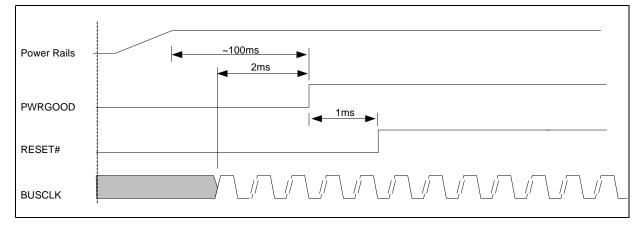

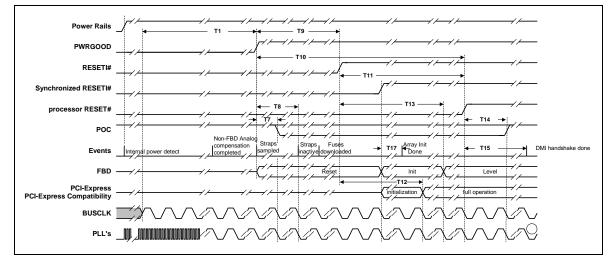

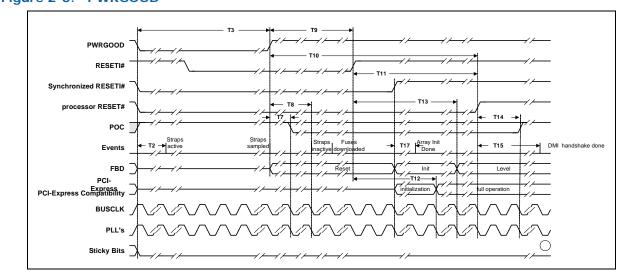

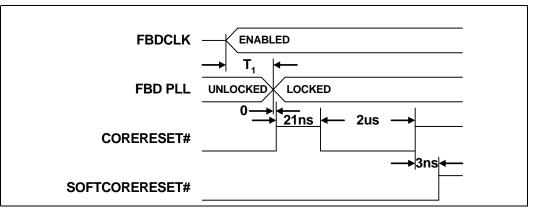

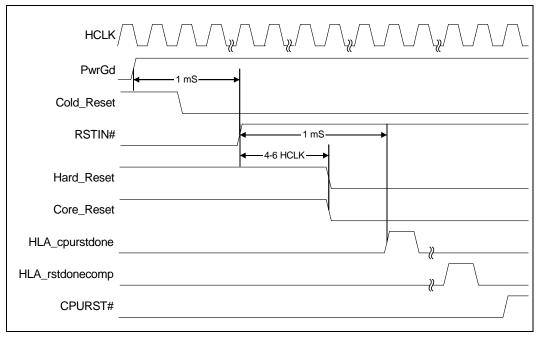

|   |             | 2.10.1 Timing Diagrams                                                    |      |

|   |             | 2.10.2 Reset Timing Requirements                                          |      |

|   |             | 2.10.3 Miscellaneous Requirements and Limitations                         |      |

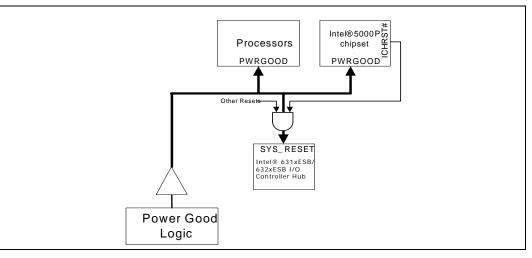

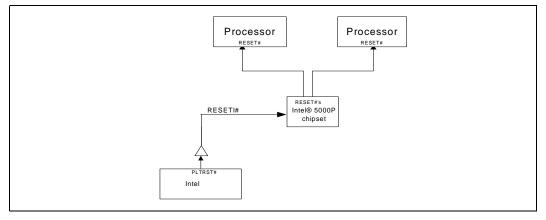

|   | 2.11        | Intel 5000P Chipset Platform Signal Routing Topology Diagrams             |      |

|   |             | 2.11.1 Intel 5000P Customer Reference Platform (SRP) Reset Topology       |      |

|   | 2.12        | Signals Used as Straps                                                    |      |

|   |             | 2.12.1 Functional Straps                                                  | . 43 |

| 3 | Reais       | ter Description                                                           | . 45 |

|   | 3.1         | Register Terminology                                                      |      |

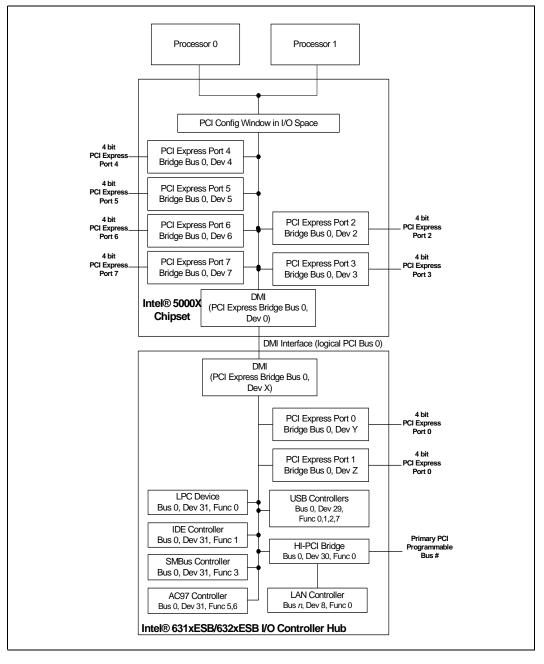

|   | 3.2         | Platform Configuration Structure                                          |      |

|   | 3.3         | Routing Configuration Accesses                                            |      |

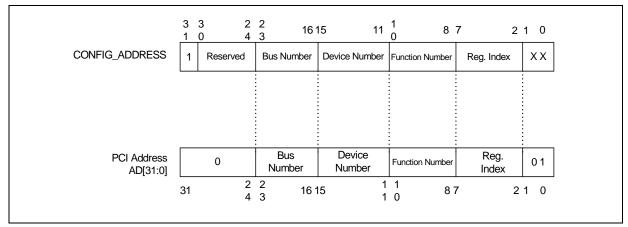

|   | 0.0         | 3.3.1 Standard PCI Bus Configuration Mechanism                            |      |

|   |             | 3.3.2 PCI Bus 0 Configuration Mechanism                                   |      |

|   |             | 3.3.3 Primary PCI and Downstream Configuration Mechanism                  |      |

|   | 3.4         | Device Mapping.                                                           |      |

|   | 0.1         | 3.4.1 Device Identification for Intel 5000P Chipset, Intel 5000Z Chipset, | . 00 |

|   |             | and Intel 5000V Chipset Components                                        | . 51 |

|   |             | 3.4.2 Special Device and Function Routing                                 |      |

|   | 3.5         | I/O Mapped Registers                                                      |      |

|   | 0.0         | 3.5.1 CFGADR: Configuration Address Register                              |      |

|   |             | 3.5.2 CFGDAT: Configuration Data Register                                 |      |

|   | 3.6         | MCH Fixed Memory Mapped Registers                                         |      |

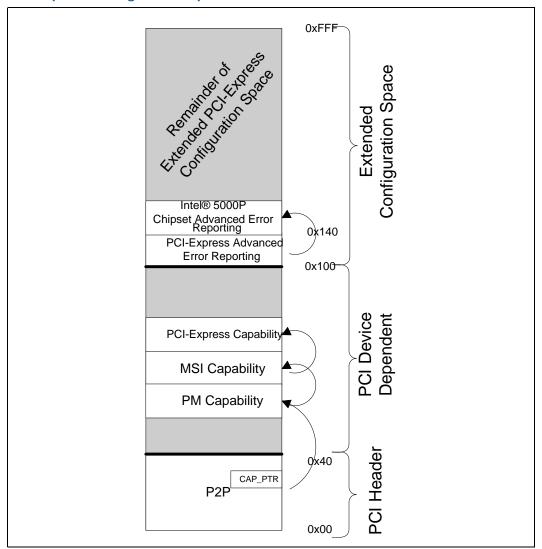

|   | 3.7         | Detailed Configuration Space Maps                                         |      |

|   | <b>.</b> ., |                                                                           |      |

| 3.8  | Register Definitions                                                      | 74  |

|------|---------------------------------------------------------------------------|-----|

|      | 3.8.1 PCI Standard Registers                                              | 74  |

|      | 3.8.2 Address Mapping Registers                                           | 83  |

|      | 3.8.3 AMB Memory Mapped Registers                                         |     |

|      | 3.8.4 Interrupt Redirection Registers                                     |     |

|      | 3.8.5 Boot and Reset Registers                                            |     |

|      | 3.8.6 Control and Interrupt Registers                                     |     |

|      | 3.8.7 PCI Express Device Configuration Registers                          |     |

|      | 3.8.8 PCI Express Header                                                  |     |

|      | 3.8.9 PCI Express Power Management Capability Structure                   |     |

|      | 3.8.10 PCI Express Message Signaled Interrupts (MSI) Capability Structure |     |

|      | 3.8.11 PCI Express Capability Structure                                   |     |

|      | 3.8.12 PCI Express Advanced Error Reporting Capability                    |     |

|      | 3.8.13 Error Registers                                                    |     |

| 3.9  | Memory Control Registers                                                  |     |

|      | 3.9.1 MC - Memory Control Settings                                        |     |

|      | 3.9.2 GBLACT - Global Activation Throttle Register                        |     |

|      | 3.9.3 THRTSTS[1:0] - Thermal Throttling Status Register                   |     |

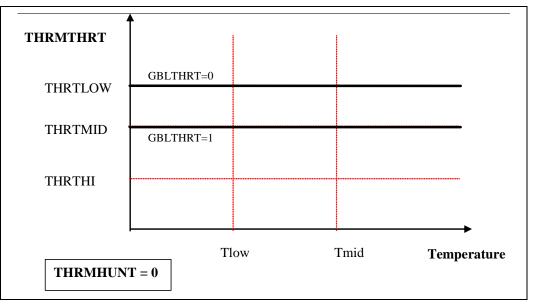

|      | 3.9.4 THRTLOW - Thermal Throttling Low Register                           |     |

|      | 3.9.5 THRTMID - Thermal Throttle Mid Register                             |     |

|      | 3.9.6 THRTHI - Thermal Throttle High Register                             |     |

|      | 3.9.7 THRTCTRL - Thermal Throttling Control Register                      |     |

|      | 3.9.8 MCA - Memory Control Settings A                                     |     |

|      | 3.9.9 DDRFRQ - DDR Frequency Ratio                                        |     |

|      | 3.9.10 FBDTOHOSTGRCFGO: FB-DIMM to Host Gear Ratio Configuration 0        |     |

|      | 3.9.11 FBDTOHOSTGRCFG1: FB-DIMM to Host Gear Ratio Configuration 1        |     |

|      | 3.9.12 HOSTTOFBDGRCFG: Host to FB-DIMM Gear Ratio Configuration           |     |

|      | 3.9.13 GRFBDVLDCFG: FB-DIMM Valid Configuration                           |     |

|      | 3.9.14 GRHOSTFULLCFG: Host Full Flow Control Configuration                |     |

|      | 3.9.15 GRBUBBLECFG: FB-DIMM Host Bubble Configuration                     |     |

|      | 3.9.16 GRFBDTOHOSTDBLCFG: FB-DIMM To Host Double Configuration            |     |

|      | 3.9.17 Summary of Memory Gearing Register operating modes                 |     |

|      | 3.9.18 DRTA - DRAM Timing Register A                                      |     |

|      | 3.9.19 DRTB - DDR Timing Register B                                       | 205 |

|      | 3.9.20 ERRPER - Error Period                                              |     |

|      | 3.9.21 Memory Map Registers                                               |     |

|      | 3.9.22 FB-DIMM Error Registers                                            |     |

|      | 3.9.23 FB-DIMM Branch Registers                                           |     |

|      | 3.9.24 FB-DIMM RAS Registers                                              |     |

|      | 3.9.25 FB-DIMM IBIST Registers                                            |     |

|      | 3.9.26 Serial Presence Detect Registers                                   |     |

| 3.10 | DMA Engine Configuration Registers                                        |     |

| 5.10 | 3.10.1 PCICMD: PCI Command Register                                       |     |

|      | 3.10.2 PCISTS: PCI Status Register                                        |     |

|      | 3.10.3 CCR: Class Code Register                                           |     |

|      | 3.10.4 CB_BAR: DMA Engine Base Address Register                           |     |

|      | 3.10.5 CAPPTR: Capability Pointer Register                                |     |

|      | 3.10.6 INTL: Interrupt Line Register                                      |     |

|      | 3.10.7 INTP: Interrupt Pin Register                                       |     |

|      | 3.10.8 Power Management Capability Structure                              |     |

|      | 3.10.9 MSICAPID - Message Signalled Interrupt Capability ID Register      |     |

|      | 3.10.10MSINXPTR - Message Signalled Interrupt Next Pointer Register       |     |

|      | 3.10.11MSICTRL - Message Signalled Interrupt Control Register             |     |

|      | 3.10.12MSIAR: Message Signalled Interrupt Address Register                |     |

|      | 3.10.13MSIDR: Message Signalled Interrupt Data Register                   |     |

|      | 3.10.14PEXCAPID: PCI Express Capability ID Register                       |     |

|      |                                                                           |     |

|   |       | 3.10.15PEXNPTR: PCI Express Next Pointer Register                                                                            | 262 |

|---|-------|------------------------------------------------------------------------------------------------------------------------------|-----|

|   |       | 3.10.16PEXCAPS - PCI Express Capabilities Register                                                                           |     |

|   |       | 3.10.17PEXDEVCAP - Device Capabilities Register                                                                              |     |

|   |       | 3.10.18PEXDEVCTRL - Device Control Register                                                                                  |     |

|   |       | 3.10.19 PEXDEVSTS - PCI Express Device Status Register                                                                       | 265 |

|   | 3.11  | PCI Express IBIST Registers                                                                                                  |     |

|   |       | 3.11.1 DIOIBSTR: PCI Express IBIST Global Start/Status Register                                                              | 266 |

|   |       | 3.11.2 DIOOIBSTAT: PCI Express IBIST Completion Status Register                                                              |     |

|   |       | 3.11.3 DIOOIBERR: PCI Express IBIST Error Register                                                                           |     |

|   |       | 3.11.4 PEX[7:2,0]IBCTL: PEX IBIST Control Register                                                                           |     |

|   |       | 3.11.5 PEX[7:2,0]IBSYMBUF: PEX IBIST Symbol Buffer                                                                           |     |

|   |       | 3.11.6 PEX[7:2,0]IBEXTCTL: PEX IBIST Extended Control Register                                                               | 270 |

|   |       | 3.11.7 PEX[7:2,0]IBDLYSYM: PEX IBIST Delay Symbol                                                                            |     |

|   |       | 3.11.8 PEX[7:2,0]IBLOOPCNT: PEX IBIST Loop Counter                                                                           | 272 |

|   |       | 3.11.9 PEX[7:2,0]IBLNS[3:0]: PEX IBIST Lane Status                                                                           |     |

|   |       | 3.11.10DIO[1:0]SQUELCH_CNT: PCIe Cluster Squelch Count                                                                       | 274 |

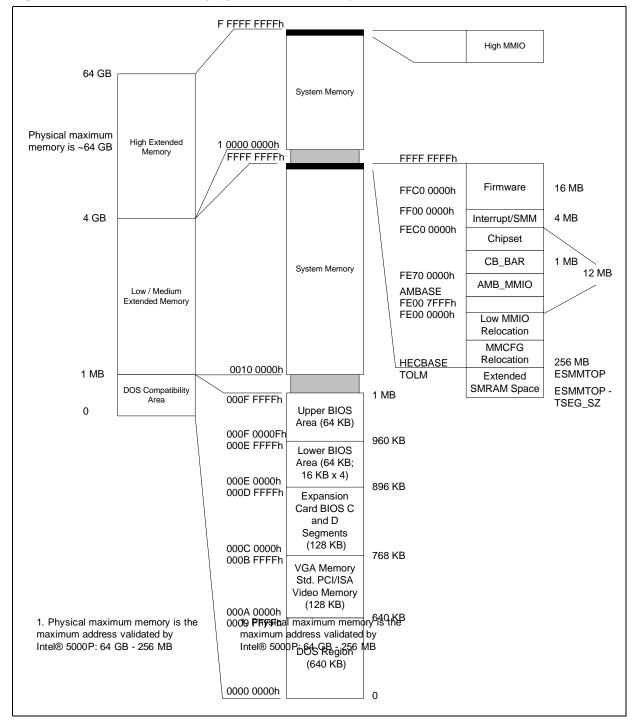

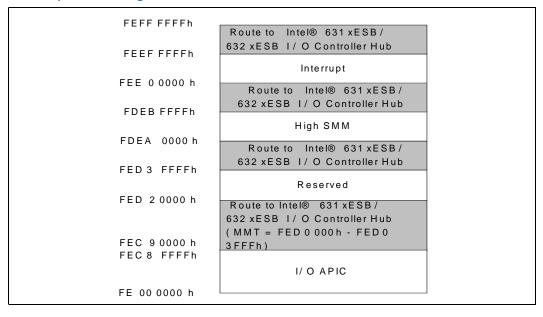

| 4 | Sveto | m Address Map                                                                                                                | 275 |

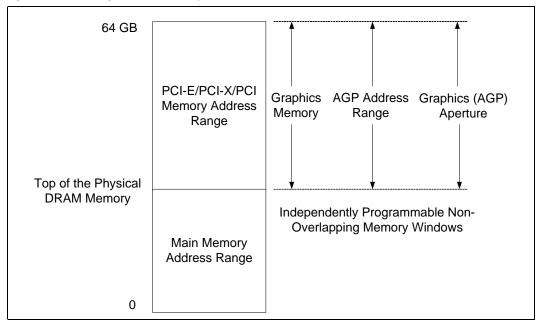

| 4 | -     | System Memory Address Ranges                                                                                                 |     |

|   | 4.1   | 4.1.1 32/64-bit addressing                                                                                                   |     |

|   | 4.0   | •                                                                                                                            |     |

|   | 4.2   | Compatibility Area                                                                                                           |     |

|   |       |                                                                                                                              |     |

|   |       |                                                                                                                              |     |

|   |       | <ul> <li>4.2.3 Expansion Card BIOS Area (C 0000h–D FFFFh)</li> <li>4.2.4 Lower System BIOS Area (E 0000h–E FFFFh)</li> </ul> |     |

|   |       | 4.2.5 Upper System BIOS Area (F 0000h–F FFFFh)                                                                               |     |

|   | 1 2   |                                                                                                                              |     |

|   | 4.3   | System Memory Area                                                                                                           |     |

|   |       | <ul> <li>4.3.1 System Memory</li> <li>4.3.2 15 MB - 16 MB Window (ISA Hole)</li> </ul>                                       |     |

|   |       |                                                                                                                              |     |

|   |       | 4.3.3 Extended SMRAM Space (TSEG)                                                                                            |     |

|   |       | <ul> <li>4.3.4 Memory Mapped Configuration (MMCFG) Region</li></ul>                                                          |     |

|   |       |                                                                                                                              |     |

|   |       |                                                                                                                              |     |

|   |       |                                                                                                                              |     |

|   |       | 4.3.8 High Extended Memory                                                                                                   |     |

|   | 4 4   | 4.3.9 Main Memory Region                                                                                                     |     |

|   | 4.4   | Memory Address Disposition                                                                                                   |     |

|   |       | 4.4.1 Registers Used for Address Routing                                                                                     |     |

|   |       | <ul><li>4.4.2 Address Disposition for Processor</li><li>4.4.3 Inbound Transactions</li></ul>                                 |     |

|   | 4 E   |                                                                                                                              |     |

|   | 4.5   | I/O Address Map<br>4.5.1 Special I/O Addresses                                                                               |     |

|   |       | •                                                                                                                            |     |

|   | 1 4   | 4.5.2 Outbound I/O Access                                                                                                    |     |

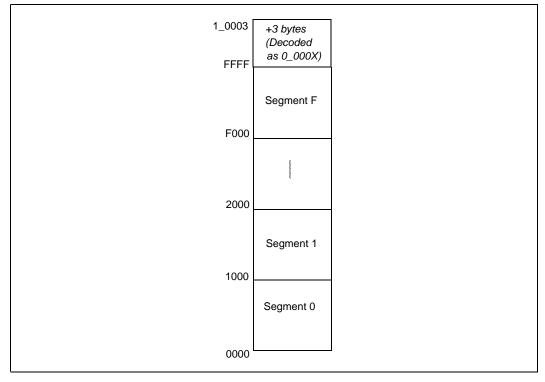

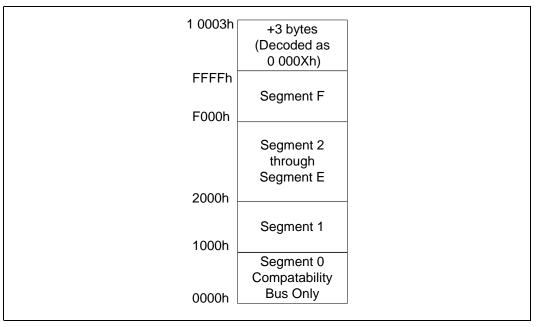

|   | 4.6   | Configuration Space                                                                                                          |     |

|   | 4.7   | I/O Address Map                                                                                                              |     |

|   |       | 4.7.1 Special I/O Addresses                                                                                                  |     |

|   | 10    | 4.7.2 Outbound I/O Access                                                                                                    |     |

|   | 4.8   | Configuration Space                                                                                                          | 296 |

| 5 | Funct | ional Description                                                                                                            | 297 |

|   | 5.1   | Processor Front Side Buses                                                                                                   |     |

|   |       |                                                                                                                              |     |

|   |       | 5.1.2 FSB Dynamic Bus Inversion                                                                                              |     |

|   |       | 5.1.3 FSB Interrupt Overview                                                                                                 |     |

|   | 5.2   | System Memory Controller                                                                                                     |     |

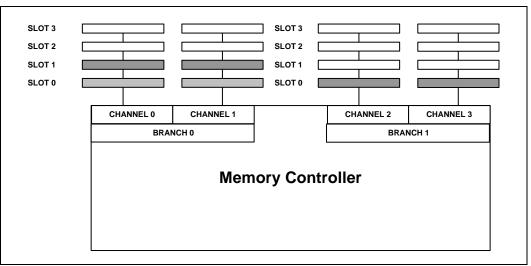

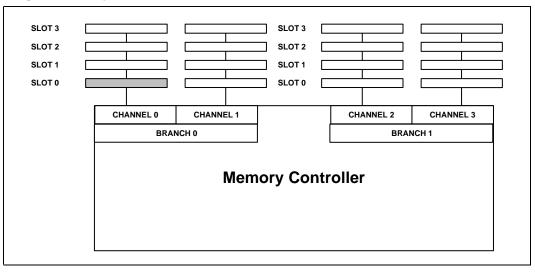

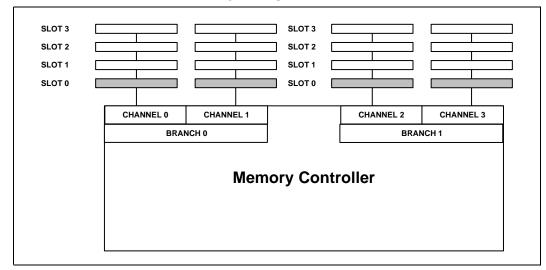

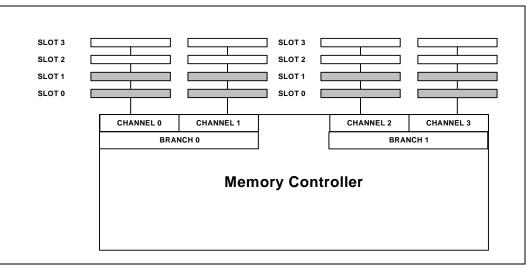

|   |       | 5.2.1 Memory Population Rules                                                                                                |     |

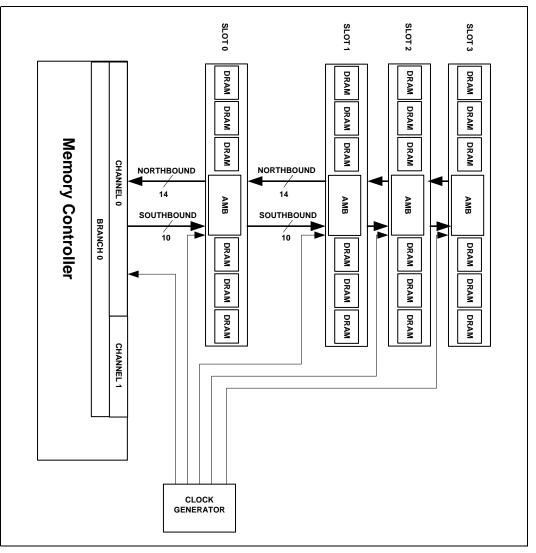

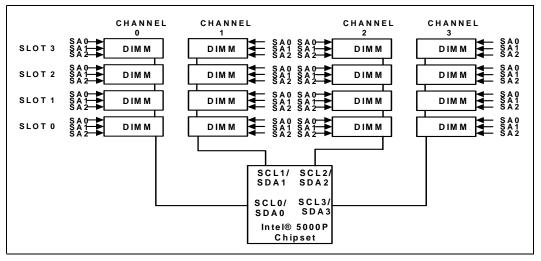

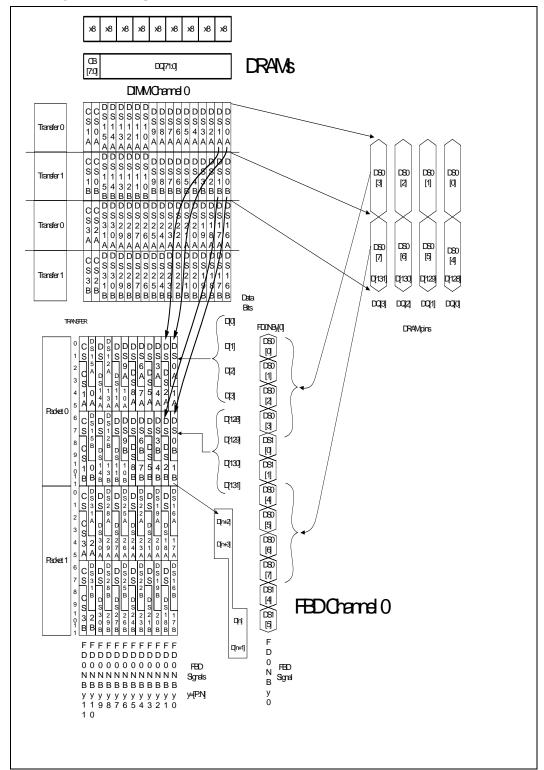

|   |       | 5.2.2 Fully Buffered DIMM Technology and Organization                                                                        |     |

|   |       |                                                                                                                              |     |

|      | 5.2.3                                | FB-DIMM Memory Operating Modes                    | 305                      |

|------|--------------------------------------|---------------------------------------------------|--------------------------|

|      | 5.2.4                                | Data Poisoning in Memory                          |                          |

|      | 5.2.5                                | Patrol Scrubbing                                  |                          |

|      | 5.2.6                                | Demand Scrubbing                                  |                          |

|      | 5.2.7                                | x8 Correction                                     |                          |

|      | 5.2.8                                | Single Device Data Correction (SDDC) Support      |                          |

|      | 5.2.9                                | FB-DIMM Memory Configuration Mechanism            |                          |

|      |                                      | FB-DIMM Memory Failure Isolation Mechanisms       |                          |

|      |                                      | DDR2 Protocol                                     |                          |

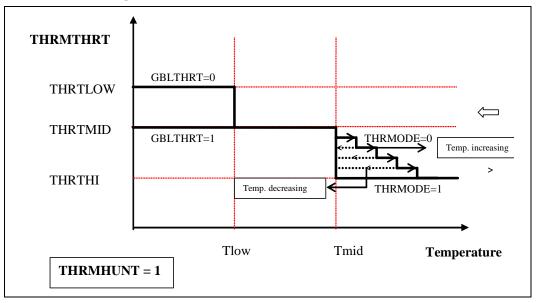

|      |                                      | Memory Thermal Management                         |                          |

|      |                                      | Electrical Throttling                             |                          |

| 5.3  |                                      | DOOP Chipset Behavior on Overtemp State in AMB    |                          |

| 5.4  |                                      | pts                                               |                          |

| 5.4  |                                      | Interrupt Message Delivery                        |                          |

| 5.5  | 5.5.1                                |                                                   |                          |

|      | 5.5.1<br>5.5.2                       | XAPIC Interrupt Message Format                    |                          |

|      |                                      | XAPIC Destination Modes                           |                          |

|      | 5.5.3                                | Interrupt Redirection                             |                          |

| F (  | 5.5.4                                | EOI                                               |                          |

| 5.6  |                                      | errupts                                           |                          |

|      | 5.6.1                                | Ordering                                          |                          |

|      | 5.6.2                                | Hardware IRQ IOxAPIC Interrupts                   |                          |

|      | 5.6.3                                | Message Signalled Interrupts                      |                          |

|      | 5.6.4                                | Non-MSI Interrupts - "Fake MSI"                   |                          |

| 5.7  |                                      | ocessor Interrupts (IPIs)                         |                          |

| 5.8  |                                      | Generated Interrupts                              |                          |

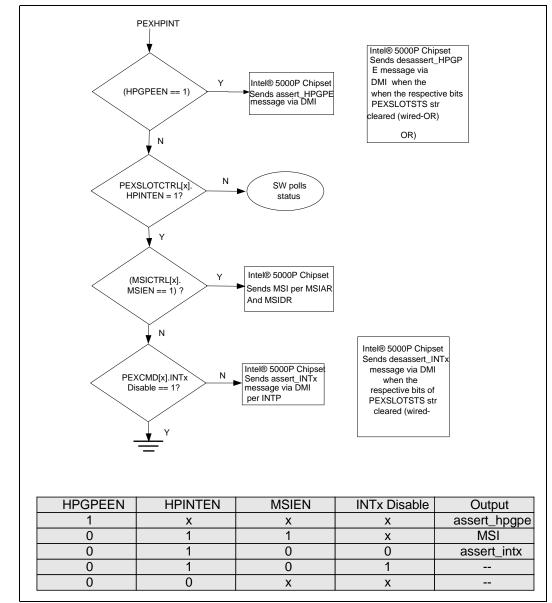

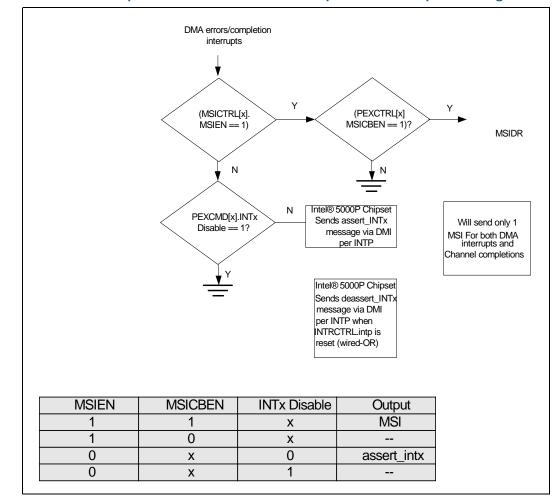

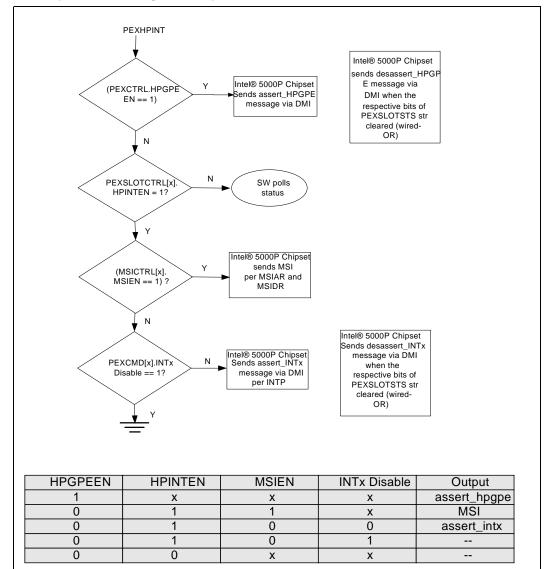

|      |                                      | Intel 5000P Chipset Generation of MSIs            |                          |

| 5.9  |                                      | /8259 Interrupts                                  |                          |

| 5.10 | Interru                              | pt Error Handling                                 | 339                      |

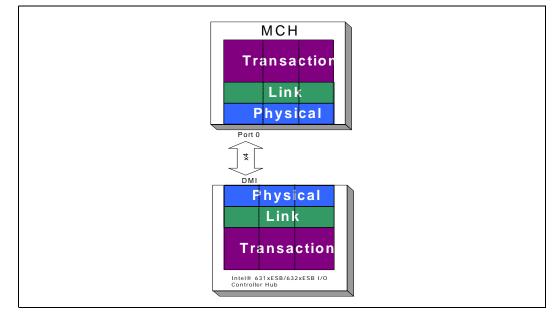

| 5.11 |                                      | ise South Bridge Interface (ESI)                  |                          |

|      |                                      | Power Management Support                          |                          |

|      |                                      | Special Interrupt Support                         |                          |

|      |                                      | Inbound Interrupts                                |                          |

|      |                                      | Legacy Interrupt Messages                         |                          |

|      | 5.11.5                               | End-of-Interrupt (EOI) Support                    | 342                      |

|      | 5.11.6                               | Error Handling                                    | 342                      |

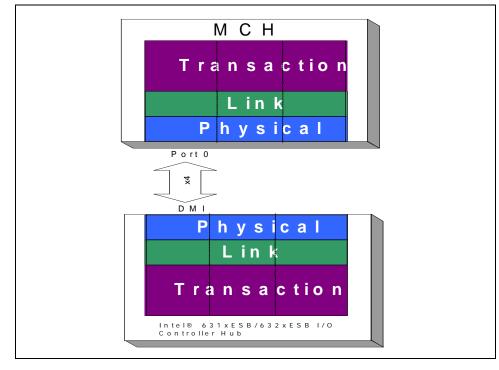

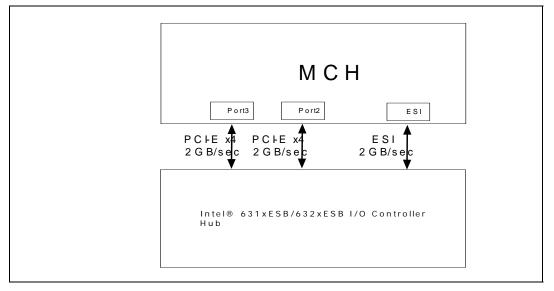

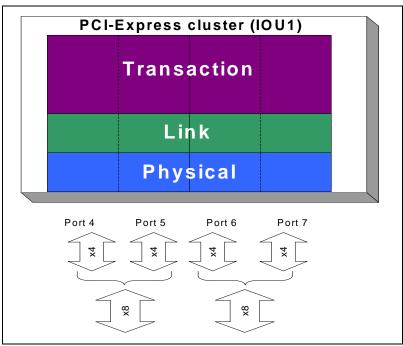

| 5.12 | PCI Exp                              | press Ports                                       | 342                      |

|      | 5.12.1                               | Intel 5000P Chipset MCH PCI Express Port Overview | 343                      |

|      | 5.12.2                               | Enterprise South Bridge Interface (ESI)           | 344                      |

|      | 5.12.3                               | PCI Express Ports 2 and 3                         | 344                      |

|      | 5.12.4                               | PCI Express General Purpose Ports                 | 345                      |

|      | 5.12.5                               | Supported Length Width Port Partitioning          | 346                      |

|      |                                      | PCI Express Port Support Summary                  |                          |

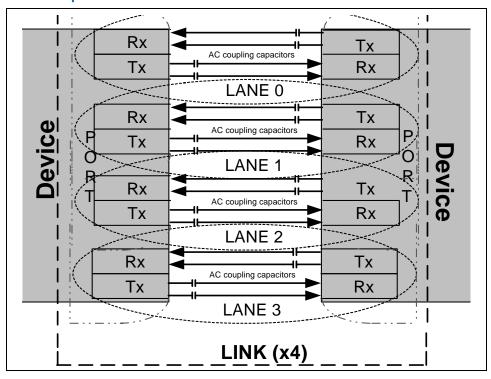

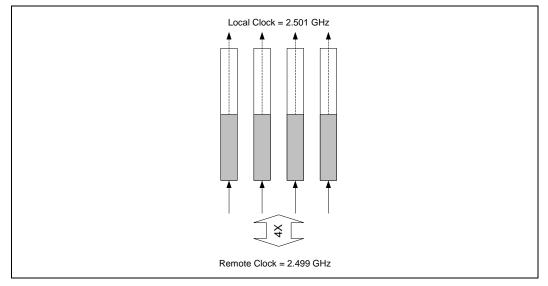

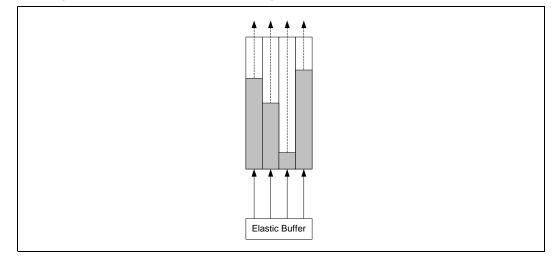

|      |                                      | PCI Express Port Physical Layer Characteristics   |                          |

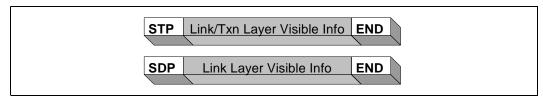

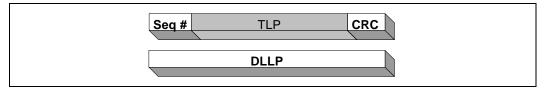

|      |                                      | Link Layer                                        |                          |

|      |                                      | Flow Control                                      |                          |

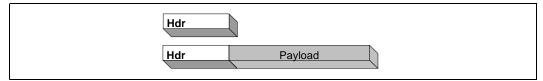

|      |                                      | )Transaction Layer                                |                          |

| 5.13 |                                      | Management                                        |                          |

|      |                                      | Supported ACPI States                             |                          |

|      |                                      | FB-DIMM Thermal Management                        |                          |

|      |                                      | FB-DIMM Thermal Diode Overview                    |                          |

| 5.14 |                                      | Reset                                             |                          |

|      |                                      |                                                   |                          |

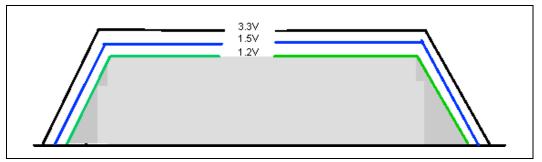

|      |                                      | MCH Power Sequencing                              |                          |

|      | 5.14.1                               | MCH Power Sequencing<br>MCH Reset Types           | 355                      |

|      | 5.14.1<br>5.14.2                     | MCH Reset Types                                   | 355<br>356               |

|      | 5.14.1<br>5.14.2<br>5.14.3           | MCH Reset Types<br>Targeted Reset Mechanism       | 355<br>356<br>357        |

|      | 5.14.1<br>5.14.2<br>5.14.3<br>5.14.4 | MCH Reset Types                                   | 355<br>356<br>357<br>358 |

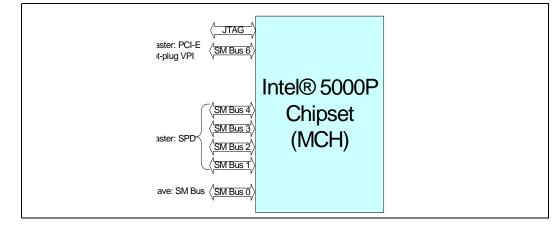

|   | 5.15                                                              | 5.15.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Interfaces Description<br>Internal Access Mechanism<br>SMBus Transaction Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 360                                                                                                                                                                         |

|---|-------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

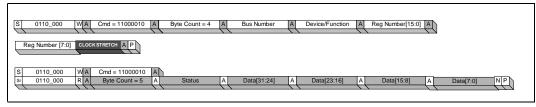

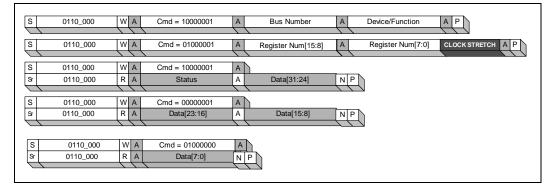

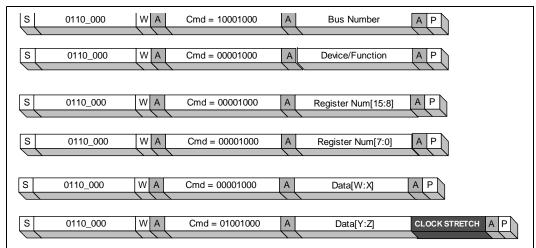

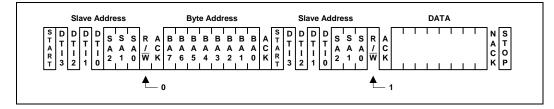

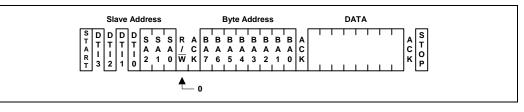

|   |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SMB Transaction Pictographs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                             |

|   |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Slave SM Bus, SM Bus 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                             |

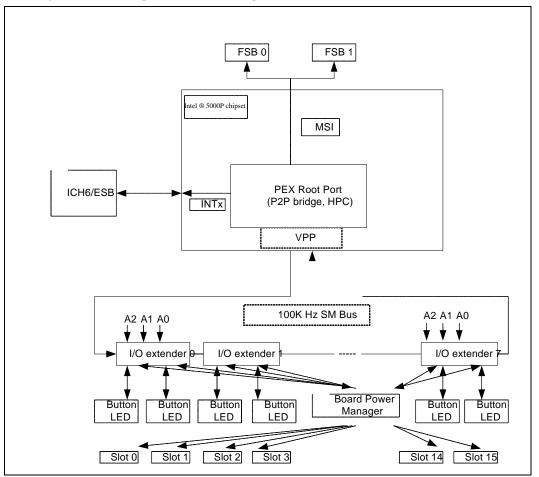

|   |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | FB-DIMM SPD Interface, SM Buses 1, 2, 3 and 4<br>PCI Express Hot-Plug Support, SM Bus 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                             |

|   |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Hot-Plug Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                             |

|   |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | PCI Express Hot-Plug Usage Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                             |

|   |                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Virtual Pin Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                             |

|   | 5.16                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ıg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                             |