# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I<sup>2</sup>C

#### **General Description**

The MAX5971B is a single-port power controller designed for use in IEEE® 802.3af/at-compliant power-sourcing equipment (PSE). This device provides powered device (PD) discovery, classification, current limit, and DC and AC load-disconnect detections. The MAX5971B supports both fully automatic operation and software programmability, and features an integrated power MOSFET and sense resistor. The device supports detection and classification operation from a single 54V supply. In addition, it supports 2-event classification and new Class 5 classification of high-power PDs. The MAX5971B provides up to 40W to a single port (Class 5 enabled) and still provides high-capacitance detection for legacy PDs.

The device provides four operating modes to suit different system requirements. By default, auto mode allows the device to operate automatically at its default settings without any software. Semiautomatic mode automatically detects and classifies a device connected to the port after initial software activation, but does not power the port until instructed to by software. Manual mode allows total software control of the device and is useful for system diagnostics. Shutdown mode terminates all port activities and securely turns off power to the port.

The IC features an I<sup>2</sup>C-compatible, 2-wire serial interface, and is fully software-configurable and programmable. The device provides instantaneous readout of port current through the I<sup>2</sup>C interface. The device's extensive programmability enhances system flexibility, enables field diagnosis and allows for uses in other, non standard applications.

The device provides input undervoltage lockout (UVLO), input undervoltage detection, input overvoltage lockout, overtemperature protection, output voltage slew-rate limit during startup, and LED status indication. The MAX5971B programmability includes startup timeout, overcurrent timeout, and load-disconnect detection timeout.

The device is available in a space-saving, 28-pin TQFN (5mm  $\times$  5mm) power package and is rated for the extended (-40°C to +105°C) temperature range.

#### \_Applications

Single-Port PSE End-Point Applications

Single-Port PSE Power Injectors (Midspan Applications)

Switches/Routers

IEEE is a registered service mark of the Institute of Electrical and Electronics Engineers, Inc.

#### **Features**

- ♦ IEEE 802.3af/at Compliant

- ♦ Up to 40W for Single-Port PSE Applications

- ♦ Integrated Power MOSFET and Sense Resistor

- ♦ Supports 54V Single-Supply Operation

- **♦ PD Detection and Classification**

- ♦ I<sup>2</sup>C-Compatible, 2-Wire Serial Interface

- ♦ Instantaneous Readout of Port Current Through I<sup>2</sup>C Interface

- ♦ Programmable Current Limit for Class 5 PDs

- ♦ High-Capacitance Detection for Legacy Devices

- ♦ Supports Both DC and AC Load Removal Detections

- ♦ Current Foldback and Duty-Cycle-Controlled Current Limit

- **♦ LED Indicator for Port Status**

- ♦ Direct Fast-Shutdown Control Capability

- ♦ Space-Saving, 28-Pin TQFN (5mm x 5mm) Power Package

#### **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE |  |  |

|--------------|-----------------|-------------|--|--|

| MAX5971BETI+ | -40°C to +105°C | 28 TQFN-EP* |  |  |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

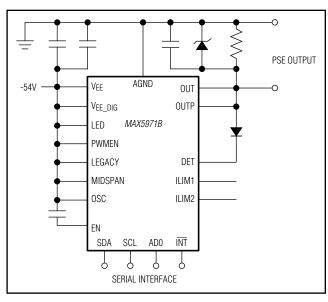

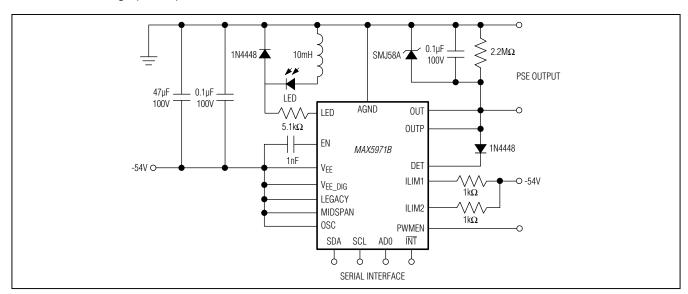

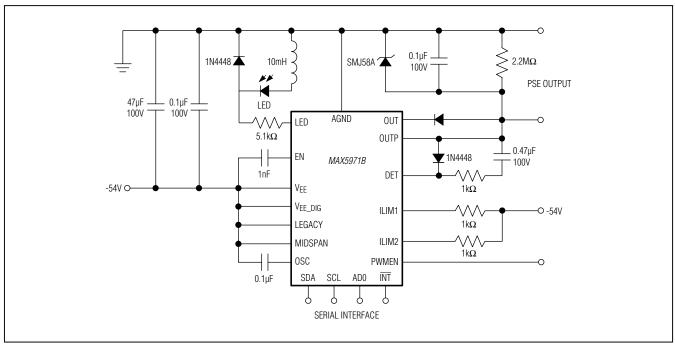

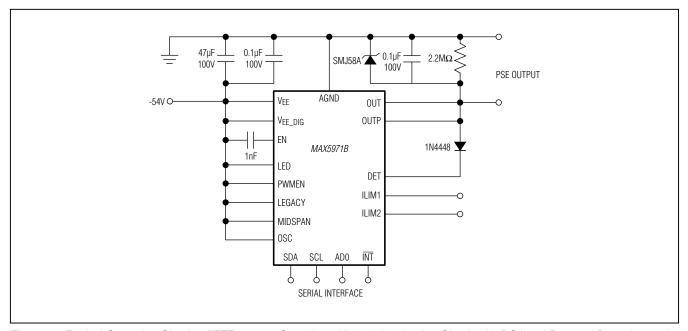

### **Typical Operating Circuit**

<sup>\*</sup>EP = Exposed pad.

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

#### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages referenced to VEE, unless otherwise noted.) | Maximum Current into LED40mA                     |

|-------------------------------------------------------|--------------------------------------------------|

| AGND, DET, LED0.3V to +80V                            | Maximum Current into OUTInternally Regulated     |

| OUT0.3V to (VAGND + 0.3V)                             | Continuous Power Dissipation (TA = +70°C)        |

| OUTP6V to (V <sub>AGND</sub> + 0.3V)                  | 28-Pin TQFN (derate 34.5mW/°C above +70°C)2758mW |

| VEE_DIG0.3V to +0.3V                                  | Operating Temperature Range40°C to +105°C        |

| OSC0.3V to +6V                                        | Storage Temperature Range65°C to +150°C          |

| EN, PWMEN, MIDSPAN, LEGACY, ILIM1, ILIM20.3V to +4V   | Junction Temperature+150°C                       |

| ĪNT, AD0, SCL, SDA0.3V to +6V                         | Lead Temperature (soldering, 10s)+300°C          |

| Maximum Current into INT and SDA80mA                  | Soldering Temperature (reflow)+260°C             |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### PACKAGE THERMAL CHARACTERISTICS (Note 1)

28 TOFN

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......29°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )...........2°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AGND} - V_{EE} = 32V \text{ to } 60V, T_{A} = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ all voltages are referenced to } V_{EE}, \text{ unless otherwise noted. Typical values are at } V_{AGND} - V_{EE} = +54V, T_{A} = +25^{\circ}\text{C}.$  Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                   | SYMBOL    |                                                                           | CONDITIONS                                                      | MIN | TYP | MAX | UNITS |  |  |

|---------------------------------------------|-----------|---------------------------------------------------------------------------|-----------------------------------------------------------------|-----|-----|-----|-------|--|--|

| POWER SUPPLIES                              |           |                                                                           |                                                                 |     |     |     |       |  |  |

| Operating Voltage Range                     | Vagnd     | VAGND - VEE                                                               |                                                                 | 32  |     | 60  | V     |  |  |

| Supply Current                              | IEE       |                                                                           | l logic inputs unconnected,<br>GND in power mode                |     | 2.5 | 4   | mA    |  |  |

| CURRENT LIMIT                               |           |                                                                           |                                                                 |     |     |     |       |  |  |

|                                             |           |                                                                           | ICUT = 010                                                      | 98  | 126 | 155 |       |  |  |

|                                             |           |                                                                           | ICUT = 011                                                      | 185 | 223 | 265 |       |  |  |

|                                             |           | Manipania                                                                 | Class 0, 1, 2, 3 or ICUT = 000                                  | 400 | 420 | 441 | mA    |  |  |

|                                             | ILIM      | Maximum ILOAD allowed during current-limit conditions, VOUT = 0V (Note 3) | Class 4 or ICUT = 001                                           | 684 | 720 | 756 |       |  |  |

| Current Limit                               |           |                                                                           | Class 5 if ILIM1 = VEE,<br>ILIM2 = unconnected or<br>ICUT = 101 | 807 | 850 | 893 |       |  |  |

|                                             |           |                                                                           | Class 5 if ILIM1 = unconnected, ILIM2 = VEE or ICUT = 110       | 855 | 900 | 945 |       |  |  |

|                                             |           |                                                                           | Class 5 if ILIM1 = VEE,<br>ILIM2 = VEE or ICUT = 111            | 902 | 950 | 998 |       |  |  |

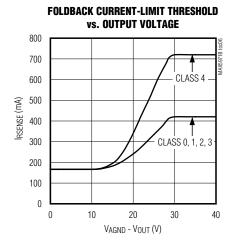

| Foldback Initial OUT Voltage                | VFLBK_ST  | VAGND - VOUT<br>limit starts foldi                                        |                                                                 | 27  |     | V   |       |  |  |

| Foldback Final OUT Voltage                  | VFLBK_END | VAGND - VOUT<br>limit reaches I <sub>T</sub>                              |                                                                 | 10  |     | V   |       |  |  |

| Minimum Foldback Current-Limit<br>Threshold | ITH_FB    | Vout = Vagnd                                                              |                                                                 |     | 166 |     | mA    |  |  |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAGND - VEE = 32V \text{ to } 60V, TA = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ all voltages are referenced to VEE, unless otherwise noted.}$  Typical values are at  $VAGND - VEE = +54V, TA = +25^{\circ}\text{C}$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                   | SYMBOL            |                                               | MIN   | TYP                                                             | MAX | UNITS |     |    |

|---------------------------------------------|-------------------|-----------------------------------------------|-------|-----------------------------------------------------------------|-----|-------|-----|----|

| OVERCURRENT                                 |                   |                                               |       |                                                                 |     |       |     |    |

|                                             |                   |                                               | ICUT  | = 010                                                           | 86  | 111   | 136 |    |

|                                             |                   |                                               | ICUT  | = 011                                                           | 162 | 196   | 233 |    |

|                                             |                   |                                               |       | s 0, 1, 2, 3 or<br>= 000                                        | 351 | 370   | 389 |    |

|                                             |                   | Overcurrent                                   | Class | s 4 or ICUT = 001                                               | 602 | 634   | 666 |    |

| Overcurrent Threshold                       | Ісит              | threshold<br>allowed for t ≤<br>tFAULT, VOUT  | ILIM  | s 5 if ILIM1 = V <sub>EE</sub> ,<br>2 = unconnected or<br>= 101 | 710 | 748   | 785 | mA |

|                                             |                   | = 0V (Note 3)                                 | unco  | s 5 if ILIM1 =<br>nnected, ILIM2 = VEE<br>UT = 110              | 752 | 792   | 832 |    |

|                                             |                   |                                               | 1     | s 5 if ILIM1 = VEE,<br>2 = VEE or ICUT = 111                    | 794 | 836   | 878 |    |

| INTERNAL POWER                              |                   |                                               |       |                                                                 |     |       |     |    |

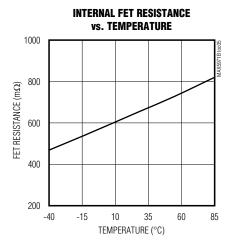

| DMOS On-Resistance                          |                   | Measured from                                 |       | T <sub>A</sub> = +25°C                                          |     | 0.5   | 0.9 | Ω  |

| DIVIOS On-Resistance                        |                   | OUT to VEE, IOUT = 100mA                      |       | T <sub>A</sub> = +105°C                                         |     | 0.6   | 1.3 |    |

| Power-Off OUT Leakage Current               | IOUT_LEAK         | VEN = VEE, VOUT = VAGND                       |       |                                                                 |     |       | 10  | μΑ |

| SUPPLY MONITORS                             |                   |                                               |       |                                                                 |     |       |     |    |

| VEE Undervoltage Lockout                    | VEE_UVLO          | VAGND - VEE, V                                |       | 28.5                                                            |     | V     |     |    |

| VEE Undervoltage Lockout<br>Hysteresis      | VEE_UVLOH         | Port is shutdow<br>UVLO - VEE_UVI             |       | 3                                                               |     | V     |     |    |

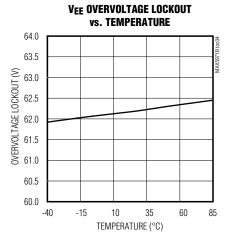

| VEE Overvoltage Lockout                     | VEE_OV            | VAGND - VEE >                                 | VEE_C | DV, VAGND increasing                                            |     | 62.5  |     | V  |

| VEE Overvoltage Lockout<br>Hysteresis       | VEE_OVH           |                                               |       |                                                                 |     | 1     |     | V  |

| VEE Undervoltage                            | VEE_UV            | VEE_UV event b                                |       | s if: VAGND - VEE <                                             |     | 40    |     | V  |

| Thermal Shutdown Threshold                  | T <sub>SHD</sub>  | Port is shut down junction temperature income |       | +150                                                            |     | °C    |     |    |

| Thermal Shutdown Hysteresis                 | TSHDH             | Temperature decreasing                        |       |                                                                 |     | 20    |     | °C |

| OUTPUT MONITOR                              |                   |                                               |       |                                                                 |     |       |     |    |

| OUT Input Current                           | IBOUT             | Vout = Vagno, probing phases                  |       |                                                                 |     |       | 6   | μΑ |

| Idle Pullup Current at OUT                  | IDIS              | OUTP discharg classification of VOUTP = VAGN  | 200   |                                                                 | 265 | μΑ    |     |    |

| Short to VEE Detection Threshold            | DCNTH             | VOUT - VEE, VO<br>during detectio             | 1.5   | 2.0                                                             | 2.5 | V     |     |    |

| Short to VEE Detection Threshold Hysteresis | DCN <sub>HY</sub> |                                               |       |                                                                 |     | 220   |     | mV |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

# **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AGND} - V_{EE} = 32V \text{ to } 60V, T_{A} = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ all voltages are referenced to } V_{EE}, \text{ unless otherwise noted.}$  Typical values are at VAGND - VEE = +54V, TA = +25°C. Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                         | SYMBOL             | COND                                                                                    | ITIONS                       | MIN  | TYP  | MAX  | UNITS |  |

|---------------------------------------------------|--------------------|-----------------------------------------------------------------------------------------|------------------------------|------|------|------|-------|--|

| LOAD DISCONNECT                                   |                    |                                                                                         |                              |      |      |      |       |  |

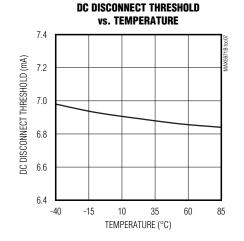

| DC Load-Disconnect Threshold                      | IDC_TH             | Minimum load curren<br>disconnect (DC disco<br>VOUT = 0V                                |                              | 5    | 7.5  | 10   | mA    |  |

| AC Load-Disconnect Threshold (Note 4)             | I <sub>AC_TH</sub> | Current into DET, for port powers off (AC of                                            |                              | 115  | 130  | 145  | μΑ    |  |

| Triangular Wave Peak-to-Peak<br>Voltage Amplitude | AMPTRW             | Measured at DET, re                                                                     | ferred to AGND               | 3.85 | 4    | 4.2  | V     |  |

| OSC Pullup/Pulldown Currents                      | losc               | Measured at OSC                                                                         |                              | 26   | 32   | 39   | μΑ    |  |

| ACD_EN Threshold                                  | VACD_EN            | VOSC - VEE > VACD_<br>disconnect                                                        | EN to activate AC            | 270  | 330  | 380  | mV    |  |

| Load-Disconnect Timer                             | tDISC              | Time from IRSENSE < disconnect active) or disconnect active) to (Note 5)                | 300                          |      | 400  | ms   |       |  |

| DETECTION                                         |                    |                                                                                         |                              |      |      |      |       |  |

| Detection Probe Voltage<br>(First Phase)          | VDPH1              | VAGND - VDET during phase                                                               | 3.8                          | 4    | 4.2  | V    |       |  |

| Detection Probe Voltage<br>(Second Phase)         | V <sub>DPH2</sub>  | VAGND - VDET during phase                                                               | 9                            | 9.3  | 9.6  | V    |       |  |

| Current-Limit Protection                          | I <sub>DLIM</sub>  | VDET = VAGND during current through DET                                                 | 1.50                         | 1.75 | 2.00 | mA   |       |  |

| Short-Circuit Threshold                           | VDCP               | If V <sub>AGND</sub> - V <sub>OUT</sub> < V <sub>I</sub> detection phase a sh detected. |                              | 1    |      | V    |       |  |

| Open-Circuit Threshold                            | ID_OPEN            | First point measurem for open condition                                                 |                              | 20   |      | μΑ   |       |  |

| Resistor Detection Window                         | RDOK               | (Note 6)                                                                                |                              | 19   |      | 26.5 | kΩ    |  |

| Resistor Rejection Window                         | R <sub>DBAD</sub>  | Detection rejects low<br>Detection rejects hig                                          |                              | 32   |      | 15.5 | kΩ    |  |

| CLASSIFICATION                                    |                    |                                                                                         |                              |      |      |      |       |  |

| Classification Probe Voltage                      | VCL                | VAGND - VDET during                                                                     | 16                           |      | 20   | V    |       |  |

| Current-Limit Protection                          | ICILIM             | VDET = VAGND, during measure current thro                                               | 65                           |      | 80   | mA   |       |  |

|                                                   |                    |                                                                                         | Class 0, Class 1             | 5.5  | 6.5  | 7.5  |       |  |

|                                                   |                    | Olympia in                                                                              | Class 1, Class 2             | 13.0 | 14.5 | 16.0 |       |  |

| Classification Current Thresholds                 | lo                 | Classification current thresholds between                                               | Class 2, Class 3             | 21   | 23   | 25   | mA    |  |

| Ciassification Current Thresholds                 | ICL                | classes                                                                                 | Class 3, Class 4             | 31   | 33   | 35   |       |  |

|                                                   |                    |                                                                                         | Class 4 upper limit (Note 7) | 45   | 48   | 51   |       |  |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AGND} - V_{EE} = 32V \text{ to } 60V, T_{A} = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ all voltages are referenced to } V_{EE}, \text{ unless otherwise noted.}$  Typical values are at VAGND - VEE = +54V, TA = +25°C. Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                     | SYMBOL               |                                                                                                     | MIN | TYP            | MAX | UNITS |

|-------------------------------|----------------------|-----------------------------------------------------------------------------------------------------|-----|----------------|-----|-------|

| Mark Event Voltage            | VMARK                | VAGND - VDET during mark event                                                                      | 8   |                | 10  | V     |

| Mark Event Current Limit      | IMARK_LIM            | V <sub>DET</sub> = V <sub>AGND</sub> during mark event measure current through DET                  | 55  |                | 80  | mA    |

| DIGITAL INPUTS/OUTPUTS (Vo    | tages Refere         | enced to VEE)                                                                                       |     |                |     |       |

| Digital Input Low             | V <sub>I</sub> L     |                                                                                                     |     |                | 0.8 | V     |

| Digital Input High            | ViH                  |                                                                                                     | 2.4 |                |     | V     |

| Internal Input Pullup Current | IPU                  | Pullup current to internal digital supply to set default values                                     | 3   | 5              | 7   | μA    |

| Open-Drain Output Low Voltage | VoL                  | ISINK = 10mA                                                                                        |     |                | 0.4 | V     |

| Open-Drain Leakage            | loL                  | Open-drain high impedance                                                                           |     |                | 2   | μA    |

| LED Output Low Voltage        | VLED_LOW             | ILED = 10mA, PWM disabled, port power-on                                                            |     |                | 0.8 | V     |

| LED Output Leakage            | ILED_LEAK            | PWM disabled, shutdown mode, VLED = 60V                                                             |     |                | 10  | μA    |

| PWM Frequency                 |                      |                                                                                                     |     | 25             |     | kHz   |

| PWM Duty Cycle                |                      |                                                                                                     |     | 6.25           |     | %     |

| TIMING                        | •                    |                                                                                                     |     |                |     |       |

| Startup Time                  | tstart               | Time during which a current limit set to 420mA is allowed, starts when power is turned on (Note 8)  | 50  | 60             | 70  | ms    |

| Fault Time                    | tFAULT               | Maximum allowed time for an overcurrent condition set by ICUT after startup (Note 8)                | 50  | 60             | 70  | ms    |

| Detection Reset Time          | t <sub>ME</sub>      | Time allowed for the port voltage to reset before detection starts                                  |     | 80             | 90  | ms    |

| Detection Time                | tDET                 | Maximum time allowed before detection is completed                                                  |     |                | 330 | ms    |

| Midspan Mode Detection Delay  | tDMID                |                                                                                                     | 2   | 2.2            | 2.4 | S     |

| Classification Time           | tCLASS               | Time allowed for classification                                                                     |     | 19             | 23  | ms    |

| Mark Event Time               |                      | Time allowed for mark event                                                                         | 7   | 9              | 11  | ms    |

| VEE_UVLO Turn-On Delay        | tDLY                 | Time V <sub>AGND</sub> must be above the V <sub>EE_UVLO</sub> thresholds before the device operates |     | 5.2            |     | ms    |

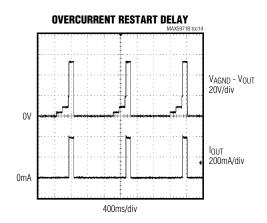

| Restart Timer                 | <sup>t</sup> RESTART | Time the device waits before turning on after an overcurrent fault (Note 8)                         |     | 16 x<br>tfault |     | ms    |

| Watchdog Clock Period         |                      | Rate of decrement of the watchdog time                                                              |     | 164            |     | ms    |

| ADC PERFORMANCE (Power-O      | n Mode)              |                                                                                                     |     |                |     |       |

| Resolution                    |                      |                                                                                                     |     | 9              |     | Bits  |

| Range                         |                      |                                                                                                     |     | 1              |     | А     |

| LSB Step Size                 |                      |                                                                                                     |     | 1.95           |     | mA    |

| Gain Error                    |                      | T <sub>A</sub> = +25°C                                                                              |     |                | 2   | %     |

| Guil Elloi                    |                      | $T_A = -40$ °C to $+105$ °C                                                                         |     | 3              |     | /6    |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(VAGND - VEE = 32V \text{ to } 60V, TA = -40^{\circ}\text{C} \text{ to } +105^{\circ}\text{C}, \text{ all voltages are referenced to } VEE, unless otherwise noted. Typical values are at VAGND - VEE = +54V, TA = +25^{\circ}\text{C}$ . Currents are positive when entering the pin and negative otherwise.) (Note 2)

| PARAMETER                                        | SYMBOL         | CONDITIONS                                                                        | MIN                       | TYP | MAX | UNITS |  |

|--------------------------------------------------|----------------|-----------------------------------------------------------------------------------|---------------------------|-----|-----|-------|--|

| ADC Absolute Assures                             |                | IOUT = 400mA, TA = +25°C                                                          | 201                       | 205 | 209 | LCD   |  |

| ADC Absolute Accuracy                            |                | $I_{OUT} = 400 \text{mA}, T_{A} = -40 ^{\circ}\text{C to } +105 ^{\circ}\text{C}$ |                           | 205 |     | LSB   |  |

| Integral Newline exity                           | INL            | TA = +25°C                                                                        |                           | 0.3 | 1.5 | LOD   |  |

| Integral Nonlinearity                            | IINL           | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                                    |                           | 0.3 |     | LSB   |  |

| Differential Nonlinearity                        | DNL            | TA = +25°C                                                                        |                           | 0.3 | 1.5 | LSB   |  |

| Differential Northneamty                         | DINL           | $T_A = -40^{\circ}C \text{ to } +105^{\circ}C$                                    |                           | 0.3 |     | LOD   |  |

| TIMING CHARACTERISTICS (Fo                       | r 2-Wire Fas   | t Mode)                                                                           |                           |     | -   |       |  |

| Serial Clock Frequency                           | fscl           |                                                                                   | 100                       |     | 400 | kHz   |  |

| Bus Free Time Between a STOP and START Condition | tBUF           |                                                                                   | 1.3                       |     |     | μs    |  |

| Hold Time for a START Condition                  | tHD,STA        |                                                                                   | 0.6                       |     |     | μs    |  |

| Low Period of the SCL Clock                      | tLOW           |                                                                                   | 1.3                       |     |     | μs    |  |

| High Period of the SCL Clock                     | tHIGH          |                                                                                   | 0.6                       |     |     | μs    |  |

| Setup Time for a Repeated START Condition        | tsu,sta        |                                                                                   | 0.6                       |     |     | μs    |  |

| Data Hold Time                                   | thd,dat        |                                                                                   | 0                         |     | 150 | ns    |  |

| Data in Setup Time                               | tsu,dat        |                                                                                   | 100                       |     |     | ns    |  |

| Rise Time of Both SDA and SCL Signals, Receiving | t <sub>R</sub> | (Note 9)                                                                          | 20 +<br>0.1C <sub>B</sub> |     | 300 | ns    |  |

| Fall Time of SDA Transmitting                    | tF             | (Note 9)                                                                          |                           |     | 250 | ns    |  |

| Setup Time for STOP Condition                    | tsu,sto        |                                                                                   | 0.6                       |     |     | μs    |  |

| Capacitive Load for Each<br>Bus Line             | СВ             | (Note 9)                                                                          |                           |     | 400 | рF    |  |

| Pulse Width of Spike<br>Suppressed               | tsp            | (Note 9)                                                                          |                           | 50  |     | ns    |  |

- Note 2: This device is production tested at  $T_A = +25^{\circ}$ C. Limits to  $T_A = -40^{\circ}$ C to  $+105^{\circ}$ C are guaranteed by design.

- **Note 3:** Default thresholds are set by the classification result in auto mode. The thresholds are manually software programmable through the ICUT Register (R2Ah[2:0]). If ILIM1 and ILIM2 are both unconnected, Class 5 detection is disabled. See the Class 5 PD Classification section and Table 3 for details and settings.

- Note 4: Default value. The AC load-disconnect threshold can be programmed through the AC\_TH register (R23h[2:0]).

- Note 5: Default value. The load-disconnect time, tDISC can be programmed through the TDISC register (R16h[1:0]).

- Note 6: RDOK = (VOUT2 VOUT1)/(IDET2 IDET1). VOUT1, VOUT2, IDET2, and IDET1 represent the voltage at OUT and the current at DET during phase 1 and 2 of the detection, respectively.

- Note 7: If Class 5 is enabled, this value is the classification current threshold from Class 4 to Class 5.

- Note 8: Default values. The startup, fault, and restart timers can be programmed through the TSTART (R16h[5:4]), TFAULT (R16h[3:2]), and RSRT (R16h[7:6]) registers, respectively.

- Note 9: Guaranteed by design. Not subject to production testing.

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

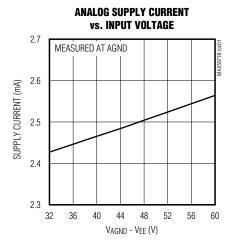

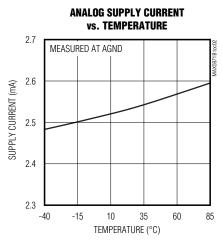

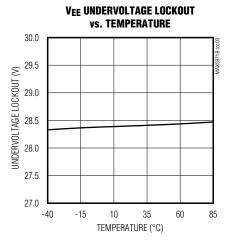

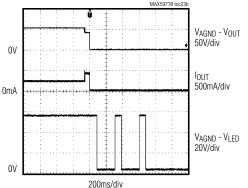

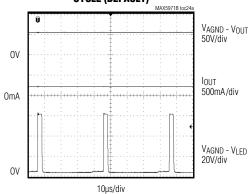

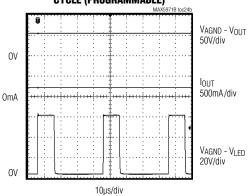

### **Typical Operating Characteristics**

(VAGND = 54V, VEE = VEE\_DIG = 0V, TA = +25°C, endpoint mode and default register settings with a Class 0 PD, unless otherwise otherwise noted.)

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

### **Typical Operating Characteristics (continued)**

(VAGND = 54V, VEE = VEE\_DIG = 0V, TA = +25°C, endpoint mode and default register settings with a Class 0 PD, unless otherwise otherwise noted.)

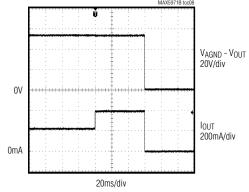

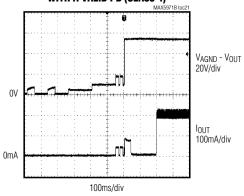

#### OVERCURRENT TIMEOUT (240 $\Omega$ TO 138 $\Omega$ )

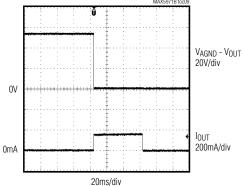

#### SHORT-CIRCUIT RESPONSE TIME

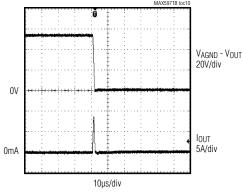

#### SHORT-CIRCUIT TRANSIENT RESPONSE

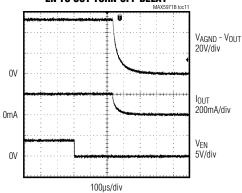

#### **EN TO OUT TURN-OFF DELAY**

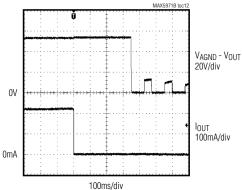

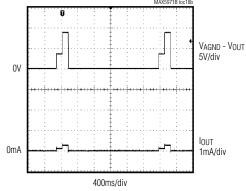

# ZERO-CURRENT DETECTION WAVEFORM WITH DC DISCONNECT ENABLED

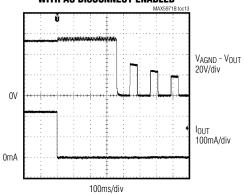

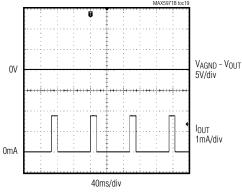

# ZERO-CURRENT DETECTION WAVEFORM WITH AC DISCONNECT ENABLED

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

### **Typical Operating Characteristics (continued)**

(VAGND = 54V, VEE = VEE\_DIG = 0V, TA = +25°C, endpoint mode and default register settings with a Class 0 PD, unless otherwise otherwise noted.)

# DETECTION WITH INVALID PD (25kΩ AND 10μF) MAXS9718 Ibc15a VAGND - VOUT 1V/div OMA 40ms/div

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

### Typical Operating Characteristics (continued)

$(V_{AGND} = 54V, V_{EE} = V_{EE\_DIG} = 0V, T_{A} = +25^{\circ}C$ , endpoint mode and default register settings with a Class 0 PD, unless otherwise otherwise noted.)

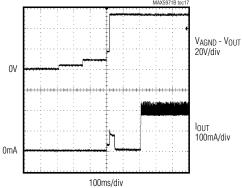

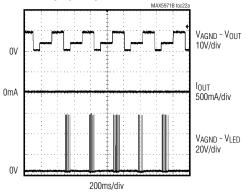

#### STARTUP IN MIDSPAN WITH A VALID PD

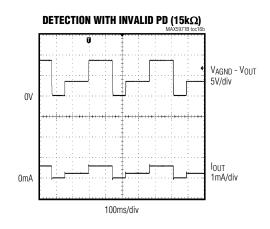

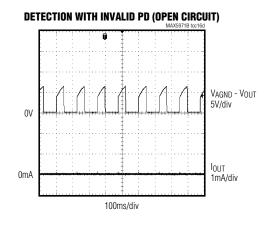

#### DETECTION IN MIDSPAN WITH INVALID PD (15 $k\Omega$ )

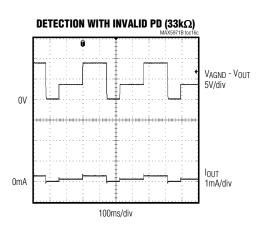

#### DETECTION IN MIDSPAN WITH INVALID PD (33 $k\Omega$ )

**DETECTION WITH OUTPUT SHORTED TO AGND**

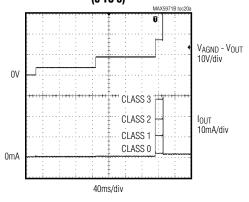

# CLASSIFICATION WITH DIFFERENT PD CLASSES (0 TO 3)

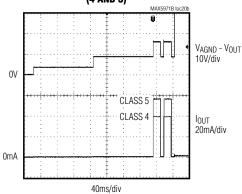

# CLASSIFICATION WITH DIFFERENT PD CLASSES (4 AND 5)

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

### **Typical Operating Characteristics (continued)**

$(V_{AGND} = 54V, V_{EE} = V_{EE\_DIG} = 0V, T_{A} = +25^{\circ}C$ , endpoint mode and default register settings with a Class 0 PD, unless otherwise otherwise noted.)

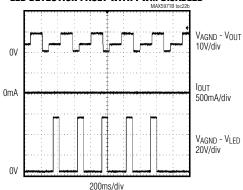

# STARTUP USING 2-EVENT CLASSIFICATION WITH A VALID PD (CLASS 4)

#### **LED DETECTION FAULT WITH PWM ENABLED**

#### **LED DETECTION FAULT WITH PWM DISABLED**

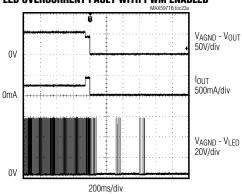

#### LED OVERCURRENT FAULT WITH PWM ENABLED

#### LED OVERCURRENT FAULT WITH PWM DISABLED

# LED PWM TIMING: MINIMUM DUTY CYCLE (DEFAULT)

# LED PWM TIMING: MAXIMUM DUTY CYCLE (PROGRAMMABLE)

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

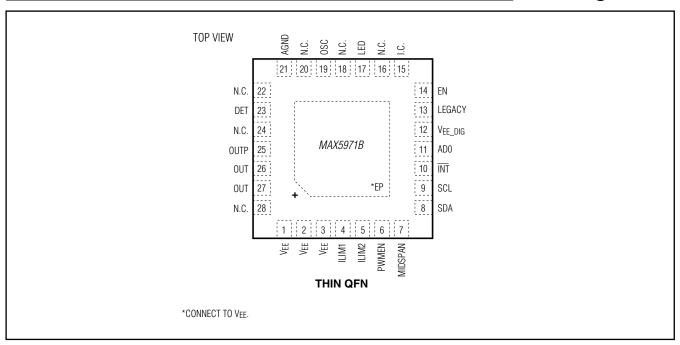

### **Pin Configuration**

# Pin Description

| PIN     | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                                           |

|---------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 3 | VEE     | Analog Low-Side Supply Input. Bypass with an external 100V, 47µF capacitor in parallel with a 100V, 0.1µF ceramic capacitor between AGND and VEE.                                                                                                                                                                                                                                  |

| 4       | ILIM1   | Class 5 Current-Limit Digital Adjust 1. Referenced to VEE. ILIM1 is internally pulled up to the digital supply. Use ILIM1 with ILIM2 to enable Class 5 operation and to adjust the Class 5 current-limit value. See the <i>Electrical Characteristics</i> table and Table 3 in the <i>Class 5 PD Classification</i> section for details.                                           |

| 5       | ILIM2   | Class 5 Current-Limit Digital Adjust 2. Referenced to VEE. ILIM2 is internally pulled up to the digital supply. Use ILIM2 with ILIM1 to enable Class 5 operation and to adjust the Class 5 current-limit value. See the <i>Electrical Characteristics</i> table and Table 3 in the <i>Class 5 PD Classification</i> section for details.                                           |

| 6       | PWMEN   | PWM Control Logic Input. Referenced to V <sub>EE</sub> . PWMEN is internally pulled up to the digital supply. Leave unconnected to enable the internal PWM to drive the LED pin. Force low to disable the internal PWM.                                                                                                                                                            |

| 7       | MIDSPAN | Detection Collision Avoidance Logic Input. Referenced to VEE. MIDSPAN is internally pulled up to the digital supply. Leave unconnected to activate the detection collision avoidance circuitry for midspan PSE systems. Force low to disable this function for an end-point PSE system. The MIDSPAN logic level latches after the device is powered up or after a reset condition. |

| 8       | SDA     | 2-Wire Serial Interface Input/Output Data Line. Referenced to VEE. Connect to VEE if the I <sup>2</sup> C interface is not used.                                                                                                                                                                                                                                                   |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

### Pin Description (continued)

| PIN                       | NAME    | FUNCTION                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9                         | SCL     | 2-Wire Serial Interface Input Clock Line. Referenced to VEE. Connect to VEE if the I <sup>2</sup> C interface is not used.                                                                                                                                                                                                                                             |

| 10                        | ĪNT     | Open-Drain Interrupt Output. Referenced to V <sub>EE</sub> . INT is pulled low whenever an interrupt is sent to the microcontroller. See the <i>Interrupt</i> section for details. Connect to V <sub>EE</sub> if the I <sup>2</sup> C interface is not used.                                                                                                           |

| 11                        | AD0     | Address Input. Referenced to VEE. AD0 is used to form the lower part of the device address. See the <i>Device Address (AD0)</i> section and Table 5 for details. Connect to VEE if the I <sup>2</sup> C interface is not used.                                                                                                                                         |

| 12                        | VEE_DIG | Digital Low-Side Supply Input. Connect to VEE externally.                                                                                                                                                                                                                                                                                                              |

| 13                        | LEGACY  | Legacy Detection Logic Input. Referenced to VEE. LEGACY is internally pulled up to the digital supply. Leave unconnected to activate the legacy PD detection. Force low to disable this function. The LEGACY logic level latches after the device is powered up or after a reset condition.                                                                            |

| 14                        | EN      | Enable Input. Referenced to V <sub>EE</sub> . EN is internally pulled up to the digital supply. Leave unconnected to enable the device. Force low for at least 40µs to reset the device. The MIDSPAN, OSC, and LEGACY states latch-in when the reset condition is removed (low-to-high transition). Bypass EN to V <sub>EE</sub> with a 1nF ceramic capacitor.         |

| 15                        | I.C.    | Internally Connected. Connect I.C. to VEE.                                                                                                                                                                                                                                                                                                                             |

| 16, 18, 20,<br>22, 24, 28 | N.C.    | No Connection. Not internally connected. Leave N.C. unconnected.                                                                                                                                                                                                                                                                                                       |

| 17                        | LED     | LED Indicator Open-Drain Output. Referenced to V <sub>EE</sub> . LED can sink 10mA and can drive an external LED directly. Blinking functionality is provided to signal different conditions (see the <i>PWM and LED Signals</i> section). Connect LED to AGND externally (see Figures 15 and 16) or to an external supply (if available) through a series resistance. |

| 19                        | OSC     | AC-Disconnect Triangular Wave Output. Bypass with a 100nF (±10% tolerance) external capacitor to VEE to enable the AC disconnect function. Connect OSC to VEE to disable the AC disconnect function and to activate the DC disconnect function. The OSC state latches after the device is powered up or after a reset condition.                                       |

| 21                        | AGND    | High-Side Supply Input                                                                                                                                                                                                                                                                                                                                                 |

| 23                        | DET     | Detection/Classification Voltage Output. DET is used to set the detection and classification probe voltages and for the AC current sensing when using the AC disconnect function. To use the AC disconnect function, place a $1k\Omega$ and $0.47\mu F$ RC series in parallel with the external protection diode to OUTP (see Figure 16).                              |

| 25                        | OUTP    | Port Pullup Output. OUTP is used to pull up the port voltage to AGND when needed. If AC disconnect is used, connect OUTP to the anode of the AC-blocking diode. If AC disconnect is not used, connect OUTP to OUT (see Figures 15 and 17). Bypass OUTP to AGND with a 100V, 0.1µF ceramic capacitor.                                                                   |

| 26, 27                    | OUT     | Integrated MOSFET Output. If DC disconnect is used, connect the port output to OUTP (see Figures 15 and 17). If the AC disconnect function is used, connect OUT to the cathode of the AC-blocking diode (see Figure 16).                                                                                                                                               |

|                           | EP      | Exposed Pad. Connect EP to VEE externally. See the Layout Procedure section for details.                                                                                                                                                                                                                                                                               |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

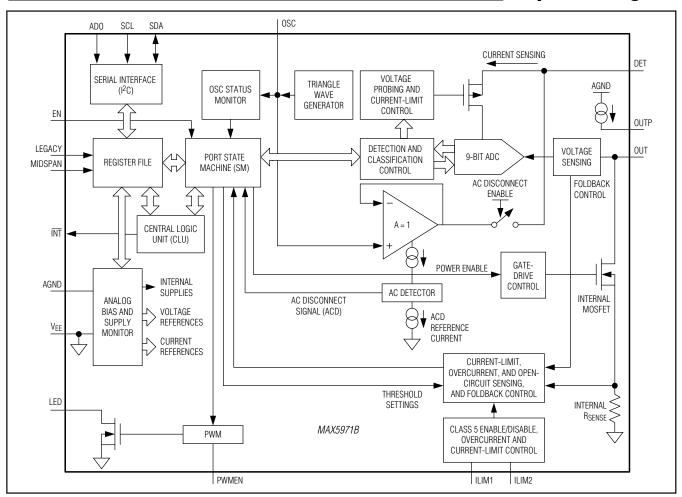

#### Simplified Diagram

#### **Detailed Description**

The MAX5971B is a single-port power controller designed for use in IEEE 802.3af/802.3at-compliant PSE. This device provides PD discovery, classification, current limit, and DC and AC load-disconnect detections. The MAX5971B supports both fully automatic operation and software programmability, and features an integrated power MOSFET and sense resistor. The device also supports new Class 5 and 2-event classification for detection and classification of high-power PDs. The MAX5971B provides up to 40W to a single port (Class 5 enabled), and still provides high-capacitance detection for legacy PDs.

The MAX5971B features an I<sup>2</sup>C-compatible, 2-wire serial interface, and is fully software configurable and programmable. The device provides instantaneous readout

of port current through the I<sup>2</sup>C interface. The MAX5971B provides input undervoltage lockout (UVLO), input undervoltage detection, input overvoltage lockout, overtemperature protection, output voltage slew-rate limit during startup, and LED status indication. The MAX5971B programmability includes startup timeout, overcurrent timeout, and load-disconnect detection timeout.

#### Reset

The MAX5971B is reset by any of the following conditions:

- 1) Power-Up. Reset condition is cleared once VEE rises above the UVLO threshold.

- 2) Hardware Reset. Reset occurs once the EN input is driven low (> 40µs, typ) any time after power-up. The device exits the reset condition once the EN input is driven high again.

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

- Software Reset. To initiate a software reset, write a logical 1 to the RESET\_IC register (R1Ah[4]) any time after power-up. Reset clears automatically and all registers are set to their default states.

- 4) Thermal Shutdown. The device enters thermal shutdown at 150°C. The device exits thermal shutdown and is reset once the temperature drops below 130°C.

At the end of a reset event, the MAX5971B latches in the state of MIDSPAN, LEGACY, and OSC. During normal operation, changes to the MIDSPAN and LEGACY inputs are ignored, and these inputs can be changed at any time prior to the end of a reset state. Changes to OSC input during normal operation can impact device functionality. Therefore, OSC is only changed while the device is held in a reset state (or powered down), and OSC then latches in when the reset state ends (other schematic modifications may be needed, see Figures 15 and 16).

#### **Port Reset**

Set RESET\_P (R1Ah[0]) high anytime during normal operation to turn off port power and clear the port event and status registers. Port reset does not initiate a global device reset.

#### Midspan Mode

In midspan mode, the device adopts cadence timing during the detection phase. When cadence timing is enabled and a failed detection occurs, the port waits between 2s and 2.4s before attempting to detect again. Midspan mode is activated by setting MIDSPAN high and then powering or resetting the device. Alternatively, midspan mode is software enabled by setting BCKOFF (R15h[0], Table 23) to a logical 1. By default, the MIDSPAN input is internally pulled high, enabling cadence timing. Force MIDSPAN low to disable this function.

#### **Operation Modes**

The MAX5971B provides four operating modes to suit different system requirements. By default, auto mode allows the device to operate automatically at its default settings without any software. Semiautomatic mode automatically detects and classifies a device connected to the port after initial software activation, but does not power up the port until instructed to by software. Manual mode allows total software control of the device and is useful for system diagnostics. Shutdown mode terminates all activities and securely turns off power to the port.

Switching between auto, semiautomatic, and manual mode does not interfere with the operation of the output port. When the port is set into shutdown mode, all

port operations are immediately stopped and the port remains idle until shutdown mode is exited.

#### Auto (Automatic) Mode

By default, the MAX5971B enters auto mode after the reset condition is cleared. To manually place the MAX5971B into auto mode from any other mode, set P\_M[1:0] (R12h[1:0]) to [11] during normal operation (see Tables 19 and 20).

In auto mode, the MAX5971B performs detection and classification, and powers up the port automatically if a valid PD is connected to the port. If a valid PD is not connected at the port, the MAX5971B repeats the detection routine continuously until a valid PD is connected.

When entering auto mode, the DET\_EN and CLASS\_EN bits (R14h[0] and R14h[4], Table 22) are set to high and stay high unless changed by software. Using software to set DET\_EN and/or CLASS\_EN low causes the MAX5971B to skip detection and/or classification. As a protection, disabling the detection routine in auto mode does not allow the corresponding port to power up, unless the DET\_BY bit (R23h[4], Table 33) is set to 1.

#### Semiautomatic (Semi) Mode

The MAX5971B is put into semiautomatic mode by setting P\_M[1:0] (R12h[1:0]) to [10] during normal operation (see Tables 19 and 20). In semi mode, the MAX5971B, upon request, performs detection and/or classification repeatedly but does not power up the port. To power the port, set the PWR\_ON bit (R19h[0], Table 27) to 1. This immediately terminates the detection/classification routine and turns on power to the port.

DET\_EN and CLASS\_EN (R14h[0] and R14h[4], Table 22) default to low in semiautomatic mode. Use software to set DET\_EN (R14h[0]) to 1 to start the detection routine and CLASS\_EN (R14h[4]) to 1 to enable classification routine. They are reset every time the software commands a power-off of the port, either through a reset event or by writing a 1 to the PWR\_OFF bit (R19h[4]). In any other case, the status of the bits is left unchanged (including when the state machine turns off the power when a load disconnect or a fault condition is encountered).

#### Manual Mode

The MAX5971B is placed in manual mode by setting P\_M[1:0] (R12h[1:0]) to [01] during normal operation (see Tables 19 and 20). Manual mode allows the software to dictate the sequence of operation. Write a 1 to both R14h[0] (DET\_EN) and R14h[4] (CLASS\_EN) to start detection and classification operations, respectively, and in that priority order. In manual mode, after

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

execution, the command is cleared from the register(s). PWR\_ON has highest priority. Setting PWR\_ON to 1 at any time causes the device to immediately enter the powered mode. Setting DET\_EN and CLASS\_EN to 1 at the same time causes detection to be performed first. Once in the powered state, the device ignores DET\_EN or CLASS\_EN commands.

When switching to manual mode from another mode, DET\_EN and CLASS\_EN default to low. These bits become pushbutton rather than configuration bits. Writing 1 to these bits while in manual mode commands the device to execute one cycle of detection and/or classification. They are reset back to 0 at the end of the execution.

#### Shutdown Mode

To put the MAX5971B into shutdown mode, set P\_M[1:0] (R12h[1:0]) to [00] during normal operation (see Table 19 and Table 20). Putting the MAX5971B into shutdown mode immediately turns off port power, clears the event and status bits, and halts all port operations. In shutdown mode the serial interface is still fully active, however, all DET\_EN, CLASS\_EN, and PWR\_ON commands are ignored.

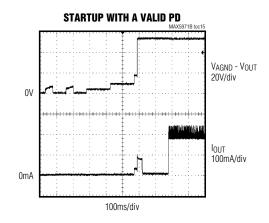

#### **PD Detection**

During normal operation, the MAX5971B probes the output for a valid PD. A valid PD has a  $25 \mathrm{k}\Omega$  discovery signature characteristic as specified in the IEEE 802.3af/802.3at standard. Table 1 shows the IEEE 802.3at specification for a PSE detecting a valid PD signature.

After each detection cycle, the MAX5971B sets DET\_END (R04h[0] and R05h[0]) to 1 and reports the detection results in the detection status bits, DET\_ST[2:0]

(R0Ch[2:0], see Table 14). The DET\_END registers are reset to 0 when read through the CoR (clear-on-read) register R05h[0], or after a reset event.

During detection, the MAX5971B keeps the internal MOSFET off and forces two probe voltages through DET. The current through DET is measured as well as the voltage at OUT. A two-point slope measurement is used, as specified by the IEEE 802.3af/802.3at standard, to verify the device connected to the port. By default, The MAX5971B load stability check is disabled. Set LSC\_EN (R29h[4], Table 36) to 1 to enable the load stability check. The MAX5971B implements appropriate settling times to reject 50Hz/60Hz power-line noise coupling.

An external diode, in series with the DET input, restricts PD detection to the first quadrant as specified by the IEEE 802.3af/802.3at standard. To prevent damage to non-PD devices, and to protect itself from an output short circuit, the MAX5971B limits the current into DET to less than 2mA (max) during PD detection.

In midspan mode, after every failed detection cycle, the MAX5971B waits at least 2.0s before attempting another detection cycle. The first detection, however, still happens immediately after exiting a reset condition.

#### High-Capacitance Detection

High-capacitance detection for legacy PDs is both software and pin programmable (LEGACY). To use software to enable high-capacitance detection, set CLC\_EN (R23h[5]) to 1 during normal operation. Alternatively, the status of the LEGACY input is latched and written to CLC\_EN during power-up or after reset condition is cleared. The LEGACY input is internally pulled

Table 1. PSE PI Detection Modes Electrical Requirements (IEEE 802.3at)

| PARAMETER                              | SYMBOL           | MIN  | MAX  | UNITS | ADDITIONAL INFORMATION                                |

|----------------------------------------|------------------|------|------|-------|-------------------------------------------------------|

| Open-Circuit Voltage                   | Voc              |      | 30   | V     | In detection mode only                                |

| Short-Circuit Current                  | Isc              |      | 5    | mA    | In detection mode only                                |

| Valid Test Voltage                     | VVALID           | 2.8  | 10   | V     |                                                       |

| Voltage Difference Between Test Points | ΔVTEST           | 1    |      | V     |                                                       |

| Time Between Any Two Test Points       | tBP              | 2    |      | ms    | This timing implies a 500Hz maximum probing frequency |

| Slew Rate                              | Vslew            |      | 0.1  | V/µs  |                                                       |

| Accept Signature Resistance            | RGOOD            | 19   | 26.5 | kΩ    |                                                       |

| Reject Signature Resistance            | R <sub>BAD</sub> | < 15 | > 33 | kΩ    |                                                       |

| Open-Circuit Resistance                | ROPEN            | 500  |      | kΩ    |                                                       |

| Accept Signature Capacitance           | CGOOD            |      | 150  | nF    |                                                       |

| Reject Signature Capacitance           | CBAD             | 10   |      | μF    |                                                       |

| Signature Offset Voltage Tolerance     | Vos              | 0    | 2.0  | V     |                                                       |

| Signature Offset Current Tolerance     | los              | 0    | 12   | μΑ    |                                                       |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

high, enabling high-capacitance detection. Unless high-capacitance detection is needed, connect LEGACY to VEE to disable this function. If high-capacitance detection is enabled, PD signature capacitances up to  $47\mu\text{F}$  (typ) are accepted.

# Powered Device Classification (PD Classification)

During PD classification, the MAX5971B forces a probe voltage (-18V, typ) at DET and measures the current into DET. The measured current determines the class of the PD.

After each classification cycle, the MAX5971B sets CL\_END (R04h[4] and R05h[4]) to 1 and reports the classification results in the classification status bits, CLASS[2:0] (R0Ch[6:4], see Table 14). The CL\_END "registers are reset to 0 when read through the CoR (clear- on-read) register, R05h, or after a reset event.

If ILIM1 and ILIM2 are both left unconnected, the MAX5971B classifies the PD based on Table 33.9 of the IEEE 802.3at standard (see Table 2). If the measured

Table 2. PSE Classification of a PD (Table 33.9 of the IEEE 802.3at Standard)

| MEASURED ICLASS (mA) | CLASSIFICATION            |  |  |  |

|----------------------|---------------------------|--|--|--|

| 0 to 5               | Class 0                   |  |  |  |

| > 5 and < 8          | Can be Class 0 or 1       |  |  |  |

| 8 to 13              | Class 1                   |  |  |  |

| > 13 and < 16        | Either Class 1 or 2       |  |  |  |

| 16 to 21             | Class 2                   |  |  |  |

| > 21 and < 25        | Either Class 2 or 3       |  |  |  |

| 25 to 31             | Class 3                   |  |  |  |

| > 31 and < 35        | Either Class 3 or 4       |  |  |  |

| 35 to 45             | Class 4                   |  |  |  |

| > 45 and < 51        | Either Class 4 or Invalid |  |  |  |

current exceeds 51mA, the MAX5971B does not power the PD, but returns to idle state before attempting a new detection cycle.

#### Class 5 PD Classification

The MAX5971B supports high power beyond the IEEE 802.3at standard by providing an additional classification (Class 5) if needed. To enable Class 5 detection and select the corresponding current-limit/overcurrent thresholds, ILIM1 and ILIM2 must be set based on the combinations detailed in Table 3. Once Class 5 is enabled, during classification, if the MAX5971B detects currents in excess of the Class 4 upper limit threshold, the PD is classified as a Class 5 powered device. The PD is guaranteed to be classified as a Class 5 device for any classification current from 51mA up to the classification current-limit threshold.

The Class 5 overcurrent threshold and current limit is set with ILIM1 and ILIM2. ILIM1 and ILIM2 are both referenced to VEE and are internally pulled up to the digital supply. Leave ILIM1 and ILIM2 unconnected to disable Class 5 detection and to be fully compliant to IEEE 802.3at standard classification. Class 5 detection is enabled, and the corresponding overcurrent threshold and current limit is adjusted, by connecting one or both to VEE (see Table 3).

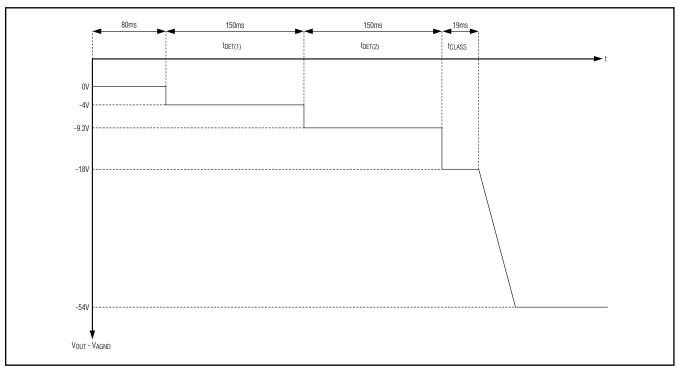

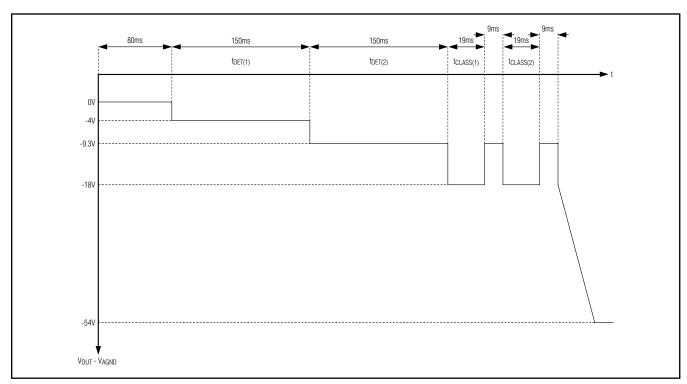

#### 2-Event PD Classification

If the result of the first classification event is Class 0 through Class 3, then only a single classification event occurs as shown in Figure 1. However, if the result is Class 4 or Class 5 (when enabled), the device performs a second classification event as shown in Figure 2. Between the classification cycles, the MAX5971B performs a first and second mark event as required by the IEEE 802.3at standard, forcing a -9.3V probing voltage at DET.

Table 3. Class 5 Overcurrent Threshold and Current-Limit Settings

| ILIM1<br>CONFIGURATION | ILIM2<br>CONFIGURATION | OVERCURRENT<br>THRESHOLD (mA) | CURRENT<br>LIMIT (mA) |

|------------------------|------------------------|-------------------------------|-----------------------|

| Unconnected            | Unconnected            | Class 5 disabled              | Class 5 disabled      |

| VEE                    | Unconnected            | 748                           | 850                   |

| Unconnected            | VEE                    | 792                           | 900                   |

| VEE                    | VEE                    | 836                           | 950                   |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

Figure 1. Detection, Classification, and Port Power-Up Sequence

Figure 2. Detection, 2-Event Classification, and Port Power-Up Sequence

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

#### **Powered State**

When the MAX5971B enters a powered state, the tFAULT and tDISC timers are reset. When the startup timer (tSTART) has timed out, the device enters a normal powered condition, allowing power delivery to the PD. PGOOD (R10h[4], Table 17) is set to 1 when the device enters the normal powered condition. PGOOD immediately resets to 0 whenever the power to the port is turned off. The power-good change bits, PG\_CHG (R02h[4] and R03h[4], Table 9) are set both when the port powers up and when it powers down. PWR\_EN (R10h[0], Table 17) is set to 1 when the port powers up and resets to 0 when a port shuts down. Set PWR\_OFF (R19h[4], Table 27) to 1 to immediately turn off power to the port.

#### **Overcurrent Protection**

The MAX5971B has an internal sense resistor, RSENSE (see the *Simplified Diagram*), connected between the source of the internal MOSFET and VEE to monitor the load current. Under normal operating conditions, the current through RSENSE (IRSENSE) never exceeds the threshold I<sub>LIM</sub>. If IRSENSE exceeds I<sub>LIM</sub>, an internal current-limiting circuit regulates the gate voltage of the internal MOSFET, limiting the current. During transient conditions, if IRSENSE exceeds I<sub>LIM</sub> by more than 2A, a fast pulldown circuit activates to quickly recover from the current overshoot.

In the normal powered state, the MAX5971B checks for overcurrent conditions, as determined by ICUT = ~88% of ILIM. The tFAULT counter sets the maximum-allowed continuous overcurrent period. This timer is incremented both in startup and in normal powered state, but under different conditions. During startup it increases when IRSENSE exceeds ILIM, while in the normal powered state the counter increases when IRSENSE exceeds ICUT. It decreases at a slower pace when IRSENSE drops below ILIM or ICUT. A slower decrement for the tFAULT counter allows for detection of repeated short-duration overcurrent events. When the counter reaches the tFAULT limit,

the MAX5971B powers down the port and asserts the IMAX\_FLT bits (R06h[0] and R07h[0]). For a continuous overstress, a fault occurs exactly after a period of tFAULT. The timing is software programmable through the timing register (R16h, Table 24).

After a power-off due to an overcurrent fault, the tFAULT timer is not immediately reset but starts decrementing. The MAX5971B allows the port to be powered on only when the tFAULT counter reaches zero. This feature sets an automatic port power duty-cycle protection to the internal MOSFET to avoid overheating. Through programmable registers, the MAX5971B allows the rate of decrement to be adjusted or for the restart timeout to be disabled entirely (see Tables 24 and 25).

In the normal powered state, the I<sub>LIM</sub> and I<sub>CUT</sub> thresholds are set automatically according to the classification result (see Table 4 for classification results based on detection current, and the *Electrical Characteristics* table for the corresponding thresholds). The thresholds can also be set manually by programming the ICUT register (R2Ah[2:0]). During startup, I<sub>LIM</sub> is always set to 420mA regardless of the detected class.

#### The ICUT Register

The ICUT register determines the maximum current limit allowed for the MAX5971B during the powered state. The ICUT bits (R2Ah[2:0]) allow manual programming of the current limit (ILIM) and overcurrent (ICUT) thresholds (see Tables 37 and 38). The ICUT register can be written to directly through the I<sup>2</sup>C interface when the automatic ICUT programming bit, CL\_DISC (R17h[2]), is set to 1 (see Table 4). In this case, the current limit of the port is configured regardless of the status of the classification. By setting the CL\_DISC bit to 0 (default), the MAX5971B automatically sets the ICUT register based upon the classification result (see Tables 4, 37, and 38 in the *Register Map and Description* section).

**Table 4. Automatic ICUT Programming**

| CL_DISC<br>(R17h[2]) | PORT CLASSIFICATION<br>RESULT | ILIM1<br>SETTING | ILIM2<br>SETTING | RESULTING ICUT REGISTER<br>BITS (R2Ah[2:0]) | CURRENT LIMIT<br>(mA) |

|----------------------|-------------------------------|------------------|------------------|---------------------------------------------|-----------------------|

| 1                    | Any                           | _                | _                | User programmed                             | _                     |

| 0                    | 0, 1, 2, 3                    | _                | _                | ICUT = 000                                  | 420                   |

| 0                    | 4                             | _                | _                | ICUT = 001                                  | 720                   |

| 0                    | 5                             | VEE              | Unconnected      | ICUT = 101                                  | 850                   |

| 0                    | 5                             | Unconnected      | VEE              | ICUT = 110                                  | 900                   |

| 0                    | 5                             | VEE              | VEE              | ICUT = 111                                  | 950                   |

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

#### **Foldback Current**

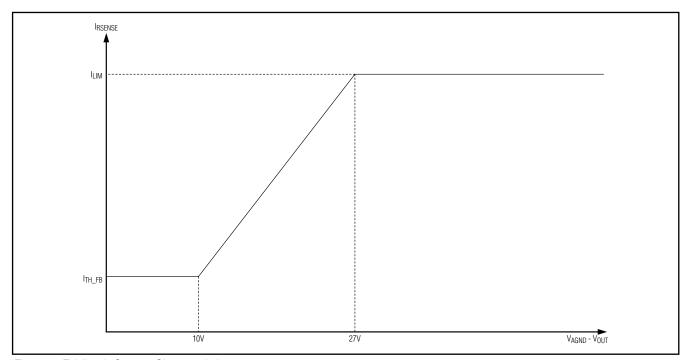

During startup and normal operation, an internal circuit senses the port voltage and reduces the current-limit value and the overcurrent threshold when (VAGND - VOUT) < 27V. The foldback function helps to reduce the power dissipation on the internal MOSFET. The current limit eventually reduces down to ITH\_FB (166mA, typ) when (VAGND - VOUT) < 10V (see Figure 3).

#### **Digital Logic**

The MAX5971B internally generates digital supplies (referenced to VEE) to power the internal logic circuitry. All logic inputs and outputs are referenced to VEE. See the *Electrical Characteristics* table for digital input thresholds. If digital logic inputs are driven externally, the nominal digital logic level is 3.3V.

#### Interrupt

The MAX5971B contains an open-drain logic output (INT) that goes low when an interrupt condition exists. The interrupt register (R00h, Table 7) contains the interrupt flag bits and the interrupt mask register (R01h, Table 8) determines which events can trigger an interrupt. When an event occurs, the appropriate interrupt event register bits (in R02h through R0Bh) and the corresponding interrupt (in R00h) are set to 1 and INT is asserted low (unless masked).

As a response to an interrupt, the controller can read the status of the event register(s) to determine the cause of the interrupt and take appropriate action. Each interrupt event register is paired with a clear-on-read (CoR) register. When an interrupt event register is read through the corresponding CoR register, the interrupt register is reset to 0. INT remains low and the interrupt is not reset when the interrupt event register is read through the read-only addresses. For example, to clear a supply event fault, read ROBh (CoR) not ROAh (read only, see Table 13). Use the CLR\_INT bit (R1Ah[7]) to clear an interrupt, or the RESET\_IC (R1Ah[4]) or RESET\_P (R1Ah[0]) bit to initiate a software reset (see Table 28).

#### **Undervoltage and Overvoltage Protection**

The MAX5971B contains both undervoltage and overvoltage protection features. Table 13 in the *Register Map and Description* section shows a detailed list of the undervoltage and overvoltage protection features. An internal VEE undervoltage lockout (VEE\_UVLO) circuit keeps the port off and the MAX5971B in reset until VAGND - VEE exceeds 28.5V (typ) for more than 2.5ms. An internal VEE overvoltage (VEE\_OV) circuit shuts down the port when VAGND - VEE exceeds 62.5V (typ). The MAX5971B also features a VEE undervoltage interrupt (VEE\_UV) that triggers when VAGND - VEE drops below

Figure 3. Foldback Current Characteristics

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

40V (typ). A fault latches into the supply event register VEE\_UV (R0Ah[2] and R0Bh[2], Table 13) but the MAX5971B does not power down the port in this case.

#### **DC Disconnect Monitoring**

Force OSC to VEE and power or reset the device to activate DC load-disconnect monitoring. DCD\_EN (R13h[0]) is set to 1 to enable DC load disconnect. If IRSENSE (the current across RSENSE) falls below the DC load-disconnect threshold, IDC\_TH, for more than tDISC, the device turns off port power and sets LD\_DISC in the fault event registers (R06h[4] and R07h[4]) to 1.

#### **AC Disconnect Monitoring**

The MAX5971B features AC load-disconnect monitoring. Bypass OSC with a 100nF (±10% tolerance) external capacitor to VEE and power or reset the device to automatically enable AC disconnect. ACD\_EN (R13h[4]) is set to 1 to enable AC disconnect (the bypass from OSC to VEE must be in place as well). When AC disconnect is enabled, a blocking diode in series to OUT and an RC circuit in parallel to the DET diode must be used, as shown in the typical operating circuit of Figure 16.

The AC disconnect uses an internal triangle-wave generator to supply the probing signal. Then the resulting

4VP-P amplitude wave is forced on DET. The common mode of the output signal probed on DET is 5V below AGND. If the AC current peak at DET falls below IAC\_TH for more than tDISC, the device powers down the port and asserts LD\_DISC (R06h[4] and R07h[4]). The AC load-disconnect threshold (IAC\_TH) is programmable using the AC\_TH[2:0] bits (R23h[2:0], see Table 33 for settings).

#### **PWM and LED Signals**

The MAX5971B includes a multifunction LED driver to inform the user of the port status. LED is an open-drain, multifunction output referenced to VEE and can sink 10mA (typ) while driving an external LED. The LED is turned on when the port is connected to a valid PD and powered. If the port is not powered or is disconnected, the LED is off.

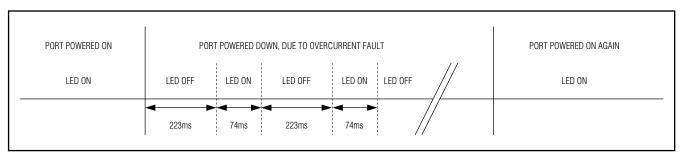

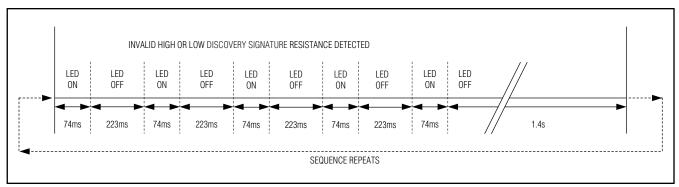

For two other conditions, the MAX5971B blinks a code to communicate the port status. A series of two flashes indicates an overcurrent fault occurred during port power-on, and has a timing characteristic detailed by Figure 4. A series of five flashes indicates that during detection an invalid low or high discovery signature resistance was detected, and has a timing characteristic detailed by Figure 5.

Figure 4. LED Code Timing for Overcurrent Fault During Port Power-On

Figure 5. LED Code Timing for Detection Fault Due to High- or Low-Discovery Signature Resistance

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

The MAX5971B also contains an internal square wave, PWM signal generator. The PWM runs at a typical frequency of 25kHz with a default duty cycle of 6.25%. The duty cycle is programmable from 6.25% up to 25% through the PWM\_TH[1:0] bits (R24h[5:4], Tables 34 and 35). PWMEN is used to enable or disable the PWM. PWMEN is internally pulled up to the digital supply, and can be left unconnected to enable the internal PWM. When enabled, the LED pulses are driven by the PWM to reduce the power dissipation and increase the system efficiency. Force PWMEN low to disable the internal PWM; LED is then driven directly.

#### Thermal Shutdown

If the MAX5971B die temperature reaches +150°C (typ), an overtemperature fault is generated and the device shuts down. The die temperature must cool down below 130°C (typ) to remove the overtemperature fault condition. After a thermal shutdown condition clears, the device is reset.

#### Watchdog

The R1Eh and R1Fh registers control the watchdog operation. The watchdog function, when enabled, allows the MAX5971B to automatically take over control and securely shut down the power to the port in case of software/firmware crashes. See the *Register Map and Description* section for register configuration and settings (Tables 30, 31, and 32).

#### **Device Address (AD0)**

The MAX5971B is programmable to one of four unique slave addresses. To program the device address, connect AD0 to VEE, SCL, SDA or to an external VCC supply referenced to VEE. This external VCC (at AD0)

must exceed the digital input logic-high threshold (VCC > 2.4V, see Table 5), but should not exceed 5.5V. An external regulated 3.3V or 5V supply is recommended for VCC.

#### I<sup>2</sup>C-Compatible Serial Interface

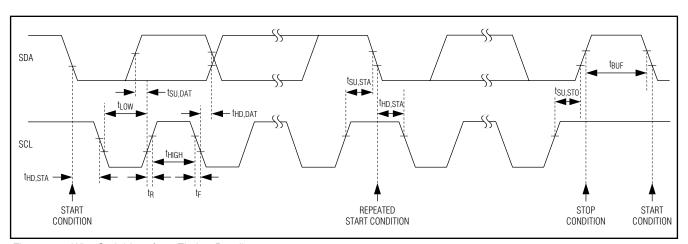

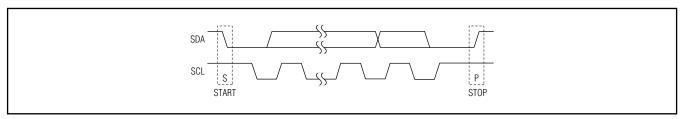

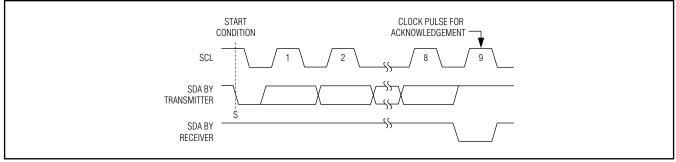

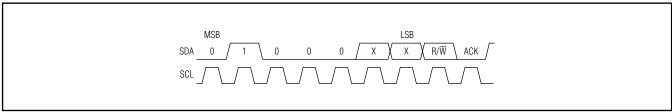

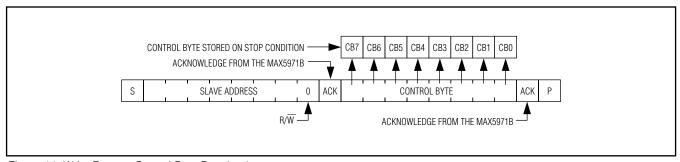

The MAX5971B operates as a slave that sends and receives data through an I<sup>2</sup>C-compatible 2-wire interface. The interface uses a serial-data line (SDA) and a serial-clock line (SCL) to achieve communication between master(s) and slave(s). A master (typically a microcontroller) initiates all data transfers to and from the MAX5971B, and generates the SCL clock that synchronizes the data transfer (see Figure 6).

The MAX5971B SDA line operates as both an input and an output. A pullup resistor, typically 4.7k $\Omega$ , may be required on SDA. The MAX5971B SCL line operates only as an input. A pullup resistor may be required (typically 4.7k $\Omega$ ) on SCL if there are multiple masters, or if the master in a single-master system has an open-drain SCL output.

**Table 5. Programmable Device Address Settings**

| 400 | DEVICE ADDRESS |            |            |    |    |           |    |  |  |  |

|-----|----------------|------------|------------|----|----|-----------|----|--|--|--|

| AD0 | <b>A</b> 7     | <b>A</b> 6 | <b>A</b> 5 | A4 | А3 | <b>A2</b> | A1 |  |  |  |

| VEE | 0              | 1          | 0          | 0  | 0  | 0         | 0  |  |  |  |

| Vcc | 0              | 1          | 0          | 0  | 0  | 0         | 1  |  |  |  |

| SCL | 0              | 1          | 0          | 0  | 0  | 1         | 0  |  |  |  |

| SDA | 0              | 1          | 0          | 0  | 0  | 1         | 1  |  |  |  |

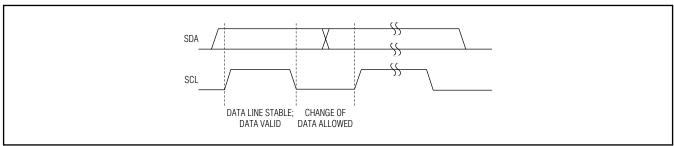

Figure 6. 2-Wire Serial Interface Timing Details

# Single-Port, 40W, IEEE 802.3af/at, PSE Controller with I2C

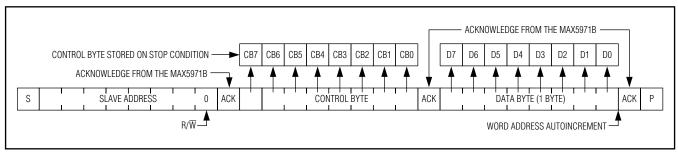

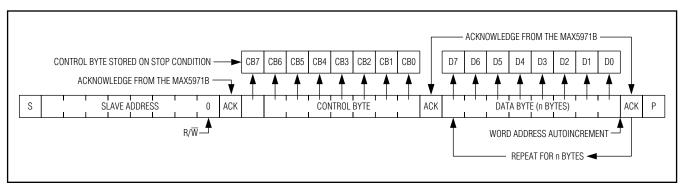

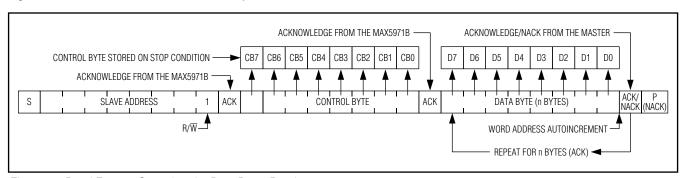

#### Serial-Addressing