# Freescale Semiconductor

**Datasheet: Technical Data**

Document Number: MPC8313EEC Rev. 4, 11/2011

# MPC8313E PowerQUICC II Pro Processor Hardware Specifications

This document provides an overview of the MPC8313E PowerQUICC<sup>™</sup> II Pro processor features, including a block diagram showing the major functional components. The MPC8313E is a cost-effective, low-power, highly integrated host processor that addresses the requirements of several printing and imaging, consumer, and industrial applications, including main CPUs and I/O processors in printing systems, networking switches and line cards, wireless LANs (WLANs), network access servers (NAS), VPN routers, intelligent NIC, and industrial controllers. The MPC8313E extends the PowerQUICC<sup>™</sup> family, adding higher CPU performance, additional functionality, and faster interfaces while addressing the requirements related to time-to-market, price, power consumption, and package size.

### NOTE

The information in this document is accurate for revisions 1.0, 2.x, and later. See Section 23.1, "Part Numbers Fully Addressed by this Document."

#### Contents

| 1.  | Overview                                       | . 2 |

|-----|------------------------------------------------|-----|

| 2.  | Electrical Characteristics                     | . 6 |

| 3.  | Power Characteristics                          | 11  |

| 4.  | Clock Input Timing                             | 12  |

| 5.  | RESET Initialization                           | 13  |

| 6.  | DDR and DDR2 SDRAM                             | 14  |

| 7.  | DUART                                          | 21  |

| 8.  | Ethernet: Three-Speed Ethernet, MII Management | 21  |

| 9.  | High-Speed Serial Interfaces (HSSI)            | 36  |

| 10. | USB                                            | 45  |

| 11. | Enhanced Local Bus                             | 47  |

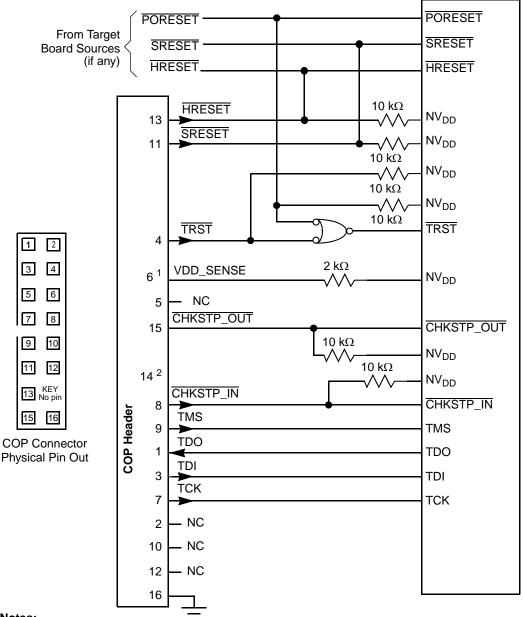

| 12. | JTAG                                           | 51  |

| 13. | $I^2C$                                         | 54  |

| 14. | PCI                                            | 56  |

| 15. | Timers                                         | 58  |

| 16. | GPIO                                           | 59  |

| 17. | IPIC                                           | 61  |

| 18. | SPI                                            | 61  |

| 19. | Package and Pin Listings                       |     |

| 20. | Clocking                                       | 77  |

| 21. | Thermal                                        | 82  |

| 22. | System Design Information                      | 87  |

| 23. | Ordering Information                           | 93  |

| 24. | Revision History                               | 95  |

© Freescale Semiconductor, Inc., 2007–2011. All rights reserved.

# 1 Overview

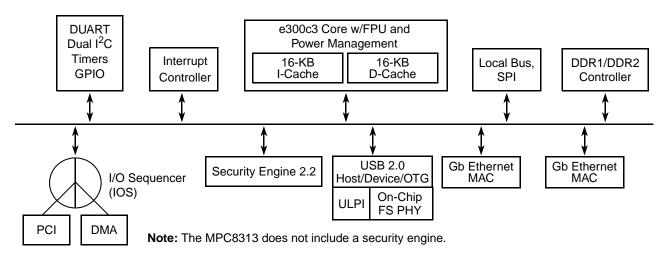

The MPC8313E incorporates the e300c3 core, which includes 16 Kbytes of L1 instruction and data caches and on-chip memory management units (MMUs). The MPC8313E has interfaces to dual enhanced three-speed 10/100/1000 Mbps Ethernet controllers, a DDR1/DDR2 SDRAM memory controller, an enhanced local bus controller, a 32-bit PCI controller, a dedicated security engine, a USB 2.0 dual-role controller and an on-chip high-speed PHY, a programmable interrupt controller, dual I<sup>2</sup>C controllers, a 4-channel DMA controller, and a general-purpose I/O port. This figure shows a block diagram of the MPC8313E.

### Figure 1. MPC8313E Block Diagram

The MPC8313E security engine (SEC 2.2) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. The security-processing accelerator provides hardware acceleration for the DES, 3DES, AES, SHA-1, and MD-5 algorithms.

# 1.1 MPC8313E Features

The following features are supported in the MPC8313E:

- Embedded PowerPC<sup>TM</sup> e300 processor core built on Power Architecture<sup>TM</sup> technology; operates at up to 333 MHz.

- High-performance, low-power, and cost-effective host processor

- DDR1/DDR2 memory controller—one 16-/32-bit interface at up to 333 MHz supporting both DDR1 and DDR2

- 16-Kbyte instruction cache and 16-Kbyte data cache, a floating point unit, and two integer units

- Peripheral interfaces such as 32-bit PCI interface with up to 66-MHz operation, 16-bit enhanced local bus interface with up to 66-MHz operation, and USB 2.0 (high speed) with an on-chip PHY.

- Security engine provides acceleration for control and data plane security protocols

- Power management controller for low-power consumption

- High degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration

# 1.2 Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I<sup>2</sup>C, and an SPI interface.

# 1.3 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

- Data encryption standard execution unit (DEU), supporting DES and 3DES

- Advanced encryption standard unit (AESU), supporting AES

- Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

- One crypto-channel supporting multi-command descriptor chains

# 1.4 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

- Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

- Support for up to 333 MHz

- Support for two physical banks (chip selects), each bank independently addressable

- 64-Mbit to 2-Gbit (for DDR1) and to 4-Gbit (for DDR2) devices with x8/x16/x32 data ports (no direct x4 support)

- Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

- Support for up to 16 simultaneous open pages

- Supports auto refresh

- On-the-fly power management using CKE

- 1.8-/2.5-V SSTL2 compatible I/O

# 1.5 PCI Controller

The MPC8313E PCI controller includes the following features:

- PCI specification revision 2.3 compatible

- Single 32-bit data PCI interface operates at up to 66 MHz

- PCI 3.3-V compatible (not 5-V compatible)

- Support for host and agent modes

- On-chip arbitration, supporting three external masters on PCI

- Selectable hardware-enforced coherency

# 1.6 USB Dual-Role Controller

The MPC8313E USB controller includes the following features:

- Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI (UTMI + low-pin interface) PHY

- Compatible with Universal Serial Bus Specification, Rev. 2.0

- Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

- Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

- Supports high-speed (480 Mbps), full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is supported only in host mode.

- Supports UTMI + low pin interface (ULPI) or on-chip USB 2.0 full-speed/high-speed PHY

# 1.7 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The MPC8313E eTSECs include the following features:

- Two RGMII/SGMII/MII/RMII/RTBI interfaces

- Two controllers designed to comply with IEEE Std 802.3®, 802.3u®, 802.3x®, 802.3z®, 802.3au®, and 802.3ab®

- Support for Wake-on-Magic Packet<sup>™</sup>, a method to bring the device from standby to full operating mode

- MII management interface for external PHY control and status

- Three-speed support (10/100/1000 Mbps)

- On-chip high-speed serial interface to external SGMII PHY interface

- Support for IEEE Std 1588<sup>TM</sup>

- Support for two full-duplex FIFO interface modes

- Multiple PHY interface configuration

- TCP/IP acceleration and QoS features available

- IP v4 and IP v6 header recognition on receive

- IP v4 header checksum verification and generation

- TCP and UDP checksum verification and generation

- Per-packet configurable acceleration

- Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2<sup>®</sup>, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

- Transmission from up to eight physical queues.

- Reception to up to eight physical queues

- Full and half-duplex Ethernet support (1000 Mbps supports only full-duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and IEEE 802.1 virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound packets

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

- MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

- Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

- RMON statistics support

- 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

- MII management interface for control and status

# **1.8 Programmable Interrupt Controller (PIC)**

The programmable interrupt controller (PIC) implements the necessary functions to provide a flexible solution for general-purpose interrupt control. The PIC programming model supports 5 external and 34 internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

# 1.9 Power Management Controller (PMC)

The MPC8313E power management controller includes the following features:

- Provides power management when the device is used in both host and agent modes

- Supports PCI power management 1.2 D0, D1, D2, D3hot, and D3cold states

- On-chip split power supply controlled through external power switch for minimum standby power

- Support for PME generation in PCI agent mode, PME detection in PCI host mode

- Supports wake-up from Ethernet (Magic Packet), USB, GPIO, and PCI (PME input as host)

# 1.10 Serial Peripheral Interface (SPI)

The serial peripheral interface (SPI) allows the MPC8313E to exchange data between other PowerQUICC family chips, Ethernet PHYs for configuration, and peripheral devices such as EEPROMs, real-time clocks, A/D converters, and ISDN devices.

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (receive, transmit, clock, and slave select). The SPI block consists of transmitter and receiver sections, an independent baud-rate generator, and a control unit.

# 1.11 DMA Controller, Dual I<sup>2</sup>C, DUART, Local Bus Controller, and Timers

The MPC8313E provides an integrated four-channel DMA controller with the following features:

- Allows chaining (both extended and direct) through local memory-mapped chain descriptors (accessible by local masters)

- Supports misaligned transfers

There are two I<sup>2</sup>C controllers. These synchronous, multi-master buses can be connected to additional devices for expansion and system development.

The DUART supports full-duplex operation and is compatible with the PC16450 and PC16550 programming models. The 16-byte FIFOs are supported for both the transmitter and the receiver.

The MPC8313E local bus controller (LBC) port allows connections with a wide variety of external DSPs and ASICs. Three separate state machines share the same external pins and can be programmed separately to access different types of devices. The general-purpose chip select machine (GPCM) controls accesses to asynchronous devices using a simple handshake protocol. The three user programmable machines (UPMs) can be programmed to interface to synchronous devices or custom ASIC interfaces. Each chip select can be configured so that the associated chip interface can be controlled by the GPCM or UPM controller. The FCM provides a glueless interface to parallel-bus NAND Flash E2PROM devices. The FCM contains three basic configuration register groups—BR*n*, OR*n*, and FMR. Both may exist in the same system. The local bus can operate at up to 66 MHz.

The MPC8313E system timers include the following features: periodic interrupt timer, real time clock, software watchdog timer, and two general-purpose timer blocks.

# 2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8313E. The MPC8313E is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

# 2.1 **Overall DC Electrical Characteristics**

This section covers the ratings, conditions, and other characteristics.

## 2.1.1 Absolute Maximum Ratings

This table provides the absolute maximum ratings.

| Table 1. | Absolute | Maximum | Ratings <sup>1</sup> |

|----------|----------|---------|----------------------|

|----------|----------|---------|----------------------|

|                                                                                           | Characteristic                                                                                         | Symbol                               | Max Value                                                                    | Unit | Note |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------|------------------------------------------------------------------------------|------|------|

| Core supply volta                                                                         | age                                                                                                    | V <sub>DD</sub>                      | -0.3 to 1.26                                                                 | V    | —    |

| PLL supply voltage                                                                        |                                                                                                        | AV <sub>DD</sub>                     | -0.3 to 1.26                                                                 | V    |      |

| Core power supply for SerDes transceivers                                                 |                                                                                                        | XCOREV <sub>DD</sub>                 | -0.3 to 1.26                                                                 | V    |      |

| Pad power supply for SerDes transceivers                                                  |                                                                                                        | XPADV <sub>DD</sub>                  | -0.3 to 1.26                                                                 | V    | —    |

| DDR and DDR2                                                                              | DRAM I/O voltage                                                                                       | GV <sub>DD</sub>                     | -0.3 to 2.75<br>-0.3 to 1.98                                                 | V    |      |

| PCI, local bus, DUART, system control and power management, $I^2C$ , and JTAG I/O voltage |                                                                                                        | NV <sub>DD</sub> /LV <sub>DD</sub>   | -0.3 to 3.6                                                                  | V    |      |

| eTSEC, USB                                                                                |                                                                                                        | LV <sub>DDA</sub> /LV <sub>DDB</sub> | -0.3 to 3.6                                                                  | V    | _    |

| Input voltage                                                                             | DDR DRAM signals                                                                                       | MV <sub>IN</sub>                     | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                                                                           | DDR DRAM reference                                                                                     | MV <sub>REF</sub>                    | –0.3 to (GV <sub>DD</sub> + 0.3)                                             | V    | 2, 5 |

|                                                                                           | Enhanced three-speed Ethernet signals                                                                  | LV <sub>IN</sub>                     | -0.3 to (LV <sub>DDA</sub> + 0.3)<br>or<br>-0.3 to (LV <sub>DDB</sub> + 0.3) | V    | 4, 5 |

|                                                                                           | Local bus, DUART, SYS_CLK_IN, system control, and power management, I <sup>2</sup> C, and JTAG signals | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 3, 5 |

|                                                                                           | PCI                                                                                                    | NV <sub>IN</sub>                     | –0.3 to (NV <sub>DD</sub> + 0.3)                                             | V    | 6    |

| Storage tempera                                                                           | Storage temperature range                                                                              |                                      | -55 to 150                                                                   | °C   | —    |

Notes:

- 1. Functional and tested operating conditions are given in Table 2. Absolute maximum ratings are stress ratings only, and functional operation at the maximums is not guaranteed. Stresses beyond those listed may affect device reliability or cause permanent damage to the device.

- Caution: MV<sub>IN</sub> must not exceed GV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- 3. **Caution:** NV<sub>IN</sub> must not exceed NV<sub>DD</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

- Caution: LV<sub>IN</sub> must not exceed LV<sub>DDA</sub>/LV<sub>DDB</sub> by more than 0.3 V. This limit may be exceeded for a maximum of 20 ms during power-on reset and power-down sequences.

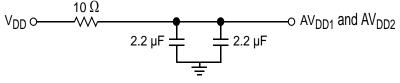

# 2.1.2 Power Supply Voltage Specification

This table provides the recommended operating conditions for the MPC8313E. Note that the values in this table are the recommended and tested operating conditions. If a particular block is given a voltage falling within the range in the Recommended Value column, the MPC8313E is capable of delivering the amount of current listed in the Current Requirement column; this is the maximum current possible. Proper device operation outside of these conditions is not guaranteed.

| Characteristic                                    | Symbol                                      | Recommended Value <sup>1</sup>                                                                                                               | Unit | Current<br>Requirement |

|---------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|

| Core supply voltage                               | V <sub>DD</sub>                             | 1.0 V ± 50 mV                                                                                                                                | V    | 469 mA                 |

| Internal core logic constant power                | V <sub>DDC</sub>                            | 1.0 V ± 50 mV                                                                                                                                | V    | 377 mA                 |

| SerDes internal digital power                     | XCOREV <sub>DD</sub>                        | 1.0                                                                                                                                          | V    | 170 mA                 |

| SerDes internal digital ground                    | XCOREV <sub>SS</sub>                        | 0.0                                                                                                                                          | V    | —                      |

| SerDes I/O digital power                          | XPADV <sub>DD</sub>                         | 1.0                                                                                                                                          | V    | 10 mA                  |

| SerDes I/O digital ground                         | XPADV <sub>SS</sub>                         | 0.0                                                                                                                                          | V    | —                      |

| SerDes analog power for PLL                       | SDAV <sub>DD</sub>                          | 1.0 V ± 50 mV                                                                                                                                | V    | 10 mA                  |

| SerDes analog ground for PLL                      | SDAV <sub>SS</sub>                          | 0.0                                                                                                                                          | V    | —                      |

| Dedicated 3.3 V analog power for USB PLL          | USB_PLL_PWR3                                | 3.3 V ± 300 mV                                                                                                                               | V    | 2–3 mA                 |

| Dedicated 1.0 V analog power for USB PLL          | USB_PLL_PWR1                                | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| Dedicated analog ground for USB PLL               | USB_PLL_GND                                 | 0.0                                                                                                                                          | V    | —                      |

| Dedicated USB power for USB bias circuit          | USB_VDDA_BIAS                               | 3.3 V ± 300 mV                                                                                                                               | V    | 4–5 mA                 |

| Dedicated USB ground for USB bias circuit         | USB_VSSA_BIAS                               | 0.0                                                                                                                                          | V    | —                      |

| Dedicated power for USB transceiver               | USB_VDDA                                    | 3.3 V ± 300 mV                                                                                                                               | V    | 75 mA                  |

| Dedicated ground for USB transceiver              | USB_VSSA                                    | 0.0                                                                                                                                          | V    | —                      |

| Analog power for e300 core APLL                   | AV <sub>DD1</sub> <sup>6</sup>              | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| Analog power for system APLL                      | AV <sub>DD2</sub> <sup>6</sup>              | 1.0 V ± 50 mV                                                                                                                                | V    | 2–3 mA                 |

| DDR1 DRAM I/O voltage (333 MHz, 32-bit operation) | GV <sub>DD</sub>                            | 2.5 V ± 125 mV                                                                                                                               | V    | 131 mA                 |

| DDR2 DRAM I/O voltage (333 MHz, 32-bit operation) | GV <sub>DD</sub>                            | 1.8 V ± 80 mV                                                                                                                                | V    | 140 mA                 |

| Differential reference voltage for DDR controller | MV <sub>REF</sub>                           | $\begin{array}{c} 1/2 \text{ DDR supply} \\ (0.49 \times \text{GV}_{\text{DD}} \text{ to} \\ 0.51 \times \text{GV}_{\text{DD}}) \end{array}$ | V    | _                      |

| Standard I/O voltage                              | NV <sub>DD</sub>                            | $3.3 \text{ V} \pm 300 \text{ mV}^2$                                                                                                         | V    | 74 mA                  |

| eTSEC2 I/O supply                                 | LV <sub>DDA</sub>                           | 2.5 V ± 125 mV/<br>3.3 V ± 300 mV                                                                                                            | V    | 22 mA                  |

| eTSEC1/USB DR I/O supply                          | LV <sub>DDB</sub>                           | 2.5 V ± 125 mV/<br>3.3 V ± 300 mV                                                                                                            | V    | 44 mA                  |

| Supply for eLBC IOs                               | LV <sub>DD</sub>                            | 3.3 V ± 300 mV                                                                                                                               | V    | 16 mA                  |

| Analog and digital ground                         | V <sub>SS</sub>                             | 0.0                                                                                                                                          | V    | —                      |

| Junction temperature range                        | T <sub>A</sub> /T <sub>J</sub> <sup>3</sup> | 0 to 105                                                                                                                                     | °C   |                        |

### Table 2. Recommended Operating Conditions

### Table 2. Recommended Operating Conditions (continued)

| Characteristic Symbol Recommended Value <sup>1</sup> Unit | Current<br>Requirement |

|-----------------------------------------------------------|------------------------|

|-----------------------------------------------------------|------------------------|

Note:

- 1. GV<sub>DD</sub>, NV<sub>DD</sub>, AV<sub>DD</sub>, and V<sub>DD</sub> must track each other and must vary in the same direction—either in the positive or negative direction.

- 2. Some GPIO pins may operate from a 2.5-V supply when configured for other functions.

- 3. Min temperature is specified with  $T_A$ ; Max temperature is specified with  $T_J$

- 4. All Power rails must be connected and power applied to the MPC8313 even if the IP interfaces are not used.

- 5. All I/O pins should be interfaced with peripherals operating at same voltage level.

- This voltage is the input to the filter discussed in Section 22.2, "PLL Power Supply Filtering" and not necessarily the voltage at the AVDD pin, which may be reduced from VDD by the filter.

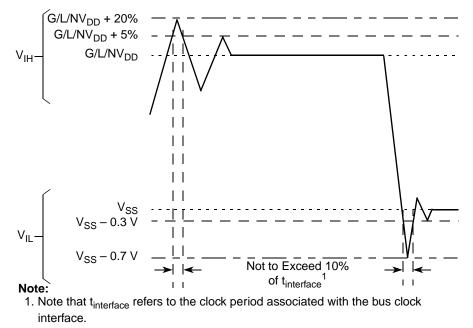

This figure shows the undershoot and overshoot voltages at the interfaces of the MPC8313E.

Figure 2. Overshoot/Undershoot Voltage for GV<sub>DD</sub>/NV<sub>DD</sub>/LV<sub>DD</sub>

### 2.1.3 Output Driver Characteristics

This table provides information on the characteristics of the output driver strengths.

Table 3. Output Drive Capability

| Driver Type                           | Output Impedance ( $\Omega$ ) | Supply Voltage           |

|---------------------------------------|-------------------------------|--------------------------|

| Local bus interface utilities signals | 42                            | NV <sub>DD</sub> = 3.3 V |

| PCI signals                           | 25                            |                          |

| DDR signal                            | 18                            | GV <sub>DD</sub> = 2.5 V |

| Driver Type                                        | Output Impedance ( $\Omega$ ) | Supply Voltage                      |

|----------------------------------------------------|-------------------------------|-------------------------------------|

| DDR2 signal                                        | 18                            | GV <sub>DD</sub> = 1.8 V            |

| DUART, system control, I <sup>2</sup> C, JTAG, SPI | 42                            | NV <sub>DD</sub> = 3.3 V            |

| GPIO signals                                       | 42                            | NV <sub>DD</sub> = 3.3 V            |

| eTSEC signals                                      | 42                            | $LV_{DDA}$ , $LV_{DDB}$ = 2.5/3.3 V |

| USB signals                                        | 42                            | LV <sub>DDB</sub> = 2.5/3.3 V       |

Table 3. Output Drive Capability (continued)

# 2.2 Power Sequencing

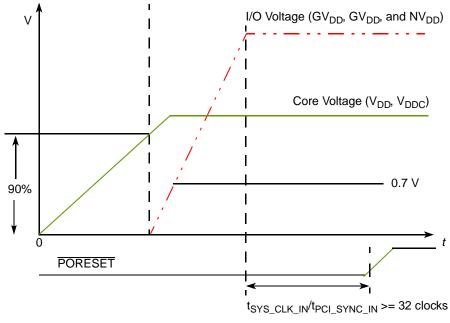

The MPC8313E does not require the core supply voltage ( $V_{DD}$  and  $V_{DDC}$ ) and I/O supply voltages ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) to be applied in any particular order. Note that during power ramp-up, before the power supplies are stable and if the I/O voltages are supplied before the core voltage, there might be a period of time that all input and output pins are actively driven and cause contention and excessive current. In order to avoid actively driving the I/O pins and to eliminate excessive current draw, apply the core voltage ( $V_{DD}$  and  $V_{DDC}$ ) before the I/O voltage ( $GV_{DD}$ ,  $LV_{DD}$ , and  $NV_{DD}$ ) and assert PORESET before the power supplies fully ramp up. In the case where the core voltage is applied first, the core voltage supply must rise to 90% of its nominal value before the I/O supplies reach 0.7 V; see Figure 3. Once both the power supplies (I/O voltage and core voltage) are stable, wait for a minimum of 32 clock cycles before negating PORESET.

Note that there is no specific power down sequence requirement for the MPC8313E. I/O voltage supplies  $(GV_{DD}, LV_{DD}, and NV_{DD})$  do not have any ordering requirements with respect to one another.

Figure 3. Power-Up Sequencing Example

# **3** Power Characteristics

The estimated typical power dissipation, not including I/O supply power, for this family of MPC8313E devices is shown in this table. Table 5 shows the estimated typical I/O power dissipation.

| Core Frequency<br>(MHz) | CSB Frequency<br>(MHz) | Typical <sup>2</sup> | Maximum for<br>Rev. 1.0 Silicon <sup>3</sup> | Maximum for<br>Rev. 2.x or Later Silicon <sup>3</sup> | Unit |

|-------------------------|------------------------|----------------------|----------------------------------------------|-------------------------------------------------------|------|

| 333                     | 167                    | 820                  | 1020                                         | 1200                                                  | mW   |

| 400                     | 133                    | 820                  | 1020                                         | 1200                                                  | mW   |

### Table 4. MPC8313E Power Dissipation<sup>1</sup>

### Note:

The values do not include I/O supply power or AV<sub>DD</sub>, but do include core, USB PLL, and a portion of SerDes digital power (not including XCOREV<sub>DD</sub>, XPADV<sub>DD</sub>, or SDAV<sub>DD</sub>, which all have dedicated power supplies for the SerDes PHY).

2. Typical power is based on a voltage of  $V_{DD}$  = 1.05 V and an artificial smoker test running at room temperature.

3. Maximum power is based on a voltage of  $V_{DD}$  = 1.05 V, a junction temperature of T<sub>J</sub> = 105°C, and an artificial smoker test.

This table describes a typical scenario where blocks with the stated percentage of utilization and impedances consume the amount of power described.

| Interface                                                                                                                                                                                                            | Parameter           | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|--------------------------|

| DDR 1, 60% utilization,<br>50% read/write                                                                                                                                                                            | 333 MHz,<br>32 bits | _                           | 0.355                       | _                           | _                                                   | —                                                   | _                           | W    |                          |

| $\begin{array}{l} R_{s} = 22 \; \Omega \\ R_{t} = 50 \; \Omega \\ \text{single pair of clock} \\ \text{capacitive load: data} = 8 \; pF, \\ \text{control address} = 8 \; pF, \\ \text{clock} = 8 \; pF \end{array}$ | 266 MHz,<br>32 bits | _                           | 0.323                       | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| DDR 2, 60% utilization,<br>50% read/write                                                                                                                                                                            | 333 MHz,<br>32 bits | 0.266                       | —                           | _                           | _                                                   | —                                                   | _                           | W    | —                        |

| $\begin{array}{l} R_{s} = 22 \; \Omega \\ R_{t} = 75 \; \Omega \\ \text{single pair of clock} \\ \text{capacitive load: data = 8 pF,} \\ \text{control address = 8 pF,} \\ \text{clock = 8 pF} \end{array}$          | 266 MHz,<br>32 bits | 0.246                       | _                           | _                           | _                                                   | _                                                   | _                           | W    | _                        |

| PCI I/O load = 50 pF                                                                                                                                                                                                 | 33 MHz              | —                           | —                           | 0.120                       |                                                     | _                                                   | —                           | W    | —                        |

|                                                                                                                                                                                                                      | 66 MHz              |                             |                             | 0.249                       |                                                     | —                                                   | —                           | W    | —                        |

| Local bus I/O load = 20 pF                                                                                                                                                                                           | 66 MHz              |                             |                             |                             |                                                     | —                                                   | 0.056                       | W    | —                        |

|                                                                                                                                                                                                                      | 50 MHz              |                             |                             | _                           | _                                                   | —                                                   | 0.040                       | W    | _                        |

| TSEC I/O load = 20 pF                                                                                                                                                                                                | MII,<br>25 MHz      | —                           | —                           | —                           | 0.008                                               | —                                                   | —                           | W    | Multiple by<br>number of |

|                                                                                                                                                                                                                      | RGMII,<br>125 MHz   | _                           | _                           | —                           | 0.078                                               | 0.044                                               | —                           | W    | interface used           |

Table 5. MPC8313E Typical I/O Power Dissipation

| Interface                     | Parameter | GV <sub>DD</sub><br>(1.8 V) | GV <sub>DD</sub><br>(2.5 V) | NV <sub>DD</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(3.3 V) | LV <sub>DDA</sub> /<br>LV <sub>DDB</sub><br>(2.5 V) | LV <sub>DD</sub><br>(3.3 V) | Unit | Comments |

|-------------------------------|-----------|-----------------------------|-----------------------------|-----------------------------|-----------------------------------------------------|-----------------------------------------------------|-----------------------------|------|----------|

| USBDR controller load = 20 pF | 60 MHz    |                             | _                           |                             | 0.078                                               |                                                     | —                           | W    |          |

| Other I/O                     | _         | —                           |                             | 0.015                       | _                                                   |                                                     | —                           | W    | _        |

Table 5. MPC8313E Typical I/O Power Dissipation (continued)

This table shows the estimated core power dissipation of the MPC8313E while transitioning into the D3 warm low-power state.

| Table 6. MPC8313E Low-Power Modes Power | Dissipation <sup>1</sup> |

|-----------------------------------------|--------------------------|

|-----------------------------------------|--------------------------|

| 333-MHz Core, 167-MHz CSB <sup>2</sup> | Rev. 1.0 <sup>3</sup> | Rev. 2.x or Later <sup>3</sup> | Unit |

|----------------------------------------|-----------------------|--------------------------------|------|

| D3 warm                                | 400                   | 425                            | mW   |

Note:

- 1. All interfaces are enabled. For further power savings, disable the clocks to unused blocks.

- The interfaces are run at the following frequencies: DDR: 333 MHz, eLBC 83 MHz, PCI 33 MHz, eTSEC1 and TSEC2: 167 MHz, SEC: 167 MHz, USB: 167 MHz. See the SCCR register for more information.

- 3. This is maximum power in D3 Warm based on a voltage of 1.05 V and a junction temperature of 105°C.

# 4 Clock Input Timing

This section provides the clock input DC and AC electrical characteristics for the MPC8313E.

# 4.1 DC Electrical Characteristics

This table provides the system clock input (SYS\_CLK\_IN/PCI\_SYNC\_IN) DC timing specifications for the MPC8313E.

| Parameter                 | Condition                                                                                                         | Symbol          | Min  | Мах                    | Unit |

|---------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------|------|------------------------|------|

| Input high voltage        | _                                                                                                                 | V <sub>IH</sub> | 2.4  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage         | _                                                                                                                 | V <sub>IL</sub> | -0.3 | 0.4                    | V    |

| SYS_CLK_IN input current  | $0 \ V \ \leq V_{IN} \leq NV_{DD}$                                                                                | I <sub>IN</sub> | —    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $\begin{array}{c} 0 \ V \leq V_{IN} \leq 0.5 \ V \\ or \\ NV_{DD} - 0.5 \ V \leq V_{IN} \leq NV_{DD} \end{array}$ | I <sub>IN</sub> | _    | ±10                    | μΑ   |

| PCI_SYNC_IN input current | $0.5~\text{V} \leq \text{V}_{\text{IN}} \leq \text{NV}_{\text{DD}} - 0.5~\text{V}$                                | I <sub>IN</sub> | —    | ±50                    | μΑ   |

Table 7. SYS\_CLK\_IN DC Electrical Characteristics

# 4.2 AC Electrical Characteristics

The primary clock source for the MPC8313E can be one of two inputs, SYS\_CLK\_IN or PCI\_CLK, depending on whether the device is configured in PCI host or PCI agent mode. This table provides the system clock input (SYS\_CLK\_IN/PCI\_CLK) AC timing specifications for the MPC8313E.

| Parameter/Condition           | Symbol                                    | Min | Тур | Max   | Unit | Note |

|-------------------------------|-------------------------------------------|-----|-----|-------|------|------|

| SYS_CLK_IN/PCI_CLK frequency  | f <sub>SYS_CLK_IN</sub>                   | 24  | _   | 66.67 | MHz  | 1    |

| SYS_CLK_IN/PCI_CLK cycle time | t <sub>SYS_CLK_IN</sub>                   | 15  | —   | _     | ns   | —    |

| SYS_CLK_IN rise and fall time | t <sub>KH</sub> , t <sub>KL</sub>         | 0.6 | 0.8 | 4     | ns   | 2    |

| PCI_CLK rise and fall time    | t <sub>PCH</sub> , t <sub>PCL</sub>       | 0.6 | 0.8 | 1.2   | ns   | 2    |

| SYS_CLK_IN/PCI_CLK duty cycle | t <sub>KHK</sub> /t <sub>SYS_CLK_IN</sub> | 40  | —   | 60    | %    | 3    |

| SYS_CLK_IN/PCI_CLK jitter     | _                                         | _   | _   | ±150  | ps   | 4, 5 |

### Table 8. SYS\_CLK\_IN AC Timing Specifications

Notes:

1. Caution: The system, core, security block must not exceed their respective maximum or minimum operating frequencies.

2. Rise and fall times for SYS\_CLK\_IN/PCI\_CLK are measured at 0.4 and 2.4 V.

3. Timing is guaranteed by design and characterization.

4. This represents the total input jitter-short term and long term-and is guaranteed by design.

5. The SYS\_CLK\_IN/PCI\_CLK driver's closed loop jitter bandwidth should be <500 kHz at -20 dB. The bandwidth must be set low to allow cascade-connected PLL-based devices to track SYS\_CLK\_IN drivers with the specified jitter.

# 5 **RESET** Initialization

This section describes the DC and AC electrical specifications for the reset initialization timing and electrical requirements of the MPC8313E.

# 5.1 **RESET DC Electrical Characteristics**

This table provides the DC electrical characteristics for the RESET pins.

| Table 9. | RESET Pins | <b>DC Electrical</b> | Characteristics |

|----------|------------|----------------------|-----------------|

|----------|------------|----------------------|-----------------|

| Characteristic      | Symbol          | Symbol Condition                                     |      | Max                    | Unit |

|---------------------|-----------------|------------------------------------------------------|------|------------------------|------|

| Input high voltage  | V <sub>IH</sub> | —                                                    | 2.1  | NV <sub>DD</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | —                                                    | -0.3 | 0.8                    | V    |

| Input current       | I <sub>IN</sub> | $0 \text{ V} \leq \text{V}_{IN} \leq \text{NV}_{DD}$ | —    | ±5                     | μA   |

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -8.0 mA                            | 2.4  | —                      | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 8.0 mA                             | —    | 0.5                    | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 3.2 mA                             | —    | 0.4                    | V    |

# 5.2 **RESET AC Electrical Characteristics**

This table provides the reset initialization AC timing specifications.

| Parameter/Condition                                                                                                                                               | Min | Max | Unit                     | Note |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|--------------------------|------|

| Required assertion time of HRESET or SRESET (input) to activate reset flow                                                                                        | 32  | —   | t <sub>PCI_SYNC_IN</sub> | 1    |

| Required assertion time of PORESET with stable clock and power applied to SYS_CLK_IN when the device is in PCI host mode                                          | 32  | —   | t <sub>SYS_CLK_IN</sub>  | 2    |

| Required assertion time of PORESET with stable clock and power applied to PCI_SYNC_IN when the device is in PCI agent mode                                        | 32  | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| HRESET assertion (output)                                                                                                                                         | 512 |     | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:3] and CFG_CLK_IN_DIV) with respect to negation of PORESET when the device is in PCI host mode | 4   | —   | <sup>t</sup> sys_clk_in  | 2    |

| Input setup time for POR configuration signals (CFG_RESET_SOURCE[0:2] and CFG_CLKIN_DIV) with respect to negation of PORESET when the device is in PCI agent mode | 4   | —   | <sup>t</sup> PCI_SYNC_IN | 1    |

| Input hold time for POR configuration signals with respect to negation of HRESET                                                                                  | 0   | —   | ns                       | —    |

| Time for the device to turn off POR configuration signal drivers with respect to the assertion of HRESET                                                          |     | 4   | ns                       | 3    |

| Time for the device to turn on POR configuration signal drivers with respect to the negation of $\overline{\text{HRESET}}$                                        | 1   |     | t <sub>PCI_SYNC_IN</sub> | 1, 3 |

#### Notes:

1. t<sub>PCI\_SYNC\_IN</sub> is the clock period of the input clock applied to PCI\_SYNC\_IN. When the device is In PCI host mode the

primary clock is applied to the SYS\_CLK\_IN input, and PCI\_SYNC\_IN period depends on the value of CFG\_CLKIN\_DIV. 2. t<sub>SYS\_CLK\_IN</sub> is the clock period of the input clock applied to SYS\_CLK\_IN. It is only valid when the device is in PCI host mode.

POR configuration signals consists of CFG\_RESET\_SOURCE[0:2] and CFG\_CLKIN\_DIV.

This table provides the PLL lock times.

### Table 11. PLL Lock Times

| Parameter/Condition | Min | Мах | Unit | Note |

|---------------------|-----|-----|------|------|

| PLL lock times      | _   | 100 | μs   | —    |

# 6 DDR and DDR2 SDRAM

This section describes the DC and AC electrical specifications for the DDR SDRAM interface. Note that DDR SDRAM is  $GV_{DD}(typ) = 2.5 \text{ V}$  and DDR2 SDRAM is  $GV_{DD}(typ) = 1.8 \text{ V}$ .

# 6.1 DDR and DDR2 SDRAM DC Electrical Characteristics

This table provides the recommended operating conditions for the DDR2 SDRAM component(s) when  $GV_{DD}(typ) = 1.8 \text{ V}.$

| Parameter/Condition                              | Symbol            | Min                       | Max                       | Unit | Note |

|--------------------------------------------------|-------------------|---------------------------|---------------------------|------|------|

| I/O supply voltage                               | GV <sub>DD</sub>  | 1.7                       | 1.9                       | V    | 1    |

| I/O reference voltage                            | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$      | $0.51 	imes GV_{DD}$      | V    | 2    |

| I/O termination voltage                          | V <sub>TT</sub>   | MV <sub>REF</sub> - 0.04  | MV <sub>REF</sub> + 0.04  | V    | 3    |

| Input high voltage                               | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.125 | GV <sub>DD</sub> + 0.3    | V    | _    |

| Input low voltage                                | V <sub>IL</sub>   | -0.3                      | MV <sub>REF</sub> – 0.125 | V    | —    |

| Output leakage current                           | I <sub>OZ</sub>   | -9.9                      | 9.9                       | μΑ   | 4    |

| Output high current (V <sub>OUT</sub> = 1.420 V) | I <sub>ОН</sub>   | -13.4                     | —                         | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.280 V)  | I <sub>OL</sub>   | 13.4                      | _                         | mA   | —    |

Table 12. DDR2 SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 1.8 V

Notes:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

2.  $MV_{REF}$  is expected to be equal to  $0.5 \times GV_{DD}$ , and to track  $GV_{DD}$  DC variations as measured at the receiver. Peak-to-peak noise on  $MV_{REF}$  may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled, 0 V  $\leq$  V<sub>OUT</sub>  $\leq$  GV<sub>DD</sub>.

This table provides the DDR2 capacitance when  $GV_{DD}(typ) = 1.8$  V.

| Parameter/Condition                          | Symbol           | Min | Max | Unit | Note |

|----------------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD}$  = 1.8 V ± 0.090 V, f = 1 MHz,  $T_A$  = 25°C,  $V_{OUT}$  =  $GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the recommended operating conditions for the DDR SDRAM component(s) when  $GV_{DD}(typ) = 2.5 \text{ V}.$

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition     | Symbol            | Min                      | Мах                      | Unit | Note |

|-------------------------|-------------------|--------------------------|--------------------------|------|------|

| I/O supply voltage      | GV <sub>DD</sub>  | 2.3                      | 2.7                      | V    | 1    |

| I/O reference voltage   | MV <sub>REF</sub> | $0.49 	imes GV_{DD}$     | $0.51 	imes GV_{DD}$     | V    | 2    |

| I/O termination voltage | V <sub>TT</sub>   | MV <sub>REF</sub> – 0.04 | MV <sub>REF</sub> + 0.04 | V    | 3    |

| Input high voltage      | V <sub>IH</sub>   | MV <sub>REF</sub> + 0.15 | GV <sub>DD</sub> + 0.3   | V    | _    |

| Input low voltage       | V <sub>IL</sub>   | -0.3                     | MV <sub>REF</sub> – 0.15 | V    |      |

Table 14. DDR SDRAM DC Electrical Characteristics for GV<sub>DD</sub>(typ) = 2.5 V (continued)

| Parameter/Condition                             | Symbol          | Min   | Мах  | Unit | Note |

|-------------------------------------------------|-----------------|-------|------|------|------|

| Output leakage current                          | I <sub>OZ</sub> | -9.9  | -9.9 | μA   | 4    |

| Output high current (V <sub>OUT</sub> = 1.95 V) | I <sub>OH</sub> | -16.2 | —    | mA   | —    |

| Output low current (V <sub>OUT</sub> = 0.35 V)  | I <sub>OL</sub> | 16.2  | _    | mA   | _    |

Note:

1.  $GV_{DD}$  is expected to be within 50 mV of the DRAM  $GV_{DD}$  at all times.

MV<sub>REF</sub> is expected to be equal to 0.5 × GV<sub>DD</sub>, and to track GV<sub>DD</sub> DC variations as measured at the receiver. Peak-to-peak noise on MV<sub>REF</sub> may not exceed ±2% of the DC value.

3. V<sub>TT</sub> is not applied directly to the device. It is the supply to which far end signal termination is made and is expected to be equal to MV<sub>REF</sub>. This rail should track variations in the DC level of MV<sub>REF</sub>.

4. Output leakage is measured with all outputs disabled,  $0 V \le V_{OUT} \le GV_{DD}$ .

This table provides the DDR capacitance when  $GV_{DD}(typ) = 2.5$  V.

### Table 15. DDR SDRAM Capacitance for GV<sub>DD</sub>(typ) = 2.5 V

| Parameter/Condition                     | Symbol           | Min | Мах | Unit | Note |

|-----------------------------------------|------------------|-----|-----|------|------|

| Input/output capacitance: DQ, DQS       | C <sub>IO</sub>  | 6   | 8   | pF   | 1    |

| Delta input/output capacitance: DQ, DQS | C <sub>DIO</sub> | _   | 0.5 | pF   | 1    |

Note:

1. This parameter is sampled.  $GV_{DD} = 2.5 V \pm 0.125 V$ , f = 1 MHz,  $T_A = 25^{\circ}C$ ,  $V_{OUT} = GV_{DD}/2$ ,  $V_{OUT}$  (peak-to-peak) = 0.2 V.

This table provides the current draw characteristics for MV<sub>REF</sub>.

### Table 16. Current Draw Characteristics for MV<sub>REF</sub>

| Parameter/Condition                | Symbol             | Min | Мах | Unit | Note |

|------------------------------------|--------------------|-----|-----|------|------|

| Current draw for MV <sub>REF</sub> | I <sub>MVREF</sub> | —   | 500 | μΑ   | 1    |

Note:

1. The voltage regulator for  $\text{MV}_{\text{REF}}$  must be able to supply up to 500  $\mu\text{A}$  current.

# 6.2 DDR and DDR2 SDRAM AC Electrical Characteristics

This section provides the AC electrical characteristics for the DDR SDRAM interface.

### 6.2.1 DDR and DDR2 SDRAM Input AC Timing Specifications

This table provides the input AC timing specifications for the DDR2 SDRAM when  $GV_{DD}(typ) = 1.8 V$ .

### Table 17. DDR2 SDRAM Input AC Timing Specifications for 1.8-V Interface

At recommended operating conditions with  $GV_{DD}$  of 1.8 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | _                        | MV <sub>REF</sub> – 0.25 | V    | —    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.25 | _                        | V    | —    |

This table provides the input AC timing specifications for the DDR SDRAM when  $GV_{DD}(typ) = 2.5 \text{ V}$ .

### Table 18. DDR SDRAM Input AC Timing Specifications for 2.5-V Interface

At recommended operating conditions with  $GV_{DD}$  of 2.5 ± 5%.

| Parameter             | Symbol          | Min                      | Мах                      | Unit | Note |

|-----------------------|-----------------|--------------------------|--------------------------|------|------|

| AC input low voltage  | V <sub>IL</sub> | —                        | MV <sub>REF</sub> – 0.31 | V    | _    |

| AC input high voltage | V <sub>IH</sub> | MV <sub>REF</sub> + 0.31 | —                        | V    | —    |

This table provides the input AC timing specifications for the DDR2 SDRAM interface.

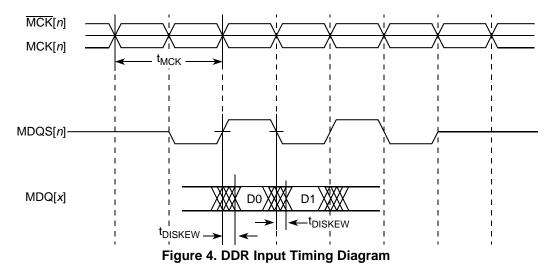

### Table 19. DDR and DDR2 SDRAM Input AC Timing Specifications

At recommended operating conditions. with  $\text{GV}_{\text{DD}}$  of 2.5 ± 5%.

| Parameter                    | Symbol              | Min  | Мах | Unit | Note |

|------------------------------|---------------------|------|-----|------|------|

| Controller skew for MDQS—MDQ | t <sub>CISKEW</sub> | _    | —   | ps   | 1, 2 |

| 333 MHz                      |                     | -750 | 750 |      | —    |

| 266 MHz                      | _                   | -750 | 750 | _    | —    |

Notes:

- 1. t<sub>CISKEW</sub> represents the total amount of skew consumed by the controller between MDQS[*n*] and any corresponding bit that is captured with MDQS[*n*]. This should be subtracted from the total timing budget.

- The amount of skew that can be tolerated from MDQS to a corresponding MDQ signal is called t<sub>DISKEW</sub>. This can be determined by the following equation: t<sub>DISKEW</sub> = ± (T/4 – abs(t<sub>CISKEW</sub>)) where T is the clock period and abs(t<sub>CISKEW</sub>) is the absolute value of t<sub>CISKEW</sub>.

This figure illustrates the DDR input timing diagram showing the t<sub>DISKEW</sub> timing parameter.

# 6.2.2 DDR and DDR2 SDRAM Output AC Timing Specifications

Table 20. DDR and DDR2 SDRAM Output AC Timing Specifications for Rev. 1.0 Silicon

| Parameter                                                              | Symbol <sup>1</sup>                         | Min                      | Мах                         | Unit | Note |

|------------------------------------------------------------------------|---------------------------------------------|--------------------------|-----------------------------|------|------|

| MCK[ <i>n</i> ] cycle time, MCK[ <i>n</i> ]/MCK[ <i>n</i> ] crossing   | t <sub>MCK</sub>                            | 6                        | 10                          | ns   | 2    |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz        | t <sub>DDKHAS</sub>                         | 2.1<br>2.5               | _                           | ns   | 3    |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz         | t <sub>DDKHAX</sub>                         | 2.4<br>3.15              |                             | ns   | 3    |

| MCS[ <i>n</i> ] output setup with respect to MCK<br>333 MHz<br>266 MHz | t <sub>DDKHCS</sub>                         | 2.4<br>3.15              | _                           | ns   | 3    |

| MCS[ <i>n</i> ] output hold with respect to MCK<br>333 MHz<br>266 MHz  | t <sub>DDKHCX</sub>                         | 2.4<br>3.15              |                             | ns   | 3    |

| MCK to MDQS Skew                                                       | t <sub>DDKHMH</sub>                         | -0.6                     | 0.6                         | ns   | 4    |

| MDQ//MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz    | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 800<br>900               |                             | ps   | 5    |

| MDQ//MDM output hold with respect to MDQS<br>333 MHz<br>266 MHz        | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 900<br>1100              | _                           | ps   | 5    |

| MDQS preamble start                                                    | t <sub>DDKHMP</sub>                         | $-0.5\times t_{MCK}-0.6$ | $-0.5 \times t_{MCK}$ + 0.6 | ns   | 6    |

| MDQS epilogue end                                                      | t <sub>DDKHME</sub>                         | -0.6                     | 0.6                         | ns   | 6    |

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ//MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

| Parameter                                                            | Symbol <sup>1</sup>                         | Min                             | Мах                         | Unit | Note |

|----------------------------------------------------------------------|---------------------------------------------|---------------------------------|-----------------------------|------|------|

| MCK[ <i>n</i> ] cycle time, MCK[ <i>n</i> ]/MCK[ <i>n</i> ] crossing | t <sub>MCK</sub>                            | 6                               | 10                          | ns   | 2    |

| ADDR/CMD output setup with respect to MCK<br>333 MHz<br>266 MHz      | t <sub>DDKHAS</sub>                         | 2.1<br>2.5                      |                             | ns   | 3    |

| ADDR/CMD output hold with respect to MCK<br>333 MHz<br>266 MHz       | t <sub>DDKHAX</sub>                         | 2.0<br>2.7                      |                             | ns   | 3    |

| MCS[n] output setup with respect to MCK<br>333 MHz<br>266 MHz        | t <sub>DDKHCS</sub>                         | 2.1<br>3.15                     |                             | ns   | 3    |

| MCS[n] output hold with respect to MCK<br>333 MHz<br>266 MHz         | t <sub>DDKHCX</sub>                         | 2.0<br>2.7                      |                             | ns   | 3    |

| MCK to MDQS Skew                                                     | t <sub>DDKHMH</sub>                         | -0.6                            | 0.6                         | ns   | 4    |

| MDQ//MDM output setup with respect to<br>MDQS<br>333 MHz<br>266 MHz  | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 800<br>900                      |                             | ps   | 5    |

| MDQ//MDM output hold with respect to MDQS<br>333 MHz<br>266 MHz      | t <sub>DDKHDX,</sub><br>t <sub>DDKLDX</sub> | 750<br>1000                     | _                           | ps   | 5    |

| MDQS preamble start                                                  | t <sub>DDKHMP</sub>                         | $-0.5\times t_{\text{MCK}}-0.6$ | $-0.5 \times t_{MCK}$ + 0.6 | ns   | 6    |

| MDQS epilogue end                                                    | t <sub>DDKHME</sub>                         | -0.6                            | 0.6                         | ns   | 6    |

### Table 21. DDR and DDR2 SDRAM Output AC Timing Specifications for Silicon Rev 2.x or Later

#### Notes:

- The symbols used for timing specifications follow the pattern of t<sub>(first two letters of functional block)(signal)(state)(reference)(state) for inputs and t<sub>(first two letters of functional block)(reference)(state)(signal)(state)</sub> for outputs. Output hold time can be read as DDR timing (DD) from the rising or falling edge of the reference clock (KH or KL) until the output went invalid (AX or DX). For example, t<sub>DDKHAS</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes from the high (H) state until outputs (A) are setup (S) or output valid time. Also, t<sub>DDKLDX</sub> symbolizes DDR timing (DD) for the time t<sub>MCK</sub> memory clock reference (K) goes low (L) until data outputs (D) are invalid (X) or data output hold time.

</sub>

- 2. All MCK/MCK referenced measurements are made from the crossing of the two signals ±0.1 V.

- 3. ADDR/CMD includes all DDR SDRAM output signals except MCK/MCK, MCS, and MDQ//MDM/MDQS.

- 4. Note that t<sub>DDKHMH</sub> follows the symbol conventions described in note 1. For example, t<sub>DDKHMH</sub> describes the DDR timing (DD) from the rising edge of the MCK[n] clock (KH) until the MDQS signal is valid (MH). t<sub>DDKHMH</sub> can be modified through control of the DQSS override bits in the TIMING\_CFG\_2 register. This is typically set to the same delay as the clock adjust in the CLK\_CNTL register. The timing parameters listed in the table assume that these 2 parameters have been set to the same adjustment value. See the MPC8313E PowerQUICC II Pro Integrated Processor Family Reference Manual, for a description and understanding of the timing modifications enabled by use of these bits.

- Determined by maximum possible skew between a data strobe (MDQS) and any corresponding bit of data (MDQ), ECC (MECC), or data mask (MDM). The data strobe should be centered inside of the data eye at the pins of the microprocessor.

- 6. All outputs are referenced to the rising edge of MCK[n] at the pins of the microprocessor. Note that t<sub>DDKHMP</sub> follows the symbol conventions described in note 1.

### NOTE

For the ADDR/CMD setup and hold specifications in Table 21, it is assumed that the clock control register is set to adjust the memory clocks by 1/2 applied cycle.

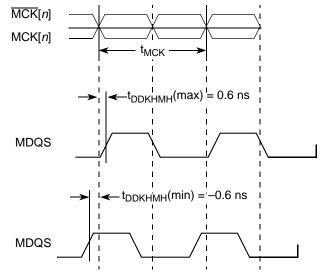

This figure shows the DDR SDRAM output timing for the MCK to MDQS skew measurement  $(t_{DDKHMH})$ .

Figure 5. Timing Diagram for t<sub>DDKHMH</sub>

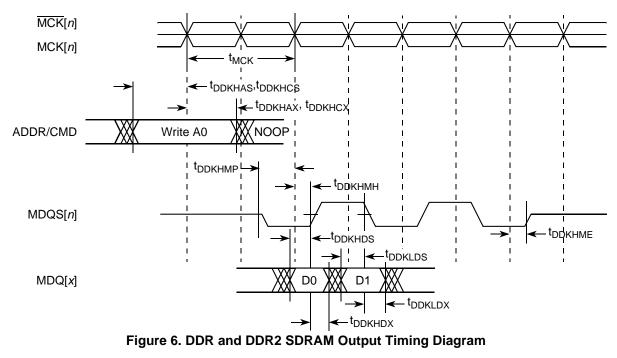

This figure shows the DDR and DDR2 SDRAM output timing diagram.

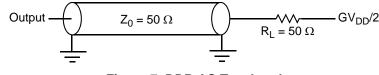

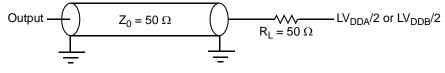

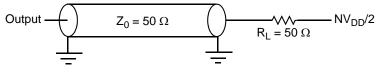

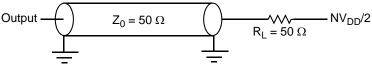

This figure provides the AC test load for the DDR bus.

Figure 7. DDR AC Test Load

# 7 DUART

This section describes the DC and AC electrical specifications for the DUART interface.

# 7.1 DUART DC Electrical Characteristics

This table provides the DC electrical characteristics for the DUART interface.

| Parameter                                                           | Symbol          | Min                    | Max                    | Unit |

|---------------------------------------------------------------------|-----------------|------------------------|------------------------|------|

| High-level input voltage                                            | V <sub>IH</sub> | 2.0                    | NV <sub>DD</sub> + 0.3 | V    |

| Low-level input voltage NV <sub>DD</sub>                            | V <sub>IL</sub> | -0.3                   | 0.8                    | V    |

| High-level output voltage, $I_{OH} = -100 \ \mu A$                  | V <sub>OH</sub> | NV <sub>DD</sub> – 0.2 | _                      | V    |

| Low-level output voltage, $I_{OL} = 100 \ \mu A$                    | V <sub>OL</sub> | —                      | 0.2                    | V    |

| Input current (0 V $\leq$ V <sub>IN</sub> $\leq$ NV <sub>DD</sub> ) | I <sub>IN</sub> | —                      | ±5                     | μA   |

# 7.2 DUART AC Electrical Specifications

This table provides the AC timing parameters for the DUART interface.

### Table 23. DUART AC Timing Specifications

| Parameter         | Value       | Unit | Note |

|-------------------|-------------|------|------|

| Minimum baud rate | 256         | baud | —    |

| Maximum baud rate | > 1,000,000 | baud | 1    |

| Oversample rate   | 16          | _    | 2    |

Notes:

1. Actual attainable baud rate is limited by the latency of interrupt processing.

2. The middle of a start bit is detected as the 8<sup>th</sup> sampled 0 after the 1-to-0 transition of the start bit. Subsequent bit values are sampled each 16<sup>th</sup> sample.

# 8 Ethernet: Three-Speed Ethernet, MII Management

This section provides the AC and DC electrical characteristics for three-speed, 10/100/1000, and MII management.

# 8.1 Enhanced Three-Speed Ethernet Controller (eTSEC) (10/100/1000 Mbps)—MII/RMII/RGMII/SGMII/RTBI Electrical Characteristics

The electrical characteristics specified here apply to all the media independent interface (MII), reduced gigabit media independent interface (RGMII), serial gigabit media independent interface (SGMII), and reduced ten-bit interface (RTBI) signals except management data input/output (MDIO) and management data clock (MDC). The RGMII and RTBI interfaces are defined for 2.5 V, while the MII interface can be operated at 3.3 V. The RMII and SGMII interfaces can be operated at either 3.3 or 2.5 V. The RGMII and RTBI interfaces follow the Hewlett-Packard reduced pin-count interface for *Gigabit Ethernet Physical Layer Device Specification Version 1.2a* (9/22/2000). The electrical characteristics for MDIO and MDC are specified in Section 8.5, "Ethernet Management Interface Electrical Characteristics."

# 8.1.1 **TSEC DC Electrical Characteristics**

All RGMII, RMII, and RTBI drivers and receivers comply with the DC parametric attributes specified in Table 24 and Table 25. The RGMII and RTBI signals are based on a 2.5-V CMOS interface voltage as defined by JEDEC EIA/JESD8-5.

### NOTE

eTSEC should be interfaced with peripheral operating at same voltage level.

| Parameter            | Symbol                               | Conditions                                   |                                    | Min             | Max                                                      | Unit |

|----------------------|--------------------------------------|----------------------------------------------|------------------------------------|-----------------|----------------------------------------------------------|------|

| Supply voltage 3.3 V | LV <sub>DDA</sub> /LV <sub>DDB</sub> | _                                            |                                    | 2.97            | 3.63                                                     | V    |

| Output high voltage  | V <sub>OH</sub>                      | I <sub>OH</sub> = -4.0 mA                    | $LV_{DDA}$ or $LV_{DDB} = Min$     | 2.40            | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Output low voltage   | V <sub>OL</sub>                      | I <sub>OL</sub> = 4.0 mA                     | $LV_{DDA}$ or $LV_{DDB}$ = Min     | V <sub>SS</sub> | 0.50                                                     | V    |

| Input high voltage   | V <sub>IH</sub>                      | _                                            | _                                  | 2.0             | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Input low voltage    | V <sub>IL</sub>                      | _                                            | —                                  | -0.3            | 0.90                                                     | V    |

| Input high current   | Ι <sub>ΙΗ</sub>                      | $V_{IN}^{1} = LV_{DDA} \text{ or } LV_{DDB}$ |                                    | —               | 40                                                       | μA   |

| Input low current    | ۱ <sub>IL</sub>                      | V                                            | / <sub>IN</sub> <sup>1</sup> = VSS | -600            | —                                                        | μΑ   |

### Table 24. MII DC Electrical Characteristics

Note:

1. The symbol  $V_{IN}$ , in this case, represents the  $LV_{IN}$  symbol referenced in Table 1 and Table 2.

### Table 25. RGMII/RTBI DC Electrical Characteristics

| Parameters           | Symbol              | Conditions | Min  | Max  | Unit |

|----------------------|---------------------|------------|------|------|------|

| Supply voltage 2.5 V | $LV_{DDA}/LV_{DDB}$ | _          | 2.37 | 2.63 | V    |

| Parameters          | Symbol          | C                                            | Conditions                        |                       | Мах                                                      | Unit |

|---------------------|-----------------|----------------------------------------------|-----------------------------------|-----------------------|----------------------------------------------------------|------|

| Output high voltage | V <sub>OH</sub> | I <sub>OH</sub> = -1.0 mA                    | $LV_{DDA}$ or $LV_{DDB} = Min$    | 2.00                  | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Output low voltage  | V <sub>OL</sub> | I <sub>OL</sub> = 1.0 mA                     | $LV_{DDA}$ or $LV_{DDB} = Min$    | V <sub>SS</sub> – 0.3 | 0.40                                                     | V    |

| Input high voltage  | V <sub>IH</sub> | —                                            | $LV_{DDA}$ or $LV_{DDB} = Min$    | 1.7                   | LV <sub>DDA</sub> + 0.3<br>or<br>LV <sub>DDB</sub> + 0.3 | V    |

| Input low voltage   | V <sub>IL</sub> | _                                            | $LV_{DDA}$ or $LV_{DDB}$ = Min    | -0.3                  | 0.70                                                     | V    |

| Input high current  | Ι <sub>ΙΗ</sub> | $V_{IN}^{1} = LV_{DDA} \text{ or } LV_{DDB}$ |                                   | —                     | 10                                                       | μΑ   |

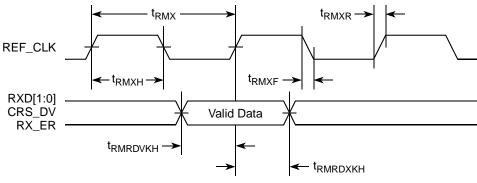

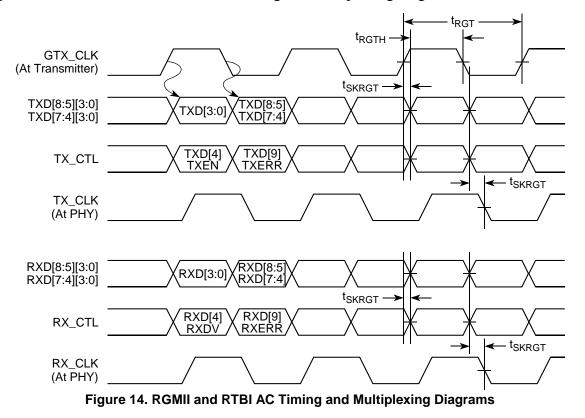

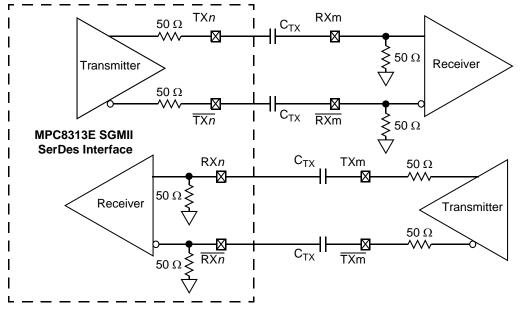

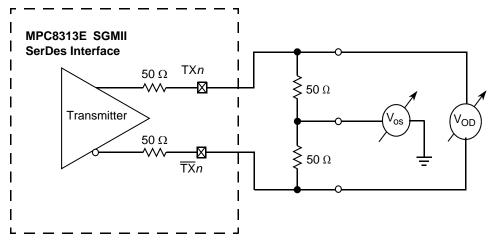

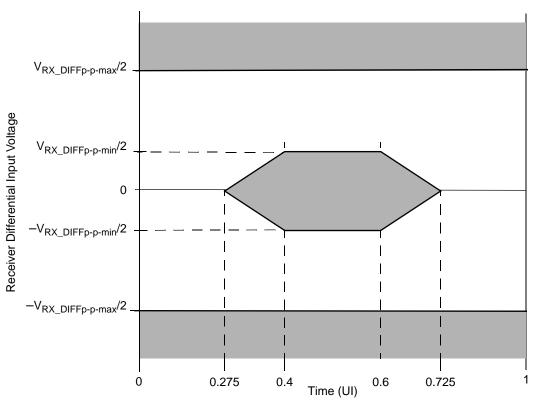

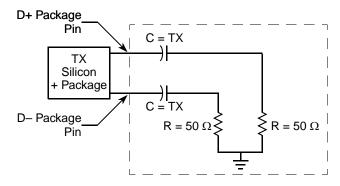

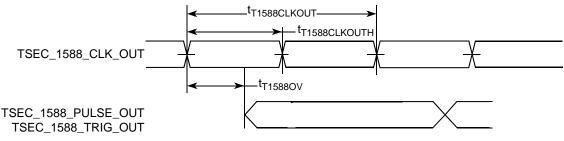

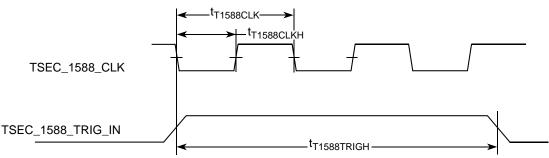

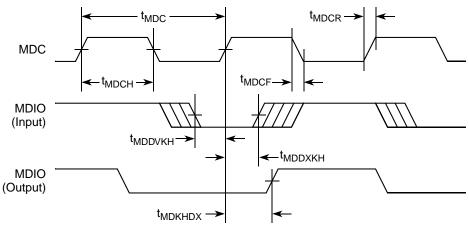

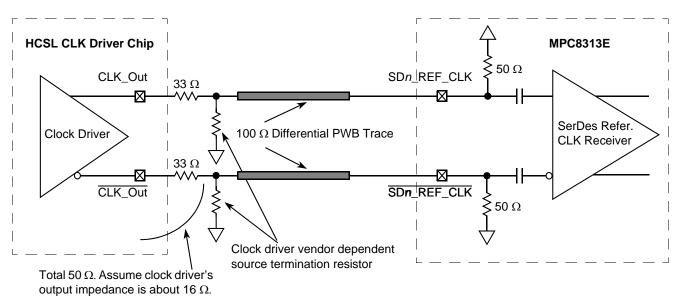

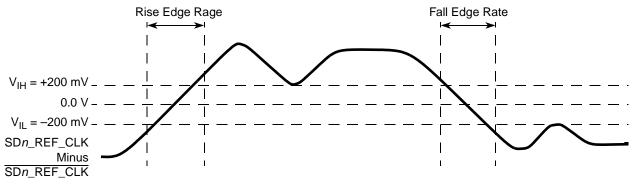

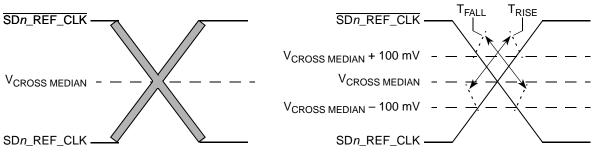

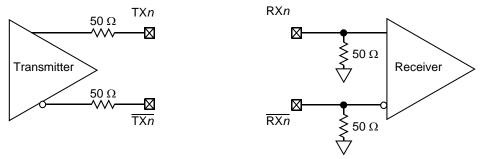

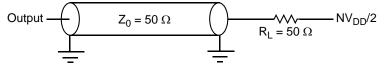

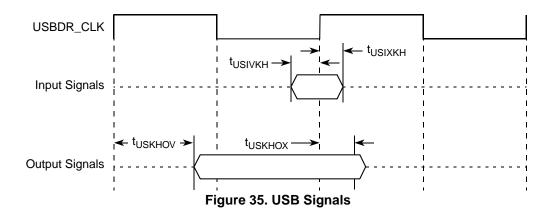

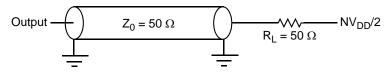

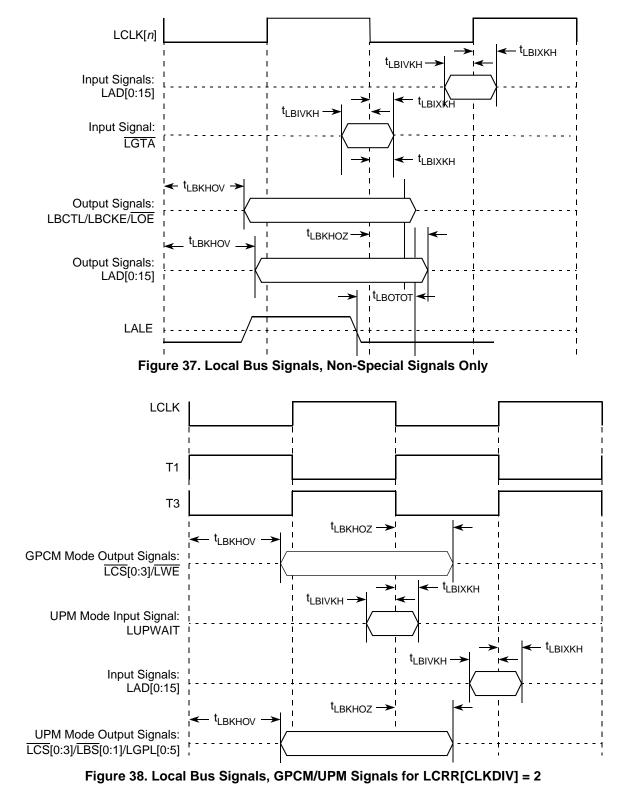

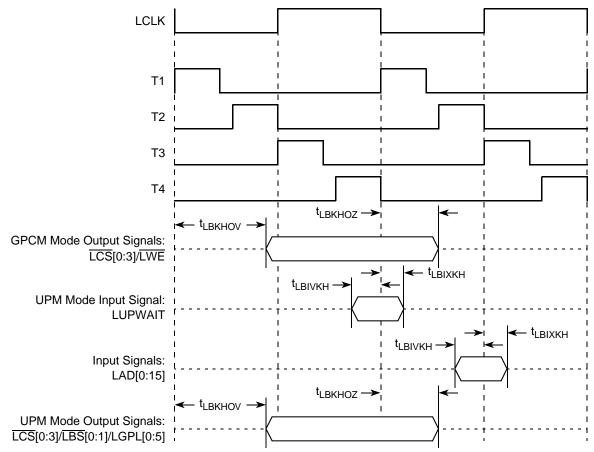

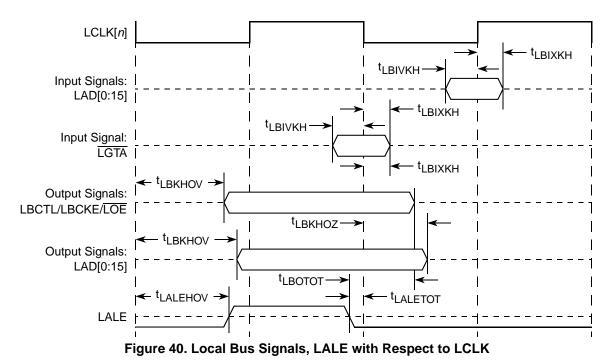

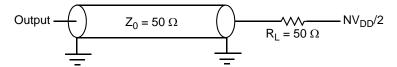

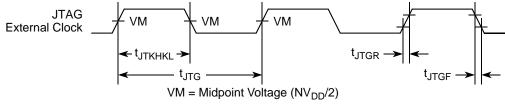

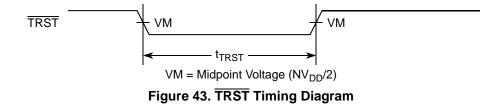

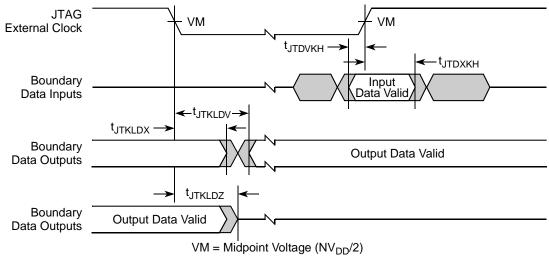

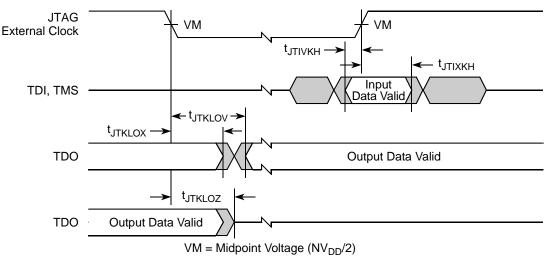

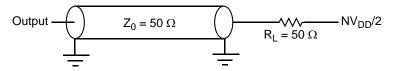

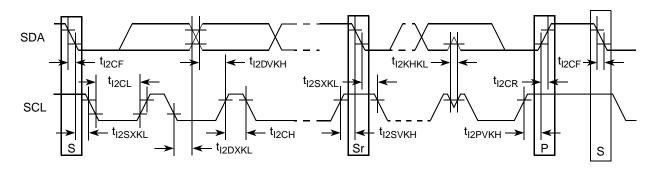

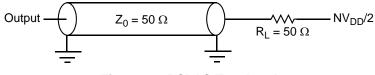

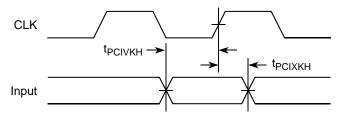

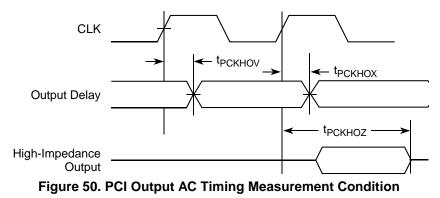

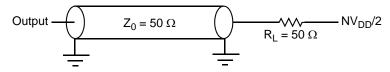

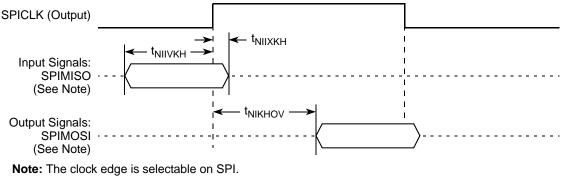

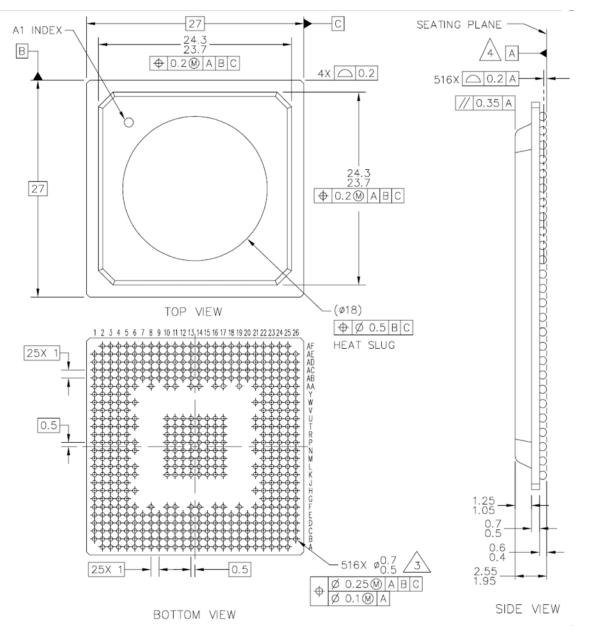

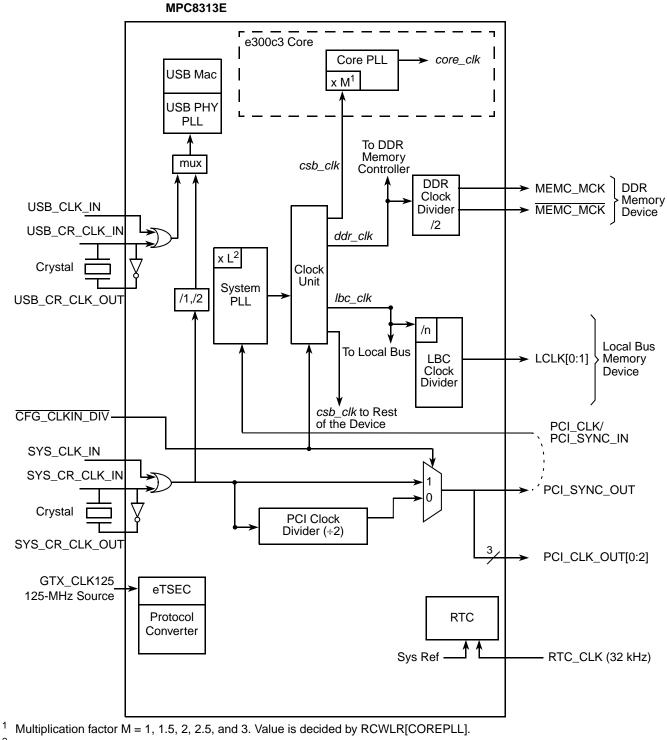

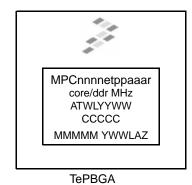

| Input low current   | ١ <sub>١L</sub> | ١                                            | $V_{\rm IN}^{1} = V_{\rm SS}^{1}$ | -15                   | —                                                        | μΑ   |