SLAS345 - DECEMBER 2001

# 5-V, LOW POWER, 14-BIT, 200-KSPS SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTO-POWER DOWN

### **FEATURES**

- 200-KSPS Sampling Rate

- Built-In Conversion Clock

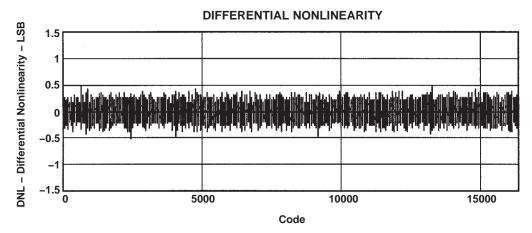

- INL: ±1 LSB Max DNL: ±1 LSB Max

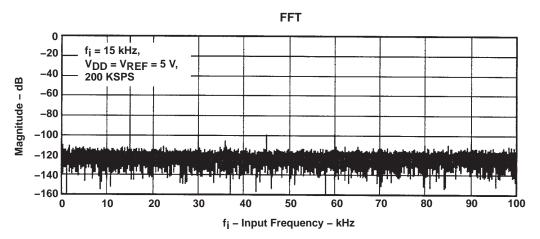

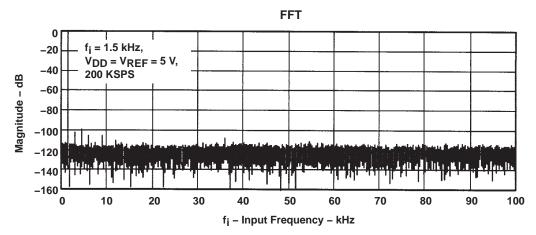

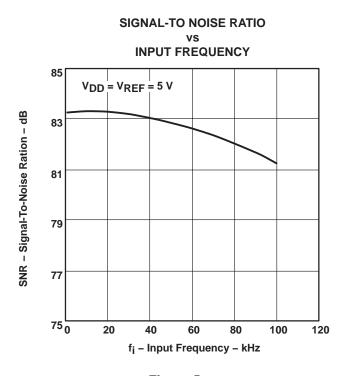

- SINAD = 81.5 dB, SFDR = 95 dB

THD = 94 dB at 15 kHz f<sub>in</sub>, 200 KSPS

- SPI/DSP-Compatible Serial Interfaces With SCLK Input up to 15 MHz

- Single 5-V Supply

- Rail-to-Rail Analog Input With 500 kHz BW

- Two Input Options Available:

- TLC3541 Single Channel Input

- TLC3545 Single Channel,

Pseudo-Differential Input

- (TLC3541) Optimized DSP Interface Requires FS Input Only

- Low Power With Auto-Power Down

- Operating Current: 3.5 mA

- Auto-Powerdown Current: 5 μA

- Pin Compatible 12-/14-/16-Bit Family in 8-Pin SOIC and MSOP Packages

### **APPLICATIONS**

- ATE System

- Industrial Process Control

- Measurement

- Motor Control

### **DESCRIPTION**

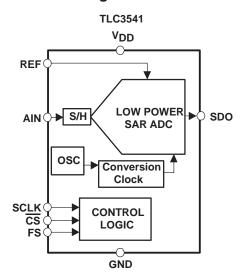

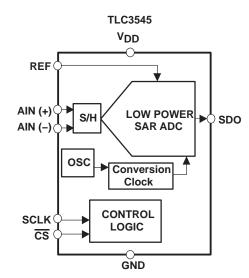

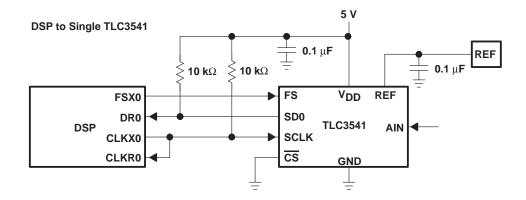

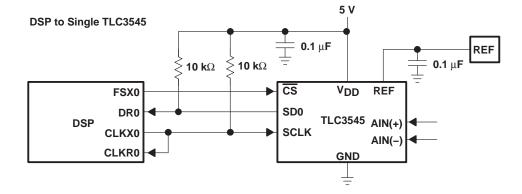

The TLC3541 and TLC3545 are a family of high performance, 14-bit, low power, miniature CMOS analog-to-digital converters (ADCs). These devices operate from a single 5-V supply. Devices are available with single, dual, or single pseudo-differential inputs. All of these devices have a chip select  $(\overline{CS})$ , serial clock (SCLK), and serial data output (SDO) that provides a direct 3-wire interface to the serial port of most popular host microprocessors (SPI interface). When interfaced with a DSP, a frame sync signal (FS) is used to indicate the start of a serial data frame on either pin 1  $(\overline{CS})$  or pin 7 (FS) for the TLC3541. The TLC3545 ADC connects to the DSP via pin 1 only  $(\overline{CS})$ .

The TLC3541 and TLC3545 are designed to operate with low power consumption. The power saving feature is further enhanced with an auto-power down mode. This product family features a high-speed serial link to modern host processors with an external SCLK up to 15 MHz. Both families use a built-in oscillator as the conversion clock, providing a 2.67  $\mu$ s maximum conversion time.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

### **AVAILABLE OPTIONS**

| _             | PACKAGED DEVICES             |            |  |  |  |  |  |

|---------------|------------------------------|------------|--|--|--|--|--|

| ТД            | 8-MSOP (DGK)                 | 8-SOIC (D) |  |  |  |  |  |

| -40°C to 85°C | TLC3541IDGK (PKG Code = AMG) | TLC3541ID  |  |  |  |  |  |

|               | TLC3545IDGK (PKG Code = AMM) | TLC3545ID  |  |  |  |  |  |

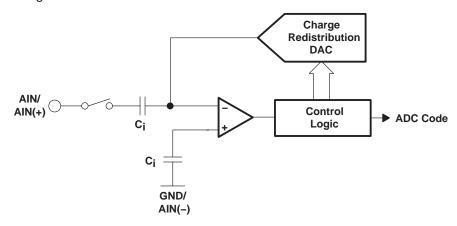

### functional block diagram

### **Terminal Functions**

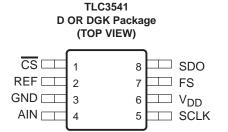

### TLC3541 single channel unipolar ADCs

| TERMIN   | AL  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                   |

|----------|-----|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                   |

| AIN      | 4   | I   | Analog input channel                                                                                                                                                                                                                                                          |

| CS       | 1   | I   | Chip select. A high-to-low transition on the $\overline{\text{CS}}$ input removes SDO from a high-impedance state within a maximum delay time. If the TLC3541 is attached to a dedicated TMS320 DSP serial port using the FS input, $\overline{\text{CS}}$ can be grounded.   |

| FS       | 7   | I   | DSP frame sync input. Indication of a start of a serial data frame. A low-to-high transition removes SDO from the high-impedance state and the MSB is presented. Tie this pin to V <sub>DD</sub> if not used.                                                                 |

| GND      | 3   | I   | Ground return for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                           |

| SDO      | 8   | 0   | $\frac{\text{The 3-state serial data output for the A/D conversion result. SDO is kept in the high-impedance state when }{\text{CS}} \text{ is high. The output format is MSB first. Remaining data bits are presented on the rising edge of SCLK.}$                          |

|          |     |     | When FS is not active (FS = 1 at the falling edge of $\overline{CS}$ ): The MSB is presented on the SDO pin on the falling edge of $\overline{CS}$ after a maximum delay time. Data is valid on each falling edge of SCLK until all data is read.                             |

|          |     |     | When FS is active (FS = 0 at the falling edge of $\overline{\text{CS}}$ ): The MSB is presented to the SDO output on the rising edge of FS. Data is valid on the falling edge SCLK and changes on the rising edge SCLK (this is typically used with an active FS from a DSP). |

|          |     |     | SDO returns to the high-impedance state after the 17th rising edge on SCLK. If a 17th SCLK cycle is not presented, as is the case when using an SPI host, SDO returns to the high-impedance state on the rising edge of $\overline{\text{CS}}$ .                              |

| SCLK     | 5   | I   | Serial clock. This terminal receives the serial SCLK from the host processor.                                                                                                                                                                                                 |

| REF      | 2   | I   | External voltage reference input                                                                                                                                                                                                                                              |

| $V_{DD}$ | 6   | Ι   | Positive supply voltage                                                                                                                                                                                                                                                       |

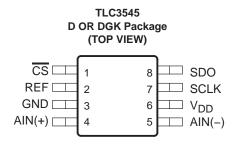

### TLC3545 single channel pseudo-differential ADCs

| TERMIN   | AL  | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|----------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NAME     | NO. | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AIN0 (+) | 4   | - 1 | Positive analog input for the TLC3545.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| AIN1 (-) | 5   | -1  | Inverted analog input for the TLC3545.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| CS       | 1   | I   | Chip select. A high-to-low transition on $\overline{\text{CS}}$ removes SDO from the high-impedance state within a maximum delay time. The $\overline{\text{CS}}$ input can be connected to a DSP frame sync (FS) output when a dedicated TMS320 DSP serial port is used.                                                                                                                                                                                                                                                                                                                                                                                                 |

| GND      | 3   | I   | Ground return for the internal circuitry. Unless otherwise noted, all voltage measurements are with respect to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| SDO      | 8   | 0   | The 3-state serial data output for the A/D conversion result. SDO is kept in the high-impedance state when $\overline{\text{CS}}$ is high and presents output data after the $\overline{\text{CS}}$ falling edge until the LSB is presented. The output format is MSB first. The remaining data bits are presented on the rising edge of SCLK. Output data is valid on each falling edge of SCLK until all data is read. SDO returns to the high-impedance state after the 17th rising edge on SCLK. If a 17th SCLK cycle is not presented, as is the case when using an SPI host, SDO returns to the high-impedance state on the rising edge of $\overline{\text{CS}}$ . |

| SCLK     | 7   | I   | Serial clock. This terminal receives the serial SCLK from the host processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| REF      | 2   | 1   | External voltage reference input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $V_{DD}$ | 6   | 1   | Positive supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

SLAS345 - DECEMBER 2001

### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage, GND to V <sub>DD</sub>                          | 0.3 V to 6.5V                   |

|-----------------------------------------------------------------|---------------------------------|

| Analog input voltage range                                      | 0.3 V to V <sub>DD</sub> +0.3 V |

| Reference input voltage                                         | V <sub>DD</sub> +0.3 V          |

| Digital input voltage range                                     |                                 |

| Operating virtual junction temperature range, T <sub>J</sub>    | –40°C to 150°C                  |

| Operating free-air temperature range: T <sub>A</sub> (I suffix) | –40°C to 85°C                   |

| Storage temperature range, T <sub>Stq</sub>                     |                                 |

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds    | 260°C                           |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### recommended operating conditions

|                                                    |                                                                                      | MIN  | NOM  | MAX      | UNIT |

|----------------------------------------------------|--------------------------------------------------------------------------------------|------|------|----------|------|

| Supply voltage, V <sub>DD</sub>                    |                                                                                      | 4.5  | 5    | 5.5      | V    |

| Frequency, SCLK                                    | V <sub>DD</sub> = 4.5 V to 5.5 V                                                     | 100  |      | 15000    | kHz  |

| Tolerable clock jitter, SCLK                       | V <sub>DD</sub> = 4.5 V to 5.5 V                                                     |      |      | 97       | ps   |

| Aperature jitter                                   | V <sub>DD</sub> = 4.5 V to 5.5 V                                                     |      | 100  |          | ps   |

| External reference voltage input, V <sub>REF</sub> | External reference voltage input, V <sub>REF</sub>                                   | 4    |      | $V_{DD}$ | V    |

|                                                    | $V_{DD} = 5 \text{ V}, \overline{CS} = 1, \text{ SCLK} = 0$                          | 100  |      |          | MΩ   |

| V <sub>REF</sub> input impedance                   | $V_{DD} = 5 \text{ V},  \overline{CS} = 0,  \text{SCLK} = 15 \text{ MHz}$            | 20   | 25   |          | kΩ   |

| External reference input current                   | $V_{DD} = V_{REF} = 4.5 \text{ V}, \overline{CS} = 0, \text{ SCLK} = 15 \text{ MHz}$ |      | 0.02 | 1        | mA   |

|                                                    | AIN, AIN(+)                                                                          | 0    |      | $V_{DD}$ | .,   |

| Analog input voltage                               | AIN(-)                                                                               | -0.2 |      | 0.2      | V    |

| High level control input voltage, V <sub>IH</sub>  |                                                                                      |      |      |          | V    |

| Low level control input voltage, V <sub>IL</sub>   |                                                                                      |      |      | 0.8      | V    |

| Operating free-air temperature, T <sub>A</sub>     | TLC3541/45I                                                                          | -40  |      | 85       | °C   |

# electrical characteristics over recommended operating free-air temperature range, $V_{DD} = 5 \text{ V}$ , $V_{REF} = 4.096 \text{ V}$ , SCLK frequency = 15 MHz (unless otherwise noted)

|         | PARAMETER                             | TEST CONDITIONS                                                                                                                                                | MIN | TYP    | MAX  | UNIT |

|---------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--------|------|------|

| Vон     | High-level output voltage             | $V_{DD} = 4.5 \text{ V}, \qquad I_{OH} = -0.2 \text{ mA}$                                                                                                      | 3.9 |        |      | V    |

| VOL     | Low-level output voltage              | $V_{DD} = 4.5 \text{ V}$ $I_{OL} = 0.8 \text{ mA}$                                                                                                             |     |        | 0.4  | V    |

|         | Off-state output current              | $V_O = V_{DD},$ $\overline{CS} = V_{DD}$                                                                                                                       |     | 1      | 2.5  |      |

| loz     | (high-impedance-state)                | $V_O = 0$ , $\overline{CS} = V_{DD}$                                                                                                                           |     | -1     | -2.5 | μΑ   |

| lн      | High-level input current              | $V_I = V_{DD}$                                                                                                                                                 |     | 0.005  | 2.5  | μΑ   |

| IIL     | Low-level input current               | V <sub>I</sub> = 0                                                                                                                                             |     | -0.005 | 2.5  | μΑ   |

| ICC     | Operating supply current              | <del>CS</del> at 0 V, V <sub>DD</sub> = 4.5 V to 5.5 V                                                                                                         |     |        | 3.5  | mA   |

| ICC(PD) | Power-down supply current             | For all digital inputs, $0 \le V_I \le 0.3 \text{ V}$<br>or $V_I \ge V_{DD} - 0.3 \text{ V}$ , SCLK= $V_{DD}$ ,<br>$V_{DD} = 4.5 \text{ V}$ to $5.5 \text{ V}$ |     | 3      | 5    | μА   |

|         | Selected analog input channel leakage | Selected channel at V <sub>DD</sub>                                                                                                                            |     |        | 1    |      |

|         | current                               | Selected channel at 0 V                                                                                                                                        |     |        | -1   | μΑ   |

|         | Land and all the second               | Analog inputs                                                                                                                                                  |     | 11     | 14   |      |

| Ci      | Input capacitance                     | Control Inputs                                                                                                                                                 |     | 20     | 25   | рF   |

| Zi      | Input resistance                      | V <sub>DD</sub> = 5.5 V                                                                                                                                        |     |        | 500  | Ω    |

### ac specifications (TLC3541/45)

|                                           | PARAMETER                              |         | TEST CONDITIONS                     | MIN | TYP  | MAX | UNIT |

|-------------------------------------------|----------------------------------------|---------|-------------------------------------|-----|------|-----|------|

| SINAD                                     | Signal-to-noise ratio +distortion      |         | f <sub>I</sub> = 15 kHz at 200 KSPS |     | 81.5 |     | dB   |

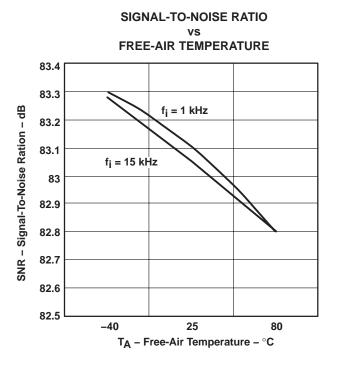

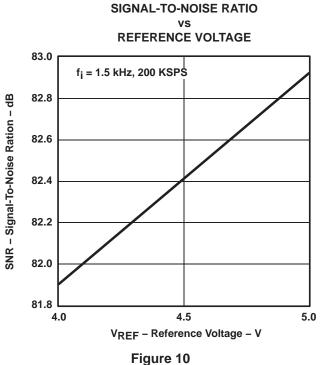

| SNR                                       | Signal-to-noise ratio                  |         | f <sub>I</sub> = 15 kHz at 200 KSPS |     | 82   |     | dB   |

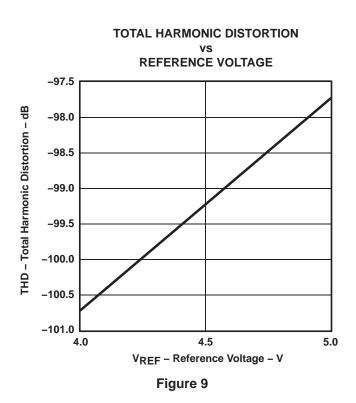

| TUD                                       | TLC3541                                |         | f <sub>I</sub> = 15 kHz at 200 KSPS |     | -94  | -87 | -10  |

| THD                                       | Total harmonic distortion TLC3545      |         | f <sub>I</sub> = 15 kHz at 200 KSPS |     | -94  | -89 | dB   |

| ENOB                                      | Effective number of bits               |         | f <sub>I</sub> = 15 kHz at 200 KSPS |     | 13.2 |     | Bits |

| OFDD                                      | 0                                      | TLC3541 | f <sub>I</sub> = 15 kHz at 200 KSPS |     | -95  | -87 | 10   |

| SFDR                                      | OR Spurious free dynamic range TLC3545 |         | f <sub>I</sub> = 15 kHz at 200 KSPS |     | -95  | -89 | dB   |

| Full-power bandwidth, –3 dB, analog input |                                        |         |                                     |     | 1    |     | MHz  |

| Full-power bandwidth, -1 dB, analog input |                                        |         |                                     |     | 500  |     | kHz  |

| Crosstal                                  | k                                      |         | 0.25 LSB                            | 80  |      |     | dB   |

### dc specifications (TLC3541/45)

|                      | ,                                     |                 |      |                  |     |      |  |

|----------------------|---------------------------------------|-----------------|------|------------------|-----|------|--|

|                      | PARAMETER                             | TEST CONDITIONS | MIN  | TYP <sup>†</sup> | MAX | UNIT |  |

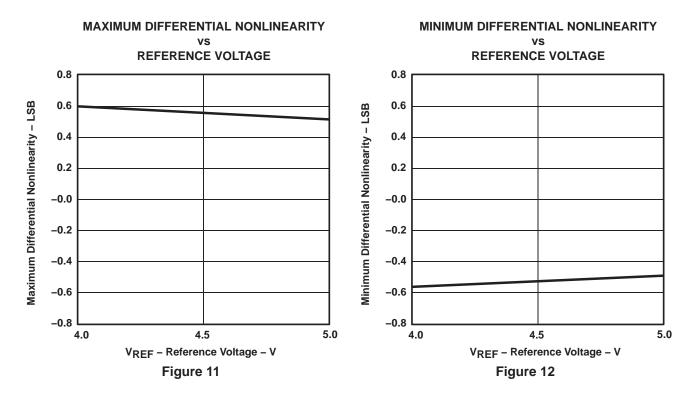

| INL                  | Integral linearity error (see Note 1) |                 | -1   |                  | 1   | LSB  |  |

| DNL                  | Differential linearity error          |                 | -1   | 0.75             | 1   | LSB  |  |

| _                    | 0" ( ) ( )                            | TLC3541         | -3.5 |                  | 3.5 | .,   |  |

| E <sub>O</sub> Offse | Offset error (see Note 2)             | TLC3545         | -1   |                  | 1   | mV   |  |

| _                    | 0 : ( ) 1 : 0                         | TLC3541         | -2   |                  | 2   | .,   |  |

| EG                   | Gain error (see Note 2)               | TLC3545         | -1.8 |                  | 1.8 | mV   |  |

<sup>†</sup> All typical values are at  $V_{DD} = 5 \text{ V}$ ,  $T_A = 25^{\circ}\text{C}$ .

NOTES: 1. Linear error is the maximum deviation from the best straight line through the A/D transfer characteristics.

<sup>2.</sup> Zero error is the difference between 0000h and the converted output for zero input voltage: full-scale error is the difference between ideal full-scale and the converted output for full-scale input voltage.

# TLC3541, TLC3545

### SLAS345 - DECEMBER 2001

# timing requirements, $V_{DD}$ = 5 V, $V_{REF}$ = 4.096 V, SCLK frequency = 15 MHz (unless otherwise specified)

|                  |                                                                                                                               | MIN  | TYP | MAX   | UNIT  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| tcyc(SCLK)       | SCLK cycle time, V <sub>DD</sub> = 4.5 V to 5.5 V (see Note 3)                                                                | 66   |     | 10000 | ns    |

| t <sub>w1</sub>  | Pulse duration, SCLK low                                                                                                      | 27   |     | 5000  | ns    |

| t <sub>w2</sub>  | Pulse duration, SCLK high                                                                                                     | 27   |     | 5000  | ns    |

| t <sub>h1</sub>  | Hold time, CS high after SCLK falling edge                                                                                    | 3    |     |       | ns    |

| t <sub>su1</sub> | Setup time, CS falling edge before the first SCLK falling edge                                                                | 15   |     |       | ns    |

| t <sub>h2</sub>  | Hold time, CS low after 16th SCLK falling edge                                                                                | 5    |     |       | ns    |

| t <sub>W3</sub>  | Pulse duration, CS high                                                                                                       | 0.5  |     |       | SCLKs |

| <sup>t</sup> d1  | Delay time, $\overline{\text{CS}}$ falling edge to SDO MSB valid, $V_{DD} = V_{REF} = 4.5 \text{ V}$ , 20 pF                  |      | 12  | 17    | ns    |

| t <sub>d2</sub>  | Delay time, SCLK rising edge to next SDO data bit valid, V <sub>DD</sub> = V <sub>REF</sub> = 4.5 V, 20 pF                    |      |     | 15    | ns    |

| t <sub>d3</sub>  | Delay time, 17 <sup>th</sup> SCLK rising edge to 3-stated SDO, V <sub>DD</sub> = V <sub>REF</sub> = 4.5 V, 20 pF (see Note 4) |      |     | 20    | ns    |

| t <sub>su3</sub> | Setup time, CS falling edge before FS rising edge (TLC3541 only)                                                              | 0.5  | 1   |       | SCLKs |

| t <sub>W4</sub>  | Pulse duration, FS high (TLC3541 only)                                                                                        | 0.5  | 1   |       | SCLKs |

| t <sub>su4</sub> | Setup time, FS rising edge before SCLK falling edge (TLC3541 only)                                                            | 12.5 |     |       | ns    |

| t <sub>h4</sub>  | Hold time, FS high after SCLK falling edge (TLC3541 only)                                                                     | 5    |     |       | ns    |

| t <sub>su5</sub> | Setup time, FS falling edge before 1st SCLK falling edge (TLC3541 only)                                                       | 12   |     |       | ns    |

| t <sub>d4</sub>  | Delay time, FS rising edge to SDO MSB valid, (V <sub>DD</sub> = V <sub>REF</sub> = 4.5 V, 20 pF TLC3541 only)                 |      |     | 15    | ns    |

| th6              | Hold time, CS low after 1st SCLK falling edge                                                                                 | 5    |     |       | ns    |

| t <sub>su6</sub> | Setup time, CS rising edge before 9th (or the last) SCLK falling edge                                                         | 5    |     |       | ns    |

| t <sub>h7</sub>  | Hold time, FS low after 1st SCLK falling edge (TLC3541 only)                                                                  | 5    |     |       | ns    |

| t <sub>su7</sub> | Setup time, FS rising edge before 9th (or the last) SCLK falling edge                                                         | 5    |     |       | ns    |

| tcyc(reset)      | Active CS/FS cycle time, SCLK falling edges required to initialize ADC                                                        | 1    |     | 8     | SCLKs |

| tconv            | Conversion time (20 conversion clocks based on 7.5 MHz to 12 MHz OSC)                                                         | 1.67 |     | 2.67  | μs    |

| t <sub>S</sub>   | Sample time, 20 SCLKs, SCLK up to 15 MHz                                                                                      | 1.33 |     | 200   | μs    |

NOTES: 3. Timing specifications given for 40/60 to 60/40 duty cycle

<sup>4.</sup> SDO goes into the high impedance state after detection of the 17th rising SCLK edge or a rising  $\overline{\text{CS}}$  edge if a 17th SCLK is not presented.

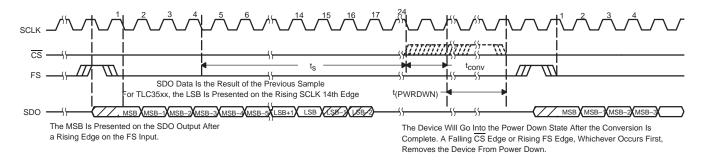

Figure 1

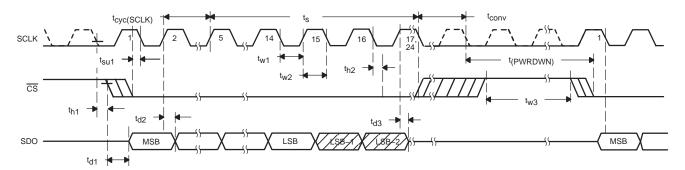

Figure 2

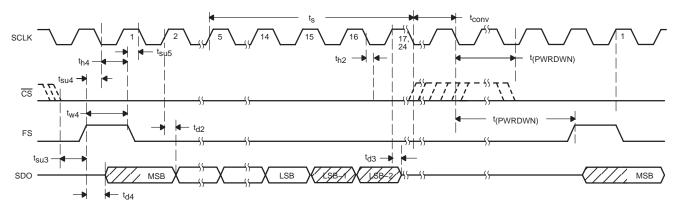

Figure 3

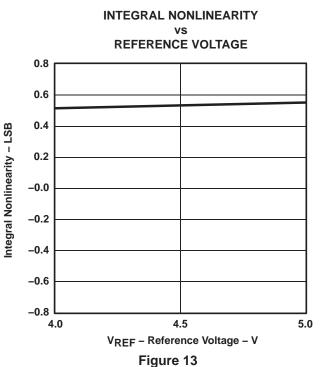

# UNTEGRAL NONLINEARITY 1.5 0.5 -0.5 -1 -1.5 0 5000 10000 15000 Code

Figure 4

# INPUT FREQUENCY -80 VDD = VREF = 5 V -90 -90 20 40 60 80 100 120

fi - Input Frequency - kHz

**TOTAL HARMONIC DISTORTION**

Figure 5 Figure 6

### **TOTAL HARMONIC DISTORTION** FREE-AIR TEMPERATURE -82 -84 THD - Total Harmonic Distortion - dB -86 f<sub>i</sub> = 100 kHz -88 -90 -92 $f_i = 15 \text{ kHz}$ -94 -96 $f_i = 1 \text{ kHz}$ -98 -40 25 80 $T_A$ – Free-Air Temperature – $^{\circ}C$

Figure 7

Figure 8

### control and timing

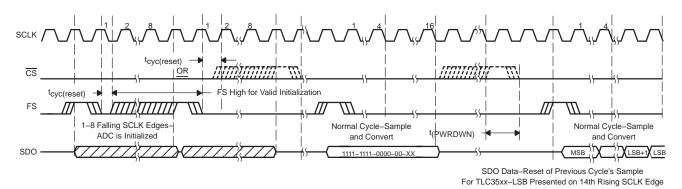

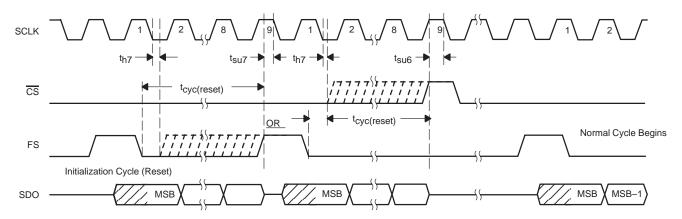

### device initialization/RESET cycle

The TLC3541/45 each require one RESET cycle after power-on for initialization in order to operate properly. The RESET cycle is initiated by asserting the  $\overline{CS}$  pin (pin 1) low for a minimum duration of at least one SCLK falling edge but no more than 8 SCLK falling edges in length. The RESET cycle is terminated by asserting  $\overline{CS}$  high. If a valid RESET cycle is issued, the data presented on the SDO output during the following cycle is 3FC0h. This output code is useful in determining when a valid reset/initialization has occurred.

The TLC3541 has separate  $\overline{CS}$  and FS pins. In this case, it is also possible to initiate the RESET cycle by asserting FS low if  $\overline{CS}$  is already asserted low. The RESET cycle can be terminated by either asserting  $\overline{CS}$  high (as shown in the first RESET cycle in Figure 14), or by asserting FS high (as shown in the second RESET cycle in Figure 14), whichever happens first.

Figure 14. TLC3541/45 Initialization Timing

### sampling

The converter sample time is 20 SCLKs in duration, beginning on the 5th SCLK received during an active signal on the  $\overline{\text{CS}}$  input (or FS input for the TLC3541.)

### conversion

Each device completes a conversion in the following manner. The conversion is started after the 24th falling SCLK edge. The  $\overline{\text{CS}}$  input can be released at this point or at any time during the remainder of the conversion cycle. The conversion takes a maximum of 2.67  $\mu$ s to complete. Enough time (for conversion) should be allowed before the next falling edge on the  $\overline{\text{CS}}$  input (or rising edge on the FS input for the TLC3541) so that no conversion is terminated prematurely. If the conversion cycle is terminated early, the data presented on SDO during the following cycle is 3FC0h. This predefined output code is helpful in determining if the cycle time is not long enough to complete the conversion. The same code is also used to determine if a reset cycle is valid.

For all devices, the SDO data presented during a cycle is the result of the conversion of the sample taken during the previous cycle. The output data format is shown in the following table.

| SERIAL OUTPUT DATA FORMAT |                              |            |  |  |  |  |  |  |

|---------------------------|------------------------------|------------|--|--|--|--|--|--|

|                           | MSB [D15:D2] LSB [D1:D0]     |            |  |  |  |  |  |  |

| TLC3541/45                | Conversion result (OD13-OD0) | Don't care |  |  |  |  |  |  |

### control and timing (continued)

### sampling and conversion cycle

### TLC3541:

Control via pin  $\underline{1}$ ,  $\overline{CS}$  (FS = 1 at the falling edge of  $\overline{CS}$ ) – The falling edge of  $\overline{CS}$  is the start of the cycle. Transitions on  $\overline{CS}$  can occur when SCLK is high or low. The MSB may be read on the first falling SCLK edge after  $\overline{CS}$  is low. Output data changes on the rising edge of SCLK. This control method is typically used for a microcontroller with an SPI interface, although it can also be used for a DSP. The microcontroller SPI interface should be programmed for CPOL = 0 (serial clock inactive low) and CPHA = 1 (data valid on the falling edge of serial clock).

Control via pin 7, FS  $\overline{\text{CS}}$  is tied/held low) – The rising edge of FS is the start of the cycle. Transitions on FS can occur when SCLK is high or low. The MSB is presented on SDO after the rising edge of FS. The MSB may be read on the first falling edge of SCLK after the FS falling edge. Output data changes on the rising edge of SCLK. This is the typical configuration when the ADC is the only device on the TMS320 DSP serial port.

Control via pin 1 and pin 7,  $\overline{\text{CS}}$  and FS – Transitions on  $\overline{\text{CS}}$  and FS can occur when SCLK is high or low. The MSB is presented after the rising edge of FS. The falling edge of FS is the start of the sampling cycle. The MSB may be read on the first falling edge of SCLK after the FS falling edge. Output data changes on the rising edge of SCLK. This is typically used for multiple devices connected to a single TMS320 DSP serial port.

### TLC3545:

All control is provided using the  $\overline{CS}$  input (pin 1) on the TLC3545. Transitions on  $\overline{CS}$  can occur when SCLK is high or low. The cycle is started on the falling edge transition on the  $\overline{CS}$  input. This signal can be provided by either a  $\overline{CS}$  signal (when interfacing with an SPI microcontroller) or FS signal (when interfacing with a TMS320 DSP). The MSB is presented to SDO on the falling edge of the signal applied to pin 1 and may be read on the first falling SCLK edge after this input is low. Output data changes on the rising edge of SCLK.

### control modes

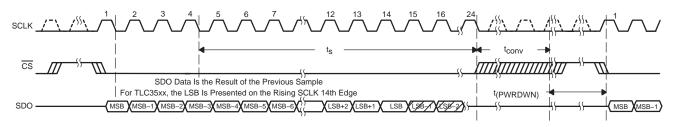

### control via pin 1 (CS, SPI interface)

All devices are compatible with this mode of operation. A falling edge on the  $\overline{CS}$  input initiates the cycle. (For the TLC3541, the FS input is tied to  $V_{DD}$ ). The  $\overline{CS}$  input remains low for the entire sampling time plus 4 SCLK decoding time (24 falling SCLK edges) and can then be released at any point during the remainder of the conversion. Enough time should be allowed before the next falling  $\overline{CS}$  edge so that the conversion cycle is not terminated prematurely. The microcontroller SPI interface should be programmed for CPOL = 0 (serial clock inactive low) and CPHA = 1 (data is valid on the falling edge of serial clock).

Figure 15. SPI Cycle Timing Using the CS Input (FS = 1 for TLC3541)

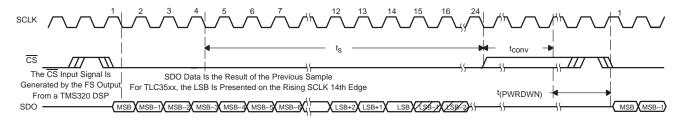

### control via pin 1 (CS, DSP interface)

All devices are compatible with this mode of operation. The FS signal from a DSP is connected directly to the  $\overline{\text{CS}}$  input of the ADC. A falling edge on the  $\overline{\text{CS}}$  input while SCLK is high or low initiates the cycle. (For TLC3541 in this configuration, the FS input is tied to  $V_{DD}$ .) Enough time should be allowed before the next rising  $\overline{\text{CS}}$  edge so that the conversion cycle is not terminated prematurely.

Figure 16. DSP Cycle Timing Using the CS Input (FS = 1 for TLC3541 only)

### control via pin 1 and pin 7 (CS and FS or FS only, DSP interface)

Only TLC3541 is compatible with this mode of operation. The  $\overline{\text{CS}}$  input to the ADC can be controlled via a general-purpose I/O pin from the DSP or tied to ground. The FS signal from the DSP is connected directly to the FS input of the ADC. A rising FS edge releases the MSB to the SDO output. The falling edge on the FS input while SCLK is high or low initiates the cycle. The  $\overline{\text{CS}}$  input should remain low for the entire sampling time plus 4 SCLK decoding time after falling FS (24 falling SCLK edges) and can then be released at any time during the remainder of the conversion cycle. The optimum DSP interface is achieved when tying  $\overline{\text{CS}}$  to ground and using only the FS input to control the ADC.

Figure 17. DSP Cycle Timing Using FS Only (or Using Both CS and FS for TLC3541)

Figure 18. Critical Timing: Control Via CS Input (FS = 1 for TLC3541)

Figure 19. Critical Timing: Control Via CS and FS Inputs (TLC3541 Only)

Figure 20. Critical Timing: Reset/Initialization Cycle (FS =1 for TLC3541)

Figure 21. Critical Timing: Initialization Cycle (TLC3541 Only)

### detailed description

The TLC3541/5 are successive approximation (SAR) ADCs utilizing a charge-redistribution DAC. Figure 22 shows a simplified version of the ADC. The sampling capacitor acquires the signal on AIN (or the AIN(+) pin for TLC3545) during the sampling period. When the conversion process starts, the SAR control logic and charge redistribution DAC are used to add and subtract fixed amounts of charge from the sampling capacitor to bring the comparator into a balanced condition. When the comparator is balanced, the conversion is complete and the ADC output code is generated.

Figure 22. Simplified SAR Circuit

### pseudo-differential inputs

The TLC3545 operates in pseudo-differential mode. The inverted input is available on pin 5. The inverted input can tolerate a maximum input ripple of  $\pm 0.2$  V. It is normally used for zero-scale offset cancellation or ground noise rejection.

### serial interface

Output data format is binary (unipolar straight binary).

### binary

- Zero-Scale Code = 0000h, V<sub>AIN</sub> = GND

- Full-Scale Code = 3FFFh, V<sub>AIN</sub> = V<sub>REF</sub> 1 LSB

### reference voltage

An external reference must be applied via pin 2,  $V_{REF}$ . The voltage level applied to this pin establishes the upper limit of the analog inputs to produce a full-scale reading. The value of  $V_{REF}$ , and the analog input should not exceed the positive supply or be less than GND, consistent with the specified absolute maximum ratings. The digital output is at full scale when the input signal is equal to or higher than  $V_{REF}$  and at zero when the input signal is equal to or less than GND.

### auto-power down and power up

Auto-power down is built into the devices in order to reduce power consumption. The wake-up time is fast enough to provide power down between each conversion cycle. The power-down state is initiated at the end of conversion and wakes up on a falling  $\overline{CS}$  edge (or rising FS edge, whichever occurs first, for TLC3541 only).

### **APPLICATION INFORMATION**

### **DSP to Multiple TLC3541s**

Figure 23. Typical ADC Interface to a TMS320 DSP

16-Aug-2012

### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package Type | Package<br>Drawing | Pins | Package Qty | Eco Plan <sup>(2)</sup>    | Lead/<br>Ball Finish | MSL Peak Temp <sup>(3)</sup> | Samples<br>(Requires Login) |

|------------------|-----------------------|--------------|--------------------|------|-------------|----------------------------|----------------------|------------------------------|-----------------------------|

| TLC3541ID        | ACTIVE                | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3541IDG4      | ACTIVE                | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3541IDGK      | ACTIVE                | VSSOP        | DGK                | 8    | 80          | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAC          | GLevel-1-260C-UNLIM          |                             |

| TLC3541IDGKG4    | ACTIVE                | VSSOP        | DGK                | 8    | 80          | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAC          | GLevel-1-260C-UNLIM          |                             |

| TLC3541IDGKR     | ACTIVE                | VSSOP        | DGK                | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAC          | GLevel-1-260C-UNLIM          |                             |

| TLC3541IDGKRG4   | ACTIVE                | VSSOP        | DGK                | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAC          | GLevel-1-260C-UNLIM          |                             |

| TLC3541IDR       | ACTIVE                | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3541IDRG4     | ACTIVE                | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3545ID        | ACTIVE                | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3545IDG4      | ACTIVE                | SOIC         | D                  | 8    | 75          | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3545IDGK      | ACTIVE                | VSSOP        | DGK                | 8    | 80          | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAC          | GLevel-1-260C-UNLIM          |                             |

| TLC3545IDGKG4    | ACTIVE                | VSSOP        | DGK                | 8    | 80          | Green (RoHS<br>& no Sb/Br) | CU NIPDAUAC          | GLevel-1-260C-UNLIM          |                             |

| TLC3545IDR       | ACTIVE                | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

| TLC3545IDRG4     | ACTIVE                | SOIC         | D                  | 8    | 2500        | Green (RoHS<br>& no Sb/Br) | CU NIPDAU            | Level-1-260C-UNLIM           |                             |

<sup>(1)</sup> The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

### PACKAGE OPTION ADDENDUM

16-Aug-2012

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

**Important Information and Disclaimer:** The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

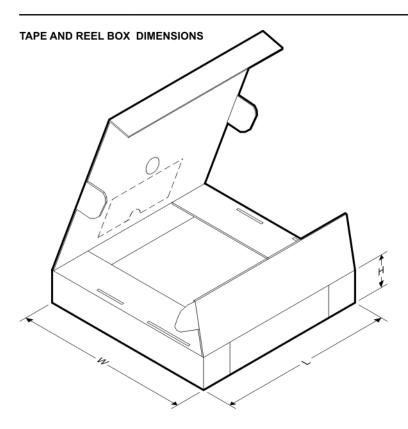

### PACKAGE MATERIALS INFORMATION

www.ti.com 16-Aug-2012

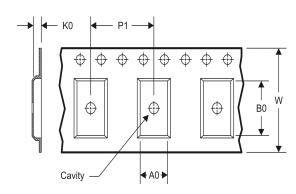

### TAPE AND REEL INFORMATION

### **REEL DIMENSIONS**

### **TAPE DIMENSIONS**

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| В0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

### TAPE AND REEL INFORMATION

\*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| TLC3541IDGKR | VSSOP           | DGK                | 8 | 2500 | 330.0                    | 12.4                     | 5.3        | 3.4        | 1.4        | 8.0        | 12.0      | Q1               |

| TLC3541IDR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

| TLC3545IDR   | SOIC            | D                  | 8 | 2500 | 330.0                    | 12.4                     | 6.4        | 5.2        | 2.1        | 8.0        | 12.0      | Q1               |

www.ti.com 16-Aug-2012

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TLC3541IDGKR | VSSOP        | DGK             | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| TLC3541IDR   | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

| TLC3545IDR   | SOIC         | D               | 8    | 2500 | 367.0       | 367.0      | 35.0        |

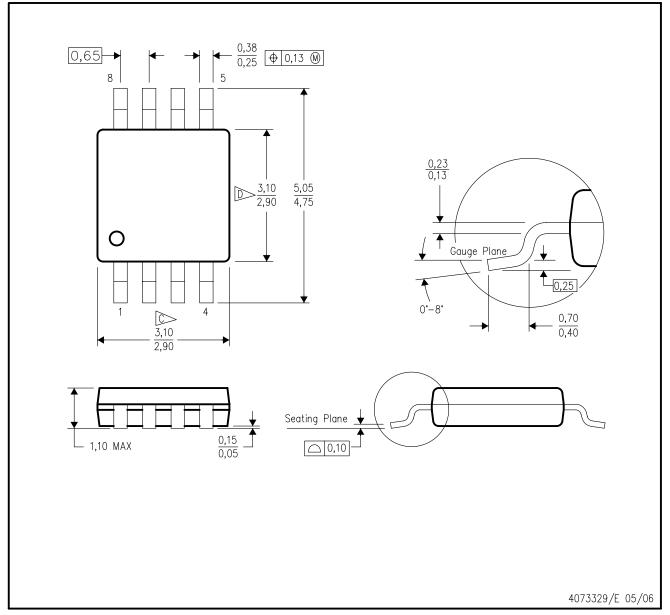

# DGK (S-PDSO-G8)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.15 per end.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.50 per side.

- E. Falls within JEDEC MO-187 variation AA, except interlead flash.

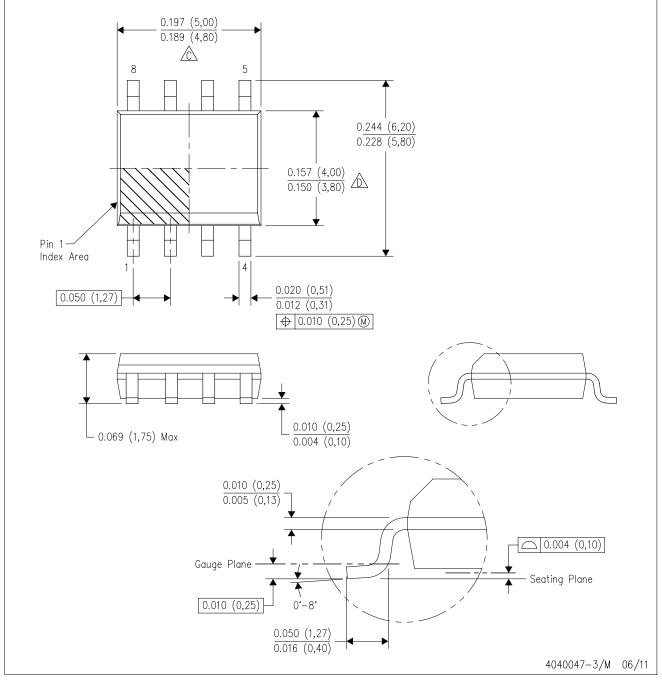

### D (R-PDSO-G8)

### PLASTIC SMALL OUTLINE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Body length does not include mold flash, protrusions, or gate burrs. Mold flash, protrusions, or gate burrs shall not exceed 0.006 (0,15) each side.

- Body width does not include interlead flash. Interlead flash shall not exceed 0.017 (0,43) each side.

- E. Reference JEDEC MS-012 variation AA.

### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46C and to discontinue any product or service per JESD48B. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components which meet ISO/TS16949 requirements, mainly for automotive use. Components which have not been so designated are neither designed nor intended for automotive use; and TI will not be responsible for any failure of such components to meet such requirements.

| roducts |                    | Applications  |

|---------|--------------------|---------------|

| udia    | ununu ti oom/oudio | Automotive on |

Audio Automotive and Transportation www.ti.com/automotive www.ti.com/audio www.ti.com/communications **Amplifiers** amplifier.ti.com Communications and Telecom **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** Consumer Electronics www.ti.com/consumer-apps www.dlp.com DSP dsp.ti.com **Energy and Lighting** www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical Logic logic.ti.com Security www.ti.com/security

Power Mgmt power.ti.com Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

OMAP Mobile Processors www.ti.com/omap TI E2E Community e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity

www.ti-rfid.com

Pr

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.