OGY High Voltage 1.5A, 200kHz Step-Down Switching Regulator with 100µA Quiescent Current

### **FEATURES**

- Wide Input Range: 3.3V to 60V

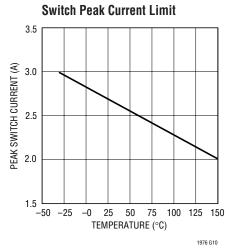

- 1.5A Peak Switch Current (LT1976)

- 100µA Quiescent Current (LT1976)\*\*

- 1.6mA Quiescent Current (LT1976B)

- Low Shutdown Current:  $I_0 < 1 \mu A$

- Power Good Flag with Programmable Threshold

- Load Dump Protection to 60V

- 200kHz Switching Frequency

- Saturating Switch Design: 0.2Ω On-Resistance

- Peak Switch Current Maintained Over Full Duty Cycle Range\*

- 1.25V Feedback Reference Voltage

- Easily Synchronizable

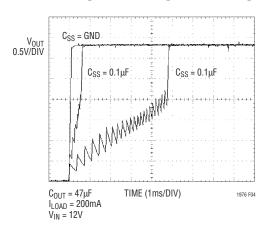

- Soft-Start Capability

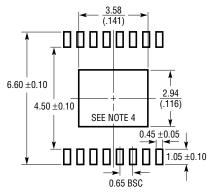

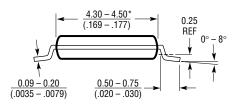

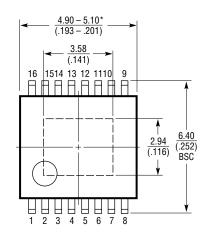

- Small 16-Pin Thermally Enhanced TSSOP Package

### **APPLICATIONS**

- High Voltage Power Conversion

- 14V and 42V Automotive Systems

- Industrial Power Systems

- Distributed Power Systems

- Battery-Powered Systems

(T, LT, LTC and LTM are registered trademarks of Linear Technology Corporation. Burst Mode is a registered trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

### DESCRIPTION

The LT®1976/LT1976B are 200kHz monolithic step-down switching regulators that accept input voltages up to 60V. A high efficiency 1.5A,  $0.2\Omega$  switch is included on the die along with all the necessary oscillator, control and logic circuitry. Current mode topology is used for fast transient response and good loop stability.

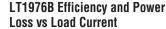

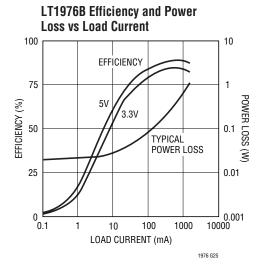

Innovative design techniques along with a new high voltage process achieve high efficiency over a wide input range. Efficiency is maintained over a wide output current range by employing Burst Mode operation at low currents, utilizing the output to bias the internal circuitry, and by using a supply boost capacitor to fully saturate the power switch. The LT1976B does not shift into Burst Mode operation at low currents, eliminating low frequency output ripple at the expense of efficiency. Patented circuitry maintains peak switch current over the full duty cycle range.\* Shutdown reduces input supply current to less than 1µA. External synchronization can be implemented by driving the SYNC pin with logic-level inputs. A single capacitor from the  $C_{SS}$  pin to the output provides a controlled output voltage ramp (soft-start). The devices also have a power good flag with a programmable threshold and time-out and thermal shutdown protection.

The LT1976/LT1976B are available in a 16-pin TSSOP package with Exposed Pad leadframe for low thermal resistance.

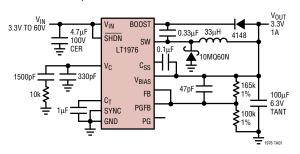

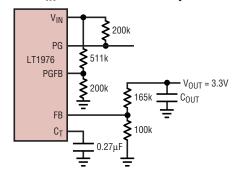

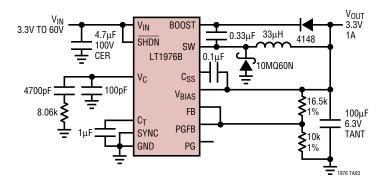

### TYPICAL APPLICATION

14V to 3.3V Step-Down Converter with 100µA No Load Quiescent Current

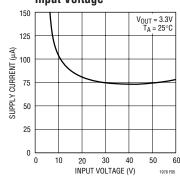

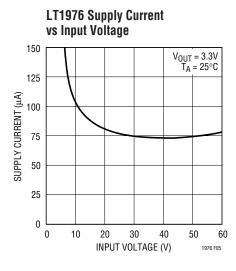

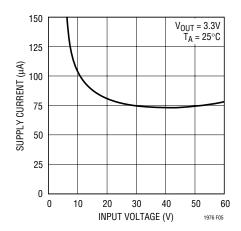

#### LT1976 Supply Current vs Input Voltage

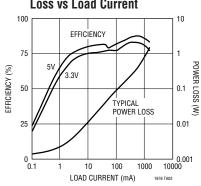

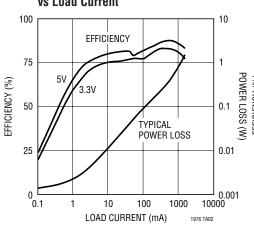

# LT1976 Efficiency and Power Loss vs Load Current

1976bfg

<sup>\*</sup>Protected by U.S. Patents, including 6498466

<sup>\*\*</sup>See Burst Mode Operation section for conditions

### **ABSOLUTE MAXIMUM RATINGS**

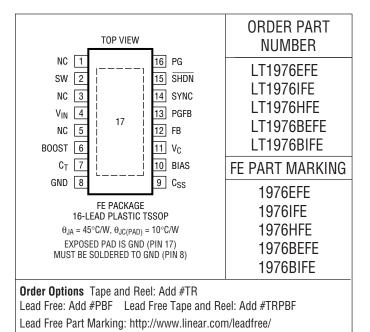

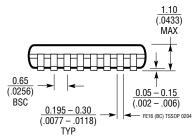

### PACKAGE/ORDER INFORMATION

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full  $-40^{\circ}\text{C}$  to  $125^{\circ}\text{C}$  operating temperature range, otherwise specifications are at  $T_J = 25^{\circ}\text{C}$ .  $V_{IN} = 12\text{V}$ ,  $\overline{\text{SHDN}} = 12\text{V}$ , BOOST = 15.3V, BIAS = 5V, FB/PGFB = 1.25V,  $C_{SS}/SYNC = 0\text{V}$  unless otherwise noted.

| SYMBOL             | PARAMETER                                    | CONDITIONS                                                                                                             |   | MIN   | TYP        | MAX          | UNITS    |

|--------------------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---|-------|------------|--------------|----------|

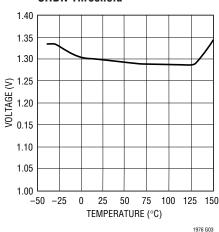

| V <sub>SHDN</sub>  | SHDN Threshold                               |                                                                                                                        | • | 1.2   | 1.3        | 1.4          | V        |

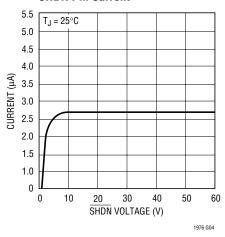

| I <sub>SHDN</sub>  | SHDN Input Current                           | SHDN = 12V                                                                                                             | • |       | 5          | 20           | μΑ       |

|                    | Minimum Input Voltage (Note 3)               |                                                                                                                        | • |       | 2.4        | 3            | V        |

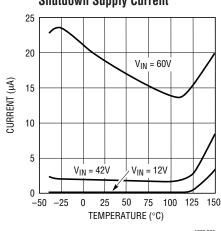

| I <sub>VINS</sub>  | Supply Shutdown Current                      | SHDN = 0V, BOOST = 0V, FB/PGFB = 0V                                                                                    |   |       | 0.1        | 2            | μΑ       |

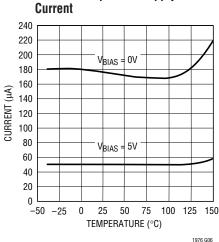

|                    | Supply Sleep Current (Note 4) (LT1976)       | BIAS = 0V, FB = 1.35V<br>FB = 1.35V                                                                                    | • |       | 170<br>45  | 230<br>75    | μΑ<br>μΑ |

| I <sub>VIN</sub>   | Supply Quiescent Current                     | BIAS = 0V, FB = 1.15V, $V_C$ = 0.8V ( $V_C$ = 0V LT1976B)<br>BIAS = 5V, FB = 1.15V, $V_C$ = 0.8V ( $V_C$ = 0V LT1976B) |   |       | 3.2<br>2.6 | 4.10<br>3.25 | mA<br>mA |

|                    | Minimum BIAS Voltage (Note 5)                |                                                                                                                        | • |       | 2.7        | 3            | V        |

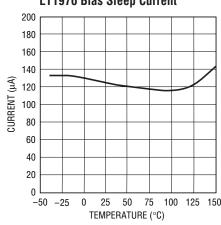

| I <sub>BIASS</sub> | BIAS Sleep Current (Note 4) (LT1976)         |                                                                                                                        | • |       | 110        | 180          | μΑ       |

| I <sub>BIAS</sub>  | BIAS Quiescent Current                       | SYNC = 3.3V                                                                                                            |   |       | 700        | 800          | μА       |

|                    | Minimum Boost Voltage (Note 6)               | I <sub>SW</sub> = 1.5A                                                                                                 |   |       | 1.8        | 2.5          | V        |

|                    | Input Boost Current (Note 7)                 | I <sub>SW</sub> = 1.5A                                                                                                 |   |       | 40         | 50           | mA       |

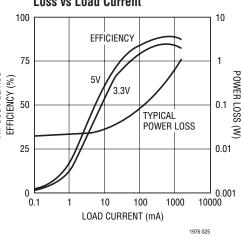

| $V_{REF}$          | Reference Voltage (V <sub>REF</sub> )        | 3.3V < V <sub>VIN</sub> < 60V                                                                                          | • | 1.225 | 1.25       | 1.275        | V        |

| I <sub>FB</sub>    | FB Input Bias Current                        |                                                                                                                        |   |       | 75         | 200          | nA       |

|                    | EA Voltage Gain (Note 8)                     |                                                                                                                        |   |       | 900        |              | V/V      |

|                    | EA Voltage g <sub>m</sub>                    | $dI(V_C) = \pm 10\mu A$                                                                                                |   | 400   | 650        | 800          | μMho     |

|                    | EA Source Current                            | FB = 1.15V                                                                                                             |   | 20    | 40         | 55           | μА       |

|                    | EA Sink Current                              | FB = 1.35V                                                                                                             |   | 15    | 30         | 40           | μΑ       |

|                    | V <sub>C</sub> to SW g <sub>m</sub>          |                                                                                                                        |   |       | 3          |              | A/V      |

|                    | V <sub>C</sub> High Clamp                    |                                                                                                                        |   | 2.1   | 2.2        | 2.4          | V        |

|                    | V <sub>C</sub> Switching Threshold (LT1976B) |                                                                                                                        | • | 0.1   | 0.4        | 0.8          | V        |

1976bfg

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the full  $-40^{\circ}$ C to  $125^{\circ}$ C operating temperature range, otherwise specifications are at  $T_J = 25^{\circ}$ C.  $V_{IN} = 12V$ ,  $\overline{SHDN} = 12V$ , BOOST = 15.3V, BIAS = 5V, FB/PGFB = 1.25V,  $C_{SS}/SYNC = 0V$  unless otherwise noted.

| SYMBOL            | PARAMETER                                   | CONDITIONS            |   | MIN        | TYP        | MAX      | UNITS  |

|-------------------|---------------------------------------------|-----------------------|---|------------|------------|----------|--------|

| I <sub>PK</sub>   | SW Current Limit                            | LT1976<br>LT1976B     | • | 1.5<br>1.2 | 2.4<br>2.5 | 3.5<br>4 | A<br>A |

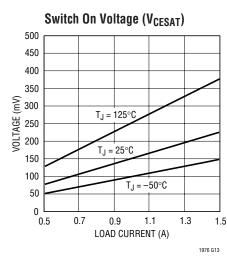

|                   | Switch On Resistance (Note 9)               |                       | • |            | 0.2        | 0.4      | Ω      |

|                   | Switching Frequency                         | BOOST = OPEN          | • | 180        | 200        | 230      | kHz    |

|                   | Maximum Duty Cycle                          |                       |   | 90         | 92         |          | %      |

|                   | Minimum SYNC Amplitude                      |                       |   |            | 1.5        | 2.0      | V      |

|                   | SYNC Frequency Range                        |                       |   | 230        | 600        |          | kHz    |

|                   | SYNC Input Impedance                        | SYNC = 0.5V           |   |            | 100        |          | kΩ     |

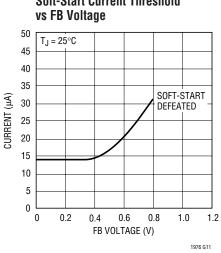

| I <sub>CSS</sub>  | C <sub>SS</sub> Current Threshold (Note 10) | FB = 0V               |   | 7          | 13         | 20       | μΑ     |

| I <sub>PGFB</sub> | PGFB Input Current                          |                       |   |            | 25         | 100      | nA     |

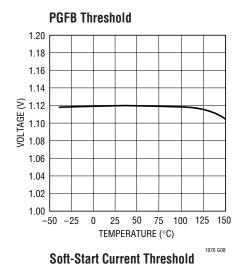

| $V_{PGFB}$        | PGFB Voltage Threshold (Note 11)            |                       | • | 88         | 90         | 92       | %      |

| I <sub>CT</sub>   | C <sub>T</sub> Source Current (Note 11)     |                       | • | 2          | 3.6        | 5.5      | μΑ     |

|                   | C <sub>T</sub> Sink Current (Note 11)       |                       |   | 1          | 2          |          | mA     |

| V <sub>CT</sub>   | C <sub>T</sub> Voltage Threshold (Note 11)  |                       |   | 1.16       | 1.2        | 1.26     | V      |

|                   | PG Leakage (Note 11)                        | PG = 12V              |   |            | 0.1        | 1        | μΑ     |

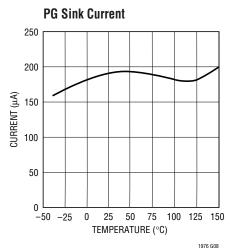

|                   | PG Sink Current (Note 11)                   | PGFB = 1V, PG = 400mV |   | 120        | 200        |          | μΑ     |

The ullet denotes the specifications which apply over the full  $-40^{\circ}$ C to  $140^{\circ}$ C operating temperature range, otherwise specifications are at  $T_J = 25^{\circ}$ C.  $V_{IN} = 12V$ , SHDN = 12V, BOOST = 15.3V, BIAS = 5V, FB/PGFB = 1.25V,  $C_{SS}/SYNC = 0V$  unless otherwise noted.

| SYMBOL             | PARAMETER                              | CONDITIONS                                                                                   |   | MIN   | TYP        | MAX          | UNITS    |

|--------------------|----------------------------------------|----------------------------------------------------------------------------------------------|---|-------|------------|--------------|----------|

| V <sub>SHDN</sub>  | SHDN Threshold                         |                                                                                              | • | 1.2   | 1.3        | 1.4          | V        |

| I <sub>SHDN</sub>  | SHDN Input Current                     | SHDN = 12V                                                                                   | • |       | 5          | 20           | μΑ       |

|                    | Minimum Input Voltage (Note 3)         |                                                                                              | • |       | 2.4        | 3            | V        |

| I <sub>VINS</sub>  | Supply Shutdown Current                | SHDN = 0V, BOOST = 0V, FB/PGFB = 0V                                                          |   |       | 0.1        | 2            | μΑ       |

|                    | Supply Sleep Current (Note 4) (LT1976) | BIAS = 0V, FB = 1.35V<br>FB = 1.35V                                                          | • |       | 170<br>45  | 300<br>100   | μA<br>μA |

| I <sub>VIN</sub>   | Supply Quiescent Current               | BIAS = 0V, FB = 1.15V, V <sub>C</sub> = 0.8V<br>BIAS = 5V, FB = 1.15V, V <sub>C</sub> = 0.8V |   |       | 3.2<br>2.6 | 4.10<br>3.25 | mA<br>mA |

|                    | Minimum BIAS Voltage (Note 5)          |                                                                                              | • |       | 2.7        | 3            | V        |

| I <sub>BIASS</sub> | BIAS Sleep Current (Note 4)            |                                                                                              | • |       | 110        | 180          | μΑ       |

| I <sub>BIAS</sub>  | BIAS Quiescent Current                 | SYNC = 3.3V                                                                                  |   |       | 700        | 800          | μΑ       |

|                    | Minimum Boost Voltage (Note 6)         | I <sub>SW</sub> = 1.5A                                                                       |   |       | 1.8        | 2.5          | V        |

|                    | Input Boost Current (Note 7)           | I <sub>SW</sub> = 1.5A                                                                       |   |       | 40         | 50           | mA       |

| $V_{REF}$          | Reference Voltage (V <sub>REF</sub> )  | 3.3V < V <sub>VIN</sub> < 60V                                                                | • | 1.212 | 1.25       | 1.288        | V        |

| I <sub>FB</sub>    | FB Input Bias Current                  |                                                                                              |   |       | 75         | 200          | nA       |

|                    | EA Voltage Gain (Note 8)               |                                                                                              |   |       | 900        |              | V/V      |

|                    | EA Voltage g <sub>m</sub>              | $dI(V_C) = \pm 10\mu A$                                                                      |   | 400   | 650        | 800          | μMho     |

|                    | EA Source Current                      | FB = 1.15V                                                                                   |   | 20    | 40         | 55           | μΑ       |

|                    | EA Sink Current                        | FB = 1.35V                                                                                   |   | 15    | 30         | 40           | μΑ       |

|                    | V <sub>C</sub> to SW g <sub>m</sub>    |                                                                                              |   |       | 3          |              | A/V      |

|                    | V <sub>C</sub> High Clamp              |                                                                                              |   | 2.1   | 2.2        | 2.4          | V        |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full  $-40^{\circ}$ C to  $140^{\circ}$ C operating temperature range, otherwise specifications are at  $T_J = 25^{\circ}$ C.  $V_{IN} = 12V$ , SHDN = 12V, BOOST = 15.3V, BIAS = 5V, FB/PGFB = 1.25V,  $C_{SS}/SYNC$  = 0V unless otherwise noted.

| SYMBOL            | PARAMETER                                   | CONDITIONS            |   | MIN  | TYP | MAX  | UNITS |

|-------------------|---------------------------------------------|-----------------------|---|------|-----|------|-------|

| I <sub>PK</sub>   | SW Current Limit                            |                       |   |      | 2.4 |      | A     |

|                   | Switch On Resistance (Note 9)               |                       | • |      | 0.2 | 0.6  | Ω     |

|                   | Switching Frequency                         | BOOST = OPEN          | • | 150  | 200 | 260  | kHz   |

|                   | Maximum Duty Cycle                          |                       |   | 90   | 92  |      | %     |

|                   | Minimum SYNC Amplitude                      |                       |   |      | 1.5 | 2.0  | V     |

|                   | SYNC Frequency Range                        |                       |   | 230  | 600 |      | kHz   |

|                   | SYNC Input Impedance                        | SYNC = 0.5V           |   |      | 85  |      | kΩ    |

| I <sub>CSS</sub>  | C <sub>SS</sub> Current Threshold (Note 10) |                       |   | 7    | 13  | 20   | μΑ    |

| I <sub>PGFB</sub> | PGFB Input Current                          |                       |   |      | 25  | 100  | nA    |

| V <sub>PGFB</sub> | PGFB Voltage Threshold (Note 11)            |                       | • | 87   | 90  | 93   | %     |

| I <sub>CT</sub>   | C <sub>T</sub> Source Current (Note 11)     |                       | • | 1.5  | 3.6 | 5.5  | μΑ    |

|                   | C <sub>T</sub> Sink Current (Note 11)       |                       |   | 1    | 2   |      | mA    |

| V <sub>CT</sub>   | C <sub>T</sub> Voltage Threshold (Note 11)  |                       |   | 1.16 | 1.2 | 1.26 | V     |

|                   | PG Leakage (Note 11)                        | PG = 12V              |   |      | 0.1 | 1    | μА    |

|                   | PG Sink Current (Note 11)                   | PGFB = 1V, PG = 400mV |   | 120  | 200 |      | μΑ    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LT1976EFE/LT1976BEFE are guaranteed to meet performance specifications from 0°C to 125°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LT1976IFE/LT1976BIFE/LT1976HFE are guaranteed and tested over the full -40°C to 125°C operating junction temperature range. The LT1976HFE is also tested to the LT1976HFE electrical characteristics table at 140°C operating junction temperature. High junction temperatures degrade operating lifetimes.

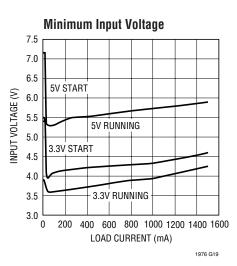

**Note 3:** Minimum input voltage is defined as the voltage where switching starts. Actual minimum input voltage to maintain a regulated output will depend upon output voltage and load current. See Applications Information.

**Note 4:** Supply input current is the quiescent current drawn by the input pin. Its typical value depends on the voltage on the BIAS pin and operating state of the LT1976. With the BIAS pin at 0V, all of the quiescent current required to operate the LT1976 will be provided by the  $V_{\rm IN}$  pin. With the BIAS voltage above its minimum input voltage, a portion of the total quiescent current will be supplied by the BIAS pin. Supply sleep current for the LT1976 is defined as the quiescent current during the "sleep" portion of Burst Mode operation. See Applications Information for determining application supply currents.

**Note 5:** Minimum BIAS voltage is the voltage on the BIAS pin when  $I_{\text{BIAS}}$  is sourced into the pin.

**Note 6:** This is the minimum voltage across the boost capacitor needed to guarantee full saturation of the internal power switch.

**Note 7:** Boost current is the current flowing into the BOOST pin with the pin held 3.3V above input voltage. It flows only during switch on time.

**Note 8:** Gain is measured with a  $V_C$  swing from 1.15V to 750mV.

**Note 9:** Switch on resistance is calculated by dividing  $V_{\text{IN}}$  to SW voltage by the forced current (1.5A LT1976, 1.2A LT1976B). See Typical Performance Characteristics for the graph of switch voltage at other currents.

**Note 10:** The  $C_{SS}$  threshold is defined as the value of current sourced into the  $C_{SS}$  pin which results in an increase in sink current from the  $V_{C}$  pin. See the Soft-Start section in Applications Information.

**Note 11:** The PGFB threshold is defined as the percentage of  $V_{REF}$  voltage which causes the current source output of the  $C_T$  pin to change from sinking (below threshold) to sourcing current (above threshold). When sourcing current, the voltage on the  $C_T$  pin rises until it is clamped internally. When the clamp is activated, the output of the PG pin will be set to a high impedance state. When the  $C_T$  clamp is inactive the PG pin will be set active low with a current sink capability of  $200\mu A$ .

# LT1976 Efficiency and Power Loss vs Load Current

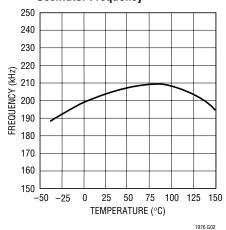

**Oscillator Frequency**

SHDN Threshold

SHDN Pin Current

**Shutdown Supply Current**

LT1976 Sleep Mode Supply

LT1976 Bias Sleep Current

1976bfg

1976 G07

1976bfg

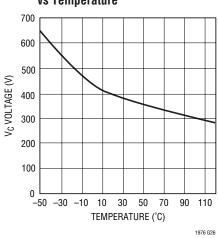

# LT1976B V<sub>C</sub> Switching Threshold vs Temperature

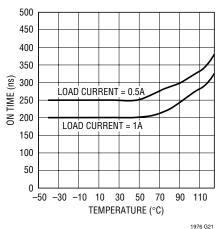

#### Minimum On Time

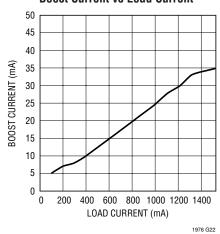

**Boost Current vs Load Current**

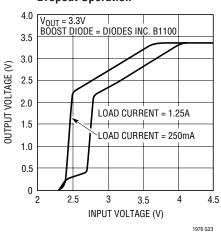

#### **Dropout Operation**

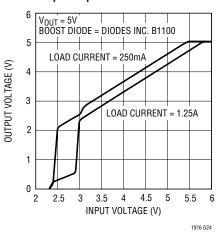

#### **Dropout Operation**

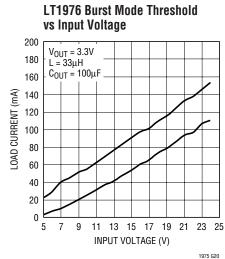

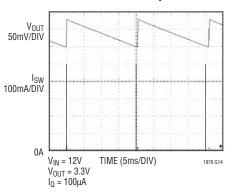

#### LT1976 Burst Mode Operation

#### LT1976 Burst Mode Operation

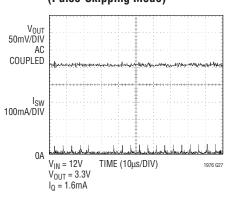

LT1976B No Load Operation (Pulse-Skipping Mode)

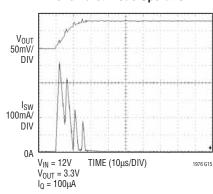

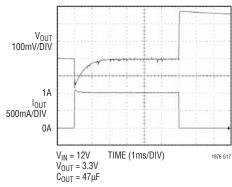

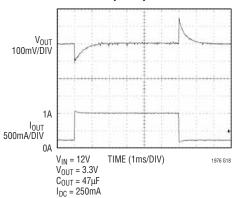

#### LT1976 No Load 1A Step Response

### PIN FUNCTIONS

**NC** (**Pins 1, 3, 5**): No Connection. Pins 1, 3, 5 are electrically isolated from the LT1976. They may be connected to PCB traces to aid in PCB layout.

**SW** (**Pin 2**): The SW pin is the emitter of the on-chip power NPN switch. This pin is driven up to the input pin voltage during switch on time. Inductor current drives the SW pin negative during switch off time. Negative voltage is clamped with the external Schottky catch diode to prevent excessive negative voltages.

$V_{IN}$  (Pin 4): This is the collector of the on-chip power NPN switch.  $V_{IN}$  powers the internal control circuitry when a voltage on the BIAS pin is not present. High di/dt edges occur on this pin during switch turn on and off. Keep the path short from the  $V_{IN}$  pin through the input bypass capacitor, through the catch diode back to SW. All trace inductance on this path will create a voltage spike at switch off, adding to the  $V_{CF}$  voltage across the internal NPN.

**BOOST (Pin 6):** The BOOST pin is used to provide a drive voltage, higher than the input voltage, to the internal bipolar NPN power switch. Without this added voltage, the typical switch voltage loss would be about 1.5V. The additional BOOST voltage allows the switch to saturate and its voltage loss approximates that of a  $0.2\Omega$  FET structure, but with much smaller die area.

$C_T$  (Pin 7): A capacitor on the  $C_T$  pin determines the amount of delay time between the PGFB pin exceeding its threshold ( $V_{PGFB}$ ) and the PG pin set to a high impedance state. When the PGFB pin rises above  $V_{PGFB}$ , current is sourced from the  $C_T$  pin into the external capacitor. When the voltage on the external capacitor reaches an internal clamp ( $V_{CT}$ ), the PG pin becomes a high impedance node. The resultant PG delay time is given by  $t = C_{CT} \cdot V_{CT}/I_{CT}$ . If the voltage on the PGFB pin drops below  $V_{PGFB}$ ,  $C_{CT}$  will be discharged rapidly to 0V and PG will be active low with a  $200\mu A \sin k$  capability. If the  $C_T$  pin is clamped (Power Good condition) during normal operation and SHDN is taken low, the  $C_T$  pin will be discharged and a delay period will occur when SHDN is returned high. See the Power Good section in Applications Information for details.

**GND** (**Pins 8, 17**): The GND pin connection acts as the reference for the regulated output, so load regulation will suffer if the "ground" end of the load is not at the same voltage as the GND pin of the IC. This condition will occur when load current or other currents flow through metal paths between the GND pin and the load ground. Keep the path between the GND pin and the load ground short and use a ground plane when possible. The GND pin also acts as a heat sink and should be soldered (along with the exposed leadframe) to the copper ground plane to reduce thermal resistance (see Applications Information).

LINEAR

### PIN FUNCTIONS

$C_{SS}$  (Pin 9): A capacitor from the  $C_{SS}$  pin to the regulated output voltage determines the output voltage ramp rate during start-up. When the current through the  $C_{SS}$  capacitor exceeds the  $C_{SS}$  threshold ( $I_{CSS}$ ), the voltage ramp of the output is limited. The  $C_{SS}$  threshold is proportional to the FB voltage (see Typical Performance Characteristics) and is defeated for FB voltage greater than 0.9V (typical). See Soft-Start section in Applications Information for details.

**BIAS (Pin 10):** The BIAS pin is used to improve efficiency when operating at higher input voltages and light load current. Connecting this pin to the regulated output voltage forces most of the internal circuitry to draw its operating current from the output voltage rather than the input supply. This architecture increases efficiency especially when the input voltage is much higher than the output. Minimum output voltage setting for this mode of operation is 3V.

$\textbf{V}_{\textbf{C}}$  (**Pin 11**): The  $V_{\textbf{C}}$  pin is the output of the error amplifier and the input of the peak switch current comparator. It is normally used for frequency compensation, but can also serve as a current clamp or control loop override. The  $V_{\textbf{C}}$  pin sits about 0.45V for light loads and 2.2V at current limit. The LT1976 clamps the  $V_{\textbf{C}}$  pin slightly below the burst threshold during sleep periods for better transient response. Driving the  $V_{\textbf{C}}$  pin to ground will disable switching and also place the LT1976 into sleep mode.

**FB** (**Pin 12**): The feedback pin is used to determine the output voltage using an external voltage divider from the output that generates 1.25V at the FB pin . When the FB pin drops below 0.9V, switching frequency is reduced, the SYNC function is disabled and output ramp rate control is enabled via the  $C_{SS}$  pin. See the Feedback section in Applications Information for details.

**PGFB (PIN 13):** The PGFB pin is the positive input to a comparator whose negative input is set at  $V_{PGFB}$ . When PGFB is taken above  $V_{PGFB}$ , current ( $I_{CSS}$ ) is sourced into the  $C_T$  pin starting the PG delay period. When the voltage on the PGFB pin drops below  $V_{PGFB}$ , the  $C_T$  pin is rapidly discharged resetting the PG delay period. The PGFB voltage is typically generated by a resistive divider from the regulated output or input supply. See Power Good section in Applications Information for details.

**SYNC (Pin 14):** The SYNC pin is used to synchronize the internal oscillator to an external signal. It is directly logic compatible and can be driven with any signal between 20% and 80% duty cycle. The synchronizing range is equal to maximum initial operating frequency up to 700kHz. When the voltage on the FB pin is below 0.9V the SYNC function is disabled. See the Synchronizing section in Applications Information for details.

SHDN (Pin 15): The  $\overline{SHDN}$  pin is used to turn off the regulator and to reduce input current to less than  $1\mu A$ . The  $\overline{SHDN}$  pin requires a voltage above 1.3V with a typical source current of  $5\mu A$  to take the IC out of the shutdown state.

**PG (Pin 16):** The PG pin is functional only when the SHDN pin is above its threshold, and is active low when the internal clamp on the  $C_T$  pin is below its clamp level and high impedance when the clamp is active. The PG pin has a typical sink capability of  $200\mu A$ . See the Power-Good section in Applications Information for details.

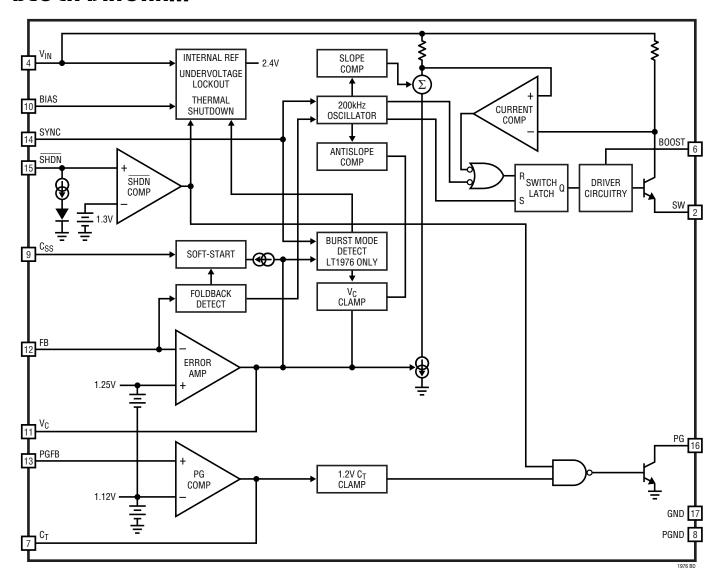

### **BLOCK DIAGRAM**

Figure 1. LT1976/LT1976B Block Diagram

The LT1976 is a constant frequency, current mode buck converter. This means that there is an internal clock and two feedback loops that control the duty cycle of the power switch. In addition to the normal error amplifier, there is a current sense amplifier that monitors switch current on a cycle-by-cycle basis. A switch cycle starts with an oscillator pulse which sets the RS latch to turn the switch on. When switch current reaches a level set by the current comparator the latch is reset and the switch turns off. Output voltage control is obtained by using the output of the error amplifier to set the switch current trip point. This technique means that the error amplifier commands current to be

delivered to the output rather than voltage. A voltage fed system will have low phase shift up to the resonant frequency of the inductor and output capacitor, then an abrupt 180° shift will occur. The current fed system will have 90° phase shift at a much lower frequency, but will not have the additional 90° shift until well beyond the LC resonant frequency. This makes it much easier to frequency compensate the feedback loop and also gives much quicker transient response.

Most of the circuitry of the LT1976 operates from an internal 2.4V bias line. The bias regulator normally draws

LINEAR

### **BLOCK DIAGRAM**

power from the  $V_{\text{IN}}$  pin, but if the BIAS pin is connected to an external voltage higher than 3V bias power will be drawn from the external source (typically the regulated output voltage). This improves efficiency.

High switch efficiency is attained by using the BOOST pin to provide a voltage to the switch driver which is higher than the input voltage, allowing switch to be saturated. This boosted voltage is generated with an external capacitor and diode.

To further optimize efficiency, the LT1976 automatically switches to Burst Mode operation in light load situations.

In Burst Mode operation, all circuitry associated with controlling the output switch is shut down reducing the input supply current to  $45\mu$ A.

The only difference between the LT1976 and the LT1976B is that the LT1976B does not shift into burst mode in light load situations, eliminating low frequency output ripple at the expense of light load efficiency.

The LT1976 contains a power good flag with a programmable threshold and delay time. A logic-level low on the  $\overline{SHDN}$  pin disables the IC and reduces input suppy current to less than 1 $\mu$ A.

### APPLICATIONS INFORMATION

#### CHOOSING THE LT1976 OR LT1977

The LT1976/LT1976B and LT1977 are high voltage 1.5A step-down switching regulators. The LT1976 and LT1977 contain circuitry which shifts into burst mode at light loads reducing quiescent current to typically  $100\mu A$ . The LT1976B pulse skips in light load situations, eliminating low frequency burst mode output ripple at the expense of light load efficiency. The difference between the LT1976/LT1976B and LT1977 is that the fixed switching frequency of the LT1976/LT1976B is 200kHz versus 500kHz for the LT1977. The switching frequency affects: inductor size, input voltage range in continuous mode operation, efficiency, thermal loss and EMI.

#### **OUTPUT RIPPLE AND INDUCTOR SIZE**

Output ripple current is determined by the input to output voltage ratio, inductor value and switch frequency. Since the switch frequency of the LT1977 is 2.5 times greater than that of the LT1976/LT1976B, the inductance used in the LT1977 application can be 2.5 times lower than the LT1976/LT1976B while maintaining the same output ripple current. The lower value used in the LT1977 application allows the use of a physically smaller inductor.

#### **INPUT VOLTAGE RANGE**

The minimum on and off times for all versions of the ic are equivalent. This results in a narrower range of continuous mode operation for the LT1977. Typical minimum and maximum duty cycles are 6% to 92% for the LT1976/LT1976B and 15% to 90% for the LT1977. Both parts will regulate up to an input voltage of 60V but the LT1977 will transistion into pulse-skipping/Burst Mode operation when the input voltage is above 30V for a 5V output. At outputs above 10V the LT1977's input range will be similar to the LT1976/LT1976B. Lowering the input voltage below the maximum duty cycle limitation will cause a dropout in regulation.

Table 1. LT1976/LT1976B/LT1977 Comparison

| · · · · · · · · · · · · · · · · · · · | •              |

|---------------------------------------|----------------|

| PARAMETER                             | ADVANTAGE      |

| Minimum Duty Cycle                    | LT1976/LT1976B |

| Maximum Duty Cycle                    | LT1976/LT1976B |

| Inductor Size                         | LT1977         |

| Output Capacitor Size                 | LT1977         |

| Efficiency                            | LT1976         |

| EMI                                   | LT1976B        |

| Input Range                           | LT1976/LT1976B |

| Output Ripple                         | LT1977         |

| Light Load Output Ripple              | LT1976B        |

|                                       |                |

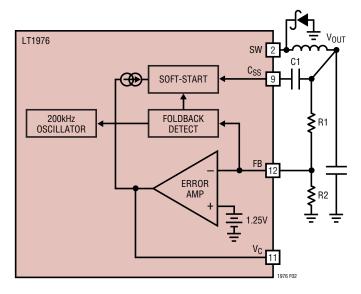

#### FEEDBACK PIN FUNCTIONS

The feedback (FB) pin on the LT1976 is used to set output voltage and provide several overload protection features. The first part of this section deals with selecting resistors to set output voltage and the remaining part talks about frequency foldback and soft-start features. Please read both parts before committing to a final design.

Referring to Figure 2, the output voltage is determined by a voltage divider from  $V_{OUT}$  to ground which generates 1.25V at the FB pin. Since the output divider is a load on the output care must be taken when choosing the resistor divider values. For light load applications the resistor values should be as large as possible to achieve peak efficiency in Burst Mode operation. Extremely large values for resistor R1 will cause an output voltage error due to the 50nA FB pin input current. The suggested value for the output divider resistor (see Figure 2) from FB to ground (R2) is 100k or less. A formula for R1 is shown below. A table of standard 1% values is shown in Table 2 for common output voltages.

$$R1 = R2 \cdot \frac{V_{OUT} - 1.25}{1.25 + R2 \cdot 50 \text{ nA}}$$

For LT1976B aplications, the suggested value for R2 is 10k or less, eliminating output voltage errors due to feedback pin current and reducing noise susceptibility.

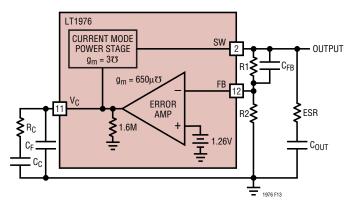

Figure 2. Feedback Network

#### More Than Just Voltage Feedback

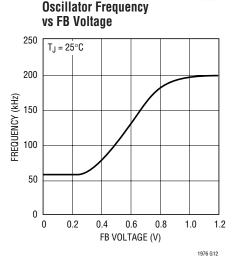

The FB pin is used for more than just output voltage sensing. It also reduces switching frequency and controls the soft-start voltage ramp rate when output voltage is below the regulated level (see the Frequency Foldback and Soft-Start Current graphs in Typical Performance Characteristics).

Frequency foldback is done to control power dissipation in both the IC and in the external diode and inductor during short-circuit conditions. A shorted output requires the switching regulator to operate at very low duty cycles. As a result the average current through the diode and inductor is equal to the short-circuit current limit of the switch (typically 2.4A for the LT1976). Minimum switch on time limitations would prevent the switcher from attaining a sufficiently low duty cycle if switching frequency were maintained at 200kHz, so frequency is reduced by about 4:1 when the FB pin voltage drops below 0.4V (see Frequency Foldback graph). In addition, if the current in the switch exceeds 1.5 times the current limitations specified by the V<sub>C</sub> pin, due to minimum switch on time, the LT1976 will skip the next switch cycle. As the feedback voltage rises, the switching frequency increases to 200kHz with 0.95V on the FB pin. During frequency foldback, external syncronization is disabled to prevent interference with foldback operation. Frequency foldback does not affect operation during normal load conditions.

In addition to lowering switching frequency the soft-start ramp rate is also affected by the feedback voltage. Large

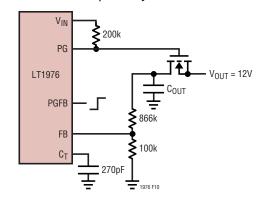

Table 2

| OUTPUT<br>VOLTAGE<br>(V) | R2<br>(kΩ, 1%) | R1<br>NEAREST (1%)<br>(kΩ) | OUTPUT<br>ERROR<br>(%) |

|--------------------------|----------------|----------------------------|------------------------|

| 2.5                      | 100            | 100                        | 0                      |

| 3                        | 100            | 140                        | 0                      |

| 3.3                      | 100            | 165                        | 0.38                   |

| 5                        | 100            | 300                        | 0                      |

| 6                        | 100            | 383                        | 0.63                   |

| 8                        | 100            | 536                        | -0.63                  |

| 10                       | 100            | 698                        | -0.25                  |

| 12                       | 100            | 866                        | 0.63                   |

TECHNOLOGY TECHNOLOGY

capacitive loads or high input voltages can cause a high input current surge during start-up. The soft-start function reduces input current surge by regulating switch current via the V<sub>C</sub> pin to maintain a constant voltage ramp rate (dV/dt) at the output. A capacitor (C1 in Figure 2) from the  $C_{SS}$  pin to the output determines the maximum output dV/dt. When the feedback voltage is below 0.4V, the  $V_C$  pin will rise, resulting in an increase in switch current and output voltage. If the dV/dt of the output causes the current through the  $C_{SS}$  capacitor to exceed  $I_{CSS}$  the  $V_C$  voltage is reduced resulting in a constant dV/dt at the output. As the feedback voltage increases l<sub>CSS</sub> increases, resulting in an increased dV/dt until the soft-start function is defeated with 0.9V present at the FB pin. The soft-start function does not affect operation during normal load conditions. However, if a momentary short (brown out condition) is present at the output which causes the FB voltage to drop below 0.9V, the soft-start circuitry will become active.

#### INPUT CAPACITOR

Step-down regulators draw current from the input supply in pulses. The rise and fall times of these pulses are very fast. The input capacitor is required to reduce the voltage ripple this causes at the input of LT1976 and force the switching current into a tight local loop, thereby minimizing EMI. The RMS ripple current can be calculated from:

$$I_{RIPPLE(RMS)} = \frac{I_{OUT}}{V_{IN}} \sqrt{V_{OUT}(V_{IN} - V_{OUT})}$$

Ceramic capacitors are ideal for input bypassing. At 200kHz switching frequency input capacitor values in the range of  $4.7\mu F$  to  $20\mu F$  are suitable for most applications. If operation is required close to the minimum input required by the LT1976 a larger value may be required. This is to prevent excessive ripple causing dips below the minimum operating voltage resulting in erratic operation.

Input voltage transients caused by input voltage steps or by hot plugging the LT1976 to a pre-powered source such as a wall adapter can exceed maximum  $V_{\text{IN}}$  ratings. The sudden application of input voltage will cause a large surge of current in the input leads that will store energy in

the parasitic inductance of the leads. This energy will cause the input voltage to swing above the DC level of input power source and it may exceed the maximum voltage rating of the input capacitor and LT1976. All input voltage transient sequences should be observed at the  $V_{\text{IN}}$  pin of the LT1976 to ensure that absolute maximum voltage ratings are not violated.

The easiest way to suppress input voltage transients is to add a small aluminum electrolytic capacitor in parallel with the low ESR input capacitor. The selected capacitor needs to have the right amount of ESR to critically damp the resonant circuit formed by the input lead inductance and the input capacitor. The typical values of ESR will fall in the range of  $0.5\Omega$  to  $2\Omega$  and capacitance will fall in the range of  $5\mu F$  to  $50\mu F$ .

If tantalum capacitors are used, values in the  $22\mu F$  to  $470\mu F$  range are generally needed to minimize ESR and meet ripple current and surge ratings. Care should be taken to ensure the ripple and surge ratings are not exceeded. The AVX TPS and Kemet T495 series are surge rated AVX recommends derating capacitor operating voltage by 2:1 for high surge applications.

#### **OUTPUT CAPACITOR**

The output capacitor is normally chosen by its effective series resistance (ESR) because this is what determines output ripple voltage. To get low ESR takes volume, so physically smaller capacitors have higher ESR. The ESR range for typical LT1976 applications is  $0.05\Omega$  to  $0.2\Omega$ . A typical output capacitor is an AVX type TPS, 100µF at 10V, with a guaranteed ESR less than  $0.1\Omega$ . This is a "D" size surface mount solid tantalum capacitor. TPS capacitors are specially constructed and tested for low ESR, so they give the lowest ESR for a given volume. The value in microfarads is not particularly critical and values from 22µF to greater than 500µF work well, but you cannot cheat Mother Nature on ESR. If you find a tiny 22µF solid tantalum capacitor, it will have high ESR and output ripple voltage could be unacceptable. Table 3 shows some typical solid tantalum surface mount capacitors.

Table 3. Surface Mount Solid Tantalum Capacitor ESR and Ripple Current

| E CASE SIZE | ESR MAX ( $\Omega$ ) | RIPPLE CURRENT (A) |  |  |

|-------------|----------------------|--------------------|--|--|

| AVX TPS     | 0.1 to 0.3           | 0.7 to 1.1         |  |  |

| D CASE SIZE |                      |                    |  |  |

| AVX TPS     | 0.1 to 0.3           | 0.7 to 1.1         |  |  |

| C CASE SIZE |                      |                    |  |  |

| AVX TPS     | 0.2                  | 0.2 0.5            |  |  |

| AVX IPS U.2 |                      | 0.5                |  |  |

Many engineers have heard that solid tantalum capacitors are prone to failure if they undergo high surge currents. This is historically true and type TPS capacitors are specially tested for surge capability but surge ruggedness is not a critical issue with the output capacitor. Solid tantalum capacitors fail during very high turn-on surges which do not occur at the output of regulators. High discharge surges, such as when the regulator output is dead shorted, do not harm the capacitors.

Unlike the input capacitor RMS, ripple current in the output capacitor is normally low enough that ripple current rating is not an issue. The current waveform is triangular with a typical value of  $200 \text{mA}_{RMS}$ . The formula to calculate this is:

Output capacitor ripple current (RMS)

$$I_{RIPPLE(RMS)} = \frac{0.29 \big(V_{OUT}\big) \big(V_{IN} - V_{OUT}\big)}{\big(L\big) \big(f\big) \big(V_{IN}\big)} = \frac{I_{P-P}}{\sqrt{12}}$$

#### **CERAMIC CAPACITORS**

Higher value, lower cost ceramic capacitors are now becoming available. They are generally chosen for their good high frequency operation, small size and very low ESR (effective series resistance). Low ESR reduces output ripple voltage but also removes a useful zero in the loop frequency response, common to tantalum capacitors. To compensate for this a resistor  $R_{\text{C}}$  can be placed in series with the  $V_{\text{C}}$  compensation capacitor  $C_{\text{C}}$  (Figure 10). Care must be taken however since this resistor sets the high frequency gain of the error amplifier including the gain at the switching frequency. If the gain of the error amplifier is high enough at the switching frequency output ripple voltage (although smaller for a ceramic output capacitor) may still affect the proper operation of the regulator. A

filter capacitor  $C_F$  in parallel with the  $R_C/C_C$  network, along with a small feedforward capacitor  $C_{FB}$ , is suggested to control possible ripple at the  $V_C$  pin. The LT1976 can be stabilized using a  $47\mu F$  ceramic output capacitor and  $V_C$  component values of  $C_C = 0.047\mu F$ ,  $R_C = 12.5k$ ,  $C_F = 100pF$  and  $C_{FB} = 27pF$ .

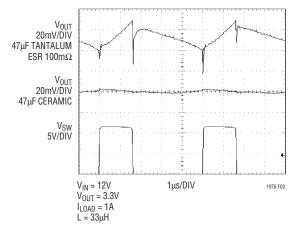

#### **OUTPUT RIPPLE VOLTAGE**

Figure 3 shows a typical output ripple voltage waveform for the LT1976. Ripple voltage is determined by the impedance of the output capacitor and ripple current through the inductor. Peak-to-peak ripple current through the inductor into the output capacitor is:

$$I_{P-P} = \frac{V_{OUT}(V_{IN} - V_{OUT})}{(V_{IN})(L)(f)}$$

For high frequency switchers the ripple current slew rate is also relevant and can be calculated from:

$$\frac{di}{dt} = \frac{V_{IN}}{L}$$

Peak-to-peak output ripple voltage is the sum of a triwave created by peak-to-peak ripple current times ESR and a square wave created by parasitic inductance (ESL) and ripple current slew rate. Capacitive reactance is assumed to be small compared to ESR or ESL.

$$V_{RIPPLE} = (I_{P-P})(ESR) + (ESL)\frac{di}{dt}$$

Figure 3. LT1976 Ripple Voltage Waveform

1976bfg

Example: with  $V_{IN} = 12V$ ,  $V_{OUT} = 3.3V$ ,  $L = 33\mu H$ , ESR = For  $V_{OUT} = 5V$ ,  $V_{IN} = 8V$  and  $L = 20\mu H$ :  $0.08\Omega$ . ESL = 10nH:

$$I_{P-P} = \frac{(3.3)(12-3.3)}{(12)(33e-6)(200e3)} = 0.362A$$

$$\frac{di}{dt} = \frac{12}{3.3e-5} = 3.63e5$$

$$V_{RIPPLE} = (0.362A)(0.08) + (10e - 9)(363e3)$$

= 0.0289 + 0.003 = 32mV<sub>P-P</sub>

#### MAXIMUM OUTPUT LOAD CURRENT

Maximum load current for a buck converter is limited by the maximum switch current rating (IPK). The current rating for the LT1976 is 1.5A. Unlike most current mode converters, the LT1976 maximum switch current limit does not fall off at high duty cycles. Most current mode converters suffer a drop off of peak switch current for duty cycles above 50%. This is due to the effects of slope compensation required to prevent subharmonic oscillations in current mode converters. (For detailed analysis. see Application Note 19.)

The LT1976 is able to maintain peak switch current limit over the full duty cycle range by using patented circuitry to cancel the effects of slope compensation on peak switch current without affecting the frequency compensation it provides.

Maximum load current would be equal to maximum switch current for an infinitely large inductor, but with finite inductor size, maximum load current is reduced by one-half peak-to-peak inductor current. The following formula assumes continuous mode operation, implying that the term on the right  $(I_{P-P}/2)$  is less than  $I_{OUT}$ .

$$I_{OUT(MAX)} = I_{PK} - \frac{(V_{OUT})(V_{IN} - V_{OUT})}{2(L)(f)(V_{IN})} = I_{PK} - \frac{I_{P-P}}{2}$$

Discontinuous operation occurs when:

$$I_{OUT(DIS)} \le \frac{V_{OUT}(V_{IN} - V_{OUT})}{2(L)(f)(V_{IN})}$$

$$I_{OUT(MAX)} = 1.5 - \frac{(5)(8-5)}{2(20e-6)(200e3)(8)}$$

$$= 1.5 - 0.24 = 1.26A$$

Note that there is less load current available at the higher input voltage because inductor ripple current increases. At  $V_{IN}$  = 15V, duty cycle is 33% and for the same set of conditions:

$$I_{OUT(MAX)} = 1.5 - \frac{(5)(15 - 5)}{2(20e - 6)(200e3)(15)}$$

$$= 1.5 - 0.42 = 1.08A$$

To calculate actual peak switch current in continuous mode with a given set of conditions, use:

$$I_{SW(PK)} = I_{OUT} + \frac{V_{OUT}(V_{IN} - V_{OUT})}{2(L)(f)(V_{IN})}$$

If a small inductor is chosen which results in discontinous mode operation over the entire load range, the maximum load current is equal to:

$$I_{OUT(MAX)} = \frac{I_{PK}^2 2(f)(L)(V_{IN})}{2(V_{OUT})(V_{IN} - V_{OUT})}$$

#### CHOOSING THE INDUCTOR

For most applications the output inductor will fall in the range of 15µH to 100µH. Lower values are chosen to reduce physical size of the inductor. Higher values allow more output current because they reduce peak current seen by the LT1976 switch, which has a 1.5A limit. Higher values also reduce output ripple voltage and reduce core

When choosing an inductor you might have to consider maximum load current, core and copper losses, allowable component height, output voltage ripple, EMI, fault current in the inductor, saturation and of course cost. The following procedure is suggested as a way of handling these somewhat complicated and conflicting requirements.

Choose a value in microhenries from the graph of maximum load current. Choosing a small inductor with lighter loads may result in discontinuous mode of operation, but the LT1976 is designed to work well in either mode.

Table 4. Inductor Selection Criteria

| Tubio 4. Illudotoi     | OUIOULIUII UIIL | oriu                 |         |             |

|------------------------|-----------------|----------------------|---------|-------------|

| VENDOR/<br>Part number | VALUE (μH)      | I <sub>RMS</sub> (A) | DCR (Ω) | HEIGHT (mm) |

| Coiltronics            |                 |                      |         |             |

| UP2B-150               | 15              | 2.4                  | 0.041   | 6           |

| UP2B-330               | 33              | 1.7                  | 0.062   | 6           |

| UP2B-470               | 47              | 1.4                  | 0.139   | 6           |

| UP2B-680               | 68              | 1.2                  | 0.179   | 6           |

| UP2B-101               | 100             | 0.95                 | 0.271   | 6           |

| UP3B-150               | 15              | 3.9                  | 0.032   | 6.8         |

| UP3B-330               | 33              | 2.4                  | 0.069   | 6.8         |

| UP3B-470               | 47              | 1.9                  | 0.101   | 6.8         |

| UP3B-680               | 68              | 1.6                  | 0.156   | 6.8         |

| UP3B-101               | 100             | 1.4                  | 0.205   | 6.8         |

| Sumida                 |                 |                      |         |             |

| CDRH8D28-150M          | 15              | 2.2                  | 0.053   | 3           |

| CDRH124-150M           | 15              | 3.2                  | 0.05    | 4.5         |

| CDRH127-150M           | 15              | 4.5                  | 0.02    | 8           |

| CDRH8D28-330M          | 33              | 1.4                  | 0.122   | 3           |

| CDRH124-330M           | 33              | 2.7                  | 0.97    | 4.5         |

| CDRH127-330M           | 33              | 3.0                  | 0.048   | 8           |

| CDRH8D28-470M          | 47              | 1.25                 | 0.150   | 3           |

| CDRH125-470M           | 47              | 1.8                  | 0.058   | 6           |

| CDRH127-470M           | 47              | 2.5                  | 0.076   | 8           |

| CDRH124-680M           | 68              | 1.5                  | 0.228   | 4.5         |

| CDRH127-680M           | 68              | 2.1                  | 0.1     | 8           |

| CDRH124-101M           | 100             | 1.2                  | 0.30    | 4.5         |

| CDRH127-101M           | 100             | 1.7                  | 0.17    | 8           |

| Coilcraft              |                 |                      |         |             |

| DT3308P-153            | 15              | 2.0                  | 0.1     | 3           |

| DT3308P-333            | 33              | 1.4                  | 0.3     | 3           |

| DT3308P-473            | 47              | 1                    | 0.47    | 3           |

|                        |                 |                      |         |             |

Assume that the average inductor current is equal to load current and decide whether or not the inductor must withstand continuous fault conditions. If maximum load current is 0.5A, for instance, a 0.5A inductor may not survive a continuous 2A overload condition.

For applications with a duty cycle above 50%, the inductor value should be chosen to obtain an inductor ripple current of less than 40% of the peak switch current.

2. Calculate peak inductor current at full load current to ensure that the inductor will not saturate. Peak current can be significantly higher than output current, especially with smaller inductors and lighter loads, so don't omit this step. Powdered iron cores are forgiving because they saturate softly, whereas ferrite cores saturate abruptly. Other core materials fall somewhere in between. The following formula assumes continuous mode of operation, but it errs only slightly on the high side for discontinuous mode, so it can be used for all conditions.

$$I_{PEAK} = I_{OUT} + \frac{V_{OUT}(V_{IN} - V_{OUT})}{2(f)(L)(V_{IN})}$$

$V_{IN}$  = maximum input voltage f = switching frequency, 200kHz

- 3. Decide if the design can tolerate an "open" core geometry like a rod or barrel, which have high magnetic field radiation, or whether it needs a closed core like a toroid to prevent EMI problems. This is a tough decision because the rods or barrels are temptingly cheap and small and there are no helpful guidelines to calculate when the magnetic field radiation will be a problem.

- 4. After making an initial choice, consider the secondary things like output voltage ripple, second sourcing, etc. Use the experts in the Linear Technology's applications department if you feel uncertain about the final choice. They have experience with a wide range of inductor types and can tell you about the latest developments in low profile, surface mounting, etc.

#### **Short-Circuit Considerations**

The LT1976 is a current mode controller. It uses the  $V_C$  node voltage as an input to a current comparator which turns off the output switch on a cycle-by-cycle basis as this peak current is reached. The internal clamp on the  $V_C$  node, nominally 2.2V, then acts as an output switch peak current limit. This action becomes the switch current limit specification. The maximum available output power is then determined by the switch current limit.

A potential controllability prod}m could occur under short-circuit conditions. If the power supply output is short circuited, the feedback amplifier responds to the low output voltage by raising the control voltage,  $V_C$ , to its peak current limit value. Ideally, the output switch would be turned on, and then turned off as its current exceeded the value indicated by  $V_C$ . However, there is finite response time involved in both the current comparator and turn-off of the output switch. These result in a minimum on time  $t_{ON(MIN)}$ . When combined with the large ratio of  $V_{IN}$  to  $(V_F + I \bullet R)$ , the diode forward voltage plus inductor  $I \bullet R$  voltage drop, the potential exists for a loss of control. Expressed mathematically the requirement to maintain control is:

$$f \bullet t_{0N} \leq \frac{V_F + I \bullet R}{V_{IN}}$$

where:

f = switching frequency

$t_{ON}$  = switch on time

V<sub>F</sub> = diode forward voltage

$V_{\text{IN}}$  = Input voltage

I • R = inductor I • R voltage drop

If this condition is not observed, the current will not be limited at  $I_{PK}$  but will cycle-by-cycle ratchet up to some higher value. Using the nominal LT1976 clock frequency of 200kHz, a  $V_{IN}$  of 40V and a  $(V_F + I \bullet R)$  of say 0.7V, the maximum  $t_{ON}$  to maintain control would be approximately 90ns, an unacceptably short time.

The solution to this dilemma is to slow down the oscillator to allow the current in the inductor to drop to a sufficiently low value such that the current doesn't continue to ratchet higher. When the FB pin voltage is abnormally low thereby indicating some sort of short-circuit condition, the oscillator frequency will be reduced. Oscillator frequency is reduced by a factor of 4 when the FB pin voltage is below 0.4V and increases linearly to its typical value of 200kHz at a FB voltage of 0.95V (see Typical Performance Characteristics). In addition, if the current in the switch exceeds 1.5  $\bullet$  I<sub>PK</sub> current demanded by the V<sub>C</sub> pin, the LT1976 will skip the next on cycle effectively reducing the oscillator frequency by a factor of 2. These oscillator frequency reductions during short-circuit conditions allow the LT1976 to maintain current control.

#### **SOFT-START**

For applications where  $[V_{IN}/(V_{OLIT} + V_F)]$  ratios > 10 or large input surge currents can't be tolerated, the LT1976 soft-start feature should be used to control the output capacitor charge rate during start-up, or during recovery from an output short circuit thereby adding additional control over peak inductor current. The soft-start function limits the switch current via the V<sub>C</sub> pin to maintain a constant voltage ramp rate (dV/dt) at the output capacitor. A capacitor (C1 in Figure 2) from the  $C_{SS}$  pin to the regulated output voltage determines the output voltage ramp rate. When the current through the C<sub>SS</sub> capacitor exceeds the  $C_{SS}$  threshold ( $I_{CSS}$ ), the voltage ramp of the output capacitor is limited by reducing the V<sub>C</sub> pin voltage. The C<sub>SS</sub> threshold is proportional to the FB voltage (see Typical Performance Characteristics) and is defeated for FB voltages greater than 0.9V (typical). The output dV/dt can be approximated by:

$$\frac{dV}{dt} = \frac{I_{CSS}}{C_{SS}}$$

but actual values will vary due to start-up load conditions, compensation values and output capacitor selection.

Figure 4. V<sub>OUT</sub> dV/dt

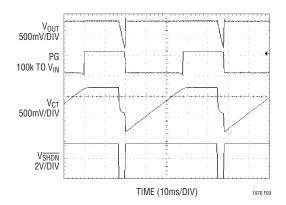

### **Burst Mode OPERATION (LT1976 ONLY)**

To enhance efficiency at light loads, the LT1976 automatically switches to Burst Mode operation which keeps the output capacitor charged to the proper voltage while minimizing the input quiescent current. During Burst Mode operation, the LT1976 delivers short bursts of current to the output capacitor followed by sleep periods where the output power is delivered to the load by the output capacitor. In addition,  $V_{IN}$  and BIAS quiescent currents are reduced to typically  $45\mu A$  and  $125\mu A$  respectively during the sleep time. As the load current decreases towards a no load condition, the percentage of time that the LT1976 operates in sleep mode increases and the average input current is greatly reduced resulting in higher efficiency.

The minimum average input current depends on the  $V_{IN}$  to  $V_{OUT}$  ratio,  $V_{C}$  frequency compensation, feedback divider network and Schottky diode leakage. It can be approximated by the following equation:

$$I_{IN(AVG)} \cong I_{VINS} + I_{SHDN} + \left(\frac{V_{OUT}}{V_{IN}}\right) \frac{\left(I_{BIASS} + I_{FB} + I_{S}\right)}{(\eta)}$$

where

$I_{VINS}$  = input pin current in sleep mode

V<sub>OUT</sub> = output voltage

V<sub>IN</sub> = input voltage

I<sub>BIASS</sub> = BIAS pin current in sleep mode

$I_{FB}$  = feedback network current

$I_S$  = catch diode reverse leakage at  $V_{OUT}$

$\eta$  = low current efficiency (non Burst Mode operation)

Example: For  $V_{OUT} = 3.3V$ ,  $V_{IN} = 12V$

$$\begin{split} I_{IN(AVG)} &= 45\mu A + 5\mu A + \left(\frac{3.3}{12}\right) \!\! \frac{\left(125\mu A + 12.5\mu A + 0.5\mu A\right)}{\left(0.8\right)} \\ &= 45\mu A + 5\mu A + 47\mu A = 97\mu A \end{split}$$

During the sleep portion of the Burst Mode cycle, the  $V_{\mathbb{C}}$  pin voltage is held just below the level needed for normal operation to improve transient response. See the Typical Performance Characteristics section for burst and transient response waveforms.

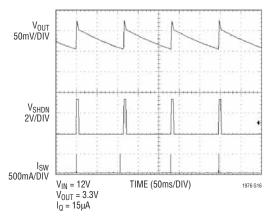

If a no load condition can be anticipated, the supply current can be further reduced by cycling the SHDN pin at a rate higher than the natural no load burst frequency. Figure 6 shows Burst Mode operation with the SHDN pin. V<sub>OUT</sub> burst ripple is maintained while the average supply current

Figure 5. IQ vs VIN

Figure 6. Burst Mode with Shutdown Pin

1976bfg

drops to  $15\mu A$ . The <u>PG</u> pin will be active low during the "on" portion of the S<u>HDN</u> waveform due to the C<sub>T</sub> capacitor discharge when SHDN is taken low. See the Power Good section for further information.

#### **CATCH DIODE**

The catch diode carries load current during the SW off time. The average diode current is therefore dependent on the switch duty cycle. At high input to output voltage ratios the diode conducts most of the time. As the ratio approaches unity the diode conducts only a small fraction of the time. The most stressful condition for the diode is when the output is short circuited. Under this condition the diode must safely handle  $I_{PEAK}$  at maximum duty cycle.

To maximize high and low load current efficiency a fast switching diode with low forward drop and low reverse leakage should be used. Low reverse leakage is critical to maximize low current efficiency since its value over temperature can potentially exceed the magnitude of the LT1976 supply current. Low forward drop is critical for high current efficiency since the loss is proportional to forward drop.

These requirements result in the use of a Schottky type diode. DC switching losses are minimized due to its low forward voltage drop and AC behavior is benign due to its lack of a significant reverse recovery time. Schottky diodes are generally available with reverse voltage ratings of 60V and even 100V and are price competitive with other types.

Table 5. Catch Diode Selection Criteria

|                        |       | (AGE<br>= 3.3V | V <sub>F</sub> A | T 1A  | I <sub>Q</sub> at 125°C<br>V <sub>IN</sub> =12V<br>V <sub>OUT</sub> = 3.3 | EFFICIENCY V <sub>IN</sub> =12V V <sub>OUT</sub> = 3.3V |

|------------------------|-------|----------------|------------------|-------|---------------------------------------------------------------------------|---------------------------------------------------------|

| DIODE                  | 25°C  | 125°C          | <b>25°C</b>      | 125°C | $I_L = 0A$                                                                | I <sub>L</sub> = 1A                                     |

| IR 10BQ100             | 0.0μΑ | 59μΑ           | 0.72V            | 0.58V | 125μΑ                                                                     | 74.1%                                                   |

| Diodes Inc.<br>B260SMA | 0.1μΑ | 242μΑ          | 0.48V            | 0.41V | 215μΑ                                                                     | 82.8%                                                   |

| Diodes Inc.<br>B360SMB | 0.2μΑ | 440μΑ          | 0.45V            | 0.36V | 270μΑ                                                                     | 83.6%                                                   |

| IR<br>MBRS360TR        | 1μΑ   | 1.81mA         | 0.42V            | 0.34V | 821μΑ                                                                     | 83.7%                                                   |

| IR 30BQ100             | 1.7μΑ | 2.64mA         | 0.40V            | 0.32V | 1088μΑ                                                                    | 84.5%                                                   |

The effect of reverse leakage and forward drop on efficiency for various Schottky diodes is shown in Table 4. As can be seen these are conflicting parameters and the user must weigh the importance of each specification in choosing the best diode for the application.

The use of so-called "ultrafast" recovery diodes is generally not recommended. When operating in continuous mode, the reverse recovery time exhibited by "ultrafast" diodes will result in a slingshot type effect. The power internal switch will ramp up  $V_{IN}$  current into the diode in an attempt to get it to recover. Then, when the diode has finally turned off, some tens of nanoseconds later, the  $V_{SW}$  node voltage ramps up at an extremely high dV/dt, perhaps 5V to even 10V/ns! With real world lead inductances the  $V_{SW}$  node can easily overshoot the  $V_{IN}$  rail. This can result in poor RFI behavior and, if the overshoot is severe enough, damage the IC itself.

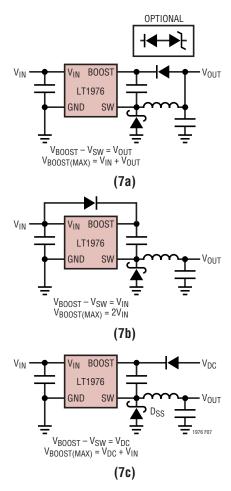

#### **BOOST PIN**

For most applications the boost components are a 0.33µF capacitor and a MMSD914 diode. The anode is typically connected to the regulated output voltage to generate a voltage approximately  $V_{OUT}$  above  $V_{IN}$  to drive the output stage (Figure 7a). However, the output stage discharges the boost capacitor during the on time of the switch. The output driver requires at least 2.5V of headroom throughout this period to keep the switch fully saturated. If the output voltage is less than 3.3V it is recommended that an alternate boost supply is used. The boost diode can be connected to the input (Figure 7b) but care must be taken to prevent the boost voltage  $(V_{BOOST} = V_{IN} \cdot 2)$  from exceeding the BOOST pin absolute maximum rating. The additional voltage across the switch driver also increases power loss and reduces efficiency. If available, an independent supply can be used to generate the required BOOST voltage (Figure 7c). Tying BOOST to  $V_{IN}$  or an independent supply may reduce efficiency but it will reduce the minimum V<sub>IN</sub> required to start-up with light loads. If the generated BOOST voltage dissipates too much power at maximum load, the BOOST voltage the LT1976 sees can be reduced by placing a Zener diode in series with the BOOST diode (Figure 7a option).

Figure 7. BOOST Pin Configurations

A  $0.33\mu F$  boost capacitor is recommended for most applications. Almost any type of film or ceramic capacitor is suitable but the ESR should be  $<1\Omega$  to ensure it can be fully recharged during the off time of the switch. The capacitor value is derived from worst-case conditions of 4700ns on time, 42mA boost current and 0.7V discharge ripple. The boost capacitor value could be reduced under less demanding conditions but this will not improve circuit operation or efficiency. Under low input voltage and low load conditions a higher value capacitor and Schottky boost diode will reduce discharge ripple and improve start-up and dropout operation.

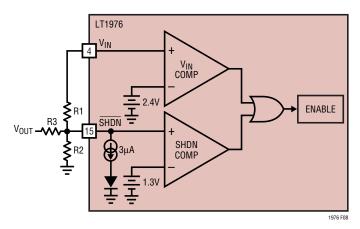

# SHUTDOWN FUNCTION AND UNDERVOLTAGE LOCKOUT

The SHDN pin on the LT1976 controls the operation of the IC. When the voltage on the SHDN pin is below the 1.2V shutdown threshold the LT1976 is placed in a "zero" supply current state. Driving the SHDN pin above the shutdown threshold enables normal operation. The SHDN pin has an internal sink current of 3µA.

In addition to the shutdown feature, the LT1976 has an undervoltage lockout function. When the input voltage is below 2.4V, switching will be disabled. The undervoltage lockout threshold doesn't have any hysteresis and is mainly used to insure that all internal voltages are at the correct level before switching is enabled. If an undervoltage lockout function with hysteresis is needed to limit input current at low  $V_{\text{IN}}$  to  $V_{\text{OUT}}$  ratios refer to Figure 8 and the following:

$$\begin{aligned} V_{UVL0} &= R1 \left( \frac{V_{\overline{SHDN}}}{R3} + \frac{V_{\overline{SHDN}}}{R2} + I_{\overline{SHDN}} \right) + V_{\overline{SHDN}} \\ V_{HYST} &= \frac{V_{OUT}(R1)}{R3} \end{aligned}$$

R1 should be chosen to minimize quiescent current during normal operation by the following equation:

$$R1 = \frac{V_{IN} - 2V}{(1.5)(I_{SHDN(MAX)})}$$

Example:

$$R1 = \frac{12 - 2}{1.5(5\mu A)} = 1.3M\Omega$$

$$R3 = \frac{5(1.3M\Omega)}{1} = 6.5M\Omega \text{ (Nearest 1% 6.49M}\Omega)$$

$$R2 = \frac{1.3}{\frac{7 - 1.3}{1.3M\Omega} - 1\mu A - \frac{1.3}{6.49M\Omega}}$$

$$= 408k \text{ (Nearest 1% 412k)}$$

TECHNOLOGY TECHNOLOGY

Figure 8. Undervoltage Lockout

See the Typical Performance Characteristics section for graphs of SHDN and V<sub>IN</sub> currents verses input voltage.

#### SYNCHRONIZING

Oscillator synchronization to an external input is achieved by connecting a TTL logic-compatible square wave with a duty cycle between 20% and 80% to the LT1976 SYNC pin. The synchronizing range is equal to initial operating frequency up to 700kHz. This means that minimum practical sync frequency is equal to the worst-case high self-oscillating frequency (230kHz), not the typical operating frequency of 200kHz. Caution should be used when synchronizing above 230kHz because at higher sync frequencies the amplitude of the internal slope compensation used to prevent subharmonic switching is reduced. This type of subharmonic switching only occurs at input voltages less than twice output voltage. Higher inductor values will tend to eliminate this problem. See Frequency Compensation section for a discussion of an entirely different cause of subharmonic switching before assuming that the cause is insufficient slope compensation. Application Note 19 has more details on the theory of slope compensation.

If the FB pin voltage is below 0.9V (power-up or output short-circuit conditions) the sync function is disabled. This allows the frequency foldback to operate to avoid and hazardous conditions for the SW pin.

If the synchronization signal is present during Burst Mode operation, synchronization will occur during the burst portion of the output waveform. Synchronizing the LT1976 during Burst Mode operation may alter the natural burst frequency which can lead to jitter and increased ripple in the burst waveform. Synchronizing the LT1976B during pulse skip operation may also increase output ripple.

If no synchronization is required this pin should be connected to ground.

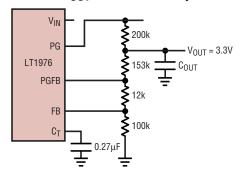

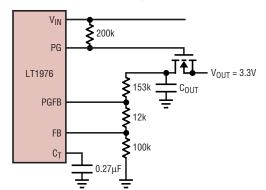

#### **POWER GOOD**

The LT1976 contains a power good block which consists of a comparator, delay timer and active low flag that allows the user to generate a delayed signal after the power good threshold is exceeded.

Referring to Figure 2, the PGFB pin is the positive input to a comparator whose negative input is set at  $V_{PGFB}$ . When PGFB is taken above  $V_{PGFB}$ , current ( $I_{CSS}$ ) is sourced into the  $C_T$  pin starting the delay period. When the voltage on the PGFB pin drops below  $V_{PGFB}$  the  $C_T$  pin is rapidly discharged resetting the delay period. The PGFB voltage is typically generated by a resistive divider from the regulated output or input supply.

The capacitor on the  $C_T$  pin determines the amount of delay time between the PGFB pin exceeding its threshold ( $V_{PGFB}$ ) and the PG pin set to a high impedance state. When the PGFB pin rises above  $V_{PGFB}$  current is sourced

$(I_{CT})$  from the  $C_T$  pin into the external capacitor. When the voltage on the external capacitor reaches an internal clamp  $(V_{CT})$ , the PG pin becomes a high impedance node. The

Figure 9. Power Good

resultant PG delay time is given by  $t = C_{CT} \cdot (V_{CT})/(I_{CT})$ . If the voltage on the PGFB pin drops below its  $V_{PGFB}$ ,  $C_{CT}$  will be discharged rapidly and PG will be active low with a 200 $\mu$ A sink capability. If the  $\overline{SHDN}$  pin is taken below its threshold during normal operation, the  $C_T$  pin will be discharged and PG inactive, resulting in a non Power Good cycle when  $\overline{SHDN}$  is taken above its threshold. Figure 9 shows the power good operation with PGFB connected to FB and the capacitance on  $C_T = 0.1\mu F$ . The PGOOD pin has a limited amount of drive capability and is susceptible to noise during start-up and Burst Mode operation. If erratic operation occurs during these conditions a small filter capacitor from the PGOOD pin to ground will ensure proper operation. Figure 10 shows several different configurations for the LT1976 Power Good circuitry.

#### PG at 80% Vout with 100ms Delay

# V<sub>OUT</sub> Disconnect at 80% V<sub>OUT</sub> with 100ms Delay

PG at V<sub>IN</sub> > 4V with 100ms Delay

Vout Disconnect 3.3V Logic Signal with 100µs Delay

Figure 10. Power Good Circuits

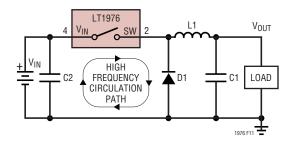

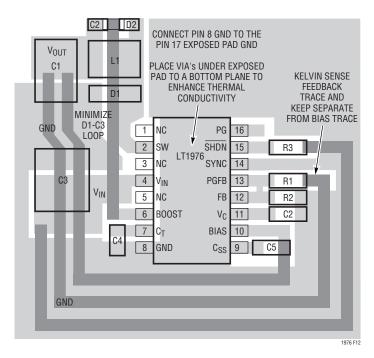

#### LAYOUT CONSIDERATIONS

As with all high frequency switchers, when considering layout, care must be taken in order to achieve optimal electrical, thermal and noise performance. For maximum efficiency switch rise and fall times are typically in the nanosecond range. To prevent noise both radiated and conducted the high speed switching current path, shown in Figure 11, must be kept as short as possible. This is implemented in the suggested layout of Figure 12. Shortening this path will also reduce the parasitic trace inductance of approximately 25nH/inch. At switch off, this parasitic inductance produces a flyback spike across the

LT1976 switch. When operating at higher currents and input voltages, with poor layout, this spike can generate voltages across the LT1976 that may exceed its absolute maximum rating. A ground plane should always be used under the switcher circuitry to prevent interplane coupling and overall noise.

The  $V_{\rm C}$  and FB components should be kept as far away as possible from the switch and boost nodes. The LT1976 pinout has been designed to aid in this. The ground for these components should be separated from the switch current path. Failure to do so will result in poor stability or subharmonic like oscillation.

Figure 11. High Speed Switching Path

Figure 12. Suggested Layout

Board layout also has a significant effect on thermal resistance. Pin 8 and the exposed die pad, Pin 17, are a continuous copper plate that runs under the LT1976 die. This is the best thermal path for heat out of the package. Reducing the thermal resistance from Pin 8 and exposed pad onto the board will reduce die temperature and increase the power capability of the LT1976. This is achieved by providing as much copper area as possible around the exposed pad. Adding multiple solder filled feedthroughs under and around this pad to an internal ground plane will also help. Similar treatment to the catch diode and coil terminations will reduce any additional heating effects.

#### THERMAL CALCULATIONS

Power dissipation in the LT1976 chip comes from four sources: switch DC loss, switch AC loss, boost circuit current, and input quiescent current. The following formulas show how to calculate each of these losses. These formulas assume continuous mode operation, so they should not be used for calculating efficiency at light load currents.

Switch loss:

$$P_{SW} = \frac{R_{SW} \big(I_{OUT}\big)^2 \big(V_{OUT}\big)}{V_{IN}} + t_{EFF} \big(1/2\big) \big(I_{OUT}\big) \big(V_{IN}\big) (f)$$

Boost current loss:

$$P_{BOOST} = \frac{(V_{OUT})^2 (I_{OUT}/36)}{V_{IN}}$$

Quiescent current loss: (LT1976)

$$P_Q = V_{IN} (0.0015) + V_{OUT} (0.003)$$

$R_{SW}$  = switch resistance ( $\approx 0.3$  when hot)

t<sub>EFF</sub> = effective switch current/voltage overlap time

$$(t_r + t_f + t_{IR} + t_{IF})$$

$t_r = (V_{IN}/1.7) ns$

$t_f = (V_{INI}/1.2) ns$

$t_{IR} = t_{IF} = (I_{OUT}/0.05)$ ns

f = switch frequency

Example: with  $V_{IN} = 40V$ ,  $V_{OUT} = 5V$  and  $I_{OUT} = 1A$ :

$$P_{SW} = \frac{(0.3)(1)^2(5)}{40} + (97e - 9)(1/2)(1)(40)(200e3)$$

0.04 + 0.388 = 0.43W

$$P_{BOOST} = \frac{(5)^2 (1/36)}{40} = 0.02W$$

$$P_Q = 40(0.0015) + 5(0.003) = 0.08W$$

Total power dissipation is:

$$P_{TOT} = 0.43 + 0.02 + 0.08 = 0.53W$$

Thermal resistance for the LT1976 package is influenced by the presence of internal or backside planes. With a full plane under the FE16 package, thermal resistance will be about 45°C/W. No plane will increase resistance to about 150°C/W. To calculate die temperature, use the proper thermal resistance number for the desired package and add in worst-case ambient temperature:

$$T_J = T_A + Q_{JA} (P_{TOT})$$

With the FE16 package ( $Q_{JA} = 45^{\circ}C/W$ ) at an ambient temperature of  $70^{\circ}C$ :

$$T_J = 70 + 45(0.53) = 94^{\circ}C$$

If a more accurate die temperature is required, a measurement of the SYNC pin resistance to ground can be used. The SYNC pin resistance can be measured by forcing a voltage no greater than 0.25V at the pin and monitoring the pin current versus temperature in a controlled temperature environment. The measurement should be done with minimal device power dissipation (pull the  $V_{\rm C}$  pin to ground for sleep mode) in order to calibrate the SYNC pin resistance with the ambient temperature.

#### HIGH TEMPERATURE OPERATION