# Six LVPECL Outputs, SiGe Clock Fanout Buffer

ADCLK946

#### **FEATURES**

4.8 GHz operating frequency75 fs rms broadband random jitterOn-chip input terminations3.3 V power supply

### **APPLICATIONS**

Low jitter clock distribution

Clock and data signal restoration

Level translation

Wireless communications

Wired communications

Medical and industrial imaging

ATE and high performance instrumentation

#### **GENERAL DESCRIPTION**

The ADCLK946 is an ultrafast clock fanout buffer fabricated on the Analog Devices, Inc., proprietary XFCB3 silicon germanium (SiGe) bipolar process. This device is designed for high speed applications requiring low jitter.

The device has a differential input equipped with center-tapped, differential,  $100~\Omega$  on-chip termination resistors. The input accepts dc-coupled LVPECL, CML, 3.3 V CMOS (single ended), and ac-coupled 1.8 V CMOS, LVDS, and LVPECL inputs. A V<sub>REF</sub> pin is available for biasing ac-coupled inputs.

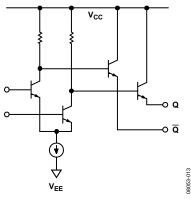

The ADCLK946 features six full-swing emitter-coupled logic (ECL) output drivers. For LVPECL (positive ECL) operation, bias  $V_{\rm CC}$  to the positive supply and  $V_{\rm EE}$  to ground. For ECL operation, bias  $V_{\rm CC}$  to ground and  $V_{\rm EE}$  to the negative supply.

The ECL output stages are designed to directly drive 800 mV each side into 50  $\Omega$  terminated to  $V_{\rm CC}$  – 2 V for a total differential output swing of 1.6 V.

The ADCLK946 is available in a 24-lead LFCSP and is specified for operation over the standard industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

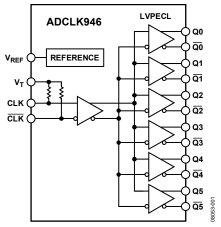

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

## **TABLE OF CONTENTS**

| Features                         | . 1 |

|----------------------------------|-----|

| Applications                     | . 1 |

| General Description              | . 1 |

| Functional Block Diagram         | . 1 |

| Revision History                 | . 2 |

| Specifications                   | . 3 |

| Electrical Characteristics       | . 3 |

| Absolute Maximum Ratings         | . 5 |

| Determining Junction Temperature | . 5 |

| FSD Caution                      | 5   |

| Thermal Performance5                         |

|----------------------------------------------|

| Pin Configuration and Function Descriptions6 |

| Typical Performance Characteristics          |

| Functional Description9                      |

| Clock Inputs9                                |

| Clock Outputs9                               |

| PCB Layout Considerations10                  |

| Input Termination Options11                  |

| Outline Dimensions                           |

| Ordering Guide                               |

### **REVISION HISTORY**

4/09—Revision 0: Initial Version

### **SPECIFICATIONS**

### **ELECTRICAL CHARACTERISTICS**

Typical (typ) values are given for  $V_{CC} - V_{EE} = 3.3 \text{ V}$  and  $T_A = 25^{\circ}\text{C}$ , unless otherwise noted. Minimum (min) and maximum (max) values are given over the full  $V_{CC} - V_{EE} = 3.3 \text{ V} \pm 10\%$  and  $T_A = -40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  variation, unless otherwise noted.

**Table 1. Clock Inputs and Outputs**

| Parameter                   | Symbol          | Min                    | Тур              | Max                    | Unit  | Test Conditions/Comments                            |

|-----------------------------|-----------------|------------------------|------------------|------------------------|-------|-----------------------------------------------------|

| DC INPUT CHARACTERISTICS    |                 |                        |                  |                        |       |                                                     |

| Input Voltage High Level    | V <sub>IH</sub> | $V_{EE} + 1.6$         |                  | $V_{CC}$               | V     |                                                     |

| Input Voltage Low Level     | V <sub>IL</sub> | VEE                    |                  | $V_{CC}-0.2$           | V     |                                                     |

| Input Differential Range    | V <sub>ID</sub> | 0.4                    |                  | 3.4                    | V p-p | ±1.7 V between input pins                           |

| Input Capacitance           | C <sub>IN</sub> |                        | 0.4              |                        | pF    |                                                     |

| Input Resistance            |                 |                        |                  |                        |       |                                                     |

| Single-Ended Mode           |                 |                        | 50               |                        | Ω     |                                                     |

| Differential Mode           |                 |                        | 100              |                        | Ω     |                                                     |

| Common Mode                 |                 |                        | 50               |                        | kΩ    | Open V <sub>T</sub>                                 |

| Input Bias Current          |                 |                        | 20               |                        | μΑ    |                                                     |

| Hysteresis                  |                 |                        | 10               |                        | mV    |                                                     |

| DC OUTPUT CHARACTERISTICS   |                 |                        |                  |                        |       |                                                     |

| Output Voltage High Level   | $V_{OH}$        | Vcc - 1.26             |                  | $V_{\text{CC}} - 0.76$ | V     | $50 \Omega$ to (V <sub>CC</sub> $- 2.0 \text{ V}$ ) |

| Output Voltage Low Level    | $V_{OL}$        | V <sub>CC</sub> – 1.99 |                  | $V_{\text{CC}}-1.54$   | V     | $50 \Omega$ to (V <sub>CC</sub> $- 2.0 V$ )         |

| Output Voltage Differential | $V_{OD}$        | 610                    |                  | 960                    | mV    | $50 \Omega$ to (V <sub>CC</sub> $- 2.0 \text{ V}$ ) |

| Reference Voltage           | $V_{REF}$       |                        |                  |                        |       |                                                     |

| Output Voltage              |                 |                        | $(V_{CC} + 1)/2$ |                        | V     | –500 μA to +500 μA                                  |

| Output Resistance           |                 |                        | 235              |                        | Ω     |                                                     |

**Table 2. Timing Characteristics**

| Parameter                             | Symbol                          | Min | Тур  | Max | Unit   | Test Conditions/Comments                                                                     |

|---------------------------------------|---------------------------------|-----|------|-----|--------|----------------------------------------------------------------------------------------------|

| AC PERFORMANCE                        |                                 |     |      |     |        |                                                                                              |

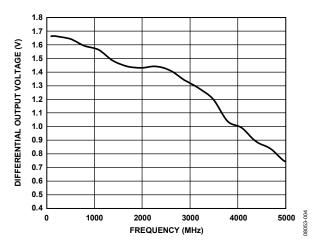

| Maximum Output Frequency              |                                 | 4.5 | 4.8  |     | GHz    | See Figure 4 for differential output voltage vs. frequency, >0.8 V differential output swing |

| Output Rise/Fall Time                 | t <sub>R</sub> , t <sub>F</sub> | 40  | 75   | 90  | ps     | 20% to 80% measured differentially                                                           |

| Propagation Delay                     | t <sub>PD</sub>                 | 150 | 185  | 220 | ps     | $V_{ICM} = 2 \text{ V}, V_{ID} = 1.6 \text{ V p-p}$                                          |

| Temperature Coefficient               |                                 |     | 50   |     | fs/°C  |                                                                                              |

| Output-to-Output Skew                 |                                 |     | 9    | 28  | ps     |                                                                                              |

| Part-to-Part Skew <sup>1</sup>        |                                 |     |      | 45  | ps     | $V_{ID} = 1.6 \text{ V p-p}$                                                                 |

| Additive Time Jitter                  |                                 |     |      |     |        |                                                                                              |

| Integrated Random Jitter              |                                 |     | 28   |     | fs rms | BW = 12 kHz – 20 MHz, CLK = 1 GHz                                                            |

| Broadband Random Jitter <sup>2</sup>  |                                 |     | 75   |     | fs rms | $V_{ID} = 1.6 \text{ V p-p}, 8 \text{ V/ns}, V_{ICM} = 2 \text{ V}$                          |

| Crosstalk-Induced Jitter <sup>3</sup> |                                 |     | 90   |     | fs rms |                                                                                              |

| CLOCK OUTPUT PHASE NOISE              |                                 |     |      |     |        |                                                                                              |

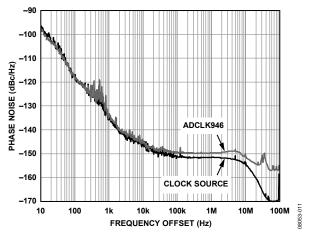

| Absolute Phase Noise                  |                                 |     |      |     |        | Input slew rate > 1 V/ns (see Figure 11 for more details)                                    |

| $f_{IN} = 1 \text{ GHz}$              |                                 |     | -119 |     | dBc/Hz | @ 100 Hz offset                                                                              |

|                                       |                                 |     | -134 |     | dBc/Hz | @ 1 kHz offset                                                                               |

|                                       |                                 |     | -145 |     | dBc/Hz | @ 10 kHz offset                                                                              |

|                                       |                                 |     | -150 |     | dBc/Hz | @ 100 kHz offset                                                                             |

|                                       |                                 |     | -150 |     | dBc/Hz | >1 MHz offset                                                                                |

<sup>&</sup>lt;sup>1</sup> The output skew is the difference between any two similar delay paths while operating at the same voltage and temperature.

<sup>&</sup>lt;sup>2</sup> Measured at the rising edge of the clock signal; calculated using the SNR of the ADC method.

<sup>&</sup>lt;sup>3</sup> The amount of added jitter measured at the output while two related, asynchronous, differential frequencies are applied to the inputs.

Table 3. Power

| Parameter                                  | Symbol                          | Min  | Тур | Max  | Unit | Test Conditions/Comments                   |

|--------------------------------------------|---------------------------------|------|-----|------|------|--------------------------------------------|

| POWER SUPPLY                               |                                 |      |     |      |      |                                            |

| Supply Voltage Requirement                 | $V_{\text{CC}} - V_{\text{EE}}$ | 2.97 |     | 3.63 | V    | 3.3 V + 10%                                |

| Power Supply Current                       |                                 |      |     |      |      | Static                                     |

| Negative Supply Current                    | I <sub>VEE</sub>                |      | 90  | 115  | mA   | $V_{CC} - V_{EE} = 3.3 \text{ V} \pm 10\%$ |

| Positive Supply Current                    | lvcc                            |      | 245 | 275  | mA   | $V_{CC} - V_{EE} = 3.3 \text{ V} \pm 10\%$ |

| Power Supply Rejection <sup>1</sup>        | PSR <sub>VCC</sub>              |      | <3  |      | ps/V | $V_{CC} - V_{EE} = 3.3 \text{ V} \pm 10\%$ |

| Output Swing Supply Rejection <sup>2</sup> | PSR <sub>vcc</sub>              |      | 28  |      | dB   | $V_{CC} - V_{EE} = 3.3 \text{ V} \pm 10\%$ |

$<sup>^1</sup>$  Change in  $t_{PD}$  per change in  $V_{CC}.$   $^2$  Change in output swing per change in  $V_{CC}.$

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| Parameter                                                       | Rating                             |

|-----------------------------------------------------------------|------------------------------------|

| Supply Voltage                                                  |                                    |

| $V_{CC} - V_{EE}$                                               | 6.0 V                              |

| Input Voltage                                                   |                                    |

| CLK, CLK                                                        | $V_{EE} - 0.5 V$ to                |

|                                                                 | $V_{CC} + 0.5 V$                   |

| CLK, $\overline{\text{CLK}}$ to V <sub>T</sub> Pin (CML, LVPECL | ±40 mA                             |

| Termination)                                                    |                                    |

| CLK to CLK                                                      | ±1.8 V                             |

| Input Termination, $V_T$ to CLK, $\overline{\text{CLK}}$        | ±2 V                               |

| Maximum Voltage on Output Pins                                  | $V_{CC} + 0.5 V$                   |

| Maximum Output Current                                          | 35 mA                              |

| Voltage Reference (V <sub>REF</sub> )                           | V <sub>CC</sub> to V <sub>EE</sub> |

| Operating Temperature Range                                     |                                    |

| Ambient                                                         | -40°C to +85°C                     |

| Junction                                                        | 150°C                              |

| Storage Temperature Range                                       | −65°C to +150°C                    |

|                                                                 |                                    |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **DETERMINING JUNCTION TEMPERATURE**

To determine the junction temperature on the application printed circuit board (PCB), use the following equation:

$$T_I = T_{CASE} + (\Psi_{IT} \times P_D)$$

where:

$T_J$  is the junction temperature (°C).

$T_{CASE}$  is the case temperature (°C) measured by the customer at the top center of the package.

$\Psi_{JT}$  is as indicated in Table 5.

$P_D$  is the power dissipation.

Values of  $\theta_{JA}$  are provided for package comparison and PCB design considerations.  $\theta_{JA}$  can be used for a first-order approximation of  $T_J$  by the equation

$$T_J = T_A + (\theta_{JA} \times P_D)$$

where  $T_A$  is the ambient temperature (°C).

Values of  $\theta_{JB}$  are provided in Table 5 for package comparison and PCB design considerations.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### THERMAL PERFORMANCE

Table 5.

| Parameter                                              | Symbol                    | Description                     | Value <sup>1</sup> | Unit |

|--------------------------------------------------------|---------------------------|---------------------------------|--------------------|------|

| Junction-to-Ambient Thermal Resistance                 |                           |                                 |                    |      |

| Still Air                                              |                           |                                 |                    |      |

| 0.0 m/sec Airflow                                      | $\theta_{JA}$             | Per JEDEC JESD51-2              | 54.3               | °C/W |

| Moving Air                                             |                           |                                 |                    |      |

| 1.0 m/sec Airflow                                      | $\theta_{JMA}$            | Per JEDEC JESD51-6              | 47.5               | °C/W |

| 2.5 m/sec Airflow                                      | $	heta_{JMA}$             | Per JEDEC JESD51-6              | 42.6               | °C/W |

| Junction-to-Board Thermal Resistance                   |                           |                                 |                    |      |

| Moving Air                                             |                           |                                 |                    |      |

| 1.0 m/sec Airflow                                      | θјв                       | Per JEDEC JESD51-8 (moving air) | 33.0               | °C/W |

| Junction-to-Case Thermal Resistance (Die-to-Heat Sink) |                           |                                 |                    |      |

| Moving Air                                             | θις                       | Per MIL-Std. 883, Method 1012.1 | 2.0                | °C/W |

| Junction-to-Top-of-Package Characterization Parameter  |                           |                                 |                    |      |

| Still Air                                              |                           |                                 |                    |      |

| 0 m/sec Airflow                                        | $\Psi_{^{\!\mathcal{H}}}$ | Per JEDEC JESD51-2              | 0.9                | °C/W |

<sup>&</sup>lt;sup>1</sup>Results are from simulations. The PCB is a JEDEC multilayer type. Thermal performance for actual applications requires careful inspection of the conditions in the application to determine if they are similar to those assumed in these calculations.

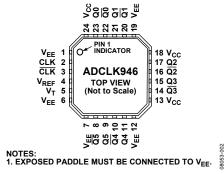

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 2. Pin Configuration

**Table 6. Pin Function Descriptions**

| Pin No.         | Mnemonic           | Description                                                                                                               |  |  |

|-----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|

| 1, 6, 7, 12, 19 | V <sub>EE</sub>    | Negative Supply Pin.                                                                                                      |  |  |

| 2               | CLK                | Differential Input (Positive).                                                                                            |  |  |

| 3               | CLK                | Differential Input (Negative).                                                                                            |  |  |

| 4               | $V_{REF}$          | Reference Voltage. This pin provides the reference voltage for biasing ac-coupled CLK and CLK inputs.                     |  |  |

| 5               | V <sub>T</sub>     | Center Tap. This pin provides the center tap of a 100 $\Omega$ input resistor for CLK and $\overline{\text{CLK}}$ inputs. |  |  |

| 8, 9            | <del>Q5</del> , Q5 | Differential LVPECL Outputs.                                                                                              |  |  |

| 10, 11          | <del>Q4</del> , Q4 | Differential LVPECL Outputs.                                                                                              |  |  |

| 13, 18, 24      | V <sub>cc</sub>    | Positive Supply Pin.                                                                                                      |  |  |

| 14, 15          | <del>Q3</del> , Q3 | Differential LVPECL Outputs.                                                                                              |  |  |

| 16, 17          | Q2, Q2             | Differential LVPECL Outputs.                                                                                              |  |  |

| 20, 21          | <del>Q1</del> , Q1 | Differential LVPECL Outputs.                                                                                              |  |  |

| 22, 23          | <del>Q0</del> , Q0 | Differential LVPECL Outputs.                                                                                              |  |  |

|                 | EPAD               | EPAD must be soldered to V <sub>EE</sub> .                                                                                |  |  |

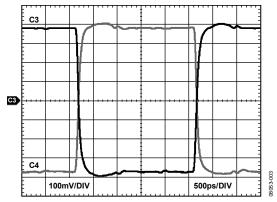

### TYPICAL PERFORMANCE CHARACTERISTICS

$V_{\text{CC}} = 3.3 \text{ V}, V_{\text{EE}} = 0.0 \text{ V}, V_{\text{ICM}} = V_{\text{REF}}, T_{\text{A}} = 25^{\circ}\text{C}, \text{ clock outputs terminated at } 50 \ \Omega \text{ to } V_{\text{CC}} - 2 \text{ V}, \text{ unless otherwise noted.}$

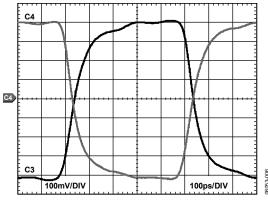

Figure 3. LVPECL Output Waveform @ 200 MHz

Figure 4. Differential Output Swing vs. Frequency

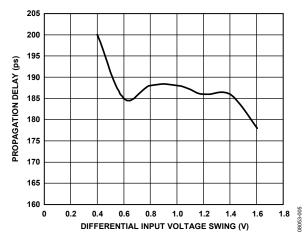

Figure 5. Propagation Delay vs. Differential Input Voltage

Figure 6. LVPECL Output Waveform @ 1000 MHz

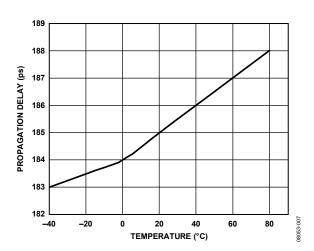

Figure 7. Propagation Delay vs. Temperature

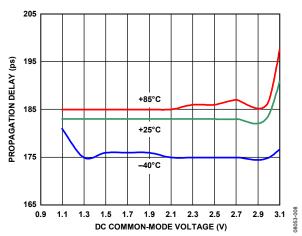

Figure 8. Propagation Delay vs. Common-Mode Voltage vs. Temperature, Input Slew Rate > 25 V/ns

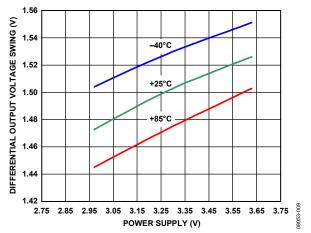

Figure 9. Differential Output Swing vs. Power Supply Voltage vs. Temperature,  $V_{\rm ID}=1.6~{\rm V}~{\rm p}{\rm -p}$

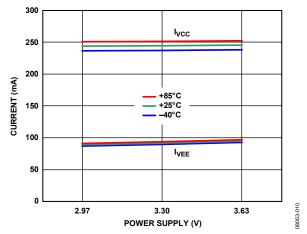

Figure 10. Power Supply Current vs. Power Supply Voltage vs. Temperature, All Outputs Loaded (50  $\Omega$  to  $V_{CC}$  – 2 V)

Figure 11. Absolute Phase Noise Measured @1 GHz with Agilent E5052

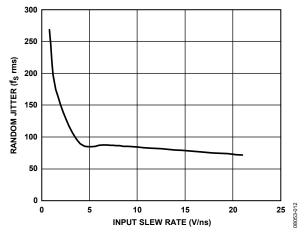

Figure 12. RMS Jitter vs. Input Slew Rate, V<sub>ID</sub> Method

# FUNCTIONAL DESCRIPTION CLOCK INPUTS

The ADCLK946 accepts a differential clock input and distributes it to all six LVPECL outputs. The maximum specified frequency is the point at which the output voltage swing is 50% of the standard LVPECL swing (see Figure 4).

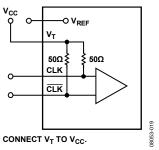

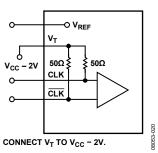

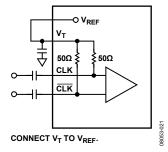

The device has a differential input equipped with center-tapped, differential,  $100~\Omega$  on-chip termination resistors. The input accepts dc-coupled LVPECL, CML, 3.3 V CMOS (single ended), and ac-coupled 1.8 V CMOS, LVDS, and LVPECL inputs. A V<sub>REF</sub> pin is available for biasing ac-coupled inputs (see Figure 1).

Maintain the differential input voltage swing from approximately 400 mV p-p to no more than 3.4 V p-p. See Figure 14 through Figure 17 for various clock input termination schemes.

Output jitter performance is degraded by an input slew rate below 1 V/ns, as shown in Figure 12. The ADCLK946 is specifically designed to minimize added random jitter over a wide input slew rate range. Whenever possible, clamp excessively large input signals with fast Schottky diodes because attenuators reduce the slew rate. Input signal runs of more than a few centimeters should be over low loss dielectrics or cables with good high frequency characteristics.

### **CLOCK OUTPUTS**

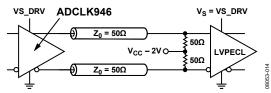

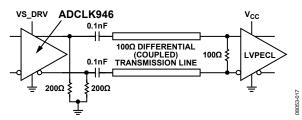

The specified performance necessitates using proper transmission line terminations. The LVPECL outputs of the ADCLK946 are designed to directly drive 800 mV into a 50  $\Omega$  cable or into microstrip/stripline transmission lines terminated with 50  $\Omega$  referenced to  $V_{\rm CC}-2$  V, as shown in Figure 14. The LVPECL output stage is shown in Figure 13. The outputs are designed for best transmission line matching. If high speed signals must be routed more than a centimeter, either the microstrip or the stripline technique is required to ensure proper transition times and to prevent excessive output ringing and pulse-width-dependent, propagation delay dispersion.

Figure 13. Simplified Schematic Diagram of the LVPECL Output Stage

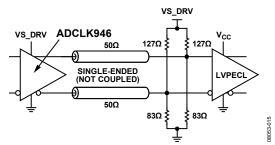

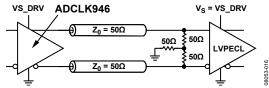

Figure 14 through Figure 17 depict various LVPECL output termination schemes. When dc-coupled,  $V_{\rm CC}$  of the receiving buffer should match the VS\_DRV.

The venin-equivalent termination uses a resistor network to provide  $50~\Omega$  termination to a dc voltage that is below  $V_{\rm OL}$  of the LVPECL driver. In this case, VS\_DRV on the ADCLK946 should equal  $V_{\rm CC}$  of the receiving buffer. Although the resistor combination shown in Figure 15 results in a dc bias point of VS\_DRV - 2 V, the actual common-mode voltage is VS\_DRV - 1.3 V because there is additional current flowing from the ADCLK946 LVPECL driver through the pull-down resistor.

LVPECL Y-termination is an elegant termination scheme that uses the fewest components and offers both odd- and even-mode impedance matching. Even-mode impedance matching is an important consideration for closely coupled transmission lines at high frequencies. Its main drawback is that it offers limited flexibility for varying the drive strength of the emitter-follower LVPECL driver. This can be an important consideration when driving long trace lengths but is usually not an issue.

Figure 14. DC-Coupled, 3.3 V LVPECL

Figure 15. DC-Coupled, 3.3 V LVPECL Far-End Thevenin Termination

Figure 16. DC-Coupled, 3.3 V LVPECL Y-Termination

Figure 17. AC-Coupled, LVPECL with Parallel Transmission Line

### **PCB LAYOUT CONSIDERATIONS**

The ADCLK946 buffer is designed for very high speed applications. Consequently, high speed design techniques must be used to achieve the specified performance. It is critically important to use low impedance supply planes for both the negative supply ( $V_{\text{EE}}$ ) and the positive supply ( $V_{\text{CC}}$ ) planes as part of a multilayer board. Providing the lowest inductance return path for switching currents ensures the best possible performance in the target application.

The following references to the ground plane assume that the  $V_{\text{EE}}$  power plane is grounded for LVPECL operation. Note that, for ECL operation, the  $V_{\text{CC}}$  power plane becomes the ground plane.

It is also important to adequately bypass the input and output supplies. Place a 1  $\mu F$  electrolytic bypass capacitor within several inches of each  $V_{\rm CC}$  power supply pin to the ground plane. In addition, place multiple high quality 0.001  $\mu F$  bypass capacitors as close as possible to each of the  $V_{\rm CC}$  supply pins, and connect the capacitors to the ground plane with redundant vias. Carefully select high frequency bypass capacitors for minimum inductance and ESR. To improve the effectiveness of the bypass at high frequencies, minimize parasitic layout inductance. Also, avoid discontinuities along input and output transmission lines that can affect jitter performance.

In a 50  $\Omega$  environment, input and output matching have a significant impact on performance. The buffer provides internal 50  $\Omega$  termination resistors for both CLK and  $\overline{\text{CLK}}$  inputs. Normally, the return side is connected to the reference pin that is provided. Carefully bypass the termination potential using ceramic capacitors to prevent undesired aberrations on the input signal due to parasitic inductance in the termination return path. If the inputs are dc-coupled to a source, take care to

ensure that the pins are within the rated input differential and common-mode ranges.

If the return is floated, the device exhibits a 100  $\Omega$  cross-termination, but the source must then control the common-mode voltage and supply the input bias currents.

There are ESD/clamp diodes between the input pins to prevent the application from developing excessive offsets to the input transistors. ESD diodes are not optimized for best ac performance. When a clamp is required, it is recommended that appropriate external diodes be used.

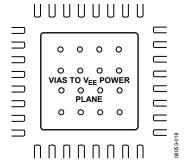

### **Exposed Metal Paddle**

The exposed metal paddle on the ADCLK946 package is both an electrical connection and a thermal enhancement. For the device to function properly, the paddle must be properly attached to the  $V_{\rm EE}$  pin.

When properly mounted, the ADCLK946 also dissipates heat through its exposed paddle. The PCB acts as a heat sink for the ADCLK946. The PCB attachment must provide a good thermal path to a larger heat dissipation area. This requires a grid of vias from the top layer down to the  $V_{\rm EE}$  power plane (see Figure 18). The ADCLK946 evaluation board (ADCLK946/PCBZ) provides an example of how to attach the part to the PCB.

Figure 18. PCB Land for Attaching Exposed Paddle

### **INPUT TERMINATION OPTIONS**

Figure 19. Interfacing to CML Inputs

Figure 20. Interfacing to PECL Inputs

Figure 21. AC-Coupling Differential Signals Inputs, Such as LVDS

CONNECT V<sub>T</sub>, V<sub>REF</sub>, AND  $\overline{\text{CLK}}$ . PLACE A BYPASS CAPACITOR FROM V<sub>T</sub> TO GROUND. ALTERNATIVELY, V<sub>T</sub>, V<sub>REF</sub>, AND CLK CAN BE CONNECTED, GIVING A CLEANER LAYOUT AND A 180° PHASE SHIFT.

Figure 22. Interfacing to AC-Coupled Single-Ended Inputs

### **OUTLINE DIMENSIONS**

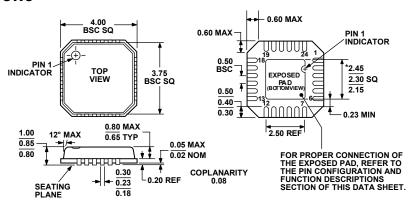

\*COMPLIANT TO JEDEC STANDARDS MO-220-VGGD-2 EXCEPT FOR EXPOSED PAD DIMENSION

Figure 23. 24-Lead Lead Frame Chip Scale Package [LFCSP\_VQ] 4 mm × 4 mm Body, Very Thin Quad CP-24-2 Dimensions shown in millimeters

### **ORDERING GUIDE**

| Model                           | Temperature Range | Package Description     | Package Option |

|---------------------------------|-------------------|-------------------------|----------------|

| ADCLK946BCPZ <sup>1</sup>       | -40°C to +85°C    | 24-Lead LFCSP_VQ        | CP-24-2        |

| ADCLK946BCPZ-REEL7 <sup>1</sup> | -40°C to +85°C    | 24-Lead LFCSP_VQ        | CP-24-2        |

| ADCLK946/PCBZ <sup>1</sup>      |                   | <b>Evaluation Board</b> |                |

$<sup>^{1}</sup>$  Z = RoHS Compliant Part.

080808-A

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.