# PolyPhase Step-Down Slave Controller for Digital Power System Management

## FEATURES

- **LTC3887-1 Phase Extender**

- **Operates with Power Blocks, DrMOS or External Gate Drivers and MOSFETs**

- **Cascade with Multiple Chips for Very Large Current Applications**

- **Accurate PolyPhase Current Sharing**

- **EXTV<sub>CC</sub> Capable of 5V to 14V Input**

- **Wide V<sub>IN</sub> Range: 4.5V to 60V**

- **Wide Output Voltage Range : 0.5V to 14V**

- **Wide SYNC Frequency Range: 100kHz to 1MHz**

- **Pin Programmable CCM/DCM Operation**

- **Pin Programmable Phase-Shift Control**

- **Available in a 24-Pin (4mm x 4mm) QFN Package**

## APPLICATIONS

- **High Power Distributed Power Systems**

- **Telecom Systems**

- **Industrial Applications**

## DESCRIPTION

The **LTC<sup>®</sup>3870-1** is a PolyPhase<sup>®</sup> step-down slave controller specially designed for multiphase operation with LTC's digital power system management DC/DC controllers. It provides a small and cost effective solution for supplying very large currents by cascading it with a LTC3887-1 controller. A peak current mode architecture provides the LTC3870-1 with excellent current sharing from phase to phase and from chip to chip.

Coherently working with the LTC3887-1, the LTC3870-1 does not require additional I<sup>2</sup>C addresses, and it supports all programmable features as well as fault protection. The constant switching frequency can be synchronized to an external clock from the LTC3887-1 over a range of 100kHz to 1MHz.

**L**T, LT, LTC, LTM, PolyPhase, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents including 5481178, 5705919, 5929620, 6144194, 6177787, 6580258, 5408150

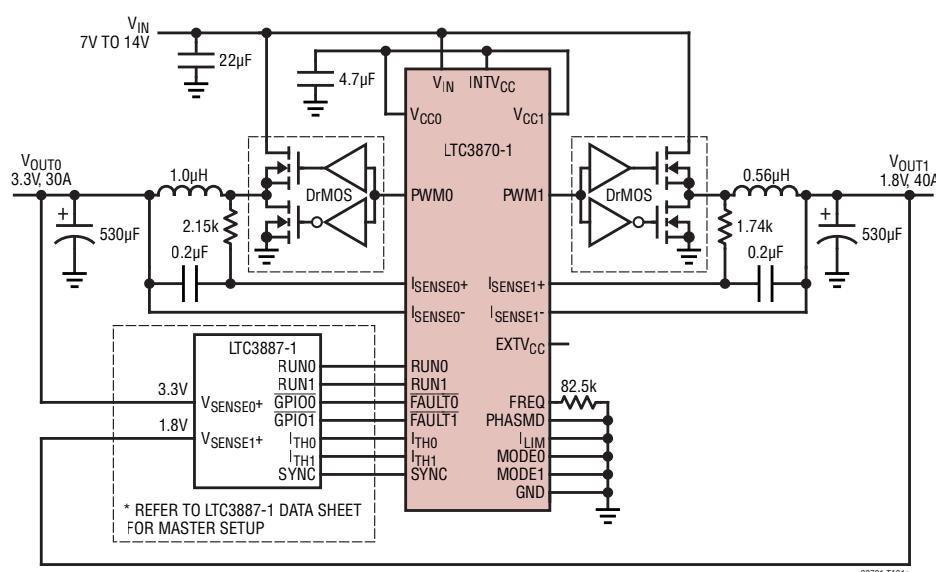

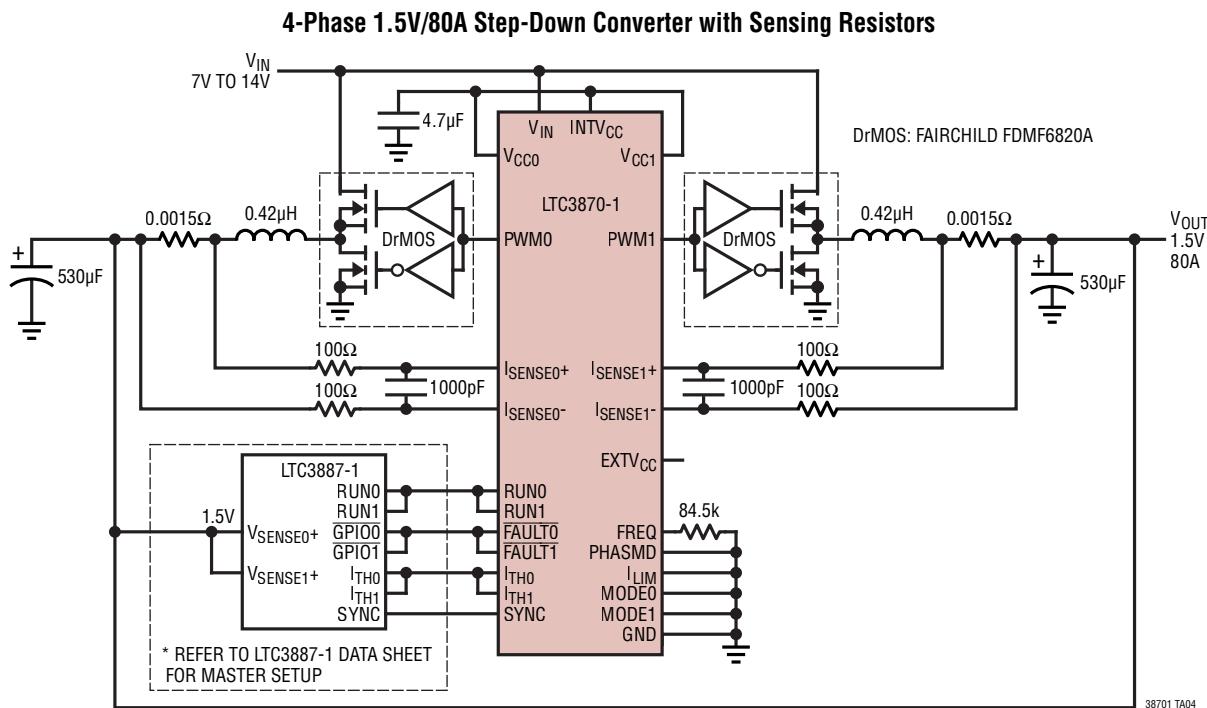

## TYPICAL APPLICATION

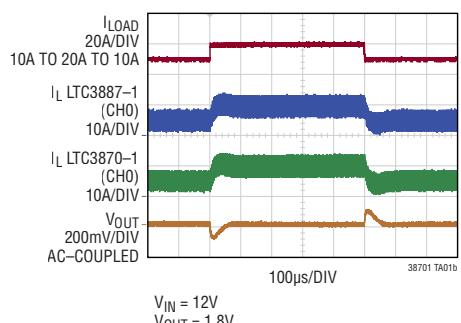

**Load Transient Response of a 2-Phase Master (3887-1)/Slave (3870-1) Converter**

V<sub>IN</sub> = 12V

V<sub>OUT</sub> = 1.8V

LTC3870-1

## ABSOLUTE MAXIMUM RATINGS

(Note 1)

|                                                            |                      |

|------------------------------------------------------------|----------------------|

| $V_{IN}$ .....                                             | -0.3V to 65V         |

| $V_{CC0}, V_{CC1}$ .....                                   | -0.3V to 6V          |

| $I_{SENSE0+}, I_{SENSE0-}, I_{SENSE1+}, I_{SENSE1-}$ ..... | -0.3V to 15V         |

| $INTV_{CC}, RUN0/RUN1$ .....                               | -0.3V to 6V          |

| $EXTV_{CC}$ .....                                          | -0.3V to 14V         |

| $MODE0/MODE1$ ,                                            |                      |

| $FREQ, PHASMD, I_{LIM}$ .....                              | -0.3V to $INTV_{CC}$ |

| $FAULT0/FAULT1, I_{TH0}/I_{TH1}, SYNC$ .....               | -0.3V to 3.6V        |

| $INTV_{CC}, EXTV_{CC}$ Peak Current (Note 7) .....         | 100mA                |

| Current limit                                              |                      |

Operating Junction Temperature Range..... -40°C to 125°C

Storage Temperature Range..... 65°C to 150°C

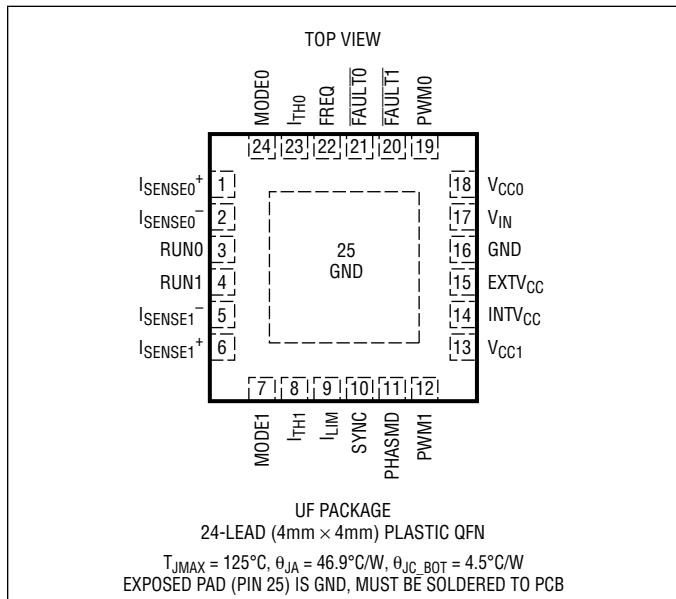

## PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC3870EUF-1#PBF | LTC3870EUF-1#TRPBF | 38701         | 24-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

| LTC3870IUF-1#PBF | LTC3870IUF-1#TRPBF | 38701         | 24-Lead (4mm × 4mm) Plastic QFN | -40°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: <http://www.linear.com/leadfree/>

For more information on tape and reel specifications, go to: <http://www.linear.com/tapeandreel/>. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

## ELECTRICAL CHARACTERISTICS

**ELECTRICAL CHARACTERISTICS** The ● denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^\circ\text{C}$ . (Note 2)  $V_{IN} = 15\text{V}$ ,  $V_{RUN0}, V_{RUN1} = 3.3\text{V}$ ,  $f_{SYNC} = 350\text{kHz}$  (externally driven) unless otherwise specified.

| Symbol     | Parameter                                              | Conditions                                               | Min | Typ        | Max | Units    |

|------------|--------------------------------------------------------|----------------------------------------------------------|-----|------------|-----|----------|

| $V_{IN}$   | Input Voltage Range                                    | (Note 3)                                                 | 4.5 | 60         |     | V        |

| $V_{OUT}$  | Output Voltage Range                                   | (Note 4)                                                 | 0.5 | 14         |     | V        |

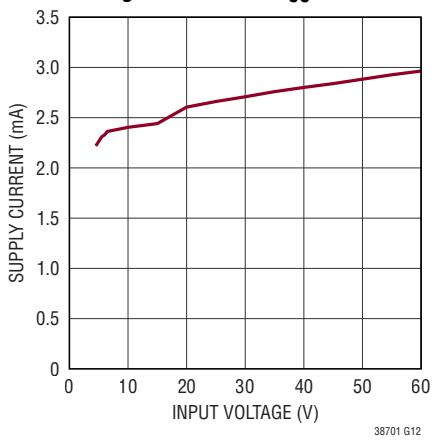

| $I_Q$      | Input Voltage Supply Current<br>Normal Operation       | $V_{RUN0}, V_{RUN1} = 0V$<br>$V_{RUN0}, V_{RUN1} = 3.3V$ |     | 1.1<br>2.6 |     | mA<br>mA |

| $V_{UVLO}$ | Undervoltage Lockout Threshold<br>when $V_{IN} > 4.2V$ | $V_{INTVCC}$ Falling<br>$V_{INTVCC}$ Rising              |     | 3.7<br>4.0 |     | V<br>V   |

---

## CONTROL LOOP

|                                                |                             |                                |   |           |         |         |

|------------------------------------------------|-----------------------------|--------------------------------|---|-----------|---------|---------|

| $I_{\text{SENSE}0+}$ ,<br>$I_{\text{SENSE}1+}$ | Current Sense + Pin Current | $V_{\text{ISENSE}0,1+} = 3.3V$ | ● | $\pm 0.1$ | $\pm 1$ | $\mu A$ |

| $I_{\text{SENSE}0-}$ ,<br>$I_{\text{SENSE}1-}$ | Current Sense – Pin Current | $V_{\text{ISENSE}0,1-} = 3.3V$ | ● | $\pm 0.1$ | $\pm 1$ | $\mu A$ |

**ELECTRICAL CHARACTERISTICS**

The ● denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^\circ\text{C}$ . (Note 2)  $V_{IN} = 15\text{V}$ ,  $V_{RUN0}, V_{RUN1} = 3.3\text{V}$ ,  $f_{SYNC} = 350\text{kHz}$  (externally driven) unless otherwise specified.

| SYMBOL                                                      | PARAMETER                                                                                | CONDITIONS                                                                                                      | MIN    | TYP                    | MAX      | UNITS                    |

|-------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|------------------------|----------|--------------------------|

| $V_{ILIMIT}$                                                | Maximum Current Sense Threshold (High Range)                                             | $V_{ITH} = 2.22\text{V}$ , $I_{LIM} = \text{INTV}_{CC}$                                                         | ●      | 70                     | 75       | 80                       |

|                                                             | Maximum Current Sense Threshold (Low Range)                                              | $V_{ITH} = 2.22\text{V}$ , $I_{LIM} = \text{GND}$                                                               | ●      | 45                     | 50       | 55                       |

| <b>PWM Outputs</b>                                          |                                                                                          |                                                                                                                 |        |                        |          |                          |

| PWM                                                         | PWM Output High Voltage<br>PWM Output Low Voltage<br>PWM Output Current in Hi-Z State    | $I_{LOAD} = 500\mu\text{A}$<br>$I_{LOAD} = -500\mu\text{A}$                                                     | ●<br>● | $V_{CC} - 0.2$<br>-5   | 0.2<br>5 | V<br>V<br>$\mu\text{A}$  |

| $t_{ON(MIN)}$                                               | Minimum On-Time                                                                          | (Note 5)                                                                                                        |        | 90                     |          | ns                       |

| <b>INTV<sub>CC</sub> Regulator</b>                          |                                                                                          |                                                                                                                 |        |                        |          |                          |

| $V_{INTVCC\_VIN}$                                           | Internal $V_{CC}$ Voltage No Load                                                        | $6.0\text{V} < V_{IN} < 60\text{V}$ , $V_{EXTVCC} = 0\text{V}$                                                  |        | 4.85                   | 5.1      | 5.35                     |

| $V_{LDO\_INT}$                                              | INTV <sub>CC</sub> Load Regulation                                                       | $I_{CC} = 0\text{mA}$ to $50\text{mA}$ , $V_{EXTVCC} = 0\text{V}$                                               |        | 0.8                    | $\pm 2$  | %                        |

| $V_{INTVCC\_EXT}$                                           | Internal $V_{CC}$ Voltage No Load                                                        | $V_{EXTVCC} = 8.5\text{V}$ (Note 6)                                                                             |        | 4.85                   | 5.1      | 5.35                     |

| $V_{LDO\_EXT}$                                              | EXTV <sub>CC</sub> Load Regulation                                                       | $I_{CC} = 0\text{mA}$ to $20\text{mA}$ , $V_{EXTVCC} = 8.5\text{V}$                                             |        | 0.5                    | $\pm 2$  | %                        |

| $V_{EXTVCC}$                                                | EXTV <sub>CC</sub> Switchover Voltage                                                    | $V_{EXTVCC}$ Ramping Positive (Note 6)                                                                          |        | 4.65                   | 4.8      | 4.95                     |

| $V_{HYS\_EXTVCC}$                                           | EXTV <sub>CC</sub> Hysteresis                                                            |                                                                                                                 |        | 200                    |          | mV                       |

| <b>Oscillator and Phase-Locked Loop</b>                     |                                                                                          |                                                                                                                 |        |                        |          |                          |

| $f_{SYNC}$                                                  | Oscillator SYNC Range                                                                    |                                                                                                                 | ●      | 100                    | 1000     | kHz                      |

| $V_{TH,SYNC}$                                               | SYNC Input Threshold                                                                     | $V_{TH,SYNC}$ Falling (Note 7)<br>$V_{TH,SYNC}$ Rising                                                          |        | 0.4<br>2.0             |          | V<br>V                   |

| $f_{NOM}$                                                   | Nominal Frequency                                                                        | $V_{FREQ} = 1.0\text{V}$                                                                                        |        | 500                    |          | kHz                      |

| $I_{FREQ}$                                                  | FREQ Setting Current                                                                     |                                                                                                                 |        | 9                      | 10       | 11                       |

| $\theta_{SYNC-\theta_0}$                                    | SYNC to Ch0 Phase Relationship Based on the Falling Edge of SYNC and Rising Edge of PWM0 | PHASMD = 0<br>PHASMD = 1/3 INTV <sub>CC</sub><br>PHASMD = 2/3 INTV <sub>CC</sub><br>PHASMD = INTV <sub>CC</sub> |        | 180<br>60<br>120<br>90 |          | Deg<br>Deg<br>Deg<br>Deg |

| $\theta_{SYNC-\theta_1}$                                    | SYNC to Ch1 Phase Relationship Based on the Falling Edge of SYNC and Rising Edge of PWM1 | PHASMD = 0<br>PHASMD = 1/3 INTV <sub>CC</sub><br>PHASMD = 2/3 INTV <sub>CC</sub><br>PHASMD = INTV <sub>CC</sub> |        | 0<br>300<br>240<br>270 |          | Deg<br>Deg<br>Deg<br>Deg |

| <b>Digital Inputs RUN0/RUN1, MODE0/MODE1, FAULT0/FAULT1</b> |                                                                                          |                                                                                                                 |        |                        |          |                          |

| $V_{IH}$                                                    | Input High Threshold Voltage                                                             |                                                                                                                 | ●      | 2.0                    |          | V                        |

| $V_{IL}$                                                    | Input Low Threshold Voltage                                                              |                                                                                                                 | ●      | 1.4                    |          | V                        |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3870-1 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3870E-1 is guaranteed to meet specifications from  $0^\circ\text{C}$  to  $85^\circ\text{C}$  junction temperature. Specifications over the  $-40^\circ\text{C}$  to  $125^\circ\text{C}$  operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3870I-1 is guaranteed over the full  $-40^\circ\text{C}$  to  $125^\circ\text{C}$  operating junction temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the related package thermal

impedance and other environmental factors. The junction temperature  $T_J$  is calculated from the ambient temperature  $T_A$  and power dissipation  $P_D$  according to the following formula:

$$T_J = T_A + (P_D \cdot 46.9^\circ\text{C/W})$$

**Note 3:** When  $V_{IN} > 15\text{V}$ , EXTV<sub>CC</sub> is recommended to reduce IC Temperature.

**Note 4:** Output voltage is set and controlled by the master controller in multiphase operations.

**Note 5:** The minimum on-time condition corresponds to an inductor peak-to-peak ripple current  $\geq 40\%$  of  $I_{MAX}$  (see Minimum On-Time Considerations in the Applications Information section).

**Note 6:** EXTV<sub>CC</sub> is enabled only if  $V_{IN}$  is higher than  $6.5\text{V}$ .

**Note 7:** Guaranteed by design.

# LTC3870-1

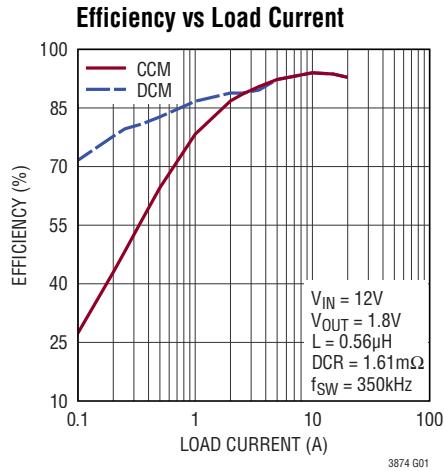

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

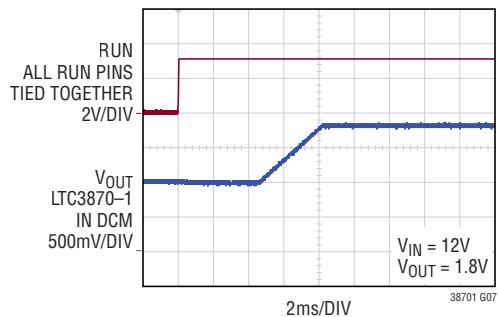

### Start-Up into a Pre-Biased Load 2-Phase Operation LTC3887-1 and LTC3870-1

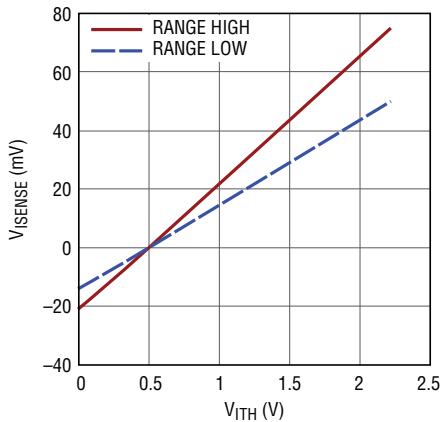

### Current Sense Threshold vs $I_{TH}$ Voltage

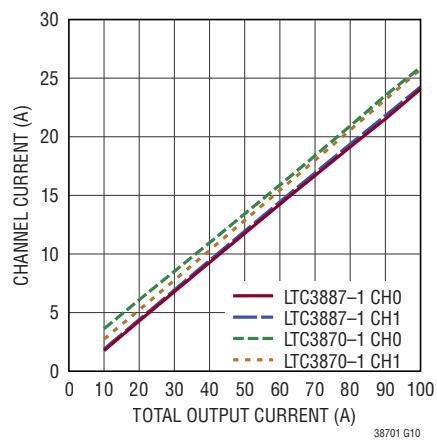

### DC Output Current Matching in a 4-Phase Operation LTC3887-1 and LTC3870-1

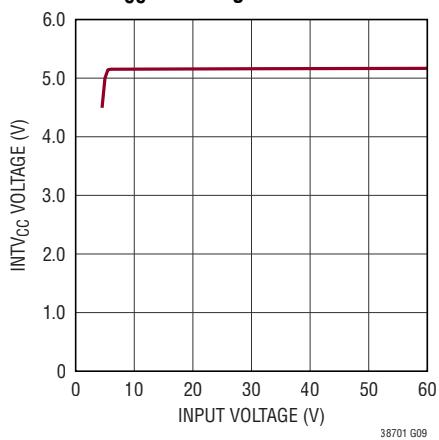

### INTV<sub>CC</sub> Line Regulation

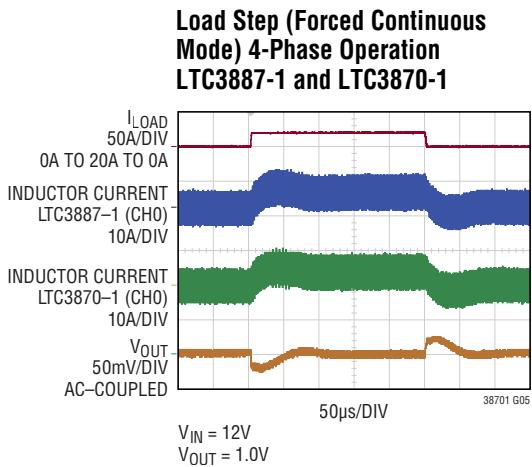

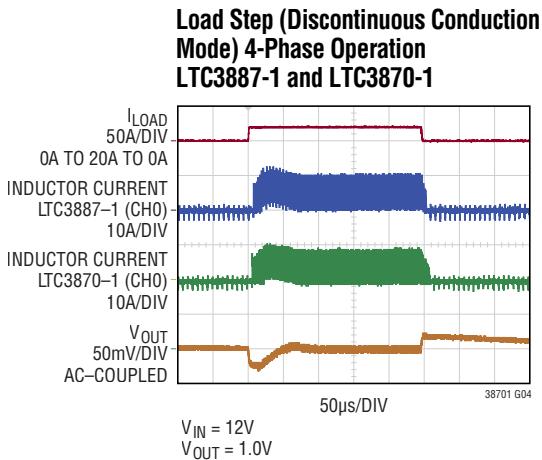

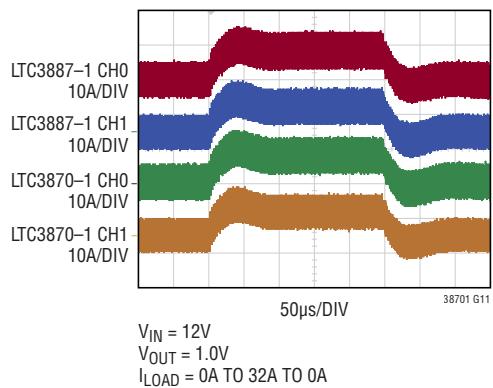

### Dynamic Current Sharing During a Load Transient in a 4-Phase System LTC3887-1 and LTC3870-1

$V_{IN} = 12V$

$V_{OUT} = 1.0V$

$I_{LOAD} = 0A \text{ TO } 32A \text{ TO } 0A$

### Quiescent Current vs Input Voltage without EXTV<sub>CC</sub>

38701f

## PIN FUNCTIONS

**$I_{SENSE0+}/I_{SENSE1+}$  (Pin 1/Pin 6):** Current Sense Comparator positive inputs, normally connected to the positive node of the DCR sensing networks or current sensing resistors.

**$I_{SENSE0-}/I_{SENSE1-}$  (Pin 2/Pin 5):** Current Sense Comparator negative inputs, normally connected to the negative node of the DCR sensing network or current sensing resistors.

**RUN0/RUN1 (Pin 3/Pin 4):** Enable Run Input Pins. A logic high on these pins enables the corresponding channel. In multiphase operation, these pins are connected to LTC3887-1's RUN pins.

**MODE0/MODE1 (Pin 24/Pin 7):** DCM/CCM Mode Control Pins. Channel0/Channel1 operate in forced continuous mode if MODE0/MODE1 pin is logic high. There is a  $500\text{k}\Omega$  pull-down resistor on MODE0/MODE1 internally. The default operation mode in each channel is discontinuous mode operation unless these pins are actively driven high.

**$I_{TH0}/I_{TH1}$  (Pin 23/Pin 8):** Current Control Threshold. Each associated channel's current comparator tripping threshold increases with its  $I_{TH}$  voltage. In multiphase operation, these pins are connected to the master controller's  $I_{TH}$  pins for current sharing.

**$I_{LIM}$  (Pin 9):** Programs Current Comparators' Sense Voltage Range. This pin can be tied to GND or INTV<sub>CC</sub> to select the maximum current sense threshold for each current comparator. GND sets both channels' current low range with maximum 50mV sensing voltage. INTV<sub>CC</sub> sets both channels' current high range with maximum 75mV sensing voltage. For equal current sharing, the setup on the  $I_{LIM}$  pin has to be same as the setup on the bit 7 of MFR\_PWM\_MODE\_3887-1 register in the master controller. See Table 2 in the Operation Section for details.

**SYNC (Pin 10):** External Clock Synchronization Input. If an external clock is present at this pin, the switching frequency will be synchronized to the falling edge of the external clock. In multiphase operation, this pin is connected to LTC3887-1 SYNC pin for frequency synchronization. Do not float the SYNC Pin.

**PHASMD (Pin 11):** Phase Set Pin. This pin can be tied to GND, INTV<sub>CC</sub> or a resistor divider from INTV<sub>CC</sub> to GND. This pin determines the relative phases between the external clock on the SYNC pin and the internal controllers. See Table 1 in the Operation Section for details.

**PWM0/PWM1 (Pin 19/Pin 12):** (Top) Gate Signal Outputs. This signal goes to the PWM or top gate input of the external driver, integrated driver MOSFET or Power Block. This is a three-state compatible output. To support three-state mode, an external resistive divider is typically used from  $V_{CC0}/V_{CC1}$  to ground.

**$V_{CC0}/V_{CC1}$  (Pin 18/Pin 13):** PWM Pin Driver Supplies. Decouple these pins to GND with a capacitor (0.1 $\mu\text{F}$ ) or tie these pins to the INTV<sub>CC</sub> pin. PWM0/PWM1 signal swing is from ground to  $V_{CC0}/V_{CC1}$ .

**INTV<sub>CC</sub> (Pin 14):** Internal Regulator 5V Output. The internal control circuits are powered from this voltage. Bypass this pin to GND with a minimum of 4.7 $\mu\text{F}$  low ESR tantalum or ceramic capacitor. INTV<sub>CC</sub> is enabled as soon as  $V_{IN}$  is powered. The INTV<sub>CC</sub> pin is not short circuit proof. If overloaded, this will disrupt internal operation that can damage the part.

**EXTV<sub>CC</sub> (Pin 15):** External power input to an internal LDO connected to INTV<sub>CC</sub>. This LDO supplies INTV<sub>CC</sub> power bypassing the internal LDO powered from  $V_{IN}$  whenever EXTV<sub>CC</sub> is higher than 4.8V. See EXTV<sub>CC</sub> connection in the Applications Information Section. Do not exceed 14V on this pin. Bypass this pin to GND with a minimum of 4.7 $\mu\text{F}$  low ESR tantalum or ceramic capacitor. If the EXTV<sub>CC</sub> pin is not used, leave it open or tie it to ground. EXTV<sub>CC</sub> can be present before  $V_{IN}$ . However, EXTV<sub>CC</sub> is enabled only if  $V_{IN}$  is higher than 6.5V.

**GND (Pin 16/Exposed Pad Pin 25):** Signal ground. All small-signal and compensation components should connect to this ground. The exposed pad must be soldered

## PIN FUNCTIONS

to the PCB ground for electrical connection and rated thermal performance.

**V<sub>IN</sub> (Pin 17):** Main Input Supply. Bypass this pin to GND with a capacitor (0.1µF to 1µF).

**FAULT0/FAULT1 (Pin 21/Pin 20):** Fault Input Pins. Connect these pins to the master chip GPIO pins to respond to fault signals from the master controller. If this pin is low, the PWM pin is in three-state. There is a 500kΩ pull-down

resistor on FAULT0/FAULT1 internally. These pins have to be driven high externally for normal operation.

**FREQ (Pin 22):** Frequency Set Pin. There is a precision 10µA current flowing out of this pin. A resistor to ground sets a voltage which in turn programs the frequency. This pin sets the default switching frequency when there is no external clock on the SYNC pin. Setting the frequency close to the external clock helps the internal PLL sync to the SYNC pin clock quickly and smoothly. See the Application Section for the detailed information.

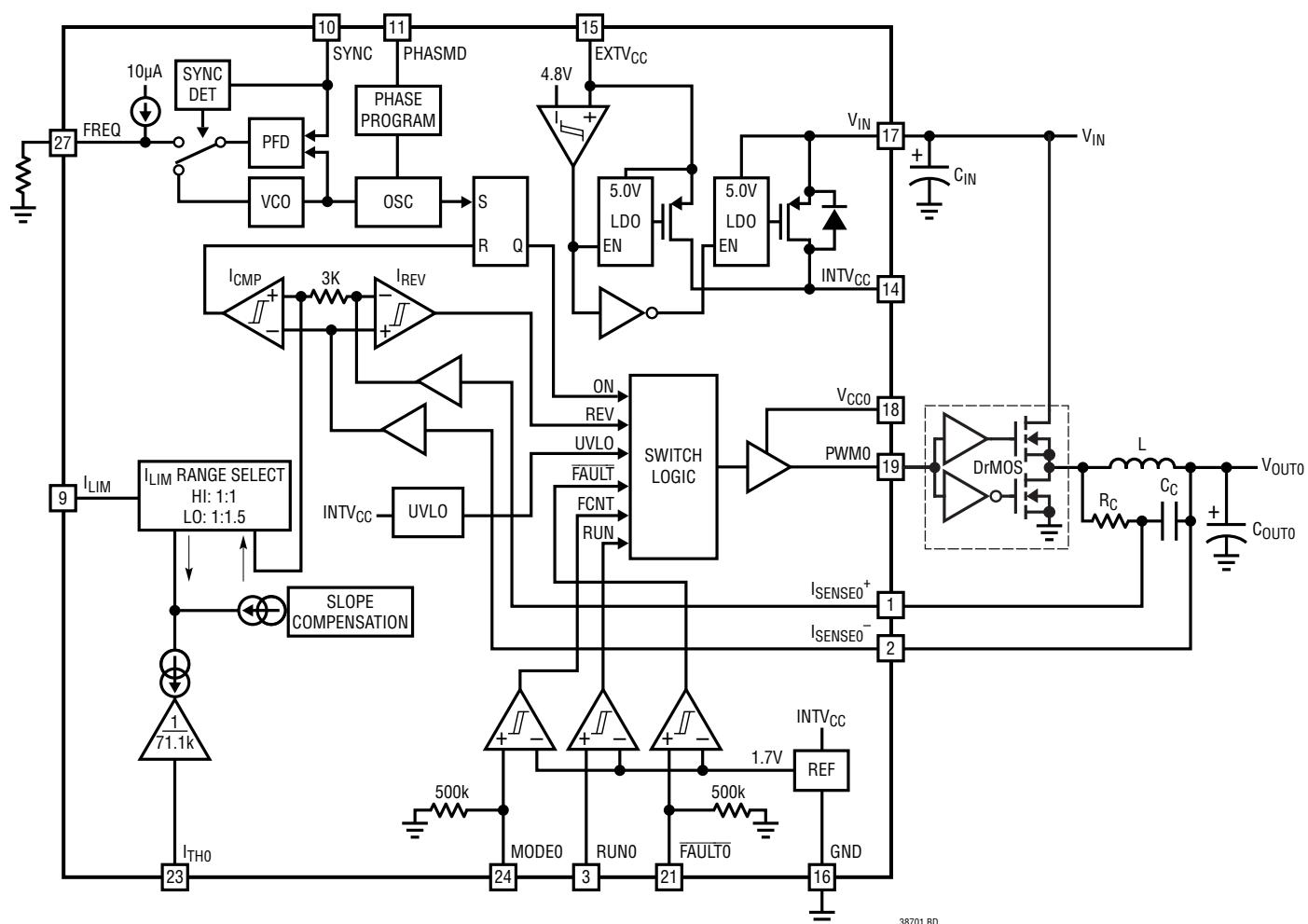

## BLOCK DIAGRAM (CH0 Shown)

38701 BD

## OPERATION

### Main Control Loop

The LTC3870-1 is a constant frequency, current mode step-down slave controller for parallel operation with the LTC3887-1. During normal operation, each top MOSFET is turned on when the clock for that channel sets the RS latch, and turned off when the main current comparator,  $I_{CMP}$ , resets the RS latch. The peak inductor current at which  $I_{CMP}$  resets the RS latch is controlled by the voltage on the  $I_{TH}$  pin, which is tied directly to the corresponding  $I_{TH}$  pin of the master controllers (LTC3887-1). When the load current increases, LTC3887-1 master controllers drive and increase the  $I_{TH}$  voltage, which in turn causes the peak current in the corresponding slave channels to increase, until the average inductor current matches the new load current. After the top MOSFET has been turned off, the bottom MOSFET is turned on until the beginning of the next cycle in Continuous Conduction Mode (CCM) or until the inductor current starts to reverse, as indicated by the reverse current comparator  $I_{REV}$ , in Discontinuous Conduction Mode (DCM). LTC3870-1 slave controllers DO NOT regulate the output voltage but regulate the current in each channel for current sharing with master controllers. Output voltage regulation is achieved through the voltage feedback loops in the master controller.

### INTV<sub>CC</sub>/EXTV<sub>CC</sub> Power

Power for most internal circuitry is derived from the INTV<sub>CC</sub> pin. Normally an internal 5.0V linear regulator supplies INTV<sub>CC</sub> power from  $V_{IN}$ . In high  $V_{IN}$  applications, if a high efficiency external voltage source is available for the EXTV<sub>CC</sub> pin, another internal 5.0V linear regulator is enabled and supplies INTV<sub>CC</sub> power from EXTV<sub>CC</sub>. To enable the linear regulator driven by the EXTV<sub>CC</sub> pin,  $V_{IN}$  needs to be higher than 6.5V and EXTV<sub>CC</sub> pin voltage has to be higher than 4.8V. Do not exceed 14V on the EXTV<sub>CC</sub> pin.

### Start-Up and Shutdown (RUN0, RUN1)

The two channels of the LTC3870-1 can independently start up and shut down using the RUN0 and RUN1 pins. Pulling either of these pins below 1.4V shuts down the control circuits for that channel. During shutdown, the PWM pin is in three-state mode. Pulling either of these pins above 2V enables the corresponding channel and internal circuits. During startup, the RUN0/RUN1 pins are actively pulled down until the INTV<sub>CC</sub> voltage passes the undervoltage lockout threshold of 4V. For multiphase parallel operation, the RUN0/RUN1 pins have to be connected and driven by the RUN pins of the master controller. Do not exceed the Absolute Maximum Rating of 6V on these pins.

The start-up of each channel's output voltage  $V_{OUT}$  is controlled and programmed by the master controller. After the RUN pins are released, the master controller drives the output based on the programmed delay time and rise time, and the slave controller LTC3870-1 just follows the master to supply equivalent current to the output during start-up.

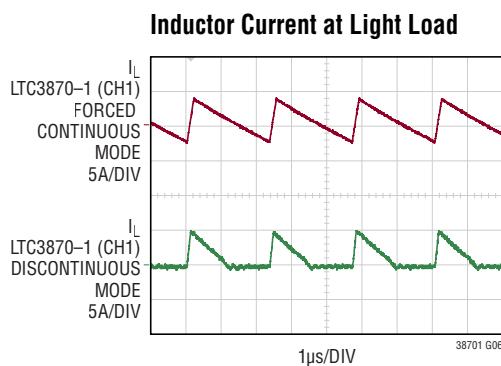

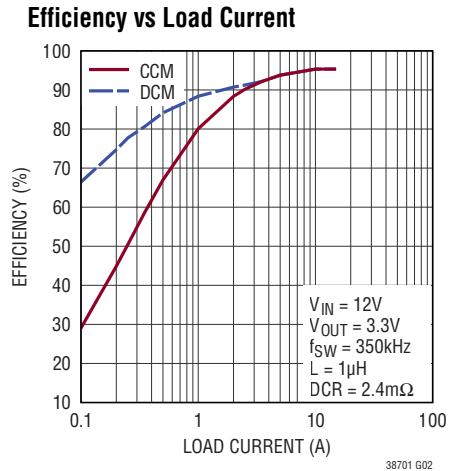

### Light Load Current Operation (Discontinuous Conduction Mode, Continuous Conduction Mode)

The LTC3870-1 can be set to operate either in Discontinuous Conduction Mode (DCM) or forced Continuous Conduction Mode (CCM). To select forced Continuous Mode of operation, tie the MODE pin to a DC voltage above 2V (e.g., INTV<sub>CC</sub>). To select Discontinuous Conduction Mode of operation, tie the MODE pin to a DC voltage below 1.4V (e.g., SGND). In forced continuous operation, the inductor current is allowed to reverse at light loads or under large transient conditions. The peak inductor current is determined by the voltage on the  $I_{TH}$  pin. In this mode, the efficiency at light loads is lower than in discontinuous mode operation. However, continuous mode has the advantages of lower output ripple and less interference with audio circuitry. When the MODE pin is connected to

## OPERATION

GND, the LTC3870-1 operates in discontinuous mode at light loads. At very light loads, the current comparator  $I_{CMP}$  may remain tripped for several cycles and force the external top MOSFET to stay off for the same number of cycles (i.e., skipping pulses). This mode provides higher light load efficiency than forced continuous mode and the inductor current is not allowed to reverse. There are  $500\text{k}\Omega$  pull-down resistors internally connected to the MODE0/MODE1 pins. If MODE0/MODE1 pins are floating, both channels default to Discontinuous Conduction Mode.

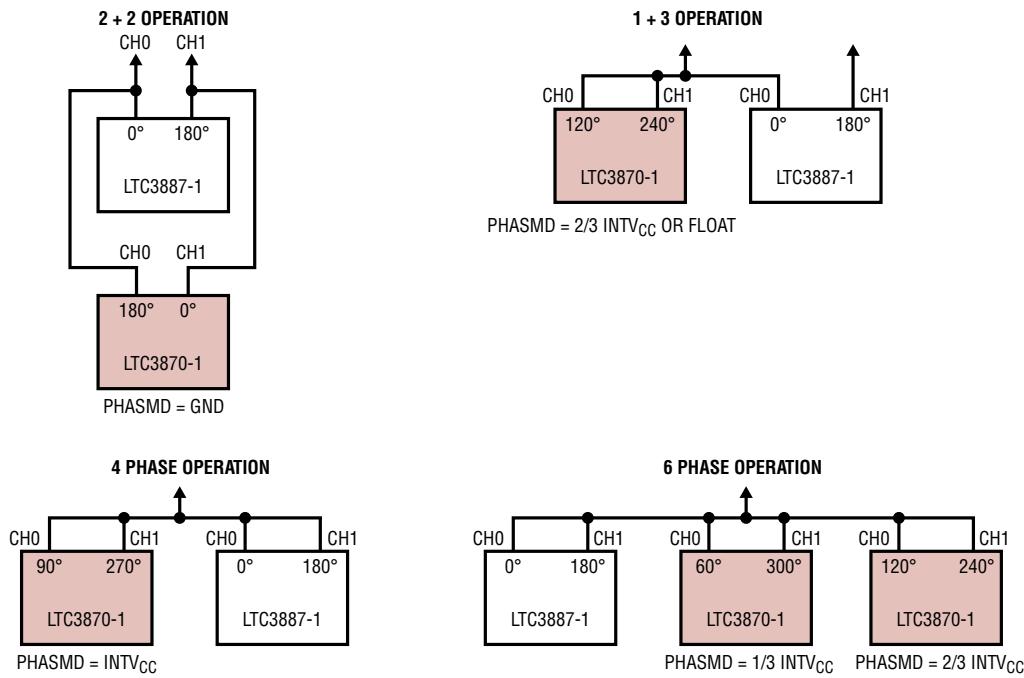

### Multichip Operation (PHASMD and SYNC Pins)

The PHASMD pin determines the relative phases between the internal channels as well as the external clock signal on the SYNC pin, as shown in Table 1. The phases tabulated are relative to zero degree phase being defined as the **falling edge** of the clock on SYNC.

Table 1.

| PHASMD                                  | Channel 0 Phase | Channel 1 Phase |

|-----------------------------------------|-----------------|-----------------|

| GND                                     | $180^\circ$     | $0^\circ$       |

| $1/3 \text{ INTV}_{\text{CC}}$          | $60^\circ$      | $300^\circ$     |

| $2/3 \text{ INTV}_{\text{CC}}$ or Float | $120^\circ$     | $240^\circ$     |

| $\text{INTV}_{\text{CC}}$               | $90^\circ$      | $270^\circ$     |

The SYNC pin is used to synchronize switching frequency between master and slave controllers. Input capacitance ESR requirements and efficiency losses are substantially reduced because the peak current drawn from the input capacitor is effectively divided by the number of phases used and power loss is proportional to the RMS current squared. A two-phase, single output voltage implementation can reduce input path power loss by 75% and radically reduce the required RMS current rating of the input capacitor(s).

### Single Output Multiphase Operation

The LTC3870-1 is designed for multiphase converters with the LTC3887-1 by making these connections:

- Tie all the  $I_{TH}$  pins of paralleled channels together for current sharing between masters and slaves. Note that  $I_{LIM}$  setup on slaves has to match MFR\_PWM\_MODE current range setup in masters.

- Tie all SYNC pins together between master and slaves for same switching frequency synchronization; one and only one of the LTC3887-1 controllers has to be programmed as master to generate clock signal on the SYNC pin.

- Tie all the RUN pins of paralleled channels together between master and slaves for startup and shutdown sequences.

- Tie the  $\overline{\text{GPIO}}$  pin of the master controller to the  $\overline{\text{FAULT}}$  pin of slave controller and program the master  $\overline{\text{GPIO}}$  as fault sharing for fault protection.

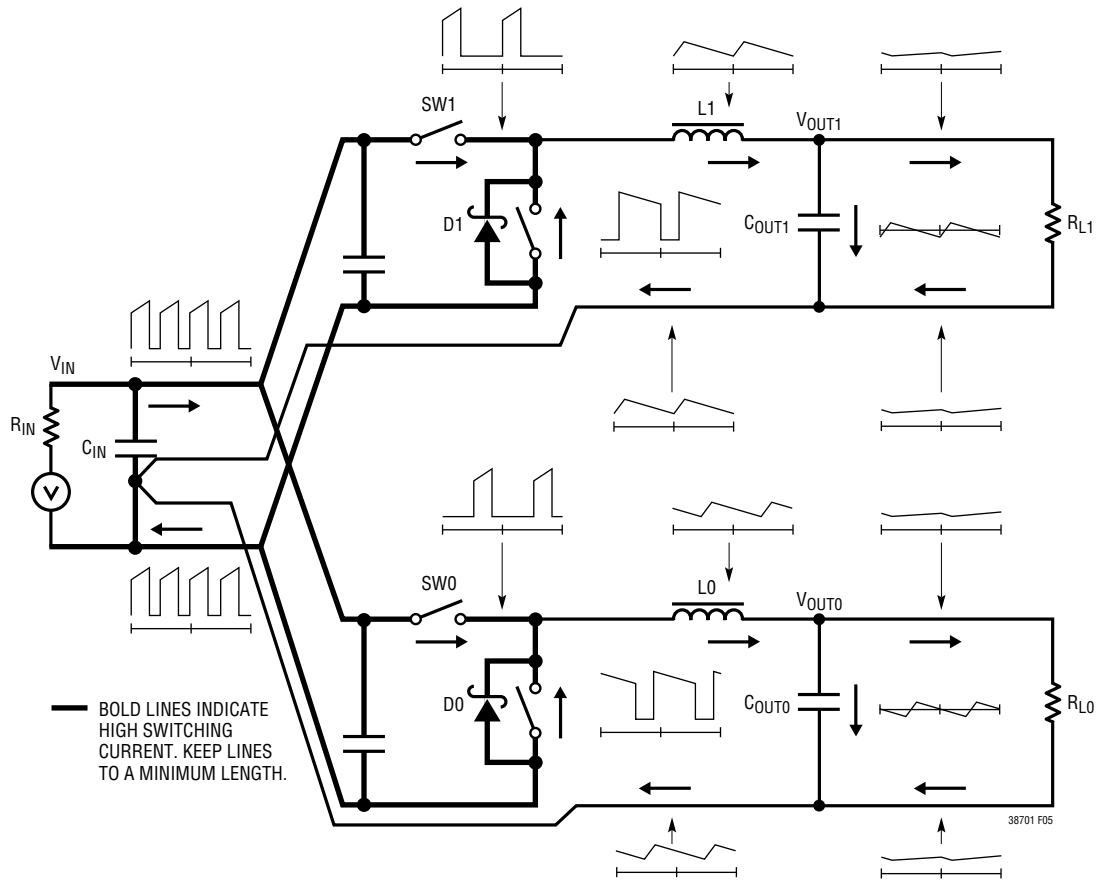

Examples of single output multiphase converters are shown in Figure 1.

### Inductor Current Sensing

Like the LTC3887-1, the LTC3870-1 can use either inductor DCR or  $R_{SENSE}$  to sense the inductor current. Inductor DCR current sensing provides a lossless method of sensing the instantaneous current. Therefore, it can provide higher efficiency for applications with high output currents. However, the DCR of a copper inductor typically has 10% tolerance. For precise current sensing, a precision sensing resistor  $R_{SENSE}$  can be used to sense the inductor current. It is important to match the current sensing circuit between master controllers and slave controllers to guarantee balanced load sharing and overcurrent protection.

# LTC3870-1

## OPERATION

Figure 1. Examples of Single/Dual Output Multiphase Converters

### Frequency Selection and Phase-Locked Loop (FREQ and SYNC Pins)

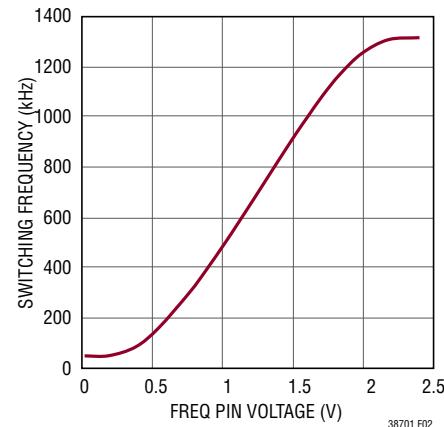

The selection of switching frequency is a trade-off between efficiency and component size. Low frequency operation increases efficiency by reducing MOSFET switching losses, but requires larger inductance and/or capacitance to maintain low output ripple voltage. The switching frequency of the LTC3870-1 controllers can be synchronized to the falling edge of the external clock on the SYNC pin or selected using the FREQ pin. A phase-locked loop (PLL) is integrated in the LTC3870-1 to synchronize the internal oscillator to an external clock source that is connected to the SYNC pin; this source is normally provided by the master controllers. The PLL loop filter network is

integrated inside the LTC3870-1. The phase-locked loop is capable of locking to any frequency within the range of 100kHz to 1MHz.

If the SYNC pin is not being driven by an external clock source, the FREQ pin can be used to program the LTC3870-1's operating frequency from 100kHz to 1MHz. There is a precision 10 $\mu$ A current flowing out of the FREQ pin, so the user can program the controller's switching frequency with a single resistor to SGND. A curve is provided later in the application section showing the relationship between the voltage on the FREQ pin and switching frequency. The frequency setting resistor should always be present to set the controller's initial switching frequency before locking to the external clock.

## APPLICATIONS INFORMATION

The Typical Application on the first page of this data sheet is a basic LTC3870-1 application circuit featuring the LTC3887-1 as a slave controller. In paralleled operation, the current sensing scheme as well as the power stage parameters in LTC3870-1 must be the same as the master controller to achieve balanced current sharing between masters and slaves. Finally, input and output capacitors are selected based on RMS current rating, ripple, and transient specs.

### Current Limit Programming

To match the master controller current limit, each channel of the LTC3870-1 can be programmed separately with two current ranges. The  $I_{LIM}$  pin of LTC3870-1 is a 4-level logic input which sets the current limit of LTC3870-1. When  $I_{LIM}$  is grounded, both channel0 and channel1 are set to be low current range. When  $I_{LIM}$  is tied to  $INTV_{CC}$ , both channel0 and channel1 are set to be high current range. Here, low current range means the current sense threshold linearly increases from 0mV to 50mV as  $I_{TH}$  voltage is increased from 0.5V to 2.22V without slope compensation. High current range means the current sense threshold increases to 75mV as  $I_{TH}$  voltage is increased to 2.22V without slope compensation. Set  $I_{LIM}$  to one-third  $INTV_{CC}$  for channel0 high current range and channel1 low current range. Set  $I_{LIM}$  to two-thirds  $INTV_{CC}$  or float for channel0 low current range and channel1 high current range. The summary of  $I_{LIM}$  pin setups is shown in Table 2. For balanced load current sharing, use the same current range setting as in the master controller. Note that the LTC3870-1 does not have active clamping circuit on the  $I_{TH}$  pin for peak current limit and over current protection. Over current protection relies on the master controller to drive and clamp the  $I_{TH}$  pin voltage not to exceed the programmed voltage through the PMBus command.

Table 2. Current Limit Programming

| $I_{LIM}$                | Channel 0<br>Current limit | Channel 1<br>Current limit |

|--------------------------|----------------------------|----------------------------|

| GND                      | Range Low                  | Range Low                  |

| 1/3 $INTV_{CC}$          | Range High                 | Range Low                  |

| 2/3 $INTV_{CC}$ or Float | Range Low                  | Range High                 |

| $INTV_{CC}$              | Range High                 | Range High                 |

### $INTV_{CC}$ Regulators and $EXTV_{CC}$

The LTC3870-1 includes a PMOS LDO that supplies power to  $INTV_{CC}$  from the  $V_{IN}$  supply.  $INTV_{CC}$  powers most of the LTC3870-1's internal circuitry. The linear regulator regulates the voltage at the  $INTV_{CC}$  pin to 5.0V when  $V_{IN}$  is greater than 6V.  $EXTV_{CC}$  connects to  $INTV_{CC}$  through another PMOS LDO and can supply the needed power when its voltage is higher than 4.8V and  $V_{IN}$  is higher than 6.5V. Each of these LDOs can supply a peak current of 100mA and must be bypassed to ground with a minimum of 4.7 $\mu$ F ceramic capacitor or low ESR electrolytic capacitor. No matter what type of bulk capacitor is used, an additional 0.1 $\mu$ F ceramic capacitor placed directly adjacent to the  $INTV_{CC}$  and PGND pins is highly recommended. Good bypassing is needed to prevent interaction between the channels.

The  $INTV_{CC}$  pin is not short-circuit proof. If overloaded, this will disrupt internal operation that can damage the part.

When the voltage applied to  $EXTV_{CC}$  rises above 4.8V and  $V_{IN}$  above 6.5V, the  $INTV_{CC}$  linear regulator is turned off and the  $EXTV_{CC}$  linear regulator is turned on. Using the  $EXTV_{CC}$  allows the control power to be derived from other high efficiency sources such as +5V or +12V rails in the system. Do not apply more than 14V to the  $EXTV_{CC}$  pin.

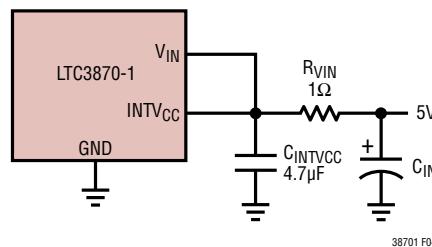

For applications where the main input power is 5V, tie the  $V_{IN}$  and  $INTV_{CC}$  pins together and tie the combined pins to the 5V input with a 1 $\Omega$  or 2.2 $\Omega$  resistor as shown in Figure 2 to minimize the voltage drop. This will override the  $INTV_{CC}$  linear regulator and will prevent  $INTV_{CC}$  from dropping too low due to the dropout voltage. Make sure the  $INTV_{CC}$  voltage is at or exceeds the  $R_{DS(ON)}$  test voltage for the external power MOSFETs which is typically 4.5V for logic-level devices.

Figure 2. Setup for a 5V Input

## APPLICATIONS INFORMATION

### Undervoltage Lockout

The LTC3870-1 has a precision UVLO comparator constantly monitoring the  $\text{INTV}_{\text{CC}}$  voltage. It locks out the switching action and pulls down the RUN pins when  $\text{INTV}_{\text{CC}}$  is below 3.7V. To prevent oscillation when there is a disturbance on the  $\text{INTV}_{\text{CC}}$ , the UVLO comparator has 300mV of precision hysteresis. In multiphase operation, when LTC3870-1 is in undervoltage lockout, the RUN0 and RUN1 pins are pulled down to disable the master's switching action.

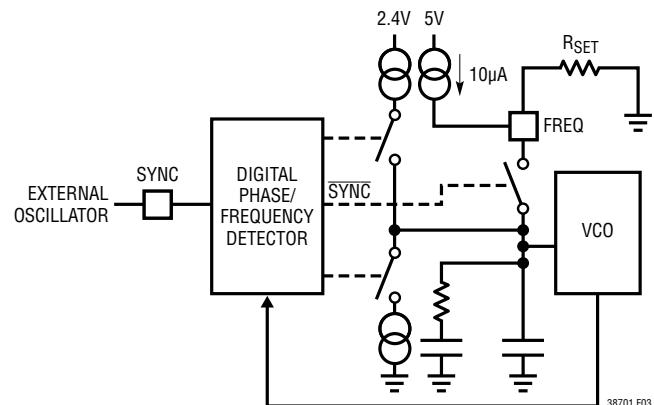

### Phase-Locked Loop and Frequency Synchronization

The LTC3870-1 has a phase-locked loop (PLL) comprised of an internal voltage-controlled oscillator (VCO) and a phase detector. This allows the internal clock to be locked to the falling edge of an external clock signal applied to the SYNC pin. The turn-on of channel 0/channel 1's top MOSFET is synchronized or out-of-phase with the falling edge of the external clock. The phase detector is an edge sensitive digital type that provides zero degree phase shift between the external and internal oscillators. This type of phase detector does not exhibit false lock to harmonics of the external clock.

The output of the phase detector is a pair of complementary current sources that charge or discharge the internal filter network. There is a precision  $10\mu\text{A}$  of current flowing out of the FREQ pin. This allows the user to use a single resistor to GND to set the switching frequency when no external clock is applied to the SYNC pin. The voltage on the FREQ pin is equal to the resistance multiplied by  $10\mu\text{A}$  current (e.g. the voltage is 1V with a 100k resistor from the FREQ pin to SGND). The internal switch between FREQ pin and the integrated PLL filter network is ON, allowing the filter network to be pre-charged to the same voltage potential as the FREQ pin. The relationship between the voltage on the FREQ pin and the operating frequency is shown in Figure 3 and specified in the Electrical Characteristics table. If an external clock is detected on the SYNC pin, the internal switch mentioned above will turn off and isolate the influence of FREQ pin. Note that the LTC3870-1 can only be synchronized to an external clock whose frequency is

Figure 3. Relationship Between Oscillator Frequency and Voltage at the FREQ Pin

Figure 4. Phase-Locked Loop Block Diagram

within the range of the LTC3870-1's internal VCO. This is guaranteed to be between 100kHz and 1MHz. A simplified block diagram is shown in Figure 4.

If the external clock frequency is greater than the internal oscillator's frequency,  $f_{\text{osc}}$ , then current is sourced continuously from the phase detector output, pulling up the filter network. When the external clock frequency is less than  $f_{\text{osc}}$ , current is sunk continuously, pulling down the filter network. If the external and internal frequencies are the same but exhibit a phase difference, the current sources turn on for an amount of time corresponding to

## APPLICATIONS INFORMATION

the phase difference. The voltage on the filter network is adjusted until the phase and frequency of the internal and external oscillators are identical. At the stable operating point, the phase detector output is high impedance and the filter capacitor holds the voltage.

Typically, the external clock (on the SYNC pin) input high threshold is 2V, while the input low threshold is 0.4V.

### Fault Protection and Responses

LTC3887-1 master controllers monitor system voltage, current, and temperature and provide many protection features during fault conditions. LTC3870-1 slave controllers do not provide as many fault monitors as master controllers and have to respond to fault signals from the master controller. FAULT0 and FAULT1 pins are designed to share fault signals between masters and slaves. In a typical parallel application, connect the FAULT pins on LTC3870-1 to the master GPIO pins of the corresponding paralleled channels and program the master GPIO as fault sharing, so that the slave controller can respond to all fault protections from the master. When the FAULT pin is pulled below 1.4V, the PWM pin in the corresponding channel is in three-state. When the FAULT pin voltage is above 2V, the corresponding channel returns to normal operation. During fault conditions, all internal circuits in LTC3870-1 are still running so the slave controllers can immediately go back to normal operation when the FAULT pin is released.

LTC3870-1 has internal thermal shutdown protection which forces the PWM pin three-state when the junction temperature is higher than 160°C. In thermal shutdown, FAULT0 and FAULT1 pins are also pulled low. There is a 500kΩ pull-down resistor on each FAULT pin which sets the default voltage on FAULT pins low if FAULT pins are left floating.

### Transient Response and Loop Stability

In a typical parallel operation, LTC3870-1 cooperates with master controllers to supply more current. To achieve

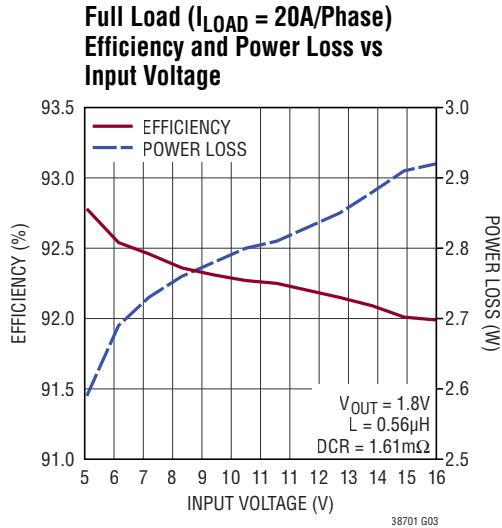

balanced current sharing between master and slave, it is recommended that each slave channel copy the design from the master channel. Select same inductors, same MOSFET driver, same current sensing circuit and same output capacitors between the master channel and slave channels. Control loop and compensation design on the  $I_{TH}$  pin should start with the single phase operation of the master controller. If the master and slave channels are exactly the same, then the transient response and loop stability of the multiphase design is almost the same as the single phase operation of the master by tying the  $I_{TH}$  pins together between the master and slaves. For example, design the compensation for a single phase 1.8V/20A output using LTC3887-1 with a 0.56μH inductor and 530μF output capacitors. To extend the output to 1.8V/40A, simply parallel one channel of LTC3870-1 with the same inductor and output capacitors (total output capacitors are 1060μF) and tie the  $I_{TH}$  pin of LTC3870-1 to the master  $I_{TH}$ . The loop stability and transient responses of the two phase converter are very similar to the single phase design without any extra compensator on the  $I_{TH}$  pin of LTC3870-1 slave controller. Furthermore, LTpowerCAD is provided on the LTC website as a free download for transient and stability analysis.

To minimize the high frequency noise on the  $I_{TH}$  trace between master and slave  $I_{TH}$  pins, a small filter capacitor in the range of tens of pF can be placed closely at each  $I_{TH}$  pin of the slave controller. This small capacitor normally does not significantly affect the closed loop bandwidth but increases the gain margin at high frequency.

### Mode Selection and Pre-Biased Startup

There may be situations that require the power supply to start up with a pre-bias on the output capacitors. In this case, it is desirable to start up without discharging the output capacitors. The LTC3870-1 can be configured to DCM mode for pre-biased start-up. If a PGOOD signal is available on the master controller, the PGOOD pin can be connected to MODE pins of LTC3870-1 to ensure DCM operation at startup and CCM operation at steady state.

## APPLICATIONS INFORMATION

### Minimum On-Time Considerations

Minimum on-time  $t_{ON(MIN)}$  is the smallest time duration that the LTC3870-1 is capable of turning on the top MOSFET. It is determined by internal timing delays and the gate charge required to turn on the top MOSFET. Low duty cycle applications may approach this minimum on-time limit and care should be taken to ensure that:

$$t_{ON(MIN)} < T_{SW} V_{OUT}/V_{IN}$$

where  $T_{SW}$  is the switching period.

If the duty cycle falls below what can be accommodated by the minimum on-time, the controller will begin to skip cycles. The output voltage will continue to be regulated, but the ripple voltage and current will increase. The minimum on-time for the LTC3870-1 is approximately 90ns, with reasonably good PCB layout, minimum 30% inductor current ripple and at least 10mV ripple on the current sense signal. The minimum on-time can be affected by PCB switching noise in the current loop. As the peak sense voltage decreases, the minimum on-time gradually increases to 130ns. This is of particular concern in forced continuous applications with low ripple current at light loads. If the duty cycle drops below the minimum on-time limit in this situation, a significant amount of cycle skipping can occur with correspondingly larger current and voltage ripple.

### PWM Pins

The PWM output pins are three-state compatible outputs, designed to drive MOSFET drivers, DrMOSs, etc. which do not represent a heavy capacitive load. An external resistor divider may be used to set the voltage to mid-rail while in the high impedance state.

The  $V_{CC}$  pin is the corresponding PWM pin driver supply. Decouple this pin to GND with a capacitor (0.1 $\mu$ F) or tie this pin to the  $INTV_{CC}$  pin.

### MOSFET Driver Selection

Gate driver ICs, DrMOSs and power blocks with an interface compatible with the LTC3870-1's three-state PWM outputs can be used.

### PC Board Layout Checklist

When laying out the printed circuit board, the following checklist should be used to ensure proper operation of the IC. Figure 5 illustrates the current waveforms present in the various branches of the 2-phase synchronous regulators operating in the continuous mode. Check the following in the PC layout:

1. Are the signal and power grounds kept separate? The combined IC signal ground pin and the ground return of  $C_{INTV_{CC}}$  must return to the combined  $C_{OUT}(-)$  terminals. The  $I_{TH}$  traces should be as short as possible. The  $C_{IN}$  capacitor should have short leads and PC trace lengths. The output capacitor (-) terminals should be connected as close as possible to the (-) terminals of the input capacitor by placing the capacitors next to each other.

2. Are the  $I_{SENSE}^+$  and  $I_{SENSE}^-$  leads routed together with minimum PC trace spacing? The filter capacitor between  $I_{SENSE}^+$  and  $I_{SENSE}^-$  should be as close as possible to the IC. Ensure accurate current sensing with Kelvin connections at the sense resistor or inductor, whichever is used for current sensing.

3. Is the  $INTV_{CC}$  bypassing capacitor connected close to the IC, between the  $INTV_{CC}$  and the ground pins? An additional 1 $\mu$ F ceramic capacitor placed immediately next to the  $INTV_{CC}$  and PGND pins can help improve noise performance substantially.

4. Keep the switching nodes (SW1, SW0), away from sensitive small-signal nodes, especially from the opposite channel's current sensing feedback pins. All of these nodes have very large and fast moving signals and therefore should be kept on the "output side" of the LTC3870-1 and occupy minimum PC trace area. If DCR sensing is used, place the right resistor (Block Diagram, " $R_C$ ") close to the switching node.

5. Use a modified "star ground" technique: a low impedance, large copper area central grounding point on the same side of the PC board as the input and output capacitors with tie-ins for the bottom of the  $INTV_{CC}$  bypassing capacitor, the bottom of the voltage feedback resistive divider and the GND pin of the IC.

## APPLICATIONS INFORMATION

### PC Board Layout Debugging

Start with one controller at a time. It is helpful to use a DC-50MHz current probe to monitor the current in the inductor while testing the circuit. Monitor the output switching node (SW pin) to synchronize the oscilloscope to the internal oscillator and probe the actual output voltage as well. Check for proper performance over the operating voltage and current range expected in the application. The frequency of operation should be maintained over the input voltage range down to dropout and until the output load drops below the low current operation threshold—typically 10% of the maximum designed current level in Burst Mode operation.

The duty cycle percentage should be maintained from cycle to cycle in a well-designed, low noise PCB implementation. Variation in the duty cycle at a sub-harmonic rate can suggest noise pickup at the current or voltage sensing inputs or inadequate loop compensation. Overcompensation of the loop can be used to tame a poor PC layout if regulator bandwidth optimization is not required. Only after each controller is checked for its individual performance should both controllers be turned on at the same time. A particularly difficult region of operation is when one controller channel is nearing its current comparator trip point when the other channel is turning on its top MOSFET. This occurs around 50% duty cycle on either channel due to the phasing of the internal clocks and may cause minor duty cycle jitter.

Reduce  $V_{IN}$  from its nominal level to verify operation of the regulator in dropout. Check the operation of the undervoltage lockout circuit by further lowering  $V_{IN}$  while monitoring the outputs to verify operation.

Investigate whether any problems exist only at higher output currents or only at higher input voltages. If problems coincide

with high input voltages and low output currents, look for capacitive coupling between the BOOST, SW, TG, and possibly BG connections and the sensitive voltage and current pins. The capacitor placed across the current sensing pins needs to be placed immediately adjacent to the pins of the IC. This capacitor helps to minimize the effects of differential noise injection due to high frequency capacitive coupling. If problems are encountered with high current output loading at lower input voltages, look for inductive coupling between  $C_{IN}$ , Schottky and the top MOSFET components to the sensitive current and voltage sensing traces. In addition, investigate common ground path voltage pickup between these components and the SGND pin of the IC.

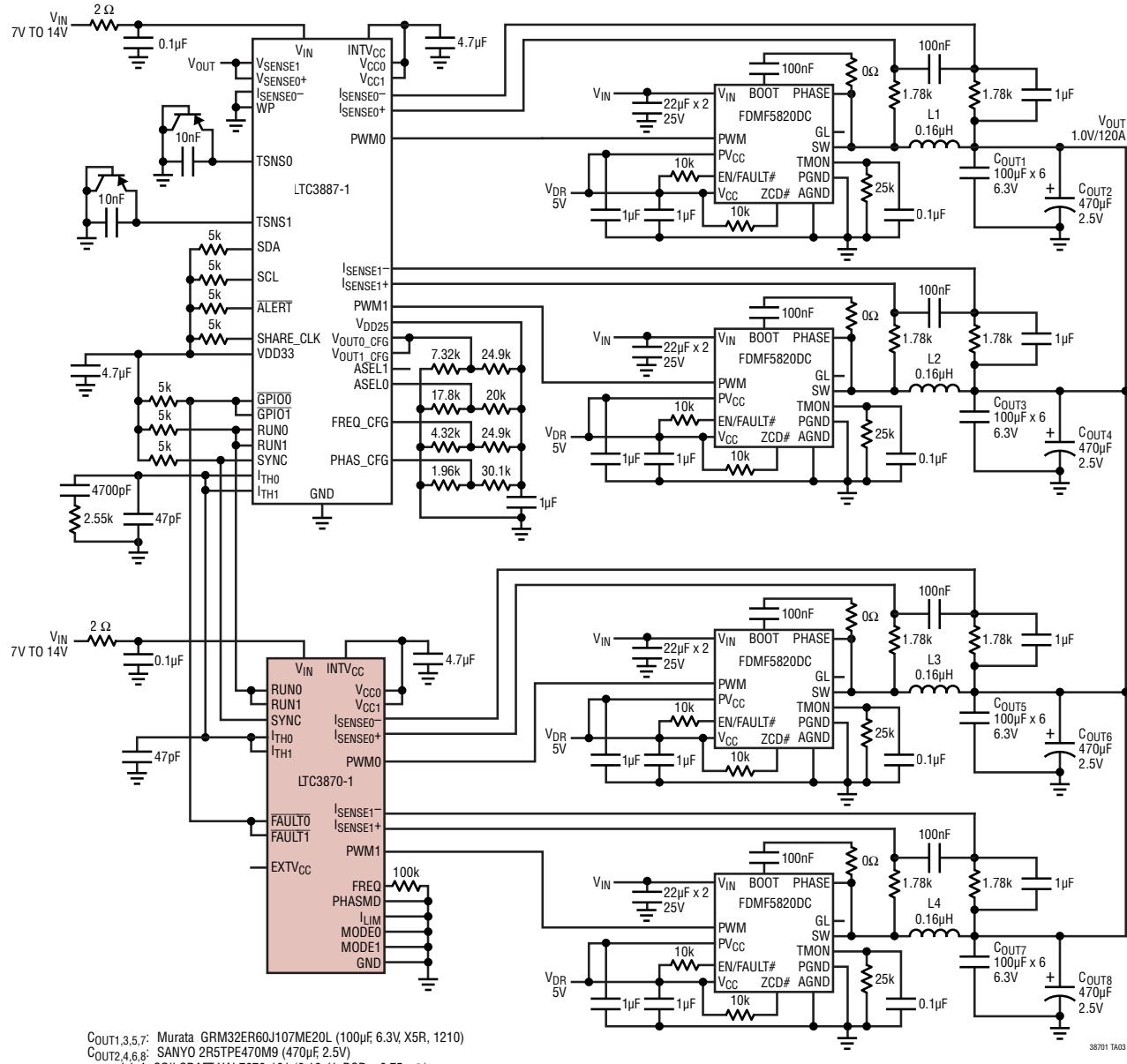

### Design Example

As a design example using master chip LTC3887-1 and slave chip LTC3870-1 for a 4-phase high current regulator, assume  $V_{IN} = 12V$  (nominal),  $V_{IN} = 14V$  (maximum),  $V_{OUT} = 1.0V$ ,  $I_{MAX} = 120A$ , and  $f = 425kHz$  (see Typical Applications).

The master chip LTC3887-1 design can be found in the LTC3887-1 data sheet Design Example section.

LTC3887-1's SYNC pin is connected to LTC3870-1's SYNC pin and LTC3870-1's PHASMD is connected to LTC3870-1's GND.

Slave chip LTC3870-1 should use the same inductor, DrMOS,  $C_{IN}$ , and  $C_{OUT}$  as the master chip. DCR sensing is also used for the slave chip.

LTC3870-1's  $I_{LIM}$  pin is forced to 0V to match the master chip's 50mV current limit. Both chips'  $V_{IN}$ ,  $V_{OUT}$ , RUN,  $I_{TH}$  pins are connected together. LTC3887-1's GPIO pins are connected to LTC3870-1's FAULT pins so the slave controller will be disabled during fault conditions.

## APPLICATIONS INFORMATION

Figure 5. Branch Current Waveforms

## TYPICAL APPLICATIONS

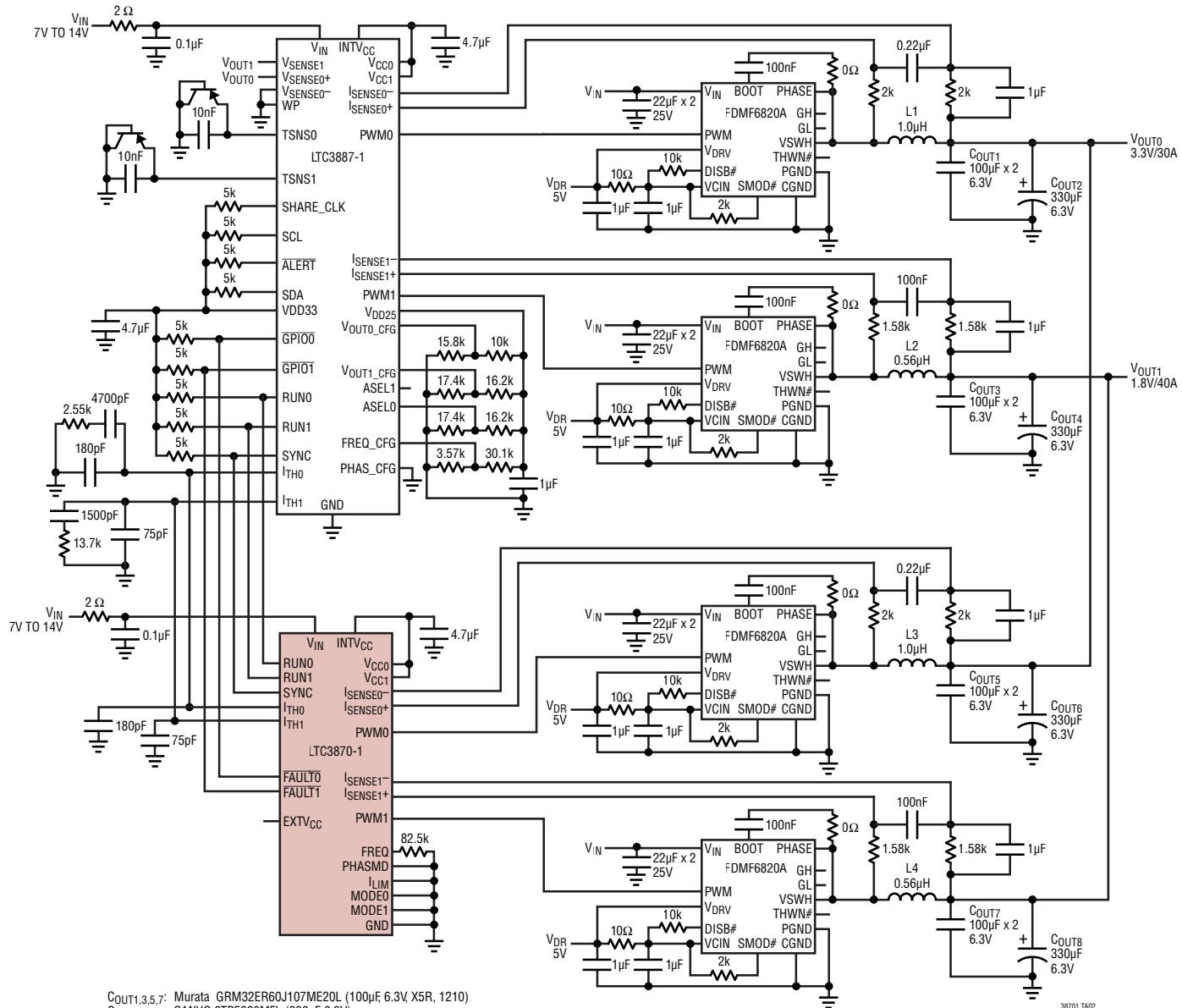

## High Efficiency 350kHz 2-Phase 3.3V and 2-Phase 1.8V Step-Down Converters

C<sub>OUT</sub>1,3,5,7: Murata GRM32ER60J107ME20L (100μF 6.3V X5R, 1210)C<sub>OUT</sub>2,4,6,8: SANYO 6TPE330MFL (330μF 6.3V)L<sub>1</sub>, L<sub>3</sub>: VISHAY IHLP-4040DZ-11 (1.0μH, DCR = 2.4mΩ)L<sub>2</sub>, L<sub>4</sub>: VISHAY IHLP-4040DZ-11 (0.56μH, DCR = 1.61mΩ)

38701 TA02

## **TYPICAL APPLICATIONS**

## High Efficiency 425kHz 4-Phase 1.0V Step-Down Converter

C<sub>OUT1,3,5,7</sub>: Murata GRM32ER60J107ME20L (100 $\mu$ F, 6.3V, X5R, 1210)

C<sub>OUT2,4,6,8</sub>: SANYO 2R5TPE470M9 (470 $\mu$ F, 2.5V)

C<sub>1,4</sub>: COH CRAFT XAL-7070-161 (0.16 $\mu$ H, PCB, 0.75mΩ)

UT2,4,6,8: SANYO 2R51PE470M9 (470 $\mu$ F, 2.5V)

U1-4: COIL CBAFT XAI7070-161 (0.16uH, PCB = 0.75mΩ)

L1-4: COILCRAFT XAL/070-161 (0.16 $\mu$ H, DCR = 0.75m $\Omega$ )

38701 TA03

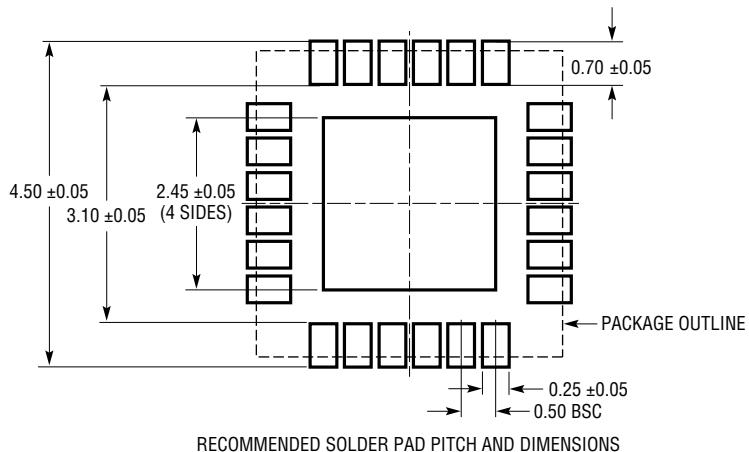

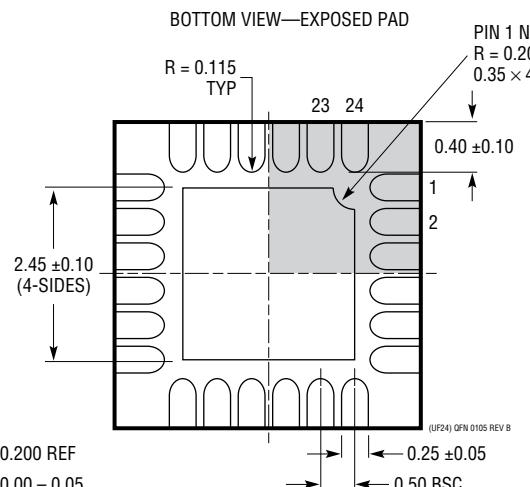

## PACKAGE DESCRIPTION

Please refer to <http://www.linear.com/product/LTC3870-1#packaging> for the most recent package drawings.

**UF Package**

**24-Lead Plastic QFN (4mm × 4mm)**

(Reference LTC DWG # 05-08-1697 Rev B)

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

NOTE:

1. DRAWING PROPOSED TO BE MADE A JEDEC PACKAGE OUTLINE MO-220 VARIATION (WGGD-X)—TO BE APPROVED

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE, IF PRESENT

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADeD AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# LTC3870-1

## TYPICAL APPLICATION

## RELATED PARTS

| PART NUMBER        | DESCRIPTION                                                                                                                        | COMMENTS                                                                                                                                                                              |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTM4676A           | Dual 13A or Single 26A Step-Down DC/DC $\mu$ Module Regulator with Digital Power System Management                                 | $4.5V \leq V_{IN} \leq 17V$ , $0.5V \leq V_{OUT} (\pm 0.5\%) \leq 5.5V$ , I <sup>2</sup> C/PMBus Interface, 16mm $\times$ 16mm $\times$ 5mm, BGA Package                              |

| LTM4675            | Dual 9A or Single 18A $\mu$ Module Regulator with Digital Power System Management                                                  | $4.5V \leq V_{IN} \leq 17V$ ; $0.5V \leq V_{OUT} (\pm 0.5\%) \leq 5.5V$ , I <sup>2</sup> C/PMBus Interface, 11.9mm $\times$ 16mm $\times$ 5mm, BGA Package                            |

| LTM4677            | Dual 18A or Single 18A $\mu$ Module Regulator with Digital Power System Management                                                 | $4.5V \leq V_{IN} \leq 16V$ ; $0.5V \leq V_{OUT} (\pm 0.5\%) \leq 1.8V$ , I <sup>2</sup> C/PMBus Interface, 16mm $\times$ 16mm $\times$ 5.01mm, BGA Package                           |

| LTC3884            | Dual Output Multiphase Step-Down Controller with Sub MilliOhm DCR Sensing Current Mode Control and Digital Power System Management | $4.5V \leq V_{IN} \leq 38V$ , $0.5V \leq V_{OUT} (\pm 0.5\%) \leq 5.5V$ , 70ms Start-Up, I <sup>2</sup> C/PMBus Interface, Programmable Analog Loop Compensation, Input Current Sense |

| LTC3887/ LTC3887-1 | Dual Output Multiphase Step-Down DC/DC Controller with Digital Power System Management, 70ms Start-Up                              | $4.5V \leq V_{IN} \leq 24V$ , $0.5V \leq V_{OUT0,1} (\pm 0.5\%) \leq 5.5V$ , 70ms Start-Up, I <sup>2</sup> C/PMBus Interface, -1 Version Uses DrMOS and Power Blocks                  |

| LTC3882/ LTC3882-1 | Dual Output Multiphase Step-Down DC/DC Voltage Mode Controller with Digital Power System Management                                | $3V \leq V_{IN} \leq 38V$ , $0.5V \leq V_{OUT1,2} \leq 5.25V$ , $\pm 0.5\% V_{OUT}$ Accuracy I <sup>2</sup> C/PMBus Interface, Uses DrMOS or Power Blocks                             |

| LTC3886            | 60V Dual Output Step-Down Controller with Digital Power System Management                                                          | $4.5V \leq V_{IN} \leq 60V$ , $0.5V \leq V_{OUT0,1} (\pm 0.5\%) \leq 13.8V$ , 70ms Start-Up, I <sup>2</sup> C/PMBus Interface, Input Current Sense                                    |

| LTC3883/ LTC3883-1 | Single Phase Step-Down DC/DC Controller with Digital Power System Management                                                       | $V_{IN}$ Up to 24V, $0.5V \leq V_{OUT} \leq 5.5V$ , Input Current Sense Amplifier, I <sup>2</sup> C/PMBus Interface with EEPROM and 16-Bit ADC, $\pm 0.5\% V_{OUT}$ Accuracy          |

| LTC3815            | 6A Monolithic Synchronous DC/DC Step-Down Converter with Digital Power System Management                                           | $2.25V \leq V_{IN} \leq 5.5V$ , $0.4V \leq V_{OUT} \leq 0.72V_{IN}$ , Programmable $V_{OUT}$ Range $\pm 25\%$ with 0.1% Resolution, Up to 3MHz Operation with 13-bit ADC              |

| LTC3874            | Multiphase Step-Down Synchronous Slave Controller with Sub MilliOhm DCR Sensing                                                    | $4.5V \leq V_{IN} \leq 38V$ , $V_{OUT}$ Up to 5.5V, Very High Output Current, Accurate Current Sharing, Current Mode Applications                                                     |

| LTC3880/ LTC3880-1 | Dual Output Multiphase Step-Down DC/DC Controller with Digital Power System Management                                             | $4.5V \leq V_{IN} \leq 24V$ , $0.5V \leq V_{OUT0} (\pm 0.5\%) \leq 5.4V$ , 145ms Start-Up, I <sup>2</sup> C/PMBus Interface with EEPROM and 16-Bit ADC                                |

38701f

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помошь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помошь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

Телефон: 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: [org@eplast1.ru](mailto:org@eplast1.ru)

Адрес: 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.