# Interleaved, 2-Phase Power Factor Controller

The NCP1631 integrates a dual MOSFET driver for interleaved PFC applications. Interleaving consists of paralleling two small stages in lieu of a bigger one, more difficult to design. This approach has several merits like the ease of implementation, the use of smaller components or a better distribution of the heating.

Also, Interleaving extends the power range of Critical Conduction Mode that is an efficient and cost–effective technique (no need for low  $t_{rr}$  diodes). In addition, the NCP1631 drivers are 180° phase shift for a significantly reduced current ripple.

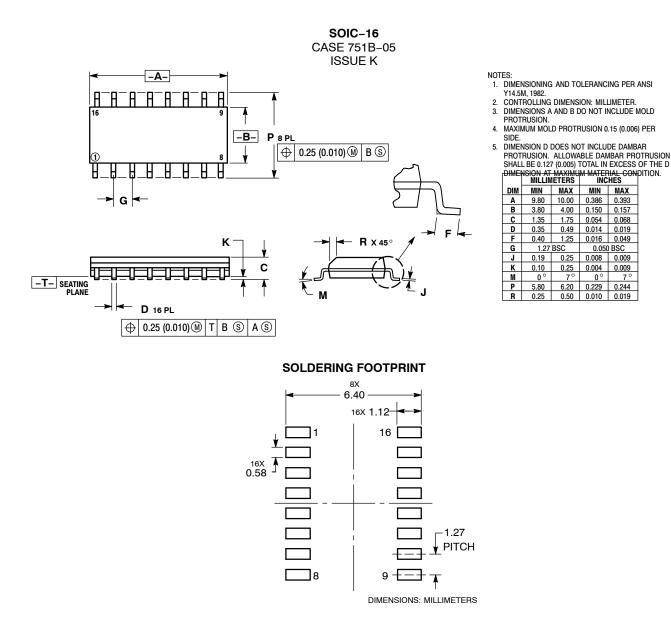

Housed in a SOIC16 package, the circuit incorporates all the features necessary for building robust and compact interleaved PFC stages, with a minimum of external components.

### **General Features**

- Near-Unity Power Factor

- Substantial 180° Phase Shift in All Conditions Including Transient Phases

- Frequency Clamped Critical Conduction Mode (<u>FCCrM</u>) i.e., Fixed Frequency, Discontinuous Conduction Mode Operation with Critical Conduction Achievable in Most Stressful Conditions

- FCCrM Operation Optimizes the PFC Stage Efficiency Over the Load Range

- Out-of-phase Control for Low EMI and a Reduced rms Current in the Bulk Capacitor

- Frequency Fold-back at Low Power to Further Improve the Light Load Efficiency

- Accurate Zero Current Detection by Auxiliary Winding for Valley Turn On

- Fast Line / Load Transient Compensation

- High Drive Capability: -500 mA / +800 mA

- Signal to Indicate that the PFC is Ready for Operation ("pfcOK" Pin)

- $V_{CC}$  Range: from 10 V to 20 V

# Safety Features

- Output Over and Under Voltage Protection

- Brown-Out Detection with a 50-ms Delay to Help Meet Hold-up Time Specifications

- Soft-Start for Smooth Start-up Operation

- Programmable Adjustment of the Maximum Power

- Over Current Limitation

- Detection of Inrush Currents

# **ON Semiconductor®**

http://onsemi.com

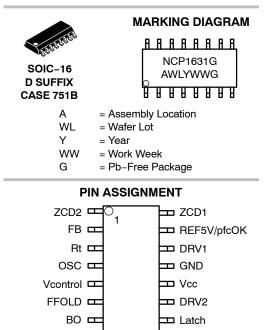

# (Top View) ORDERING INFORMATION

II CS

OVP/UVP 🞞

| Device      | Package              | Shipping <sup>†</sup> |

|-------------|----------------------|-----------------------|

| NCP1631DR2G | SOIC-16<br>(Pb-Free) | 2500 / Tape & Reel    |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

# **Typical Applications**

- Computer Power Supplies

- LCD / Plasma Flat Panels

- All Off Line Appliances Requiring Power Factor Correction

<sup>\*</sup>For additional information on our Pb–Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

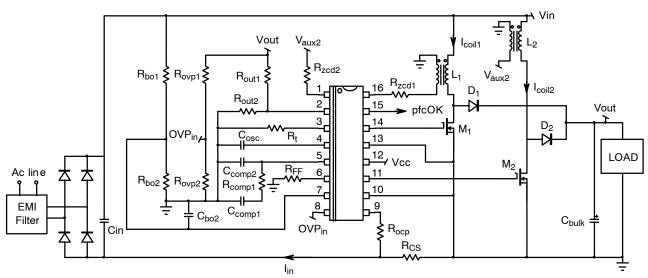

**Figure 1. Typical Application Schematic**

| Symbol                              | Rating                                                                                                                                 | Pin                                          | Value                                      | Unit       |

|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------|------------|

| V <sub>CC(MAX)</sub>                | Maximum Power Supply Voltage Continuous                                                                                                | 11                                           | -0.3, +20                                  | V          |

| V <sub>MAX</sub>                    | Maximum Input Voltage on Low Power Pins                                                                                                | 1, 2, 3, 4, 6, 7,<br>8, 9, 10, 15,<br>and 16 | -0.3, +9.0                                 | V          |

| V <sub>Control(MAX)</sub>           | V <sub>Control</sub> Pin Maximum Input Voltage                                                                                         | 5                                            | -0.3, V <sub>Control(clamp)</sub> (Note 1) | V          |

| Ρ <sub>D</sub><br>R <sub>θJ-A</sub> | Power Dissipation and Thermal Characteristics<br>Maximum Power Dissipation @ $T_A = 70^{\circ}C$<br>Thermal Resistance Junction-to-Air |                                              | 550<br>145                                 | mW<br>°C/W |

| TJ                                  | Operating Junction Temperature Range                                                                                                   |                                              | –55 to +150                                | °C         |

| T <sub>J(MAX)</sub>                 | Maximum Junction Temperature                                                                                                           |                                              | 150                                        | °C         |

| T <sub>S(MAX)</sub>                 | Storage Temperature Range                                                                                                              |                                              | -65 to +150                                | °C         |

| T <sub>L(MAX)</sub>                 | Lead Temperature (Soldering, 10s)                                                                                                      |                                              | 300                                        | °C         |

|                                     | ESD Capability, HBM model (Note 2)                                                                                                     |                                              | 3                                          | kV         |

|                                     | ESD Capability, Machine Model (Note 2)                                                                                                 |                                              | 250                                        | V          |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 1. MAXIMUM RATINGS TABLE

"V<sub>Control(clamp)</sub>" is the pin5 clamp voltage.

This device(s) contains ESD protection and exceeds the following tests:

Human Body Model 2000 V per JEDEC Standard JESD22–A114E Machine Model Method 200 V per JEDEC Standard JESD22–A115–A

3. This device contains latch-up protection and exceeds 100 mA per JEDEC Standard JESD78.

# Table 2. TYPICAL ELECTRICAL CHARACTERISTICS TABLE

(Conditions:  $V_{CC}$  = 15 V,  $V_{pin7}$  = 2 V,  $V_{pin10}$  = 0 V,  $T_J$  = -40°C to +125°C, unless otherwise specified)

| Characteristics                                         | Test Conditions                                                  | Symbol                   | Min  | Тур   | Max   | Unit |

|---------------------------------------------------------|------------------------------------------------------------------|--------------------------|------|-------|-------|------|

| STARTUP AND SUPPLY CIRCUITS                             |                                                                  | •                        | •    |       |       | •    |

| Supply Voltage                                          |                                                                  |                          |      |       |       | V    |

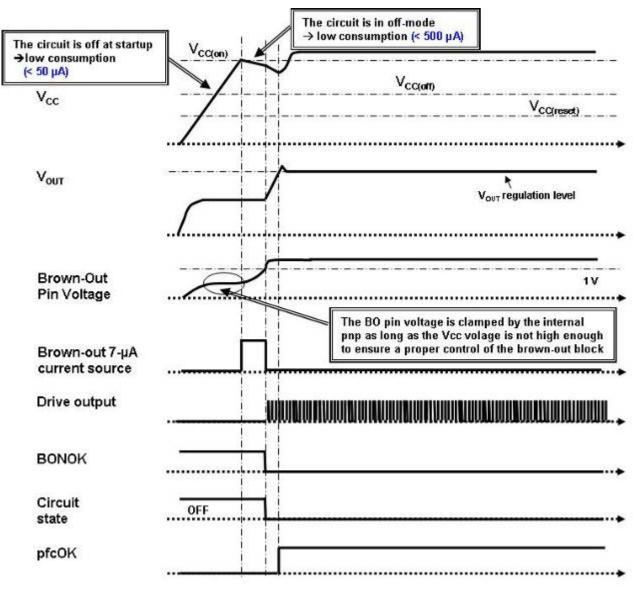

| Startup Threshold                                       | V <sub>CC</sub> increasing                                       | V <sub>CC(on)</sub>      | 11   | 11.85 | 12.7  |      |

| Minimum Operating Voltage                               | V <sub>CC</sub> decreasing                                       | V <sub>CC(off)</sub>     | 9.5  | 10    | 10.5  |      |

| Hysteresis V <sub>CC(on)</sub> – V <sub>CC(off)</sub>   |                                                                  | V <sub>CC(hyst)</sub>    | 1.5  | 1.85  | -     |      |

| Internal Logic Reset                                    | V <sub>CC</sub> decreasing                                       | V <sub>CC(reset)</sub>   | 4.0  | 5.75  | 7.5   |      |

| Startup current                                         | V <sub>CC</sub> = 9.4 V                                          | I <sub>CC(start)</sub>   | -    | 35    | 100   | μA   |

| Supply Current                                          |                                                                  |                          |      |       |       | mA   |

| Device Enabled/No output load on pin6                   | F <sub>sw</sub> = 130 kHz (Note 4)                               | I <sub>CC1</sub>         | -    | 5.0   | 7.0   |      |

| Current that discharges $V_{CC}$ in latch mode          | $V_{CC} = 15 \text{ V}, \text{ V}_{pin10} = 5 \text{ V}$         | I <sub>CC(latch)</sub>   | -    | 0.4   | 0.8   |      |

| Current that discharges V <sub>CC</sub> in OFF          | $V_{CC}$ = 15 V, pin 7 grounded                                  | I <sub>CC(off)</sub>     | -    | 0.4   | 0.8   |      |

| mode                                                    |                                                                  |                          |      |       |       |      |

| OSCILLATOR AND FREQUENCY FOLDBA                         | ACK                                                              |                          | _    |       |       | -    |

| Clamping Charging Current                               | Pin 6 open                                                       | I <sub>OSC(clamp)</sub>  | 31.5 | 35    | 38.5  | μA   |

| Charge Current with no frequency foldback               | Pin 6 grounded                                                   | I <sub>OSC(CH1)</sub>    | 126  | 140   | 154   | μA   |

| Charge Current @ $I_{pin6} = 50 \ \mu A$                | I <sub>pin6</sub> = 50 μA                                        | I <sub>OSC(CH2)</sub>    | 76.5 | 85    | 93.5  | μA   |

| Maximum Discharge Current<br>with no frequency foldback | Pin 6 grounded                                                   | IOSC(DISCH1)             | 94.5 | 105   | 115.5 | μA   |

| Discharge Current @ I <sub>pin6</sub> = 50 μA           | I <sub>pin6</sub> = 50 μA                                        | I <sub>OSC(DISCH2)</sub> | 45   | 50    | 55    | μA   |

| Voltage on pin 6                                        | I <sub>pin6</sub> = 50 μA, V <sub>pin5</sub> = 2.5 V             | V <sub>FF</sub>          | 0.9  | 1.0   | 1.3   | V    |

| Oscillator Upper Threshold                              |                                                                  | V <sub>OSC(high)</sub>   | -    | 5     | -     | V    |

| Oscillator Lower Threshold                              |                                                                  | V <sub>OSC(low)</sub>    | 3.6  | 4.0   | 4.4   | v    |

| Oscillator Swing (Note 5)                               |                                                                  |                          | 0.93 | 0.98  | 1.03  | v    |

|                                                         |                                                                  | V <sub>OSC(swing)</sub>  | 0.93 | 0.98  | 1.05  | v    |

|                                                         |                                                                  |                          |      |       |       |      |

| Current Sense Voltage Offset                            | I <sub>pin9</sub> = 100 μA                                       | V <sub>CS(TH100)</sub>   | -20  | 0     | 20    | mV   |

|                                                         | I <sub>pin9</sub> = 10 μA                                        | V <sub>CS(TH10)</sub>    | -10  | 0     | 10    |      |

| Current Sense Protection Threshold                      | T <sub>i</sub> = 25°C                                            | I <sub>ILIM1</sub>       | 202  | 210   | 226   | μΑ   |

|                                                         | $Tj = -40^{\circ}C$ to 125°C                                     | I <sub>ILIM2</sub>       | 194  | 210   | 226   |      |

| Threshold for In-rush Current Detection                 |                                                                  | l <sub>in-rush</sub>     | 11   | 14    | 17    | μA   |

| (Note 5)                                                |                                                                  |                          |      |       |       |      |

| GATE DRIVE                                              |                                                                  | T                        | 1    |       | 1     | 1    |

| Drive Resistance                                        |                                                                  |                          |      | _     | 45    | Ω    |

| DRV1 Sink                                               | $I_{pin14} = 100 \text{ mA}$                                     | R <sub>SNK1</sub>        | -    | 7     | 15    |      |

| DRV1 Source                                             | $I_{pin14} = -100 \text{ mA}$                                    | R <sub>SRC1</sub>        | -    | 15    | 25    |      |

| DRV2 Sink                                               | $I_{pin11} = 100 \text{ mA}$                                     | R <sub>SNK2</sub>        | -    | 7     | 15    |      |

| DRV2 Source                                             | I <sub>pin11</sub> = -100 mA                                     | R <sub>SRC2</sub>        | -    | 15    | 25    |      |

| Drive Current Capability (Note 5)                       | V 40.4                                                           | .                        |      | 000   |       | mA   |

| DRV1 Sink                                               | $V_{DRV1} = 10 V$                                                | I <sub>SNK1</sub>        | -    | 800   | -     |      |

| DRV1 Source                                             | $V_{DRV1} = 0 V$                                                 | I <sub>SRC1</sub>        | -    | 500   | -     |      |

| DRV2 Sink                                               | $V_{DRV2} = 10 V$                                                | I <sub>SNK1</sub>        | -    | 800   | -     |      |

| DRV2 Source                                             | $V_{DRV2} = 0 V$                                                 | I <sub>SRC1</sub>        | -    | 500   | -     |      |

| Rise Time                                               |                                                                  |                          |      |       |       | ns   |

| DRV1                                                    | $C_{DRV1} = 1 \text{ nF}, V_{DRV1} = 1 \text{ to } 10 \text{ V}$ | t <sub>r1</sub>          | -    | 40    | -     |      |

| DRV2                                                    | C <sub>DRV2</sub> = 1 nF, V <sub>DRV2</sub> = 1 to 10 V          | t <sub>r2</sub>          | -    | 40    | -     |      |

DRV1 and DRV2 pulsating at half this frequency, that is, 65 kHz.

Not tested. Guaranteed by design and characterization.

# Table 2. TYPICAL ELECTRICAL CHARACTERISTICS TABLE

(Conditions:  $V_{CC}$  = 15 V,  $V_{pin7}$  = 2 V,  $V_{pin10}$  = 0 V,  $T_J$  = -40°C to +125°C, unless otherwise specified)

| Characteristics                                                                 | Test Conditions                                                                                                                                   | Symbol                                  | Min   | Тур   | Max   | Uni |

|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------|-------|-------|-----|

| GATE DRIVE                                                                      |                                                                                                                                                   | •                                       | 1     |       |       |     |

| Fall Time                                                                       |                                                                                                                                                   |                                         | 1     | 1     |       | ns  |

| DRV1                                                                            | C <sub>DRV1</sub> = 1 nF, V <sub>DRV1</sub> = 10 to 1 V                                                                                           | t <sub>f1</sub>                         | _     | 20    | _     |     |

| DRV2                                                                            | $C_{DRV2}$ = 1 nF, $V_{DRV2}$ = 10 to 1 V                                                                                                         | t <sub>f2</sub>                         | —     | 20    | -     |     |

| REGULATION BLOCK                                                                | 1                                                                                                                                                 |                                         |       |       |       |     |

| Feedback Voltage Reference                                                      |                                                                                                                                                   | V <sub>REF</sub>                        | 2.44  | 2.500 | 2.56  | V   |

| Error Amplifier Source Current Capability                                       | @ V <sub>pin2</sub> = 2.4 V                                                                                                                       | I <sub>EA(SRC)</sub>                    |       | -20   |       | μA  |

| Error Amplifier Sink Current Capability                                         | @ V <sub>pin2</sub> = 2.6 V                                                                                                                       | I <sub>EA(SNK)</sub>                    |       | +20   |       |     |

| Error Amplifier Gain                                                            |                                                                                                                                                   | G <sub>EA</sub>                         | 110   | 200   | 290   | μS  |

| Pin 5 Source Current when (V <sub>out(low)</sub><br>Detect) is activated        |                                                                                                                                                   | I <sub>Control(boost)</sub>             | 184   | 230   | 276   | μA  |

| Pin2 Bias Current                                                               | V <sub>pin2</sub> = 2.5 V                                                                                                                         | I <sub>FB(bias)</sub>                   | -500  |       | 500   | nA  |

| Pin 5 Voltage:                                                                  | @ V <sub>pin2</sub> = 2.4 V                                                                                                                       | V <sub>Control(clamp)</sub>             | -     | 3.6   | -     | V   |

|                                                                                 | @ V <sub>pin2</sub> = 2.6 V                                                                                                                       | V <sub>Control(MIN)</sub>               | -     | 0.6   | -     |     |

|                                                                                 |                                                                                                                                                   | V <sub>Control(range)</sub>             | 2.7   | 3     | 3.3   |     |

| Internal V <sub>REGUL</sub> Voltage                                             | @ V <sub>pin2</sub> = 2.6 V, I <sub>pin6</sub> = 90 μA                                                                                            | V <sub>REGUL(MIN)</sub>                 | -     | -     | 0.1   | V   |

| (measured on pin 6):                                                            | (a) $V_{pin2} = 2.4 \text{ V}, I_{pin6} = 90 \mu\text{A}$                                                                                         | V <sub>REGUL(Clamp)</sub>               | -     | 1.66  | -     |     |

| Ratio (V <sub>out(low)</sub> Detect Threshold / V <sub>REF</sub> )<br>(Note 5)  | FB falling                                                                                                                                        | V <sub>out(low)</sub> /V <sub>REF</sub> | 95.0  | 95.5  | 96.0  | %   |

| Ratio (V <sub>out(low)</sub> Detect Hysteresis /<br>V <sub>REF</sub> ) (Note 5) | FB rising                                                                                                                                         | H <sub>out(low)</sub> /V <sub>REF</sub> | -     | -     | 0.5   | %   |

| SKIP MODE                                                                       |                                                                                                                                                   |                                         |       | l     |       |     |

| Duty Cycle                                                                      | V <sub>pin2</sub> = 3 V                                                                                                                           | D <sub>MIN</sub>                        | -     | -     | 0     | %   |

| RAMP CONTROL (valid for the two phas                                            | es)                                                                                                                                               | •                                       |       |       |       |     |

| Maximum DRV1 and DRV2 On-Time                                                   | V <sub>pin7</sub> = 1.1 V, I <sub>pin3</sub> = 50 μA                                                                                              | t <sub>on1</sub>                        | 14.5  | 19.5  | 22.5  | μs  |

| (FB pin grounded)                                                               | V <sub>pin7</sub> = 1.1 V, I <sub>pin3</sub> = 200 μA (Note 5)                                                                                    | t <sub>on2</sub>                        | 1.10  | 1.35  | 1.60  |     |

| $T_{J} = -25^{\circ}C \text{ to } +125^{\circ}C$                                | V <sub>pin7</sub> = 2.2 V, I <sub>pin3</sub> = 100 µA (Note 5)                                                                                    | t <sub>on3</sub>                        | 4.00  | 5.00  | 6.00  |     |

|                                                                                 | V <sub>pin7</sub> = 2.2 V, I <sub>pin3</sub> = 400 μA (Note 5)                                                                                    | t <sub>on4</sub>                        | 0.35  | 0.41  | 0.48  |     |

| Maximum DRV1 and DRV2 On-Time                                                   | V <sub>pin7</sub> = 1.1 V, I <sub>pin3</sub> = 50 μA                                                                                              | t <sub>on1</sub>                        | 14.0  | 19.5  | 22.5  | μ   |

| (FB pin grounded)                                                               | $V_{pin7} = 1.1 \text{ V}, I_{pin3} = 200 \mu\text{A} \text{ (Note 5)}$                                                                           | t <sub>on2</sub>                        | 1.05  | 1.35  | 1.60  |     |

| $T_{\rm J} = -40^{\circ}{\rm C}$ to $+125^{\circ}{\rm C}$                       | $V_{pin7} = 2.2 \text{ V}, I_{pin3} = 100 \ \mu\text{A} (Note 5)$                                                                                 | t <sub>on3</sub>                        | 3.84  | 5.00  | 6.00  |     |

|                                                                                 | $V_{pin7} = 2.2 \text{ V}, I_{pin3} = 400 \ \mu\text{A} \text{ (Note 5)}$                                                                         | t <sub>on4</sub>                        | 0.33  | 0.41  | 0.48  |     |

| Pin 3 voltage                                                                   | V <sub>BO</sub> = V <sub>pin7</sub> = 1.1 V, I <sub>pin3</sub> = 50 μA                                                                            | V <sub>Rt1</sub>                        | 1.071 | 1.096 | 1.121 | v   |

| Thro voltage                                                                    | $V_{BO} = V_{pin7} = 1.1 \text{ V}, \text{ I}_{pin3} = 30 \mu\text{A}$<br>$V_{BO} = V_{pin7} = 1.1 \text{ V}, \text{ I}_{pin3} = 200 \mu\text{A}$ | V <sub>Rt2</sub>                        | 1.071 | 1.096 | 1.121 | Ň   |

|                                                                                 | $V_{BO} = V_{pin7} = 2.2 \text{ V}, I_{pin3} = 200 \mu\text{A}$                                                                                   | V <sub>Rt2</sub>                        | 2.169 | 2.196 | 2.223 |     |

|                                                                                 | $V_{BO} = V_{pin7} = 2.2 \text{ V}, I_{pin3} = 30 \ \mu\text{A}$<br>$V_{BO} = V_{pin7} = 2.2 \text{ V}, I_{pin3} = 200 \ \mu\text{A}$             | V <sub>Rt3</sub>                        | 2.169 | 2.190 | 2.223 |     |

| Maximum V <sub>ton</sub> Voltage                                                | Not tested                                                                                                                                        | V <sub>ton(MAX)</sub>                   |       | 5     |       | V   |

| Pin 3 Current Capability                                                        |                                                                                                                                                   | I <sub>Rt(MAX)</sub>                    | 1     | _     | _     | m   |

| Pin 3 sourced current below which the controller is OFF                         |                                                                                                                                                   | I <sub>Rt(off)</sub>                    |       | 7     |       | μΑ  |

| Pin 3 Current Range                                                             | Not tested                                                                                                                                        | I <sub>Rt(range)</sub>                  | 20    |       | 1000  | μ/  |

|                                                                                 | valid for ZCD1 and ZCD2)                                                                                                                          | (                                       | I     | 1     |       | 1   |

| ZCD Threshold Voltage                                                           | V <sub>ZCD</sub> increasing                                                                                                                       | V <sub>ZCD(TH),H</sub>                  | 0.40  | 0.50  | 0.60  | V   |

| -                                                                               |                                                                                                                                                   | ,                                       | 1     | 1     |       | 1   |

| ZCD Threshold Voltage | V <sub>ZCD</sub> increasing<br>V <sub>ZCD</sub> falling | V <sub>ZCD(TH),H</sub><br>V <sub>ZCD(TH),L</sub> | 0.40<br>0.20 | 0.50<br>0.25 | 0.60<br>0.30 | V |

|-----------------------|---------------------------------------------------------|--------------------------------------------------|--------------|--------------|--------------|---|

| ZCD Hysteresis        | V <sub>ZCD</sub> decreasing                             | V <sub>ZCD(HYS)</sub>                            |              | 0.25         |              | V |

DRV1 and DRV2 pulsating at half this frequency, that is, 65 kHz.

Not tested. Guaranteed by design and characterization.

# Table 2. TYPICAL ELECTRICAL CHARACTERISTICS TABLE

(Conditions:  $V_{CC}$  = 15 V,  $V_{pin7}$  = 2 V,  $V_{pin10}$  = 0 V,  $T_J$  = -40°C to +125°C, unless otherwise specified)

| Characteristics                                                          | Test Conditions                                           | Symbol                                          | Min   | Тур         | Max   | Unit |

|--------------------------------------------------------------------------|-----------------------------------------------------------|-------------------------------------------------|-------|-------------|-------|------|

| ZERO VOLTAGE DETECTION CIRCUIT (va                                       | lid for ZCD1 and ZCD2)                                    | -                                               | 1     | 1           |       |      |

| Input Clamp Voltage<br>High State<br>Low State                           | I <sub>pin1</sub> = 5.0 mA<br>I <sub>pin1</sub> = -5.0 mA | V <sub>ZCD(high)</sub><br>V <sub>ZCD(low)</sub> |       | 10<br>-0.65 |       | V    |

| Internal Input Capacitance (Note 5)                                      |                                                           | C <sub>ZCD</sub>                                | -     | 10          | -     | pF   |

| ZCD Watchdog Delay                                                       |                                                           | t <sub>ZCD</sub>                                | 80    | 200         | 320   | μs   |

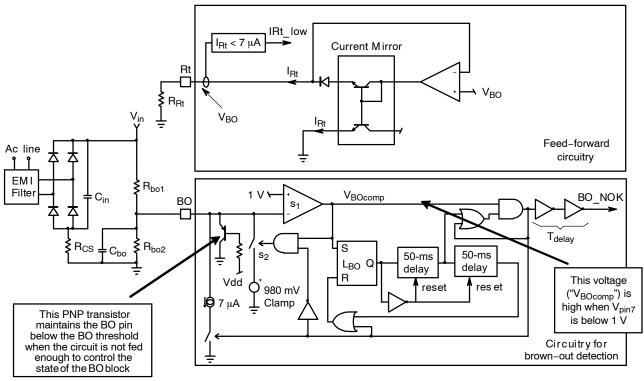

| BROWN-OUT DETECTION                                                      |                                                           |                                                 |       |             |       |      |

| Brown–Out Comparator Threshold                                           |                                                           | V <sub>BO(TH)</sub>                             | 0.97  | 1.00        | 1.03  | V    |

| Brown-Out Current Source                                                 |                                                           | I <sub>BO</sub>                                 | 6     | 7           | 8     | μA   |

| Brown-Out Blanking Time (Note 5)                                         |                                                           | t <sub>BO(BLANK)</sub>                          | 38    | 50          | 62    | ms   |

| Brown–Out Monitoring Window (Note 5)                                     |                                                           | t <sub>BO(window)</sub>                         | 38    | 50          | 62    | ms   |

| Pin 7 clamped voltage if $V_{BO} < V_{BO(TH)}$<br>during $t_{BO(BLANK)}$ | I <sub>pin7</sub> = -100 μA                               | V <sub>BO(clamp)</sub>                          | -     | 965         | -     | mV   |

| Current Capability of the BO Clamp                                       |                                                           | I <sub>BO(clamp)</sub>                          | 100   | -           | -     | μA   |

| Hysteresis V <sub>BO(TH)</sub> – V <sub>BO(clamp)</sub>                  | I <sub>pin7</sub> = - 100 μA                              | V <sub>BO(HYS)</sub>                            | 10    | 35          | 60    | mV   |

| Current Capability of the BO pin Clamp<br>PNP Transistor                 |                                                           | I <sub>BO(PNP)</sub>                            | 100   | -           | -     | μA   |

| Pin BO voltage when clamped by the PNP                                   | I <sub>pin7</sub> = - 100 μA                              | V <sub>BO(PNP)</sub>                            | 0.35  | 0.70        | 0.90  | V    |

| OVER AND UNDER VOLTAGE PROTECTION                                        | DNS                                                       |                                                 |       |             |       |      |

| Over-Voltage Protection Threshold                                        |                                                           | V <sub>OVP</sub>                                | 2.425 | 2.500       | 2.575 | V    |

| Ratio (V <sub>OVP</sub> / V <sub>REF</sub> ) (Note 5)                    |                                                           | V <sub>OVP</sub> /V <sub>REF</sub>              | 99.2  | 99.7        | 100.2 | %    |

| Ratio UVP Threshold over V <sub>REF</sub>                                |                                                           | V <sub>UVP</sub> /V <sub>REF</sub>              | 8     | 12          | 16    | %    |

| Pin 8 Bias Current                                                       | V <sub>pin8</sub> = 2.5 V<br>V <sub>pin8</sub> = 0.3 V    | I <sub>OVP(bias)</sub>                          | -500  | -           | 500   | nA   |

| LATCH INPUT                                                              |                                                           |                                                 |       |             |       |      |

| Pin Latch Threshold for Shutdown                                         |                                                           | V <sub>Latch</sub>                              | 2.375 | 2.500       | 2.625 | V    |

| Pin Latch Bias Current                                                   | V <sub>pin10</sub> = 2.3 V                                | I <sub>Latch(bias)</sub>                        | -500  | -           | 500   | nA   |

| pfcOK / REF5V                                                            |                                                           |                                                 |       |             |       |      |

| Pin 15 Voltage Low State                                                 | $V_{pin7}$ = 0 V, $I_{pin15}$ = 250 $\mu$ A               | V <sub>REF5V(low)</sub>                         | -     | 60          | 120   | mV   |

| Pin 15 Voltage High State                                                | V <sub>pin7</sub> = 0 V, I <sub>pin15</sub> = 5 mA        | V <sub>REF5V(high)</sub>                        | 4.7   | 4.85        | 5.3   | V    |

| Current Capability                                                       |                                                           | I <sub>REF5V</sub>                              | 5     | 10          | -     | mA   |

| THERMAL SHUTDOWN                                                         |                                                           |                                                 |       |             |       |      |

| Thermal Shutdown Threshold                                               |                                                           | T <sub>SHDN</sub>                               | 130   | 140         | 150   | °C   |

| Thermal Shutdown Hysteresis                                              |                                                           | T <sub>SHDN(HYS)</sub>                          | -     | 50          | -     | °C   |

DRV1 and DRV2 pulsating at half this frequency, that is, 65 kHz.

Not tested. Guaranteed by design and characterization.

# Table 3. DETAILED PIN DESCRIPTION

| Pin Number | Name                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1          | ZCD2                            | This is the zero current detection pin for phase 2 of the interleaved PFC stage. Apply the voltage from an auxiliary winding to detect the core reset of the inductor and the valley of the MOSFET drain source voltage                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 2          | FB                              | This pin receives a portion of the pre-converter output voltage. This information is used for the reg-<br>ulation and the "output low" detection (V <sub>OUT</sub> L) that drastically speed-up the loop response when the<br>output voltage drops below 95.5% of the wished level.                                                                                                                                                                                                                                                                                                                |  |  |  |

| 3          | R <sub>T</sub>                  | The resistor placed between pin 3 and ground adjusts the maximum on-time of our system for both phases, and hence the maximum power that can be delivered by the PFC stage.                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 4          | OSC                             | Connect a capacitor to set the clamp frequency of the PFC stage. If wished, this frequency can be reduced in light load as a function of the resistor placed between pin 6 and ground (frequency fold-back). If the coil current cycle is longer than the selected switching period, the circuit delays the next cycle until the core is reset. Hence, the PFC stage can operate in Critical Conduction Moc in the most stressful conditions.                                                                                                                                                      |  |  |  |

| 5          | V <sub>Control</sub>            | The error amplifier output is available on this pin. The capacitor connected between this pin and ground adjusts the regulation loop bandwidth that is typically set below 20 Hz to achieve high Pc Factor ratios.<br>Pin5 is grounded when the circuit is off so that when it starts operation, the power increases slow (soft-start).                                                                                                                                                                                                                                                            |  |  |  |

| 6          | Freq. Foldback                  | Apply a resistor between pin 6 and ground to adjust the oscillator charge current. Clamped not to exceed 100 $\mu$ A, this charge current is made proportional to the power level for a reduced switchin frequency at light load and an optimum efficiency over the load range.                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 7          | BO<br>(Brown-out<br>Protection) | Apply an averaged portion of the input voltage to detect brown–out conditions when $V_{pin2}$ drops<br>below 1 V. A 50–ms internal delay blanks short mains interruptions to help meet hold–up time re-<br>quirements. When it detects a brown–out condition, the circuit stops pulsing and grounds the<br>"pfcOK" pin to disable the downstream converter. Also an internal 7–µA current source is activated<br>to offer a programmable hysteresis.<br>The pin2 voltage is internally re–used for feed–forward.<br>Grounding pin 7 disables the part (after the 50–ms blanking time has elapsed). |  |  |  |

| 8          | OVP / UVP                       | The circuit turns off when $V_{pin9}$ goes below 480 mV (UVP) and disables the drive as long as the pin voltage exceeds 2.5 V (OVP).                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 9          | CS                              | This pin monitors a negative voltage proportional to the coil current. This signal is sensed to limit the maximum coil current and protect the PFC stage in presence of in-rush currents.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 10         | Latch                           | Apply a voltage higher than 2.5 V to latch–off the circuit. The device is reset by unplugging the PFC stage (practically when the circuit detects a brown–out detection) or by forcing the circuit $V_{CC}$ below $V_{CC}$ RST (4 V typically). Operation can then resume when the line is applied back.                                                                                                                                                                                                                                                                                           |  |  |  |

| 11         | DRV2                            | This is the gate drive pin for phase 2 of the interleaved PFC stage. The high current capability of the totem pole gate drive (+0.5/–0.8 A) makes it suitable to effectively drive high gate charge power MOSFETs.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 12         | V <sub>CC</sub>                 | This pin is the positive supply of the IC. The circuit starts to operate when $V_{CC}$ exceeds 12 V and turns off when $V_{CC}$ goes below 10 V (typical values). After start–up, the operating range is 9.5 V up to 20 V.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 13         | GND                             | Connect this pin to the pre-converter ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 14         | DRV1                            | This is the gate drive pin for phase 1 of the interleaved PFC stage. The high current capability of the totem pole gate drive (+0.5/–0.8 A) makes it suitable to effectively drive high gate charge power MOSFETs.                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 15         | REF5V /<br>pfcOK                | The pin15 voltage is high (5 V) when the PFC stage is in a normal, steady state situation and low otherwise. This signal serves to "inform" the downstream converter that the PFC stage is ready and that hence, it can start operation.                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 16         | ZCD1                            | This is the zero current detection pin for phase 1 of the interleaved PFC stage. Apply the voltage from an auxiliary winding to detect the core reset of the inductor and the valley of the MOSFET drain source voltage.                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

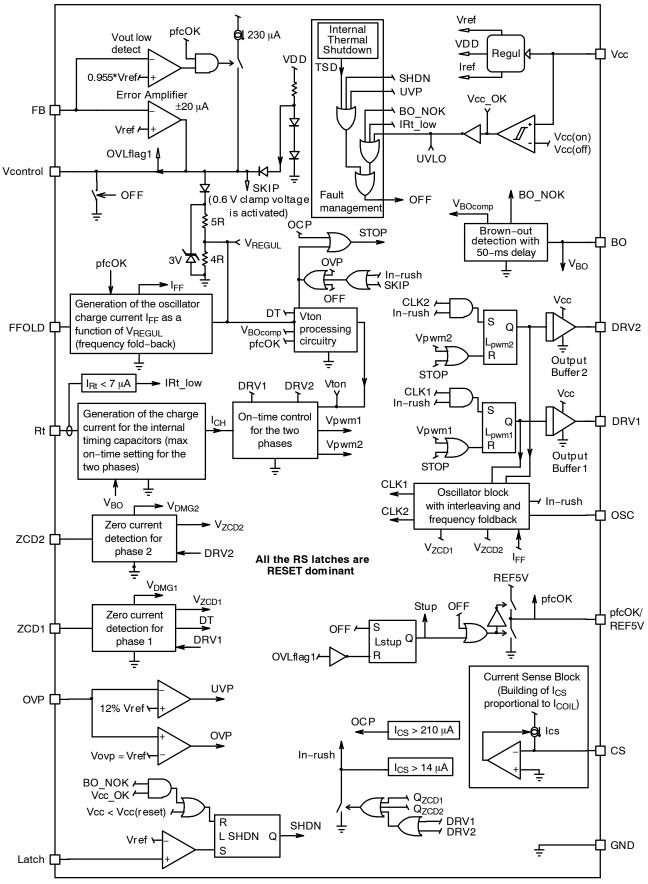

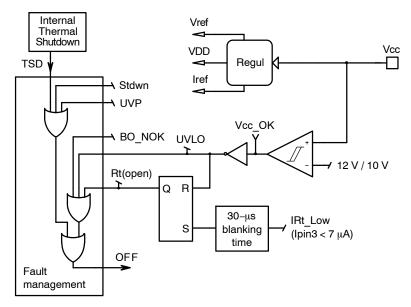

Figure 2. Functional Block Diagram

# **Detailed Operating Description**

The NCP1631 integrates a dual MOSFET driver for interleaved, 2-phase PFC applications. It drives the two branches in so-called *Frequency Clamped Critical conduction Mode* (FCCrM) where each phase operates in *Critical conduction Mode* (CrM) in the most stressful conditions and in *Discontinuous Conduction Mode* (DCM) otherwise, acting as a CrM controller with a frequency clamp (given by the oscillator). According to the conditions, the PFC stage actually jumps from DCM to CrM (and vice versa) with no discontinuity in operation and without degradation of the current shape.

Furthermore, the circuit incorporates protection features for a rugged operation together with some special circuitry to lower the power consumed by the PFC stage in no-load conditions. More generally, the NCP1631 is ideal in systems where cost-effectiveness, reliability, low stand-by power and high power factor are the key parameters:

#### Fully Stable FCCrM and Out-Of-Phase Operation.

Unlike master/slave controllers, the NCP1631 utilizes an interactive-phase approach where the two branches operate independently. Hence, the two phases necessarily operate in FCCrM, preventing risks of undesired dead-times or continuous conduction mode sequences. In addition, the circuit makes them interact so that they run out-of-phase. The NCP1631 unique interleaving technique substantially maintains the wished 180° phase shift between the 2 branches, in all conditions including start-up, fault or transient sequences.

### **Optimized Efficiency Over The Full Power Range.**

The NCP1631 optimizes the efficiency of your PFC stage in the whole line/load range. Its clamp frequency is a major contributor at nominal load. For medium and light load, the clamp frequency linearly decays as a function of the power to maintain high efficiency levels even in very light load. The power threshold under which frequency reduces is programmed by the resistor placed between pin 6 and ground. To prevent any risk of regulation loss at no load, the circuit further skips cycles when the error amplifier reaches its low clamp level.

### Fast Line / Load Transient Compensation.

Characterized by the low bandwidth of their regulation loop, PFC stages exhibit large over and under-shoots when abrupt load or line transients occur (e.g. at start-up). The NCP1631 dramatically narrows the output voltage range. First, the controller dedicates one pin to set an accurate Over-Voltage Protection level and interrupts the power delivery as long as the output voltage exceeds this threshold. Also, the NCP1631 *dynamic response enhancer* drastically speeds-up the regulation loop when the output voltage is 4.5% below its desired level. As a matter of fact, a PFC stage provides the downstream converter with a very narrow voltage range.

#### A "pfcOK" signal.

The circuit detects when the PFC stage is in steady state or if on the contrary, it is in a start–up or fault condition. In the first case, the "pfcOK" pin (pin15) is in high state and low otherwise. This signal is to disable the downstream converter unless the bulk capacitor is charged and no fault is detected. Finally, the downstream converter can be optimally designed for the narrow voltage provided by the PFC stage in normal operation.

#### Safety Protections.

The NCP1631 permanently monitors the input and output voltages, the input current and the die temperature to protect the system from possible over–stresses and make the PFC stage extremely robust and reliable. In addition to the aforementioned OVP protection, one can list:

- **Maximum Current Limit:** the circuit permanently senses the total input current and prevents it from exceeding the preset current limit, still maintaining the out-of-phase operation.

- **In-rush Detection:** the NCP1631 prevents the power switches turn on for the large in-rush currents sequence that occurs during the start-up phase.

- Under-Voltage Protection: this feature is mainly to prevent operation in case of a failure in the OVP monitoring network (e.g., bad connection).

- **Brown-Out Detection:** the circuit stops operating if the line magnitude is too low to protect the PFC stage from the excessive stress that could damage it in such conditions.

- **Thermal Shutdown:** the circuit stops pulsing when its junction temperature exceeds 150°C typically and resumes operation once it drops below about 100°C (50°C hysteresis).

### NCP1631 Operating Modes

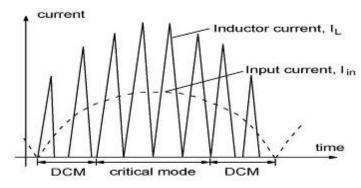

The NCP1631 drives the two branches of the interleaved in <u>FCCrM</u> where each phase operates in *Critical conduction Mode* (CrM) in the most stressful conditions and in *Discontinuous Conduction Mode* (DCM) otherwise, acting as a CrM controller with a frequency clamp (given by the oscillator). According to the conditions, the PFC stage actually jumps from DCM to CrM (and vice versa) with no discontinuity in operation and without degradation of the current shape.

The circuit can also transition within an ac line cycle so that:

- CrM reduces the current stress around the sinusoid top.

- DCM limits the frequency around the line zero crossing.

This capability offers the best of each mode without the drawbacks. The way the circuit modulates the MOSFET on-time allows this facility.

Figure 3. DCM and CRM Operation Within a Sinusoid Cycle for One Branch

#### NCP1631 On-time Modulation

Let's study the ac line current absorbed by one phase of the interleaved PFC converter.

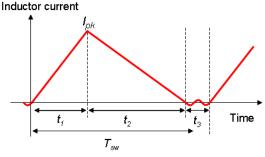

The current waveform of the inductor (L) during one switching period ( $T_{sw}$ ) is portrayed by Figure 5.

The ac line current is the averaged value of the coil current as the result of the EMI filter "polishing" action. Hence, the line current produced by one of the phase is:

$$I_{in} = \frac{1}{2} \binom{t_1}{L} \binom{t_1 + t_2}{T_{sw}} V_{in} \qquad (eq. 1)$$

Where  $(T_{sw} = t_1 + t_2 + t_3)$  is the switching period and  $V_{in}$  is the ac line rectified voltage.

#### Equation 1 shows that Iin is proportional to Vin if

$$\begin{pmatrix} \frac{t_1(t_1 + t_2)}{T_{sw}} \end{pmatrix} \text{ is a constant.}$$

Forcing  $\begin{pmatrix} \frac{t_1(t_1 + t_2)}{T_{sw}} \end{pmatrix}$

constant is what the NCP1631 does to perform *FCCrM* operation that is, to operate in discontinuous or critical conduction mode according to the conditions, without degradation of the power factor.

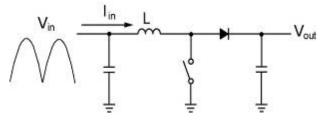

Figure 4. Boost Converter

Figure 5. Inductor Current in DCM

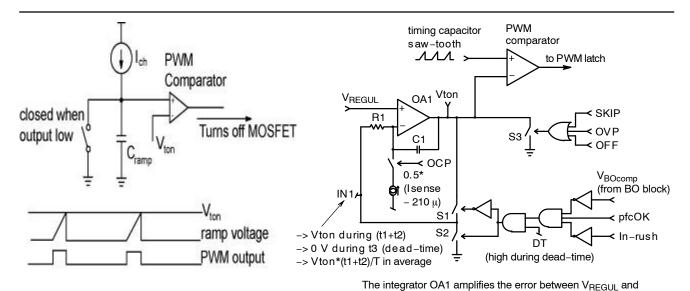

The NCP1631 operates in voltage mode. As portrayed by Figure 6, the MOSFET on time  $t_1$  is controlled by the signal  $V_{ton}$  generated by the regulation block as follows:

$$t_1 = \frac{C_t V_{TON}}{I_t}$$

(eq. 2)

Where:

- C<sub>t</sub> is the internal timing capacitor

- It is the internal current source for the timing capacitor.

The  $I_t$  charge current is constant for a given resistor placed on the  $R_t$  pin.  $C_t$  is also a constant. Hence, the condition

$$\left(\frac{t_1(t_1 + t_2)}{T_{sw}}\right)$$

to be a constant for proper power factor correction can be changed into:

$$\left(\frac{V_{TON}(t_1 + t_2)}{T_{sw}}\right)$$

is constant.

The output of the regulation block ( $V_{CONTROL}$ ) is linearly changed into a signal ( $V_{REGUL}$ ) varying between 0 and 1.66 V. ( $V_{REGUL}$ ) is the voltage that is injected into the PWM section to modulate the MOSFET duty-cycle. However, the NCP1631 inserts some circuitry that processes ( $V_{REGUL}$ ) to form the signal ( $V_{TON}$ ) that is used in the PWM section instead of ( $V_{REGUL}$ ) (see Figure 7). ( $V_{TON}$ ) is modulated in response to the dead-time sensed during the precedent current cycles, that is, for a proper shaping of the ac line current. This modulation leads to:

$$V_{TON} = \frac{T_{sw}V_{REGUL}}{t_1 + t_2} \quad \text{ or: } V_{TON}\frac{t_1 + t_2}{T_{sw}} = V_{REGUL} \text{ (eq. 3)}$$

Substitution of Equation 3 into Equation 2 leads to the following on-time expression:

$$t_1 = \frac{C_t \left(\frac{T_{sw}V_{REGUL}}{t_1 + t_2}\right)}{I_t} \qquad (eq. 4)$$

Replacing " $t_1$ " by its expression of Equation 4, Equation 1 simplifies as follows:

$$I_{in(phase1)} = I_{in(phase2)} = \frac{V_{in}C_tV_{REGUL}}{2L}$$

(eq. 5)

Given the regulation low bandwidth of the PFC systems,  $(V_{CONTROL})$  and then  $(V_{REGUL})$  are slow varying signals. Hence, the line current absorbed by each phase is:

$$\begin{split} I_{in(phase1)} &= I_{in(phase2)} = k V_{in} \quad (eq. 6) \\ where: k = constant = \left[ \frac{C_t V_{REGUL}}{2 L I_t} \right] \end{split}$$

Hence, the input current is then proportional to the input voltage and the ac line current is properly shaped.

One can note that this analysis is also valid for CrM operation that is just a particular case of this functioning where  $(t_3=0)$ , which leads to  $(t_1+t_2=T_{sw})$  and  $(V_{TON}=V_{REGUL})$ . That is why the NCP1631 automatically adapts to the conditions and jumps from DCM and CrM (and vice versa) without power factor degradation and without discontinuity in the power delivery.

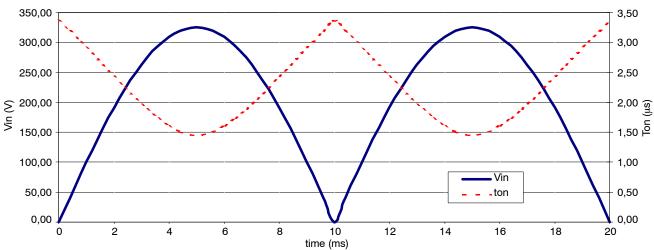

The charging current  $I_t$  is internally processed to be proportional to the square of the line magnitude. Its value is however programmed by the pin 3 resistor to adjust the available on-time as defined by the  $T_{on1}$  to  $T_{on4}$  parameters of the data sheet.

From these data, we can deduce:

$$t_1 = T_{on}(\mu s) = 50 n \frac{R_t^2}{V_{pin7}^2}$$

(eq. 7)

From this equation, we can check that if  $V_{pin7}$  (BO voltage) is 1 V and R<sub>t</sub> is 20 k $\Omega$  (I<sub>pin3</sub> = 50  $\mu$ A) that the on-time is 20  $\mu$ s as given by parameter T<sub>on1</sub>.

Since:

$$V_{\text{REGUL(max)}} = 1.66 \text{ V}$$

$$T_{\text{on}} = \frac{C_{\text{t}} V_{\text{REGUL}}}{I_{\text{t}}}$$

$$V_{\text{pin7}} = \frac{2\sqrt{2} \ V_{\text{in(rms)}}}{\pi} k_{\text{BO}}$$

where  $k_{BO}$  is the scale down factor of the BO sensing network

$$\left(k_{BO} = \frac{R_{bo2}}{R_{bo1} + R_{bo2}}\right)$$

(see Brown-out section)

We can deduce the total input current value and the average input power:

$$I_{in(rms)} \cong \frac{(R_t)^2 V_{REGUL}}{26.9 \cdot 10^{12} L k_{BO}^2 V_{in,rms}}$$

(eq. 8)

$$P_{in,avg} \approx \frac{(R_t)^2 V_{REGUL}}{26.9 \cdot 10^{12} L k_{BO}^2}$$

(eq. 9)

#### Figure 6. PWM Circuit and Timing Diagram

# IN1 so that in average, $(V_{TON}*(t_1+t_2)/T_{sw})$ equates $V_{REGUL}$ . Figure 7. $V_{TON}$ Processing Circuit

The "V<sub>TON</sub> processing circuit" is "informed" when there is an OVP condition or a skip sequence, not to over-dimension V<sub>TON</sub> in that conditions. Otherwise, an OVP sequence or a skipped cycle would be viewed as a "normal" dead-time phase by the circuit and V<sub>TON</sub> would inappropriately increase to compensate it. (Refer to Figure 7). The output of the " $V_{TON}$  processing circuit" is also grounded when the circuit is in OFF state to discharge the capacitor C1 and initialize it for the next active phase.

Finally, the " $V_{TON}$ " is not allowed to be further increased compared to  $V_{REGUL}$  when the circuit has not completed the start-up phase (pfcOK low) and if  $V_{BOcomp}$  from the brown-out block is high (refer to brown-out section for more information).

Figure 8. Input Voltage and On-time vs. Time (example with  $F_{SW}$  = 100 kHz, Pin = 150 W,  $V_{AC}$  = 230 V, L = 200  $\mu$ H)

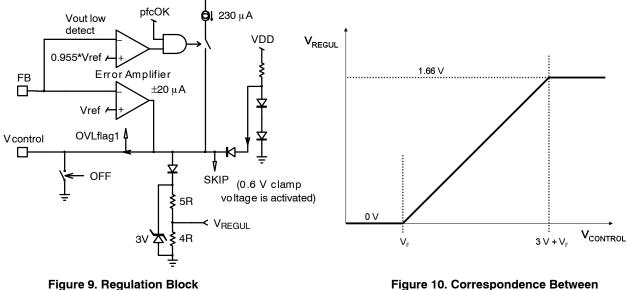

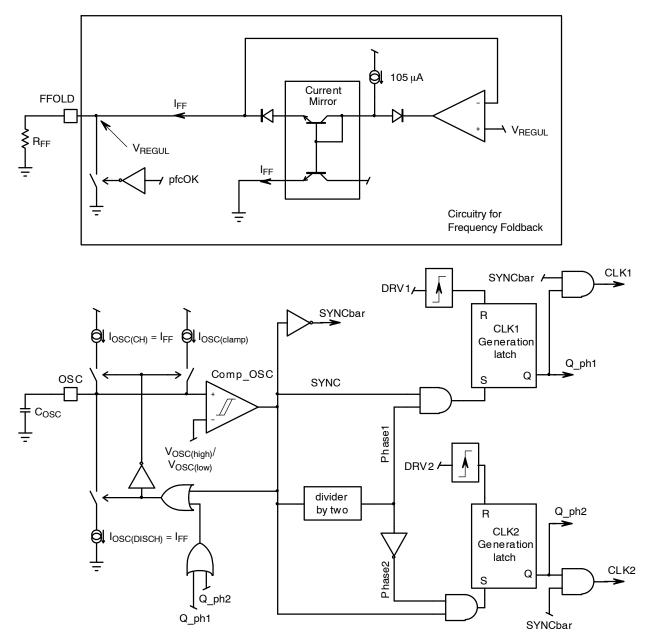

#### **Regulation Block and Low Output Voltage Detection**

A trans-conductance error amplifier with access to the inverting input and output is provided. It features a typical trans-conductance gain of 200  $\mu$ S and a typical capability of  $\pm 20 \,\mu$ A. The output voltage of the PFC stage is typically scaled down by a resistors divider and monitored by the inverting input (feed-back pin – pin2). The bias current is minimized (less than 500 nA) to allow the use of a high impedance feed-back network. The output of the error amplifier is pinned out for external loop compensation (pin5). Typically a type-2 compensator is applied between pin5 and ground, to set the regulation bandwidth below 20 Hz, as need in PFC applications (refer to application note AND8407).

The swing of the error amplifier output is limited within an accurate range:

- It is forced above a voltage drop (V<sub>F</sub>) by the "low clamp" circuitry. When this circuitry is activated, the power demand is minimum and the NCP1631 enters skip mode (the controller stops pulsating) until the clamp is no more active.

- It is clamped not to exceed 3.0 V + the same V<sub>F</sub> voltage drop.

Hence,  $V_{pin5}$  features a 3 V voltage swing.  $V_{pin5}$  is then offset down by (V<sub>F</sub>) and further divided before it connects to the "V<sub>ton</sub> processing block" and the PWM section. Finally, the output of the regulation is a signal ("V<sub>REGUL</sub>" of the block diagram) that varies between 0 and 1.66 V.

V<sub>CONTROL</sub> and V<sub>REGUL</sub>

Provided the low bandwidth of the regulation loop, sharp variations of the load, may result in excessive over and under-shoots. Over-shoots are limited by the Over-Voltage Protection (see OVP section). To contain the under-shoots, an internal comparator monitors the feed-back signal ( $V_{pin2}$ ) and when  $V_{pin2}$  is lower than 95.5% of its nominal value, it connects a 230 µA current source to speed-up the charge of the compensation capacitor ( $C_{pin5}$ ). Finally, it is like if the comparator multiplied the error amplifier gain by 10.

One must note that this circuitry for under-shoots limitation, is not enabled during the start-up sequence of the PFC stage but only once the converter has stabilized (that is when the "pfcOK" signal of the block diagram, is high). This is because, at the beginning of operation, the pin5 capacitor must charge slowly and gradually for a soft start-up.

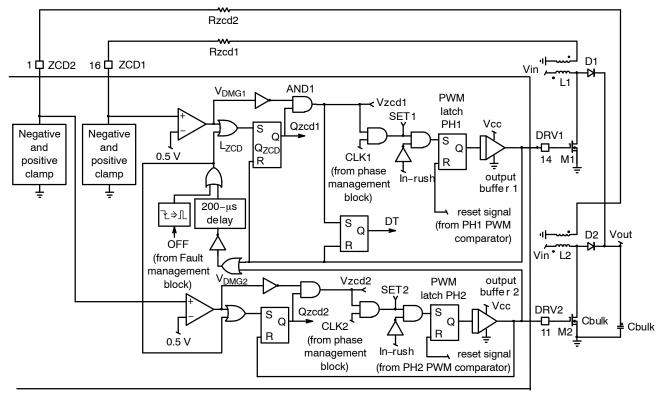

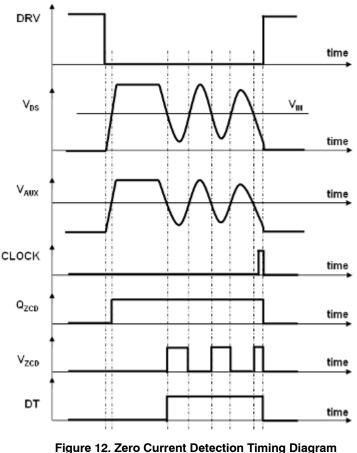

#### **Zero Current Detection**

While the on time is constant, the core reset time varies with the instantaneous input voltage. The NCP1631 determines the demagnetization completion by sensing the inductor voltage, more specifically, by detecting when the inductor voltage drops to zero.

Practically, an auxiliary winding in flyback configuration is taken off of the boost inductor and gives a scaled down version of the inductor voltage that is usable by the controller (Figure 12). In that way, the ZCD voltage (" $V_{AUX}$ ") falls and starts to ring around zero volts when the inductor current drops to zero. The NCP1631 detects this falling edge and allows the next driver on time.

Figure 1 shows how it is implemented.

For each phase, a comparator detects when the voltage of the ZCD winding exceeds 0.5 V. When this is the case, the coil is in demagnetization phase and the latch  $L_{ZCD}$  is set. This latch is reset when the next driver pulse occurs.

Figure 11. Zero Current Detection

To prevent negative voltages on the ZCD pins (ZCD1 for phase 1 and ZCD2 for phase 2), these pins are internally clamped to about 0 V when the voltage applied by the corresponding ZCD winding is negative. Similarly, the ZCD pins are clamped to  $V_{ZCD(high)}$  (10 V typical), when the ZCD voltage rises too high. Because of these clamps, a resistor (R<sub>ZCD</sub> of Figure 11) is necessary to limit the current from the ZCD winding to the ZCD pin. The clamps are designed to respectively source and sink 5 mA minimum. It is recommended not to exceed this 5 mA level within the ZCD clamps for a proper operation. At startup or after an inactive period (because of a protection that has tripped for instance), there is no energy in the ZCD winding and therefore no voltage signal to activate the ZCD comparator. This means that the driver will never turn on. To avoid this, an internal watchdog timer is integrated into the controller. If the driver remains low for more than 200  $\mu$ s (typical), the timer sets the L<sub>ZCD</sub> latch as the ZCD winding signal would do. Obviously, this 200- $\mu$ s delay acts as a minimum off-time if there is no demagnetization winding while it has no action if there is a ZCD voltage provided by the auxiliary winding.

(V<sub>AUX</sub> is the Voltage Provided by the ZCD Winding)

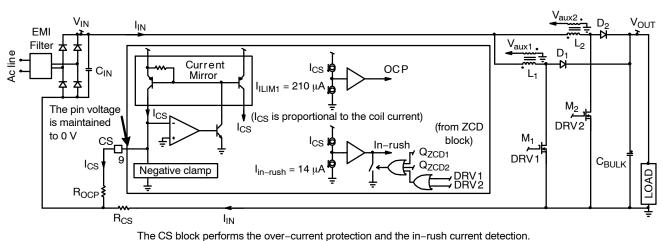

#### **Current Sense**

The NCP1631 is designed to monitor a negative voltage proportional to total input current, i.e., the current drawn by the two interleaved branches ( $I_{in}$ ). As portrayed by Figure 13, a current sense resistor ( $R_{CS}$ ) is practically inserted within the return path to generate a negative voltage ( $V_{CS}$ ) proportional to  $I_{in}$ . The circuit uses  $V_{CS}$  to detect when  $I_{in}$  exceeds its maximum permissible level. To do so, the circuit incorporates an operational amplifier that sources the current necessary to maintain the CS pin voltage null (refer to Figure 13). By inserting a resistor  $R_{OCP}$  between the CS pin and  $R_{CS}$ , we adjust the current that is sourced by the CS pin ( $I_{CS}$ ) as follows:

$$- [R_{CS}I_{COIL}] + [R_{OCP}I_{CS}] = 0$$

(eq. 10)

Which leads to:

$$I_{CS} = \frac{R_{CS}}{R_{OCP}} I_{COIL}$$

(eq. 11)

In other words, the pin 9 current  $(I_{CS})$  is proportional to the coil current.

A negative clamp protects the circuit from the possible negative voltage that can be applied to the pin. This protection is permanently active (even if the circuit off). The clamp is designed to sustain 5 mA. It is recommended not to sink more than 5 mA from the CS pin for a proper operation.

Two functions use  $I_{CS}$ : the over current protection and the in–rush current detection.

#### Over-Current Protection (OCP)

If  $I_{CS}$  exceeds  $I_{ILIM1}$  (210  $\mu$ A typical), an over-current is detected and the on-time is decreased proportionally to the difference between the sensed current  $I_{IN}$  and the 210  $\mu$ A OCP threshold.

The on-time reduction is done by injecting a current  $I_{neg}$  in the negative input of the "V<sub>TON</sub> processing circuit" OPAMP. (See Figure 7)

$$I_{neg} = 0.5(I_{CS} - 210 \,\mu)$$

(eq. 12)

This current is injected each time the OCP signal is high. The maximum coil current is:

$$I_{\text{COIL(max)}} = \frac{R_{\text{OCP}}}{R_{\text{CS}}} I_{\text{ILIM1}}$$

(eq. 13)

#### In-rush Current Detection

When the PFC stage is plugged to the mains, the bulk capacitor is abruptly charged to the line voltage. The charge current (named in-rush current) can be very huge depending on the presence or absence of an effective in-rush limiting circuitry. If the MOSFET turns on during this severe transient, it may be over-stressed and finally damaged. That is why, the NCP1631 permanently monitors the input current and delays the MOSFET turn on until the in-rush current has vanished. This is the function of the I<sub>CS</sub> comparison to the I<sub>in-rush</sub> threshold (14  $\mu$ A typical). When I<sub>CS</sub> exceeds I<sub>in-rush</sub>, the comparator output ("In-rush") is high and prevents the PWM latches from setting (see block diagram). Hence, the two drivers cannot turn high and the MOSFETs cannot switch on. This is to guarantee that the MOSFETs remain off as long as if the input current exceeds 10% of its maximum value. This feature protects the MOSFETs from the possible excessive stress it could suffer from if it was allowed to turn on while a huge current flowed through the coil as it can be the case at start-up or during an over-load transient.

The propagation delay ( $I_{CS} < I_{in-rush}$ ) to (drive outputs high) is in the range of few  $\mu$ s.

However when the circuit starts to operate, the NCP1631 disables this protection to avoid that the current produced by one phase and sensed by the circuit prevents the other branch from operating. Practically, some logic grounds the In–rush protection output when it detects the presence of current cycles with a zero current detection signal provided by the auxiliary winding (Figure 13).

Figure 13. Current Sense Block

#### **Over-Voltage Protection**

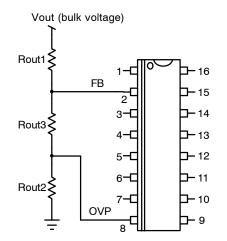

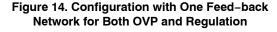

While PFC circuits often use one single pin for both the Over-Voltage Protection (OVP) and the feed-back, the NCP1631 dedicates one specific pin for the under-voltage and over-voltage protections. The NCP1631 configuration

allows the implementation of two separate feed-back networks (see Figure 15):

- 1. One for regulation applied to pin 2.

- 2. Another one for the OVP function (pin 8).

Figure 15. Configuration with Two Separate Feed-back Networks

The double feed-back configuration offers some up-graded safety level as it protects the PFC stage even if there is a failure of one of the two feed-back arrangements.

However, if wished, one single feed-back arrangement is possible as portrayed by Figure 14. The regulation and OVP blocks having the same reference voltage, the resistance ratio  $R_{out2}$  over  $R_{out3}$  adjusts the OVP threshold. More specifically,

The bulk regulation voltage ("Vout(nom)") is:

$$V_{out(nom)} = \frac{R_{out1} + R_{out2} + R_{out3}}{R_{out2} + R_{out3}} \cdot V_{ref}$$

(eq. 14)

The OVP level ("V<sub>out(ovp)</sub>") is:

$$V_{out(ovp)} = \frac{R_{out1} + R_{out2} + R_{out3}}{R_{out2}} \cdot V_{ref}$$

(eq. 15)

The ratio OVP level over regulation level is:

$$\frac{V_{out(ovp)}}{V_{out(nom)}} = 1 + \frac{R_{out3}}{R_{out2}}$$

(eq. 16)

For instance,  $(V_{out(nom)} = 105\% \text{ x } V_{out(nom)})$  leads to:  $(R_{out3} = 5\% \text{ x } R_{out2})$ .

When the circuit detects that the output voltage exceeds the OVP level, it maintains the power switch open to stop the power delivery.

As mentioned previously, the " $V_{TON}$  processing circuit" is "informed" when there is an OVP condition, not to over-dimension  $V_{TON}$  in that conditions. Otherwise, an OVP sequence would be viewed as a dead-time phase by the circuit and  $V_{TON}$  would inappropriately increase to compensate it (refer to Figure 7).

#### PfcOK / REF5V Signal

The NCP1631 can communicate with the downstream converter. The signal "pfcOK/REF5V" is high (5 V) when the PFC stage is in normal operation (its output voltage is stabilized at the nominal level) and low otherwise.

More specifically, "pfcOK/REF5V" is low:

- During the PFC stage start-up, that is, as long as the output voltage has not yet stabilized at the right level. The start-up phase is detected by the latch " $L_{STUP}$ " of the block diagram in Figure 2. " $L_{STUP}$ " is set during each "off" phase so that its output ("STUP") is high when the circuit enters an active phase. The latch is reset when the error amplifier stops charging its output capacitor, that is, when the output voltage of the PFC stage has reached its desired regulation level. At that moment, "STUP" falls down to indicate the end of the start-up phase.

- Any time, the circuit is off or a fault condition is detected as described by the "Fault management and OFF mode" section

Finally, "pfcOK/REF5V" is high when the PFC output voltage is properly and safely regulated. "pfcOK/REF5V"

should be used to allow operation of the downstream converter.

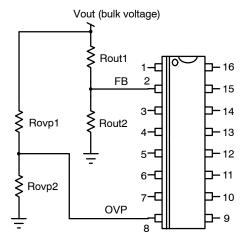

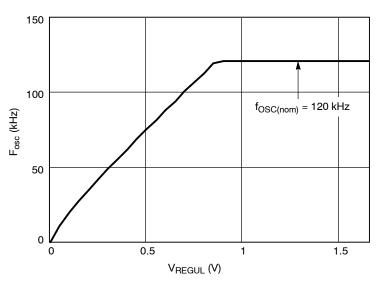

#### **Oscillator Section – Phase Management**

The oscillator generates the clock signal that dictates the maximum switching frequency for the global system ( $f_{osc}$ ). In other words, each of the two interleaved branches cannot operate above the clamp frequency that is half the oscillator frequency ( $f_{osc}/2$ ). The oscillator frequency ( $f_{osc}$ ) is adjusted by the capacitor applied to pin 4. Typically, a **440** pF capacitor approximately leads to a 120-kHz operating frequency, meaning a 60-kHz clamp frequency for each branch. The oscillator frequency should be kept below 500 kHz (which corresponds to a pin4 capacitor in the range of **100 pF**).

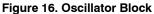

As shown by Figure 16, two current sources  $I_{OSC(clamp)}$ (35 µA typical) and  $I_{OSC(CH)}$  (105 µA typical) charge the pin 4 capacitor until its voltage exceeds  $V_{OSC(high)}$  (5 V typically). At that moment, the output of the COMP\_OSC comparator ("SYNC" of Figure 16) turns high and changes the COMP\_OSC reference threshold that drops from  $V_{OSC(high)}$  down to  $V_{OSC(low)}$  (hysteresis). The system enters a discharge phase where the  $I_{CH}$  current source is disabled and instead a sink current  $I_{OSC(DISCH)}$  (105 µA typ.) discharges the pin 4 capacitor. This sequence lasts until  $V_{pin4}$  goes below  $V_{OSC(low)}$  when the "SYNC" signal turns low and a new charging phase starts. A divider by two uses the "SYNC" information to manage the phases of the interleaved PFC: the first SYNC pulse sets "phase 1", the second one, "phase 2", the third one phase 1 again... etc...

According to the selected phase, the "SYNC" signal sets the relevant "Clock generator latch" that will generate the clock signal ("CLK1" for phase 1, "CLK2" for phase 2) when SYNC drops to zero (falling edge detector). So, the drivers are synchronized to SYNC falling edge.

Actually, the drivers cannot turn on at this very moment if the demagnetization of the coil is not yet complete (CrM operation). In this case, the clock signal is maintained high until the driver turns high (the clock generator latches are reset by the corresponding driver is high – reset on rising edge detector). Also, the discharge time can be prolonged if when  $V_{pin4}$  drops below  $V_{OSC(low)}$ , the driver of the phase cannot turn on because the core is not reset yet (CrM operation). In this case,  $V_{pin4}$  decreases until the driver turns high. The further discharge of  $V_{pin4}$  below  $V_{OSC(low)}$ helps maintain a substantial 180° phase shift in CrM that is in essence, guaranteed in DCM. In the two conditions (CrM or DCM), operation is stable and robust.

Figure 17 portrays the clock signal waveforms in different cases:

In fixed frequency operation (DCM), the cycle time of the coil current is shorter than an oscillator period. Hence, as soon as the clock signal goes high, the driver can turn on and reset the clock generator latch. The clock signal is then a short pulse. However, the coil current can possibly be non zero when the clock signal turns high. The circuit would enter Continuous Conduction Mode (CCM) if the MOSFET turned on in that moment. In order to avoid CCM operation, the clock is prevented from setting the PWM latch until the core is reset (that is as low as "V<sub>ZCD</sub>" of Figure 8 is low). The clock signal remains high during this waiting phase (refer to Figure 12). Hence the next MOSFET conduction time occurs as soon as the coil

current has totally vanished. In other words, critical conduction mode (CrM) operation is obtained.

The clamp frequency can be computed using the following equation:

$$f_{\rm osc} \cong {60 \ \mu \over C_{\rm OSC} + 10 \ p}$$

(eq. 17)

where  $C_{OSC}$  is the pin 4 external capacitor and  $C_{pin}$  the pin 4 parasitic capacitance (about 10 pF).

Figure 17. Typical Waveforms (T<sub>delay</sub> not shown here for the sake of simplicity)

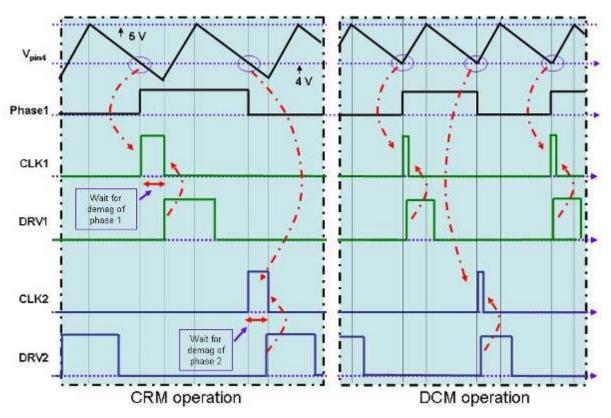

#### Frequency Foldback

In addition, the circuit features the frequency fold-back function to improve the light load efficiency. Practically, the oscillator charge and discharge currents ( $I_{OSC(CH)}$  and  $I_{OSC(DISCH)}$  of Figure 16) are not constant but dependent on the power level. More specifically,  $I_{OSC(CH)}$  and  $I_{OSC(DISCH)}$  linearly vary as a function of  $V_{control}$  output of the regulation block that thanks to the feed-forward featured by the NCP1631, is representative of the load.

The practical implementation is portrayed by Figure 16.

>

" $V_{REGUL}$ " is the signal derived from  $V_{control}$  that is effectively used to modulate the MOSFET on-time.  $V_{REGUL}$  is buffered and applied to pin 6 ("Frequency fold-back" pin). A resistor  $R_{FF}$  is to be connected to pin 6 to sink a current proportional to  $V_{REGUL}$

$$\left(I_{\text{pin6}} = I_{\text{FF}} = \frac{V_{\text{REGUL}}}{R_{\text{FF}}}\right).$$

This current is clamped not to exceed 105  $\mu$ A and copied by a current mirror to form I<sub>OSC(CH)</sub> and I<sub>OSC(DISCH)</sub>.

As a matter of fact, the oscillator charge current is:

$$\begin{cases} I_{OSC(CH)} = I_{OSC(clamp)} + \frac{V_{REGUL}}{R_{FF}} & \text{if}\left(\frac{V_{REGUL}}{R_{FF}} \le 105 \,\mu\text{A}\right) \\ I_{OSC(CH)} = I_{OSC(clamp)} + I_{OSC(CH1)} = I_{OSC(CHT1)} = 140 \,\mu\text{A} & \text{otherwise} \end{cases}$$

The oscillator charge current is then an increasing function of  $V_{REGUL}$  and is clamped to 140  $\mu A.$  The oscillator discharge current is:

$$\begin{cases} I_{OSC(DISCH)} = \frac{V_{REGUL}}{R_{FF}} & \text{if} \left(\frac{V_{REGUL}}{R_{FF}} \le 105 \,\mu\text{A}\right) \\ I_{OSC(DISCH)} = I_{OSC(DISCH1)} = 105 \,\mu\text{A} & \text{otherwise} \end{cases}$$

The oscillator discharge current is also an increasing function of  $V_{REGUL}$  and is clamped to105  $\mu A.$

As a consequence, the clamp frequency is also an increasing function of  $V_{REGUL}$  until it reaches a maximum

value for ( $I_{FF} = 105 \ \mu A$ ). If we consider the clamp frequency  $f_{OSC}$  computed by Equation 17 as the nominal value obtained at full load and if we name it " $f_{OSC(nom)}$ ":

$$f_{OSC} = f_{OSC(nom)} \qquad \text{if} \left( V_{\text{REGUL}} \ge R_{\text{FF}} \cdot 105 \,\mu\text{A} \right)$$

$$f_{OSC} = \frac{V_{\text{REGUL}}(R_{\text{FF}}I_{\text{OSC}(clamp)} + V_{\text{REGUL}})}{60 \,\mu R_{\text{FF}}(R_{\text{FF}}I_{\text{OSC}(clamp)} + 2V_{\text{REGUL}})} \cdot f_{\text{OSC}(nom)} \quad \text{if} \left( V_{\text{REGUL}} \le R_{\text{FF}} \cdot 105 \,\mu\text{A} \right)$$

$$(eq. 20)$$

Let's illustrate this operation on an example.

$V_{REGUL}$  is the control signal that varies between 0 and 1.66 V, ( $V_{REGUL} = 1.66$  V) corresponding to the maximum power ( $P_{in}$ )<sub>HL</sub> that can virtually be delivered by the PFC stage as selected by the timing resistor (for more details, you can refer to the application note AND8407).