# APDS-9250

Digital RGB, IR and Ambient Light Sensor

# **Data Sheet**

## Description

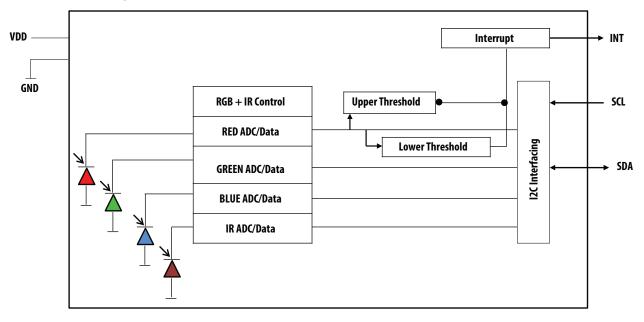

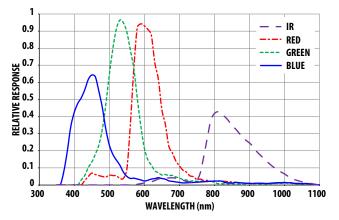

The APDS-9250 device uses 4 individual channels of red, green, blue, and IR (RGB+IR) in a specially designed matrix arrangement. This allows the device to have optimal angular response and accurate RGB spectral response with high lux accuracy over various light sources. APDS-9250 supports the I<sup>2</sup>C interface and has a programmable interrupt controller that frees up micro-controller resources.

The device detects light intensity under a variety of lighting conditions and through a variety of attenuation materials, including dark glass. APDS-9250 could be configured as Ambient Light Sensor and RGB+IR Sensor. The color-sensing feature is useful in applications such as LED RGB backlight control, solid-state lighting, reflected LED color sampler, or fluorescent light color temperature detection. The integrated IR blocking filter makes this device an excellent ambient light sensor and color temperature compensation that allows output to have less variation over the temperature.

## **Ordering Information**

| Part Number | Packaging   | Quantity      |

|-------------|-------------|---------------|

| APDS-9250   | Tape & Reel | 5000 per reel |

## Features

- Colour and Ambient Light Sensing (CS-RGB and ALS)

- Accuracy of Correlated Color Temperature (CCT)

- Individual channels for Red, Green, Blue and Infared

- Approximates Human Eye Response with Green Channel

- Red, Green, Blue, Infrared and ALS Sensing

- High Sensitivity in low lux condition Ideally suited for Operation Behind Dark Glass

- Wide Dynamic Range: 18,000,000: 1

- Up to 20-Bit Resolution

- Power Management

- Low Active Current 130 µA typical

- Low Standby Current 1µA typical

- I<sup>2</sup>C-bus Fast Mode Compatible Interface

- Up to 400 kHz (I<sup>2</sup>C Fast-Mode)

- Dedicated Interrupt Pin

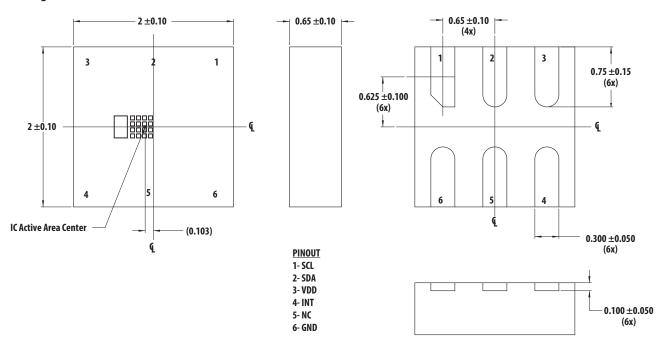

- Small Package L 2.0 × W 2.0 × H 0.65 mm

#### **Applications**

- OLED Display Control

- RGB LED Backlight Control

- Ambient Light Color Temperature Sensing

#### **Functional Block Diagram**

# **Description:**

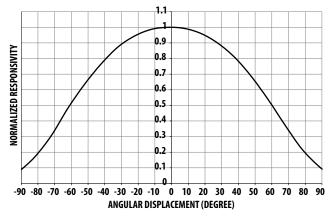

The APDS-9250 device contains multiple photodiodes for Light Sensor (R, G, B, IR channel) that are designed in a matrix placement to achieve optimal angular response at the fall of incident light angle.

The device provides on-chip multiple diodes, ADCs, state machine, non-volatile memory and an I<sup>2</sup>C interface.

Integration of all color sensing channels occurs simultaneously. Upon completion of the conversion cycle, the conversion result is transferred to the corresponding data registers. Communication with the device is accomplished through a fast (up to 400 kHz), two-wire I<sup>2</sup>C serial bus for easy connection to a microcontroller or embedded controller.

The APDS-9250 provides a separate pin for interrupts. When interrupts are enabled and a preset value is exceeded, the interrupt pin is asserted and remains asserted until cleared by the controlling firmware. The interrupt feature simplifies and improves system efficiency by eliminating the need to poll a sensor for a light intensity. An interrupt is generated after completion of new conversion of the light sensor channels where the light sensor interrupt source can work on any of the Red, Green, Blue, IR channels. Additionally, a programmable interrupt persistence feature allows the user to determine how many consecutive exceeded thresholds are necessary to trigger an interrupt.

#### I/O Pins Configuration

| Pin | Name | Туре   | Description                                                                                     |

|-----|------|--------|-------------------------------------------------------------------------------------------------|

| 1   | SCL  | I      | l <sup>2</sup> C Serial Clock Input Terminal –<br>Clock Signal for l <sup>2</sup> C Serial Data |

| 2   | SDA  | I/O    | Serial Data I/O for I <sup>2</sup> C                                                            |

| 3   | VDD  | Supply | Power Supply Voltage                                                                            |

| 4   | INT  | 0      | Interrupt – Open Drain                                                                          |

| 5   | NC   |        | No Connect                                                                                      |

| 6   | GND  | Ground | Power Supply Ground. All<br>Voltages are referenced to GND                                      |

#### **Absolute Maximum Ratings**

over operating free-air temperature range (unless otherwise noted)†

| Parameter                           | Symbol           | Min. | Max. | Units | Conditions |

|-------------------------------------|------------------|------|------|-------|------------|

| Power Supply Voltage <sup>[1]</sup> | V <sub>DD</sub>  |      | 3.8  | V     |            |

| Max Voltage on SCL, SDA, INT pads   | V <sub>I2C</sub> | -0.5 | 3.8  | V     |            |

| Storage Temperature Range           | T <sub>stg</sub> | -40  | 85   | °C    |            |

Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Note 1. All voltages are with respect to GND.

#### **Recommended Operating Conditions**

| Parameter                                                                    | Symbol          | Min. | Тур. | Max. | Units |  |

|------------------------------------------------------------------------------|-----------------|------|------|------|-------|--|

| Operating Ambient Temperature                                                | T <sub>A</sub>  | -40  |      | 85   | °C    |  |

| Supply voltage                                                               | V <sub>DD</sub> | 1.7  |      | 3.6  | V     |  |

| Supply Voltage Accuracy, V <sub>DD</sub><br>total error including transients |                 | -3   |      | 3    | %     |  |

#### Operating Characteristics, $V_{DD} = 2.8 \text{ V}$ , $T_A = 25^{\circ}\text{C}$ (unless otherwise noted)

| Parameter                                             | Symbol            | Min | Тур | Мах             | Units | Test Conditions                                           |

|-------------------------------------------------------|-------------------|-----|-----|-----------------|-------|-----------------------------------------------------------|

| Active Mode Current                                   | I <sub>CS</sub>   |     | 130 |                 | μΑ    | V <sub>DD</sub> =2.8V, Gain Mode 3                        |

| Standby Current                                       | I <sub>STBY</sub> |     | 1   | 2               | μΑ    | In Standby Mode. No active I <sup>2</sup> C communication |

| SCL, SDA Input High Voltage                           | VIH               | 1.5 |     | V <sub>DD</sub> | V     |                                                           |

| SCL, SDA Input Low Voltage                            | VIL               | 0   |     | 0.4             | V     |                                                           |

| V <sub>OL</sub> INT, Output Low Voltage               | V <sub>OL</sub>   | 0   |     | 0.4             | V     |                                                           |

| I <sub>LEAK</sub> Leakage Current, SDA, SCL, INT Pins | I <sub>LEAK</sub> | -5  |     | 5               | μΑ    |                                                           |

#### Optical Characteristics, $V_{DD} = 2.8 V$ , $T_A = 25^{\circ}C$ (unless otherwise noted)

| Parameter  | Test            | Test RED Channel |      | Green Channel |      | Blue Channel |      | IR Channel |      |      |  |

|------------|-----------------|------------------|------|---------------|------|--------------|------|------------|------|------|--|

|            | Condition       | Min.             | Max. | Min.          | Max. | Min.         | Max. | Min.       | Max. | Unit |  |

| Irradiance | $\lambda = 465$ | 0                | 5    | 6             | 17   | 80           | 120  | 0          | 4    | %    |  |

| Response   | $\lambda = 525$ | 3                | 10   | 80            | 120  | 10           | 30   | 0          | 3    | -    |  |

|            | $\lambda = 625$ | 80               | 120  | 18            | 33   | 0            | 3    | 0          | 3    | -    |  |

|            | $\lambda = 850$ | 0                | 3    | 0             | 3    | 0            | 3    | 80         | 120  | -    |  |

Notes:

1. The percentage shown represents the ratio of the respective red, green, or blue channel value to the IR channel value.

2. The 465 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength D = 465 nm, spectral halfwidth  $\frac{1}{2} = 22$  nm.

The 525 nm input irradiance is supplied by an InGaN light-emitting diode with the following characteristics: dominant wavelength \_D = 525 nm, spectral halfwidth \_\_½ = 35 nm.

4. The 625 nm input irradiance is supplied by a AllnGaP light-emitting diode with the following characteristics: dominant wavelength \_D = 625 nm, spectral halfwidth \_½ = 15 nm.

5. The 850 nm input irradiance is supplied by a AllnGaP light-emitting diode with the following characteristics: dominant wavelength  $_D = 850$  nm, spectral halfwidth  $_{1/2} = 40$  nm.

#### RGB Characteristics, $V_{DD} = 2.8 V$ , $T_A = 25^{\circ}C$ (unless otherwise noted)

| Parameter                      | Min. | Тур.  | Max.    | Units  | Test Conditions     |

|--------------------------------|------|-------|---------|--------|---------------------|

| Dark Count                     | 0    |       | 3       | counts |                     |

| ADC Integration Time           | 2.97 | 3.125 | 3.28    | ms     |                     |

| Full Scale ADC Counts Per Step |      | 8192  |         | counts | 13 bit              |

| Full Scale ADC Count Value     |      |       | 262,143 | counts | 18 bit, 100ms, G=1x |

| Parameter            | Symbol               | Min | Тур   | Мах | Units | Test Conditions                                           |

|----------------------|----------------------|-----|-------|-----|-------|-----------------------------------------------------------|

| Peak Wavelength      | λp                   |     | 550   |     | nm    |                                                           |

| Min Integration Time | T <sub>intmin1</sub> |     | 3.125 |     | ms    |                                                           |

|                      | T <sub>intmin2</sub> |     | 50    |     | ms    | With 50/60Hz rejection                                    |

| Max Integration Time | T <sub>intmax</sub>  |     | 400   |     | ms    | With 50/60Hz rejection                                    |

| Output Resolution    | RES <sub>ALS</sub>   | 13  | 18    | 20  | bit   | Programmable                                              |

| ADC Count Value      |                      |     | 1000  |     | count | $\lambda$ = 530nm, 50ms, Gain=3x, Ee=59uW/cm <sup>2</sup> |

ALS Characteristics,  $V_{DD} = 2.8 V$ ,  $T_A = 25^{\circ}C$  (unless otherwise noted)

Figure 1. Normalized ALS PD Angular Response

Figure 2. Normalized PD Spectral Response

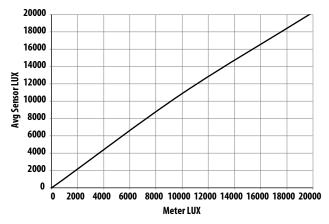

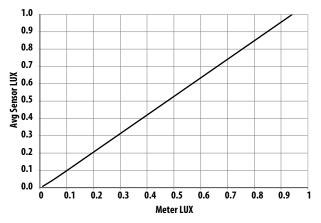

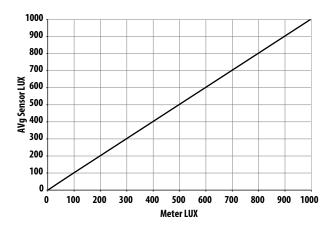

Figure 3. ALS Sensor LUX vs Meter LUX using White Light

Figure 4. ALS Sensor LUX vs Meter LUX using White Light

Figure 5. ALS Sensor LUX vs Meter LUX using Incandescent Light

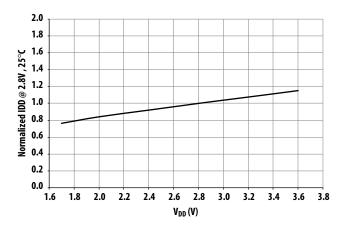

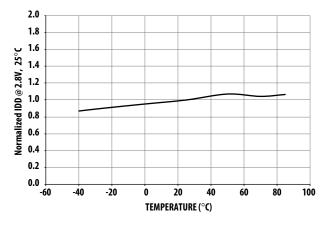

Figure 6. Normalized IDD vs VDD

Figure 7. Normalized IDD vs Temperature

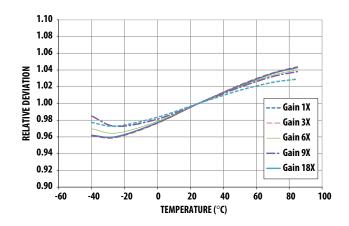

Figure 8. ALS vs Temperature @ 1000 LUX (White LED)

## **System State Machine**

#### Start Up after Power-On or Software Reset

The main state machine is set to "Start State" during power-on or software reset. As soon as the reset is released, the internal oscillator is started and the programmed I<sup>2</sup>C address and the trim values are read from the internal non volatile memory (NVM) trimming data block. The device enters Standby Mode as soon as the Idle State is reached.

NOTE: As long as the  $I^2C$  address has not yet been read, the device will respond with NACK to any  $I^2C$  command and ignore any request to avoid responding to a wrong  $I^2C$  address.

#### **Standby Mode**

Standby Mode is the default mode after power-up. In this state, the oscillator, all internal support blocks, and the ADCs are switched off but I<sup>2</sup>C communication is fully supported.

#### **Light Sensor Operation**

Light Sensor (LS) measurements can be activated by setting the LS\_EN bit to 1 in the MAIN\_CTRL register.

In Light Sensor mode the user can select to activate either ALS or CS operation mode. ALS mode is activated by setting CS\_Mode bit to 0 while CS mode is activated by CS\_Mode bit set to 1 in the MAIN\_CTRL register.

As soon as Light Sensor become activated through  $I^2C$  command, the internal support blocks are powered on. Once the voltages and currents are settled (typically after 5ms), the state machine checks for trigger events from a measurement scheduler to start the LS conversions according to the selected measurement repeat rates.

Once LS\_EN is changed back to 0, a conversion running on the respective sensor will be completed and the relevant ADCs and support blocks will move to standby mode thereafter.

## **Light Sensor Interrupt**

The LS interrupt is enabled by LS\_INT\_EN=1. It can function as either threshold triggered (LS\_VAR\_MODE=0) or variance trigged (LS\_VAR\_MODE=1). The LS interrupt source generator can work on any of the four LS channels (R, G, B, IR). The LS interrupt source is selected by the LS\_INT\_SEL bits in the INT\_CFG register.

The Light Sensor threshold interrupt is enabled with  $LS_INT_EN = 1$  and  $LS_VAR_MODE = 0$ . It is set when the data of the selected  $LS_DATA$  input register ( $LS_RED$ ,  $LS_GREEN$ ,  $LS_BLUE$ ,  $LS_IR$ ) is above the upper or below the lower threshold for a specified number of consecutive measurements.

The Light Sensor variance interrupt is enabled with LS\_INT\_EN = 1 and LS\_VAR\_MODE = 1. It is set when the absolute value of the difference between the previous and current LS\_DATA data value is above the decoded LS variance threshold for a specified number of consecutive measurements.

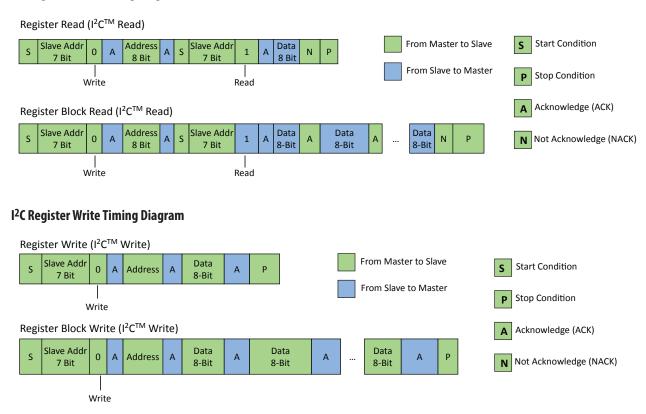

# I<sup>2</sup>C Protocol

Interface and control of the APDS-9250 is accomplished through an I<sup>2</sup>C serial compatible interface (standard or fast mode) to a set of registers that provide access to device control functions and output data. The device supports a single slave address of 0x52 hex using 7 bit addressing protocol. (Contact factory for other addressing options.)

# I<sup>2</sup>C Register Read

The registers can be read individually or in block read mode. When two or more bytes are read in block read mode, reserved register addresses are skipped and the next valid address is referenced. If the last valid address has been reached, but the master continues with the block read, the address counter in the device will not roll over and the device returns 00HEX for every subsequent byte read.

The block read operation is the only way to ensure correct data read out of multi-byte registers and to avoid splitting of results with HIGH and LOW bytes originating from different conversions. During block read access on LS and PS result registers, the result update is blocked.

If a read access is started on an address belonging to a non-readable register, the device will return NACK until the  $I^2C^{TM}$  operation is ended.

Read operations must follow the timing diagram shown below.

# **I<sup>2</sup>C Register Write**

The device registers can be written to individually or in block write mode. When two or more bytes are written in block write mode, reserved registers and read-only registers are skipped. The transmitted data is automatically applied to the next writable register. If a register includes read (R) and read/write (RW) bits, the register is not skipped. Data written to read-only bits are ignored.

If the last valid address of the device address range is reached but the master attempts to continue the block write operation, the address counter of the device will not roll over. The device will return NACK for every following byte sent by the master until the  $l^2C^{TM}$  operation is ended.

If a write access is started on an address belonging to a non-writeable register, the device will return NACK until the  $I^2C^{TM}$  operation is ended.

Write operations must follow the timing diagram shown below.

#### I<sup>2</sup>C Register Read Timing Diagram

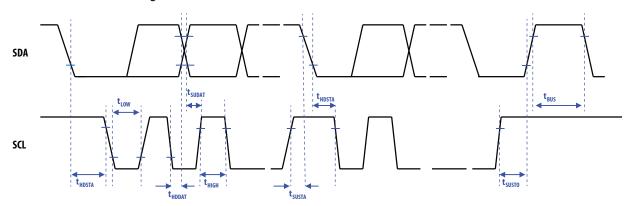

# I<sup>2</sup>C Interface – Bus Timing

# **Bus Timing Characteristics**

| Parameter                                                         | Symbol             | Standard Mode | Fast Mode | Units |

|-------------------------------------------------------------------|--------------------|---------------|-----------|-------|

| Maximum SCL Clock Frequency                                       | f <sub>SCL</sub>   | 100           | 400       | kHz   |

| Minimum START Condition Hold Time Relative to SCL Edge            | t <sub>DSTA</sub>  | 4             |           | μs    |

| Minimum SCL Clock Low Width                                       | t <sub>LOW</sub>   | 4.7           |           | μs    |

| Minimum SCL Clock High Width                                      | t <sub>HIGH</sub>  | 4             |           | μs    |

| Minimum START Condition Setup Time Relative to SCL Edge           | tsusta             | 4.7           |           | μs    |

| Minimum Data Hold Time on SDA Relative to SCL Edge                | t <sub>HDDAT</sub> | 0             |           | μs    |

| Minimum Data Setup Time on SDA Relative to SCL Edge               | t <sub>SUDAT</sub> | 0.1           | 0.1       | μs    |

| Minimum STOP Condition Setup Time on SCL                          | tsusto             | 4             |           | μs    |

| Minimum Bus Free Time Between Stope Condition and Start Condition | t <sub>BUS</sub>   | 4.7           |           | μs    |

# **Register set:**

The APDS-9250 is controlled and monitored by data registers and a command register accessed through the serial interface. These registers provide for a variety of control functions and can be read to determine results of the ADC conversions.

| Address      | Туре | Name            | Description                                       | <b>Reset Value</b> |

|--------------|------|-----------------|---------------------------------------------------|--------------------|

| 00HEX        | RW   | MAIN_CTRL       | LS operation mode control, SW reset               | 00HEX              |

| 04HEX        | RW   | LS_MEAS_RATE    | LS measurement rate and resolution in active mode | 22HEX              |

| 05HEX        | RW   | LS_GAIN         | LS analog gain range                              | 01HEX              |

| 06HEX        | R    | PART_ID         | Part number ID and revision ID                    | B2HEX              |

| 07HEX        | R    | MAIN_STATUS     | Power-on status, interrupt status, data status    | 20HEX              |

| <b>OAHEX</b> | R    | LS_DATA_IR_0    | IR ADC measurement data - LSB                     | 00HEX              |

| OBHEX        | R    | LS_DATA_IR_1    | IR ADC measurement data                           | 00HEX              |

| <b>OCHEX</b> | R    | LS_DATA_IR_2    | IR ADC measurement data - MSB                     | 00HEX              |

| 0DHEX        | R    | LS_DATA_GREEN_0 | Green ADC measurement data - LSB                  | 00HEX              |

| <b>OEHEX</b> | R    | LS_DATA_GREEN_1 | Green ADC measurement data                        | 00HEX              |

| OFHEX        | R    | LS_DATA_GREEN_2 | Green ADC measurement data - MSB                  | 00HEX              |

| 10HEX        | R    | LS_DATA_BLUE_0  | Blue ADC measurement data - LSB                   | 00HEX              |

| 11HEX        | R    | LS_DATA_BLUE_1  | Blue ADC measurement data                         | 00HEX              |

| 12HEX        | R    | LS_DATA_BLUE_2  | Blue ADC measurement data - MSB                   | 00HEX              |

| 13HEX        | R    | LS_DATA_RED_0   | Red ADC measurement data - LSB                    | 00HEX              |

| 14HEX        | R    | LS_DATA_RED_1   | Red ADC measurement data                          | 00HEX              |

| 15HEX        | R    | LS_DATA_RED_2   | Red ADC measurement data - MSB                    | 00HEX              |

| 19HEX        | RW   | INT_CFG         | Interrupt configuration                           | 10HEX              |

| 1AHEX        | RW   | INT_PERSISTENCE | Interrupt persist setting                         | 00HEX              |

| 21HEX        | RW   | LS_THRES_UP_0   | LS interrupt upper threshold, LSB                 | FFHEX              |

| 22HEX        | RW   | LS_THRES_UP_1   | LS interrupt upper threshold                      | FFHEX              |

| 23HEX        | RW   | LS_THRES_UP_2   | LS interrupt upper threshold, MSB                 | <b>OFHEX</b>       |

| 24HEX        | RW   | LS_THRES_LOW_0  | LS interrupt lower threshold, LSB                 | 00HEX              |

| 25HEX        | RW   | LS_THRES_LOW_1  | LS interrupt lower threshold                      | 00HEX              |

| 26HEX        | RW   | LS_THRES_LOW_2  | LS interrupt lower threshold, MSB                 | 00HEX              |

| 27HEX        | RW   | LS_THRES_VAR    | LS interrupt variance threshold                   | 00HEX              |

|              |      |                 |                                                   |                    |

#### MAIN\_CTRL

Default Value : 00HEX

| 7 | 6 | 5 | 4        | 3 | 2       | 1     | 0 |   |

|---|---|---|----------|---|---------|-------|---|---|

| 0 | 0 | 0 | SW_Reset | 0 | CS_Mode | LS_EN | 0 | C |

FIELD

BIT

DESCRIPTION

SW\_Reset

4

1 = Reset will be triggered

CS\_Mode

2

0 = ALS, IR and compensation channels activated 1 = All RGB+IR + compensation channels activated

LS\_EN

1

1 = Light sensor active 0 = Light sensor standby

Writing to this register stops the ongoing measurements and starts new measurements (depends on the enable bit).

## LS\_MEAS\_RATE

Default Value : 22HEX

| 7 | 6     | 5               | 4     | 3 | 2    | 1           | 0    |

|---|-------|-----------------|-------|---|------|-------------|------|

| 0 | LS Re | esolution/Bit \ | Width | 0 | LS N | leasurement | Rate |

0X04

| FIELD                      | BIT | DESCRIPTION                                                                                                                                                                                |

|----------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LS<br>Resolution/Bit Width | 6:4 | 000 : 20 bit – 400ms<br>001 : 19 bit – 200ms<br>010 : 18 bit – 100ms (default)<br>011 : 17 bit – 50ms<br>100 : 16 bit – 25ms<br>101 : 13 bit – 3.125ms<br>110 : Reserved<br>111 : reserved |

| LS<br>Measurement Rate     | 2:0 | 000 – 25ms<br>001 – 50ms<br>010 – 100ms (default)<br>011 – 200ms<br>100 – 500ms<br>101 – 1000ms<br>110 – 2000ms<br>111 – 2000ms                                                            |

When the measurement repeat rate is programmed to be faster than possible for the specified ADC measurement time, the repeat rate will be lower than programmed (maximum speed).

Writing to this register stops the ongoing measurement and starts new measurements (depending on the respective bits)

# LS\_GAIN

Default Value : 01HEX

| 7 | 6 | 5 | 4 | 3 | 2 | 1          | 0 |    |

|---|---|---|---|---|---|------------|---|----|

| 0 | 0 | 0 | 0 | 0 |   | Gain Range |   | ох |

| FIELD      | BIT | DESCRIPTION                                                                   |

|------------|-----|-------------------------------------------------------------------------------|

| Gain Range | 2:0 | 000 : Gain 1<br>001 : Gain 3<br>010 : Gain 6<br>011 : Gain 9<br>100 : Gain 18 |

The channels of the light sensor always run on the same gain range setting. Sensitivity settings correlate between the channels. Result output in Lux is available from ALS/green channel.

Writing to this register stops the ongoing measurement and starts new measurements (depending on the respective bits)

#### PART\_ID

Default Value : B2HEX

|   | 7 | 6   | 5     | 4 | 3 | 2      | 1      | 0 | ] |

|---|---|-----|-------|---|---|--------|--------|---|---|

| [ |   | Par | rt ID |   |   | Revisi | ion ID |   | 0 |

0X06

| FIELD          | BIT | DESCRIPTION                   |

|----------------|-----|-------------------------------|

| Part Number ID | 7:4 | Part number ID                |

| Revision ID    | 3:0 | Revision ID of the component. |

# MAIN\_STATUS

Default Value : 20HEX

| 7 | 6 | 5                     | 4                         | 3                 | 2 | 1 | 0 |     |

|---|---|-----------------------|---------------------------|-------------------|---|---|---|-----|

| 0 | 0 | Power<br>On<br>Status | LS<br>Interrupt<br>Status | LS Data<br>Status | 0 | 0 | 0 | 0X0 |

0X07

| FIELD               | BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power On Status     | 5   | <ul> <li>1 = Part went through a power-up event, either because the part was turned on or because there was power supply disturbance.</li> <li>All interrupt threshold settings in the registers have been reset to power-on default states and should be examined if necessary.</li> <li>The flag is cleared after the register is read.</li> </ul> |

| LS Interrupt Status | 4   | 0 : Interrupt condition not fulfilled (default)<br>1 : Interrupt condition fulfilled (cleared after read)                                                                                                                                                                                                                                            |

| LS Data Status      | 3   | 0 : old data, already read (default)<br>1 : new data, not yet read (cleared after read)                                                                                                                                                                                                                                                              |

# LS\_DATA\_IR

Default Value : 00HEX, 00HEX, 00HEX

| 7 | 6                   | 5 | 4        | 3           | 2         | 1           | 0 |      |

|---|---------------------|---|----------|-------------|-----------|-------------|---|------|

|   |                     |   | LS_DATA_ | _IR_0 [7:0] |           |             |   | 0X0A |

|   | LS_DATA_IR_1 [15:8] |   |          |             |           |             |   | 0X0B |

| 0 | 0                   | 0 | 0        |             | LS_DATA_I | R_2 [19:16] |   | 0X0C |

IR channel output data (unsigned integer, 13 to 20 bit, LSB aligned)

The IR channel output is already temperature compensated internally:

LS\_DATA\_IR - (IRint - LS\_DATA\_COMP)

When an  $l^2C^{\mathbb{M}}$  read operation is active and points to an address in the range 07HEX to 18HEX, all registers in this range are locked until the  $l^2C^{\mathbb{M}}$  read operation is completed or this address range is left.

This guarantees that the data in the registers comes from the same measurement even if an additional measurement cycle ends during the read operation. New measurement data is stored into temporary registers and the actual LS\_DATA registers are updated as soon as there is no on-going  $l^2C^{m}$  read operation to the address range 07HEX to 18HEX.

| Reg 0AHEX | Bit[7:0] | IR diode data least significant data byte |

|-----------|----------|-------------------------------------------|

| Reg 0BHEX | Bit[7:0] | IR diode data intervening data byte       |

| Reg 0CHEX | Bit[3:0] | IR diode data most significant data byte  |

#### LS\_DATA\_GREEN

Default Value : 00HEX, 00HEX, 00HEX

| 7 | 6                      | 5 | 4          | 3            | 2          | 1             | 0    |      |

|---|------------------------|---|------------|--------------|------------|---------------|------|------|

|   |                        |   | LS_DATA_GI | REEN_0 [7:0] |            |               |      | 0X0D |

|   | LS_DATA_GREEN_1 [15:8] |   |            |              |            |               | OXOE |      |

| 0 | 0                      | 0 | 0          |              | LS_DATA_GR | EEN_2 [19:16] |      | 0X0F |

ALS/CS Green channel digital output data.

The channel output is already temperature compensated internally:

LS\_DATA\_GREEN = (Greenint – LS\_DATA\_COMP)

When an  $l^2C^{\mathbb{M}}$  read operation is active and points to an address in the range 07HEX to 18HEX, all registers in this range are locked until the  $l^2C^{\mathbb{M}}$  read operation is completed or this address range is left.

This guarantees that the data in the registers comes from the same measurement even if an additional measurement cycle ends during the read operation. New measurement data is stored into temporary registers and the actual LS\_DATA registers are updated as soon as there is no on-going  $I^2C^m$  read operation to the address range 07HEX to 18HEX.

Reg 0DHEX Bit[7:0] ALS / Green diode data least significant data byte

Reg 0EHEX Bit[7:0] ALS / Green diode data intervening data byte

Reg 0FHEX Bit[3:0] ALS / Green diode data most significant data byte

## LS\_DATA\_BLUE

Default Value : 00HEX, 00HEX, 00HEX

| 7 | 6                     | 5 | 4         | 3           | 2          | 1            | 0    |      |

|---|-----------------------|---|-----------|-------------|------------|--------------|------|------|

|   |                       |   | LS_DATA_B | LUE_0 [7:0] |            |              |      | 0X10 |

|   | LS_DATA_BLUE_1 [15:8] |   |           |             |            |              | 0X11 |      |

| 0 | 0                     | 0 | 0         |             | LS_DATA_BL | UE_2 [19:16] |      | 0X12 |

CS Blue channel output data.

The channel output is already temperature compensated internally:

LS\_DATA\_BLUE = (Blueint – LS\_DATA\_COMP)

When an  $l^2C^{\mathbb{M}}$  read operation is active and points to an address in the range 07HEX to 18HEX, all registers in this range are locked until the  $l^2C^{\mathbb{M}}$  read operation is completed or this address range is left.

This guarantees that the data in the registers comes from the same measurement even if an additional measurement cycle ends during the read operation. New measurement data is stored into temporary registers and the actual LS\_DATA registers are updated as soon as there is no on-going  $l^2C^{m}$  read operation to the address range 07HEX to 18HEX.

| Reg 10HEX | Bit[7:0] | Blue diode data least significant data byte |

|-----------|----------|---------------------------------------------|

| Reg 11HEX | Bit[7:0] | Blue diode data intervening data byte       |

| Reg 12HEX | Bit[3:0] | Blue diode data most significant data byte  |

#### LS\_DATA\_RED

Default Value : 00HEX, 00HEX, 00HEX

| 7                    | 6 | 5 | 4 | 3 | 2         | 1            | 0 |      |  |

|----------------------|---|---|---|---|-----------|--------------|---|------|--|

| LS_DATA_RED_0 [7:0]  |   |   |   |   |           |              |   |      |  |

| LS_DATA_RED_1 [15:8] |   |   |   |   |           |              |   |      |  |

| 0                    | 0 | 0 | 0 |   | LS_DATA_R | ED_2 [19:16] |   | 0X15 |  |

The channel output is already temperature compensated internally:

LS\_DATA\_RED = (Redint – LS\_DATA\_COMP)

When an  $l^2C^{m}$  read operation is active and points to an address in the range 07HEX to 18HEX, all registers in this range are locked until the  $l^2C^{m}$  read operation is completed or this address range is left.

This guarantees that the data in the registers comes from the same measurement even if an additional measurement cycle ends during the read operation. New measurement data is stored into temporary registers and the actual LS\_DATA registers are updated as soon as there is no on-going  $l^2C^{m}$  read operation to the address range 07HEX to 18HEX.

| Reg 13HEX | Bit[7:0] | Red diode data least significant data byte |

|-----------|----------|--------------------------------------------|

| Reg 14HEX | Bit[7:0] | Red diode data intervening data byte       |

| Reg 15HEX | Bit[3:0] | Red diode data most significant data byte  |

# INT\_CFG

Default Value : 10HEX

| 7 | 6 | 5     | 4              | 3                        | 2                      | 1 | 0 | ]    |

|---|---|-------|----------------|--------------------------|------------------------|---|---|------|

| 0 | 0 |       | errupt<br>urce | LS Variation<br>Int Mode | LS Interrupt<br>Enable | 0 | 0 | 0X19 |

| 0 | 0 | LS_IN | IT_SEL         | LS_VAR_MODE              | LS_INT_EN              | 0 | 0 |      |

| FIELD       | BIT | DESCRIPTION                                                                                  |

|-------------|-----|----------------------------------------------------------------------------------------------|

| LS_INT_SEL  | 5:4 | 00 : IR channel<br>01 : ALS/Green channel (default)<br>10 : Red channel<br>11 : Blue channel |

| LS_VAR_MODE | 3   | 0 : LS threshold interrupt mode (default)<br>1 : LS variation interrupt mode                 |

| LS_INT_EN   | 2   | 0 : LS Interrupt disabled (default)<br>1 : LS Interrupt enabled                              |

# INT\_PERSISTENCE

Default Value : 00HEX

| 7 | 6          | 5 | 4 | 3 | 2 | 1 | 0 | ]    |

|---|------------|---|---|---|---|---|---|------|

|   | LS_PERSIST |   |   | 0 | 0 | 0 | 0 | 0X1A |

This register sets the number of similar consecutive LS interrupt events that must occur before the interrupt is asserted.

| FIELD      | BIT | DESCRIPTION                                                                                                                                                                                                                            |

|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LS_PERSIST | 7:4 | 0000 : Every LS value out of threshold range (default) asserts an interrupt<br>0001 : 2 consecutive LS values out of threshold range assert an interrupt<br>1111 : 16 consecutive LS values out of threshold range assert an interrupt |

## LS\_THRES\_UP

Default Value : FFHEX, FFHEX, OFHEX

| 7 | 6                    | 5 | 4 | 3 | 2          | 1            | 0 |      |  |  |

|---|----------------------|---|---|---|------------|--------------|---|------|--|--|

|   | LS_THRES_UP_0 [7:0]  |   |   |   |            |              |   |      |  |  |

|   | LS_THRES_UP_1 [15:8] |   |   |   |            |              |   |      |  |  |

| 0 | 0                    | 0 | 0 |   | LS_THRES_U | JP_2 [19:16] |   | 0X23 |  |  |

LS\_THRES\_UP sets the upper threshold value for the LS interrupt. The Interrupt Controller compares the value in LS\_ THRES\_UP against measured data in the LS\_DATA registers of the selected LS interrupt channel. It generates an interrupt event if DATA exceeds the threshold level.

The data format for LS\_THRES\_UP must match that of the LS\_DATA registers.

| Reg 21HEX | Bit[7:0] | LS upper interrupt threshold value, LSB              |

|-----------|----------|------------------------------------------------------|

| Reg 22HEX | Bit[7:0] | LS upper interrupt threshold value, intervening byte |

| Reg 23HEX | Bit[3:0] | LS upper interrupt threshold value, MSB              |

#### LS\_THRES\_LOW

Default value: 00HEX, 00HEX, 00HEX

| 7                    | 6                                | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |  |

|----------------------|----------------------------------|---|---|---|---|---|---|--|--|--|--|

| LS_THRES_LOW_0 [7:0] |                                  |   |   |   |   |   |   |  |  |  |  |

|                      | LS_THRES_LOW_1 [15:8]            |   |   |   |   |   |   |  |  |  |  |

| 0                    | 0 0 0 0 0 LS_THRES_LOW_2 [19:16] |   |   |   |   |   |   |  |  |  |  |

LS\_THRES\_LOW sets the lower threshold value for the LS interrupt. The Interrupt Controller compares the value in LS\_THRES\_LOW against measured data in the LS\_DATA registers of the selected LS interrupt channel. It generates an interrupt event if the LS\_DATA is below the threshold level.

The data format for LS\_THRES\_LOW must match that of the LS\_DATA registers.

Reg 24HEX Bit[7:0] LS lower interrupt threshold value, LSB

Reg 25HEX Bit[7:0] LS lower interrupt threshold value, intervening byte

Reg 26HEX Bit[3:0] LS lower interrupt threshold value, MSB

#### LS\_THRES\_VAR

Default Value : 00HEX

| 7 | 6 | 5 | 4 | 3 | 2 | 1           | 0 | ]    |

|---|---|---|---|---|---|-------------|---|------|

| 0 | 0 | 0 | 0 | 0 |   | _S_THRES_VA | R | 0X27 |

| FIELD        | BIT | DESCRIPTION                                                                                                                                                                                                                                                                                                                                            |

|--------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LS_THRES_VAR | 2:0 | 000 : new LS_DATA varies by 8 counts compared to previous result<br>001 : new LS_DATA varies by 16 counts compared to previous result<br>010 : new LS_DATA varies by 32 counts compared to previous result<br>011 : new LS_DATA varies by 64 counts compared to previous result<br>111 : new LS_DATA varies by 1024 counts compared to previous result |

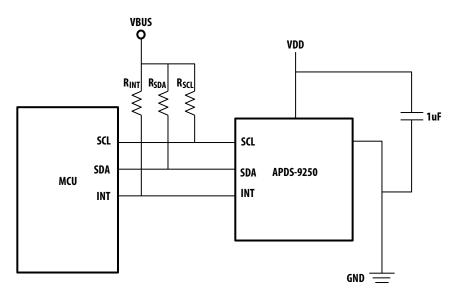

# **Application Information Hardware**

The application hardware circuit for using implementing RGB, ALS and IR solution is simple with the APDS-9250 and is shown in following figure. The bypass capacitor is placed as close to the device package and is connected directly to the power source and to the ground, as shown in Figure below. It allows the AC component of the VDD to pass through to ground. Suggested to have bypass capacitor that have low effective series resistance (ESR) and low effective series inductance (ESI), such as the common ceramic types, which provide a low impedance path to ground at high frequencies to handle transient currents caused by internal logic switching.

Pull-up resistors, RSDA and RSCL, maintain the SDA and SCL lines at a high level when the bus is free and ensure the signals are pulled up from a low to a high level within the required rise time. A pull-up resistor, RINT, is also required for the interrupt (INT), which functions as a wired-AND signal in a similar fashion to the SCL and SDA lines. A typical impedance value of 10 k $\Omega$  can be used.

For a complete description of I<sup>2</sup>C maximum and minimum R1 and R2 values, please review the I<sup>2</sup>C Specification at http://www.semiconductors.philips.com.

# **Package Outline Dimensions**

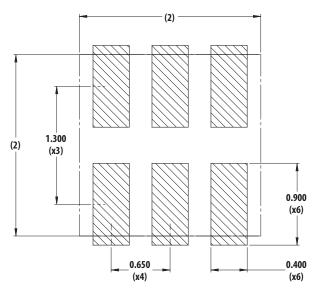

**PCB Pad Layout**

Dimensions are in mm

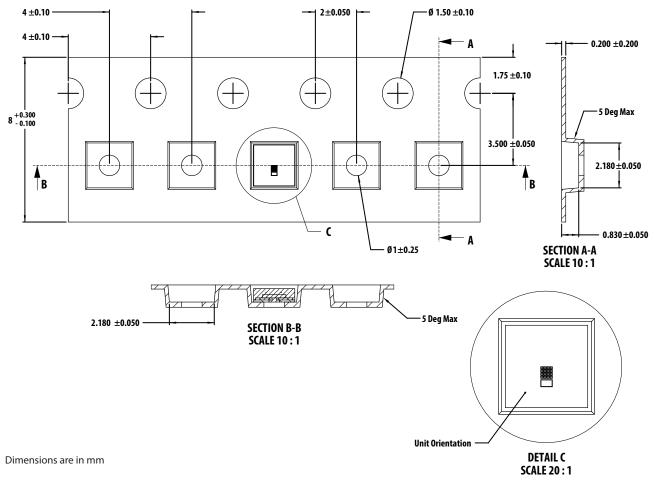

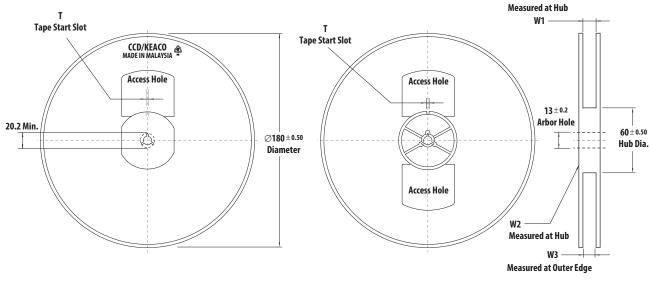

# **Tape Dimensions**

## **Reel Dimensions**

#### **Front View**

**Back View**

**Side View**

| TAPE WIDTH | T          | W1                 | W2       | W3                  |

|------------|------------|--------------------|----------|---------------------|

| 8 MM       | $3\pm0.50$ | 8.4 + 1.5<br>- 0.0 | 14.4 MAX | 7.9 MIN<br>10.9 MAX |

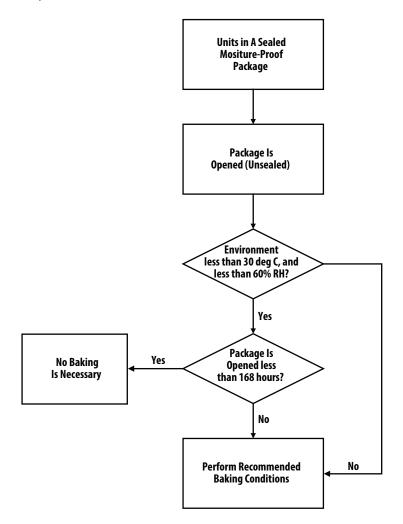

# **Moisture Proof Packaging**

All APDS-9250 options are shipped in moisture proof package. Once opened, moisture absorption begins. This part is compliant to JEDEC MSL 3.

#### **Recommended Storage Conditions**

| Storage Temperature | 10° C to 30° C |

|---------------------|----------------|

| Relative Humidity   | Below 60% RH   |

#### **Time from Unsealing to Soldering**

After removal from the bag, the parts should be soldered within seven days if stored at the recommended storage conditions. When MBB (Moisture Barrier Bag) is opened and the parts are exposed to the recommended storage conditions more than seven days the parts must be baked before reflow to prevent damage to the parts.

#### **Baking conditions**

If the parts are not stored per the recommended storage conditions they must be baked before reflow to prevent damage to the parts.

| Package  | Temp. | Time     |

|----------|-------|----------|

| In Reels | 60°C  | 48 hours |

| In Bulk  | 100°C | 4 hours  |

Note: Baking should only be done once.

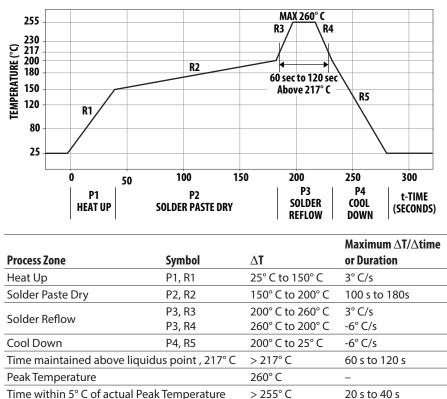

#### **Recommended Reflow Profile**

Time 25° C to Peak Temperature

25° C to 260° C

8 mins

The reflow profile is a straight-line representation of a nominal temperature profile for a convective reflow solder process. The temperature profile is divided into four process zones, each with different  $\Delta T/\Delta$ time temperature change rates or duration. The  $\Delta T/\Delta$ time rates or duration are detailed in the above table. The temperatures are measured at the component to printed circuit board connections.

In process zone P1, the PC board and component pins are heated to a temperature of 150° C to activate the flux in the solder paste. The temperature ramp up rate, R1, is limited to 3° C per second to allow for even heating of both the PC board and component pins.

Process zone P2 should be of sufficient time duration (100 to 180 seconds) to dry the solder paste. The temperature is raised to a level just below the liquidus point of the solder.

Process zone P3 is the solder reflow zone. In zone P3, the temperature is quickly raised above the liquidus point of solder to 260° C (500° F) for optimum results. The dwell

time above the liquidus point of solder should be between 60 and 120 seconds. This is to assure proper coalescing of the solder paste into liquid solder and the formation of good solder connections. Beyond the recommended dwell time the intermetallic growth within the solder connections becomes excessive, resulting in the formation of weak and unreliable connections. The temperature is then rapidly reduced to a point below the solidus temperature of the solder to allow the solder within the connections to freeze solid.

Process zone P4 is the cool down after solder freeze. The cool down rate, R5, from the liquidus point of the solder to  $25^{\circ}$  C (77° F) should not exceed 6° C per second maximum. This limitation is necessary to allow the PC board and component pins to change dimensions evenly, putting minimal stresses on the component.

It is recommended to perform reflow soldering no more than twice.

**DISCLAIMER:** Avago's products and software are not specifically designed, manufactured or authorized for sale as parts, components or assemblies for the planning, construction, maintenance or direct operation of a nuclear facility or for use in medical devices or applications. Customer is solely responsible, and waives all rights to make claims against Avago or its suppliers, for all loss, damage, expense or liability in connection with such use.

For product information and a complete list of distributors, please go to our web site: www.avagotech.com

Avago Technologies, and the A logo are trademarks of Avago Technologies in the United States and other countries. Data subject to change. Copyright © 2005-2015 Avago Technologies. All rights reserved. AV02-4733EN - November 13, 2015

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.