# System Motor Driver Series for CD·DVD·BD Player

# 6ch System Motor Driver For Car AV

#### BD8255MUV-M

## **General Description**

BD8255MUV-M is a 6ch motor driver developed for driving coil actuator (2ch), sled motor (2ch), a loading motor, and a three-phase motor for spindle. This can drive the motor and coil of CD/DVD drive.

It has a built-in Serial Peripheral Interface (SPI) with a max clock frequency of 35MHz, for interfacing with the Micro-controller.

# **Features**

- Built-in Serial Peripheral Interface(SPI)

- High efficiency at 180° PWM for spindle driver

- Built-in 2-channel stepping motor driver for sled

- Built-in loading driver short-circuit protection

# **Applications**

- Car navigation

- Car AV

#### **Key Specifications**

■ Ron(Spindle):  $1.0\Omega(Typ)$ ■ Ron(Loading):  $1.0\Omega(Typ)$

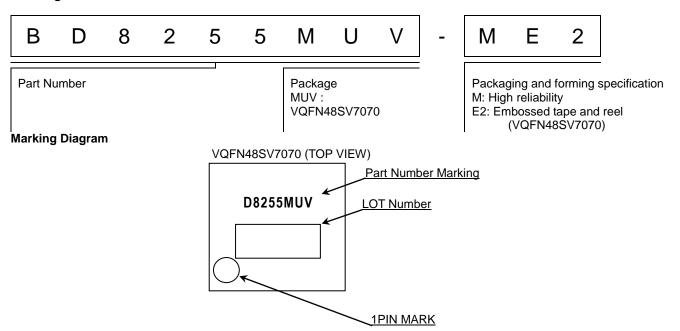

Package W(Typ VQFN48SV7070 7.00mr

W(Typ) **x** D(Typ) **x** H(Max) 7.00mm **x** 7.00mm **x** 1.00mm

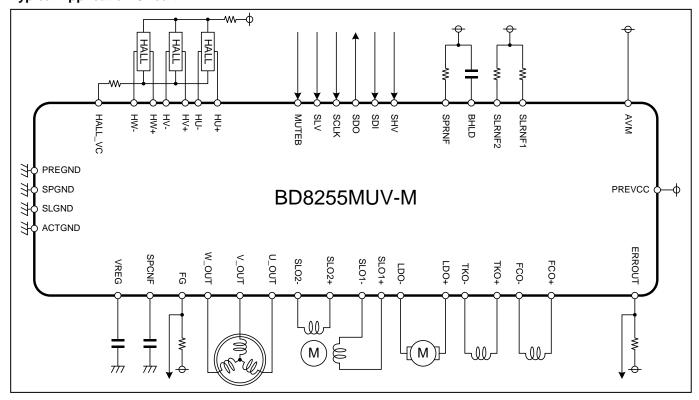

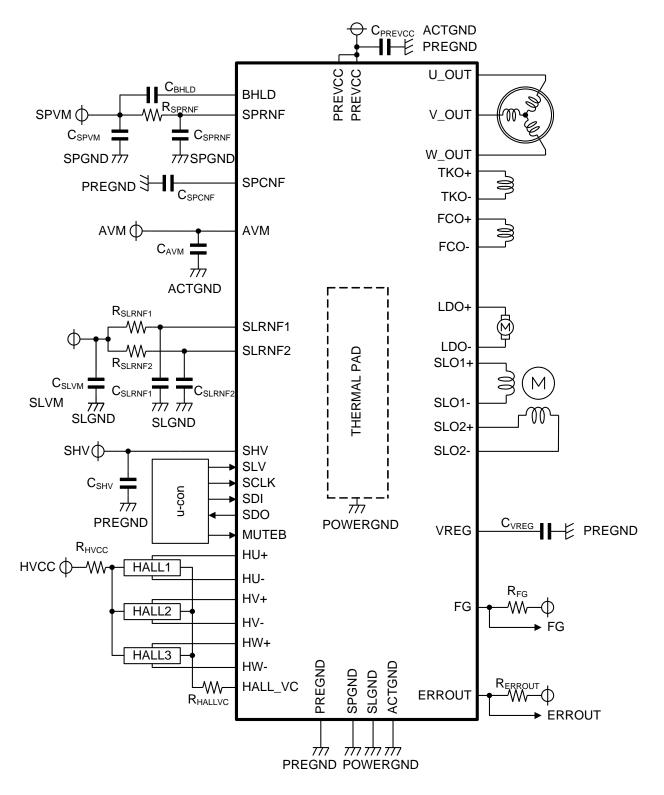

### **Typical Application Circuit**

Figure 1. Typical Application Circuit

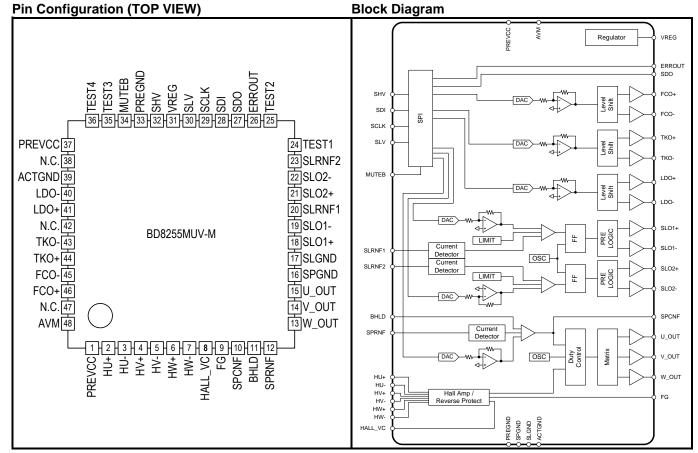

Figure 2. Pin configuration

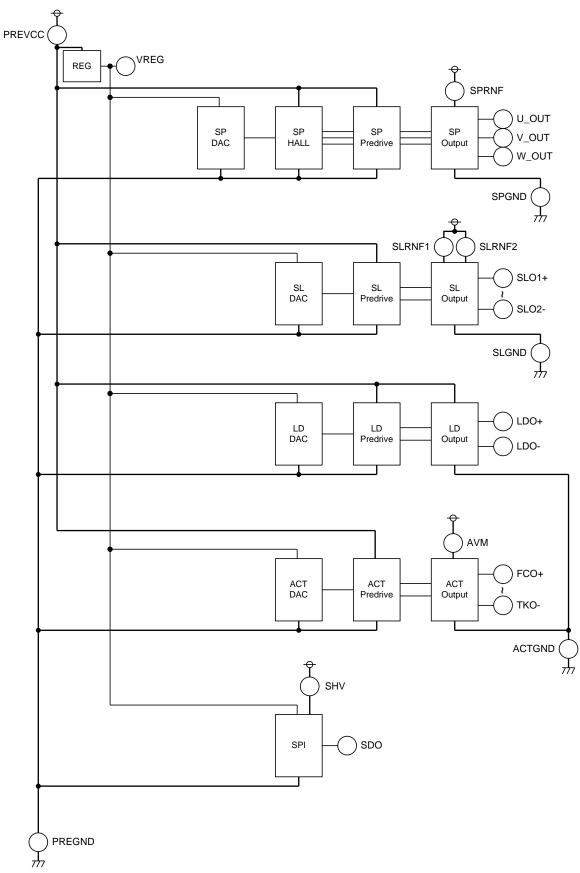

Figure 3. Block diagram

# **Pin Description**

| 1 111 0 | escription |                                             |     |          |                                             |

|---------|------------|---------------------------------------------|-----|----------|---------------------------------------------|

| No.     | Pin Name   | Function                                    | No. | Pin Name | Function                                    |

| 1       | PREVCC     | Pre driver power supply <sup>(Note 1)</sup> | 25  | TEST2    | TEST Pin (use with GND short)               |

| 2       | HU+        | Hall amp. U positive input                  | 26  | ERROUT   | Serial data error output                    |

| 3       | HU-        | Hall amp. U negative input                  | 27  | SDO      | Serial data output                          |

| 4       | HV+        | Hall amp. V positive input                  | 28  | SDI      | Serial data input                           |

| 5       | HV-        | Hall amp. V negative input                  | 29  | SCLK     | Serial clock input                          |

| 6       | HW+        | Hall amp. W positive input                  | 30  | SLV      | Serial slave input                          |

| 7       | HW-        | Hall amp. W negative input                  | 31  | VREG     | Inside power supply for SPI logic           |

| 8       | HALL_VC    | Hall bias                                   | 32  | SHV      | Power supply for SDO output                 |

| 9       | FG         | FG output                                   | 33  | PREGND   | Pre block ground                            |

| 10      | SPCNF      | Spindle driver loop filter                  | 34  | MUTEB    | Mute input                                  |

| 11      | BHLD       | Spindle current bottom hold                 | 35  | TEST3    | TEST Pin (use open)                         |

| 12      | SPRNF      | Spindle power supply and current sense      | 36  | TEST4    | TEST Pin (use open)                         |

| 13      | W_OUT      | Spindle driver W output                     | 37  | PREVCC   | Pre driver power supply <sup>(Note 1)</sup> |

| 14      | V_OUT      | Spindle driver V output                     | 38  | N.C.     | -                                           |

| 15      | U_OUT      | Spindle driver U output                     | 39  | ACTGND   | Actuator and loading power ground           |

| 16      | SPGND      | Spindle power ground                        | 40  | LDO-     | Loading driver negative output              |

| 17      | SLGND      | Sled power ground                           | 41  | LDO+     | Loading driver positive output              |

| 18      | SLO1+      | Sled driver 1 positive output               | 42  | N.C.     | -                                           |

| 19      | SLO1-      | Sled driver 1 negative output               | 43  | TKO-     | Tracking driver negative output             |

| 20      | SLRNF1     | Sled 1 power supply and current sense       | 44  | TKO+     | Tracking driver positive output             |

| 21      | SLO2+      | Sled driver 2 positive output               | 45  | FCO-     | Focus driver negative output                |

| 22      | SLO2-      | Sled driver 2 negative output               | 46  | FCO+     | Focus driver positive output                |

| 23      | SLRNF2     | Sled 2 power supply and current sense       | 47  | N.C.     | -                                           |

| 24      | TEST1      | TEST Pin (use with GND short)               | 48  | AVM      | Actuator power supply                       |

(Note1) Use with Pin1 and Pin37 are shorted.

Absolute Maximum Ratings (Ta = 25°C)

| Parameter                            | Symbol                                                       | Rating                   | Unit |

|--------------------------------------|--------------------------------------------------------------|--------------------------|------|

| Power MOS power supply voltage       | V <sub>SPRNF</sub> ,V <sub>SLRNF1</sub> ,V <sub>SLRNF2</sub> | 7                        | V    |

| Predriver / BTL power supply voltage | V <sub>PREVCC</sub> ,V <sub>AVM</sub>                        | 7                        | V    |

| Serial Output power supply           | V <sub>SHV</sub>                                             | 7                        | V    |

| Input pin voltage 1                  | V <sub>IN1</sub> (Note 1)                                    | 7                        | V    |

| Output pin voltage 1                 | V <sub>OUT1</sub> (Note 2)                                   | 7                        | V    |

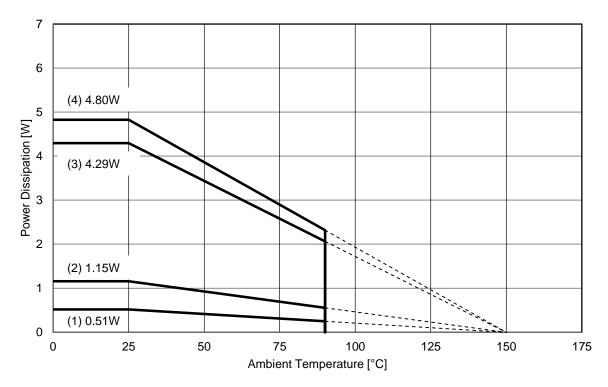

| Power Consumption                    | Pd                                                           | 1.15 <sup>(Note 3)</sup> | W    |

| Operating temperature range          | Topr                                                         | -40 to +90               | °C   |

| Storage temperature range            | Tstg                                                         | -55 to +150              | °C   |

| Junction temperature                 | Tjmax                                                        | 150                      | °C   |

<sup>(</sup>Note 1) BHLD, SPCNF, HU+, HU-, HV+, HV-, HW+, HW-, HALL\_VC, SLV, SCLK, SDI, MUTEB

Caution: Operating the IC over the absolute maximum ratings may damage the IC. In addition, it is impossible to predict all destructive situations such as short-circuit modes, open circuit modes, etc. Therefore, it is important to consider circuit protection measures, like adding a fuse, in case the IC is operated in a special mode exceeding the absolute maximum ratings.

Recommended Operating Conditions (Ta = -40°C to +90°C)

| Description                                             | Ohl                                       |      | Unit                |                     |      |

|---------------------------------------------------------|-------------------------------------------|------|---------------------|---------------------|------|

| Parameter                                               | Symbol                                    | Min. | Тур                 | Max.                | Unit |

| Spindle driver power supply voltage (Note 1)(Note 2)    | V <sub>SPRNF</sub>                        | -    | V <sub>PREVCC</sub> | -                   | V    |

| Sled motor driver power supply voltage (Note 1)(Note 2) | V <sub>SLRNF1</sub> , V <sub>SLRNF2</sub> | -    | $V_{PREVCC}$        | -                   | V    |

| Predriver power supply voltage (Note 1)                 | V <sub>PREVCC</sub>                       | 4.5  | 5                   | 5.5                 | V    |

| Actuator driver power supply voltage (Note 2)           | $V_{AVM}$                                 | 4.5  | 5                   | V <sub>PREVCC</sub> | V    |

| Serial output power supply (Note 2)                     | V <sub>SHV</sub>                          | 3.0  | 3.3                 | 3.6                 | V    |

<sup>(</sup>Note 1) Consider power consumption when deciding power supply voltage.

<sup>(</sup>Note 2) FG, U\_OUT, V\_OUT, W\_OUT, SLO1+, SLO1-, SLO2+, SLO2-, ERROUT, LDO+, LDO-, SDO, VREG, FCO+, FCO-, TKO+, TKO-

<sup>(</sup>Note 3) Ta=25°C, PCB (74.2mm×74.2mm×1.6mm, glass epoxy substrate 1-layer platform, board copper foil area 34.09mm²) mounting. Derated by 9.3mW/°C when operating above 25°C

<sup>(</sup>Note 2) Set the voltage same as V<sub>PREVCC</sub>.

**Electrical Characteristics** (Unless otherwise specified, Ta=25°C,  $V_{PRECC} = V_{SPRNF} = V_{SLRNF1} = V_{SLRNF2} = V_{AVM} = 5V$ ,  $V_{SHV} = 3.3V$ ,  $R_{SPRNF} = 0.33\Omega$ ,  $R_{SLRNF} = 0.56\Omega$ )

| Parameter                                                                                   | Symbol             |                       | Limits |      | Unit  | Conditions                                |

|---------------------------------------------------------------------------------------------|--------------------|-----------------------|--------|------|-------|-------------------------------------------|

|                                                                                             | Cymbol             | Min.                  | Тур    | Max. | Offic | Conditions                                |

| Circuit Current                                                                             | 1                  | 1                     |        | 1    | 1     | T                                         |

| PREVCC Quiescent Current                                                                    | $I_{Q1}$           | -                     | 19     | 32   | mA    | MUTEB=H<br>SPI=72h FE, 70h FE             |

| PREVCC Standby Current                                                                      | I <sub>ST1</sub>   | -                     | 3      | 6    | mA    | MUTEB=L                                   |

| Spindle Driver                                                                              |                    |                       |        |      |       |                                           |

| Hall Bias Voltage                                                                           | $V_{HB}$           | 0.45                  | 0.9    | 1.35 | V     | IHB=10mA                                  |

| Input Bias Current                                                                          | I <sub>HIB</sub>   | -                     | 0.5    | 3    | μA    |                                           |

| Input Level                                                                                 | $V_{HIM}$          | 50                    | -      | -    | mVpp  |                                           |

| Common Mode Input Range                                                                     | $V_{HICM}$         | 1.5                   | -      | 3.8  | V     |                                           |

| Input Dead Zone (One Side)                                                                  | $V_{DZSP}$         | 0                     | 10     | 40   | mV    |                                           |

| Input-Output Gain                                                                           | gm <sub>SP</sub>   | 0.98                  | 1.24   | 1.50 | A/V   | $R_{SPRNF}=0.33\Omega$ , $R_{L}=2\Omega$  |

| Output ON Resistance (Total Sum)                                                            | Ronsp              | -                     | 1.0    | 1.8  | Ω     | IL=500mA                                  |

| Output limit Current                                                                        | I <sub>LIMSP</sub> | 0.85                  | 1.06   | 1.27 | Α     | R <sub>SPRNF</sub> =0.33Ω                 |

| PWM Frequency                                                                               | fosc               | -                     | 100    | -    | kHz   | $R_L=2\Omega$                             |

| FG Output Low Level Voltage                                                                 | $V_{FGL}$          | -                     | 0.1    | 0.3  | V     | 33KΩ pull-up(3.3V)                        |

| Sled Motor Driver                                                                           |                    |                       |        | •    | •     |                                           |

| Input Dead Zone (One Side)                                                                  | $V_{DZSL}$         | 5                     | 15     | 30   | mV    |                                           |

| Input-Output Gain                                                                           | gm <sub>SL</sub>   | 0.84                  | 1.10   | 1.36 | A/V   | $R_{SLRNF1,2}=0.56\Omega$ , $R_L=8\Omega$ |

| Output ON Resistance (Total sum)                                                            | Ronsl              | -                     | 1.8    | 2.5  | Ω     | IL=500mA                                  |

| Output Limit Current                                                                        | I <sub>LIMSL</sub> | 0.79                  | 0.93   | 1.07 | Α     | R <sub>SLRNF1,2</sub> =0.56Ω              |

| PWM Frequency                                                                               | fosc               | -                     | 100    | -    | kHz   | $R_L=8\Omega$                             |

| Actuator Driver                                                                             |                    |                       |        | "    |       |                                           |

| Output Offset Voltage                                                                       | Vofact             | -50                   | 0      | 50   | mV    | Low Gain mode, R <sub>L</sub> =8Ω         |

| Output ON Resistance                                                                        | RONACT             | -                     | 1.5    | 2.0  | Ω     | IL=500mA                                  |

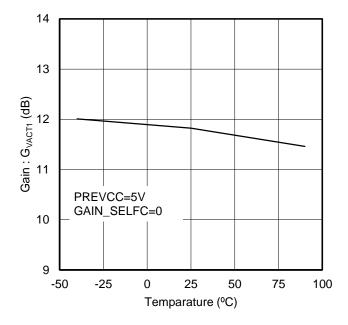

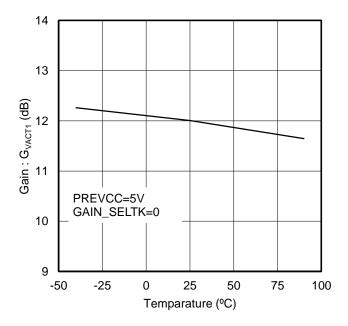

| Voltage Gain 1                                                                              | G <sub>VACT1</sub> | 10.5                  | 11.7   | 12.9 | dB    | Low Gain mode, R <sub>L</sub> =8Ω         |

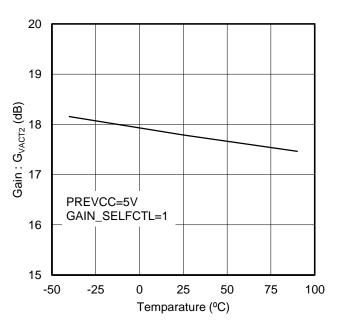

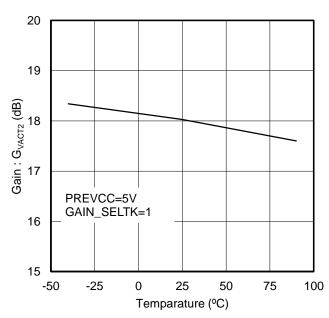

| Voltage Gain 2                                                                              | G <sub>VACT2</sub> | 16.4                  | 17.7   | 18.9 | dB    | High Gain mode, R <sub>L</sub> =8Ω        |

| Loading Driver                                                                              | 1                  |                       |        | 1    |       |                                           |

| Output Offset Voltage                                                                       | $V_{OFLD}$         | -100                  | 0      | 100  | mV    | Low Gain mode, R <sub>L</sub> =8Ω         |

| Output ON Resistance                                                                        | Ronld              | -                     | 1.0    | 1.5  | Ω     | IL=500mA                                  |

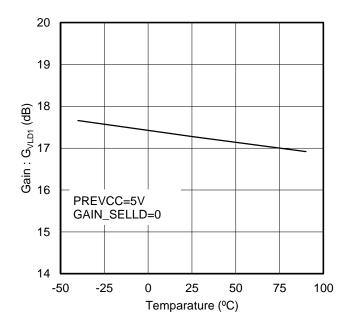

| Voltage Gain 1                                                                              | G <sub>VLD1</sub>  | 15.2                  | 17.2   | 19.2 | dB    | Low Gain mode, R <sub>L</sub> =8Ω         |

| Voltage Gain 2                                                                              | G <sub>VLD2</sub>  | 16.7                  | 18.7   | 20.7 | dB    | High Gain mode, R <sub>L</sub> =8Ω        |

| Protect Sign Output                                                                         | •                  |                       |        | •    | •     |                                           |

| ERROUT Low Level Output Voltage                                                             | $V_{OL2}$          | -                     | 0.1    | 0.3  | V     | 33kΩ pull-up(3.3V)                        |

| Logic Inputs (SDI,SCLK,SLV,MUTEB                                                            |                    |                       |        | 1    | 4     |                                           |

| Low Level Input Voltage                                                                     | V <sub>INL</sub>   | -                     | -      | 0.5  | V     |                                           |

| High Level Voltage                                                                          | $V_{INH}$          | 2.2                   | -      | -    | V     |                                           |

| High Level Current                                                                          |                    |                       | 33     | 66   | 11.0  | SDI,SCLK,MUTEB=3.3V                       |

| (SDI,SCLK,MUTEB)                                                                            | I <sub>INH</sub>   | -                     |        | 00   | μA    | , , , , , , , , , , , , , , , , , , ,     |

| Low Level Current (SLV)                                                                     | I <sub>INL</sub>   | -60                   | -30    | -    | μA    | SLV=0V                                    |

| Logic Output (SDO)                                                                          | 1                  | ,                     |        | 1    |       |                                           |

| Low Level Output Voltage                                                                    | V <sub>OUTL</sub>  | -                     | -      | 0.3  | V     |                                           |

| High Level Output Voltage                                                                   | V <sub>OUTH</sub>  | V <sub>SHV</sub> -0.3 | -      | -    | V     |                                           |

| Function                                                                                    |                    |                       |        |      |       |                                           |

| PREVCC Drop Mute Voltage                                                                    | $V_{MVCC}$         | 3.4                   | 3.8    | 4.0  | V     |                                           |

| TSD                                                                                         |                    |                       |        |      |       |                                           |

| TOD 1 (: T (Note 1)                                                                         |                    | 150                   | 175    | 200  | °C    |                                           |

| TSD Junction Temperature <sup>(Note 1)</sup> TSD Hysteresis Temperature <sup>(Note 1)</sup> | T <sub>TSD</sub>   | 150                   | 175    | 200  |       |                                           |

(Note 1) These items are specified by design, not tested during production

Electrical Characteristics (Unless otherwise specified, Ta=-40°C to 90°C, VPRECC=VSPRNF=VSLRNF1=VSLRNF2=VAVM=5V,

| Veuv=3.3V    | Repone=0.330     | $R_{SLRNF}=0.56\Omega$ ) |

|--------------|------------------|--------------------------|

| V SHV-J.J V. | INSPRINE U.UUSZ. | I VSLRNF TO. JUSZI       |

| Parameter                        | Symbol             |                       | Limits |      | Unit  | Conditions                                  |

|----------------------------------|--------------------|-----------------------|--------|------|-------|---------------------------------------------|

|                                  | Cyrribor           | Min.                  | Тур    | Max. | Offic | Conditions                                  |

| Circuit Current                  |                    |                       |        |      |       |                                             |

| PREVCC Quiescent Current         | I <sub>Q1</sub>    | -                     | 19     | 39   | mA    | MUTEB=H<br>SPI=72h FE, 70h FE               |

| PREVCC Standby Current           | I <sub>ST1</sub>   | -                     | 3      | 6    | mA    | MUTEB=L                                     |

| Spindle Driver                   |                    |                       |        |      |       |                                             |

| Hall Bias Voltage                | V <sub>HB</sub>    | 0.45                  | 0.9    | 1.35 | V     | IHB=10mA                                    |

| Input Bias Current               | I <sub>HIB</sub>   | -                     | 0.5    | 3    | μA    |                                             |

| Input Level                      | V <sub>HIM</sub>   | 50                    | -      | -    | mVpp  |                                             |

| Common Mode Input Range          | V <sub>HICM</sub>  | 1.5                   | -      | 3.8  | V     |                                             |

| Input Dead Zone (One Side)       | $V_{DZSP}$         | 0                     | 10     | 45   | mV    |                                             |

| Input-Output Gain                | gm <sub>SP</sub>   | 0.85                  | 1.24   | 1.63 | A/V   | $R_{SPRNF}=0.33\Omega$ , $R_{L}=2\Omega$    |

| Output ON Resistance (Total Sum) | Ronsp              | -                     | 1.0    | 1.8  | Ω     | IL=500mA                                    |

| Output limit Current             | I <sub>LIMSP</sub> | 0.85                  | 1.06   | 1.27 | Α     | $R_{SPRNF}=0.33\Omega$                      |

| PWM Frequency                    | fosc               | -                     | 100    | -    | kHz   | $R_L=2\Omega$                               |

| FG Output Low Level Voltage      | $V_{FGL}$          | -                     | 0.1    | 0.3  | V     | 33KΩ pull-up(3.3V)                          |

| Sled Motor Driver                |                    |                       |        |      |       |                                             |

| Input Dead Zone (One Side)       | $V_{DZSL}$         | 5                     | 15     | 35   | mV    |                                             |

| Input-Output Gain                | gm <sub>SL</sub>   | 0.84                  | 1.10   | 1.36 | A/V   | $R_{SLRNF1,2}=0.56\Omega$ , $R_{L}=8\Omega$ |

| Output ON Resistance (Total sum) | R <sub>ONSL</sub>  | -                     | 1.8    | 2.5  | Ω     | IL=500mA                                    |

| Output Limit Current             | I <sub>LIMSL</sub> | 0.79                  | 0.93   | 1.07 | Α     | R <sub>SLRNF1,2</sub> =0.56Ω                |

| PWM Frequency                    | fosc               | -                     | 100    | -    | kHz   | R <sub>L</sub> =8Ω                          |

| Actuator Driver                  |                    |                       |        |      |       |                                             |

| Output Offset Voltage            | V <sub>OFACT</sub> | -50                   | 0      | 50   | mV    | Low Gain mode, R <sub>L</sub> =8Ω           |

| Output ON Resistance             | RONACT             | -                     | 1.5    | 2.0  | Ω     | IL=500mA                                    |

| Voltage Gain 1                   | G <sub>VACT1</sub> | 9.4                   | 11.7   | 13.5 | dB    | Low Gain mode, R <sub>L</sub> =8Ω           |

| Voltage Gain 2                   | G <sub>VACT2</sub> | 15.4                  | 17.7   | 19.5 | dB    | High Gain mode, R <sub>L</sub> =8Ω          |

| Loading Driver                   |                    |                       |        |      |       |                                             |

| Output Offset Voltage            | $V_{OFLD}$         | -110                  | 0      | 110  | mV    | Low Gain mode, R <sub>L</sub> =8Ω           |

| Output ON Resistance             | R <sub>ONLD</sub>  | -                     | 1.0    | 1.5  | Ω     | IL=500mA                                    |

| Voltage Gain 1                   | G <sub>VLD1</sub>  | 14.1                  | 17.2   | 19.5 | dB    | Low Gain mode, R <sub>L</sub> =8Ω           |

| Voltage Gain 2                   | G <sub>VLD2</sub>  | 15.6                  | 18.7   | 21.0 | dB    | High Gain mode, R <sub>L</sub> =8Ω          |

| Protect Sign Output              |                    |                       |        |      |       |                                             |

| ERROUT Low Level Output Voltage  | V <sub>OL2</sub>   | -                     | 0.1    | 0.3  | V     | 33kΩ pull-up(3.3V)                          |

| Logic Inputs (SDI,SCLK,SLV,MUTER |                    |                       |        |      |       |                                             |

| Low Level Input Voltage          | V <sub>INL</sub>   | -                     | -      | 0.5  | V     |                                             |

| High Level Voltage               | V <sub>INH</sub>   | 2.2                   | -      | -    | V     |                                             |

| High Level Current               | I                  | _                     | 33     | 75   | μA    | SDI,SCLK,MUTEB=3.3V                         |

| (SDI,SCLK,MUTEB)                 | I <sub>INH</sub>   |                       |        | 70   | -     |                                             |

| Low Level Current (SLV)          | I <sub>INL</sub>   | -75                   | -30    | -    | μA    | SLV=0V                                      |

| Logic Output (SDO)               |                    |                       |        |      |       |                                             |

| Low Level Output Voltage         | Voutl              | -                     | -      | 0.3  | V     |                                             |

| High Level Output Voltage        | V <sub>OUTH</sub>  | V <sub>SHV</sub> -0.3 | -      | -    | V     |                                             |

| Function                         |                    |                       |        |      |       |                                             |

| PREVCC Drop Mute Voltage         | V <sub>MVCC</sub>  | 3.4                   | 3.8    | 4.1  | V     |                                             |

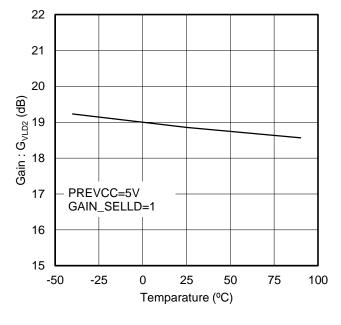

# **Typical Performance Curves**

FC Voltage gain 1 (Low gain mode)

FC Voltage gain 2 (High gain mode)

TK Voltage gain 1 (Low gain mode)

TK Voltage gain 2 (High gain mode)

LD Voltage gain 1 (Low gain mode)

LD Voltage gain 2 (High gain mode)

#### **Description of Blocks**

# ■ Serial Peripheral Interface (SPI)

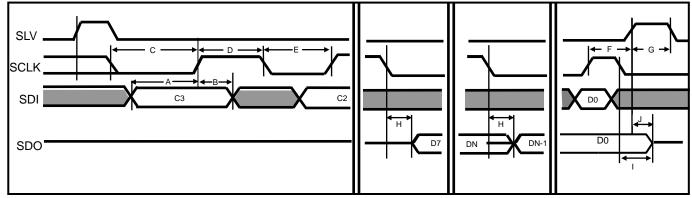

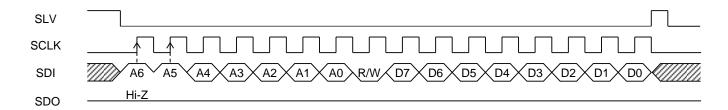

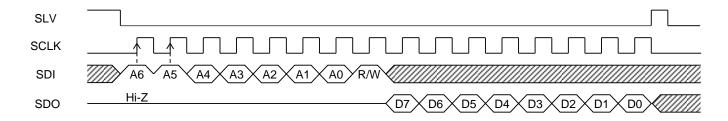

16 bit serial interfaces (SLV, SCLK, SDI, SDO) are provided to perform setting of operations and output levels. SPI communication is performed while SLV terminal is in Low. SDI data are sent to internal shift register at the rising edge of SCLK terminal. Shift register data are loaded into 12 bit internal shift register at the rising edge of SLV terminal according to the address map. Readout operation is performed when readout bit is set to 1. Then state is read out at the falling edge of SCLK terminal and output to SDO terminal.

#### ◆ Input-Output Timing

Figure 4 shows write/read timing of the serial ports.

Minimum timing of each item is as shown in the table below. In order to prevent increase in delay of SPI input/output timing, wiring between SLV/SCLK/SDI/SDO and the microcomputer should be as short as possible to minimize the wiring capacitance.

| Symbol | Item                            | Min | Тур | Max | Unit |

|--------|---------------------------------|-----|-----|-----|------|

| Α      | SDI setup time *                | 9   | 1   | 1   | ns   |

| В      | SDI hold time *                 | 9   | 1   | 1   | ns   |

| С      | Setup SLV to SCLK rising edge * | 9   | -   | •   | ns   |

| D      | SCLK high pulse width *         | 10  | -   | -   | ns   |

| Е      | SCLK low pulse width *          | 10  | -   | -   | ns   |

| F      | Setup SCLK rising edge to SLV * | 9   | -   | -   | ns   |

| G      | SLV pulse width *               | 15  | -   | -   | ns   |

| Н      | SDO delay time *                | -   | -   | 10  | ns   |

| I      | SDO hold time *                 | 2   | -   | -   | ns   |

| J      | SDO OFF time *                  | -   | -   | 20  | ns   |

| K      | SCLK frequency                  | -   | -   | 35  | MHz  |

<sup>\*</sup> Guaranteed Design Items

Figure 4. SPI Input / Output Timing

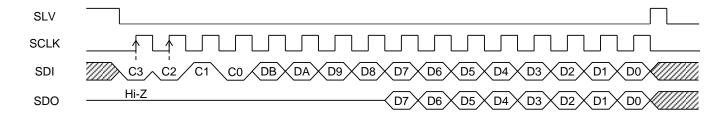

# ◆ DAC Register

#### 1. Input / Output Sequence

Enter the register address in the SDI input on the first 4 bits and data for a specific DAC voltage in the next 12 bits. When specified as REG=02h (address for focus), REG 77h data is output to the SDO. When specified as REG≠02h (address for non-focus), SDO becomes Hi-Z.

Figure 5. 12bit Write / 8bit Read Sequence (when specified as REG=02h)

Figure 6. 12bit Write Sequence (when specified as REG≠02h, C3, C2≠1, 1)

# 2. Address Map (hereinafter register address is referred to as REG)

## **DAC Register Address Map**

| REG | NAME | R/W | DB | DA | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1  | D0  | Reset |

|-----|------|-----|----|----|----|----|----|----|----|----|----|----|-----|-----|-------|

| 00h | N/A  | -   | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   | -     |

| 01h | N/A  | -   | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   | -     |

| 02h | DFC  | W   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   | В     |

| 03h | DTK  | W   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   | В     |

| 04h | DSL1 | W   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1 * | 0 * | В     |

| 05h | DSL2 | W   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1 * | 0 * | В     |

| 06h | N/A  | -   | ı  | -  | -  | -  | 1  | -  | -  | -  | 1  | ı  | -   | -   | -     |

| 07h | N/A  | -   | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   | -     |

| 08h | DSP  | W   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   | В     |

| 09h | DLD  | W   | 11 | 10 | 9  | 8  | 7  | 6  | 5  | 4  | 3  | 2  | 1   | 0   | В     |

| 0Ah | N/A  | -   | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   | -     |

| 0Bh | N/A  | -   | -  | -  | -  | -  | -  | -  | -  | -  | -  | -  | -   | -   | -     |

Default : 0

\*: fixed at 0

\*\* : refer to P.15 about reset - : not affected even when data is written

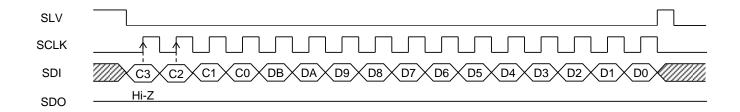

#### ◆ Control register

#### 1. Input / Output Sequence

When writing data to the control register, enter the register address in the first 7 bits of the SDI input, then set the 1bit R/W to 0 and enter the data of each setting in the last 8 bits. SDO is Hi-Z when R/W=0.

When reading data from the control register, enter the register address in the first 7 bits of the SDI input, then set the 1 bit R/W to 1. The last 8 bits are ignored. When R/W=1, 8-bit data of specified address is output to the SDO.

Figure 7. Control Register 8 bit Write Sequence (A6, A5=1,1, R/W= 0)

Figure 8. Control Register 8 bit Read Sequence (A6, A5=1,1, R/W= 1)

#### 2. Address Map

#### Control Register Address Map

| REG | NAME             | R/W | D7             | D6             | D5                | D4                | D3       | D2            | D1             | D0              |

|-----|------------------|-----|----------------|----------------|-------------------|-------------------|----------|---------------|----------------|-----------------|

| 70h | OUTPUT<br>_EN1   | R/W | N/A            | FC<br>_OUTEN   | TK<br>_OUTEN      | SL<br>_OUTEN      | N/A      | SP<br>_OUTEN  | LD<br>_OUTEN   | N/A             |

| 71h | =                | -   | =              | =              | =                 | =                 | =        | =             | =              | -               |

| 72h | POWER<br>_SAVE1  | R/W | N/A            | FC<br>_PSB     | TK<br>_PSB        | SL<br>_PSB        | N/A      | SP<br>_PSB    | LD<br>_PSB     | N/A             |

| 73h | =                | -   | -              | -              | -                 | -                 | -        | -             | -              | -               |

| 74h | DRIVER<br>_SET   | R/W | N/A            | SP<br>_BRAKE   | GAIN<br>_SELFC    | GAIN<br>_SELTK    | N/A      | LD<br>_BRAKE  | GAIN<br>_SELLD | N/A             |

| 75h | RESET            | W   | RST<br>_DAC    | RST<br>_CTLREG | RST<br>_PKTERR    | RST<br>_PKTSTOP   | N/A      | RST<br>_SHORT | N/A            | N/A             |

| 76h | PKT<br>_TIME     | R/W | N/A            | N/A            | PKTSTOP<br>_TIME1 | PKTSTOP<br>_TIME0 | N/A      | N/A           | N/A            | N/A             |

| 77h | STATUS<br>_FLAG1 | R   | ALL<br>_ERR    | N/A            | N/A               | SHORT<br>_LD      | TSD      | PKT<br>_ERR   | PKT<br>_STOP   | UVLO<br>_PREVCC |

| 78h | TEST0            | R/W | Reserved       | Reserved       | Reserved          | Reserved          | Reserved | Reserved      | Reserved       | Reserved        |

| 79h | TEST1            | R/W | Reserved       | Reserved       | Reserved          | Reserved          | Reserved | N/A           | N/A            | N/A             |

| 7Ah | TEST2            | R/W | N/A            | N/A            | Reserved          | N/A               | Reserved | Reserved      | Reserved       | N/A             |

| 7Bh | RST<br>_CHECK    | R/W | RST<br>_CHECKA | RST<br>_CHECKB | N/A               | N/A               | N/A      | N/A           | N/A            | N/A             |

| 7Ch | =                | -   | =              | =              | =                 | =                 | =        | =             | =              | -               |

| 7Dh | -                | -   | -              | -              | -                 | -                 | -        | -             | -              | -               |

| 7Eh | -                | -   | -              | -              | -                 | -                 | -        | -             | -              | -               |

| 7Fh | -                | -   | -              | -              | -                 | -                 | -        | -             | -              | -               |

Write access to "Reserved" bits should be made by "0" input.

Read access to "N/A" bits will return "0".

3. Details of Control Registers

Functions of each register are as shown below.

• REG 70h OUTPUT\_EN1 (Read / Write) Each driver output settings (Hi-Z/Active) can be changed in REG 70h.

| Bit | Name     | Default | Function              | Set "0" | Set "1" | Reset |

|-----|----------|---------|-----------------------|---------|---------|-------|

| 7   | N/A      | 0       | -                     | -       | -       | -     |

| 6   | FC_OUTEN | 0       | FC Output Enable      | Disable | Enable  | Α     |

| 5   | TK_OUTEN | 0       | TK Output Enable      | Disable | Enable  | Α     |

| 4   | SL_OUTEN | 0       | SL1,SL2 Output Enable | Disable | Enable  | Α     |

| 3   | N/A      | 0       | -                     | -       | -       | -     |

| 2   | SP_OUTEN | 0       | SP Output Enable      | Disable | Enable  | Α     |

| 1   | LD_OUTEN | 0       | LD Output Enable      | Disable | Enable  | Α     |

| 0   | N/A      | 0       | -                     | -       | -       | -     |

• REG 71h -

| Bit | Name | Default | Function     | Set "0" | Set "1" | Reset |

|-----|------|---------|--------------|---------|---------|-------|

| 7   | -    | -       | -            | -       | -       | -     |

| 6   | -    | -       | -            | -       | -       | -     |

| 5   | -    | -       | -            | -       | -       | -     |

| 4   | -    | -       | -            | -       | -       | -     |

| 3   | -    | -       | -            | -       | -       | -     |

| 2   | -    | -       | -            | -       | -       | -     |

| 1   | -    | -       | -            | -       | -       | -     |

| 0   | -    | -       | <del>-</del> | -       | -       | -     |

# • REG 72h POWER\_SAVE1 (Read / Write)

Power save mode settings for each block can be set in REG 72h.

Power save mode makes the output Hi-Z and turns OFF the internal circuit to reduce the current consumption.

| Bit | Name   | Default | Function                 | Set "0" | Set "1" | Reset |

|-----|--------|---------|--------------------------|---------|---------|-------|

| 7   | N/A    | 0       | -                        | -       | -       | -     |

| 6   | FC_PSB | 0       | FC Block Power Save      | Enable  | Disable | Α     |

| 5   | TK_PSB | 0       | TK Block Power Save      | Enable  | Disable | Α     |

| 4   | SL_PSB | 0       | SL1,SL2 Block Power Save | Enable  | Disable | Α     |

| 3   | N/A    | 0       | -                        | -       | -       | -     |

| 2   | SP_PSB | 0       | SP Block Power Save      | Enable  | Disable | Α     |

| 1   | LD_PSB | 0       | LD Block Power Save      | Enable  | Disable | Α     |

| 0   | N/A    | 0       | -                        | -       | -       | -     |

• REG 73h -

| Bit | Name | Default | Function | Set "0" | Set "1" | Reset |

|-----|------|---------|----------|---------|---------|-------|

| 7   | -    | -       | -        | -       | -       | -     |

| 6   | -    | -       | -        |         |         |       |

| 5   | -    | -       | -        | -       | -       | -     |

| 4   | -    | -       | -        | -       | -       | -     |

| 3   | -    | -       | -        | -       | -       | -     |

| 2   | -    | -       | -        | -       | -       | -     |

| 1   | -    | -       | -        | -       | -       | -     |

| 0   | -    | -       | -        | -       | -       | -     |

REG 74h DRIVER\_SET (Read / Write)

Operation mode settings of the driver can be changed in REG 74h.

| Bit | Name       | Default | Function       | Set "0"                     | Set "1"                  | Reset |  |

|-----|------------|---------|----------------|-----------------------------|--------------------------|-------|--|

| 7   | N/A        | 0       | -              |                             |                          |       |  |

| 6   | SP_BRAKE   | 0       | SP Brake Mode  | SP Brake Mode Short Brake R |                          |       |  |

| 5   | GAIN_SELFC | 0       | Gain Select FC | Low Gain                    | High Gain                | Α     |  |

| 4   | GAIN_SELTK | 0       | Gain Select TK | Gain Select TK Low Gain     |                          | Α     |  |

| 3   | N/A        | 0       | -              | -                           | -                        | -     |  |

| 2   | LD_BRAKE   | 0       | LD Brake Mode  | LD Output Active            | LD Output<br>Short Brake | Α     |  |

| 1   | GAIN_SELLD | 0       | Gain Select LD | Low Gain                    | High Gain                | Α     |  |

| 0   | N/A        | 0       | -              | -                           | -                        | -     |  |

- <Bit 6> Short brake/reverse brake can be selected as spindle brake mode.

- <Bit 5> Low/high gain mode of the focus driver's gain can be selected.

- <Bit 4> Low/high gain mode of the tracking driver's gain can be selected.

- <Bit 2> Short brake mode (both positive & negative output low) can be activated when loading output is "Active".

- <Bit 1> Low/high gain mode of the loading driver's gain can be switched.

- REG 75h RESET (Write)

Resister settings and latched error flag can be reset in REG 75h.

| Bit | Name        | Default | Function                                          | Set "0" | Set "1" | Reset |

|-----|-------------|---------|---------------------------------------------------|---------|---------|-------|

| 7   | RST_DAC     | 0       | DAC Reset                                         | Reset   | Е       |       |

| 6   | RST_CTLREG  | 0       | Control Register Reset                            | Normal  | Reset   | Е     |

| 5   | RST_PKTERR  | 0       | Packet Bit Counts Error Reset Normal Reset        |         |         |       |

| 4   | RST_PKTSTOP | 0       | No Packet Input Error Reset                       | Normal  | Reset   | Е     |

| 3   | N/A         | 0       | -                                                 | -       | -       | -     |

| 2   | RST_SHORT   | 0       | LD Supply/Ground-Fault Protection Latch Off Reset | Normal  | Reset   | Е     |

| 1   | N/A         | 0       | -                                                 | -       | -       | -     |

| 0   | N/A         | 0       | -                                                 | -       | -       | -     |

- <Bit 7>Reset all DAC register value to 0.

- <Bit 6>Reset all control register value to default.

- <Bit 5>Reset packet bit counts error flag register value to 0.

- <Bit 4>Reset no packet input error flag register value to 0.

- <Bit 2>Reset loading supply/ground-fault protection flag register value to 0.

• REG 76h PKT\_TIME (Read / Write)

In REG 76h, you can specify or disable wait time until error operation in case of no SPI input.

| Bit | Name          | Default | Function                  | Set "0"      | Set "1" | Reset |

|-----|---------------|---------|---------------------------|--------------|---------|-------|

| 7   | N/A           | 0       | -                         | -            | -       | -     |

| 6   | N/A           | 0       | -                         | -            | -       | -     |

| 5   | PKTSTOP_TIME1 | 0       | SPI Packet Watchdog Timer | (00)=Disable | А       |       |

| 4   | PKTSTOP_TIME0 | 0       | Operation Time Selection  | (10)=100µs   | А       |       |

| 3   | N/A           | 0       | -                         | -            | -       | -     |

| 2   | N/A           | 0       | -                         | -            | -       | -     |

| 1   | N/A           | 0       | -                         | -            | -       | -     |

| 0   | N/A           | 0       | -                         | -            | -       | -     |

• REG 77h STATUS\_FLAG (Read) REG 77h outputs each protection state flag

| Bit | Name        | Default | Function                                                          | Set "0" | Set "1"  | Reset |  |  |

|-----|-------------|---------|-------------------------------------------------------------------|---------|----------|-------|--|--|

| 7   | ALL_ERR     | 0       | All Error Flags                                                   | Normal  | Abnormal | *     |  |  |

| 6   | N/A         | 0       | -                                                                 | -       | -        |       |  |  |

| 5   | N/A         | 0       | -                                                                 |         |          |       |  |  |

| 4   | SHORT_LD    | 0       | LD Supply/Ground-Fault Protection Detection Flag (LD Output Hi-Z) | Normal  | Abnormal | С     |  |  |

| 3   | TSD         | 0       | TSD Detection Flag (All Output Hi-Z)                              | Normal  | Abnormal | F     |  |  |

| 2   | PKT_ERR     | 0       | Number of Packet Bits Error Flag<br>(Flag Only)                   | Normal  | Abnormal | С     |  |  |

| 1   | PKT_STOP    | 0       | Packet Watchdog Timer (All Output Hi-Z)                           | Normal  | Abnormal | С     |  |  |

| 0   | UVLO_PREVCC | 0       | VCC Low Voltage Fault Flag (All Output Hi-Z)                      | Normal  | Abnormal | D     |  |  |

<sup>&</sup>lt;Bit7> \*How to reset: ALL\_ERR outputs all the error flags (OCP\_FCTL, OCP\_TK, SHORT\_LD, TSD, PKT\_ERR, PKT\_STOP, UVLO\_VCC). Therefore, reset conditions are depending on each flags.

# REG 78h TEST0 (Read / Write)

| Bit | Name     | Default | Function | Set "0" | Set "1" | Reset |

|-----|----------|---------|----------|---------|---------|-------|

| 7   | Reserved | 0       | -        | -       | -       | D     |

| 6   | Reserved | 0       | -        | -       | -       | D     |

| 5   | Reserved | 0       | -        | -       | -       | D     |

| 4   | Reserved | 0       | -        | -       | -       | D     |

| 3   | Reserved | 0       | -        | -       | -       | D     |

| 2   | Reserved | 0       | -        | -       | -       | D     |

| 1   | Reserved | 0       | -        | -       | -       | D     |

| 0   | Reserved | 0       | -        | -       | -       | D     |

• REG 79h TEST1 (Read / Write)

| Bit | Name     | Default | Function | Set "0" | Set "1" | Reset |

|-----|----------|---------|----------|---------|---------|-------|

| 7   | Reserved | 0       | -        | -       | -       | F     |

| 6   | Reserved | 0       | -        | -       | -       | F     |

| 5   | Reserved | 0       | -        | -       | -       | F     |

| 4   | Reserved | 0       | -        | -       | -       | F     |

| 3   | Reserved | 0       | -        | -       | -       | F     |

| 2   | N/A      | 0       | -        | -       | -       | -     |

| 1   | N/A      | 0       | -        | -       | -       | -     |

| 0   | N/A      | 0       | -        | -       | -       | -     |

# • REG 7Ah TEST2 (Read / Write)

| Bit | Name     | Default | Function | Set "0" | Set "1" | Reset |

|-----|----------|---------|----------|---------|---------|-------|

| 7   | N/A      | 0       | -        | -       | -       | -     |

| 6   | N/A      | 0       | -        | -       | -       | -     |

| 5   | Reserved | 0       | -        | -       | -       | F     |

| 4   | N/A      | 0       | -        | -       | -       | -     |

| 3   | Reserved | 0       | -        | -       | -       | F     |

| 2   | Reserved | 0       | -        | -       | -       | F     |

| 1   | Reserved | 0       | -        | -       | -       | F     |

| 0   | N/A      | 0       | -        | -       | -       | -     |

# • REG 7Bh RST\_CHECK (Read / Write)

REG 7Bh is the flag confirming reset completion of registers listed in page 15.

| Bit | Name       | Default | Function                      | Set "0" | Set "1" | Reset |

|-----|------------|---------|-------------------------------|---------|---------|-------|

| 7   | RST_CHECKA | 0       | Reset A Completion Check Flag | 0       | 1       | Α     |

| 6   | RST_CHECKB | 0       | Reset B Completion Check Flag | 0       | 1       | В     |

| 5   | N/A        | 0       | -                             | -       | -       | -     |

| 4   | N/A        | 0       | -                             | -       | -       | -     |

| 3   | N/A        | 0       | -                             | -       | -       | -     |

| 2   | N/A        | 0       | -                             | -       | -       | -     |

| 1   | N/A        | 0       | -                             | -       | -       | -     |

| 0   | N/A        | 0       | -                             | -       | -       | -     |

#### ◆ Register Reset Operations

Type "A" : MODE Setting Bit (REG 70h, 72h, 74h, 76h, 7Bh[7])

Reset Conditions: PREVCC < 3.8V or VREG < 2.0V or MUTEB < 0.5V

or RST\_CTLREG(75h[6]) = 1

# Type "B" : DAC Setting Bit (REG 01h~09h, 7Bh[6])

Reset Conditions: PREVCC < 3.8V or VREG < 2.0V or MUTEB < 0.5V or RST\_DAC(75h[7]) = 1

#### Type "C" : Operational State (Latched) Output Bit (REG 77h[1,2,4])

Reset Conditions: PREVCC < 3.8V or VREG < 2.0V or MUTEB < 0.5V or RST\_CTLREG (75h[6]) = 1

or RST\_PKTERR (75h[5]) = 1 (for PKT\_ERR(77h[2])) or RST\_PKTSTOP (75h[4]) = 1 (for PKT\_STOP(77h[1])) or RST\_SHORT (75h[2]) = 1 (for SHORT\_LD(77h[4]))

#### Type "D" : Operational State (Continuously Updated) Output Bit 1 (REG 77h[0])

Reset Conditions: PREVCC < 2.0V or VREG < 1.2V or MUTEB < 0.5V

# Type "E" : Reset Setting Bit (REG 75h)

Reset Conditions: Self-reset (If set to 1, automatically returns to "0" following reset operation)

# Type "F" : Operational State (Continuously Updated) Output Bit 2 (REG 77h[3])

Reset Conditions: PREVCC < 3.8V or VREG < 2.0V or MUTEB < 0.5V

### **Reset Operations**

|      |                    |            | DAC REG |      |       |         |     |           | Contr | ol RE | G  |    |    |     |    |    |

|------|--------------------|------------|---------|------|-------|---------|-----|-----------|-------|-------|----|----|----|-----|----|----|

|      | Reset condition    |            |         | 70h  | 72h   | 741 751 |     | 751- 701- | 77h   |       |    |    |    | 7Bh |    |    |

|      |                    |            |         | 7011 | 7 211 | 74h     | 75h | 76h       | D7    | D4    | D3 | D2 | D1 | D0  | D7 | D6 |

|      | PREVCC <           | 2.0V       | 0       | 0    | 0     | 0       |     | 0         | 0     | 0     | 0  | 0  | 0  | 0   | 0  | 0  |

| Hard | PREVCC <           | 3.8V       | 0       | 0    | 0     | 0       |     | 0         | 0     | 0     | 0  | 0  | 0  |     | 0  | 0  |

|      | MUTEB < 0.5V       |            | 0       | 0    | 0     | 0       |     | 0         | 0     | 0     | 0  | 0  | 0  | 0   | 0  | 0  |

|      | RST_SHORT          | 75h[2] = 1 |         |      |       |         |     |           | *1    | 0     |    |    |    |     |    |    |

|      | RST_PKTSTOP        | 75h[4] = 1 |         |      |       |         |     |           | *1    |       |    |    | 0  |     |    |    |

| Soft | RST_PKTERR         | 75h[5] = 1 |         |      |       |         |     |           | *1    |       |    | 0  |    |     |    |    |

|      | RST_CTLREG         | 75h[6] = 1 |         | 0    | 0     | 0       |     | 0         | *1    |       |    |    |    |     | 0  |    |

|      | RST_DAC 75h[7] = 1 |            | 0       |      |       |         |     |           | *1    |       |    |    |    |     |    | 0  |

|      | Self reset         |            |         |      |       |         | 0   |           |       |       |    |    |    |     |    |    |

\*1 Reset conditions of REG 77h[7] are dependent upon REG 77h[4]-77h[0].

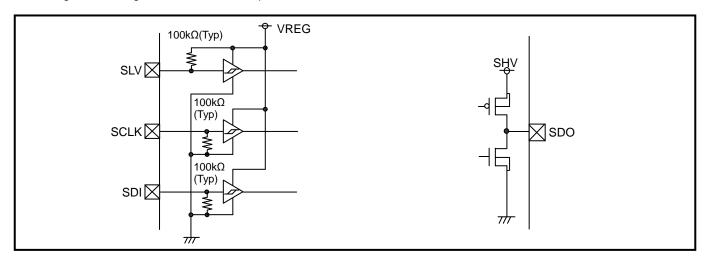

■ SPI Input / Output Terminal Processing

Provided with input terminals SLV, SCLK and SDI, and output terminal SDO, as serial interfaces. Input terminals SLV, SCLK and SDI have built-in 100kΩ (Typ) pull-up/pull-down resistor. Output terminal SDO is able to output the voltage set at SHV as high level voltage in 3-state CMOS output.

Figure 9. SPI Input / Output Terminal Processing

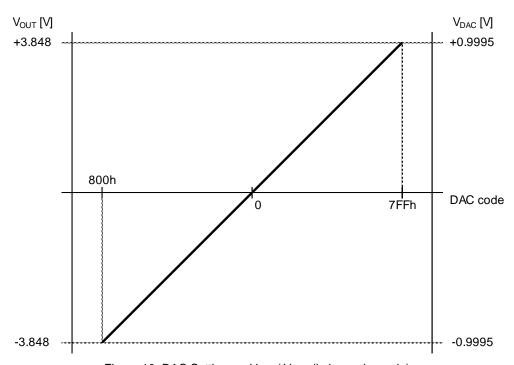

#### ■ DAC and Gain Setting

#### Actuator (FC, TK)

Suppose that voltage difference between positive/negative outputs is V<sub>OUT</sub>, V<sub>OUT</sub> can be expressed as follows.

$$V_{OUT} = G_{VACT} \times V_{DAC}$$

Here, G<sub>VACT</sub> value will be different as below depending upon gain mode settings.

Low Gain Mode (REG 74h[5] GAIN\_SELFC, REG74h[4] GAIN\_SELTK = 0 (Default))

GVACT1 = 3.85 times (11.7dB)

High Gain Mode (GAIN\_SELFC, GAIN\_SELTK = 1) G<sub>VACT2</sub> = 7.67 times (17.7dB)

V<sub>DAC</sub>, the DAC output voltage, can be obtained from DAC register settings through the following equation.

MSB=0:

$V_{DAC} = 1.0 \times (bit[10] \times 0.5^{1} + bit[9] \times 0.5^{2} + bit[8] \times 0.5^{3} + ... + bit[0] \times 0.5^{11})$

MSB=1::

$V_{DAC} = (-1.0) \times (^{\text{bit}}[10] \times 0.5^{1} + ^{\text{bit}}[9] \times 0.5^{2} + ^{\text{bit}}[8] \times 0.5^{3} + \dots + ^{\text{bit}}[0] \times 0.5^{11} + 0.5^{11})$

DAC format (DFC, DTK)

| REG       | MSB Digital input (BIN) LSB | Hex  | Dec   | V <sub>DAC</sub> [V] | V <sub>OUT</sub> [V]* |

|-----------|-----------------------------|------|-------|----------------------|-----------------------|

|           | 1000_0000_0000              | 800h | -2048 | -0.9995              | -3.848                |

|           | 1000_0000_0001              | 801h | -2047 | -0.9995              | -3.848                |

|           | 1000_0000_0010              | 802h | -2046 | -0.9990              | -3.846                |

| 02h(DFC), | 1111_1111_1111              | FFFh | -1    | -0.0005              | -0.002                |

| 03h(DTK)  | 0000_0000_0000              | 000h | 0     | 0                    | 0.000                 |

|           | 0000_0000_0001              | 001h | +1    | +0.0005              | +0.002                |

|           | 0111_1111_1110              | 7FEh | +2046 | +0.9990              | +3.846                |

|           | 0111_1111_1111              | 7FFh | +2047 | +0.9995              | +3.848                |

<sup>\*</sup> In low gain mode setting. Output voltage saturation is not taken into account in the table.

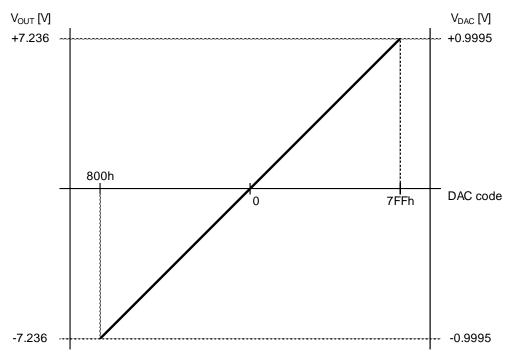

Figure 10. DAC Setting vs.  $V_{DAC}/V_{OUT}$  (in low gain mode)

#### ◆Loading (LD)

Suppose that voltage difference between positive/negative outputs is V<sub>OUT</sub>, V<sub>OUT</sub> can be expressed as follows.

$$V_{OUT} = G_{VLD} \times V_{DAC}$$

Here, G<sub>VLD</sub> value will be different as below depending upon gain mode settings.

$$\label{eq:conditional_condition} \begin{split} &\text{Low Gain Mode (REG 74h[1] GAIN\_SELLD = 0 (Default))} \\ &G_{\text{VLD1}} = 7.24 \text{ times (17.2dB)} \\ &\text{High Gain Mode (GAIN\_SELLD = 1)} \\ &G_{\text{VLD2}} = 8.51 \text{ times (18.7dB)} \end{split}$$

V<sub>DAC</sub>, the DAC output voltage, can be obtained from DAC register settings through the following equation.

#### MSB=0:

$$V_{DAC} = 1.0 \times (bit[10] \times 0.5^{1} + bit[9] \times 0.5^{2} + bit[8] \times 0.5^{3} + ... + bit[0] \times 0.5^{11})$$

#### MSB=1:

$$V_{DAC} = (-1.0) \times (^{\text{bit}}[10] \times 0.5^{1} + ^{\text{bit}}[9] \times 0.5^{2} + ^{\text{bit}}[8] \times 0.5^{3} + \dots + ^{\text{bit}}[0] \times 0.5^{11} + 0.5^{11})$$

DAC format (DLD)

| REG      | MSB Digital input (BIN) LSB | Hex  | Dec   | V <sub>DAC</sub> [V] | V <sub>OUT</sub> [V]* |

|----------|-----------------------------|------|-------|----------------------|-----------------------|

|          | 1000_0000_0000              | 800h | -2048 | -0.9995              | -7.236                |

|          | 1000_0000_0001              | 801h | -2047 | -0.9995              | -7.236                |

|          | 1000_0000_0010              | 802h | -2046 | -0.9990              | -7.233                |

| 00b(DLD) | 1111_1111_1111              | FFFh | -1    | -0.0005              | -0.004                |

| 09h(DLD) | 0000_0000_0000              | 000h | 0     | 0                    | 0.000                 |

|          | 0000_0000_0001              | 001h | +1    | +0.0005              | +0.004                |

|          | 0111_1111_1110              | 7FEh | +2046 | +0.9990              | +7.233                |

|          | 0111_1111_1111              | 7FFh | +2047 | +0.9995              | +7.236                |

<sup>\*</sup> In low gain mode setting. Output voltage saturation is not taken into account in the table.

Figure 11. DAC Setting vs. V<sub>DAC</sub> / V<sub>OUT</sub> (in low gain mode)

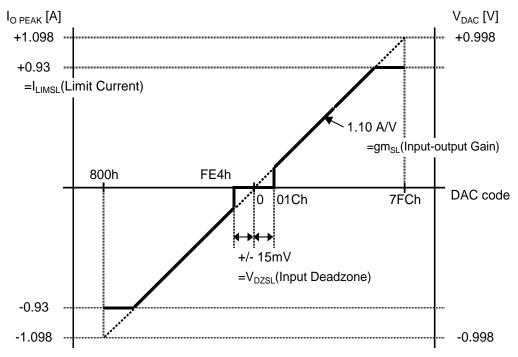

#### ♦ Sled (SL1, SL2)

Suppose that I<sub>O PEAK</sub> represents peak output current, I<sub>O PEAK</sub> can be expressed in the following ways.

```

\begin{split} I_{O \; PEAK} &= 0 & (\mid V_{DAC} \mid < V_{DZSL} \,) \\ I_{O \; PEAK} &= g m_{SL} \times \mid V_{DAC} \mid & (g m_{SL} \times \mid V_{DAC} \mid < I_{LIMSL} \,) \\ I_{O \; PEAK} &= I_{LIMSL} & (g m_{SL} \times \mid V_{DAC} \mid > I_{LIMSL} \,) \end{split}

```

Where  $V_{DZSL}$  is input deadzone (single-sided) of 15mV (Typ). The gm<sub>SL</sub> is output/input gain and  $I_{LIMSL}$  is output limit current, and they can be obtained respectively as follows.

$$\begin{split} gm_{SL} &= 0.616 \, / \, R_{SLRNF} \, [A/V] \\ I_{LIMSL} &= 0.52 \, / \, R_{SLRNF} \, [A] \end{split}$$

V<sub>DAC</sub>, the DAC output voltage, can be obtained from DAC register settings through the following equation.

MSB=0

$$V_{DAC} = 1.0 \times (bit[10] \times 0.5^{1} + bit[9] \times 0.5^{2} + bit[8] \times 0.5^{3} + ... + bit[2] \times 0.5^{9})$$

MSB=1

$$V_{DAC} = (-1.0) \times (^{bit}[10] \times 0.5^{1} + ^{bit}[9] \times 0.5^{2} + ^{bit}[8] \times 0.5^{3} + ... + ^{bit}[2] \times 0.5^{9} + 0.5^{9})$$

DAC format (DSL1, DSL2)

| REG                     | MSB Digital input (BIN) LSB | Hex  | Dec   | V <sub>DAC</sub> [V] | I <sub>O PEAK</sub> [A]* |

|-------------------------|-----------------------------|------|-------|----------------------|--------------------------|

|                         | 1000_0000_0000              | 800h | -2048 | -0.9980              | -1.098                   |

|                         | 1000_0000_0100              | 804h | -2044 | -0.9980              | -1.098                   |

|                         | 1111_1110_0000              | FE0h | -32   | -0.0156              | -0.017                   |

|                         | 1111_1110_0100              | FE4h | -28   | -0.0137              | 0                        |

| 0.41 (D.01.4)           | 1111_1111_1100              | FFCh | -4    | 0.0020               | 0                        |

| 04h(DSL1),<br>05h(DSL2) | 0000_0000_0000              | 000h | 0     | 0                    | 0                        |

| OSH(DOLZ)               | 0000_0000_0100              | 004h | +4    | +0.0020              | 0                        |

|                         | 0000_0001_1100              | 01Ch | +28   | +0.0137              | 0                        |

|                         | 0000_0010_0000              | 020h | +32   | +0.0156              | +0.017                   |

|                         | 0111_1111_1000              | 7F8h | +2040 | +0.9961              | +1.096                   |

|                         | 0111_1111_1100              | 7FCh | +2044 | +0.9980              | +1.098                   |

<sup>\*</sup>Output voltage saturation and limit current setting are not taken into account in the table. Condition:R<sub>SLRNF</sub>=0.56Ω

Figure 12.  $I_{O PEAK}$  Characteristics (When set as  $R_{SLRNF}$ =0.56  $\Omega$ ).

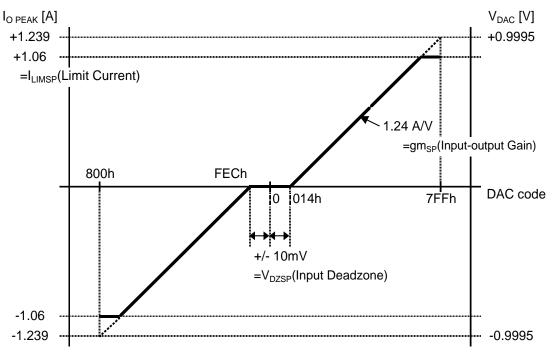

#### ◆ Spindle (SP)

Suppose that IO PEAK represents peak output current, IO PEAK can be expressed in the following ways.

```

\begin{split} I_{O \; PEAK} &= 0 & \left( \; \mid V_{DAC} \mid < V_{DZSP} \; \right) \\ I_{O \; PEAK} &= \; gm_{SP} \times \mid V_{DAC} \mid & \left( \; gm_{SP} \times \mid V_{DAC} \mid < \; l_{LIMSP} \; \right) \\ I_{O \; PEAK} &= \; I_{LIMSP} & \left( \; gm_{SP} \times \mid V_{DAC} \mid > \; l_{LIMSP} \; \right) \end{split}

```

Where  $V_{DZSP}$  is input deadzone (single-sided) of 10mV (Typ). The  $gm_{SP}$  is output/input gain and  $I_{LIMSP}$  is output limit current, and they can be obtained respectively as follows.

$$gm_{SP} = 0.409 / R_{SPRNF} [A/V]$$

$I_{LIMSP} = 0.35 / R_{SPRNF} [A]$

V<sub>DAC</sub>, the DAC output voltage, can be obtained from DAC register settings through the following equation.

#### MSB=0:

$$V_{DAC} = 1.0 \times (bit[10] \times 0.5^{1} + bit[9] \times 0.5^{2} + bit[8] \times 0.5^{3} + ... + bit[0] \times 0.5^{11})$$

#### MSB=1:

$$V_{DAC} = (-1.0) \times (^{\text{bit}}[10] \times 0.5^{1} + ^{\text{bit}}[9] \times 0.5^{2} + ^{\text{bit}}[8] \times 0.5^{3} + \dots + ^{\text{bit}}[0] \times 0.5^{11} + 0.5^{11})$$

#### DAC format (DSP)

| REG      | MSB Digital input (BIN) LSB | Hex  | Dec   | V <sub>DAC</sub> [V] | I <sub>O PEAK</sub> [A]※ |

|----------|-----------------------------|------|-------|----------------------|--------------------------|

|          | 1000_0000_0000              | 800h | -2048 | -0.9995              | -1.239                   |

|          | 1000_0000_0001              | 801h | -2047 | -0.9995              | -1.239                   |

|          | 1111_1110_1011              | FEBh | -21   | -0.0103              | -0.013                   |

|          | 1111_1110_1100              | FECh | -20   | -0.0098              | 0                        |

|          | 1111_1111_1111              | FFFh | -1    | -0.0005              | 0                        |

| 08h(DSP) | 0000_0000_0000              | 000h | 0     | 0                    | 0                        |

|          | 0000_0000_0001              | 001h | +1    | +0.0005              | 0                        |

|          | 0000_0001_0100              | 014h | +20   | +0.0098              | 0                        |

|          | 0000_0001_0101              | 015h | +21   | +0.0103              | +0.013                   |

|          | 0111_1111_1110              | 7FEh | +2046 | +0.9990              | +1.238                   |

|          | 0111_1111_1111              | 7FFh | +2047 | +0.9995              | +1.239                   |

<sup>\*</sup>Output voltage saturation and limit current setting are not taken into account in the table. Condition:R<sub>SPRNF</sub>=0.33Ω

Figure 13.  $I_{O PEAK}$  Characteristics (When set as  $R_{SPRNF}$ =0.33  $\Omega$ ).

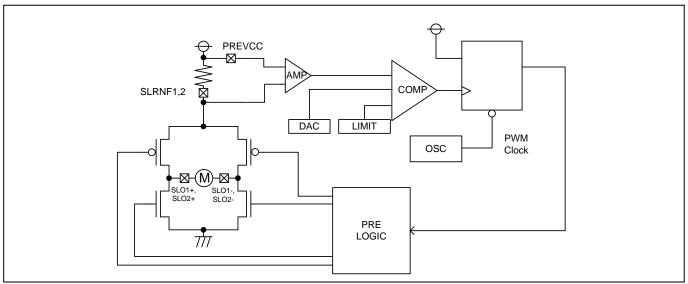

- Description of Driver Operations

- Sled Motor Driver

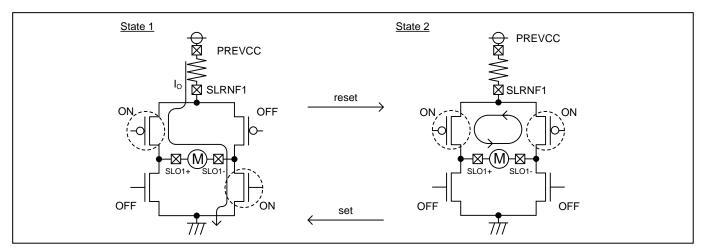

Figure 14. Sled motor driver block

Figure 15. Current Paths in Set [State 1] and Reset [State 2]

Figure 16. Sled Motor Driver Operation Timing Chart

Set [State1]: Output turned ON at the rise of PWM clock --> Load current supplied from PREVCC.

Reset [State2]: Output turned OFF when load current increases to reach current value proportional to input or limit current value --> Load current regenerated by L component of the motor through the path shown in State 2 diagram.

#### ◆ Spindle Driver

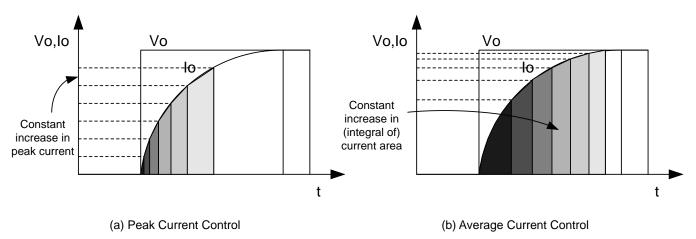

#### 1. Spindle Driver Input-Output Characteristics

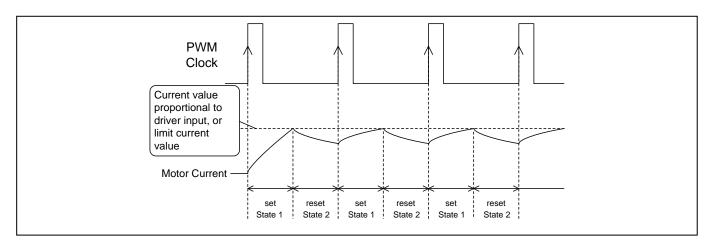

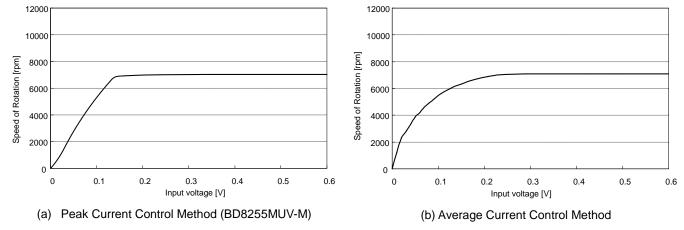

Figure 17 shows input-output characteristics of the average current detection control and the peak current detection control. This IC controls output by detecting peak current. Linearity of the input/output characteristics is improved compared with the one in the average current detection method.

Figure 17. Spindle Driver Input-Output Characteristics

Difference in input/output characteristics due to control method can be explained as below. Motor coil comprises not only pure inductance but also impedance component. Suppose that  $V_0$  represents peak value of output pulse,  $I_0$ , current which flows into the motor when output pulse is turned on, can be expressed in the following ways.

Figure 18. Current Waveform Including Impedance Component

You can see from the above equation that motor current lo follows a curve of natural logarithm. If you try to express this as motor current characteristics as opposed to input voltage controlled by the respective methods, you will get Figure 19. Spindle motor speed is proportional to motor current. In case of PWM driver, motor current is roughly equivalent to peak current because it includes regenerative current. In the peak current control, therefore, motor current (rotation speed) becomes proportional to input voltage.

In contrast, in the average current control, average value of supply current (integral of supply current) becomes proportional to input voltage. So motor current (rotation speed) as opposed to input voltage roughly follows a curve of natural logarithm (Figure 19. (b)). And therefore, you get higher gain in low speed range.

Figure 19. Input Voltage vs. Motor Current

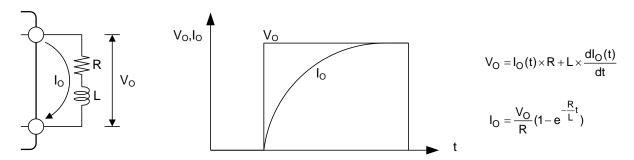

#### 2. Current Limit Operation.

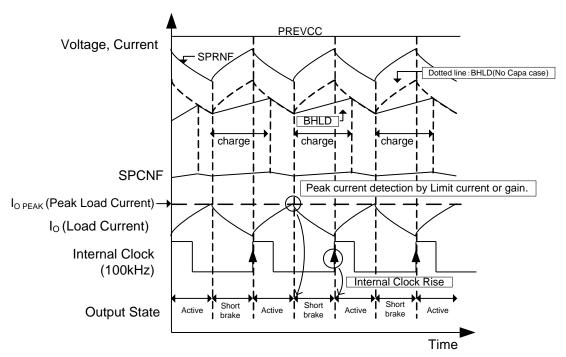

Figure 20 shows the operation timing chart.

In this IC, flip-flop is activated based on a clock signal generated by the built-in triangular wave generator to generate PWM pulse. The spindle driver starts operation at the rising edge of internal clock. Short brake mode is activated if peak current defined by limit current or gain is detected, and no output pulse is delivered until next clock input. Both during limit current detection and usual peak current detection, it operates at PWM oscillating frequency generated by the same internal clock.

Figure 20. Spindle Driver Operation Timing Chart

3. Role of Capacitors of BHLD and SPCNF Terminals

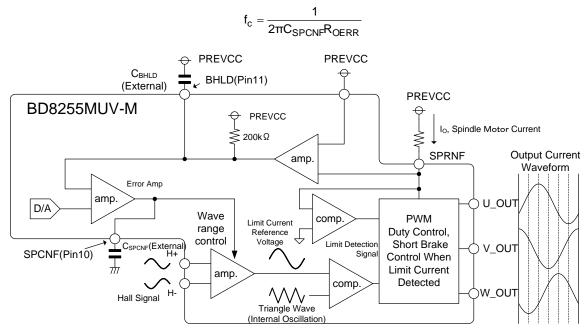

Figure 21 shows a block diagram of the spindle driver.

In this IC, peak current control method is realized by monitoring Io, the load current flowing in the spindle motor, at SPRNF terminal, and holding the peak current in  $C_{BHLD}$ , the capacitor connected to BHLD terminal. Charging time of BHLD terminal is a time constant defined by capacity of  $C_{BHLD}$  and 200 k $\Omega$  (Typ) internal resistance.

$C_{SPCNF}$ , the capacitor of SPCNF terminal, influences  $f_c$ , the cut-off frequency, of the spindle driver control loop.  $f_c$  can be expressed in the following formula. Where  $R_{OERR}$  is internal error amplifier output impedance of approximately 700 k $\Omega$  (Typ).

Figure 21. Spindle Driver Block Diagram

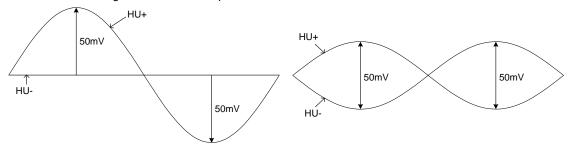

#### 4. Spindle Hall Signal Setting

In this IC, as shown in Figure 21, low noise (silence) is realized by controlling output current into a sine wave. Hall signal amplified according to REG 08h DSP is used to control the output current. So, if amplitude of the hall signal is too small, amplitude of the output current will also be too small, and rotation speed will become too low. Therefore, make sure that input level of the hall signal be 50 mV (input level at hall amplifier: V<sub>HIM</sub>) or greater as shown in Figure 22. Also make sure that waveform of the hall signal be as close as possible to sine wave.

Figure 22. Minimum Amplitude of Hall Input (Example of HU+ and HU- Input).

#### 5. Hall input (Pin 2 to Pin 7) / Hall bias (Pin 8) (Spindle)

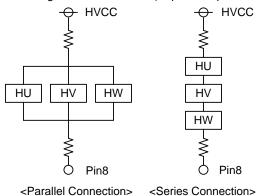

Hall elements can be connected either in series or in parallel as shown in Figure 23.

Hall input voltage should be set within the range of 1.5 V to 3.8 V (In-phase input voltage range of hall amplifier: V<sub>HICM</sub>).

Figure 23. Example of Hall Elements Connection

#### 6. FG Pulse

3FG is output to FG terminal. Pull-up resistor of FG is recommended to be  $3.3~k\Omega$  or less. If the resistance setting is higher than that, High logic of FG output can be reversed to become "Low" as soon as spindle output becomes Hi-Z. Since FG pulse is generated from hall output signal, it can become unstable if the hall signal catches noise. Radiation noise on circuit patterns or flexible cables should be avoided as much as possible. Against any remaining noise, it is recommended to insert a capacitor (around  $0.01~\mu\text{F}$ ) between positive and negative sides of the hall signal.

#### 7. Reverse brake

When reverse brake is done coming from high speed, take note of the counter-electromotive force. Also, consider the speed of motor rotation to ensure sufficient output current when using the reverse brake. Rated current of spindle outputs are 1.66 A.

#### 8. Capacitor between SPVM-SPGND

There is change in voltage and current because of the steep drive PWM. The capacitor between SPVM-SPGND is placed in order to suppress the fluctuations due to the SPVM voltage. However, the effect is reduced if this capacitor is placed far from the IC due to the effect of line impedances. Therefore, this capacitor should be placed near the IC.

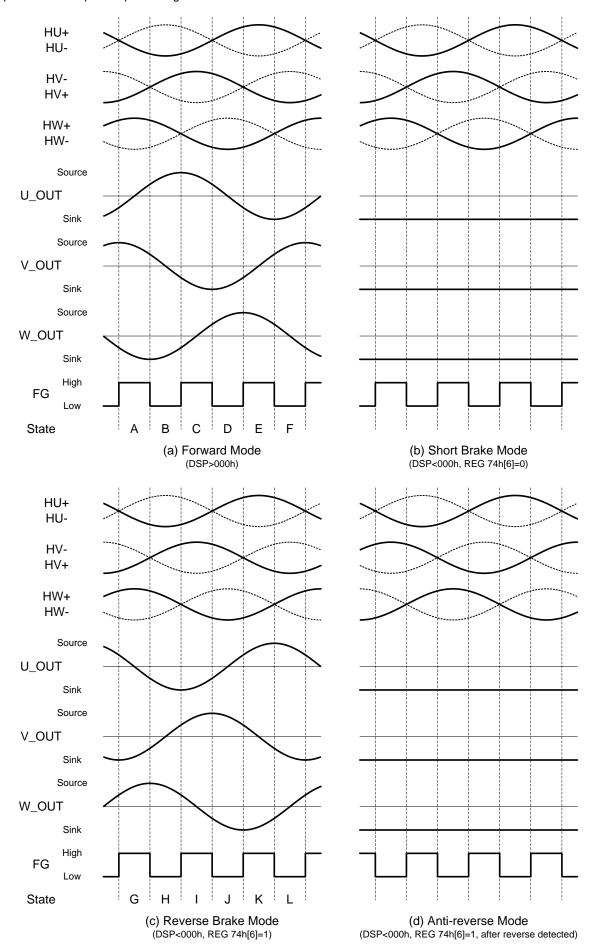

#### 9. Spindle Dricer Input-Output Timing Chart

#### **Start-up Operation**

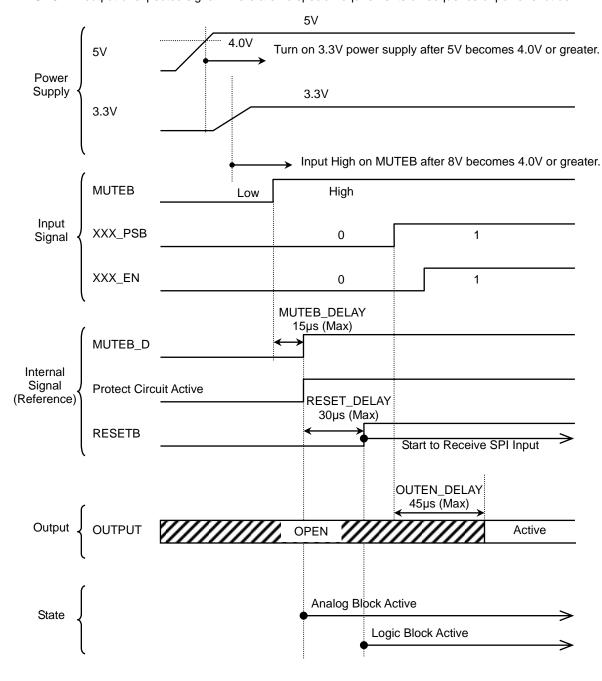

1. Startup Signals

5V Power supply

PREVCC, AVM, SPRNF, SLRNF1, SLRNF2

• 3.3V Power supply : SHV

• MUTEB (Input terminal) : Standby (Low) / Active (High) setting for whole IC

• XXX\_PSB (SPI control signal) : Power save (0) / Active (1) setting for control circuits of 6ch blocks

XXX EN (SPI control signal)

Open (0) / Active (1) setting for output of 6ch blocks

• MUTEB\_D (Internal signal) : Standby / active control for analog block

There may be 15 µs (Max) delay from MUTEB.

RESETB (Internal signal)

Reset /active control for SPI block and logic block

#### 2. Start-up and Shut-down Sequences

Make sure to turn on 5V power supply before 3.3V power supplys. If 3.3V power is turned on first, there is a possibility that SDO Pin output unexpected signal. There are no special requirements on sequence of power shut down.

#### **Description of Functions**

1. Output Voltage State (Spindle / Sled Motor)

|                               | Spindle     | Sled Motor  |

|-------------------------------|-------------|-------------|

| Under Input Dead Zone         | Hi-Z        | Short Brake |

| Under Current Limit Operation | Short Brake | Short Brake |

#### 2. PWM Oscillation Frequency (Spindle / Sled Motor)

PWM oscillation of the spindle and the sled motor is internally free-running. Oscillation frequency is 100 kHz (Typ).

#### 3. UVLO (PREVCC Drop Mute)

If PREVCC terminal voltage becomes 3.8 V (Typ) or less, or VREG terminal voltage becomes 2.0 V (Typ) or less, output of all channels turns OFF (Hi-Z). This IC continue the operation until UVLO turns on under the voltage less than the recommended operating condition.

\* REG 77h[0] UVLO\_PREVCC is set to "1" while UVLO is activated. And UVLO\_PREVCC is reset to "0" if PREVCC terminal voltage becomes 2.0 V (Typ) or less, or VREG terminal voltage becomes 1.2 V (Typ) or less, but this is below the operational voltage range and some register state may be unsustainable depending on degree of voltage drop.

#### 4. Thermal Shutdown

Thermal shutdown (over temperature protection circuit) is built-in in order to prevent thermal breakage of IC.

The package should be used within acceptable power dissipation, but in case where it is left beyond the acceptable power dissipation, junction temperature rises, and thermal shutdown is activated at 175°C (Typ) and all the channel outputs are turned OFF (Hi-Z).

Then, when the junction temperature falls down to 150°C (Typ), the channel outputs are turn ON again. Note that even though the thermal shut down is operating, IC may be overheated and end up broken if heat is continuously applied from outside.

\* REG 77h[3] TSD is set to "1" while thermal shutdown is activated, but this condition is beyond the rated temperature and all register states may be unsustainable depending on degree of temperature rise.

#### 5. Loading Supply/Ground-Fault Protection

This is the function to prevent breakage of output POWER MOS when there exist the conditions that may break the output POWER MOS if loading output is supply/ground-faulted.

- Supply-fault occurs when SINK-side POWER MOS is ON, and the supply-fault protection is performed if output terminal voltage of (Power Supply 1 Vf) or greater and supply-fault current are detected at the same time. Here, the output is OFF-latched. Note that 1 Vf = 0.7V (Typ).

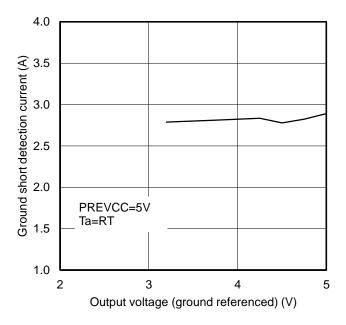

- Ground-fault occurs when SOURCE-side POWER MOS is ON, and the ground-fault protection is performed if ground-fault current is detected. Here, the output is OFF-latched. Note that the ground-fault detection current is dependent on the output voltage. See Figure 24.

- \* REG 77h[4] SHORT\_LD is set to "1" if the loading supply/ground-fault protection is activated.

- \* You can reset the protection mode by resetting REG 75h[2] SHORT\_RESET if the protection mode is activated and the output is OFF-latched.

- \* High frequency noise suppression filter is built in the supply/ground-fault protection circuit, but the supply/ground-fault protection may be activated against the noise of 10 µs (Typ) or greater.

Figure 24. Output voltage vs Ground short detection current

#### 6. Packet Bit Counts Error

Serial input signal of this IC consists of 16 bits in one packet. If counts of the SCLK rising during the period between falling and rising of SLV are anything but 16 times, it is determined as a erroneous packet and REG 77h[2] PKT\_ERR is set to "1". Any data determined as an erroneous packet are nullified, and the registers maintain the state immediately before the error. Note that PKT\_ERR remains at "1" even though the next 1 packet is sent and counts of the clock rising during the period between falling and rising of SLV are 16 times. But this error will not open (i.e. turn off) the output circuit.

#### 7. Packet Watchdog Timer

If REG 76h[5,4] PKTSTOP\_TIME is preset to anything but "00" and there is no valid packet (16 bits) rising of SLV within this preset time period, REG 77h[1] PKT\_STOP will be set to "1" and all outputs will be OFF-latched (Hi-Z).

You can reset the protection mode by resetting REG 75h[4] RST\_PKTSTOP if the protection mode is activated and the output is OFF-latched.

#### 8. ERROUT Terminal

If either the packet bit counts error or the packet watchdog timer is activated, this terminal switches to High as an error flag.

#### 9. VREG Terminal

VREG terminal is the regurator output for internal blocks. A 0.01µF compensating capacitor shall be connected across the VREG terminal. Any value less than 0.01µF, or no compensating capacitor will result in system instablity.

#### **Noise Suppression**

- The following are possible causes of noise of the PWM driver.

- A. Noise from power line or ground

- B. Radiated noise

- Countermeasures against A -

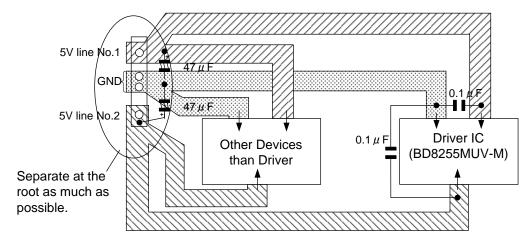

- (1) Reduce impedance in wiring for the driver's 5 V power supply (SPRNF, SLRNF1, SLRNF2, PREVCC, AVM) and power GND (SPGND, SLGND, ACTGND) lines where high current flows. Make sure that they be separated from power supply lines of other devices at the root so that they do not have common impedance. (Figure 25.)

Figure 25. Pattern Example

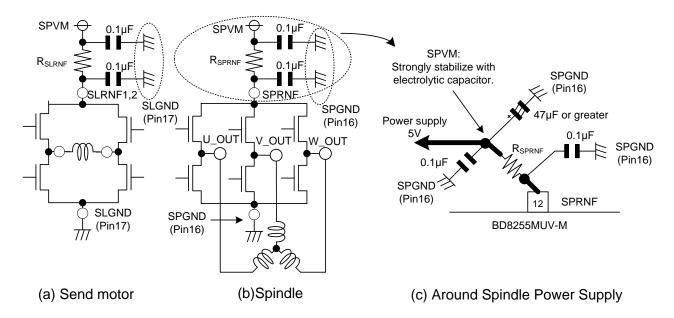

(2) Provide a low ESR electrolytic capacitor between the power terminal and the ground terminal of the driver to achieve strong stabilization. Provide a ceramic capacitor with good high frequency property next to the IC. Also provide a ceramic capacitor with good high frequency property between RNF and GND. (Figure 26.) Then power supply ripple due to PWM switching and spindle motor rotation can be reduced.

Figure 26. Position of Ceramic Capacitors

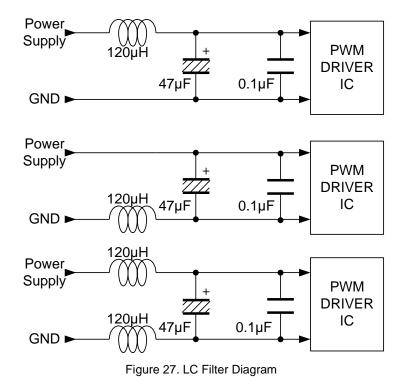

(3) If you could not improve the situation by (1) and (2), another way is to insert a LC filter in the power line or the ground line.

#### Example:

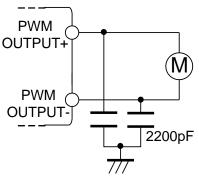

(4) Or you can also add a capacitor of around 2200 pF between each output and the ground. In this case, ensure that the GND wiring should not have any common impedance with other signals.

Figure 28. Snubber Circuit

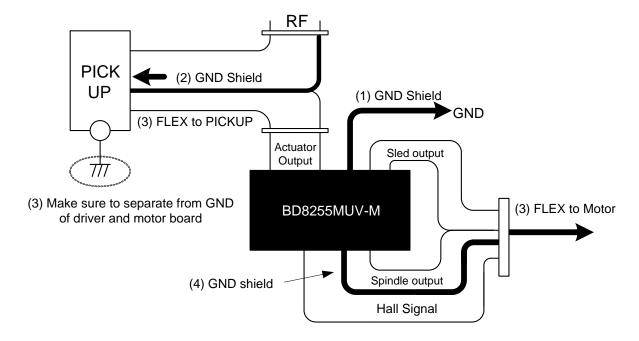

- Countermeasures against B See Figure 29. -

- (1) Ensure certain distance between RF signal line and PWM-driven output line. If they must be located inevitably too close, shield the RF signal line with GND except the stable GND.

- (2) Like in (1), flexible cable to the pickup should be shielded with GND in order to separate noise between the signal line and the actuator drive output line.

- (3) Connect the motor system and the actuator system to separate flexible cables.

- (4) As FG pulse is generated from hall signal, provide a shield with stable GND or other wire with low impedance between the PWM output and the hall signal so that noise is not radiated from the flexible cable and the board pattern.

Figure 29. RF Noise Suppression

Power Supply and Ground \*(O) is pin.

Figure 30. Power Supply and Ground

# **Application Example**

Figure 31. Application Example

# ▼Recommended values

| Component name      | Component value | Product name      | Manufacturer |

|---------------------|-----------------|-------------------|--------------|

| 0                   | 0.1µF           | GCM188R11H Series | murata       |

| $C_PREVCC$          | 47µF            | UCD1E470MCL       | Nichicon     |

| Свнго               | 470pF           | GCM188R11H Series | murata       |

| 0                   | 0.1µF           | GCM188R11H Series | murata       |

| $C_{SPVM}$          | 47µF            | UCD1E470MCL       | Nichicon     |

| R <sub>SPRNF</sub>  | 0.33Ω           | MCR100 Series     | Rohm         |

| C <sub>SPRNF</sub>  | 0.1µF           | GCM188R11H Series | murata       |

| C <sub>SPCNF</sub>  | 0.01µF          | GCM188R11H Series | murata       |

| 0                   | 0.1µF           | GCM188R11H Series | murata       |

| $C_{AVM}$           | 47µF            | UCD1E470MCL       | Nichicon     |

| 0                   | 0.1µF           | GCM188R11H Series | murata       |

| $C_{SLVM}$          | 47µF            | UCD1E470MCL       | Nichicon     |

| R <sub>SLRNF1</sub> | 0.56Ω           | MCR100 Series     | Rohm         |

| R <sub>SLRNF2</sub> | 0.56Ω           | MCR100 Series     | Rohm         |

| C <sub>SLRNF1</sub> | 0.1µF           | GCM188R11H Series | murata       |

| C <sub>SLRNF2</sub> | 0.1µF           | GCM188R11H Series | murata       |

| C <sub>SHV</sub>    | 0.1µF           | GCM188R11H Series | murata       |

| R <sub>HVCC</sub>   | 100Ω            | MCR03 Series      | Rohm         |

| R <sub>HALLVC</sub> | 100Ω            | MCR03 Series      | Rohm         |

| $C_{VREG}$          | 0.01µF          | GCM188R11H Series | murata       |