## **MCP3909**

### **Energy Metering IC with SPI Interface and Active Power Pulse Output**

#### **Features**

- Supports IEC 62053 International Energy Metering Specification

- Digital Waveform Data Access Through SPI Interface

- 16-bit Dual ADC Output Data Words

- 20-bit Multiplier Output Data Word

- Dual Functionality Pins Support Serial Interface Access and Simultaneous Active Power Pulse Output

- Two 16-bit Second Order Delta-sigma Analogto-Digital Converters (ADCs) with Multi-bit DAC

- 81 dB SINAD (typical) on Both Channels

- 0.1% Typical Active Energy Measurement Error Over 1000:1 Dynamic Range

- PGA for Small Signal Input Supports Low Value Shunt Current Sensor

- Ultra-low Drift On-chip Reference,15 ppm/°C (typical)

- Direct Drive for Electromagnetic Mechanical Counter and Two-phase Stepper Motors

- Low I<sub>DD</sub> of 4 mA (maximum)

- · Tamper Output Pin for Negative Power Indication

- · Temperature Ranges:

- Industrial: -40°C to +85°C

- Extended: -40°C to +125°C

### Description

The MCP3909 device is an energy-metering IC designed to support the IEC 62053 international metering standard specification. It supplies a frequency output proportional to the average active real power, with simultaneous serial access to ADC channels and multiplier output data. This output waveform data is available at up to 14 kHz with 16-bit ADC output and 20-bit multiplier output words. The 16-bit, delta-sigma ADCs allow for a wide range of  $I_B$  and  $I_{MAX}$  currents and/or small shunt (<200 µOhms) meter designs. A no-load threshold block prevents any current creep measurements for the active power pulse The integrated on-chip voltage reference has an ultra-low temperature drift of 15 ppm per degree C. This accurate energy metering IC with high field reliability is available in the industry standard 24-lead SSOP pinout.

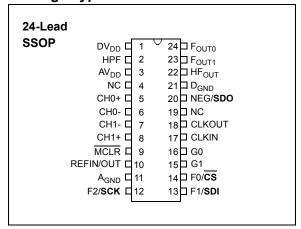

### **Package Type**

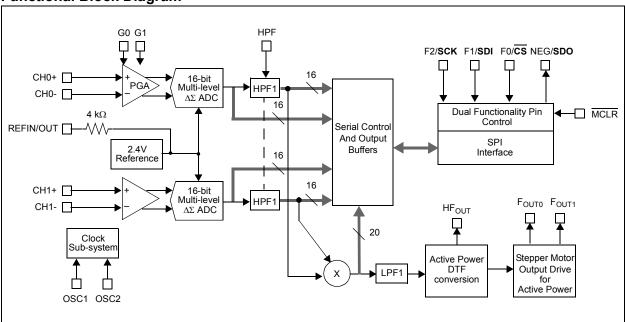

### **Functional Block Diagram**

### 1.0 ELECTRICAL CHARACTERISTICS

### Absolute Maximum Ratings †

| V <sub>DD</sub>                                    | 7.0V                          |

|----------------------------------------------------|-------------------------------|

| Digital inputs and outputs w.r.t. A <sub>GND</sub> | 0.6V to V <sub>DD</sub> +0.6V |

| Analog input w.r.t. A <sub>GND</sub>               | 6V to +6V                     |

| V <sub>REF</sub> input w.r.t. A <sub>GND</sub>     | 0.6V to V <sub>DD</sub> +0.6V |

| Storage temperature                                | 65°C to +150°C                |

| Ambient temp. with power applied                   | 65°C to +125°C                |

| Soldering temperature of leads (10 second          | nds)+300°C                    |

| ESD on the analog inputs (HBM,MM)                  | 5.0 kV, 500V                  |

| ESD on all other pins (HBM,MM)                     | 5.0 kV, 500V                  |

† Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

| <b>Electrical Specifications:</b> Unless otherwise indicated, all parameters apply at $AV_{DD} = DV_{DD} = 4.5V$ to 5.5V, Internal $V_{REF}$ , HPF turned on (AC mode), $A_{GND}$ , $D_{GND} = 0V$ , MCLK = 3.58 MHz; $T_A = -40^{\circ}$ C to +85°C. |         |     |        |        |                           |                                                                                                                                                                |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-----|--------|--------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                                                                                                                                                                                                                             | Sym     | Min | Тур.   | Max    | Units                     | Comment                                                                                                                                                        |  |  |

| Active Power Measurement Accuracy                                                                                                                                                                                                                     |         |     |        |        |                           |                                                                                                                                                                |  |  |

| Active Energy Measurement<br>Error                                                                                                                                                                                                                    | E       | _   | 0.1    | _      | % F <sub>OUT</sub>        | Channel 0 swings 1000:1 range, F <sub>OUT0</sub> , F <sub>OUT1</sub> Frequency outputs only, does not apply to serial interface data. ( <b>Note 1, Note 4)</b> |  |  |

| No-Load Threshold/<br>Minimum Load                                                                                                                                                                                                                    | NLT     | _   | 0.0015 | _      | % F <sub>OUT</sub><br>Max | Frequency outputs only, does not apply to serial interface data.  Disabled when F2, F1, F0 = 0, 1, 1  (Note 5, Note 6)                                         |  |  |

| System Gain Error                                                                                                                                                                                                                                     |         |     | 1      | 5      | % F <sub>OUT</sub>        | (Note 2, Note 5)                                                                                                                                               |  |  |

| AC Power Supply Rejection (output frequency variation)                                                                                                                                                                                                | AC PSRR | _   | 0.01   | _      | % F <sub>OUT</sub>        | F2, F1, F0 = 0, 1, 1 (Note 3)                                                                                                                                  |  |  |

| DC Power Supply Rejection (output frequency variation)                                                                                                                                                                                                | DC PSRR | _   | 0.01   | _      | % F <sub>OUT</sub>        | HPF = 1, Gain = 1 (Note 3)                                                                                                                                     |  |  |

| Waveform Sampling                                                                                                                                                                                                                                     |         |     |        |        |                           |                                                                                                                                                                |  |  |

| A/D Converter Signal-to-<br>Noise and Distortion Ratio                                                                                                                                                                                                | SINAD   | _   | 81     | _      | dB                        | Applies to both channels,<br>V <sub>IN</sub> = 0 dBFS at 50 Hz<br>(V <sub>IN</sub> = Full Scale)                                                               |  |  |

| Bandwidth<br>(Notch Frequency)                                                                                                                                                                                                                        |         | _   | 14     | _      | kHz                       | Applies to both channels, MCLK/256                                                                                                                             |  |  |

| Phase Delay Between<br>Channels                                                                                                                                                                                                                       |         | _   | _      | 1/MCLK | S                         | HPF = 0 and 1, < 1 MCLK period (Note 4, Note 6, Note 7)                                                                                                        |  |  |

- Note 1: Measurement error = (Energy Measured By Device True Energy)/True Energy \* 100%. Accuracy is measured with signal (±660 mV) on Channel 1. F<sub>OUT0</sub>, F<sub>OUT1</sub> pulse outputs. Valid from 45 Hz to 75 Hz. See typical performance curves for higher frequencies and increased dynamic range. This parameter is not 100% production tested.

- 2: Does not include internal V<sub>REF</sub>. Gain = 1, CH0 = 470 mVDC, CH1 = 660 mVDC, difference between measured output frequency and expected transfer function.

- 3: Percent of HF<sub>OUT</sub> output frequency variation; Includes external  $V_{REF}$  = 2.5V, CH1 = 100 mV<sub>RMS</sub> @ 50 Hz, CH2 = 100 mV<sub>RMS</sub> @ 50 Hz, AV<sub>DD</sub> = 5V + 1 V<sub>pp</sub> @ 100 Hz. DC PSRR: 5V ±500 mV

- 4: Error applies down to 60 degree lead (PF = 0.5 capacitive) and 60 degree lag (PF = 0.5 inductive).

- 5: Refer to Section 4.0 "Device Overview" for complete description.

- **6:** Specified by characterization, not production tested.

- 7: 1 MCLK period at 3.58 MHz is equivalent to less than < 0.005 degrees at 50 or 60 Hz.

### **ELECTRICAL CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 4.5V$  to 5.5V, Internal  $V_{REF}$ , HPF turned on (AC mode),  $A_{GND}$ ,  $D_{GND} = 0V$ , MCLK = 3.58 MHz;  $T_A = -40$ °C to +85°C.

| Parameter                                     | Sym               | Min | Тур. | Max    | Units              | Comment                                     |  |  |

|-----------------------------------------------|-------------------|-----|------|--------|--------------------|---------------------------------------------|--|--|

| ADC/PGA Specifications                        |                   |     |      |        |                    |                                             |  |  |

| Offset Error                                  | V <sub>OS</sub>   | _   | 2    | 5      | mV                 | Referred to Input, applies to both channels |  |  |

| Gain Error Match                              |                   | _   | 0.5  | _      | % F <sub>OUT</sub> | (Note 5)                                    |  |  |

| Internal Voltage Reference                    |                   |     |      |        |                    |                                             |  |  |

| Voltage                                       |                   | _   | 2.4  | _      | V                  |                                             |  |  |

| Tolerance                                     |                   | _   | ±2   | _      | %                  |                                             |  |  |

| Tempco                                        |                   | _   | 15   | _      | ppm/°C             |                                             |  |  |

| Reference Input                               |                   |     |      |        |                    |                                             |  |  |

| Input Range                                   |                   | 2.2 |      | 2.6    | V                  |                                             |  |  |

| Input Impedance                               |                   | 3.2 |      |        | kΩ                 |                                             |  |  |

| Input Capacitance                             |                   | _   |      | 10     | pF                 |                                             |  |  |

| Analog Inputs                                 |                   |     |      |        |                    |                                             |  |  |

| Maximum Signal Level                          |                   | _   | _    | ±1     | V                  | CH0+,CH0-,CH1+,CH1- to A <sub>GND</sub>     |  |  |

| Differential Input Voltage<br>Range Channel 0 |                   |     |      | ±470/G | mV                 | G = PGA Gain on Channel 0                   |  |  |

| Differential Input Voltage<br>Range Channel 1 |                   | _   | _    | ±660   | mV                 |                                             |  |  |

| Input Impedance                               |                   | 390 | _    | _      | kΩ                 | Proportional to 1/MCLK                      |  |  |

| Oscillator Input                              |                   |     |      |        |                    |                                             |  |  |

| Frequency Range                               | MCLK              | 1   | _    | 4      | MHz                |                                             |  |  |

| Power Specifications                          |                   |     |      |        |                    |                                             |  |  |

| Operating Voltage                             |                   | 4.5 | _    | 5.5    | V                  | $AV_{DD,}DV_{DD}$                           |  |  |

| $I_{DD,A}$                                    | $I_{DD,A}$        |     | 2.3  | 2.8    | mA                 | AV <sub>DD</sub> pin only                   |  |  |

| $I_{DD,D}$                                    | I <sub>DD,D</sub> | _   | 0.8  | 1.2    | mA                 | DV <sub>DD</sub> pin only                   |  |  |

- Note 1: Measurement error = (Energy Measured By Device True Energy)/True Energy \* 100%. Accuracy is measured with signal (±660 mV) on Channel 1. F<sub>OUT0</sub>, F<sub>OUT1</sub> pulse outputs. Valid from 45 Hz to 75 Hz. See typical performance curves for higher frequencies and increased dynamic range. This parameter is not 100% production tested.

- 2: Does not include internal V<sub>REF</sub>. Gain = 1, CH0 = 470 mVDC, CH1 = 660 mVDC, difference between measured output frequency and expected transfer function.

- 3: Percent of HF<sub>OUT</sub> output frequency variation; Includes external  $V_{REF}$  = 2.5V, CH1 = 100 mV<sub>RMS</sub> @ 50 Hz, CH2 = 100 mV<sub>RMS</sub> @ 50 Hz, AV<sub>DD</sub> = 5V + 1 V<sub>pp</sub> @ 100 Hz. DC PSRR: 5V ±500 mV

- 4: Error applies down to 60 degree lead (PF = 0.5 capacitive) and 60 degree lag (PF = 0.5 inductive).

- 5: Refer to Section 4.0 "Device Overview" for complete description.

- 6: Specified by characterization, not production tested.

- 7: 1 MCLK period at 3.58 MHz is equivalent to less than < 0.005 degrees at 50 or 60 Hz.

#### TEMPERATURE CHARACTERISTICS

| <b>Electrical Specifications:</b> Unless otherwise indicated, $V_{DD}$ = 4.5V to 5.5V, $A_{GND}$ , $D_{GND}$ = 0V. |                   |                       |    |            |      |      |  |  |

|--------------------------------------------------------------------------------------------------------------------|-------------------|-----------------------|----|------------|------|------|--|--|

| Parameters                                                                                                         | Sym               | Sym Min Typ Max Units |    | Conditions |      |      |  |  |

| Temperature Ranges                                                                                                 |                   |                       |    |            |      |      |  |  |

| Specified Temperature Range                                                                                        | T <sub>A</sub>    | -40                   | _  | +85        | °C   |      |  |  |

| Operating Temperature Range                                                                                        | T <sub>A</sub>    | -40                   | _  | +125       | °C   | Note |  |  |

| Storage Temperature Range                                                                                          | T <sub>A</sub>    | -65                   | _  | +150       | °C   |      |  |  |

| Thermal Package Resistances                                                                                        |                   |                       |    |            |      |      |  |  |

| Thermal Resistance, 24L-SSOP                                                                                       | $\theta_{\sf JA}$ | _                     | 73 | _          | °C/W |      |  |  |

**Note:** The MCP3909 operates over this extended temperature range, but with reduced performance. In any case, the Junction Temperature (T<sub>J</sub>) must not exceed the Absolute Maximum specification of +150°C.

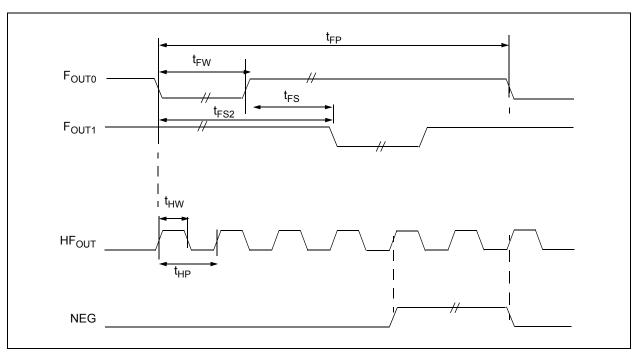

### **TIMING CHARACTERISTICS**

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 4.5V$  to 5.5V,  $A_{GND}$ ,  $D_{GND}$  = 0V, MCLK = 3.58 MHz;  $T_A$  = -40°C to +85°C. Sym **Parameter** Units Min Тур Max Comment **Frequency Outputs** F<sub>OUT0</sub> and F<sub>OUT1</sub> Pulse Width 275 ms 984376 MCLK periods  $t_{FW}$ (Logic Low) (Note 1) HF<sub>OUT</sub> Pulse Width 90 ms 322160 MCLK periods  $t_{HW}$ (Note 2) Refer to Equation 4-1 F<sub>OUT0</sub> and F<sub>OUT1</sub> Pulse Period  $t_{FP}$ S Refer to Equation 4-2 HF<sub>OUT</sub> Pulse Period s  $t_{HP}$  $F_{OUT0}$  to  $F_{OUT1}$  Falling-Edge  $0.5 t_{FP}$ t<sub>FS2</sub> 4/MCLK F<sub>OUT0</sub> to F<sub>OUT1</sub> Minimum Sepa $t_{FS}$ ration Digital I/O FOUT0 and FOUT1 Output High  $V_{OH}$ 4.5 V  $I_{OH} = 10 \text{ mA}, DV_{DD} = 5.0V$ Voltage  $F_{OUT0}$  and  $F_{OUT1}$  Output Low  $V_{OL}$ 0.5 V  $I_{OL}$  = 10 mA,  $DV_{DD}$  = 5.0V Voltage V HF<sub>OUT</sub> and NEG Output High  $V_{OH}$ 4.0  $I_{OH} = 5 \text{ mA}, DV_{DD} = 5.0 \text{V}$ Voltage V  $I_{OL} = 5 \text{ mA}, DV_{DD} = 5.0 \text{V}$ HF<sub>OUT</sub> and NEG Output Low 0.5  $V_{OL}$ Voltage  $DV_{DD} = 5.0\overline{V}$ ٧ High-Level Input Voltage  $V_{IH}$ 2.4 (All Digital Input Pins) V  $DV_{DD} = 5.0V$ Low Level Input Voltage  $V_{II}$ 0.85 (All Digital Input Pins)

- **Note 1:** If output pulse period ( $t_{EP}$ ) falls below 984376\*2 MCLK periods, then  $t_{EW}$  = 1/2  $t_{EP}$ .

- 2: If output pulse period ( $t_{HP}$ ) falls below 322160\*2 MCLK periods, then  $t_{HW}$  = 1/2  $t_{HP}$ . When F2, F1, F0 equals 0,1,1, the HF<sub>OUT</sub> pulse time is fixed at 64 x MCLK periods or 18 µs for MCLK = 3.58 MHz.

0.1

±1

μΑ

- 3: Specified by characterization, not production tested.

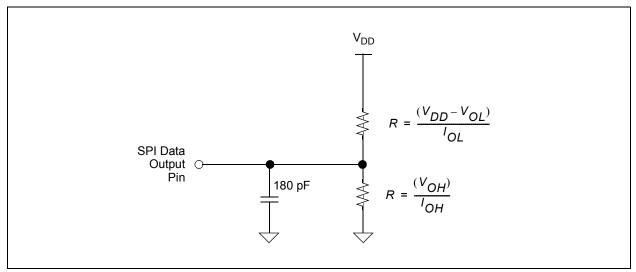

- 4: Serial timings specified and production tested with 180 pF load.

Input Leakage Current

Pin Capacitance

$V_{IN} = 0$ ,  $V_{IN} = DV_{DD}$

(Note 3)

### MCP3909

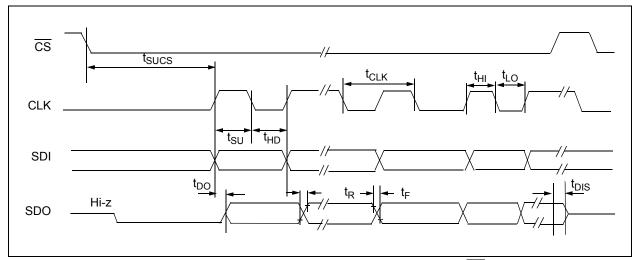

### **TIMING CHARACTERISTICS (CONTINUED)**

**Electrical Specifications:** Unless otherwise indicated, all parameters apply at  $AV_{DD} = DV_{DD} = 4.5V$  to 5.5V,  $A_{GND}$ ,  $D_{GND} = 0V$ , MCLK = 3.58 MHz;  $T_A = -40$ °C to +85°C.

| - GIVD, - GIVD                                | , . А               |        |          |             |       |                                               |

|-----------------------------------------------|---------------------|--------|----------|-------------|-------|-----------------------------------------------|

| Parameter                                     | Sym                 | Min    | Тур      | Max         | Units | Comment                                       |

| Serial Interface Timings (Note 4              | )                   |        |          |             |       |                                               |

| Data Ready Pulse Width                        | t <sub>DR</sub>     |        | 4/MCLK   |             |       |                                               |

| Reset Time                                    | t <sub>RST</sub>    | 100    | _        | _           | ns    |                                               |

| Output Data Rate                              | f <sub>ADC</sub>    | _      | MCLK/256 | _           |       |                                               |

| Serial Clock Frequency                        | f <sub>CLK</sub>    |        | _        | 20          | MHz   | V <sub>DD</sub> = 5V                          |

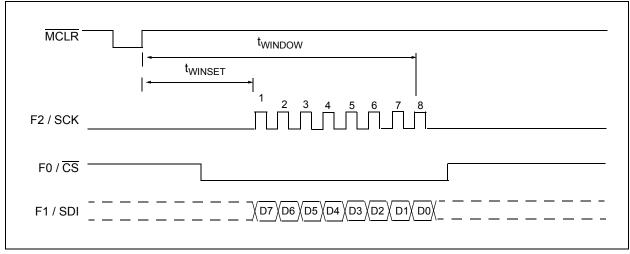

| Window for serial mode entry codes            | t <sub>WINDOW</sub> | _      | _        | 32/<br>MCLK | _     | Last bit must be clocked in before this time. |

| Window start time for serial mode entry codes | t <sub>WINSET</sub> | 1/MCLK | _        | _           | _     | First bit must be clocked in after this time. |

| Serial Clock High Time                        | t <sub>HI</sub>     | _      | _        | 25          | ns    | f <sub>CLK</sub> = 20 MHz                     |

| Serial Clock Low Time                         | t <sub>LO</sub>     | _      | _        | 25          | ns    | f <sub>CLK</sub> = 20 MHz                     |

| CS Fall to First Rising CLK Edge              | t <sub>SUCS</sub>   | 15     | _        | _           | ns    |                                               |

| Data Input Setup Time                         | t <sub>SU</sub>     | 10     | _        | _           | ns    |                                               |

| Data Input Hold Time                          | t <sub>HD</sub>     | _      | _        | 10          | ns    |                                               |

| CS Rise to Output Disable                     | t <sub>DIS</sub>    | _      | _        | 150         | ns    |                                               |

| CLK Rise to Output Data Valid                 | t <sub>DO</sub>     | _      | _        | 30          | ns    |                                               |

| SDO Rise Time                                 | t <sub>R</sub>      | _      | 2        | _           | ns    |                                               |

| SDO Fall Time                                 | t <sub>F</sub>      | _      | 2        | _           | ns    |                                               |

|                                               |                     |        |          |             |       |                                               |

**Note 1:** If output pulse period ( $t_{EP}$ ) falls below 984376\*2 MCLK periods, then  $t_{EW}$  = 1/2  $t_{EP}$ .

- 3: Specified by characterization, not production tested.

- 4: Serial timings specified and production tested with 180 pF load.

<sup>2:</sup> If output pulse period ( $t_{HP}$ ) falls below 322160\*2 MCLK periods, then  $t_{HW}$  = 1/2  $t_{HP}$ . When F2, F1, F0 equals 0,1,1, the HF<sub>OUT</sub> pulse time is fixed at 64 x MCLK periods or 18  $\mu$ s for MCLK = 3.58 MHz.

FIGURE 1-1: Output Timings for Active Power Pulse Outputs and Negative Power Pin.

FIGURE 1-2: Serial Interface Timings showing Output, Rise, Hold, and  $\overline{\text{CS}}$  Times.

FIGURE 1-3: SPI Output Pin Loading Circuit During SPI Testing.

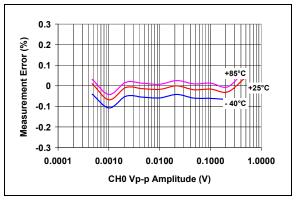

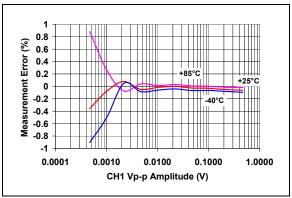

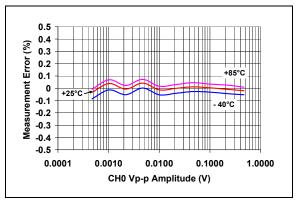

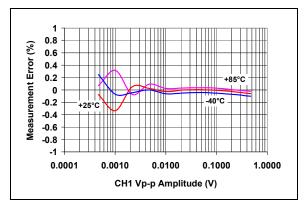

### 2.0 TYPICAL PERFORMANCE CURVES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore outside the warranted range.

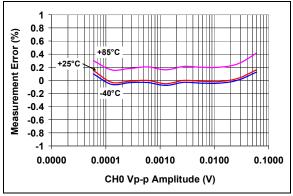

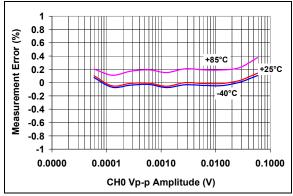

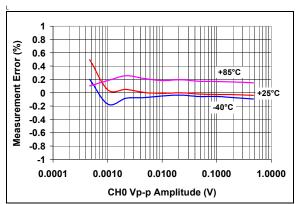

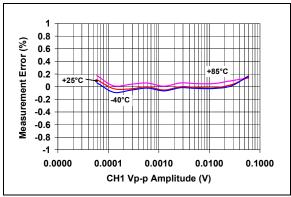

**FIGURE 2-1:** Active Power Measurement Error (Gain = 8, PF = 1).

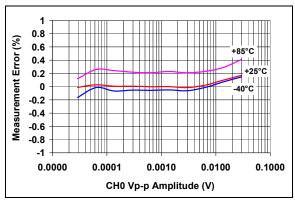

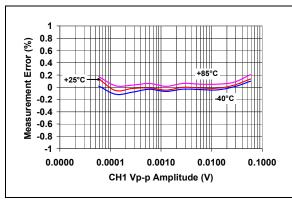

FIGURE 2-2: Active Power Measurement Error (Gain = 16, PF = 1).

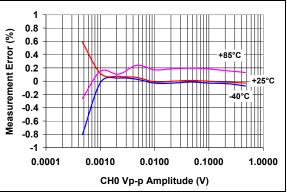

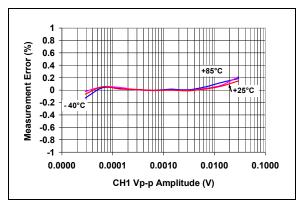

**FIGURE 2-3:** Active Power Measurement Error (Gain = 2, PF = 1).

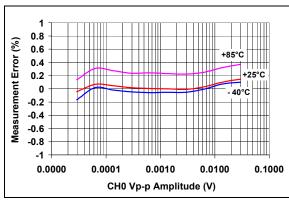

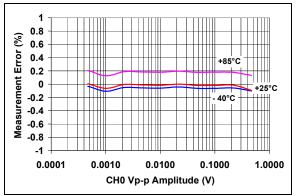

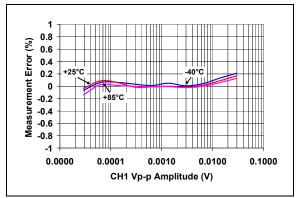

FIGURE 2-4: Active Power Measurement Error (Gain = 8, PF = 0.5).

FIGURE 2-5: Active Power Measurement Error (Gain = 16, PF = 0.5).

**FIGURE 2-6:** Active Power Measurement Error (Gain =2, PF = 0.5).

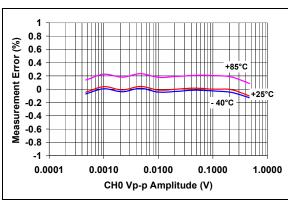

FIGURE 2-7: Active Power Measurement Error (Gain = 1, PF = 1).

**FIGURE 2-8:** Active Power Measurement Error (Gain = 1, PF = 0.5).

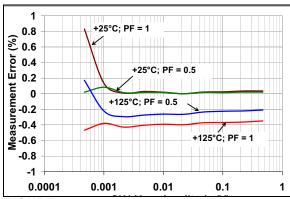

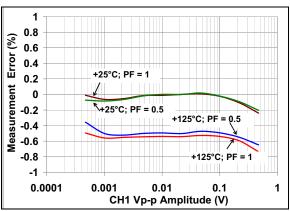

FIGURE 2-9: Measurement Error, Temperature = +125°C, Gain = 1.

FIGURE 2-10: Measurement Error, Temperature = +125°C, Gain = 2.

FIGURE 2-11: Measurement Error, Temperature = +125°C, Gain = 8.

FIGURE 2-12: Measurement Error, Temperature = +125°C, Gain = 16.

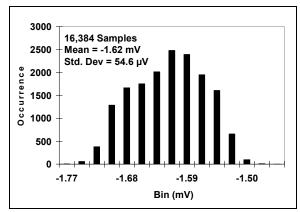

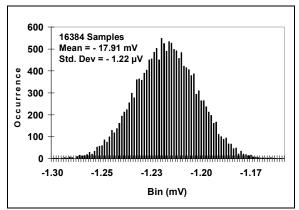

**FIGURE 2-13:** Channel 0 Offset Error (DC Mode, HPF off, G = 1, PF = 1).

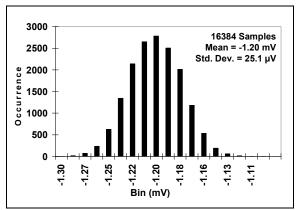

FIGURE 2-14: Channel 0 Offset Error (DC Mode, HPF off, G = 2, PF = 1).

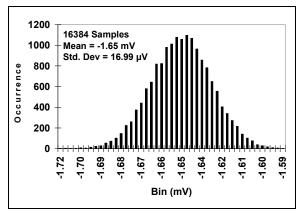

**FIGURE 2-15:** Channel 0 Offset Error (DC Mode, HPF off, G = 8, PF = 1).

**FIGURE 2-16:** Channel 0 Offset Error (DC Mode, HPF Off, G = 16, PF = 1).

### MCP3909

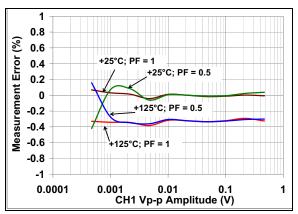

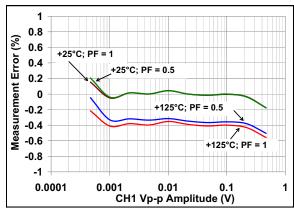

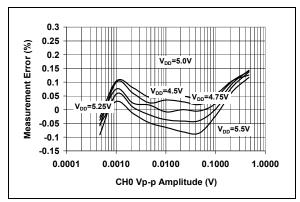

**FIGURE 2-17:** Active Power Measurement Error over  $V_{DD}$ , Internal  $V_{REF}$  (G = 16, PF = 1).

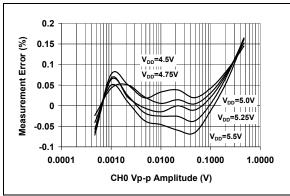

**FIGURE 2-18:** Active Power Measurement Error over  $V_{DD}$ , External  $V_{REF}$  (G = 1, PF = 1).

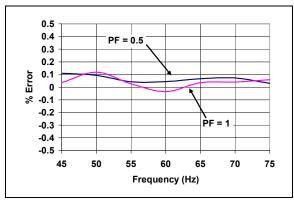

**FIGURE 2-19:** Active Power Measurement Error vs. Input Frequency (G = 16).

**FIGURE 2-20:** Active Power Measurement Error with External  $V_{RFF}$  (G = 1, PF = 1).

**FIGURE 2-21:** Active Power Measurement Error with External  $V_{REF}$  (G = 1, PF = 0.5).

**FIGURE 2-22:** Active Power Measurement Error with External  $V_{REF}$  (G = 2, PF = 1).

**FIGURE 2-23:** Active Power Measurement Error with External  $V_{REF}$  (G = 2, PF = 0.5).

**FIGURE 2-24:** Active Power Measurement Error with External  $V_{REF}$  (G = 8, PF = 1).

**FIGURE 2-25:** Active Power Measurement Error with External  $V_{REF}$  (G = 8, PF = 0.5).

**FIGURE 2-26:** Active Power Measurement Error with External  $V_{REF}$  (G = 16, PF = 1).

**FIGURE 2-27:** Active Power Measurement Error with External  $V_{REF}$  (G =16, PF = 0.5).

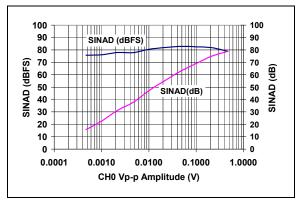

**FIGURE 2-28:** Signal-to-Noise and Distortion Ratio vs. Input Signal Amplitude (G = 1).

### MCP3909

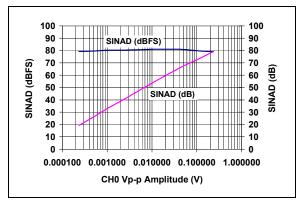

**FIGURE 2-29:** Signal-to-Noise and Distortion Ratio vs. Input Signal Amplitude (G = 2).

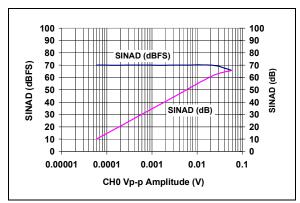

**FIGURE 2-30:** Signal-to-Noise and Distortion Ratio vs. Input Signal Amplitude (G = 8).

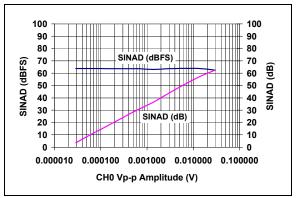

**FIGURE 2-31:** Signal-to-Noise and Distortion Ratio vs. Input Signal Amplitude (G = 16).

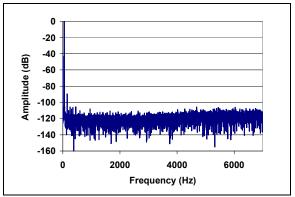

**FIGURE 2-32:** Frequency Spectrum, 50 Hz Input Signal.

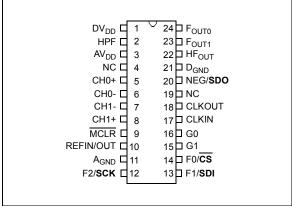

### 3.0 PIN DESCRIPTIONS

The descriptions of the pins are listed in Table 3-1.

TABLE 3-1: PIN FUNCTION TABLE

| MCP3909 | 0                 | 2                                                                              |  |  |  |

|---------|-------------------|--------------------------------------------------------------------------------|--|--|--|

| SSOP    | Symbol            | Description                                                                    |  |  |  |

| 1       | DV <sub>DD</sub>  | Digital Power Supply Pin                                                       |  |  |  |

| 2       | HPF               | High-Pass Filters Control Logic Pin                                            |  |  |  |

| 3       | $AV_DD$           | Analog Power Supply Pin                                                        |  |  |  |

| 4       | NC                | No Connect                                                                     |  |  |  |

| 5       | CH0+              | Non-Inverting Analog Input Pin for Channel 0 (Current Channel)                 |  |  |  |

| 6       | CH0-              | Inverting Analog Input Pin for Channel 0 (Current Channel)                     |  |  |  |

| 7       | CH1-              | Inverting Analog Input Pin for Channel 1 (Voltage Channel)                     |  |  |  |

| 8       | CH1+              | Non-Inverting Analog Input Pin for Channel 1 (Voltage Channel)                 |  |  |  |

| 9       | MCLR              | Master Clear Logic Input Pin                                                   |  |  |  |

| 10      | REFIN/OUT         | Voltage Reference Input/Output Pin                                             |  |  |  |

| 11      | A <sub>GND</sub>  | Analog Ground Pin, Return Path for internal analog circuitry                   |  |  |  |

| 12      | SCK / F2          | Serial Clock or Frequency Control for HF <sub>OUT</sub> Logic Input Pin        |  |  |  |

| 13      | SDI / F1          | Serial Data Input or Frequency Control for F <sub>OUT0/1</sub> Logic Input Pin |  |  |  |

| 14      | CS / F0           | Chip Select or Frequency Control for F <sub>OUT0/1</sub> Logic Input Pin       |  |  |  |

| 15      | G1                | Gain Control Logic Input Pin                                                   |  |  |  |

| 16      | G0                | Gain Control Logic Input Pin                                                   |  |  |  |

| 17      | OSC1              | Oscillator Crystal Connection Pin or Clock Input Pin                           |  |  |  |

| 18      | OSC2              | Oscillator Crystal Connection Pin or Clock Output Pin                          |  |  |  |

| 19      | NC                | No Connect                                                                     |  |  |  |

| 20      | SDO / NEG         | Serial Data Out or Negative Power Logic Output Pin                             |  |  |  |

| 21      | D <sub>GND</sub>  | Digital Ground Pin, Return Path for Internal Digital Circuitry                 |  |  |  |

| 22      | HF <sub>OUT</sub> | High-Frequency Logic Output Pin (Intended for Calibration)                     |  |  |  |

| 23      | F <sub>OUT1</sub> | Differential Mechanical Counter Logic Output Pin                               |  |  |  |

| 24      | F <sub>OUT0</sub> | Differential Mechanical Counter Logic Output Pin                               |  |  |  |

### 3.1 Digital V<sub>DD</sub> (DV<sub>DD</sub>)

$\ensuremath{\mathsf{DV}_{\mathsf{DD}}}$  is the power supply pin for the digital circuitry within the MCP3909 device.

This pin requires appropriate bypass capacitors and should be maintained to  $5V \pm 10\%$  for specified operation. Refer to **Section 6.0 "Applications Information"**.

### 3.2 High-Pass Filter Input Logic Pin (HPF)

HPF controls the state of the high-pass filter in both input channels. A logic '1' enables both filters, removing any DC offset coming from the system or the device. A logic '0' disables both filters allowing DC voltages to be measured.

### 3.3 Analog $V_{DD}$ (AV<sub>DD</sub>)

${\rm AV}_{\rm DD}$  is the power supply pin for the analog circuitry within the MCP3909.

This pin requires appropriate bypass capacitors and should be maintained to  $5V \pm 10\%$  for specified operation. Refer to **Section 6.0** "Applications Information".

### 3.4 Current Channel (CH0-, CH0+)

CH0- and CH0+ are the fully differential analog voltage input channels for the current measurement, containing a PGA for small-signal input, such as shunt current sensing. The linear and specified region of this channel is dependant on the PGA gain. This corresponds to a maximum differential voltage of  $\pm 470$  mV/G and maximum absolute voltage, with respect to  $A_{GND}$ , of  $\pm 1 V$ . Up to  $\pm 6 V$  can be applied to these pins without the risk of permanent damage.

Refer to Section 1.0 "Electrical Characteristics".

### 3.5 Voltage Channel (CH1-,CH1+)

CH1- and CH1+ are the fully differential analog voltage input channels for the voltage measurement. The linear and specified region of these channels have a maximum differential voltage of  $\pm 660~\text{mV}$  and a maximum absolute voltage of  $\pm 1\text{V}$ , with respect to  $A_{GND}$ . Up to  $\pm 6\text{V}$  can be applied to these pins without the risk of permanent damage.

Refer to Section 1.0 "Electrical Characteristics".

### 3.6 Master Clear (MCLR)

MCLR controls the reset for both delta-sigma ADCs, all digital registers, the SINC filters for each channel and all accumulators post multiplier. The MCLR pin is also used to change pin functionality and enter the serial interface mode. A logic '0' resets all registers and holds both ADCs in a Reset condition. The charge stored in both ADCs is flushed and their output is maintained to 0x0000h. The only block consuming power on the digital power supply during Reset is the oscillator circuit.

### 3.7 Reference (REFIN/OUT)

REFIN/OUT is the output for the internal 2.4V reference. This reference has a typical temperature coefficient of 15 ppm/°C and a tolerance of  $\pm 2\%$ . In addition, an external reference can also be used by applying voltage to this pin within the specified range. This pin requires appropriate bypass capacitors to  $A_{GND}$ , even when using the internal reference only.

Refer to Section 6.0 "Applications Information".

### 3.8 Analog Ground (A<sub>GND</sub>)

$A_{GND}$  is the ground connection to internal analog circuitry (ADCs, PGA, band gap reference, POR). To ensure accuracy and noise cancellation, this pin must be connected to the same ground as  $D_{GND}$ , preferably with a star connection. If an analog ground plane is available, it is recommended that this device be tied to this plane of the PCB. This plane should also reference all other analog circuitry in the system.

### 3.9 Serial Clock Input or F2 Frequency Control Pin

This dual function pin can act as either the serial clock input for SPI communication or the F2 selection for the high-frequency output and low-frequency output pin ranges, changing the value of the constants  $F_C$  and  $H_{FC}$  used in the device transfer function.  $F_C$  and  $H_{FC}$  are the frequency constants that define the period of the output pulses for the device.

### 3.10 Serial Data Input or F1 Frequency Control Pin

This dual function pin can act as either the serial data input for SPI communication or the F1 selection for the high-frequency output and low-frequency output pin ranges, changing the value of the constants  $F_C$  and  $H_{FC}$  used in the device transfer function.  $F_C$  and  $H_{FC}$  are the frequency constants that define the period of the output pulses for the device.

### 3.11 Chip Select (CS) or F0 Frequency Control Pin

This dual function pin can act as either the chip select for SPI communication or the F0 selection for the high-frequency output and low-frequency output pin ranges by changing the value of the constants  $\mathsf{F}_{\mathsf{C}}$  and  $\mathsf{H}_{\mathsf{FC}}$  used in the device transfer function.  $\mathsf{F}_{\mathsf{C}}$  and  $\mathsf{H}_{\mathsf{FC}}$  are the frequency constants that define the period of the output pulses for the device.

### 3.12 Gain Control Logic Pins (G1, G0)

G1 and G0 select the PGA gain (G) on Channel 0 from four different values: 1, 2, 8 and 16.

### 3.13 Oscillator (OSC1, OSC2)

OSC1 and OSC2 provide the master clock for the device. A resonant crystal or clock source with a similar sinusoidal waveform must be placed across these pins to ensure proper operation. The typical clock frequency specified is 3.579545 MHz. However, the clock frequency can be within the range of 1 MHz to 4 MHz without disturbing measurement error. Appropriate load capacitance should be connected to these pins for proper operation.

A full-swing, single-ended clock source may be connected to OSC1 with proper resistors in series to ensure no ringing of the clock source due to fast transient edges.

### 3.14 Serial Data Output or Negative Power Output Logic Pin (NEG)

This dual function pin can act as either the serial data output for SPI communication or NEG. NEG detects the phase difference between the two channels and will go to a logic '1' state when the phase difference is greater than 90° (i.e., when the measured real power is negative). The output state is synchronous with the rising edge of HF $_{\rm OUT}$  and maintains the logic '1' until the real power becomes positive again and HF $_{\rm OUT}$  shows a pulse.

### 3.15 Ground Connection (D<sub>GND</sub>)

$D_{GND}$  is the ground connection to internal digital circuitry (SINC filters, multiplier, HPF, LPF, digital-to-frequency converter and oscillator). To ensure accuracy and noise cancellation,  $D_{GND}$  must be connected to the same ground as  $A_{GND},$  preferably with a star connection. If a digital ground plane is available, it is recommended that this device be tied to this plane of the Printed Circuit Board (PCB). This plane should also reference all other digital circuitry in the system.

### 3.16 High-Frequency Output (HF<sub>OUT</sub>)

${\sf HF}_{\sf OUT}$  is the high-frequency output of the device and supplies the instantaneous real-power information. The output is a periodic pulse output, with its period proportional to the measured real power, and to the  ${\sf HF}_{\sf C}$  constant defined by F0, F1 and F2 pin logic states. This output is the preferred output for calibration due to faster output frequencies, giving smaller calibration times. Since this output gives instantaneous real power, the  $2\omega$  ripple on the output should be noted. However, the average period will show minimal drift.

### 3.17 Frequency Output (FOUTO, FOUT1)

$F_{OUT0}$  and  $F_{OUT1}$  are the frequency outputs of the device that supply the average real-power information. The outputs are periodic pulse outputs, with its period proportional to the measured real power, and to the  $F_{C}$  constant, defined by F0 and F1 pin logic states. These pins include high-output drive capability for direct use of electromechanical counters and 2-phase stepper motors. Since this output supplies average real power, any  $2\omega$  ripple on the output pulse period is minimal.

#### 4.0 DEVICE OVERVIEW

The MCP3909 is an energy metering IC that serves two distinct functions that can operate simultaneously:

- Active Power Pulse Output

- Waveform Output via SPI Interface

For the active power output, the device supplies a frequency output proportional to active (real) power, and higher frequency output proportional to the instantaneous power for meter calibration.

For the waveform output, it can be used serially to gather 16-bit voltage channel and current channel A/D data, or 20-bit wide multiplier output data. Both channels use 16-bit, second-order, delta-sigma ADCs that oversample the input at a frequency equal to MCLK/4, allowing for wide dynamic range input signals.

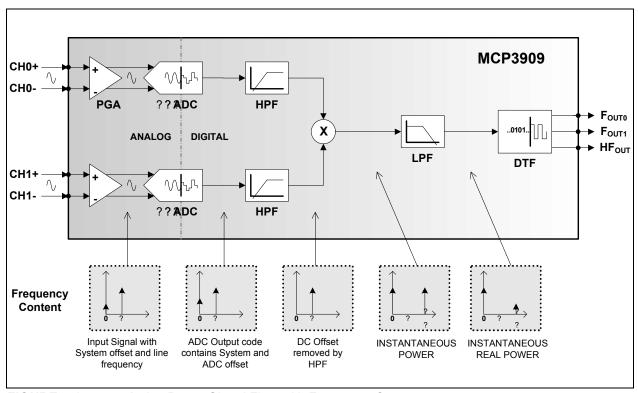

A Programmable Gain Amplifier (PGA) increases the usable range on the current input channel (Channel 0). Figure 4-1 represents the simplified block diagram of the MCP3909, detailing its main signal processing blocks.

Two digital high-pass filters cancel the system offset on both channels such that the real-power calculation does not include any circuit or system offset. After being high-pass filtered, the voltage and current signals are multiplied to give the instantaneous power signal. This signal does not contain the DC offset components, such that the averaging technique can be efficiently used to give the desired active-power output.

#### 4.1 Active Power

The instantaneous power signal contains the active power information; it is the DC component of the instantaneous power. The averaging technique can be used with both sinusoidal and non-sinusoidal waveforms, as well as for all power factors. The instantaneous power is thus low-pass filtered in order to produce the instantaneous real-power signal.

digital-to-frequency converter accumulates the instantaneous active real power information to produce output pulses with a frequency proportional to the average real power. The low-frequency pulses present at the F<sub>OUT0</sub> and F<sub>OUT1</sub> outputs are designed to drive electromechanical counters and two-phase stepper motors displaying the real-power energy consumed. Each pulse corresponds to a fixed quantity of real energy, selected by the F2, F1 and F0 logic settings. The HF<sub>OUT</sub> output has a higher frequency setting and less integration period such that it can represent the instantaneous real-power signal. Due to the shorter accumulation time, it enables the user to proceed to faster calibration under steady load conditions (see Section 4.8 "Active Power FOUT0/1 and HFOUT Output Frequencies").

FIGURE 4-1: Active Power Signal Flow with Frequency Contents.

### 4.2 Analog Inputs

The MCP3909 analog inputs can be connected directly to the current and voltage transducers (such as shunts or current transformers). Each input pin is protected by specialized ESD structures that are certified to pass 5 kV HBM and 500V MM contact charge. These structures also allow up to  $\pm 6$ V continuous voltage to be present at their inputs without the risk of permanent damage.

Both channels have fully differential voltage inputs for better noise performance. The absolute voltage at each pin relative to  $A_{GND}$  should be maintained in the  $\pm 1V$  range during operation in order to ensure the measurement error performance. The common-mode signals should be adapted to respect both the previous conditions and the differential input voltage range. For best performance, the common-mode signals should be referenced to  $A_{GND}$ .

The current channel comprises a PGA on the front-end to allow for smaller signals to be measured without additional signal conditioning. The maximum differential voltage specified on Channel 0 is equal to  $\pm 470$  mV/ Gain (see Table 4-1). The maximum peak voltage specified on Channel 1 is equal to  $\pm 660$  mV.

TABLE 4-1: GAIN SELECTIONS

| G1 | G0 | CH0 Gain | Maximum<br>CH0 Voltage |

|----|----|----------|------------------------|

| 0  | 0  | 1        | ±470 mV                |

| 0  | 1  | 2        | ±235 mV                |

| 1  | 0  | 8        | ±60 mV                 |

| 1  | 1  | 16       | ±30 mV                 |

### 4.3 16-Bit Delta-Sigma A/D Converters

The ADCs used in the MCP3909 for both current and voltage channel measurements are delta-sigma ADCs. They comprise a second-order, delta-sigma modulator using a multi-bit DAC and a third-order SINC filter. The delta-sigma architecture is very appropriate for the applications targeted by the MCP3909 because it is a waveform-oriented converter architecture that can offer both high linearity and low distortion performance throughout a wide input dynamic range. It also creates minimal requirements for the anti-aliasing filter design. The multi-bit architecture used in the ADC minimizes quantization noise at the output of the converters without disturbing the linearity.

Each ADC has a 16-bit resolution, allowing wide input dynamic range sensing. The oversampling ratio of both converters is 64. Both converters are continuously converting during normal operation. When the MCLR pin is low, both converters will be in Reset and output code 0x0000h. If the voltage at the inputs of the ADC is larger than the specified range, the linearity is no longer specified. However, the converters will continue to produce output codes until their saturation point is reached. The DC saturation point is around 700 mV for Channel 0 and 1V for Channel 1, using internal voltage reference. The output code will be locked past the saturation point to the maximum output code.

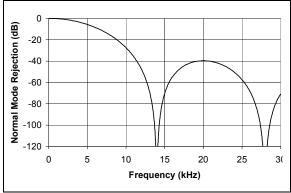

The clocking signals for the ADCs are equally distributed between the two channels in order to minimize phase delays to less than 1 MCLK period (see Section 3.2 "High-Pass Filter Input Logic Pin (HPF)"). The SINC filters main notch is positioned at MCLK/256 (14 kHz with MCLK = 3.58 MHz), allowing the user to be able to measure wide harmonic content on either channel. The data ready signals used for synchronization of the part with a MCU will come at a rate of MCLK/256 and a pipeline delay of 3 data readys is required to settle the SINC 3rd order digital filter. The magnitude response of the SINC filter is shown in Figure 4-2.

FIGURE 4-2: SINC Filter Magnitude Response (MCLK = 3.58 MHz).

### 4.4 Ultra-Low Drift V<sub>RFF</sub>

The MCP3909 contains an internal voltage reference source specially designed to minimize drift over temperature. This internal  $V_{REF}$  supplies reference voltage to both current and voltage channels ADCs. The typical value of this voltage reference is 2.4V ±100 mV. The internal reference has a very low typical temperature coefficient of ±15 ppm/°C, allowing the output frequencies to have minimal variation with respect to temperature since they are proportional to  $(1/V_{REF})^2$ .

The output pin for the voltage reference is REFIN/OUT. Appropriate bypass capacitors must be connected to the REFIN/OUT pin for proper operation (see **Section 6.0 "Applications Information"**). The voltage reference source impedance is typically 4 k $\Omega$ , which enables this voltage reference to be overdriven by an external voltage reference source.

If an external voltage reference source is connected to the REFIN/OUT pin, the external voltage will be used as the reference for both current and voltage channel ADCs. The voltage across the source resistor will then be the difference between the internal and external voltage. The allowed input range for the external voltage source goes from 2.2V to 2.6V for accurate measurement error. A  $V_{\rm REF}$  value outside of this range will cause additional heating and power consumption due to the source resistor, which might affect measurement error.

### 4.5 Power-On Reset (POR)

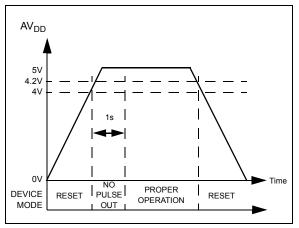

The MCP3909 contains an internal POR circuit that monitors analog supply voltage  ${\rm AV}_{\rm DD}$  during operation. This circuit ensures correct device startup at system power-up and system power-down events. The POR circuit has built-in hysteresis and a timer to give a high degree of immunity to potential ripple and noise on the power supplies, allowing proper settling of the power supply during power-up. A 0.1  $\mu F$  decoupling capacitor should be mounted as close as possible to the  ${\rm AV}_{\rm DD}$  pin, providing additional transient immunity (see Section 6.0 "Applications Information").

The threshold voltage is typically set at 4V, with a tolerance of about  $\pm 5\%$ . If the supply voltage falls below this threshold, the MCP3909 will be held in a Reset condition (equivalent to applying logic '0' on the  $\overline{\text{MCLR}}$  pin). The typical hysteresis value is approximately 200 mV in order to prevent glitches on the power supply.

Once a power-up event has occurred, an internal timer prevents the part from outputting any pulse for approximately 1s (with MCLK = 3.58 MHz), thereby preventing potential metastability due to intermittent resets caused by an unsettled regulated power supply. Figure 4-3 illustrates the different conditions for a power-up and a power-down event in the typical conditions.

FIGURE 4-3:

Power-On Reset Operation.

### 4.6 High-Pass Filters and Multiplier

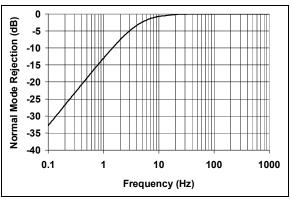

The active real-power value is extracted from the DC instantaneous power. Therefore, any DC offset component present on Channel 0 and Channel 1 affects the DC component of the instantaneous power and will cause the real-power calculation to be erroneous. In order to remove DC offset components from the instantaneous power signal, a high-pass filter has been introduced on each channel. Since the high-pass filtering introduces phase delay, identical high-pass filters are implemented on both channels. The filters are clocked by the same digital signal, ensuring a phase difference between the two channels of less than one MCLK period. Under typical conditions (MCLK = 3.58 MHz), this phase difference is less than 0.005°, with a line frequency of 50 Hz. The cut-off frequency of the filter (4.45 Hz) has been chosen to induce minimal gain error at typical line frequencies, allowing sufficient settling time for the desired applications. The two highpass filters can be disabled by applying logic '0' to the HPF pin.

FIGURE 4-4: HPF Magnitude Response (MCLK = 3.58 MHz).

The multiplier output gives the product of the two high-pass filtered channels, corresponding to instantaneous real power. Multiplying two sine wave signals by the same  $\omega$  frequency gives a DC component and a  $2\omega$  component. The instantaneous power signal contains the real power of its DC component, while also containing  $2\omega$  components coming from the line frequency multiplication. These  $2\omega$  components come for the line frequency (and its harmonics) and must be removed in order to extract the real-power information. This is accomplished using the low-pass filter and DTF converter.

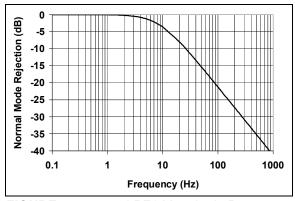

### 4.7 Active Power Low-Pass Filter and DTF Converter

For the active power signal calculation, the MCP3909 uses a digital low-pass filter. This low-pass filter is a first-order IIR filter, which is used to extract the active real-power information (DC component) from the instantaneous power signal. The magnitude response of this filter is detailed in Figure 4-5. Due to the fact that the instantaneous power signal has harmonic content (coming from the  $2\omega$  components of the inputs), and since the filter is not ideal, there will be some ripple at the output of the low-pass filter at the harmonics of the line frequency.

The cut-off frequency of the filter (8.9 Hz) has been chosen to have sufficient rejection for commonly-used line frequencies (50 Hz and 60 Hz). With a standard input clock (MCLK = 3.58 MHz) and a 50 Hz line frequency, the rejection of the  $2\omega$  component (100 Hz) will be more than 20 dB. This equates to a  $2\omega$  component containing 10 times less power than the main DC component (i.e., the average active real power).

FIGURE 4-5: LPF1 Magnitude Response (MCLK = 3.58 MHz).

The output of the low-pass filter is accumulated in the digital-to-frequency converter. This accumulation is compared to a different digital threshold for  $F_{OUT0/1}$  and  $HF_{OUT}$ , representing a quantity of real energy measured by the part. Every time the digital threshold on  $F_{OUT0/1}$  or  $HF_{OUT}$  is crossed, the part will output a pulse (See Section 4.8 "Active Power FOUT0/1 and HFOUT Output Frequencies").

The equivalent quantity of real energy required to output a pulse is much larger for the  $F_{OUT0/1}$  outputs than the  $HF_{OUT}$ . This is such that the integration period for the  $F_{OUT0/1}$  outputs is much larger. This larger integration period acts as another low-pass filter so that the output ripple due to the  $2\omega$  components is minimal. However, these components are not totally removed, since realized low-pass filters are never ideal. This will create a small jitter in the output frequency. Averaging the output pulses with a counter or a MCU in the application will then remove the small sinusoidal content of the output frequency and filter out the remaining  $2\omega$  ripple.

$HF_{OUT}$  is intended to be used for calibration purposes due to its instantaneous power content. The shorter integration period of  $HF_{OUT}$  demands that the  $2\omega$  component be given more attention. Since a sinusoidal signal average is zero, averaging the  $HF_{OUT}$  signal in steady-state conditions will give the proper real energy value.

### 4.8 Active Power F<sub>OUT0/1</sub> and HF<sub>OUT</sub> Output Frequencies

The thresholds for the accumulated energy are different for  $F_{OUT0/1}$  and  $HF_{OUT}$  (i.e., they have different transfer functions). The  $F_{OUT0/1}$  allowed output frequencies are quite low in order to allow superior integration time (see **Section 4.7 "Active Power Low-Pass Filter and DTF Converter"**). The  $F_{OUT0/1}$  output frequency can be calculated with the following equation:

### EQUATION 4-1: F<sub>OUT</sub> FREQUENCY OUTPUT EQUATION

$$F_{OUT}(Hz) = \frac{8.06 \times V_0 \times V_1 \times G \times F_C}{(V_{REE})^2}$$

Where:

V<sub>0</sub> = the RMS differential voltage on Channel 0

V<sub>1</sub> = the RMS differential voltage on

Channel 1

G = the PGA gain on Channel 0 (current channel)

F<sub>C</sub> = the frequency constant selected

$V_{REF}$  = the voltage reference

For a given DC input V, the DC and RMS values are equivalent. For a given AC input signal with amplitude of V, the equivalent RMS value is V/ sqrt(2), assuming purely sinusoidal signals. Note that since the real power is the product of two RMS inputs, the output frequencies of AC signals are half of the DC inputs ones, again assuming purely sinusoidal AC signals. The constant  $F_{\rm C}$  depends on the  $F_{\rm OUT0}$  and  $F_{\rm OUT1}$  digital settings. Table 4-2 shows  $F_{\rm OUT0/1}$  output frequencies for the different logic settings.

TABLE 4-2: ACTIVE POWER OUTPUT FREQUENCY CONSTANT  $F_C$  FOR FOUT0/1 ( $V_{REF} = 2.4V$ )

| F1 | F0 | F <sub>C</sub> (Hz)  | F <sub>C</sub> (Hz)<br>(MCLK = 3.58 MHz) | F <sub>OUT</sub> Frequency (Hz)<br>with Full-Scale<br>DC Inputs | F <sub>OUT</sub> Frequency (Hz)<br>with Full-Scale<br>AC Inputs |

|----|----|----------------------|------------------------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| 0  | 0  | MCLK/2 <sup>21</sup> | 1.71                                     | 0.74                                                            | 0.37                                                            |

| 0  | 1  | MCLK/2 <sup>20</sup> | 3.41                                     | 1.48                                                            | 0.74                                                            |

| 1  | 0  | MCLK/2 <sup>19</sup> | 6.83                                     | 2.96                                                            | 1.48                                                            |

| 1  | 1  | MCLK/2 <sup>18</sup> | 13.66                                    | 5.93                                                            | 2.96                                                            |

The high-frequency output  ${\sf HF}_{\sf OUT}$  has lower integration times and, thus, higher frequencies. The output frequency value can be calculated with the following equation:

# EQUATION 4-2: ACTIVE POWER HF<sub>OUT</sub> FREQUENCY OUTPUT EQUATION

$$HF_{OUT}(Hz) = \frac{8.06 \times V_0 \times V_1 \times G \times HF_C}{(V_{REF})^2}$$

Where:

V<sub>0</sub> = the RMS differential voltage on Channel 0

V<sub>1</sub> = the RMS differential voltage on Channel 1

G = the PGA gain on Channel 0 (current channel)

HF<sub>C</sub> = the frequency constant selected

$V_{REF}$  = the voltage reference

The constant  $HF_C$  depends on the  $F_{OUT0}$  and  $F_{OUT1}$  digital settings with the Table 4-3.

The detailed timings of the output pulses are described in the **Timing Characteristics** table (see **Section 1.0** "**Electrical Characteristics**" and Figure 1-1).

### 4.8.1 MINIMAL OUTPUT FREQUENCY FOR NO-LOAD THRESHOLD

The MCP3909 also includes, on each output frequency, a no-load threshold circuit that will eliminate any creep effects in the meter. The outputs will not show any pulse if the output frequency falls below the no-load threshold. This threshold only applies to the pulse outputs and does not gate any serial data coming from either the A/D output or the multiplier output. The minimum output frequency on F<sub>OUT0/1</sub> and HF<sub>OUT</sub> is equal to 0.0015% of the maximum output frequency (respectively F<sub>C</sub> and HF<sub>C</sub>) for each of the F2, F1 and F0 selections (see Table 4-2 and Table 4-3); except when F2, F1, F0 = 011. In this last configuration, the no-load threshold feature is disabled. The selection of F<sub>C</sub> will determine the start-up current load. In order to respect the IEC standards requirements, the meter will have to be designed to allow start-up currents compatible with the standards by choosing the FC value matching these requirements. For additional applications information on no-load threshold, startup current and other meter design points, refer to AN994, "IEC Compliant Active Energy Meter Design Using The MCP3905/6", (DS00994).

TABLE 4-3: OUTPUT FREQUENCY CONSTANT HF<sub>C</sub> FOR HF<sub>OUT</sub> ( $V_{REF} = 2.4V$ )

| F2 | F1 | F0 | HF <sub>C</sub>       | HF <sub>C</sub> (Hz) | HF <sub>C</sub> (Hz)<br>(MCLK = 3.58 MHz) | HF <sub>OUT</sub> Frequency (Hz) with full scale AC Inputs |

|----|----|----|-----------------------|----------------------|-------------------------------------------|------------------------------------------------------------|

| 0  | 0  | 0  | 64 x F <sub>C</sub>   | MCLK/2 <sup>15</sup> | 109.25                                    | 27.21                                                      |

| 0  | 0  | 1  | 32 x F <sub>C</sub>   | MCLK/2 <sup>15</sup> | 109.25                                    | 27.21                                                      |

| 0  | 1  | 0  | 16 x F <sub>C</sub>   | MCLK/2 <sup>15</sup> | 109.25                                    | 27.21                                                      |

| 0  | 1  | 1  | 2048 x F <sub>C</sub> | MCLK/2 <sup>7</sup>  | 27968.75                                  | 6070.12                                                    |

| 1  | 0  | 0  | 128 x F <sub>C</sub>  | MCLK/2 <sup>16</sup> | 219.51                                    | 47.42                                                      |

| 1  | 0  | 1  | 64 x F <sub>C</sub>   | MCLK/2 <sup>16</sup> | 219.51                                    | 47.42                                                      |

| 1  | 1  | 0  | 32 x F <sub>C</sub>   | MCLK/2 <sup>16</sup> | 219.51                                    | 47.42                                                      |

| 1  | 1  | 1  | 16 x F <sub>C</sub>   | MCLK/2 <sup>16</sup> | 219.51                                    | 47.42                                                      |

### 5.0 SERIAL INTERFACE DESCRIPTION

### 5.1 Dual Functionality Pin And Serial Interface Overview

The MCP3909 device contains three serial modes that are accessible by changing the pin functionality of the NEG, F2, F1, and F0 pins to SDO, SCK, SDI and  $\overline{\text{CS}}$ , respectively.

These modes are entered by giving the MCP3909 device a serial command on these pins during a time window after device reset or POR. During this window of time, F2 acts as SCK, F1 acts as SDI and F0 acts as CS. Once a serial mode has been entered, the device must be reset to disable mode functionality, or change to another serial mode. This is done by using MCLR pin or power on reset event.

During serial mode entry and the three serial modes, data is clocked into the device on the rising edge of SCK and out of the device on the falling edge of SCK.

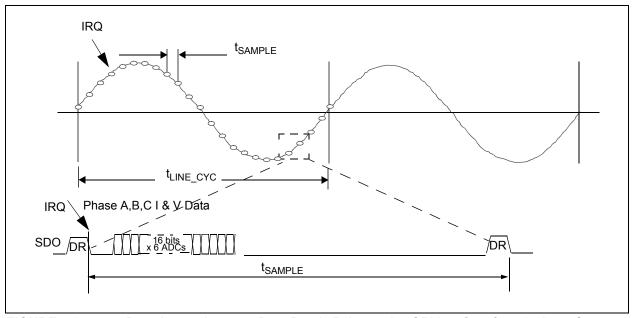

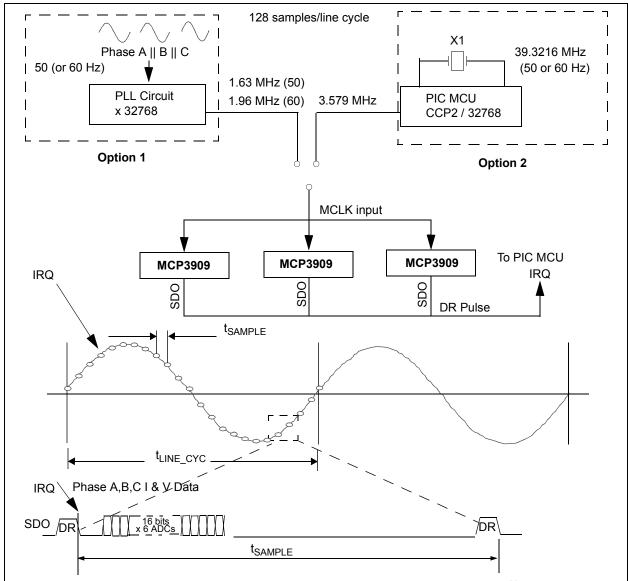

The SPI data can be access at up to 20 MHz. This speed enables quick data retrieval in between conversion times. For 3-phase metering applications with multiple ADCs, this fast communication is essential to allow for power calculation windows between conversions, as shown in Figure 5-3.

After a serial mode has been entered, all blocks of the MCP3909 device are still operational. The PGA, A/D converters, HPF, multiplier, LPF, and other digital sections are still functional, allowing the device to have true dual functionality in energy metering systems.

FIGURE 5-1: Dual Functionality Pins for the MCP3909.

FIGURE 5-2: Data Access between Data Ready Pulses using SPI Interface for a 3-phase System.

FIGURE 5-3: Dual Functionality Pin Serial Mode Entry Protocol.

### 5.2 Serial Mode Entry Codes

The MCP3909 devices contains three different serial modes with data presented in 2's complement coding.

- · Multiplier Output

- · Dual Channel Output

- · Filter Input

After entering any of these modes the active power calculation block is still functional and presents output pulses on  $F_{OUT0}$ ,  $F_{OUT1}$ , and  $HF_{OUT}$ . For this reason, the F2, F1, F0 output frequency selection constant can be changed with multiple command bytes for serial mode entry.

The command bytes to enter these modes are described in Table 5-1.

TABLE 5-1: ENTRY CODES

| Command<br>D7D0 | Serial Mode                   | Internal State of F2, F1, F0 Constants Frequency<br>Selection During Serial Mode <sup>(1)</sup> |        |        |  |

|-----------------|-------------------------------|-------------------------------------------------------------------------------------------------|--------|--------|--|

| D7              |                               | F2                                                                                              | F1     | F0     |  |

| 1 0 1 0 0 0 0 1 | Multiplier Output             | 0                                                                                               | F1 pin | 1      |  |

| 1 0 1 0 1 0 0 1 | Multiplier Output             | 1                                                                                               | F1 pin | 1      |  |

| 10100100        | Dual Channel Output Pre HPF1  | 0                                                                                               | F1 pin | 1      |  |

| 10101100        | Dual Channel Output Post HPF1 | 1                                                                                               | F1 pin | 1      |  |

| 10101010        | Filter Input                  | 1                                                                                               | 0      | F0 pin |  |

| 10101110        | Filter Input                  | 1                                                                                               | 1      | F0 pin |  |

| 10100010        | Filter Input                  | 0                                                                                               | 0      | F0 pin |  |

| 10100110        | Filter Input                  | 0                                                                                               | 1      | F0 pin |  |

Note 1: The active power frequency outputs F<sub>OUT0</sub>, F<sub>OUT1</sub>, and HF<sub>OUT</sub> remain active after serial mode entry. Leaving the SDI (F1) and CS (F0) pins at a known state after serial communication will control the frequency selection. The HPF pin controls the state of the HPF for the multiplier mode output and the output pulses from the active power D to F block.

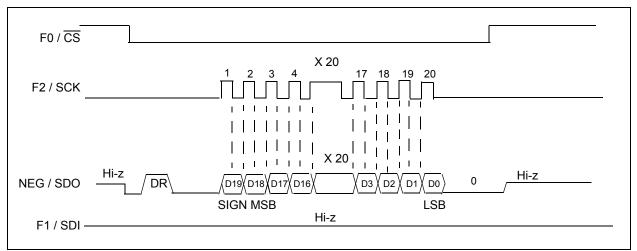

### 5.3 Multiplier Output Mode

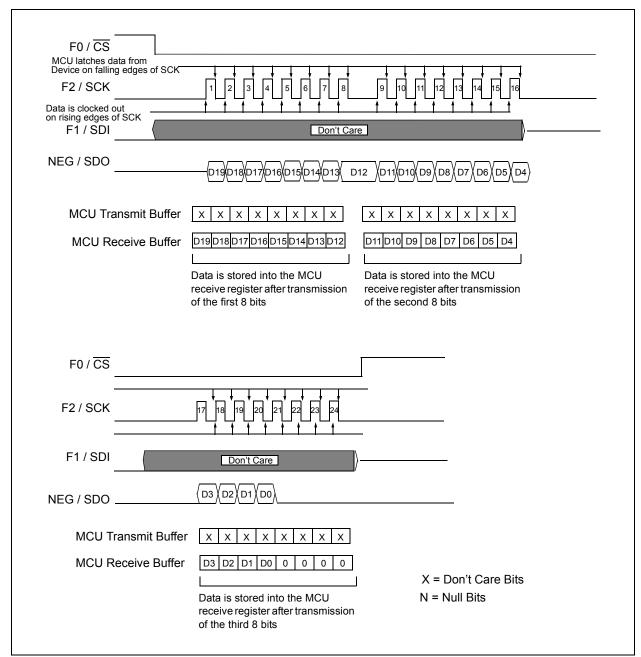

Multiplier mode allows the user to retrieve the output of the multiplier on the MCP3909 device. Data is presented in a 20 bit (19 bit + sign) protocol, MSB first. A data ready flag (DR) is output for every MCLK/256 clock cycles and a new multiplier output value is ready. If the multiplier value is not clocked out of the device it will be over-written. Data is clocked out on the rising edge of SCK.

### **EQUATION 5-1:**

Multiplier Code =

$$\frac{(CH0^{+} - CH0^{-})(CH1^{+} - CH1^{-})}{V_{REF} 2} \bullet 524288 \bullet 8.06 \bullet G$$

TABLE 5-2: MULTIPLIER OUTPUT MODE CODING

| Binary                                  | Decimal |

|-----------------------------------------|---------|

| 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | +524287 |

| 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0     | +524286 |

| 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0     | 0       |

| 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 | -1      |

| 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1   | -524287 |

| 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0   | -524288 |

FIGURE 5-4: Multiplier Output Mode.

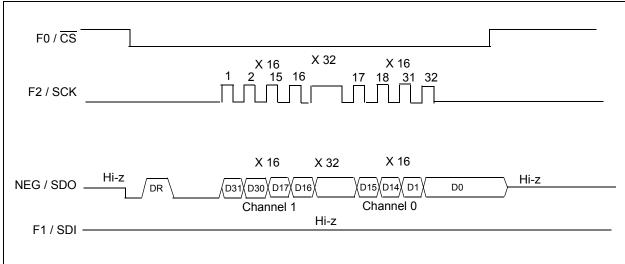

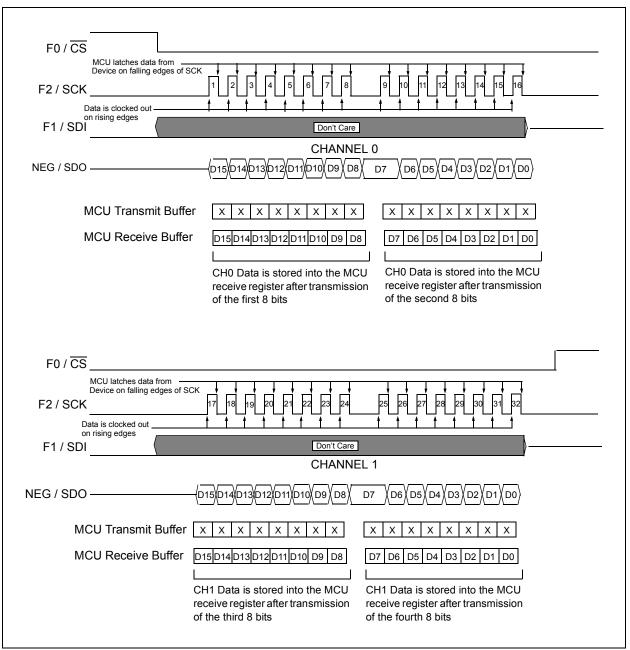

### 5.4 Dual Channel Output Mode

This mode allows the user to retrieve the individual channel information from the ADC outputs. The ADC outputs of both channels are synchronized together and their data ready is represented by the data ready pulse on SDO. If the ADC output values are not clocked out of the device, they will be over-written. A 32-bit data word is given, each channel is 16 bits (15 bits + sign), presented in 2's complement coding. Channel 1 comes first then channel 0.

A data ready flag (DR) is output for every MCLK / 256 clock cycles and a new filter output value is ready. If the dual channel output values are not clocked, and is not clocked out of the device, they will be over-written.

The following formulas relate the channel input voltages to their respective output code. The code locks to +32767 on the positive side, and to -32768 on the negative side.

#### **EQUATION 5-2:**

Channel 0 Code =

$$\left(\frac{(V_{IN+} - V_{IN-})}{V_{REF}}\right) \times 32768 \times \left(\sqrt{8.06 \times \frac{0.66}{0.47}}\right) \times PGA$$

Channel 1 Code =  $\frac{(V_{IN+} - V_{IN-})}{V_{REF}} \times 32768 \times \left(\sqrt{8.06 \times \frac{0.47}{0.66}}\right)$

TABLE 5-3: CHANNEL OUTPUT MODE CODING

|   |     | Bi   | nary | Decimal |          |

|---|-----|------|------|---------|----------|

| 0 | 111 | 1111 | 1111 | 1111    | + 32,767 |

| 0 | 111 | 1111 | 1111 | 1110    | + 32,766 |

| 0 | 000 | 0000 | 0000 | 0000    | 0        |

| 1 | 111 | 1111 | 1111 | 1111    | -1       |

| 1 | 000 | 0000 | 0000 | 0001    | - 32,767 |

| 1 | 000 | 0000 | 0000 | 0000    | - 32,768 |

### 5.5 High-Pass Filter Control

There are two options for the channel output data. The first options collects the channel data pre-high pass filter, or the output of the SINC filter of the delta sigma modulator. The second option collects the channel data post high pass filter. It is important to note that the HPF pin controls the state of the high pass filter for this second option. If the HPF pin is low, the post high pass filter mode will output all zero's. This HPF pin must be high to access the post HPF data in the channel output mode.

FIGURE 5-5: Dual Channel Output Mode.

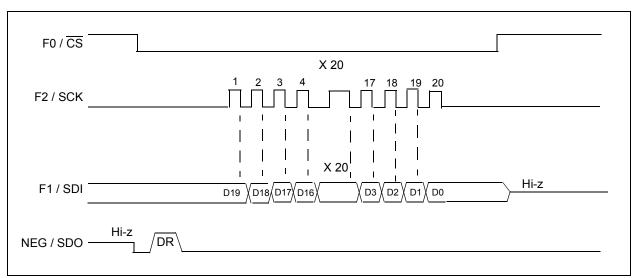

### 5.6 Filter Input Mode

The filter input mode allows the user to feed the MCP3909 device an input to the LPF1. Data is received MSB first. The MCP3909 will treat this data as if it were the output of the multiplier and will LPF and D-F the result as normal, giving the resulting output frequency on HF $_{\rm OUT}$ , F $_{\rm OUT0}$  and F $_{\rm OUT1}$ . See Tables 4-2 and 4-3 for transfer functions of the output frequencies.

When using filter input mode, the user must wait for the data ready flag (DR) to appear on SDO before attempting to clock in data to the device. The user can not access either the multiplier output or the dual channel output while in this mode.

FIGURE 5-6: Filter Input Mode.

### 5.7 Using the MCP3909 with Microcontroller (MCU) SPI Ports

With microcontroller SPI ports, it is required to send groups of eight bits. It is also required that the microcontroller SPI port be configured to clock out data on the falling edge of clock and latch data in on the rising edge, or vice versa depending on the mode.

#### 5.7.1 SPI MODE DEFINITIONS

The following table represents the standard SPI mode terminology, the respective PIC bit settings, and a description of compatibility for the MCP3909 device.

The MCP3909 works in SPI mode 0,1 mode, that is the data is clocked out of the part on the **rising** edge and clocked in on the **falling** edge of SCK.

TABLE 5-4: SPI MODE COMPATIBILITY

| Standard SPI<br>Mode | PIC Control Bits<br>State |     | MCP3909       | Description                                                                                    |  |

|----------------------|---------------------------|-----|---------------|------------------------------------------------------------------------------------------------|--|

| Terminology          | CKP                       | CKE | Compatibility |                                                                                                |  |

| 0,0                  | 0                         | 1   | _             | Idle state for clock is low level, transmit (from PIC) occurs from active to idle clock state  |  |

| 0,1                  | 0                         | 0   | $\sqrt{}$     | Idle state for clock is low level, transmit (from PIC) occurs from idle to active clock state  |  |

| 1,0                  | 1                         | 1   | _             | Idle state for clock is high level, transmit (from PIC) occurs from active to idle clock state |  |

| 1,1                  | 1                         | 0   | _             | Idle state for clock is high level, transmit (from PIC) occurs from idle to active clock state |  |

**FIGURE 5-7:** Multiplier Output Mode 1 SPI Communication using 8-bit segments (Mode 0,1: SCK idles low).

**FIGURE 5-8:** Dual Channel Output Mode SPI Communication using 8-bit segments (Mode 0,1: SCK idles low).

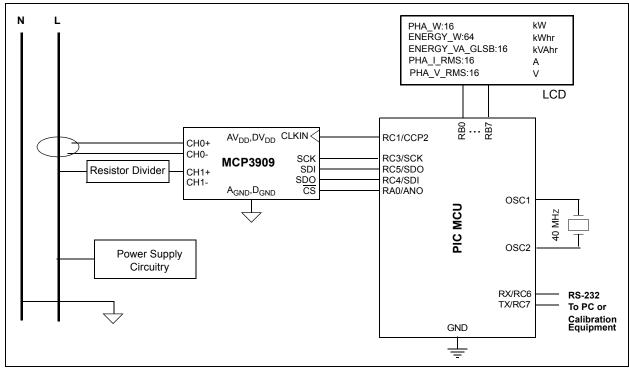

#### 6.0 APPLICATIONS INFORMATION

The following application figures represent meter designs using the MCP3909 device. Some of these applications ideas are available as fully function meter reference designs and demo boards. For complete schematic and for fully function meter designs, visit Microchip's web page for demo board and reference design availability.

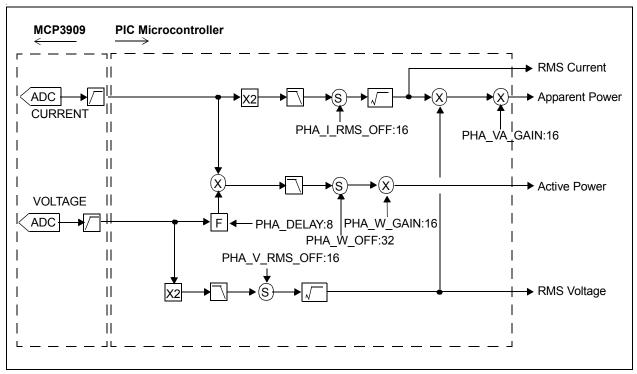

# 6.1 Performing RMS, Apparent Power, and Active Power using MCP3909 Waveform Data

Figure 6-1 represents power calculations from waveform data based on a PIC MCU and MCP3909 device. The PIC MCU accomplishes the following energy meter calculation outputs per phase, per line cycle:

- RMS Current

- RMS Voltage

- Active Power

- Apparent Power

Output registers for the power quantities and calibration registers for phase, offset, gain, and LSB adjustment are available through a serial interface to the PIC microcontroller. See Microchip's web page for firmware solution and demo board.

The example signal flow here shows 4 output power quantities and 6 calibration registers. For a 60 Hz design that is using 128 samples per line cycle for the power calculation the MCP3909 would have a new data ready pulse every 130  $\mu$ s. The SPI communication to gather 16-bits x 2 channels at 10 MHz is approximately 3.2  $\mu$ s, leaving ~125  $\mu$ s for the power calculations before the next sample is ready.

**FIGURE 6-1:** Power Calculations from Waveform Sampling Using a PIC MCU. Register names shown are used on MCP3909 Energy Meter Reference Design.

### 6.2 Achieving Line Cycle Sampling with Zero Blind Cycles

In most energy meter applications, it will be necessary to have  $2^N$  samples for each 50 or 60 Hz line cycle, where N is typically 64, 128 or 256. Controlling the MCLK of the MCP3909 allows you to control the sample rate and ultimately the data ready (DR) pulses for coherent waveform sampling.

The following scheme shows how the TIMER and COMPARATOR modules of the PIC MCU can be used to generate the clock for the MCP3909 from either a PLL internal MCLK. For class 0.2 or class 0.1 meter designs that require harmonic analysis using a PLL is recommended to shift sample rate with line cycle drift, e.g. line cycle changes from 60 Hz to 59.1 Hz. This is shown as option 1 in Figure 6-2.

A simpler lower cost option would be to choose a frequency that would give an integer number of line cycles for exactly 50 Hz (or 60 Hz). This is possible using a 39.3216 MHz crystal for the PIC18F device.

Figure 6-2 shows example clock frequencies to achieve 128 samples for each line cycle, 1.63 MHz for a 50 Hz line, or 1.96 MHz for a 60 Hz line. The MCP3909 clock can operate from 1 MHz to 4 MHz.

Using this approach, the PIC MCU can gather the waveform data immediately after the data ready pulse, at up to 10 MHz. The remainder of the time can be used to calculate the power measurements to achieve true line cycle sampling with zero blind cycles.

For more information and firmware, see the Microchip web page for demo board information.

**FIGURE 6-2:** Using the PIC device to control the MCP3909 MCLK to achieve 2<sup>N</sup> samples per line cycle, 3-phase sampling shown with 6 ADCs.

FIGURE 6-3: Simplified MCU Based Energy Meter.

### 6.3 Meter Calibration

To achieve meter calibration the MCP3909 waveform samples are adjusted during the power calculations on the PIC MCU. In Figure 6-3, this interface is shown via RS-232 on the PIC microcontroller. This process is streamlined using calibration software available from the Microchip's web site.

### 6.4 Analog Meter Design Tips

For analog design tips and PCB layout recommendations, refer to AN994, "IEC Compliant Active Energy Meter Design Using The MCP390X" (DS00994). This application note includes all required energy meter design information, including the following:

- · Meter rating and current sense choices

- · Shunt design

- PGA selection

- · F2, F1, F0 selection

- · Meter calibration

- Anti-aliasing filter design

- · Compensation for parasitic shunt inductance

- · EMC design

- · Power supply design

- · No-Load threshold

- · Start-up current

- Accuracy testing results from MCP390X-based meter

- · EMC testing results from MCP390X-based meter

### 7.0 PACKAGING INFORMATION

### 7.1 Package Marking Information

24-Lead SSOP

#### Examples:

Legend: XX...X Customer-specific information

Y Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

e3 Pb-free JEDEC designator for Matte Tin (Sn)

This package is Pb-free. The Pb-free JEDEC designator (@3)

can be found on the outer packaging for this package.

**Note**: In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

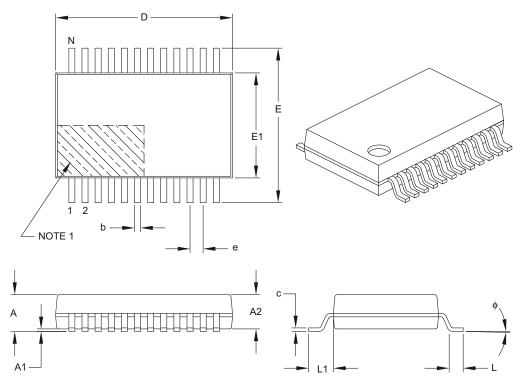

### 24-Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |          |      | MILLIMETERS |  |  |  |

|--------------------------|------------------|----------|------|-------------|--|--|--|

| Dimensio                 | Dimension Limits |          |      | MAX         |  |  |  |

| Number of Pins           | 24               |          |      |             |  |  |  |

| Pitch                    | е                | 0.65 BSC |      |             |  |  |  |

| Overall Height           | Α                | _        | -    | 2.00        |  |  |  |

| Molded Package Thickness | A2               | 1.65     | 1.75 | 1.85        |  |  |  |

| Standoff                 | A1               | 0.05     | -    | _           |  |  |  |

| Overall Width            | Е                | 7.40     | 7.80 | 8.20        |  |  |  |

| Molded Package Width     | E1               | 5.00     | 5.30 | 5.60        |  |  |  |

| Overall Length           | D                | 7.90     | 8.20 | 8.50        |  |  |  |

| Foot Length              | L                | 0.55     | 0.75 | 0.95        |  |  |  |

| Footprint                | L1               | 1.25 REF |      |             |  |  |  |

| Lead Thickness           | С                | 0.09     | -    | 0.25        |  |  |  |

| Foot Angle               | ф                | 0°       | 4°   | 8°          |  |  |  |

| Lead Width               | b                | 0.22     | _    | 0.38        |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.20 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-132B

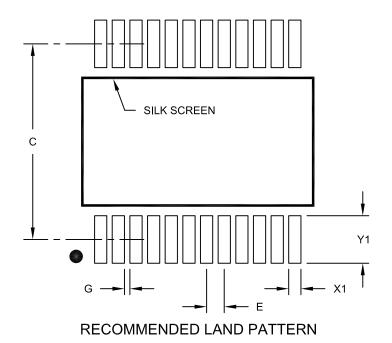

### 24 Lead Plastic Shrink Small Outline (SS) - 5.30 mm Body [SSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS      |          |      |      |  |  |

|--------------------------|------------------|----------|------|------|--|--|

| Dimensior                | Dimension Limits |          |      | MAX  |  |  |

| Contact Pitch            | E                | 0.65 BSC |      |      |  |  |

| Contact Pad Spacing      | С                |          | 7.20 |      |  |  |

| Contact Pad Width (X24)  | X1               |          |      | 0.45 |  |  |

| Contact Pad Length (X24) | Y1               |          |      | 1.75 |  |  |

| Distance Between Pads    | G                | 0.20     |      |      |  |  |

### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.