# DS2780 Standalone Fuel Gauge IC

#### www.maxim-ic.com

#### **GENERAL DESCRIPTION**

The DS2780 measures voltage, temperature and current, and estimates available capacity for rechargeable Lithium Ion and Lithium Ion Polymer batteries. Cell characteristics and application parameters used in the calculations are stored in onchip EEPROM. The available capacity registers report a conservative estimate of the amount of charge that can be removed given the current temperature, discharge rate, stored charge and application parameters. Capacity estimation reported in mAh remaining and percentage of full.

# **APPLICATIONS**

Digital Still Cameras

Sub-Notebook Computers

Handheld PC Data Terminals

3G Multimedia Wireless Handsets

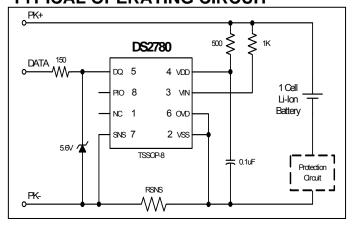

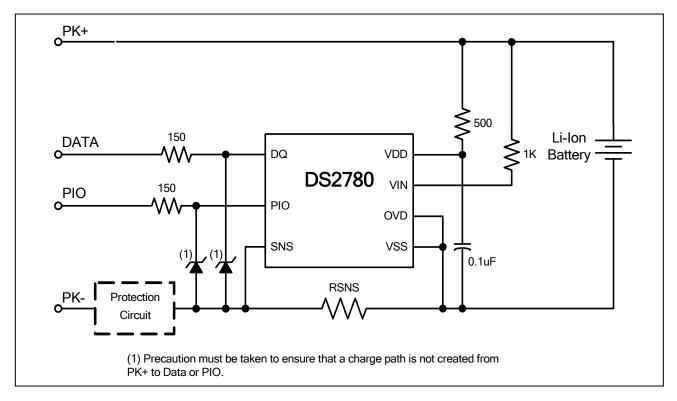

# TYPICAL OPERATING CIRCUIT

#### **FEATURES**

- Precision Voltage, Temperature, and Current Measurement System

- Internal Time Base is Accurate and Temperature Stable

- Absolute and Relative Capacity Estimated from Coulomb Count, Discharge Rate, Temperature and Battery Cell Characteristics

- Accurate Warning of Low Battery Conditions

- Automatic Backup of Coulomb Count and Age Estimation to Nonvolatile (NV) EEPROM

- Gain and Tempco Calibration Allows the Use of Low-Cost Sense Resistors

- 24-Byte Battery/Application Parameter EEPROM

- 16-Byte User EEPROM

- Unique ID and Multidrop 1-Wire<sup>®</sup> Interface

- Tiny 8-pin TSSOP & 10-pin TDFN Package Embeds Easily in Battery Packs Using Thin Prismatic Cells

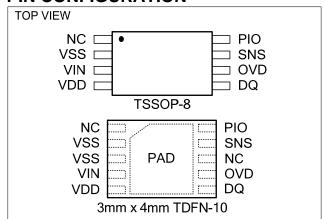

#### PIN CONFIGURATION

# ORDERING INFORMATION

| PART        | MARKING | PACKAGE INFORMATION |

|-------------|---------|---------------------|

| DS2780E     | 2780    | TSSOP               |

| DS2780E/T&R | 2780    | TSSOP Tape-and-Reel |

| DS2780E+    | 2780    | TSSOP               |

| DS2780E+T&R | 2780    | TSSOP Tape-and-Reel |

| DS2780G+    | 2780    | TDFN                |

| DS2780G+T&R | 2780    | TDFN Tape-and-Reel  |

<sup>+</sup>Denotes lead(Pb)-free/RoHS-compliant package.

**Note:** Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device may be simultaneously available through various sales channels. For information about device errata, click here: <a href="https://www.maxim-ic.com/errata">www.maxim-ic.com/errata</a>.

<sup>1-</sup>Wire is a registered trademark of Maxim Integrated Products, Inc.

#### ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Pin Relative to VSS Voltage on VIN Relative to VSS Operating Temperature Range Storage Temperature Range Soldering Temperature (10s) -0.3V to +6.0V -0.3V to  $(V_{DD} + 0.3V)$   $-40^{\circ}$ C to  $+85^{\circ}$ C  $-55^{\circ}$ C to  $+125^{\circ}$ C See JEDEC J-STD-020

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to the absolute maximum rating conditions for extended periods may affect device reliability.

# RECOMMENDED DC OPERATING CHARACTERISTICS

(VDD = 2.5V to 4.5V,  $T_A$  = -20°C to +70°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER             | SYMBOL | CONDITIONS | MIN  | TYP | MAX  | UNITS |

|-----------------------|--------|------------|------|-----|------|-------|

| Supply Voltage        | VDD    | (Note 1)   | +2.5 |     | +4.5 | V     |

| OVD Voltage           |        | (Note 1)   | -0.3 |     | +4.5 | V     |

| DQ, PIO Voltage Range |        | (Note 1)   | -0.3 |     | +5.5 | V     |

# DC ELECTRICAL CHARACTERISTICS

(VDD = 2.5V to 4.5V,  $T_A$  = -20°C to +70°C, unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                    | SYMBOL              | CONDITIONS                     | MIN          | TYP  | MAX       | UNITS     |

|------------------------------|---------------------|--------------------------------|--------------|------|-----------|-----------|

| ACTIVE Current               | I <sub>ACTIVE</sub> | 2.5V ≤ VDD ≤ 4.2V              |              | 65   | 95        | μA        |

| ACTIVE CUITCH                | ACTIVE              |                                |              |      | 105       | μπ        |

| SLEEP Mode Current           | I <sub>SLEEP</sub>  | 2.5V ≤ VDD ≤ 4.2V              |              | 1    | 3         | μA        |

| Input Logic High: DQ, PIO    | V <sub>IH</sub>     | (Note 1)                       | 1.5          |      |           | V         |

| Input Logic Low: DQ, PIO     | $V_{IL}$            | (Note 1)                       |              |      | 0.6       | V         |

| Output Logic Low: DQ, PIO    | $V_{OL}$            | I <sub>OL</sub> = 4mA (Note 1) |              |      | 0.4       | V         |

| Pulldown Current: DQ, PIO    | $I_{PD}$            | $V_{DQ}$ , $V_{PIO} = 0.4V$    |              | 0.2  |           | μA        |

| Input Logic High: OVD        | V <sub>IH</sub>     | (Note 1)                       | VDD –<br>0.2 |      |           | ٧         |

| Input Logic Low: OVD         | $V_{IL}$            | (Note 1)                       |              |      | VSS + 0.2 | V         |

| VIN Input Resistance         | R <sub>IN</sub>     |                                | 15           |      |           | $M\Omega$ |

| DQ Capacitance               | $C_{DQ}$            |                                |              | 50   |           | pF        |

| DQ SLEEP Timeout             | t <sub>SLEEP</sub>  | DQ < V <sub>IL</sub> (Note 5)  | 1.5          | 2.0  | 2.5       | S         |

| Undervoltage SLEEP Threshold | V <sub>SLEEP</sub>  | (Note 1)                       | 2.40         | 2.45 | 2.50      | V         |

# **ELECTRICAL CHARACTERISTICS: TEMPERATURE, VOLTAGE, CURRENT**

$(V_{CC} = 2.5 \text{V to } 4.5 \text{V}, T_A = -20 ^{\circ}\text{C} \text{ to } +70 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25 ^{\circ}\text{C}.)$

| PARAMETER              | SYMBOL           | CONDITIONS | MIN | TYP   | MAX   | UNITS |

|------------------------|------------------|------------|-----|-------|-------|-------|

| Temperature Resolution | T <sub>LSB</sub> |            |     | 0.125 |       | °C    |

| Temperature Error      | $T_{ERR}$        |            |     |       | ±3    | °C    |

| Voltage Resolution     | $V_{LSB}$        |            |     | 4.88  |       | mV    |

| Voltage Full-Scale     | $V_{FS}$         |            | 0   |       | 4.992 | V     |

| Voltage Error          | $V_{ERR}$        |            |     |       | ±50   | mV    |

| Current Resolution     | I <sub>LSB</sub> |            |     | 1.56  |       | μV    |

| PARAMETER                  | SYMBOL            | CONDITIONS                                                                                                                                | MIN   | TYP | MAX   | UNITS            |

|----------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------|-----|-------|------------------|

| Current Full-Scale         | I <sub>FS</sub>   |                                                                                                                                           |       |     | ±51.2 | mV               |

| Current Gain Error         | I <sub>GERR</sub> | (Note 2)                                                                                                                                  |       |     | ±1    | % Full-<br>Scale |

| Current Offset Error       | I <sub>OERR</sub> | 0°C ≤ T <sub>A</sub> ≤ +70°C,<br>2.5V ≤ VDD ≤ 4.2V<br>(Note 4)                                                                            | -7.82 |     | +12.5 | μV               |

| Accumulated Current Offset | <b>q</b> oerr     | $0^{\circ}\text{C} \le \text{T}_{A} \le +70^{\circ}\text{C},$<br>$2.5\text{V} \le \text{VDD} \le 4.2\text{V}$<br>VSNS = VSS, (Notes 3, 4) | -188  |     | +0    | μVhr/<br>day     |

|                            |                   | VDD = 3.8V, T <sub>A</sub> = +25°C                                                                                                        |       |     | ±1    |                  |

| Timebase Error             | t <sub>ERR</sub>  | $0^{\circ}\text{C} \le \text{T}_{\text{A}} \le +70^{\circ}\text{C},$<br>$2.5\text{V} \le \text{VDD} \le 4.2\text{V}$                      |       |     | ±2    | %                |

|                            |                   |                                                                                                                                           |       |     | ±3    |                  |

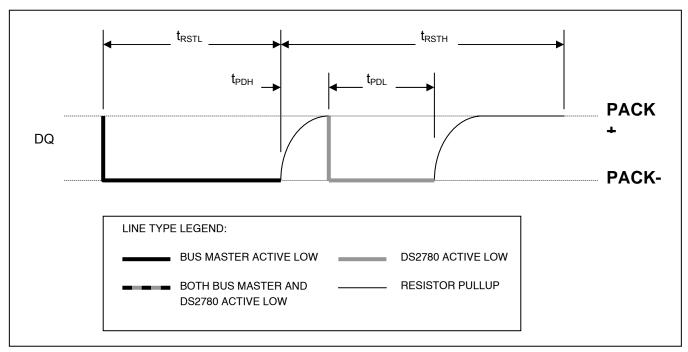

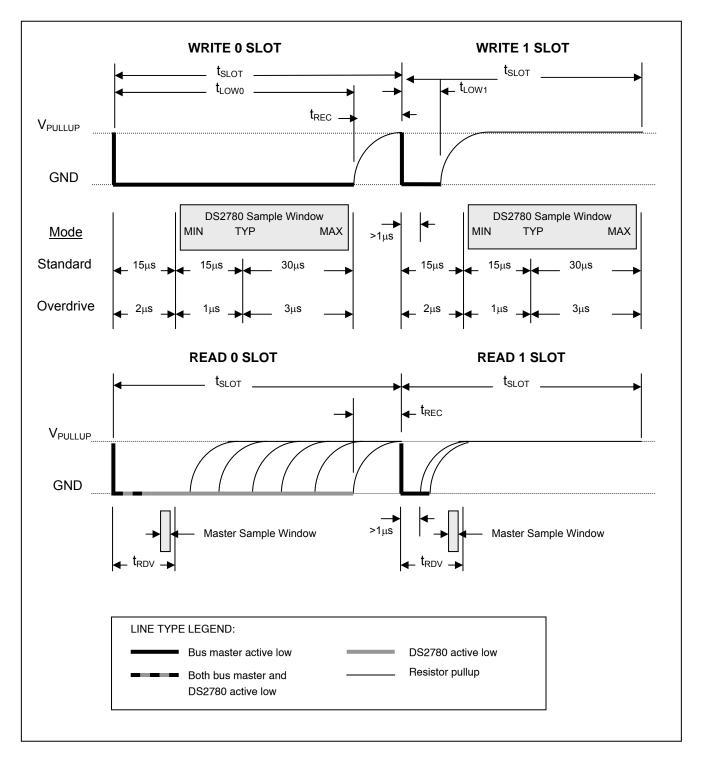

# **ELECTRICAL CHARACTERISTICS: 1-WIRE INTERFACE, STANDARD**

$(V_{CC} = 2.5V \text{ to } 4.5V, T_A = -20^{\circ}\text{C to } +70^{\circ}\text{C.})$

| PARAMETER            | SYMBOL            | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------|-------------------|------------|-----|-----|-----|-------|

| Time Slot            | t <sub>SLOT</sub> |            | 60  |     | 120 | μS    |

| Recovery Time        | t <sub>REC</sub>  |            | 1   |     |     | μS    |

| Write-0 Low Time     | t <sub>LOW0</sub> |            | 60  |     | 120 | μS    |

| Write-1 Low Time     | t <sub>LOW1</sub> |            | 1   |     | 15  | μS    |

| Read Data Valid      | t <sub>RDV</sub>  |            |     |     | 15  | μS    |

| Reset Time High      | t <sub>RSTH</sub> |            | 480 |     |     | μS    |

| Reset Time Low       | t <sub>RSTL</sub> |            | 480 |     | 960 | μS    |

| Presence Detect High | t <sub>PDH</sub>  |            | 15  |     | 60  | μS    |

| Presence Detect Low  | t <sub>PDL</sub>  |            | 60  |     | 240 | μS    |

# **ELECTRICAL CHARACTERISTICS: 1-WIRE INTERFACE, OVERDRIVE**

$(V_{CC} = 2.5V \text{ to } 4.5V, T_A = -20^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER            | SYMBOL            | CONDITIONS | MIN | TYP | MAX | UNITS |

|----------------------|-------------------|------------|-----|-----|-----|-------|

| Time Slot            | t <sub>SLOT</sub> |            | 6   |     | 16  | μS    |

| Recovery Time        | t <sub>REC</sub>  |            | 1   |     |     | μS    |

| Write-0 Low Time     | t <sub>LOW0</sub> |            | 6   |     | 16  | μS    |

| Write-1 Low Time     | t <sub>LOW1</sub> |            | 1   |     | 2   | μS    |

| Read Data Valid      | t <sub>RDV</sub>  |            |     |     | 2   | μS    |

| Reset-Time High      | t <sub>RSTH</sub> |            | 48  |     |     | μS    |

| Reset-Time Low       | t <sub>RSTL</sub> |            | 48  |     | 80  | μS    |

| Presence-Detect High | t <sub>PDH</sub>  |            | 2   |     | 6   | μS    |

| Presence-Detect Low  | t <sub>PDL</sub>  |            | 8   |     | 24  | μS    |

# **EEPROM RELIABILITY SPECIFICATION**

$(V_{CC} = 2.5V \text{ to } 4.5V, T_A = -20^{\circ}\text{C to } +70^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}\text{C}.)$

| PARAMETER             | SYMBOL           | CONDITIONS             | MIN    | TYP | MAX | UNITS  |

|-----------------------|------------------|------------------------|--------|-----|-----|--------|

| EEPROM Copy Time      | t <sub>EEC</sub> |                        |        |     | 10  | ms     |

| EEPROM Copy Endurance | N <sub>EEC</sub> | T <sub>A</sub> = +50°C | 50,000 |     |     | cycles |

Note 1: All voltages are referenced to VSS.

Note 2: Factory calibrated accuracy. Higher accuracy can be achieved by in-system calibration by the user.

Note 3: Accumulation bias register set to 00h.

Note 4: Parameters guaranteed by design.

**Note 5:** The application must wait for the maximum DQ SLEEP Timeout to confirm that the IC has entered sleep mode.

# PIN DESCRIPTION

| NAME | TSSOP<br>PIN | TDFN<br>PIN | FUNCTION                                                                                                                                                                                                                                        |

|------|--------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| NC   | 1            | 1           | Not Connected. Pin not connected internally, float or connect to VSS.                                                                                                                                                                           |

| VSS  | 2            | 2, 3        | <b>Device Ground.</b> Connect directly to the negative terminal of the battery cell. Connect the sense resistor between VSS and SNS.                                                                                                            |

| VIN  | 3            | 4           | <b>Voltage Sense Input.</b> The voltage of the battery cell is monitored through this input pin.                                                                                                                                                |

| VDD  | 4            | 5           | <b>Power-Supply Input.</b> Connect to the positive terminal of the battery cell through a decoupling network.                                                                                                                                   |

| DQ   | 5            | 6           | <b>Data Input/Output</b> . 1-Wire data line. Open-drain output driver. Connect this pin to the DATA terminal of the battery pack. This pin has a weak internal pulldown (I <sub>PD</sub> ) for sensing pack disconnection from host or charger. |

| OVD  | 6            | 7           | 1-Wire Bus Speed Control. Input logic level selects the speed of the 1-Wire bus.  Logic 1 selects overdrive (OVD) and Logic 0 selects standard timing (STD). On a multidrop bus, all devices must operate at the same speed.                    |

| NC   | _            | 8           | Not Connected. Pin not connected internally, float or connect to VSS.                                                                                                                                                                           |

| SNS  | 7            | 9           | Sense Resistor Connection. Connect to the negative terminal of the battery pack. Connect the sense resistor between VSS and SNS.                                                                                                                |

| PIO  | 8            | 10          | <b>Programmable I/O Pin.</b> Can be configured as input or output to monitor or control user-defined external circuitry. Output driver is open drain. This pin has an weak internal pulldown (I <sub>PD</sub> ).                                |

| PAD  | _            | PAD         | <b>Exposed Pad.</b> Connect to VSS or leave floating. (Only present on TDFN package)                                                                                                                                                            |

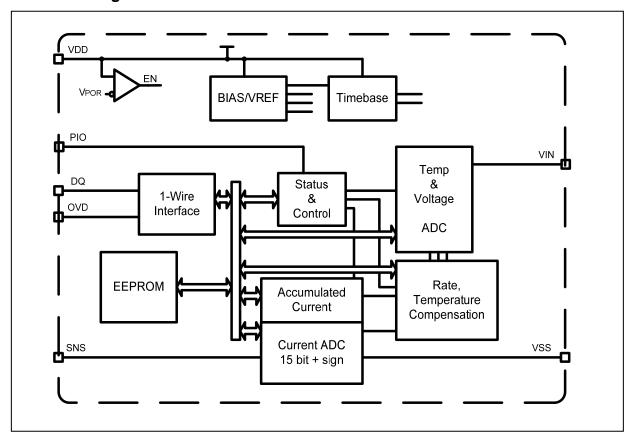

Figure 1. Block Diagram

#### DETAILED DESCRIPTION

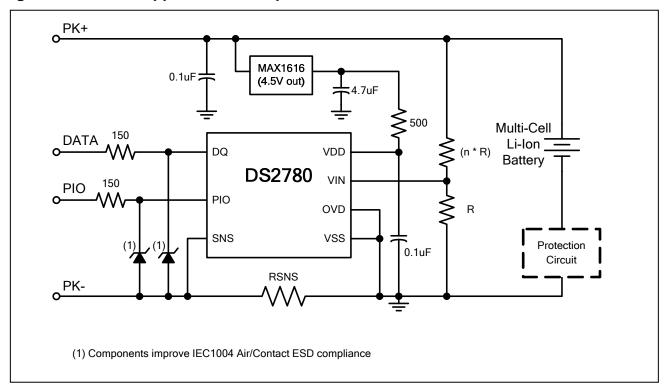

The DS2780 operates directly from 2.5V to 4.5V and supports single cell Lithium-ion battery packs. As shown in Figure 2, the DS2780 accommodates multicell applications by adding a voltage regulator for VDD and voltage divider for VIN. Nonvolatile storage is provided for cell compensation and application parameters. Host side development of fuel-gauging algorithms is eliminated. On-chip algorithms and convenient status reporting of operating conditions reduce the serial polling required of the host processor. For 2-cell applications, the DS2781 is recommended, since it includes a voltage regulator and accepts VIN up to 10V.

Additionally, 16 bytes of EEPROM memory are made available for the exclusive use of the host system and/or pack manufacturer. The additional EEPROM memory can be used to facilitate battery lot and date tracking and non-volatile storage of system or battery usage statistics.

A Dallas 1-Wire interface provides serial communication at the standard 16kbps or overdrive 140kbps speeds. It allows access to data registers, control registers and user memory. A unique, factory programmed 64-bit registration number (8-bit family code + 48-bit serial number + 8-bit CRC) assures that no two parts are alike and enables absolute traceability. The Dallas 1-Wire interface on the DS2780 supports multidrop capability so that multiple slave devices may be addressed with a single pin.

Figure 2. Multicell Application Example

Figure 3. Inside Protector Example

# PROTECTOR CIRCUIT LOCATION

The battery protection circuitry can be located inside or outside the DS2780. Either location is acceptable but there are some advantages and disadvantages to both. With the protection circuit located inside, see Figure 2 and Typical Operating Circuit on page 1, the DS2780 will loose power in a circuit protection event. The DS2780 stores

fuel gauge data to EEPROM, but some data loss can occur depending on the timing of the protection event and the backup. When the protection circuit is connected directly to the battery the protection is absolute, no charging will occur during a protection event. With the protection circuit located outside, see Figure 3, the DS2780 will remain powered up during a protection event. The disadvantage to this configuration is that you run the risk of overcharging the battery by creating an unintentional charge path from PK+ to DATA or PIO ( $V_{PK+} > V_{CELL} + V_{DIODE}$ ). Communication to the DS2780 is broken during a protection event regardless of protector location.

#### **POWER MODES**

The DS2780 has two power modes: ACTIVE and SLEEP. On initial power up, the DS2780 defaults to ACTIVE mode. While in ACTIVE mode, the DS2780 is fully functional with measurements and capacity estimation continuously updated. In SLEEP mode, the DS2780 conserves power by disabling measurement and capacity estimation functions, but preserves register contents. SLEEP mode is entered under two different conditions and an enable bit for each condition makes entry into SLEEP optional. SLEEP mode can be enabled using the Power Mode (PMOD) bit or the Under Voltage Enable (UVEN) bit.

The PMOD type SLEEP is entered if the PMOD bit is set AND DQ is low for  $t_{SLEEP}$  (2s nominal). The condition of DQ low for  $t_{SLEEP}$  can be used to detect a pack disconnection or system shutdown, in which no charge or discharge current will flow. A PMOD SLEEP condition transitions back to ACTIVE mode when DQ is pulled high.

The second option for entering SLEEP is an under voltage condition. When the UVEN bit is set, the DS2780 transitions to SLEEP if the voltage on VIN is less than  $V_{SLEEP}$  (2.45V nominal) AND DQ is stable at a low or high logic level for  $t_{SLEEP}$ . An under-voltage condition occurs when a pack is fully discharged, where loading on the battery should be minimized. UVEN type SLEEP relieves the battery of the  $I_{ACTIVE}$  load until communication on DQ resumes.

**NOTE:** PMOD and UVEN SLEEP features must be disabled when a battery is charged on an external charger that does not connect to the DQ pin. PMOD SLEEP can be used if the charger pulls DQ high. UVEN SLEEP can be used if the charger toggles DQ. The DS2780 remains in SLEEP on a charger that fails to properly drive DQ and therefore does not measure or accumulate current when a battery is charged.

#### INITIATING COMMUNICATION IN SLEEP

When beginning communication with a DS2780 in PMOD SLEEP, DQ must be pulled up first and then a 1-Wire Reset pulse must be issued by the master. In UVEN SLEEP, the procedure depends on the state of DQ when UVEN SLEEP was entered. If DQ was low, DQ must be pulled up and then a 1-Wire Reset pulse must be issued by the master as with PMOD SLEEP. If DQ was high when UVEN SLEEP was entered, then the DS2780 is prepared to receive a 1-Wire reset from the master. In the first two cases with DQ low during SLEEP, the DS2780 does not respond to the first rising edge of DQ with a presence pulse.

#### VOLTAGE MEASUREMENT

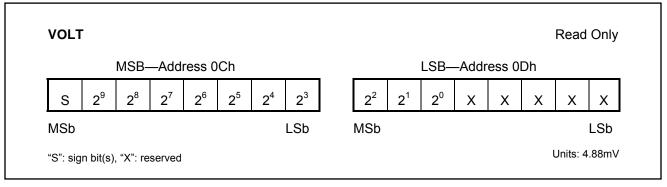

Battery voltage is measured at the VIN input with respect to VSS. It has a range of 0V to 4.992V (pin voltage limited to 4.5V) and a resolution of 4.88mV. The measurement is stored in the VOLTAGE register in two's compliment form and is updated every 440ms. Voltages above the maximum register value are reported at the maximum value; voltages below the minimum register value are reported at the minimum value. The format of the voltage register is shown in Figure 4.

Figure 4. Voltage Register Format

VIN is usually connected to the positive terminal of a single cell Lithium-Ion battery via a  $1k\Omega$  resistor. The input impedance is large enough ( $15M\Omega$ ) to be connected to a high impedance voltage divider in order to support multiple cell applications. The pack voltage should be divided by the number of series cells to present a single cell average voltage to the VIN input. In Figure 2, the value of R can be up to  $1M\Omega$  without incurring significant error due to input loading.

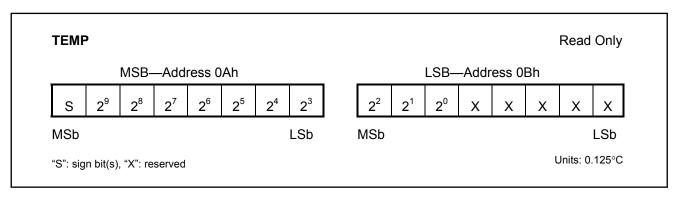

#### TEMPERATURE MEASUREMENT

The DS2780 uses an integrated temperature sensor to measure battery temperature with a resolution of 0.125°C. Temperature measurements are updated every 440ms and placed in the temperature register in two's complement form. The format of the temperature register is shown in Figure 5.

Figure 5. Temperature Register Format

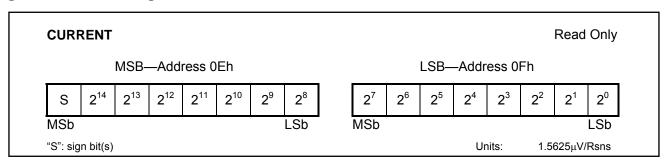

#### **CURRENT MEASUREMENT**

In the ACTIVE mode of operation, the DS2780 continually measures the current flow into and out of the battery by measuring the voltage drop across a low-value current-sense resistor,  $R_{SNS}$ . The voltage-sense range between SNS and VSS is  $\pm 51.2$ mV. The input linearly converts peak signal amplitudes up to 102.4mV as long as the continuous signal level (average over the conversion cycle period) does not exceed  $\pm 51.2$ mV. The ADC samples the input differentially at 18.6kHz and updates the Current register at the completion of each conversion cycle.

The Current register is updated every 3.515s with the current conversion result in two's complement form. Charge currents above the maximum register value are reported at the maximum value (7FFFh = +51.2mV). Discharge currents below the minimum register value are reported at the minimum value (8000h = -51.2mV).

Figure 6. Current Register Format

| CURRENT RESOLUTION (1 LSB) |         |              |              |         |  |  |  |  |

|----------------------------|---------|--------------|--------------|---------|--|--|--|--|

| VSS- R <sub>SNS</sub>      |         |              |              |         |  |  |  |  |

| VSNS                       | 20m $Ω$ | 15m $\Omega$ | 10m $\Omega$ | 5m $Ω$  |  |  |  |  |

| 1.5625μV                   | 78.13μA | 104.2μΑ      | 156.3μΑ      | 312.5μA |  |  |  |  |

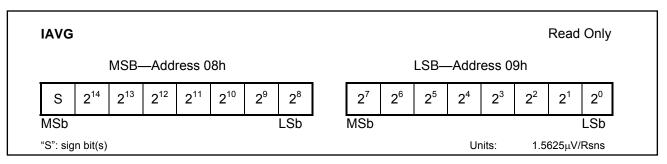

#### AVERAGE CURRENT MEASUREMENT

The Average Current register reports an average current level over the preceding 28 seconds. The register value is updated every 28s in two's complement form, and is the average of the 8 preceding Current register updates. The format of the Average Current register is shown in Figure 7. Charge currents above the maximum register value are reported at the maximum value (7FFFh = +51.2mV). Discharge currents below the minimum register value are reported at the minimum value (8000h = -51.2mV).

Figure 7. Average Current Register Format

#### CURRENT OFFSET CORRECTION

Every 1024th conversion, the ADC measures its input offset to facilitate offset correction. Offset correction occurs approximately once per hour. The resulting correction factor is applied to the subsequent 1023 measurements. During the offset correction conversion, the ADC does not measure the sense resistor signal. A maximum error of 1/1024 in the accumulated current register (ACR) is possible; however, to reduce the error, the current measurement made just prior to the offset conversion is displayed in the current register and is substituted for the dropped current measurement in the current accumulation process. This results in an accumulated current error due to offset correction of less than 1/1024.

#### **CURRENT MEASUREMENT CALIBRATION**

The DS2780's current measurement gain can be adjusted through the RSGAIN register, which is factory-calibrated to meet the data sheet specified accuracy. RSGAIN is user accessible and can be reprogrammed after module or pack manufacture to improve the current measurement accuracy. Adjusting RSGAIN can correct for variation in an external sense resistor's nominal value, and allows the use of low-cost, non-precision current sense resistors. RSGAIN is an 11 bit value stored in 2 bytes of the Parameter EEPROM Memory Block. The RSGAIN value adjusts the gain from 0 to 1.999 in steps of 0.001 (precisely 2<sup>-10</sup>). The user must program RSGAIN cautiously to ensure accurate current measurement. When shipped from the factory, the gain calibration value is stored in two separate locations in the Parameter EEPROM Block, RSGAIN which is reprogrammable and FRSGAIN which is read only. RSGAIN determines the gain used in the current measurement. The read-only FRSGAIN is provided to preserve the factory value only and is not used in the current measurement.

#### SENSE RESISTOR TEMPERATURE COMPENSATION

The DS2780 is capable of temperature compensating the current sense resistor to correct for variation in a sense resistor's value over temperature. The DS2780 is factory programmed with the sense resistor temperature coefficient, RSTC, set to zero, which turns off the temperature compensation function. RSTC is user accessible and can be reprogrammed after module or pack manufacture to improve the current accuracy when using a high temperature coefficient current-sense resistor. RSTC is an 8-bit value stored in the Parameter EEPROM Memory Block. The RSTC value sets the temperature coefficient from 0 to +7782ppm/°C in steps of 30.5ppm/°C. The user must program RSTC cautiously to ensure accurate current measurement.

Temperature compensation adjustments are made when the Temperature register crosses  $0.5^{\circ}$ C boundaries. The temperature compensation is most effective with the resistor placed as close as possible to the VSS terminal. This will optimize thermal coupling of the resistor to the on-chip temperature sensor. The current shunt trace should be run under the DS2780 package, and it should be constructed with a copper PCB trace.

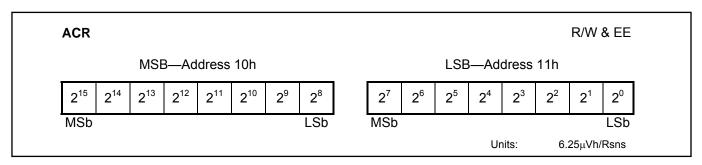

#### **CURRENT ACCUMULATION**

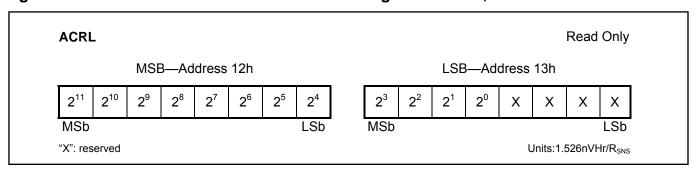

Current measurements are internally summed, or accumulated, at the completion of each conversion period and the results are stored in the Accumulated Current Register (ACR). The accuracy of the ACR is dependent on the

current measurement and the conversion timebase. The ACR has a range of 0 to 409.6mVh with an LSb of  $6.25\mu Vh$ . Additional read-only registers (ACRL) hold fractional results of each accumulation to avoid truncation errors. Accumulation of charge current above the maximum register value is reported at the maximum register value (7FFFh); conversely, accumulation of discharge current below the minimum register value is reported at the minimum value (8000h).

Charge currents (positive Current register values) less than  $100\mu V$  are not accumulated in order to mask the effect of accumulating small positive offset errors over long periods. This limits the minimum charge current, for coulomb-counting purposes, to 5mA for RSNS =  $0.020\Omega$  and 20mA for RSNS =  $0.005\Omega$ .

Read and write access is allowed to the ACR. The ACR must be written MSByte first then LSByte. The write must be completed within 3.515s (one ACR register update period). A write to the ACR forces the ADC to perform an offset correction conversion and update the internal offset correction factor. Current measurement and accumulation begins with the second conversion following a write to the ACR. Writing the ACR clears the fractional values in the ACRL. The format of the ACR is shown in Figure 8, and the ACRL is shown in Figure 9.

To preserve the ACR value in case of power loss, it is backed up to EEPROM. The ACR value is recovered from EEPROM on power-up. See the Memory Map in Table 2 for specific address location and backup frequency.

Figure 8. Accumulated Current Register Format, ACR

Figure 9. Fractional/Low Accumulated Current Register Format, ACRL

| ACR LSb |          |              |              |                    |  |  |  |  |

|---------|----------|--------------|--------------|--------------------|--|--|--|--|

| VSS-    |          | Rs           | SNS          |                    |  |  |  |  |

| VSNS    | 20m $Ω$  | 15m $\Omega$ | 10m $\Omega$ | $5 \text{m}\Omega$ |  |  |  |  |

| 6.25μVh | 312.5μAh | 416.7μAh     | 625μAh       | 1.250mAh           |  |  |  |  |

| ACR RANGE |          |              |              |          |  |  |  |

|-----------|----------|--------------|--------------|----------|--|--|--|

| VSS-      |          | Rs           | SNS          |          |  |  |  |

| VSNS      | 20m $Ω$  | 15m $\Omega$ | 10m $\Omega$ | 5m $Ω$   |  |  |  |

| ±409.6mVh | ±20.48Ah | ±27.30Ah     | ±40.96Ah     | ±81.92Ah |  |  |  |

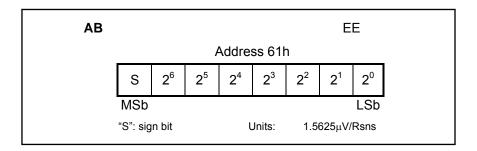

#### **ACCUMULATION BIAS**

The Accumulation Bias register (AB) allows an arbitrary bias to be introduced into the current-accumulation process. The AB can be used to account for currents that do not flow through the sense resistor, estimate currents too small to measure, estimate battery self-discharge or correct for static offset of the DS2780. The AB register allows a user programmed constant positive or negative polarity bias to be included in the current accumulation process. The user-programmed two's compliment value, with bit weighting the same as the current register, is added to the ACR once per current conversion cycle. The AB value is loaded on power-up from EEPROM. The format of the AB register is shown in Figure 10.

Figure 10. Accumulation Bias Register Formats

# **CAPACITY ESTIMATION ALGORITHM**

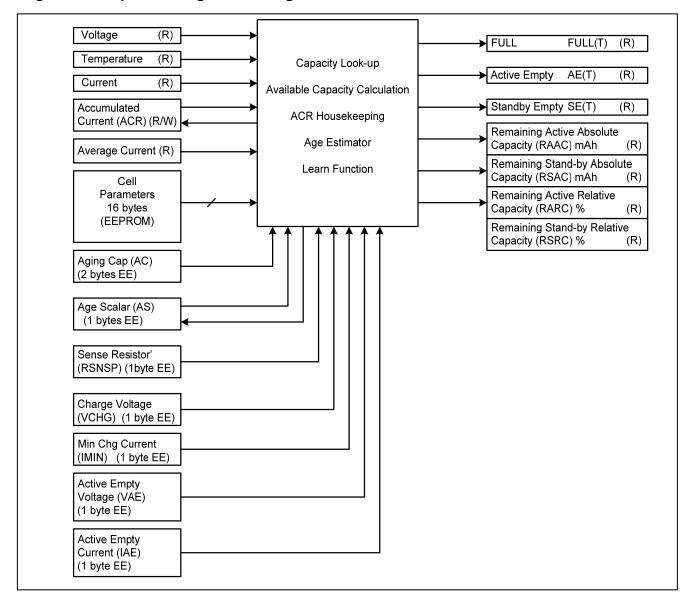

Remaining capacity estimation uses real-time measured values, stored parameters describing the cell characteristics, and application operating limits. The following diagram describes the algorithm inputs and outputs.

Figure 11. Top Level Algorithm Diagram

# **MODELING CELL CHARACTERISTICS**

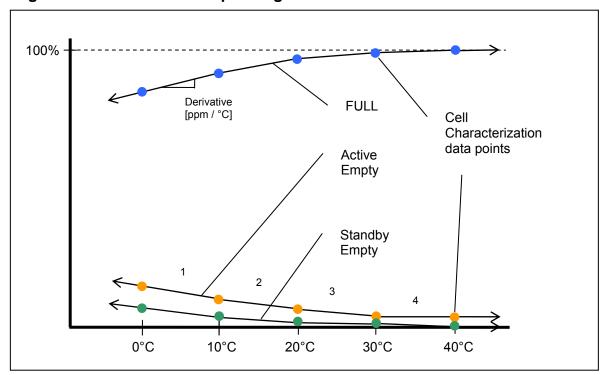

In order to achieve reasonable accuracy in estimating remaining capacity, the cell performance characteristics over temperature, load current, and charge termination point must be considered. Since the behavior of Li-ion cells is non-linear, even over a limited temperature range of 10°C to 35°C, these characteristics must be included in the capacity estimation to achieve a reasonable accuracy. See Applications Note AN131 "Li+ Fuel Gauging with Dallas Semiconductor Devices" for general information on the FuelPack™ method used in the DS2780. To facilitate efficient implementation in hardware, a modified version of the method outlined in AN131 is used to store cell characteristics in the DS2780. Full and empty points are retrieved in a lookup process which re-traces a piece-wise linear model. Three model curves are stored: Full, Active Empty and Standby Empty. Each model curve is constructed with 4 line segments and spans from 0°C to 40°C. Operation outside the 0°C to 40°C model span is supported by the model with minimal loss of accuracy. Above 40°C, the 40°C fixed points are extended with zero slope. This achieves a conservative capacity estimate for temperatures above 40°C. Below 0°C, the model curves are extended using the slope of each 0°C to 10°C segment. If low temperature operation is expected, the 0°C to 10°C slopes can be selected to optimize the model accuracy. A diagram of example battery cell model curves is shown in Figure 12.

Figure 12. Cell Model Example Diagram

**Full:** The Full curve defines how the full point of a given cell depends on temperature for a given charge termination. The application's charge termination method should be used to determine the table values. The DS2780 reconstructs the Full line from the cell characteristic table to determine the Full capacity of the battery at each temperature. Reconstruction occurs in one-degree temperature increments.

Active Empty: The Active Empty curve defines the variation of the Active Empty Point over temperature. The Active Empty Point is defined as the minimum voltage required for system operation at a discharge rate based on a high level load current (one that is sustained during a high power operating mode). This load current is programmed as the Active Empty current (IAE) and should be a 3.5s average to correspond to values read from the Current register. The specified minimum voltage, or Active Empty voltage (VAE), should be a 220ms average to correspond to values read from the Voltage register. The DS2780 reconstructs the Active Empty line from the cell characteristic table to determine the Active Empty capacity of the battery at each temperature. Reconstruction occurs in one-degree temperature increments.

**Standby Empty:** The Standby Empty curve defines the variation of the standby empty point over temperature. The standby empty point is defined as the minimum voltage required for standby operation at a discharge rate dictated by the application standby current. In typical PDA applications, Standby Empty represents the point that the battery can no longer support RAM refresh and thus the standby voltage is set by the RAM voltage supply requirements. In other applications, Standby Empty can represent the point that the battery can no longer support a subset of the full application operation, such as games or organizer functions on a wireless handset. The standby load current and voltage are used for determining the cell characteristics but are not programmed into the DS2780. The DS2780 reconstructs the Standby Empty line from the cell characteristic table to determine the Standby Empty capacity of the battery at each temperature. Reconstruction occurs in one-degree temperature increments.

#### **CELL MODEL CONSTRUCTION**

The model is constructed with all points normalized to the fully charged state at +40°C. All values are stored in the cell parameter EEPROM block. The +40°C Full value is stored in uVhr with an LSB of 6.25uVhr. The +40°C Active Empty value is stored as a percentage of +40°C Full with a resolution of 2<sup>-10</sup>. Standby Empty at +40°C is by definition zero and therefore no storage is required. The slopes (derivatives) of the 4 segments for each model curve are stored in the cell parameter EEPROM block as PPM/°C. Segment endpoints are fixed at 0°C, +10°C, +20°C, +30°C and +40°C. (See Application Note 3584 for more details on how values are stored.) An example of cell model data is shown in Table 1a. Table 1b shows the actual data values stored in memory.

Table 1a. Example Cell Characterization Table (Normalized to +40°C)

| Rated cell capacity           | /: 1000mAh                |       |        |                           |       |       |

|-------------------------------|---------------------------|-------|--------|---------------------------|-------|-------|

| Charge Voltage: 4.            | 2V                        |       | Termi  | Terminating Current: 50mA |       |       |

| Active Empty (V):             | 3.0V                      |       | Active | Empty (I): 3              | 300mA |       |

| Sense Resistor: $0.020\Omega$ |                           |       |        |                           |       |       |

|                               | +40°C<br>Nominal<br>[mAh] | 0°C   | +10°C  | +20°C                     | +30°C | +40°C |

| Full                          | 1051                      | 0.927 | 0.951  | 0.974                     | 0.991 | 1.0   |

| Active Empty                  |                           | 0.051 | 0.040  | 0.022                     | 0.012 | 0.008 |

| Standby Empty                 |                           | 0.013 | 0.0067 | 0.0038                    | 0.001 | 0     |

Table 1b. Example Cell Characterization Table (Actual data values stored in EEPROM)

| Rated cell capacity: 0C80h |                           |     |       |                          |       |       |

|----------------------------|---------------------------|-----|-------|--------------------------|-------|-------|

| Charge Voltage: D          | 7h                        |     | Term  | Terminating Current: 14h |       |       |

| Active Empty (V): 9        | 9Ah                       |     | Activ | Active Empty (I): 1Eh    |       |       |

| Sense Resistor: 32         | 2h                        |     |       |                          |       |       |

|                            | +40°C<br>Nominal<br>[mAh] | 0°C | +10°C | +20°C                    | +30°C | +40°C |

| Full                       | 0D32h                     | 27h | 26h   | 1Ch                      | 0Fh   | 0D32h |

| Active Empty               |                           | 12h | 1Eh   | 10h                      | 07h   | 08h   |

| Standby Empty              |                           | 0Ah | 05h   | 05h                      | 02h   |       |

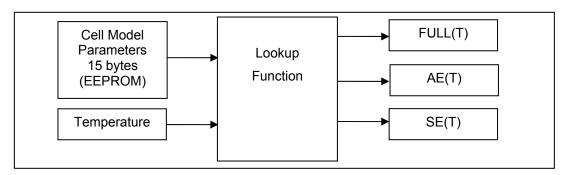

Figure 13. Lookup Function Diagram

#### **APPLICATION PARAMETERS**

In addition to cell model characteristics, several application parameters are needed to detect the full and empty points, as well as calculate results in mAh units.

Sense Resistor Prime (RSNSP[1/ $\Omega$ ]): RSNSP stores the value of the sense resistor for use in computing the absolute capacity results. The resistance is stored as a 1-byte conductance value with units of mhos (1/ $\Omega$ ). RSNSP supports resistor values of 1 $\Omega$  to 3.922m $\Omega$ . RSNSP is located in the Parameter EEPROM block.

RSNSP = 1/RSNS (units of mhos;  $1/\Omega$ )

**Charge Voltage (VCHG):** VCHG stores the charge voltage threshold used to detect a fully charged state. The voltage is stored as a 1-byte value with units of 19.52mV and can range from 0V to 4.978V. VCHG should be set marginally less than the cell voltage at the end of the charge cycle to ensure reliable charge termination detection. VCHG is located in the Parameter EEPROM block.

**Minimum Charge Current (IMIN):** IMIN stores the charge current threshold used to detect a fully charged state. It is stored as a 1-byte value with units of  $50\mu\text{V}$  (IMIN \* RSNS) and can range from 0 to 12.75mV. Assuming RSNS =  $20m\Omega$ , IMIN can be programmed from 0mA to 637.5mA in 2.5mA steps. IMIN should be set marginally greater than the charge current at the end of the charge cycle to ensure reliable charge termination detection. IMIN is located in the Parameter EEPROM block.

**Active Empty Voltage (VAE):** VAE stores the voltage threshold used to detect the Active Empty Point. The value is stored in 1-byte with units of 19.52mV and can range from 0V to 4.978V. VAE is located in the Parameter EEPROM block. See the *Cell Characteristics* section for more information.

Active Empty Current (IAE): IAE stores the discharge current threshold used to detect the Active Empty Point. The unsigned value represents the magnitude of the discharge current and is stored in 1-byte with units of  $200\mu$ V. It can range from 0 to 51.2mV. Assuming RSNS =  $20m\Omega$ , IAE can be programmed from 0mA to 2550mA in 10mA steps. IAE is located in the Parameter EEPROM block. See the *Cell Characteristics* section for more information.

Aging Capacity (AC): AC stores the rated cell capacity which is used to estimate the decrease in battery capacity that occurs during normal use. The value is stored in 2-bytes in the same units as the ACR ( $6.25\mu Vh$ ). When set to the manufacturer's rated cell capacity the Aging Estimation rate is approximately 2.4% per 100 cycles of equivalent full capacity discharges. Partial discharge cycles are added to form equivalent full capacity discharges. The default aging estimation results in 88% capacity after 500 equivalent cycles. The Aging Estimation rate can be adjusted by setting the AC to a value other than the cell manufacturer's rating. Setting AC to a lower value, accelerates the Aging Estimation rate. Setting the AC to a higher value, retards the Aging Estimation rate. The AC is located in the Parameter EEPROM block.

Age Scalar (AS): AS adjusts the cell capacity estimation results downward to compensate for aging. The AS is a 1-byte value that has a range of 49.2% to 100%. The lsb is weighted at 0.78% (precisely 2<sup>-7</sup>). A value of 100% (128 decimal or 80h) represents an un-aged battery. A value of 95% is recommended as the starting AS value at the time of pack manufacture to allow the learning of a larger capacity on batteries that have an initial capacity greater than the rated cell capacity programmed in the cell characteristic table. The AS is modified by the Aging Estimation introduced under Aging Capacity and by the Learn function. The host system has read and write access to the AS, however caution should be exercised when writing it to ensure that the cumulative aging estimate is not over written with an incorrect value. Usually, writing the AS by the host is not necessary because it is automatically saved to EEPROM on a periodic basis by the DS2780. (See the *Memory* section for details.) The AS value stored in EEPROM is recalled on power-up.

#### CAPACITY ESTIMATION UTILITY FUNCTIONS

#### **Aging Estimation**

As discussed above, the AS register value is adjusted occasionally based on cumulative discharge. As the ACR register decrements during each discharge cycle, an internal counter is incremented until equal to 32 times the AC. The AS is then decremented by one, resulting in a decrease in the scaled full battery capacity of 0.78% (approximately 2.4% per 100 cycles). Refer to the AC register description above for recommendations on customizing the age estimation rate.

#### **Learn Function**

Since Li+ cells exhibit charge efficiencies near unity, the charge delivered to a Li+ cell from a known empty point to a known full point is a dependable measure of the cell capacity. A continuous charge from empty to full results in a

"learn cycle". First, the Active Empty Point must be detected. The Learn Flag (*LEARNF*) is set at this point. Then, once charging starts, the charge must continue uninterrupted until the battery is charged to full. Upon detecting full, *LEARNF* is cleared, the Charge to Full (*CHGTF*) flag is set and the Age Scalar (AS) is adjusted according to the learned capacity of the cell.

#### **ACR Housekeeping**

The ACR value is adjusted occasionally to maintain the coulomb count within the model curve boundaries. When the battery is charged to full (*CHGTF* set), the ACR is set equal to the age scaled full lookup value at the present temperature. If a learn cycle is in progress, correction of the ACR value occurs after the age scalar (AS) is updated.

When an empty condition is detected (*AEF* or *LEARNF* set), the ACR adjustment is conditional. If *AEF* is set and *LEARNF* is not, then the Active Empty Point was not detected and the battery is likely below the Active Empty capacity of the model. The ACR is set to the Active Empty model value only if it is greater than the Active Empty model value. If *LEARNF* is set, then the battery is at the Active Empty Point and the ACR is set to the Active Empty model value.

#### **Full Detect**

Full detection occurs when the Voltage (VOLT) readings remain above the VCHG (Charge Voltage) threshold for the duration of two Average Current (IAVG) readings, where both IAVG readings are below IMIN (Terminating Current). The two consecutive IAVG readings must also be positive and non-zero. This ensures that removing the battery from the charger does not result in a false detection of full. Full Detect sets the Charge to Full (*CHGTF*) bit in the Status register.

#### **Active Empty Point Detect**

Active Empty Point detection occurs when the Voltage register drops below the VAE threshold and the two previous Current readings are above IAE. This captures the event of the battery reaching the Active Empty Point. Note that the two previous Current readings must be negative and greater in magnitude than IAE, that is, a larger discharge current than specified by the IAE threshold. Qualifying the Voltage level with the discharge rate ensures that the Active Empty Point is not detected at loads much lighter than those used to construct the model. Also, the Active Empty Point must not be detected when a deep discharge at a very light load is followed by a load greater than IAE. Either case would cause a learn cycle on the following charge to include part of the Standby capacity in the measurement of the Active capacity. Active Empty Point detection sets the Learn Flag (LEARNF) bit in the Status register. **DO NOT** confuse the Active Empty Point with the Active Empty Flag. The Active Empty Flag is set only when the VAE threshold is passed.

# **RESULT REGISTERS**

The DS2780 processes measurement and cell characteristics on a 440ms interval and yields seven result registers. The result registers are sufficient for direct display to the user in most applications. The host system can produce customized values for system use, or user display by combining measurement, result and User EEPROM values.

**FULL(T) []:** The Full capacity of the battery at the present temperature is reported normalized to the 40°C Full value. This 15-bit value reflects the cell model Full value at the given temperature. FULL(T) reports values between 100% and 50% with a resolution of 61ppm (precisely 2<sup>-14</sup>). The register is clamped to a maximum value of 100% even though the format permits values greater than 100%,.

**Active Empty, AE(T) [ ]:** The Active Empty capacity of the battery at the present temperature is reported normalized to the  $40^{\circ}$ C Full value. This 13-bit value reflects the cell model Active Empty Point at the given temperature. AE(T) reports values between 0% and 49.8% with a resolution of 61ppm (precisely  $2^{-14}$ ).

**Standby Empty, SE(T) []:** The Standby Empty capacity of the battery at the present temperature is reported normalized to the 40°C Full value. This 13-bit value reflects the cell model Standby Empty value at the current temperature. SE(T) reports values between 0% and 49.8% with a resolution of 61ppm (precisely 2<sup>-14</sup>).

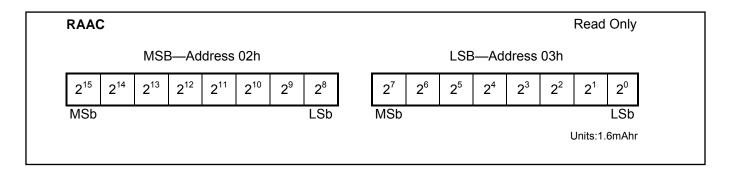

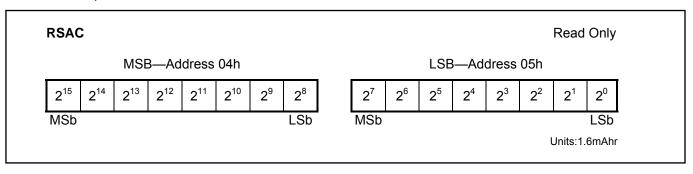

Remaining Active Absolute Capacity (RAAC) [mAh] – RAAC reports the remaining battery capacity under the current temperature conditions at the Active Empty discharge rate (IAE) to the Active Empty Point in absolute units of milli-amp-hours. RAAC is 16 bits.

Remaining Standby Absolute Capacity (RSAC) [mAh] – RSAC reports the remaining battery capacity under the current temperature conditions at the Standby Empty discharge rate (ISE) to the Standby Empty point in absolute units of milli-amp-hours. RSAC is 16 bits.

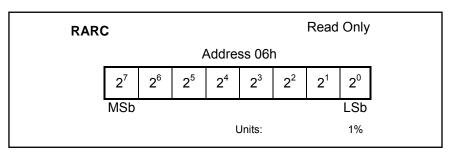

Remaining Active Relative Capacity (RARC) [%] – RARC reports the remaining battery capacity under the current temperature conditions at the Active Empty discharge rate (IAE) to the Active Empty Point in relative units of percent. RARC is 8 bits.

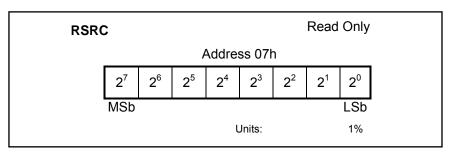

Remaining Standby Relative Capacity (RSRC) [%] – RSRC reports the remaining battery capacity under the current temperature conditions at the Standby Empty discharge rate (ISE) to the Standby Empty point in relative units of percent. RSRC is 8 bits.

#### **Calculation of Results**

#### STATUS REGISTER

The STATUS register contains bits which report the device status. The bits can be set internally by the DS2780. The CHGTF, AEF, SEF, LEARNF and VER bits are read only bits which can be cleared by hardware. The UVF and PORF bits can only be cleared via the 1-Wire interface.

Figure 14. Status Register Format

| Address  | 01h |                | Bit Definition                                                                                                                                                                                                                                                                                                     |

|----------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Field    | Bit | Format         | Allowable Values                                                                                                                                                                                                                                                                                                   |

| CHGTF    | 7   | Read Only      | Charge Termination Flag Set to 1 when: ( VOLT > VCHG ) AND ( 0 < IAVG < IMIN ) continuously for a period between two IAVG register updates ( 28s to 56s ). Cleared to 0 when: RARC < 90%                                                                                                                           |

| AEF      | 6   | Read Only      | Active Empty Flag Set to 1 when: VOLT < VAE Cleared to 0 when: RARC > 5%                                                                                                                                                                                                                                           |

| SEF      | 5   | Read Only      | Standby Empty Flag Set to 1 when: RSRC < 10% Cleared to 0 when: RSRC > 15%                                                                                                                                                                                                                                         |

| LEARNF   | 4   | Read Only      | Learn Flag – When set to 1, a charge cycle can be used to learn battery capacity. Set to 1 when: ( VOLT falls from above VAE to below VAE ) AND ( CURRENT > IAE ) Cleared to 0 when: ( CHGTF = 1 ) OR ( CURRENT < +100 $\mu$ V/R ) OR ( ACR = 0 **) OR ( ACR written or recalled from EEPROM) OR ( SLEEP Entered ) |

| Reserved | 3   | Read Only      | Undefined                                                                                                                                                                                                                                                                                                          |

| UVF      | 2   | Read / Write * | Under-Voltage Flag Set to 1 when: VOLT < V <sub>SLEEP</sub> Cleared to 0 by: User                                                                                                                                                                                                                                  |

| PORF     | 1   | Read / Write * | Power-On Reset Flag – Useful for reset detection, see text below. Set to 1 upon Power-Up by hardware. Cleared to 0 by: User                                                                                                                                                                                        |

| Reserved | 0   | Read Only      | Undefined                                                                                                                                                                                                                                                                                                          |

<sup>\* -</sup> This bit can be set by the DS2780, and may only be cleared via the 1-Wire interface.

<sup>\*\* -</sup> LEARNF is only cleared if ACR reaches 0 after VOLT < VAE.

# **CONTROL REGISTER**

All CONTROL register bits are read and write accessible. The CONTROL register is recalled from Parameter EEPROM memory at power-up. Register bit values can be modified in shadow RAM after power-up. Shadow RAM values can be saved as the power up default values by using the Copy Data command.

Figure 15. Control Register Format

| Address  | 60h |            | Bit Definition                                                                      |

|----------|-----|------------|-------------------------------------------------------------------------------------|

| Field    | Bit | Format     | Allowable Values                                                                    |

| Reserved | 7   |            | Undefined                                                                           |

| UVEN     | 6   | Read/Write | Under Voltage SLEEP Enable                                                          |

|          |     |            | 0: Disables transition to SLEEP mode based on VIN voltage                           |

|          |     |            | 1: Enables transition to SLEEP mode if,                                             |

|          |     |            | VIN < V <sub>SLEEP</sub> AND DQ stable at either logic level for t <sub>SLEEP</sub> |

| PMOD     | 5   | Read/Write | Power Mode Enable                                                                   |

|          |     |            | 0: Disables transition to SLEEP mode based on DQ logic state                        |

|          |     |            | 1: Enables transition to SLEEP mode if DQ at a logic low for t <sub>SLEEP</sub>     |

| RNAOP    | 4   | Read/Write | Read Net Address Opcode                                                             |

|          |     |            | 0: Read Net Address Command = 33h                                                   |

|          |     |            | 1: Read Net Address Command = 39h                                                   |

| Reserved | 0:3 |            | Undefined                                                                           |

# SPECIAL FEATURE REGISTER

All Special Feature Register bits are read and write accessible, with default values specified in each bit definition.

Figure 16. Special Feature Register Format

| Address  | 15h |            | Bit Definition                                                                            |

|----------|-----|------------|-------------------------------------------------------------------------------------------|

| Field    | Bit | Format     | Allowable Values                                                                          |

| Reserved | 1:7 |            | Undefined                                                                                 |

| PIOSC    | 0   | Read/Write | PIO Sense and Control                                                                     |

|          |     |            | Read values                                                                               |

|          |     |            | 0: PIO pin ≤ Vil                                                                          |

|          |     |            | 1: PIO pin ≥ Vih                                                                          |

|          |     |            | Write values                                                                              |

|          |     |            | 0: Activates PIO pin open-drain output driver, forcing the PIO pin low                    |

|          |     |            | 1: Disables the output driver, allowing the PIO pin to be pulled high or used as an input |

|          |     |            | Power-up and SLEEP mode default: 1 (PIO pin is hi-Z)                                      |

|          |     |            | Note: PIO pin has weak pulldown                                                           |

#### **EEPROM REGISTER**

The EEPROM register provides access control of the EEPROM blocks. EEPROM blocks can be locked to prevent alteration of data within the block. Locking a block disables write access to it. Once a block is locked, it cannot be unlocked. Read access to EEPROM blocks is unaffected by the lock/unlock status.

Figure 17. EEPROM REGISTER FORMAT

| Address  | 1Fh |            | Bit Definition                                                                                                              |

|----------|-----|------------|-----------------------------------------------------------------------------------------------------------------------------|

| Field    | Bit | Format     | Allowable Values                                                                                                            |

| EEC      | 7   | Read Only  | EEPROM Copy Flag                                                                                                            |

|          |     |            | Set to 1 when: Copy Data command executed                                                                                   |

|          |     |            | Cleared to 0 when: Copy Data command completes                                                                              |

|          |     |            | Note: While EEC = 1, writes to EEPROM addresses are ignored                                                                 |

| 10016    |     |            | Power-up default: 0                                                                                                         |

| LOCK     | 6   | Read /     | EEPROM Lock Enable                                                                                                          |

|          |     | Write to 1 | Host write to 1: Enables the Lock command. Host must issue Lock command as next command after writing Lock Enable bit to 1. |

|          |     |            | Cleared to 0 when: Lock command completes or when the Lock                                                                  |

|          |     |            | command is not issued immediately following the setting of the Lock Enable bit.                                             |

|          |     |            | Power-up default: 0                                                                                                         |

| Reserved | 2:6 |            | Undefined                                                                                                                   |

| BL1      | 1   | Read Only  | EEPROM Block 1 Lock Flag (Parameter EEPROM 60h – 7Fh)                                                                       |

|          |     |            | 0: EEPROM is not locked                                                                                                     |

|          |     |            | 1: EEPROM block is locked                                                                                                   |

|          |     |            | Factory default: 0                                                                                                          |

| BL0      | 0   | Read Only  | EEPROM Block 0 Lock Flag (User EEPROM 20h – 2Fh)                                                                            |

|          |     |            | 0: EEPROM is not locked                                                                                                     |

|          |     |            | 1: EEPROM block is locked                                                                                                   |

|          |     |            | Factory default: 0                                                                                                          |

#### **MEMORY**

The DS2780 has a 256 byte linear memory space with registers for instrumentation, status, and control, as well as EEPROM memory blocks to store parameters and user information. Byte addresses designated as "Reserved" return undefined data when read. Reserved bytes should not be written. Several byte registers are paired into two-byte registers in order to store 16-bit values. The most significant byte (MSB) of the 16 bit value is located at a even address and the least significant byte (LSB) is located at the next address (odd) byte. When the MSB of a two-byte register is read, the MSB and LSB are latched simultaneously and held for the duration of the read data command to prevent updates to the LSB during the read. This ensures synchronization between the two register bytes. For consistent results, always read the MSB and the LSB of a two-byte register during the same read data command sequence.

EEPROM memory consists of the non-volatile EEPROM cells overlaid with volatile shadow RAM. The Read Data and Write Data commands allow the 1-Wire interface to directly access the shadow RAM only. The Copy Data and Recall Data function commands transfer data between the shadow RAM and the EEPROM cells. In order to modify the data stored in the EEPROM cells, data must be written to the shadow RAM and then copied to the EEPROM. In order to verify the data stored in the EEPROM cells, the EEPROM data must be recalled to the shadow RAM and then read from the shadow RAM.

#### **USER EEPROM**

A 16 byte User EEPROM memory (block 0, addresses 20h - 2Fh) provides non-volatile memory that is uncommitted to other DS2780 functions. Accessing the User EEPROM block does not affect the operation of the DS2780. User EEPROM is lockable, and once locked, write access is not allowed. The battery pack or host system manufacturer can program lot codes, date codes and other manufacturing, warranty, or diagnostic information and then lock it to safeguard the data. User EEPROM can also store parameters for charging to support different size batteries in a host device as well as auxiliary model data such as time to full charge estimation parameters.

#### PARAMETER EEPROM

Model data for the cells, as well as application operating parameters are stored in the Parameter EEPROM (block 1, addresses 60h - 7Fh). The **ACR** (MSB and LSB) and **AS** registers are automatically saved to EEPROM when

the **RARC** result crosses 4% boundaries. This allows the DS2780 to be located outside the protection FETs. In this manner, if a protection device is triggered, the DS2780 cannot lose more that 4% of charge or discharge data.

**Table 2. MEMORY MAP**

| ADDRESS (HEX) | DESCRIPTION                                    | READ/WRITE |

|---------------|------------------------------------------------|------------|

| 00            | Reserved                                       | R          |

| 01            | STATUS - Status Register                       | R/W        |

| 02            | RAAC - Remaining Active Absolute Capacity MSB  | R          |

| 03            | RAAC - Remaining Active Absolute Capacity LSB  | R          |

| 04            | RSAC - Remaining Standby Absolute Capacity MSB | R          |

| 05            | RSAC - Remaining Standby Absolute Capacity LSB | R          |

| 06            | RARC - Remaining Active Relative Capacity      | R          |

| 07            | RSRC - Remaining Standby Relative Capacity     | R          |

| 08            | IAVG - Average Current Register MSB            | R          |

| 09            | IAVG - Average Current Register LSB            | R          |

| 0A            | TEMP - Temperature Register MSB                | R          |

| 0B            | TEMP - Temperature Register LSB                | R          |

| 0C            | VOLT - Voltage Register MSB                    | R          |

| 0D            | VOLT - Voltage Register LSB                    | R          |

| 0E            | CURRENT - Current Register MSB                 | R          |

| 0F            | CURRENT - Current Register LSB                 | R          |

| 10            | ACR - Accumulated Current Register MSB         | R/W*       |

| 11            | ACR - Accumulated Current Register LSB         | R/W *      |

| 12            | ACRL – Low Accumulated Current Register MSB    | R          |

| 13            | ACRL – Low Accumulated Current Register LSB    | R          |

| 14            | AS - Age Scalar                                | R/W *      |

| 15            | SFR - Special Feature Register                 | R/W        |

| 16            | FULL - Full Capacity MSB                       | R          |

| 17            | FULL - Full Capacity LSB                       | R          |

| 18            | AE - Active Empty MSB                          | R          |

| 19            | AE - Active Empty LSB                          | R          |

| 1A            | SE - Standby Empty MSB                         | R          |

| 1B            | SE - Standby Empty LSB                         | R          |

| 1C to 1E      | Reserved                                       | _          |

| 1F            | EEPROM - EEPROM Register                       | R/W        |

| 20 to 2F      | User EEPROM, Lockable, Block 0                 | R/W        |

| 30 to 5F      | Reserved                                       | _          |

| 60 to 7F      | Parameter EEPROM, Lockable, Block 1            | R/W        |

| 80 to FF      | Reserved                                       | _          |

<sup>\*</sup> Register value is automatically saved to EEPROM during ACTIVE mode operation and recalled from EEPROM on power up.

Table 3. PARAMETER EEPROM MEMORY BLOCK 1

| ADDRESS<br>(HEX) | DESCRIPTION                   | ADDRESS<br>(HEX) | DESCRIPTION                        |

|------------------|-------------------------------|------------------|------------------------------------|

| 60               | CONTROL - Control Register    | 70               | AE 3040 Slope                      |

| 61               | AB - Accumulation Bias        | 71               | AE 2030 Slope                      |

| 62               | AC - Aging Capacity MSB       | 72               | AE 1020 Slope                      |

| 63               | AC - Aging Capacity LSB       | 73               | AE 0010 Slope                      |

| 64               | VCHG - Charge Voltage         | 74               | SE 3040 Slope                      |

| 65               | IMIN - Minimum Charge Current | 75               | SE 2030 Slope                      |

| 66               | VAE - Active Empty Voltage    | 76               | SE 1020 Slope                      |

| 67               | IAE - Active Empty Current    | 77               | SE 0010 Slope                      |

| 68               | Active Empty 40               | 78               | RSGAIN - Sense Resistor Gain MSB   |

| 69               | RSNSP - Sense Resistor Prime  | 79               | RSGAIN - Sense Resistor Gain LSB   |

| 6A               | Full 40 MSB                   | 7A               | RSTC - Sense Resistor Temp. Coeff. |

| 6B               | Full 40 LSB                   | 7B               | FRSGAIN - Factory Gain MSB         |

| 6C               | Full 3040 Slope               | 7C               | FRSGAIN - Factory Gain LSB         |

| 6D               | Full 2030 Slope               | 7D               | Reserved                           |

| 6E               | Full 1020 Slope               | 7E               | Reserved                           |

| 6F               | Full 0010 Slope               | 7F               | Reserved                           |

#### 1-WIRE BUS SYSTEM

The 1-Wire bus is a system that has a single bus master and one or more slaves. A multidrop bus is a 1-Wire bus with multiple slaves. A single-drop bus has only one slave device. In all instances, the DS2780 is a slave device. The bus master is typically a microprocessor in the host system. The discussion of this bus system consists of four topics: 64-bit net address, hardware configuration, transaction sequence, and 1-Wire signaling.

#### **64-BIT NET ADDRESS**

Each DS2780 has a unique, factory-programmed 1-Wire net address that is 64 bits in length. The first eight bits are the 1-Wire family code (**32h** for DS2780). The next 48 bits are a unique serial number. The last eight bits are a cyclic redundancy check (CRC) of the first 56 bits (see Figure 18). The 64-bit net address and the 1-Wire I/O circuitry built into the device enable the DS2780 to communicate through the 1-Wire protocol detailed in the *1-Wire Bus System* section of this data sheet.

Figure 18. 1-Wire Net Address Format

| 8-BIT CRC | 48-BIT SERIAL NUMBER  | 8-BIT FAMILY        |

|-----------|-----------------------|---------------------|

| O-BIT CKC | 40-BIT SERIAL NOWIDER | CODE ( <b>32h</b> ) |

| MSb       |                       | LSb                 |

#### **CRC GENERATION**

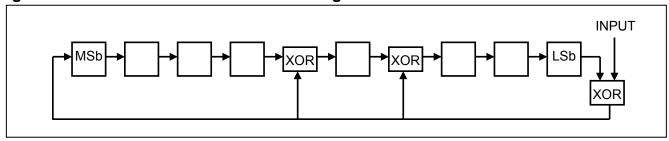

The DS2780 has an 8-bit CRC stored in the most significant byte of its 1-Wire net address. To ensure error-free transmission of the address, the host system can compute a CRC value from the first 56 bits of the address and compare it to the CRC from the DS2780. The host system is responsible for verifying the CRC value and taking action as a result. The DS2780 does not compare CRC values and does not prevent a command sequence from proceeding as a result of a CRC mismatch. Proper use of the CRC can result in a communication channel with a very high level of integrity.

The CRC can be generated by the host using a circuit consisting of a shift register and XOR gates as shown in Figure 19, or it can be generated in software. Additional information about the Dallas 1-Wire CRC is available in

Application Note 27, Understanding and Using Cyclic Redundancy Checks with Dallas Semiconductor Touch Memory Products. (This application note can be found on the Maxim/Dallas Semiconductor website at www.maxim-ic.com.)

In the circuit in Figure 19, the shift register bits are initialized to 0. Then, starting with the least significant bit of the family code, one bit at a time is shifted in. After the 8th bit of the family code has been entered, then the serial number is entered. After the 48th bit of the serial number has been entered, the shift register contains the CRC value.

Figure 19. 1-Wire CRC Generation Block Diagram

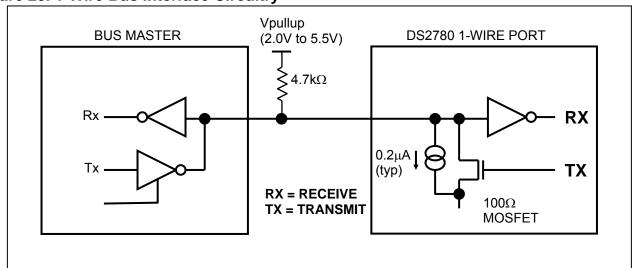

#### HARDWARE CONFIGURATION

Because the 1-Wire bus has only a single line, it is important that each device on the bus be able to drive it at the appropriate time. To facilitate this, each device attached to the 1-Wire bus must connect to the bus with open-drain or tri-state output drivers. The DS2780 uses an open-drain output driver as part of the bidirectional interface circuitry shown in Figure 20. If a bidirectional pin is not available on the bus master, separate output and input pins can be connected together.

The 1-Wire bus must have a pullup resistor at the bus-master end of the bus. For short line lengths, the value of this resistor should be approximately  $5k\Omega$ . The idle state for the 1-Wire bus is high. If, for any reason, a bus transaction must be suspended, the bus must be left in the idle state to properly resume the transaction later. If the bus is left low for more than  $120\mu s$  ( $16\mu s$  for overdrive speed), slave devices on the bus begin to interpret the low period as a reset pulse, effectively terminating the transaction.

The DS2780 can operate in two communication speed modes, standard and overdrive. The speed mode is determined by the input logic level of the OVD pin; a logic 0 selects standard speed and a logic 1 selects overdrive speed. The OVD pin must be at a stable logic level of 0 or 1 before initializing a transaction with a reset pulse. All 1-Wire devices on a multinode bus must operate at the same communication speed for proper operation. 1-Wire timing for both standard and overdrive speeds are listed in the *Electrical Characteristics: 1-Wire Interface* tables.

Figure 20. 1-Wire Bus Interface Circuitry

#### TRANSACTION SEQUENCE

The protocol for accessing the DS2780 through the 1-Wire port is as follows:

- Initialization

- Net Address Command

- Function Command

- Transaction/Data

The sections that follow describe each of these steps in detail.

All transactions of the 1-Wire bus begin with an initialization sequence consisting of a reset pulse transmitted by the bus master followed by a presence pulse simultaneously transmitted by the DS2780 and any other slaves on the bus. The presence pulse tells the bus master that one or more devices are on the bus and ready to operate. For more details, see the *1-Wire Signaling* section.

#### **NET ADDRESS COMMANDS**

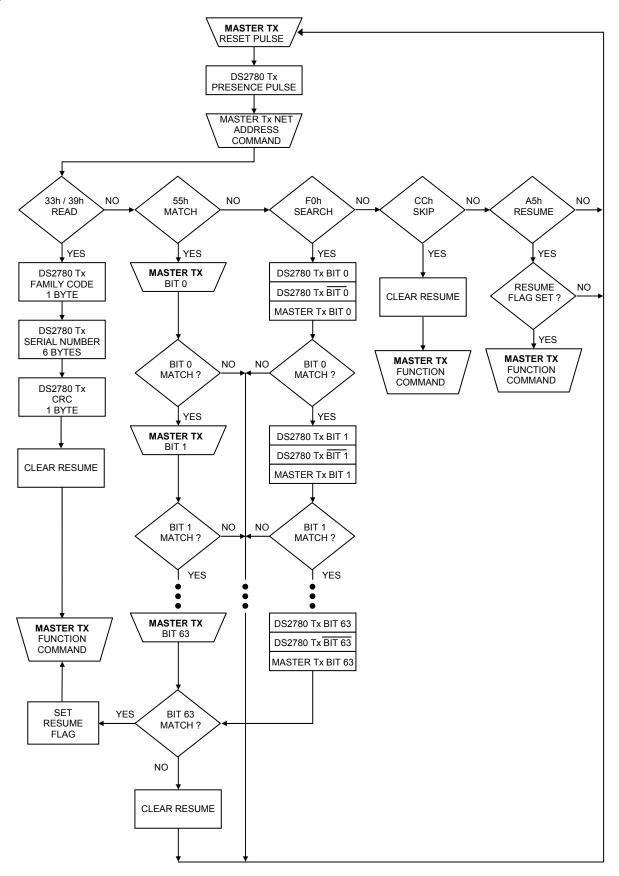

Once the bus master has detected the presence of one or more slaves, it can issue one of the net address commands described in the following paragraphs. The name of each ROM command is followed by the 8-bit opcode for that command in square brackets. Figure 21 presents a transaction flowchart of the net address commands.

**Read Net Address [33h or 39h].** This command allows the bus master to read the DS2780's 1-Wire net address. This command can only be used if there is a single slave on the bus. If more than one slave is present, a data collision occurs when all slaves try to transmit at the same time (open drain produces a wired-AND result). The RNAOP bit in the status register selects the opcode for this command, with RNAOP = 0 indicating 33h, and RNAOP = 1 indicating 39h.

**Match Net Address [55h].** This command allows the bus master to specifically address one DS2780 on the 1-Wire bus. Only the addressed DS2780 responds to any subsequent function command. All other slave devices ignore the function command and wait for a reset pulse. This command can be used with one or more slave devices on the bus.

**Skip Net Address [CCh].** This command saves time when there is only one DS2780 on the bus by allowing the bus master to issue a function command without specifying the address of the slave. If more than one slave device is present on the bus, a subsequent function command can cause a data collision when all slaves transmit data at the same time.

**Search Net Address [F0h].** This command allows the bus master to use a process of elimination to identify the 1-Wire net addresses of all slave devices on the bus. The search process involves the repetition of a simple three-step routine: read a bit, read the complement of the bit, then write the desired value of that bit. The bus master performs this simple three-step routine on each bit location of the net address. After one complete pass through all 64 bits, the bus master knows the address of one device. The remaining devices can then be identified on additional iterations of the process. See Chapter 5 of the *Book of DS19xx iButton® Standards* for a comprehensive discussion of a net address search, including an actual example. (This publication can be found on the Maxim/Dallas Semiconductor website at www.maxim-ic.com.)

Resume [A5h]. This command increases data throughput in multidrop environments where the DS2780 needs to be accessed several times. Resume is similar to the Skip Net Address command in that the 64-bit net address does not have to be transmitted each time the DS2780 is accessed. After successfully executing a Match Net Address command or Search Net Address command, an internal flag is set in the DS2780. When the flag is set, the DS2780 can be repeatedly accessed through the Resume command function. Accessing another device on the bus clears the flag, thus preventing two or more devices from simultaneously responding to the Resume command function.

iButton is a registered trademark of Maxim Integrated Products, Inc.

#### **FUNCTION COMMANDS**

After successfully completing one of the net address commands, the bus master can access the features of the DS2780 with any of the function commands described in the following paragraphs. The name of each function is followed by the 8-bit opcode for that command in square brackets. The function commands are summarized in Table 4.

Read Data [69h, XX]. This command reads data from the DS2780 starting at memory address XX. The LSb of the data in address XX is available to be read immediately after the MSb of the address has been entered. Because the address is automatically incremented after the MSb of each byte is received, the LSb of the data at address XX + 1 is available to be read immediately after the MSb of the data at address XX. If the bus master continues to read beyond address FFh, data is read starting at memory address 00 and the address is automatically incremented until a reset pulse occurs. Addresses labeled "Reserved" in the memory map contain undefined data values. The read data command can be terminated by the bus master with a reset pulse at any bit boundary. Reads from EEPROM block addresses return the data in the shadow RAM. A Recall Data command is required to transfer data from the EEPROM to the shadow. See the *Memory* section for more details.