## **High Performance Audio Hub CODEC**

## DESCRIPTION

The WM8998<sup>[1]</sup> is a highly-integrated low-power audio hub CODEC for smartphones, tablets and other portable audio devices. It is optimised for the needs of multimedia devices using SLIMbus application processors.

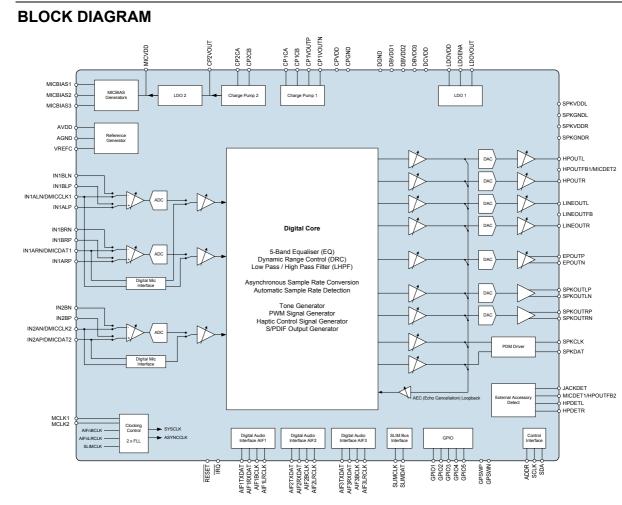

The WM8998 digital core combines fixed-function signal processing blocks with a fully-flexible, all-digital audio mixing and routing engine, for extensive use-case flexibility. Signal processing blocks include filters, EQ, dynamics processors and sample rate converters.

A SLIMbus interface supports multi-channel audio paths and host control register access. Multiple sample rates are supported concurrently via the SLIMbus interface. Three further digital audio interfaces are provided, each supporting a wide range of standard audio sample rates and serial interface formats. Automatic sample rate detection enables seamless wideband/narrowband voice call handover.

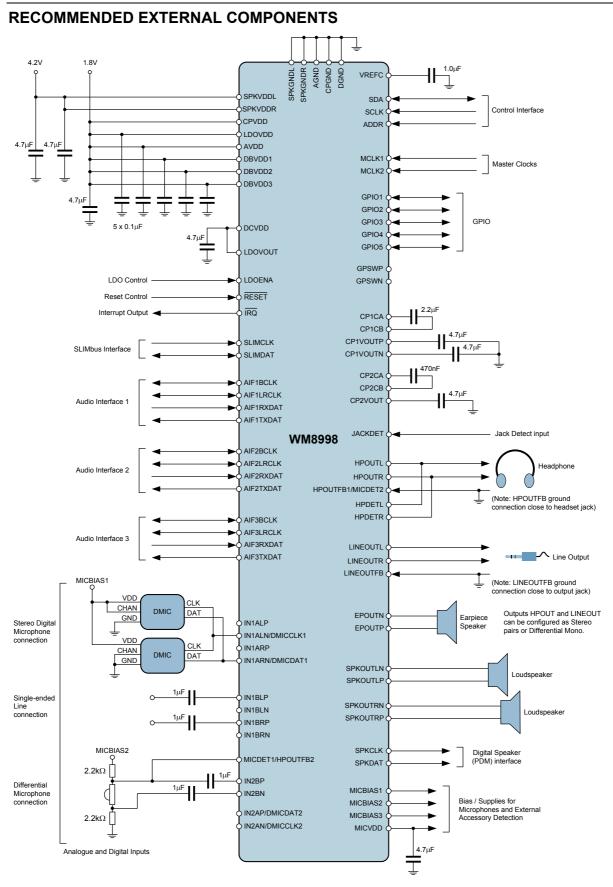

The stereo headphone driver provides ground-referenced outputs, with noise levels as low as  $1\mu V_{\text{RMS}}$  for hi-fi quality line or headphone output. The CODEC also features a stereo line output, stereo 2W Class-D speaker outputs, a dedicated BTL earpiece output, PDM for external speaker amplifiers, and an IEC-60958-3 compatible S/PDIF transmitter. A signal generator for controlling haptics devices is included; vibe actuators can connect directly to the Class-D speaker output, or via an external driver on the PDM output interface. All inputs, outputs and system interfaces can function concurrently.

The WM8998 supports up to six analogue mic/line inputs, and up to three PDM digital inputs. The input multiplexers support up to three signal paths. Microphone activity detection with interrupt is available. A smart accessory interface supports most standard 3.5mm accessories. Impedance sensing and measurement is provided for external accessory and push-button detection.

The WM8998 power, clocking and output driver architectures are all designed to maximise battery life in voice, music and standby modes. Low-power 'Sleep' is supported, with configurable wake-up events. The WM8998 is powered from a 1.8V external supply. A separate supply is required for the Class D speaker drivers (typically direct connection to 4.2V battery).

Two integrated FLLs provide support for a wide range of system clock frequencies. The WM8998 is configured using the I2C or SLIMbus interfaces. The fully-differential internal analogue architecture, minimal analogue signal paths and on-chip RF noise filters ensure a very high degree of noise immunity.

## FEATURES

- Hi-Fi audio hub CODEC for mobile applications

- Digital audio processing core

- Fully flexible digital signal routing and mixing

- Wind noise, sidetone and other programmable filters

- Dynamic Range Control (compressor, limiter)

- Fully parametric EQs

- Low-pass / High-pass filters

- Multi-channel asynchronous sample rate conversion

- Integrated multi-channel 24-bit hi-fi audio hub CODEC

- 3 ADCs, 96dB SNR microphone input (48kHz)

- 7 DACs, 122dB SNR headphone playback (48kHz)

- Audio inputs

- Up to 6 analogue or 3 digital microphone inputs

- Single-ended or differential mic/line inputs

- Stereo headphone output driver

- 28mW into 32Ω load at 0.1% THD+N

- 6.9mW typical headphone playback power consumption

- Pop suppression functions

- 1µV<sub>RMS</sub> noise floor (A-weighted)

- Ground-referenced line output driver

- Stereo single-ended or Mono differential configuration

- Mono BTL earpiece output driver

- 100mW into 32Ω BTL load at 5% THD+N

- Stereo (2 x 2W) Class D speaker output drivers

- Direct drive of external haptics vibe actuators

- Two-channel digital speaker (PDM) output interface

- IEC-60958-3 compatible S/PDIF transmitter

- SLIMbus audio and control interface

- 3 full digital audio interfaces

- Standard sample rates from 8kHz up to 192kHz

- TDM support on all AIFs

- 6 channel input and output on AIF1 and AIF2

- Flexible clocking, derived from MCLKn, BCLKn or SLIMbus

- 2 low-power FLLs support reference clocks down to 32kHz

- Advanced accessory detection functions

- Low-power standby mode and configurable wake-up

- Configurable functions on 5 GPIO pins

- Integrated LDO regulators and charge pumps

- Support for single 1.8V supply operation

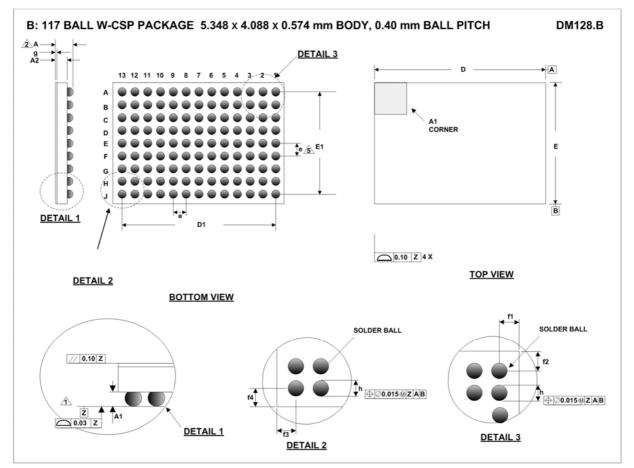

- Small W-CSP package, 0.4mm pitch

## **APPLICATIONS**

- Smartphones and Multimedia handsets

- Tablets and Mobile Internet Devices (MID)

[1] This product is protected by Patents US 7,622,984, US 7,626,445, US 7,765,019 and GB 2,432,765

Product Brief, June 2014, Rev 3.0

## TABLE OF CONTENTS

| DESCRIPTION                      | 1  |

|----------------------------------|----|

| FEATURES                         | 1  |

| APPLICATIONS                     | 1  |

| BLOCK DIAGRAM                    | 2  |

| TABLE OF CONTENTS                | 3  |

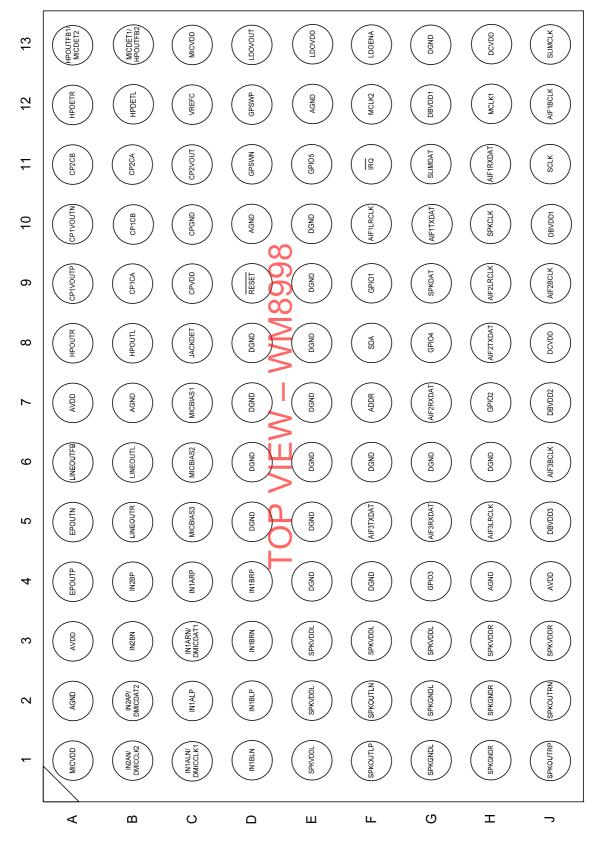

| PIN CONFIGURATION                | 4  |

| ORDERING INFORMATION             | 5  |

| PIN DESCRIPTION                  | 5  |

| ABSOLUTE MAXIMUM RATINGS         | 8  |

| RECOMMENDED OPERATING CONDITIONS |    |

| ELECTRICAL CHARACTERISTICS       | 10 |

| TERMINOLOGY                      | 20 |

| DEVICE DESCRIPTION               | 21 |

| INTRODUCTION                     |    |

| HI-FI AUDIO CODEC                |    |

| DIGITAL AUDIO CORE               | 22 |

| DIGITAL INTERFACES               |    |

| OTHER FEATURES                   |    |

| RECOMMENDED EXTERNAL COMPONENTS  |    |

| PACKAGE DIMENSIONS               | 25 |

| IMPORTANT NOTICE                 | 26 |

| ADDRESS:                         |    |

| REVISION HISTORY                 | 27 |

|                                  |    |

## **PIN CONFIGURATION**

Product Brief , June 2014, Rev 3.0

## ORDERING INFORMATION

| ORDER CODE  | TEMPERATURE<br>RANGE | PACKAGE                           | MOISTURE<br>SENSITIVITY LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|-------------|----------------------|-----------------------------------|-------------------------------|-------------------------------|

| WM8998ECS/R | -40°C to +85°C       | W-CSP<br>(Pb-free, Tape and reel) | MSL1                          | 260°C                         |

Note:

Reel quantity = 7000

## **PIN DESCRIPTION**

A description of each pin on the WM8998 is provided below.

Note that, where multiple pins share a common name, these pins should be tied together on the PCB.

All Digital Output pins are CMOS outputs, unless otherwise stated.

| PIN NO                                                                          | NAME      | TYPE                   | DESCRIPTION                                                          |

|---------------------------------------------------------------------------------|-----------|------------------------|----------------------------------------------------------------------|

| F7                                                                              | ADDR      | Digital Input          | Control interface (I2C) address select                               |

| A2, B7, D10,<br>E12, H4                                                         | AGND      | Supply                 | Analogue ground (Return path for AVDD)                               |

| J12                                                                             | AIF1BCLK  | Digital Input / Output | Audio interface 1 bit clock                                          |

| F10                                                                             | AIF1LRCLK | Digital Input / Output | Audio interface 1 left / right clock                                 |

| H11                                                                             | AIF1RXDAT | Digital Input          | Audio interface 1 RX digital audio data                              |

| G10                                                                             | AIF1TXDAT | Digital Output         | Audio interface 1 TX digital audio data                              |

| J9                                                                              | AIF2BCLK  | Digital Input / Output | Audio interface 2 bit clock                                          |

| H9                                                                              | AIF2LRCLK | Digital Input / Output | Audio interface 2 left / right clock                                 |

| G7                                                                              | AIF2RXDAT | Digital Input          | Audio interface 2 RX digital audio data                              |

| H8                                                                              | AIF2TXDAT | Digital Output         | Audio interface 2 TX digital audio data                              |

| J6                                                                              | AIF3BCLK  | Digital Input / Output | Audio interface 3 bit clock                                          |

| H5                                                                              | AIF3LRCLK | Digital Input / Output | Audio interface 3 left / right clock                                 |

| G5                                                                              | AIF3RXDAT | Digital Input          | Audio interface 3 RXdigital audio data                               |

| F5                                                                              | AIF3TXDAT | Digital Output         | Audio interface 3 TX digital audio data                              |

| A3, A7, J4                                                                      | AVDD      | Supply                 | Analogue supply                                                      |

| B9                                                                              | CP1CA     | Analogue Output        | Charge pump 1 fly-back capacitor pin                                 |

| B10                                                                             | CP1CB     | Analogue Output        | Charge pump 1 fly-back capacitor pin                                 |

| A10                                                                             | CP1VOUTN  | Analogue Output        | Charge pump 1 negative output decoupling pin                         |

| A9                                                                              | CP1VOUTP  | Analogue Output        | Charge pump 1 positive output decoupling pin                         |

| B11                                                                             | CP2CA     | Analogue Output        | Charge pump 2 fly-back capacitor pin                                 |

| A11                                                                             | CP2CB     | Analogue Output        | Charge pump 2 fly-back capacitor pin                                 |

| C11                                                                             | CP2VOUT   | Analogue Output        | Charge pump 2 output decoupling pin / Supply for LDO2                |

| C10                                                                             | CPGND     | Supply                 | Charge pump 1 & 2 ground (Return path for CPVDD)                     |

| C9                                                                              | CPVDD     | Supply                 | Supply for Charge Pump 1 & 2                                         |

| G12, J10                                                                        | DBVDD1    | Supply                 | Digital buffer (I/O) supply (core functions and Audio Interface 1)   |

| J7                                                                              | DBVDD2    | Supply                 | Digital buffer (I/O) supply (for Audio Interface 2, GPIO2, GPIO4)    |

| J5                                                                              | DBVDD3    | Supply                 | Digital buffer (I/O) supply (for Audio Interface 3, GPIO3)           |

| H13, J8                                                                         | DCVDD     | Supply                 | Digital core supply                                                  |

| D5, D6, D7,<br>D8, E4, E5,<br>E6, E7, E8,<br>E9, E10, F4,<br>F6, G6, G13,<br>H6 | DGND      | Supply                 | Digital ground<br>(Return path for DCVDD, DBVDD1, DBVDD2 and DBVDD3) |

| A5                                                                              | EPOUTN    | Analogue Output        | Earpiece negative output                                             |

| A4                                                                              | EPOUTP    | Analogue Output        | Earpiece positive output                                             |

| F9                                                                              | GPIO1     | Digital Input / Output | General Purpose pin GPIO1.                                           |

|                                                                                 |           |                        | The output configuration is selectable CMOS or Open Drain.           |

Product Brief, June 2014, Rev 3.0

Pre-Production

| PIN NO     | NAME                 | TYPE                              | DESCRIPTION                                                                                                                                                |

|------------|----------------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| H7         | GPIO2                | Digital Input / Output            | General Purpose pin GPIO2.<br>The output configuration is selectable CMOS or Open Drain.                                                                   |

| G4         | GPIO3                | Digital Input / Output            | General Purpose pin GPIO3.<br>The output configuration is selectable CMOS or Open Drain.                                                                   |

| G8         | GPIO4                | Digital Input / Output            | General Purpose pin GPIO4.                                                                                                                                 |

| E11        | GPIO5                | Digital Input / Output            | The output configuration is selectable CMOS or Open Drain.<br>General Purpose pin GPIO5.                                                                   |

| D11        | GPSWN                |                                   | The output configuration is selectable CMOS or Open Drain.                                                                                                 |

| D11<br>D12 | GPSWP                | Analogue Output<br>Analogue Input | General Purpose analogue switch contact (negative)<br>General Purpose analogue switch contact (positive)                                                   |

| B12        | HPDETL               | <b>°</b> .                        | Headphone left (HPOUTL) sense input                                                                                                                        |

|            |                      | Analogue Input                    |                                                                                                                                                            |

| A12        | HPDETR               | Analogue Input                    | Headphone right (HPOUTR) sense input                                                                                                                       |

| A13        | HPOUTFB1/<br>MICDET2 | Analogue Input                    | HPOUTL and HPOUTR ground feedback pin 1/<br>Microphone & accessory sense input 2                                                                           |

| B8         | HPOUTL               | Analogue Output                   | Left headphone output                                                                                                                                      |

| A8         | HPOUTR               | Analogue Output                   | Right headphone output                                                                                                                                     |

| C1         | IN1ALN/              | Analogue Input /                  | Left channel negative differential Mic/Line input /                                                                                                        |

|            | DMICCLK1             | Digital Output                    | Digital MIC clock output 1                                                                                                                                 |

| C2         | IN1ALP               | Analogue Input                    | Left channel single-ended Mic/Line input /<br>Left channel positive differential Mic/Line input                                                            |

| C3         | IN1ARN/              | Analogue input /                  | Right channel negative differential Mic/Line input /                                                                                                       |

|            | DMICDAT1             | Digital Input                     | Digital MIC data input 1                                                                                                                                   |

| C4         | IN1ARP               | Analogue Input                    | Right channel single-ended Mic/Line input /<br>Right channel positive differential Mic/Line input                                                          |

| B1         | IN2AN/               | Analogue Input /                  | Negative differential Mic/Line input /                                                                                                                     |

|            | DMICCLK2             | Digital Output                    | Digital MIC clock output 2                                                                                                                                 |

| B2         | IN2AP/               | Analogue Input /                  | Single-ended Mic/Line input /                                                                                                                              |

|            | DMICDAT2             | Digital Input                     | Positive differential Mic/Line input/                                                                                                                      |

|            |                      |                                   | Digital MIC data input 2                                                                                                                                   |

| D1         | IN1BLN               | Analogue Input                    | Left channel negative differential Mic/Line input                                                                                                          |

| D2         | IN1BLP               | Analogue Input                    | Left channel single-ended Mic/Line input /<br>Left channel positive differential Mic/Line input                                                            |

| D3         | IN1BRN               | Analogue input                    | Right channel negative differential Mic/Line input                                                                                                         |

| D4         | IN1BRP               | Analogue Input                    | Right channel single-ended Mic/Line input /<br>Right channel positive differential Mic/Line input                                                          |

| B3         | IN2BN                | Analogue Input                    | Negative differential Mic/Line input                                                                                                                       |

| B3<br>B4   | IN2BP                | Analogue Input                    | Single-ended Mic/Line input /                                                                                                                              |

| F11        | IRQ                  | Digital Output                    | Positive differential Mic/Line input<br>Interrupt Request (IRQ) output (default is active low).<br>The pin configuration is selectable CMOS or Open Drain. |

| C8         | JACKDET              | Analogue Input                    | Jack detect input                                                                                                                                          |

| F13        | LDOENA               | Digital Input                     | Enable pin for LDO1                                                                                                                                        |

| E13        | LDOVDD               | Supply                            | Supply for LDO1                                                                                                                                            |

| D13        | LDOVOUT              | Analogue Output                   | LDO1 output                                                                                                                                                |

| A6         | LINEOUTFB            | Analogue Input                    | LINEOUTL and LINEOUTR ground loop noise rejection feedbac                                                                                                  |

| B6         | LINEOUTL             | Analogue Output                   | Left line output                                                                                                                                           |

| B5         | LINEOUTR             | Analogue Output                   | Right line output                                                                                                                                          |

| H12        | MCLK1                | Digital Input                     | Master clock 1                                                                                                                                             |

| F12        | MCLK2                | Digital Input                     | Master clock 2                                                                                                                                             |

| C7         | MICBIAS1             | Analogue Output                   | Misci cioci 2<br>Microphone bias 1                                                                                                                         |

| C6         | MICBIAS2             | Analogue Output                   | Microphone bias 2                                                                                                                                          |

| C5         | MICBIAS3             | Analogue Output                   | Microphone bias 3                                                                                                                                          |

| B13        | MICDET1/             | Analogue Input                    | Microphone & accessory sense input 1/                                                                                                                      |

| 2.5        | HPOUTFB2             |                                   | HPOUTL and HPOUTR ground feedback pin 2                                                                                                                    |

Product Brief, June 2014, Rev 3.0

Pre-Production

| PIN NO                | NAME     | ТҮРЕ                   | DESCRIPTION                                                      |

|-----------------------|----------|------------------------|------------------------------------------------------------------|

| A1, C13               | MICVDD   | Analogue Output        | LDO2 output decoupling pin (generated internally by WM8998).     |

|                       |          |                        | (Can also be used as reference/supply for external microphones.) |

| D9                    | RESET    | Digital Input          | Digital Reset input (active low)                                 |

| J11                   | SCLK     | Digital Input          | Control interface (I2C) clock input                              |

| F8                    | SDA      | Digital Input / Output | Control interface (I2C) data input and output                    |

|                       |          |                        | The output function is implemented as an Open Drain circuit.     |

| J13                   | SLIMCLK  | Digital Input          | SLIMBus Clock input                                              |

| G11                   | SLIMDAT  | Digital Input / Output | SLIMBus Data input / output                                      |

| H10                   | SPKCLK   | Digital Output         | Digital speaker (PDM) clock output                               |

| G9                    | SPKDAT   | Digital Output         | Digital speaker (PDM) data output                                |

| G1, G2                | SPKGNDL  | Supply                 | Left speaker driver ground (Return path for SPKVDDL)             |

| H1, H2                | SPKGNDR  | Supply                 | Right speaker driver ground (Return path for SPKVDDR)            |

| F2                    | SPKOUTLN | Analogue Output        | Left speaker negative output                                     |

| F1                    | SPKOUTLP | Analogue Output        | Left speaker positive output                                     |

| J2                    | SPKOUTRN | Analogue Output        | Right speaker negative output                                    |

| J1                    | SPKOUTRP | Analogue Output        | Right speaker positive output                                    |

| E1, E2, E3,<br>F3, G3 | SPKVDDL  | Supply                 | Left speaker driver supply                                       |

| H3, J3                | SPKVDDR  | Supply                 | Right speaker driver supply                                      |

| C12                   | VREFC    | Analogue Output        | Bandgap reference decoupling capacitor connection                |

## **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020 for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                                                            | MIN             | MAX           |

|--------------------------------------------------------------------------------------|-----------------|---------------|

| Supply voltages (LDOVDD, AVDD, DCVDD, CPVDD)                                         | -0.3V           | +2.0V         |

| Supply voltages (DBVDD1, DBVDD2, DBVDD3)                                             | -0.3V           | +4.0V         |

| Supply voltages (SPKVDDL, SPKVDDR)                                                   | -0.3V           | +6.0V         |

| Voltage range digital inputs (DBVDD1 domain)                                         | AGND - 0.3V     | DBVDD1 + 0.3V |

| Voltage range digital inputs (DBVDD2 domain)                                         | AGND - 0.3V     | DBVDD2 + 0.3V |

| Voltage range digital inputs (DBVDD3 domain)                                         | AGND - 0.3V     | DBVDD3 + 0.3V |

| Voltage range digital inputs (DMICDATn)                                              | AGND - 0.3V     | MICVDD + 0.3V |

| Voltage range analogue inputs<br>(IN1A*, IN1B*, IN2A*, MICDETn, HPOUTFBn, LINEOUTFB) | AGND - 0.3V     | MICVDD + 0.3V |

| Voltage range analogue inputs (IN2B*)                                                | AGND - 3.3V     | MICVDD + 0.3V |

| Voltage range analogue inputs (JACKDET, HPDETL, HPDETR)                              | CP1VOUTN - 0.3V | AVDD + 0.3V   |

| Voltage range analogue inputs (GPSWP, GPSWN)                                         | AGND - 0.3V     | MICVDD + 0.3V |

| Ground (DGND, CPGND, SPKGNDL, SPKGNDR)                                               | AGND - 0.3V     | AGND + 0.3V   |

| Operating temperature range, T <sub>A</sub>                                          | -40°C           | +85°C         |

| Operating junction temperature, T <sub>J</sub>                                       | -40°C           | +125°C        |

| Storage temperature after soldering                                                  | -65°C           | +150°C        |

**Note:** CP1VOUTN is an internal supply, generated by the WM8998 Charge Pump (CP1). The CP1VOUTN voltage may vary between AGND and -CPVDD.

## **RECOMMENDED OPERATING CONDITIONS**

| PARAMETER                                           | SYMBOL                                 | MIN  | TYP | MAX  | UNIT |

|-----------------------------------------------------|----------------------------------------|------|-----|------|------|

| Digital supply range (Core)<br>See notes 2, 3, 4, 5 | DCVDD<br>(≤24.576MHz clocking)         | 1.14 | 1.2 | 1.9  | V    |

|                                                     | DCVDD<br>(>24.576MHz clocking)         | 1.71 | 1.8 | 1.9  |      |

| Digital supply range (I/O)                          | DBVDD1                                 | 1.7  |     | 1.9  | V    |

| Digital supply range (I/O)                          | DBVDD2, DBVDD3                         | 1.7  |     | 3.47 | V    |

| LDO supply range                                    | LDOVDD                                 | 1.7  | 1.8 | 1.9  | V    |

| Charge Pump supply range                            | CPVDD                                  | 1.7  | 1.8 | 1.9  | V    |

| Speaker supply range                                | SPKVDDL, SPKVDDR                       | 2.4  |     | 5.5  | V    |

| Analogue supply range<br>See note 2                 | AVDD                                   | 1.7  | 1.8 | 1.9  | V    |

| Ground<br>See note 1                                | DGND, AGND, CPGND,<br>SPKGNDL, SPKGNDR |      | 0   |      | V    |

| Power supply rise time                              | DCVDD                                  | 10   |     | 2000 | μs   |

| See notes 7, 8, 9, 10                               | All other supplies                     | 1    |     |      | 1    |

| Operating temperature range                         | TA                                     | -40  |     | 85   | °C   |

#### Notes:

- 1. The grounds must always be within 0.3V of AGND.

- 2. AVDD must be supplied before DCVDD. DCVDD must not be powered if AVDD is not present. There are no other power sequencing requirements.

- 3. An internal LDO (powered by LDOVDD) can be used to provide the DCVDD supply.

- 4. 'Sleep' mode is supported when DCVDD is below the limits noted, provided AVDD and DBVDD1 are present.

- 5. Under default conditions, digital core clocking rates above 24.576MHz are inhibited. The register-controlled clocking limit should only be raised when the applicable DCVDD voltage is present.

- 6. An internal Charge Pump and LDO (powered by CPVDD) provide the microphone bias supply; the MICVDD pin should not be connected to an external supply.

- 7. DCVDD minimum rise time does not apply when this is powered using the internal LDO.

- 8. If DCVDD is supplied externally, and the rise time exceeds 2ms, then RESET must be asserted (low) during the rise, and held asserted until after DCVDD is within the recommended operating limits.

- 9. The specified minimum power supply rise times assume a minimum decoupling capacitance of 100nF per pin. However, Wolfson strongly advises that the recommended decoupling capacitors are present on the PCB and that appropriate layout guidelines are observed.

- 10. The specified minimum power supply rise times also assume a maximum PCB inductance of 10nH between decoupling capacitor and pin.

## **ELECTRICAL CHARACTERISTICS**

#### **Test Conditions**

#### AVDD = 1.8V,

With the exception of the condition(s) noted above, the following electrical characteristics are valid across the full range of recommended operating conditions.

| PARAMETER                                                            | SYMBOL | TEST CONDITIONS                         | MIN | TYP       | MAX | UNIT                    |  |

|----------------------------------------------------------------------|--------|-----------------------------------------|-----|-----------|-----|-------------------------|--|

| Analogue Input Signal Level (IN1AL, IN1AR, IN1BL, IN1BR, IN2A, IN2B) |        |                                         |     |           |     |                         |  |

| Full-scale input signal level (0dBFS output)                         | VINFS  | Single-ended PGA input,<br>6dB PGA gain |     | 0.5<br>-6 |     | V <sub>RMS</sub><br>dBV |  |

|                                                                      |        | Differential PGA input,<br>0dB PGA gain |     | 1<br>0    |     | V <sub>RMS</sub><br>dBV |  |

#### Notes:

- 1. The full-scale input signal level is also the maximum analogue input level, before clipping occurs.

- 2. The full-scale input signal level changes in proportion with AVDD. For differential input, it is calculated as AVDD / 1.8.

- 3. A  $1.0V_{RMS}$  differential signal equates to  $0.5V_{RMS}$ /-6dBV per input.

- 4. A sinusoidal input signal is assumed.

#### **Test Conditions**

#### T<sub>A</sub> = +25°C

With the exception of the condition(s) noted above, the following electrical characteristics are valid across the full range of recommended operating conditions.

| PARAMETER                                                                   | SYMBOL | TEST CONDITIONS                              | MIN | TYP | MAX | UNIT |  |  |

|-----------------------------------------------------------------------------|--------|----------------------------------------------|-----|-----|-----|------|--|--|

| Analogue Input Pin Characteristics (IN1AL, IN1AR, IN1BL, IN1BR, IN2A, IN2B) |        |                                              |     |     |     |      |  |  |

| Input resistance                                                            | Rin    | Differential input,<br>All PGA gain settings |     | 24  |     | kΩ   |  |  |

|                                                                             |        | Single-ended input,<br>0dB PGA gain          |     | 16  |     |      |  |  |

| Input capacitance                                                           | CIN    |                                              |     |     | 5   | pF   |  |  |

#### **Test Conditions**

The following electrical characteristics are valid across the full range of recommended operating conditions.

| PARAMETER                                 | SYMBOL | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |  |

|-------------------------------------------|--------|----------------------|-----|-----|-----|------|--|

| Input Programmable Gain Amplifiers (PGAs) |        |                      |     |     |     |      |  |

| Minimum programmable gain                 |        |                      |     | 0   |     | dB   |  |

| Maximum programmable gain                 |        |                      |     | 31  |     | dB   |  |

| Programmable gain step size               |        | Guaranteed monotonic |     | 1   |     | dB   |  |

#### **Test Conditions**

The following electrical characteristics are valid across the full range of recommended operating conditions.

| PARAMETER                                                  | SYMBOL | TEST CONDITIONS | MIN | TYP | MAX | UNIT |  |  |

|------------------------------------------------------------|--------|-----------------|-----|-----|-----|------|--|--|

| Digital Microphone Input Signal Level (DMICDAT1, DMICDAT2) |        |                 |     |     |     |      |  |  |

| Full-scale input signal level (0dBFS output)               |        | 0dB gain        |     | -6  |     | dBFS |  |  |

#### Notes:

5. The digital microphone input signal level is measured in dBFS, where 0dBFS is a signal level equal to the full-scale range (FSR) of the PDM input. The FSR is defined as the amplitude of a 1kHz sine wave whose positive and negative peaks are represented by the maximum and minimum digital codes respectively - this is the largest 1kHz sine wave that will fit in the digital output range without clipping. Note that, because the definition of FSR is based on a sine wave, the PDM data format can support signals larger than 0dBFS.

Pre-Production

#### **Test Conditions**

The following electrical characteristics are valid across the full range of recommended operating conditions.

| PARAMETER                          | SYMBOL        | TEST CONDITIONS                                   | MIN            | TYP           | MAX            | UNIT |

|------------------------------------|---------------|---------------------------------------------------|----------------|---------------|----------------|------|

| Headphone Output Driver (HPOUT     | L, HPOUTR)    |                                                   | U              |               |                | •    |

| Load resistance                    |               | Charge Pump<br>Normal mode (default)              | 15             |               |                | Ω    |

|                                    |               | Charge Pump<br>Low Impedance mode                 | 6              |               |                |      |

|                                    |               | Device survival with load<br>applied indefinitely | 0.1            |               |                |      |

| Load capacitance                   |               | Direct connection,<br>Single-ended mode           |                |               | 500            | pF   |

|                                    |               | Direct connection,<br>Differential (BTL) mode     |                |               | 250            |      |

|                                    |               | Connection via 16Ω<br>series resistor             |                |               | 2              | nF   |

| DC offset at Load                  |               | Single-ended mode                                 |                | 0.1           |                | mV   |

|                                    |               | Differential (BTL) mode                           |                | 0.2           |                |      |

| Note - to support HPOUT loads less | than 15Ω, the | e Charge Pump (CP1) must be                       | e configured f | or low impeda | ince operatior | 1.   |

| Line Output Driver (LINEOUTL, LI   | NEOUTR)       |                                                   |                |               |                |      |

| Load resistance                    |               | Normal operation                                  | 600            |               |                | Ω    |

|                                    |               | Mono Mode (BTL)                                   | 600            |               |                |      |

|                                    |               | Device survival with load<br>applied indefinitely | 0.1            |               |                |      |

| Load capacitance                   |               | Direct connection,<br>Single-ended mode           |                |               | 500            | pF   |

|                                    |               | Direct connection,<br>Differential (BTL) mode     |                |               | 250            |      |

|                                    |               | Connection via 16Ω<br>series resistor             |                |               | 2              | nF   |

| DC offset at Load                  |               | Single-ended mode                                 |                | 0.1           |                | mV   |

|                                    |               | Differential (BTL) mode                           |                | 0.2           |                |      |

| Earpiece Output Driver (EPOUTP+    | EPOUTN)       |                                                   |                |               |                |      |

| Load resistance                    |               | Charge Pump<br>Normal mode (default)              | 30             |               |                | Ω    |

|                                    |               | Charge Pump<br>Low Impedance mode                 | 15             |               |                |      |

|                                    |               | Device survival with load<br>applied indefinitely | 0.1            |               |                |      |

| Load capacitance                   |               | Direct connection (BTL)                           |                |               | 250            | pF   |

|                                    |               | Connection via 16Ω<br>series resistor             |                |               | 2              | nF   |

| DC offset at Load                  |               |                                                   |                | 0.1           |                | mV   |

| Note - to support HPOUT loads less | than 15Ω, the | e Charge Pump (CP1) must be                       | e configured f | or low impeda | ince operatior | 1.   |

| Speaker Output Driver (SPKOUTL     | P+SPKOUTL     | N, SPKOUTRP+SPKOUTRN                              | )              |               |                |      |

| Load resistance                    |               | Normal operation                                  | 4              |               |                | Ω    |

|                                    |               | Device survival with load applied indefinitely    | 0              |               |                |      |

| Load capacitance                   |               | · · · ·                                           |                |               | 200            | pF   |

| DC offset at Load                  |               |                                                   |                | 5             |                | mV   |

| SPKVDD leakage current             |               |                                                   |                | 1             |                | μA   |

DBVDD1 = DBVDD2 = DBVDD3 = LDOVDD = CPVDD = AVDD = 1.8V,

DCVDD = 1.2V (powered from LDO1), MICVDD = 3.0V (powered from LDO2), SPKVDDL = SPKVDDR = 4.2V,

T<sub>A</sub> = +25°C, 1kHz sinusoid signal, fs = 48kHz, Input PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                                     | SYMBOL         | TEST CONDITIONS                                            | MIN            | TYP              | MAX           | UNIT                          |

|-------------------------------------------------------------------------------|----------------|------------------------------------------------------------|----------------|------------------|---------------|-------------------------------|

| Analogue Input Paths (IN1AL, IN                                               | 1AR, IN1BL, II | N1BR, IN2A, IN2B) to ADC (Di                               | ifferential li | nput Mode, IN    | n_SRC = x0)   |                               |

| Signal to Noise Ratio<br>(A-weighted)                                         | SNR            | High performance mode<br>(INn_OSR = 1)                     | 86             | 96               |               | dB                            |

|                                                                               |                | Normal mode<br>(INn_OSR = 0)                               |                | 93               |               |                               |

| Total Harmonic Distortion                                                     | THD            | -1dBV input                                                |                | -88              |               | dB                            |

| Total Harmonic Distortion Plus<br>Noise                                       | THD+N          | -1dBV input                                                |                | -86              | -76           | dB                            |

| Channel separation (Left/Right)                                               |                |                                                            |                | 100              |               | dB                            |

| Input noise floor                                                             |                | A-weighted,<br>PGA gain = +18dB                            |                | 3.2              |               | μV <sub>RMS</sub>             |

| Common mode rejection ratio                                                   | CMRR           | PGA gain = +30dB                                           |                | 65               |               | dB                            |

|                                                                               |                | PGA gain = 0dB                                             |                | 70               |               |                               |

| PSRR (DBVDDn, LDOVDD,                                                         | PSRR           | 100mV (peak-peak) 217Hz                                    |                | 70               |               | dB                            |

| CPVDD, AVDD)                                                                  |                | 100mV(peak-peak) 10kHz                                     |                | 65               |               |                               |

| PSRR (SPKVDDL, SPKVDDR)                                                       | PSRR           | 100mV (peak-peak) 217Hz                                    |                | 95               |               | dB                            |

|                                                                               |                | 100mV(peak-peak) 10kHz                                     |                | 95               |               |                               |

| Analogue Input Paths (IN1AL, IN<br>PGA Gain = +6dB unless otherwise           | , ,            | N1BR, IN2A, IN2B) to ADC (Si                               | ngle-Endeo     | l Input Mode     | , INn_SRC = : | <b>x1</b> )                   |

| Signal to Noise Ratio<br>(A-weighted)                                         | SNR            | High performance mode<br>(INn_OSR = 1)                     | 83             | 94               |               | dB                            |

|                                                                               |                | Normal mode<br>(INn_OSR = 0)                               |                | 92               |               |                               |

| Total Harmonic Distortion                                                     | THD            | -7dBV input                                                |                | -81              |               |                               |

| Total Harmonic Distortion Plus                                                |                |                                                            |                |                  |               | dB                            |

| Noise                                                                         | THD+N          | -7dBV input                                                |                | -80              | -71           | dB<br>dB                      |

| Noise<br>Channel separation (Left/Right)                                      | THD+N          | -7dBV input                                                |                | -80<br>100       | -71           | -                             |

|                                                                               | THD+N          | -7dBV input<br>A-weighted,<br>PGA gain = +18dB             |                |                  | -71           | dB                            |

| Channel separation (Left/Right)                                               | THD+N          | A-weighted,                                                |                | 100              | -71           | dB<br>dB                      |

| Channel separation (Left/Right)<br>Input noise floor                          |                | A-weighted,<br>PGA gain = +18dB                            |                | 100<br>4.6       | -71           | dB<br>dB<br>µV <sub>RMS</sub> |

| Channel separation (Left/Right)<br>Input noise floor<br>PSRR (DBVDDn, LDOVDD, |                | A-weighted,<br>PGA gain = +18dB<br>100mV (peak-peak) 217Hz |                | 100<br>4.6<br>70 | -71           | dB<br>dB<br>µV <sub>RMS</sub> |

DBVDD1 = DBVDD2 = DBVDD3 = LDOVDD = CPVDD = AVDD = 1.8V,

DCVDD = 1.2V (powered from LDO1), MICVDD = 3.0V (powered from LDO2), SPKVDDL = SPKVDDR = 4.2V,  $T_A = +25^{\circ}$ C, 1kHz sinusoid signal, fs = 48kHz, Input PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                               | SYMBOL           | TEST CONDITIONS                      | MIN    | TYP | MAX | UNIT              |

|-----------------------------------------|------------------|--------------------------------------|--------|-----|-----|-------------------|

| DAC to Headphone Output (HPO            | UTL, HPOUTF      | R; R <sub>L</sub> = 32Ω)             |        |     |     |                   |

| Maximum output power                    | Po               | 0.1% THD+N                           |        | 28  |     | mW                |

| Signal to Noise Ratio                   | SNR              | A-weighted,<br>Output signal = 1Vrms |        | 122 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 20mW                            |        | -86 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | Po = 20mW                            |        | -84 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 5mW                             |        | -89 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | P <sub>o</sub> = 5mW                 |        | -85 |     | dB                |

| Channel separation (Left/Right)         |                  | Po = 20mW                            |        | 110 |     | dB                |

| Output noise floor                      |                  | A-weighted                           |        | 1   |     | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                   | PSRR             | 100mV (peak-peak) 217Hz              |        | 115 |     | dB                |

| CPVDD, AVDD)                            |                  | 100mV (peak-peak) 10kHz              |        | 80  |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                 | PSRR             | 100mV (peak-peak) 217Hz              |        | 115 |     | dB                |

|                                         |                  | 100mV(peak-peak) 10kHz               |        | 80  |     |                   |

| DAC to Headphone Output (HPO            | UTL, HPOUTF      | R; R∟ = 16Ω)                         |        |     |     |                   |

| Maximum output power                    | Po               | 0.1% THD+N                           |        | 34  |     | mW                |

| Signal to Noise Ratio                   | SNR              | A-weighted,<br>Output signal = 1Vrms | 114    | 122 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 20mW                            |        | -78 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | P <sub>o</sub> = 20mW                |        | -76 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 5mW                             |        | -78 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | P <sub>o</sub> = 5mW                 |        | -77 | -67 | dB                |

| Channel separation (Left/Right)         |                  | P <sub>o</sub> = 20mW                |        | 110 |     | dB                |

| Output noise floor                      |                  | A-weighted                           |        | 1   | 2   | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                   | PSRR             | 100mV (peak-peak) 217Hz              |        | 115 |     | dB                |

| CPVDD, AVDD)                            |                  | 100mV (peak-peak) 10kHz              |        | 80  |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                 | PSRR             | 100mV (peak-peak) 217Hz              |        | 115 |     | dB                |

|                                         |                  | 100mV(peak-peak) 10kHz               |        | 115 |     |                   |

| DAC to Line Output (HPOUTL, H           | POUTR; Load      | = 10kΩ, 50pF)                        |        |     |     |                   |

| Full-scale output signal level          | V <sub>OUT</sub> | 0dBFS input                          | 1<br>0 |     |     | Vrms<br>dBV       |

| Signal to Noise Ratio                   | SNR              | A-weighted,<br>Output signal = 1Vrms | 114    | 122 |     | dB                |

| Total Harmonic Distortion               | THD              | 0dBFS input                          |        | -89 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | 0dBFS input                          |        | -88 | -73 | dB                |

| Channel separation (Left/Right)         |                  |                                      |        | 110 |     | dB                |

| Output noise floor                      |                  | A-weighted                           |        | 1   | 2   | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                   | PSRR             | 100mV (peak-peak) 217Hz              |        | 115 |     | dB                |

| CPVDD, AVDD)                            |                  | 100mV (peak-peak) 10kHz              |        | 80  |     | 1                 |

| PSRR (SPKVDDL, SPKVDDR)                 | PSRR             | 100mV (peak-peak) 217Hz              |        | 115 |     | dB                |

|                                         |                  | 100mV(peak-peak) 10kHz               |        | 80  |     | ]                 |

DBVDD1 = DBVDD2 = DBVDD3 = LDOVDD = CPVDD = AVDD = 1.8V,

DCVDD = 1.2V (powered from LDO1), MICVDD = 3.0V (powered from LDO2), SPKVDDL = SPKVDDR = 4.2V,

T<sub>A</sub> = +25°C, 1kHz sinusoid signal, fs = 48kHz, Input PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                               | SYMBOL           | TEST CONDITIONS                      | MIN          | TYP | MAX | UNIT              |

|-----------------------------------------|------------------|--------------------------------------|--------------|-----|-----|-------------------|

| DAC to Line Output (LINEOUTL,           | LINEOUTR; L      | oad = 10kΩ, 50pF)                    |              |     |     |                   |

| Full-scale output signal level          | V <sub>OUT</sub> | 0dBFS input                          | 1            |     |     | Vrms              |

|                                         |                  |                                      | 0            |     |     | dBV               |

| Signal to Noise Ratio                   | SNR              | A-weighted,<br>Output signal = 1Vrms | 114          | 122 |     | dB                |

| Total Harmonic Distortion               | THD              | 0dBFS input                          |              | -89 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | 0dBFS input                          |              | -88 | -73 | dB                |

| Channel separation (Left/Right)         |                  |                                      |              | 110 |     | dB                |

| Output noise floor                      |                  | A-weighted                           |              | 1   | 2   | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                   | PSRR             | 100mV (peak-peak) 217Hz              |              | 127 |     | dB                |

| CPVDD, AVDD)                            |                  | 100mV (peak-peak) 10kHz              |              | 90  |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                 | PSRR             | 100mV (peak-peak) 217Hz              |              | 130 |     | dB                |

|                                         |                  | 100mV(peak-peak) 10kHz               |              | 85  |     |                   |

| DAC to Earpiece Output (EPOUT           | P+EPOUTN, F      | R∟ = 32Ω BTL)                        |              |     |     |                   |

| Maximum output power                    | Po               | 0.1% THD+N                           | .1% THD+N 83 | mW  |     |                   |

|                                         |                  | 5% THD+N                             |              | 100 |     |                   |

| Signal to Noise Ratio                   | SNR              | A-weighted,<br>Output signal = 2Vrms | 118          | 127 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 50mW                            |              | -92 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | P <sub>o</sub> = 50mW                |              | -90 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 5mW                             |              | -85 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | P <sub>o</sub> = 5mW                 |              | -83 | -73 | dB                |

| Output noise floor                      |                  | A-weighted                           |              | 1   | 2.5 | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                   | PSRR             | 100mV (peak-peak) 217Hz              |              | 113 |     | dB                |

| CPVDD, AVDD)                            |                  | 100mV (peak-peak) 10kHz              |              | 115 |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                 | PSRR             | 100mV (peak-peak) 217Hz              |              | 130 |     | dB                |

|                                         |                  | 100mV(peak-peak) 10kHz               |              | 100 |     |                   |

| DAC to Earpiece Output (EPOUT           | P+EPOUTN, F      | R∟ = 16Ω BTL)                        |              |     |     |                   |

| Maximum output power                    | Po               | 0.1% THD+N                           |              | 83  |     | mW                |

|                                         |                  | 10% THD+N                            |              | 110 |     |                   |

| Signal to Noise Ratio                   | SNR              | A-weighted,<br>Output signal = 2Vrms |              | 127 |     | dB                |

| Total Harmonic Distortion               | THD              | P <sub>o</sub> = 50mW                |              | -92 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | Po = 50mW                            |              | -90 |     | dB                |

| Total Harmonic Distortion               | THD              | Po = 5mW                             |              | -90 |     | dB                |

| Total Harmonic Distortion Plus<br>Noise | THD+N            | P <sub>o</sub> = 5mW                 |              | -88 |     | dB                |

| Output noise floor                      |                  | A-weighted                           |              | 1   |     | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                   | PSRR             | 100mV (peak-peak) 217Hz              | _            | 113 |     | dB                |

| CPVDD, AVDD)                            |                  | 100mV (peak-peak) 10kHz              |              | 115 |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                 | PSRR             | 100mV (peak-peak) 217Hz              |              | 130 |     | dB                |

|                                         |                  | 100mV(peak-peak) 10kHz               |              | 100 |     |                   |

Pre-Production

#### **Test Conditions**

DBVDD1 = DBVDD2 = DBVDD3 = LDOVDD = CPVDD = AVDD = 1.8V,

DCVDD = 1.2V (powered from LDO1), MICVDD = 3.0V (powered from LDO2), SPKVDDL = SPKVDDR = 4.2V,  $T_A = +25^{\circ}$ C, 1kHz sinusoid signal, fs = 48kHz, Input PGA gain = 0dB, 24-bit audio data unless otherwise stated.

| PARAMETER                                                     | SYMBOL | TEST CONDITIONS                      | MIN          | TYP          | MAX | UNIT              |

|---------------------------------------------------------------|--------|--------------------------------------|--------------|--------------|-----|-------------------|

| DAC to Speaker Output (SPKOU<br>High Performance mode (OUT4_C |        | LN, SPKOUTRP+SPKOUTRN                | l, Load = 8Ω | , 22µH, BTL) |     |                   |

| Maximum output power                                          | Po     | SPKVDD = 5.0V,<br>1% THD+N           |              | 1.37         |     | W                 |

|                                                               |        | SPKVDD = 4.2V,<br>1% THD+N           |              | 0.97         |     |                   |

|                                                               |        | SPKVDD = 3.6V,<br>1% THD+N           |              | 0.71         |     |                   |

| Signal to Noise Ratio                                         | SNR    | A-weighted,<br>Output signal = 3Vrms | 90           | 100          |     | dB                |

| Total Harmonic Distortion                                     | THD    | P <sub>0</sub> = 0.7W                |              | -74          |     | dB                |

| Total Harmonic Distortion Plus<br>Noise                       | THD+N  | P <sub>0</sub> = 0.7W                |              | -73          |     | dB                |

| Total Harmonic Distortion                                     | THD    | Po = 0.5W                            |              | -74          |     | dB                |

| Total Harmonic Distortion Plus<br>Noise                       | THD+N  | P <sub>0</sub> = 0.5W                |              | -73          | -57 | dB                |

| Channel separation (Left/Right)                               |        | P <sub>0</sub> = 0.5W                |              | 95           |     | dB                |

| Output noise floor                                            |        | A-weighted                           |              | 30           | 95  | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                                         | PSRR   | 100mV (peak-peak) 217Hz              |              | 80           |     | dB                |

| CPVDD, AVDD)                                                  |        | 100mV (peak-peak) 10kHz              |              | 70           |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                                       | PSRR   | 100mV (peak-peak) 217Hz              |              | 70           |     | dB                |

|                                                               |        | 100mV (peak-peak) 10kHz              |              | 70           |     |                   |

| DAC to Speaker Output (SPKOU<br>High Performance mode (OUT4_C |        | LN, SPKOUTRP+SPKOUTRN                | l, Load = 4Ω | , 15µH, BTL) |     |                   |

| Maximum output power                                          | Po     | SPKVDD = 5.0V,<br>1% THD+N           |              | 2.4          |     | W                 |

|                                                               |        | SPKVDD = 4.2V,<br>1% THD+N           |              | 1.69         |     |                   |

|                                                               |        | SPKVDD = 3.6V,<br>1% THD+N           |              | 1.24         |     |                   |

| Signal to Noise Ratio                                         | SNR    | A-weighted,<br>Output signal = 3Vrms |              | 100          |     | dB                |

| Total Harmonic Distortion                                     | THD    | Po = 1.0W                            |              | -61          |     | dB                |

| Total Harmonic Distortion Plus<br>Noise                       | THD+N  | P <sub>0</sub> = 1.0W                |              | -60          |     | dB                |

| Total Harmonic Distortion                                     | THD    | Po = 0.5W                            |              | -64          |     | dB                |

| Total Harmonic Distortion Plus<br>Noise                       | THD+N  | P <sub>o</sub> = 0.5W                |              | -63          |     | dB                |

| Channel separation (Left/Right)                               |        | Po = 0.5W                            |              | 85           |     | dB                |

| Output noise floor                                            |        | A-weighted                           |              | 30           |     | μV <sub>RMS</sub> |

| PSRR (DBVDDn, LDOVDD,                                         | PSRR   | 100mV (peak-peak) 217Hz              |              | 80           |     | dB                |

| CPVDD, AVDD)                                                  |        | 100mV (peak-peak) 10kHz              |              | 70           |     |                   |

| PSRR (SPKVDDL, SPKVDDR)                                       | PSRR   | 100mV (peak-peak) 217Hz              |              | 70           |     | dB                |

|                                                               |        |                                      |              |              |     |                   |

**Test Conditions**

The following electrical characteristics are valid across the full range of recommended operating conditions.

| PARAMETER                                                                                                                                                                                                           | SYMBOL                                                                                    | TEST CONDITIONS                                                                                  | MIN                                                           | TYP | MAX                                             | UNI                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----|-------------------------------------------------|-----------------------------------------------------------|

| Digital Input / Output (except DM<br>Digital I/O is referenced to DBVI<br>See "Recommended Operating                                                                                                                | DD1, DBVDD2 o                                                                             | or DBVDD3.                                                                                       | e range of eac                                                |     | domain                                          |                                                           |

| Input HIGH Level                                                                                                                                                                                                    |                                                                                           | $V_{DBVDDn} = 1.8V \pm 10\%$                                                                     |                                                               |     |                                                 | V                                                         |

|                                                                                                                                                                                                                     | VIH                                                                                       | V DBVDDn - 1.0V 11070                                                                            | V <sub>DBVDDn</sub>                                           |     |                                                 | v                                                         |

|                                                                                                                                                                                                                     |                                                                                           | VDBVDDn =3.3V ±10%                                                                               | 0.7 ×                                                         |     |                                                 |                                                           |

|                                                                                                                                                                                                                     |                                                                                           |                                                                                                  | V <sub>DBVDDn</sub>                                           |     |                                                 |                                                           |

| Input LOW Level                                                                                                                                                                                                     | VIL                                                                                       | $V_{DBVDDn}$ =1.8V ±10%                                                                          |                                                               |     | 0.35 ×                                          | V                                                         |

|                                                                                                                                                                                                                     |                                                                                           |                                                                                                  |                                                               |     | V <sub>DBVDDn</sub>                             |                                                           |

|                                                                                                                                                                                                                     |                                                                                           | $V_{DBVDDn}$ =3.3V ±10%                                                                          |                                                               |     | 0.3 ×                                           |                                                           |

|                                                                                                                                                                                                                     |                                                                                           |                                                                                                  |                                                               |     | V <sub>DBVDDn</sub>                             |                                                           |

| Note that digital input pins should                                                                                                                                                                                 | - T - T                                                                                   | •                                                                                                |                                                               |     | 1                                               |                                                           |

| Output HIGH Level                                                                                                                                                                                                   | V <sub>OH</sub>                                                                           | I <sub>ОН</sub> = 1mA                                                                            | 0.9 ×                                                         |     |                                                 | V                                                         |

| Output LOW Level                                                                                                                                                                                                    |                                                                                           | 1 - 1                                                                                            | V <sub>DBVDDn</sub>                                           |     | 0.1                                             | V                                                         |

|                                                                                                                                                                                                                     | Vol                                                                                       | l <sub>o∟</sub> = -1mA                                                                           |                                                               |     | 0.1 ×<br>V <sub>DBVDDn</sub>                    | v                                                         |