# NN31001A

http://www.semicon.panasonic.co.jp/en/

# 7 A Synchronous DC-DC Step down Regulator, Power Supply in Package $(V_{IN} = 4.5 \text{ V to } 28 \text{ V}, V_{OUT} = 0.6 \text{ V to } 5.5 \text{ V})$

#### FEATURES

- High-Speed Response DC-DC Step Down Regulator Circuit that employs Hysteretic Control System

- Built-in inductor and capacitors

- Skip (discontinuous) Mode for high efficiency at light load Maximum Output Current : 7 A

- Input Voltage Range : PVIN=AVIN = 4.5 V to 28 V, Output Voltage Range : 0.6 V to 5.5 V Selectable Switching Frequency 400 kHz / 600 kHz / 800kHz

- Built-in Feed Back Resistors for 1.0 V / 3.3 V default settings Configurable output voltage settings using external Resistors

- Adjustable Soft Start

- Low Operating and Standby Quiescent Current

- Open Drain Power Good Indication for Output Over / Under Voltage

- Selectable Auto recovery / latch off protection system

- Adjustable current limit threshold

- Built-in Under Voltage Lockout (UVLO), Thermal Shut Down (TSD), Under Voltage Detection (UVD), Over Voltage Detection (OVD), Short Circuit Protection (SCP) Over Current Protection (OCP)

- Plastic Quad Flat Non-leaded Package Heat Slug Down (QFN Type, Size : 8.5 mm × 7.5 mm, 0.5 mm pitch)

#### DESCRIPTION

NN31001A is a synchronous DC-DC step down regulator (1-ch), Power Supply in Package (PSiP), which integrates a Controller IC that employs a hysteretic control system, two Power MOSFETs, an Inductor and Capacitors into a single 8.5 x 7.5 x 4.7mm QFN package.

The easiness of mounting PSiP onto a Printed Circuit Board (PCB), a very small footprint and a highly reduced number of external components, offers very compact and simplified solutions for applications requiring pointof-load design.

The number of external components have been reduced to only input/output capacitor, slow start capacitor and feedback resistors.

Furthermore, for applications requiring an output voltage of 1.0 V / 3.3 V, the external feedback resistors can be eliminated, resulting into even a smaller footprint.

The PSiP achieves efficiencies of greater than 94% with very good power dissipation capabilities.

### APPLICATIONS

High Current Distributed Power Systems such as

- DSP and FPGA Point-of-Load Applications

- Routers

- Industrial Equipment

- · Space constrained Applications etc.

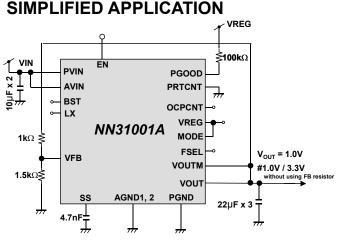

Note : The application circuit is an example. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit in the design of the equipment.

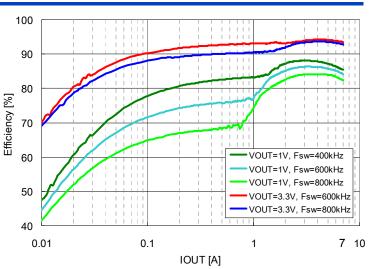

Condition :

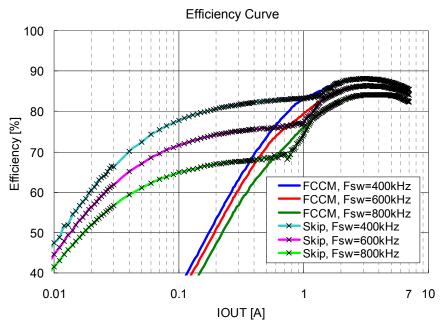

Vin = 12 V,  $V_{OUT}$  Setting = 1.0 V / 3.3 V Switching Frequency = 400 / 600 / 800 kHz, Skip mode Co = 66  $\mu$ F ( 22  $\mu$ F x 3 )

#### **ORDERING INFORMATION**

| Order Number | Feature                      | Package     | Output Supply |

|--------------|------------------------------|-------------|---------------|

| NN31001A-BB  | Maximum Output Current : 7 A | 57 pin HQFN | Emboss Taping |

#### **ABSOLUTE MAXIMUM RATINGS**

| Parameter                      | Symbol                                                                                                               | Rating                            | Unit | Notes    |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|-----------------------------------|------|----------|

| Supply voltage                 | V <sub>IN</sub>                                                                                                      | 30                                | V    | *1       |

| Operating free-air temperature | T <sub>opr</sub>                                                                                                     | – 40 to + 85                      | °C   | *2       |

| Operating junction temperature | Tj                                                                                                                   | – 40 to + 150                     | °C   | *2       |

| Storage temperature            | T <sub>stg</sub>                                                                                                     | – 55 to + 150                     | °C   | *2       |

| Input Voltage Range            | V <sub>MODE</sub> ,V <sub>FSEL</sub> ,V <sub>OUTM</sub> ,V <sub>PRTCNT</sub><br>V <sub>OCPCNT</sub> ,V <sub>FB</sub> | – 0.3 to (V <sub>REG</sub> + 0.3) | V    | *1<br>*3 |

|                                | V <sub>EN</sub>                                                                                                      | – 0.3 to 6.0                      | V    | *1       |

| Output Voltage Denge           | V <sub>PGOOD</sub>                                                                                                   | – 0.3 to (V <sub>REG</sub> + 0.3) | V    | *1<br>*3 |

| Output Voltage Range           | V <sub>LX</sub>                                                                                                      | – 0.3 to (V <sub>IN</sub> + 0.3)  | V    | *1<br>*4 |

| ESD                            | HBM                                                                                                                  | 2                                 | kV   | _        |

Notes : This product may sustain permanent damage if subjected to conditions higher than the above stated absolute maximum rating. This rating is the maximum rating and device operating at this range is not guaranteed as it is higher than our stated recommended operating range.

When subjected under the absolute maximum rating for a long time, the reliability of the product may be affected.  $V_{IN}$  is voltage for AVIN, PVIN.  $V_{IN} = AV_{IN} = PV_{IN}$ .

Do not apply external currents and voltages to any pin not specifically mentioned.

- \*1 : The values under the condition not exceeding the above absolute maximum ratings and the power dissipation.

- \*2 : Except for the power dissipation, operating ambient temperature, and storage temperature, all ratings are for T<sub>a</sub> = 25 °C.

\*3 :(V<sub>REG</sub> + 0.3) V must not exceed 6 V.

\*4 : (V<sub>IN</sub> + 0.3) V must not exceed 30 V.

## POWER DISSIPATION RATING

| Package                              | $\theta_{j\text{-}C}$ | PD<br>(Ta = 25 °C) | PD<br>(Ta = 85 °C) | Notes |

|--------------------------------------|-----------------------|--------------------|--------------------|-------|

| Plastic Quad Flat Non-leaded Package | 6.7 °C / W            | 3.49 W             | 1.82 W             | *1    |

| Heat Slug Down (QFN Type)            | 5.7 °C / W            | 5.56 W             | 2.89 W             | *2    |

Notes : For the actual usage, please follow the power supply voltage, load and ambient temperature conditions to ensure that there is enough margin and the thermal design does not exceed the allowable value.

\*1:Glass Epoxy Substrate (4 Layers) [50  $\times$  50  $\times$  0.8 t (mm)]

\*2:Glass Epoxy Substrate (4 Layers) [50  $\times$  50  $\times$  1.57 t (mm)]

### CAUTION

Although this IC has built-in ESD protection circuit, it may still sustain permanent damage if not handled properly. Therefore, proper ESD precautions are recommended to avoid electrostatic damage to the MOS gates.

## **RECOMMENDED OPERATING CONDITIONS**

| Parameter            | Symbol              | Min   | Тур | Max                    | Unit | Notes |

|----------------------|---------------------|-------|-----|------------------------|------|-------|

|                      | AV <sub>IN</sub>    | 4.5   | 12  | 28                     | V    | —     |

| Supply voltage range | PV <sub>IN</sub>    | 4.5   | 12  | 28                     | V    | —     |

|                      | V <sub>MODE</sub>   | - 0.3 | _   | V <sub>REG</sub> + 0.3 | V    | *1    |

| Input Voltage Denge  | $V_{FSEL}$          | - 0.3 | _   | V <sub>REG</sub> + 0.3 | V    | *1    |

| Input Voltage Range  | V <sub>PRTCNT</sub> | - 0.3 | _   | V <sub>REG</sub> + 0.3 | V    | *1    |

|                      | V <sub>EN</sub>     | - 0.3 | _   | 5.0                    | V    |       |

|                      | V <sub>PGOOD</sub>  | - 0.3 | —   | V <sub>REG</sub> + 0.3 | V    | *1    |

| Output Voltage Range | $V_{LX}$            | - 0.3 | _   | V <sub>IN</sub> + 0.3  | V    | *2    |

Notes : Voltage values, unless otherwise specified, are with respect to GND.

GND is voltage for AGND, PGND. AGND = PGND

$V_{IN}$  is voltage for AVIN, PVIN.  $V_{IN}$  = AV<sub>IN</sub> = PV<sub>IN</sub>.

Do not apply external currents or voltages to any pin not specifically mentioned.

\*1 : ( $V_{REG}$  + 0.3) V must not exceed 6 V.

\*2 : ( $V_{IN}$  + 0.3) V must not exceed 30 V.

### **ELECTRICAL CHARACTERISTICS**

$C_{O}$  = 22 µF × 3,  $V_{OUT}$  Setting = 1.0 V,  $V_{IN}$  = A $V_{IN}$  = P $V_{IN}$  = 12 V, Switching Frequency = 600 kHz  $V_{MODE}$  =  $V_{REG}$  (FCCM),  $T_{a}$  = 25 °C ± 2 °C unless otherwise noted.

| Deveneter                                     | Currential | Condition                                                                                                                                                                                                                                                     |                           | Limits |                             | Linit | Nata |

|-----------------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--------|-----------------------------|-------|------|

| Parameter                                     | Symbol     | Condition                                                                                                                                                                                                                                                     | Min                       | Тур    | Max                         | Unit  | Note |

| Current Consumption                           |            |                                                                                                                                                                                                                                                               |                           |        |                             | i     |      |

| Current Consumption at active1<br>(Skip mode) | Ivddactni  | $\begin{split} I_{OUT} &= 0 \text{ A},  \text{V}_{\text{FB}} = 0.620 \text{ V} \\ R_{\text{FB1}} &= 1.0  \text{k} \Omega \\ R_{\text{FB2}} &= 1.5  \text{k} \Omega \\ \text{V}_{\text{MODE}} &= 0 \text{ V},  \text{V}_{\text{EN}} = 5 \text{ V} \end{split}$ | _                         | 700    | 1200                        | μA    | —    |

| Current Consumption at active2<br>(FCCM)      | Ivddactn2  | $V_{EN} = 5 V, I_{OUT} = 0 A$ $R_{FB1} = 1.0 k\Omega$ $R_{FB2} = 1.5 k\Omega$ $V_{MODE} = V_{REG}$ $V_{FSEL} = OPEN$                                                                                                                                          | _                         | 15     | 23                          | mA    | _    |

| AVIN/PVIN Current Consumption at standby      | Ivinstb    | AV <sub>IN</sub> = PV <sub>IN</sub> = 12 V<br>V <sub>EN</sub> = 0 V                                                                                                                                                                                           | _                         | 2      | 5                           | μA    | —    |

| Logic Pin Characteristics                     | -          |                                                                                                                                                                                                                                                               |                           |        |                             |       |      |

| EN pin Low-level input voltage                | VENL       | _                                                                                                                                                                                                                                                             | _                         | _      | 0.3                         | V     | —    |

| EN pin High-level input voltage               | Venh       | —                                                                                                                                                                                                                                                             | 1.5                       |        | 5.0                         | V     | —    |

| EN pin leakage current                        | ILEAKEN    | V <sub>EN</sub> = 5 V                                                                                                                                                                                                                                         | —                         | 10     | 20                          | μA    | —    |

| MODE pin Low-level input voltage              | VMODEL     | —                                                                                                                                                                                                                                                             | —                         | _      | $V_{\text{REG}} \times 0.3$ | V     | —    |

| MODE pin High-level input voltage             | Vmodeh     | _                                                                                                                                                                                                                                                             | $V_{REG} 	imes 0.7$       | _      | $V_{REG}$                   | V     | _    |

| MODE pin leakage current                      | ILEAKMD    | V <sub>MODE</sub> = 5 V                                                                                                                                                                                                                                       | _                         | 12.5   | 25                          | μA    |      |

| PRTCNT pin Low-level input voltage            | Vprtl      | _                                                                                                                                                                                                                                                             | _                         | _      | 0.3                         | V     | —    |

| PRTCNT pin High-level input voltage           | Vprth      | _                                                                                                                                                                                                                                                             | V <sub>REG</sub><br>- 0.3 | _      | _                           | V     | —    |

| PRTCNT pin leakage current                    | ILEAKPRT   | $V_{\rm EN}$ = 5 V, $V_{\rm PRTCNT}$ = 5 V                                                                                                                                                                                                                    |                           | 0      | 2                           | μA    |      |

| FSEL pin Low-level input voltage              | VFSELL     | —                                                                                                                                                                                                                                                             | _                         | _      | 0.3                         | V     | _    |

| FSEL pin High-level input voltage             | Vfselh     | —                                                                                                                                                                                                                                                             | V <sub>REG</sub><br>- 0.3 | _      | _                           | V     |      |

| FSEL pin High leakage current                 | ILEAKFSH   | V <sub>FSEL</sub> = 5 V                                                                                                                                                                                                                                       | _                         | 6.25   | 12.5                        | μA    | —    |

| FSEL pin Low leakage current                  | ILEAKFSL   | V <sub>FSEL</sub> = 0 V                                                                                                                                                                                                                                       | _                         | 6.25   | 12.5                        | μA    | —    |

### **ELECTRICAL CHARACTERISTICS (Continued)**

$C_{O}$  = 22 µF × 3,  $V_{OUT}$  Setting = 1.0 V,  $V_{IN}$  = A $V_{IN}$  = P $V_{IN}$  = 12 V, Switching Frequency = 600 kHz  $V_{MODE}$  =  $V_{REG}$  (FCCM),  $T_{a}$  = 25 °C ± 2 °C unless otherwise noted.

| Deserveter                                                   | Currence al       | Condition                                                                                |       | Limits |       | Linit | Nata |

|--------------------------------------------------------------|-------------------|------------------------------------------------------------------------------------------|-------|--------|-------|-------|------|

| Parameter                                                    | Symbol Condition  |                                                                                          | Min   | Тур    | Max   | Unit  | Note |

| VREG Characteristics                                         |                   |                                                                                          |       |        |       |       |      |

| Output voltage                                               | Vrego             | I <sub>VREG</sub> = 5mA                                                                  | 5.3   | 5.6    | 5.9   | V     | _    |

| Input voltage variation                                      | Vreglin           | $V_{REGLIN} = V_{REG} (V_{IN} = 12 V)$<br>- $V_{REG} (V_{IN} = 6 V)$<br>$I_{VREG} = 5mA$ |       |        | 150   | mV    | _    |

| Drop out voltage                                             | Vregdo            | V <sub>IN</sub> = 4.5 V, I <sub>VREG</sub> = 5mA                                         | 4.1   | _      | _     | V     | —    |

| VFB Characteristics                                          |                   |                                                                                          |       |        |       |       |      |

| VFB comparator threshold                                     | Vfbth             | —                                                                                        | 0.594 | 0.600  | 0.606 | V     |      |

| VFB pin leakage current 1                                    | LEAKFB1           | V <sub>FB</sub> = 0 V                                                                    | – 1   | _      | 1     | μA    | _    |

| VFB pin leakage current 2                                    | LEAKFB2           | V <sub>FB</sub> = 6 V                                                                    | – 1   | _      | 1     | μA    | _    |

| Under Voltage Lock Out                                       |                   |                                                                                          |       |        |       |       |      |

| UVLO shutdown voltage                                        | VUVLODE           | V <sub>IN</sub> = 5 V to 0 V                                                             | 3.97  | 4.10   | 4.23  | V     |      |

| UVLO wakeup voltage                                          | VUVLORE           | $V_{IN} = 0 V \text{ to } 5 V$                                                           | 4.17  | 4.30   | 4.43  | V     |      |

| UVLO hysteresis                                              | $\Delta V_{UVLO}$ | -                                                                                        | 150   | 200    | 250   | mV    | _    |

| PGOOD                                                        | 1                 |                                                                                          |       |        |       |       |      |

| PGOOD Threshold 1<br>(VFB ratio for UVD detect)              | Vpguv             | PGOOD : High to Low                                                                      | 77    | 85     | 93    | %     |      |

| PGOOD Hysteresis 1<br>(VFB ratio for UVD release)            | $\Delta V_{PGUV}$ | PGOOD : Low to High                                                                      | 3.5   | 5.0    | 6.5   | %     |      |

| PGOOD Threshold 2<br>(VFB ratio for OVD detect)              | Vpgov             | PGOOD : High to Low                                                                      | 107   | 115    | 123   | %     |      |

| PGOOD Hysteresis 2<br>(VFB ratio for OVD release)            | $\Delta V_{PGOV}$ | PGOOD : Low to High                                                                      | 3.5   | 5.0    | 6.5   | %     | _    |

| PGOOD start up delay time ( After reached $V_{FB}$ = 0.6 V ) | Tpgd              | _                                                                                        | 0.4   | 1.0    | 1.6   | ms    | —    |

| PGOOD ON resistance                                          | R <sub>PG</sub>   | -                                                                                        | _     | 10     | 15    | Ω     | —    |

### **ELECTRICAL CHARACTERISTICS (Continued)**

$C_{O}$  = 22 µF × 3,  $V_{OUT}$  Setting = 1.0 V,  $V_{IN}$  = A $V_{IN}$  = P $V_{IN}$  = 12 V, Switching Frequency = 600 kHz  $V_{MODE}$  =  $V_{REG}$  (FCCM),  $T_{a}$  = 25 °C ± 2 °C unless otherwise noted.

| Deveneter             | Queebal          | Condition                                                                                                                              |       | Limits |       | Llpit | Nata |  |

|-----------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------|-------|--------|-------|-------|------|--|

| Parameter             | Symbol Condition |                                                                                                                                        | Min   | Тур    | Max   | Unit  | Note |  |

| DC-DC Characteristics |                  |                                                                                                                                        |       |        |       |       |      |  |

| Output voltage 1      | V <sub>01</sub>  | $R_{FB1}$ = 1.0 kΩ<br>$R_{FB2}$ = 1.5 kΩ<br>$V_{MODE}$ = $V_{REG}$<br>$I_{OUT}$ = 3.5 A                                                | 0.985 | 1.000  | 1.015 | V     |      |  |

| Output voltage 2      | V <sub>02</sub>  | $R_{FB1} = 4.5 \text{ k}\Omega$ $R_{FB2} = 1 \text{ k}\Omega$ $V_{MODE} = V_{REG}$ $I_{OUT} = 3.5 \text{ A}$                           | 3.250 | 3.300  | 3.350 | v     |      |  |

| Output voltage 3      | V <sub>03</sub>  | $V_{FB}$ = OPEN<br>before $V_{EN}$ = 0 V to 1.5 V<br>$V_{MODE}$ = $V_{REG}$<br>$I_{OUT}$ = 3.5 A                                       | 0.985 | 1.000  | 1.015 | V     |      |  |

| Output voltage 4      | Vo4              | $V_{FB} = V_{REG}$<br>before $V_{EN} = 0$ V to 1.5 V<br>$V_{MODE} = V_{REG}$<br>$I_{OUT} = 3.5$ A                                      | 3.250 | 3.300  | 3.350 | V     | _    |  |

| Efficiency 1          | Veff1            | $\begin{aligned} PV_{IN} &= 12 \ V \\ V_{OUT} &= 5 \ V, \ I_{OUT} &= 4 \ A \\ V_{FSEL} &= V_{REG} \ ( \ 800kHz \ ) \end{aligned}$      |       | 95     | _     | %     | *1   |  |

| Efficiency 2          | Veff2            | PV <sub>IN</sub> = 12 V<br>V <sub>OUT</sub> = 3.3 V, I <sub>OUT</sub> = 4 A<br>V <sub>FSEL</sub> = OPEN ( 600kHz )                     | _     | 95     | _     | %     | *1   |  |

| Efficiency 3          | Veff3            | $PV_{IN} = 12 V$<br>$V_{OUT} = 3.3 V$ , $I_{OUT} = 4 A$<br>$V_{FSEL} = V_{REG} (800 \text{kHz})$                                       | _     | 94     | _     | %     | *1   |  |

| Efficiency 4          | Veff4            | PV <sub>IN</sub> = 12 V<br>V <sub>OUT</sub> = 1.0 V, I <sub>OUT</sub> = 4 A<br>V <sub>FSEL</sub> = 0 V (400kHz)                        | _     | 88     | _     | %     | *1   |  |

| Efficiency 5          | Veff5            | PV <sub>IN</sub> = 12 V<br>V <sub>OUT</sub> = 1.0 V, I <sub>OUT</sub> = 4 A<br>V <sub>FSEL</sub> = OPEN ( 600kHz )                     | _     | 87     | _     | %     | *1   |  |

| Efficiency 6          | Veff6            | $\begin{array}{l} PV_{IN} = 12 \ V \\ V_{OUT} = 1.0 \ V, \ I_{OUT} = 4 \ A \\ V_{FSEL} = V_{REG} \ ( \ 800 \text{kHz} \ ) \end{array}$ | _     | 85     |       | %     | *1   |  |

Note : \*1 : Typical design value

### **ELECTRICAL CHARACTERISTICS (Continued)**

$C_{O}$  = 22 µF × 3,  $V_{OUT}$  Setting = 1.0 V,  $V_{IN}$  = A $V_{IN}$  = P $V_{IN}$  = 12 V, Switching Frequency = 600 kHz  $V_{MODE}$  =  $V_{REG}$  (FCCM),  $T_{a}$  = 25 °C ± 2 °C unless otherwise noted.

| Parameter                                   | Symbol            | condition                                                                                                                          |     | Limits  |     |             | Note |

|---------------------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------|-----|---------|-----|-------------|------|

| Parameter                                   | Symbol            | Condition                                                                                                                          | Min | Typ Max |     | Unit        | note |

| DC-DC Characteristics                       |                   |                                                                                                                                    |     |         |     |             |      |

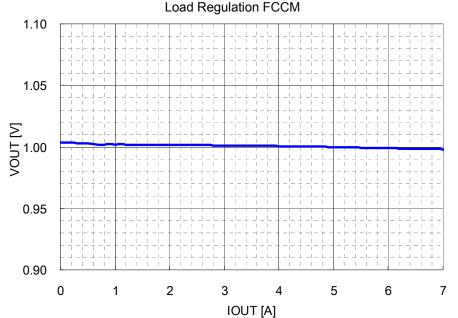

| Load regulation1                            | VLOA1             | $I_{OUT}$ = 10 mA to 7 A<br>$V_{MODE}$ = 0 V                                                                                       | _   | 2.0     | —   | %           | *1   |

| Load regulation2                            | Vloa2             | $I_{OUT}$ = 10 mA to 7 A<br>$V_{MODE}$ = $V_{REG}$                                                                                 | _   | 1.0     | —   | %           | *1   |

| Line regulation                             | VLIN              | $PV_{IN} = 6 V \text{ to } 28 V$ $V_{MODE} = V_{REG}$ $I_{OUT} = 2.0 \text{ A}$                                                    |     | 0.1     | 0.3 | %/V         | _    |

| Output ripple voltage 1                     | V <sub>RL1</sub>  | I <sub>OUT</sub> = 10 mA<br>V <sub>MODE</sub> = 0 V                                                                                | —   | 30      | —   | mV<br>[p-p] | *1   |

| Output ripple voltage 2                     | V <sub>RL2</sub>  | I <sub>OUT</sub> = 10 mA<br>V <sub>MODE</sub> = V <sub>REG</sub>                                                                   | —   | 15      | —   | mV<br>[p-p] | *1   |

| Output ripple voltage 3                     | V <sub>RL3</sub>  | I <sub>OUT</sub> = 3.5 A<br>V <sub>MODE</sub> = V <sub>REG</sub>                                                                   | _   | 10      | —   | mV<br>[p-p] | *1   |

| Load transient response 1                   | $\Delta V_{TR1}$  | $I_{OUT} = 100 \text{ mA to } 3.5 \text{ A}$<br>$\Delta t = 0.5 \text{ A} / \mu \text{s}$<br>$V_{MODE} = 0 \text{ V or } V_{REG}$  |     | 15      | _   | mV          | *1   |

| Load transient response 2                   | $\Delta V_{TR2}$  | $I_{OUT} = 3.5 \text{ A to } 100 \text{ mA}$<br>$\Delta t = 0.5 \text{ A / } \mu \text{s}$<br>$V_{MODE} = 0 \text{ V or } V_{REG}$ |     | 20      | _   | mV          | *1   |

| Minimum Input and output voltage difference | V <sub>DIFF</sub> | $V_{DIFF} = V_{IN} - V_{OUT}$                                                                                                      | _   | 2.5     | _   | V           | *1   |

Note : \*1 : Typical design value

## **ELECTRICAL CHARACTERISTICS (Continued)**

$C_{O}$  = 22 µF × 3,  $V_{OUT}$  Setting = 1.0 V,  $V_{IN}$  = A $V_{IN}$  = P $V_{IN}$  = 12 V, Switching Frequency = 600 kHz  $V_{MODE}$  =  $V_{REG}$  (FCCM),  $T_{a}$  = 25 °C ± 2 °C unless otherwise noted.

| Deventer                                 | Queebal             | Condition                                                    |     | Limits  |    | Linit  | Nata |

|------------------------------------------|---------------------|--------------------------------------------------------------|-----|---------|----|--------|------|

| Parameter                                | Symbol Condition –  |                                                              | Min | Тур Мах |    | - Unit | Note |

| Protection                               |                     |                                                              |     |         |    |        |      |

| DC-DC Over Current<br>Protection Limit 1 | ILMT1               | OCPCNT=OPEN                                                  | —   | 9.0     | _  | А      | *1   |

| DC-DC Over Current<br>Protection Limit 2 | Ilmt2               | OCPCNT=220 kΩ                                                | _   | 7.0     | _  | A      | *1   |

| DC-DC Over Current<br>Protection Limit 3 | Іімтз               | OCPCNT=100 kΩ                                                |     | 4.7     | _  | А      | *1   |

| Thermal Shut Down (TSD)<br>Threshold     | T <sub>TSDTH</sub>  | _                                                            | _   | 130     | _  | °C     | *1   |

| Thermal Shut Down (TSD)<br>Hysteresis    | T <sub>TSDHYS</sub> | _                                                            | _   | 30      | _  | °C     | *1   |

| Soft-Start Timing                        |                     |                                                              |     |         |    |        |      |

| SS Charge Current                        | Isschg              | V <sub>SS</sub> = 0.3 V                                      | 1   | 2       | 4  | μA     | —    |

| SS Discharge Resistance (Shut-down)      | Rssdis              | V <sub>EN</sub> = 0 V                                        |     | 5       | 10 | kΩ     |      |

| Switching Frequency Adjustment           |                     |                                                              |     |         |    |        |      |

| DC-DC Switching Frequency 1              | Fsw1                | I <sub>OUT</sub> = 4 A, V <sub>FSEL</sub> = 0 V              |     | 400     |    | kHz    | *1   |

| DC-DC Switching Frequency 2              | Fsw2                | I <sub>OUT</sub> = 4 A, V <sub>FSEL</sub> = OPEN             |     | 600     |    | kHz    | *1   |

| DC-DC Switching Frequency 3              | Fsw3                | I <sub>OUT</sub> = 4 A, V <sub>FSEL</sub> = V <sub>REG</sub> |     | 800     |    | kHz    | *1   |

Note : \*1 : Typical design value

# NN31001A

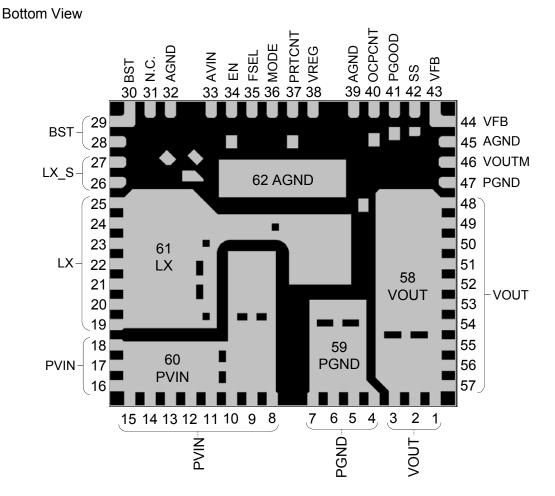

#### **PIN CONFIGURATION**

#### **PIN FUNCTIONS**

| Pin No. | Pin name | Туре   | Description        |

|---------|----------|--------|--------------------|

| 1       |          |        |                    |

| 2       |          |        |                    |

| 3       |          |        |                    |

| 48      |          |        |                    |

| 49      |          |        |                    |

| 50      |          |        |                    |

| 51      | VOUT     | Output | Output voltage pin |

| 52      |          |        |                    |

| 53      |          |        |                    |

| 54      |          |        |                    |

| 55      |          |        |                    |

| 56      |          |        |                    |

| 57      |          |        |                    |

Note : Detailed pin descriptions are provided in the OPERATION and APPLICATION INFORMATION section.

## **PIN FUNCTIONS (Continued)**

| Pin No.  | Pin name | Туре         | Description                                                                                                                                               |                                                                 |  |  |       |

|----------|----------|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|-------|

| 4        |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 5        |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 6        | PGND     | Ground       | Ground pin for Power MOSFET<br>* Pin No. 47 : recommended settings – no connection                                                                        |                                                                 |  |  |       |

| 7        |          |              | Fin No. 47 : recommended settings – no connection                                                                                                         |                                                                 |  |  |       |

| 47       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 8        |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 9        |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 10       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 11       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 12       |          | Power        | Power supply pin for Power MOSFET                                                                                                                         |                                                                 |  |  |       |

| 13       | PVIN     | supply       | Recommended rise time ( time to reach 90 % of set value ) setting is                                                                                      |                                                                 |  |  |       |

| 14       |          |              | greater than or equal to 10 $\mu$ s and less than or equal to 1 s.                                                                                        |                                                                 |  |  |       |

| 15       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 16       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 17       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 18       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 19       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 20       |          | Output       | Output                                                                                                                                                    | Power MOSFET output pin                                         |  |  |       |

| 21<br>22 | LX       |              |                                                                                                                                                           | An inductor is connected and switching operation is carried out |  |  |       |

| 22       | LA       |              | between V <sub>IN</sub> and GND.                                                                                                                          |                                                                 |  |  |       |

| 23       |          |              |                                                                                                                                                           |                                                                 |  |  | * Pin |

| 25       |          |              |                                                                                                                                                           |                                                                 |  |  |       |

| 26       |          |              | Power MOSFET output sense pin                                                                                                                             |                                                                 |  |  |       |

| 20       | LX_S     | Output       | * Pin No. 26 to 27 : recommended settings – no connection                                                                                                 |                                                                 |  |  |       |

| 28       |          |              | High side Power MOSFET gate driver pin                                                                                                                    |                                                                 |  |  |       |

| 29       | BST      | Output       | Bootstrap operation is carried out in order to drive the gate voltage of High                                                                             |                                                                 |  |  |       |

| 30       | 100      | στιραί       | side Power MOSFET.                                                                                                                                        |                                                                 |  |  |       |

|          | NO       |              | * Pin No. 28 to 30 : recommended settings – no connection                                                                                                 |                                                                 |  |  |       |

| 31       | NC       | -            | Non Connection pin                                                                                                                                        |                                                                 |  |  |       |

| 32       |          | O manus d    | Cround him                                                                                                                                                |                                                                 |  |  |       |

| 39       | AGND     | Ground       | Ground pin                                                                                                                                                |                                                                 |  |  |       |

| 45       |          |              | Power outpoly pin                                                                                                                                         |                                                                 |  |  |       |

| 33       | AVIN     | Power supply | Power supply pin<br>Recommended rise time ( time to reach 90 % of set value ) setting is<br>greater than or equal to 10 µs and less than or equal to 1 s. |                                                                 |  |  |       |

| 34       | EN       | Input        | ON / OFF control pin<br>DC-DC is stopped at Low level input, and it is started at High level input.                                                       |                                                                 |  |  |       |

Note : Detailed pin descriptions are provided in the OPERATION and APPLICATION INFORMATION section.

## **PIN FUNCTIONS (Continued)**

| Pin No. | Pin name | Туре            | Description                                                                                                                                                                                                                                                         |

|---------|----------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35      | FSEL     | Input           | Frequency select pin<br>This is set to 400 kHz at Low level input, 800 kHz at High level input,<br>and 600 kHz at open.                                                                                                                                             |

| 36      | MODE     | Input           | Skip (discontinuous) mode / FCCM (Forced Continuous Conduction Mode)<br>select pin<br>Skip mode is set at Low level input, FCCM is set at High level input.                                                                                                         |

| 37      | PRTCNT   | Input           | Protection Control Set pin for Latch mode / Auto recovery mode during OVD / SCP operations                                                                                                                                                                          |

| 38      | VREG     | Output          | LDO output pin<br>This is Output pin of Power supply (LDO) for internal control circuit.                                                                                                                                                                            |

| 40      | OCPCNT   | Input           | Programmable over-current protection. Connected resistor on this pin will adjust the over-current protection threshold.                                                                                                                                             |

| 41      | PGOOD    | Output          | Power good open drain pin<br>A pull up resistor between PGOOD and V <sub>REG</sub> terminal is necessary.<br>Output is low during Over or Under Voltage Detection conditions.                                                                                       |

| 42      | SS       | Output          | Soft start capacitor connect pin<br>The output voltage at a start up is smoothly controlled<br>by adjusting Soft Start time.<br>Please connect capacitor between SS and GND.                                                                                        |

| 43      | VFB      | Input           | Comparator negative input pin / 1.0 V, 3.3 V output voltage select pin<br>VFB terminal voltage is regulated to REF output (internal reference voltage).<br>Since VFB is a high impedance terminal, it should not be routed near<br>other noisy path (LX, BST, etc.) |

| 44      |          |                 | Routing path should be kept as short as possible.                                                                                                                                                                                                                   |

| 46      | VOUTM    | Input           | Output voltage sense pin<br>Switching frequency is controlled by monitoring output voltage.<br>This pin is also used as Feedback pin during internal feedback function.                                                                                             |

| 58      | VOUT     | Output          | Voltage output pin for heat radiation                                                                                                                                                                                                                               |

| 59      | PGND     | Ground          | Ground pin of Power MOSFET for heat radiation                                                                                                                                                                                                                       |

| 60      | PVIN     | Power<br>supply | Power supply pin for heat radiation                                                                                                                                                                                                                                 |

| 61      | LX       | Output          | Power MOSFET output pin for heat radiation                                                                                                                                                                                                                          |

| 62      | AGND     | Ground          | Ground pin for heat radiation                                                                                                                                                                                                                                       |

Note : Detailed pin descriptions are provided in the OPERATION and APPLICATION INFORMATION section.

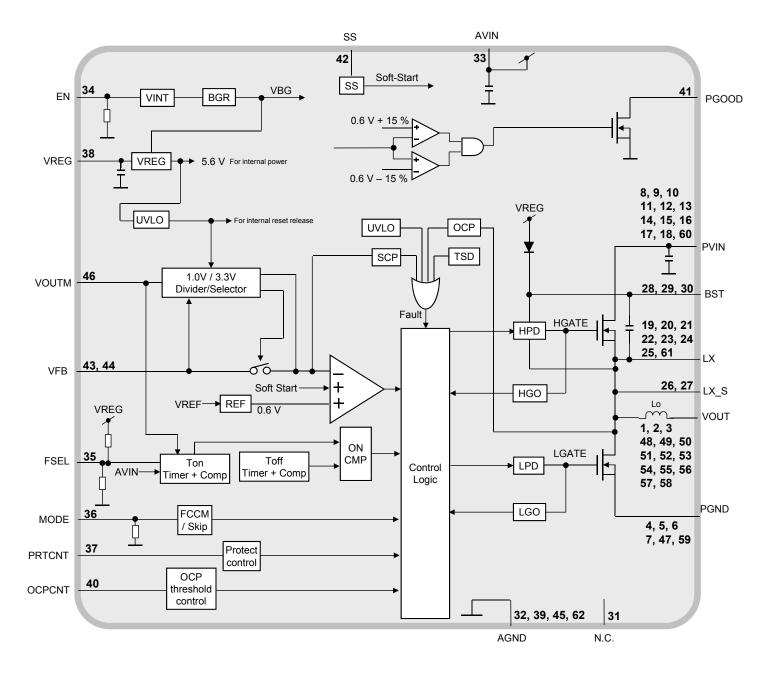

## FUNCTIONAL BLOCK DIAGRAM

Note : This block diagram is for explaining functions. Part of the block diagram may be omitted, or it may be simplified.

### OPERATION

### 1. Protection

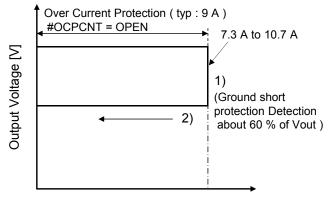

#### (1) Output Over-Current Protection (OCP) function And Short-Circuit Protection (SCP) function

The Over Current Protection is activated at about 9 A (Typ.) when OCPCNT pin is set to open. This device uses pulse – by – pulse valley current protection method. When the low side MOSFET is turned on, the voltage across the drain and source is monitored which is proportional to the inductor current. The high side MOSFET is only allowed to turn on when the current flowing in the low side MOSFET falls below the OCP level. Hence, during the OCP, the output voltage continues to drop at the specified current.

Output current [A] Figure : OCP and SCP Operation

Note: PRTCNT = V<sub>REG</sub> ( SCP latch off mode )

- 2) The Over Current Protection threshold level can be programmed by connecting a pull down resistor at OCPCNT pin. The value of the resistor connected between OCPCNT pin and ground will determine the OCP threshold level.

- Note: The OCP level is fixed to around 0.7 A when OCPCNT pin is connected to Ground.

| OCP level ( typ ) | OCPCNT resistor               |  |

|-------------------|-------------------------------|--|

| 9 A               | OPEN ( more than $1M\Omega$ ) |  |

| 7 A               | <b>220 k</b> Ω                |  |

| 4.7 A             | 100 kΩ                        |  |

Table : OCP threshold level

The accuracy of OCP level is around  $\pm$  20 % of the typical value in the above table.

OCP level with resistor at OCPCNT pin (  $R_{\text{OCP}}$  ) can be calculated by the following approximate equation.

OCP level[A] =

$$9 - \frac{435}{R_{OCP}[k\Omega]}$$

Note: R<sub>OCP</sub> is recommended to be more than 100 kΩ.

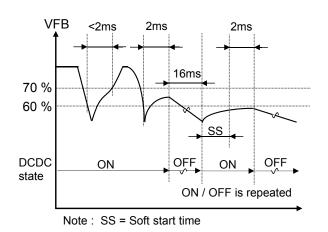

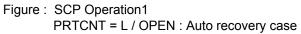

The Short-Circuit Protection function is implemented when the output voltage decreases and the VFB pin reaches to about 60 % of the set voltage of 0.6 V. If the VFB voltage stays below 70 % of 0.6 V for more than 250 µs after SCP triggers, both high side and low side MOSFET will be turned off and the output will be discharged by internal MOS transistor. (The above operation after SCP triggered is at latch off mode. The details are described in the next page)

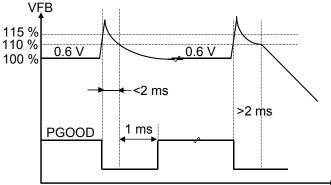

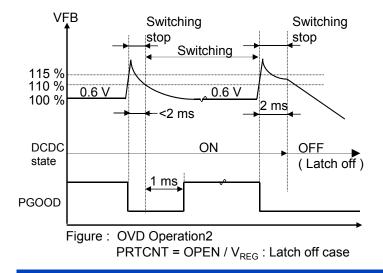

#### (2) Output Over Voltage Detection

If the VFB pin voltage exceeds 115 % of a predetermined value (0.6 V) and lasts more than 10ns, overvoltage detection will be triggered and PGOOD pin will be pulled down. Furthermore, in an overvoltage condition, high side and low side MOSFETs are turned off to stop PWM operation. If the VFB pin voltage drops below 110 % of the predetermined value (0.6 V) within 2 ms after overvoltage detection triggers, PGOOD pin will be pulled up again and PWM operation will resume. Otherwise, IC is transferred to latch off state and the output will be discharged by internal MOS transistor. (The above operation after OVD triggered is at latch off mode. The details are described in the next page)

Figure : OVD Operation Note: PRTCNT = V<sub>REG</sub> ( OVD latch off mode )

#### (3) Output discharging function

When EN is low, the output is discharged by an internal MOSFET transistor.

When EN is high, if the controller is turned off either by Under Voltage Lock Out (UVLO), Over Voltage Detection (OVD) or Short Circuit Protection (SCP), the output is discharged by an internal MOSFET transistor. The ON-resistance of the internal MOSFET transistor is about 35  $\Omega$ .

# NN31001A

## **OPERATION** (Continued)

#### 1. Protection (Continued)

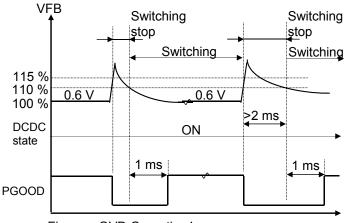

#### (4) Protection control (PRTCNT) function

The IC turn-off operation after Over Voltage Detection and Short Circuit Protection can be programmed by PRTCNT pin voltage. Changing the input level of PRTCNT will select Latch off and Auto recovery mode for OVD and SCP operations. The following table and figures represents detailed explanation of this function.

After latch off detection, power reset or EN pin reset is necessary to activate the device again.

| PRTCNT           | OVD operation | SCP operation |  |

|------------------|---------------|---------------|--|

| L                | Auto recovery |               |  |

| OPEN             | Latch off     | Auto recovery |  |

| V <sub>REG</sub> | Latch off     |               |  |

Table : PRTCNT pin threshold level and protection mode

PRTCNT =  $V_{REG}$  : Latch off case

# NN31001A

### **OPERATION** (Continued)

#### 1. Protection (Continued)

#### (5) Output Under Voltage Detection (UVD)

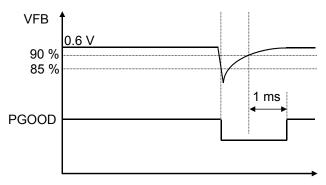

During normal operation, if output voltage drops and VFB pin voltage reaches 85 % of its set value (0.6 V), the internal MOSFET connected to PGOOD pin, will turn on and the voltage of PGOOD will be set to low. If the output voltage returns to 90 % of its set value (0.6 V) prior to triggering short-circuit-protection, the MOSFET connected to PGOOD pin will turn off and PGOOD voltage will become high again after 1 ms delay.

Figure : UVD Operation

#### (6) Thermal Shut Down (TSD)

When the IC internal temperature becomes more than about 130  $^\circ\text{C},$  TSD operates and DC-DC turns off.

#### 2. Pin Setting

#### (1) Operating MODE Setting

The IC can operate at two different modes : Skip (discontinuous) mode and Forced Continuous Conduction Mode (FCCM).

In Skip mode, the IC is working under pulse skipping mechanism to improve efficiency at light load condition. In FCCM, the IC is working at fixed frequency to avoid EMI issues.

The operating mode can be set by MODE pin as follows.

| MODE pin         | Mode      |

|------------------|-----------|

| L                | Skip mode |

| V <sub>REG</sub> | FCCM      |

#### (2) Switching Frequency Setting

The IC can operate at three different frequencies : 400 kHz, 600kHz and 800 kHz.

The Switching Frequency can be set by FSEL pin as indicated in the table below.

| FSEL pin         | Frequency [kHz] |  |  |

|------------------|-----------------|--|--|

| L                | 400             |  |  |

| OPEN             | 600             |  |  |

| V <sub>REG</sub> | 800             |  |  |

Inductor current amplitude is calculated by the following equation ;

Inductor Current Amplitude[A] =

$$\frac{V_{OUT}(V_{IN} - V_{OUT})}{V_{IN}} \times \frac{1000}{F_{sw}[kHz]}$$

At  $V_{IN}$  = 12 V, the recommended settings for the switching frequency, depending on  $V_{OUT}$  is as follows :

V<sub>OUT</sub> = 1.0V : 400, 600, 800 kHz V<sub>OUT</sub> = 1.8V : 400, 600, 800 kHz V<sub>OUT</sub> = 3.3V : 600, 800 kHz V<sub>OUT</sub> = 5.0V : 800 kHz

### **OPERATION** (Continued)

#### 3. Output Voltage Setting

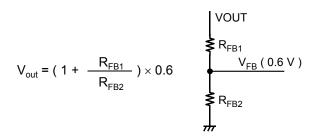

#### (1) Output Voltage setting by external resistor

The Output Voltage can be set by external resistance of FB pin, and its calculation is as follows. Below resistors are recommended for following popular output voltage

| V <sub>OUT</sub> <b>[V]</b> | R <sub>FB1</sub> [Ω] | R <sub>FB2</sub> [Ω] |

|-----------------------------|----------------------|----------------------|

| 5.0                         | 11 k                 | 1.5 k                |

| 3.3                         | 4.5 k                | 1 k                  |

| 1.8                         | 2 k                  | 1 k                  |

| 1.2                         | 1 k                  | 1 k                  |

| 1.0                         | 1 k                  | 1.5 k                |

VFB comparator threshold is adjusted to  $\pm$  1 %, but the actual output voltage accuracy becomes more than  $\pm$  1 % due to the influence from the circuits other than VFB comparator.

In the case of VOUT Setting = 1.0 V, the actual output voltage accuracy becomes  $\pm$  1.5 %.

(  $V_{IN}$  = 12 V,  $I_{OUT}$  = 3.5 A, Fsw = 600 kHz, FCCM ).

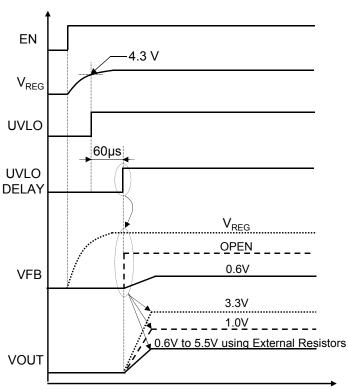

#### (2) Built-in Feed Back Resistors for 1.0 V / 3.3 V

NN31001A has built-in feedback resistors for 1.0 V and 3.3 V output voltage.

When the UVLO delay (internal) signal changes from Low to High (UVLO release), depending on the state of FB pin, the output voltage can be configured as follows :

| Table : Output voltage setting     |                    |  |  |

|------------------------------------|--------------------|--|--|

| VFB voltage [V] Output voltage [V] |                    |  |  |

| V <sub>REG</sub>                   | 3.3 V              |  |  |

| OPEN                               | 1.0 V              |  |  |

| Resistor divider                   | Adjustable between |  |  |

| Resistor divider                   | 0.6 V and 5.5 V    |  |  |

Figure : Timing chart of output voltage setting

# NN31001A

# **OPERATION (Continued)**

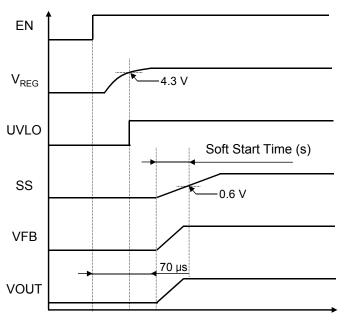

## 4. Soft Start Setting

Soft Start function maintains the smooth control of the output voltage during start up by adjusting soft start time. When the EN pin becomes High, the current (2  $\mu$ A) begin to charge toward the external capacitor (Css) of SS pin, and the voltage of SS pin increases straightly. Because the voltage of VFB pin is controlled by the voltage of SS pin during start up, the voltage of VFB increase straightly to the regulation voltage (0.6 V) together with the voltage of SS pin and keep the regulation voltage after that. On the other hand, the voltage of SS pin increase to about 2.8 V and keep the voltage. The calculation of Soft Start Time is as follows.

Soft Start Time(s) =

$$\frac{0.6}{2\mu} \times Css$$

When Css is set at 4.7nF, soft-start time is Approximately 1.5ms in 1.0V setting.

Figure : Soft Start Operation

# NN31001A

#### **OPERATION** (Continued)

#### 5. Start Up / Shut Down Settings

The Start up / Shut down is enabled by the EN pin. The EN pin can be set by either applying voltage from an external voltage source or through a resistor connected to the AVIN pin.

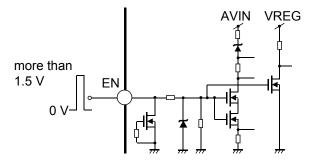

Case 1 : Setting up the EN pin using an external voltage source. When an external voltage source is used, the EN pin input voltage  $(V_{\text{ENH}}, V_{\text{ENL}})$  should satisfy the conditions as defined in the electrical characteristics.

Figure : Internal circuit with EN pin

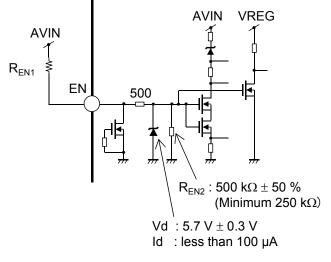

Case 2 : Setting up the EN pin through a resistor connected to AVIN pin. When setting up the EN pin through a resistor connected to the AVIN pin, refer to the following equation to calculate the optimal resistor settings.

#### [Equation]

$$\frac{AV_{IN} - V_{dMIN}}{Id} < R_{EN1} < \frac{(AV_{IN} - V_{ENH}) \times R_{EN2MIN}}{V_{ENH}}$$

$$R_{EN1} : \text{pull up resistor of EN pin}$$

$$AV_{IN} : \text{input voltage}$$

$$V_{dMIN} : \text{minimum internal zener diode voltage}$$

$$(5.4 \text{ V})$$

Id : internal zener diode current (100 μA ) V<sub>ENH</sub> : EN pin high level input voltage (1.5 V to 5 V )

$R_{\text{EN2MIN}}\,$  : minimum pull down resistor ( 250 k $\!\Omega$  )

$[\text{Example (AV_{IN} = 12 V, V_{ENH} = 5 V)]}$

66 kΩ <

$$R_{EN1}$$

< 350 kΩ

Figure : Internal circuit with EN pin

#### **TYPICAL CHARACTERISTICS CURVES**

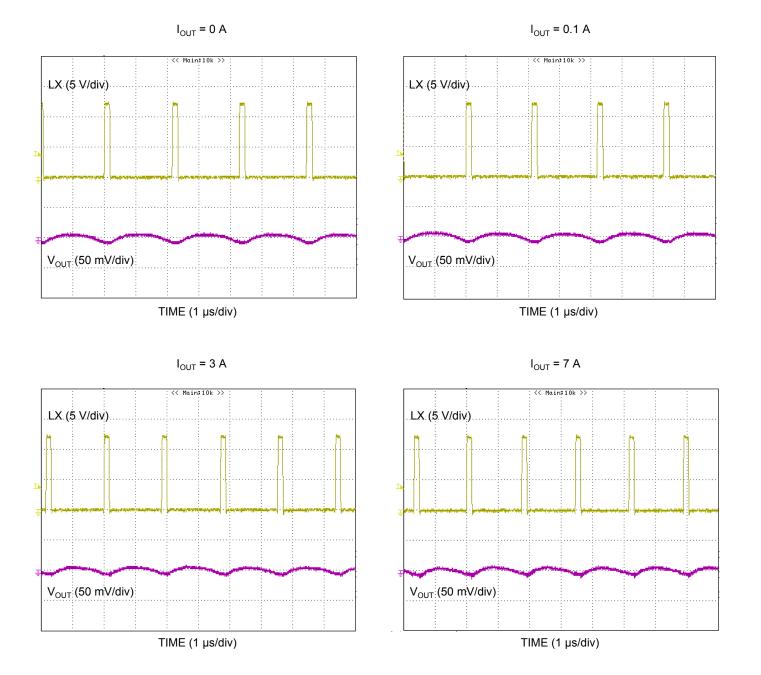

#### 1. Output Ripple Voltage

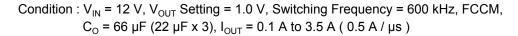

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 1.0 V, Switching Frequency = 600 kHz, FCCM, C<sub>O</sub> = 66  $\mu$ F (22  $\mu$ F x 3)

Established : 2014-07-03 Revised : 2014-07-08

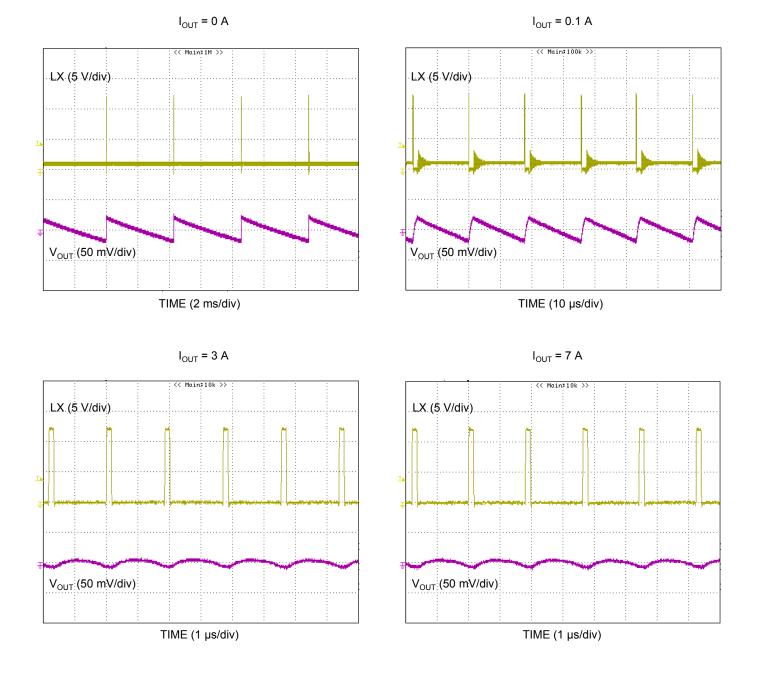

#### **TYPICAL CHARACTERISTICS CURVES (Continued)**

#### 1. Output Ripple Voltage (Continued)

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 1.0 V, Switching Frequency = 600 kHz, Skip mode,  $C_0$  = 66 µF (22 µF x 3)

#### **TYPICAL CHARACTERISTICS CURVES (Continued)**

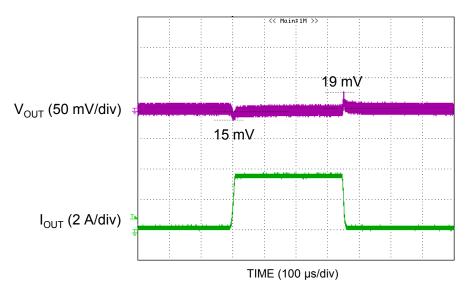

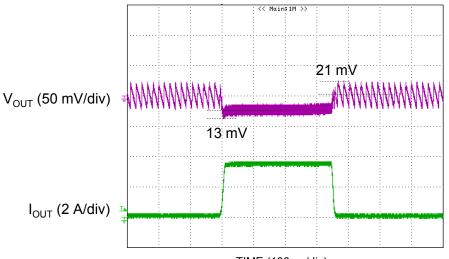

#### 2. Load Transient Response

Condition :  $V_{IN}$  = 12 V,  $V_{OUT}$  Setting = 1.0 V, Switching Frequency = 600 kHz, Skip mode,  $C_{\rm O}$  = 66  $\mu F$  (22  $\mu F$  x 3),  $I_{\rm OUT}$  = 0.1 A to 3.5 A ( 0.5 A /  $\mu s$  )

TIME (100 µs/div)

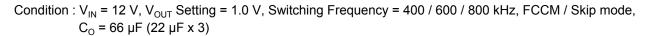

#### **TYPICAL CHARACTERISTICS CURVES**

#### 3. Efficiency

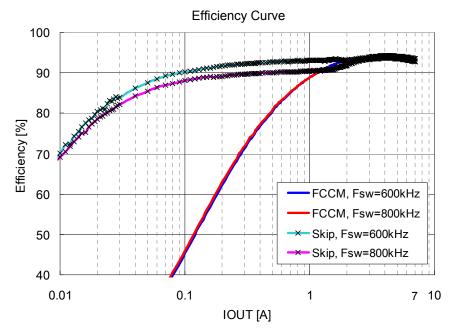

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 3.3 V, Switching Frequency = 600 / 800 kHz, FCCM / Skip mode,  $C_0$  = 66 µF (22 µF x 3)

## **TYPICAL CHARACTERISTICS CURVES (Continued)**

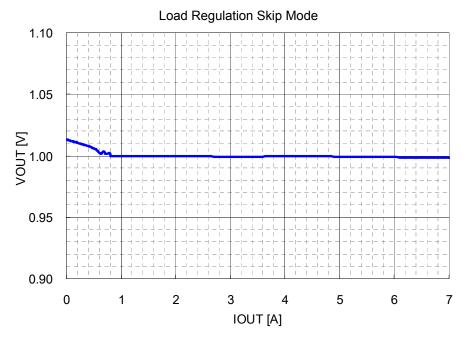

## 4. Load Regulation

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 1.0 V, Switching Frequency = 600 kHz, FCCM,  $C_0 = 66 \ \mu F \ (22 \ \mu F \ x \ 3)$

## **TYPICAL CHARACTERISTICS CURVES (Continued)**

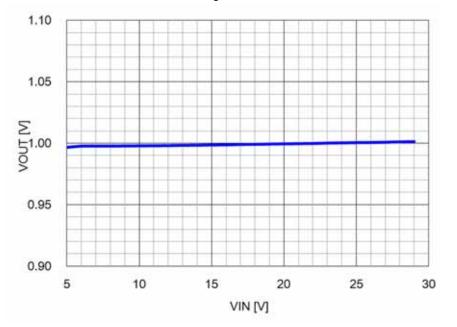

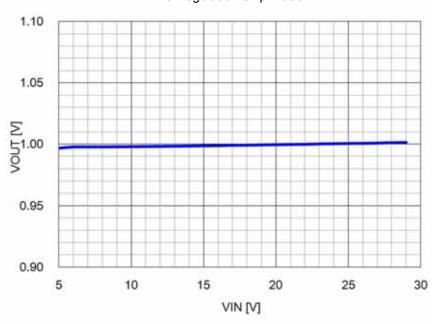

#### 5. Line Regulation

Condition :  $I_{OUT}$  = 2 A,  $V_{OUT}$  Setting = 1.0 V, Switching Frequency = 600 kHz, FCCM,  $C_0$  = 66  $\mu$ F (22  $\mu$ F x 3)

Line Regulation FCCM

Line Regulation Skip Mode

Established : 2014-07-03 Revised : 2014-07-08

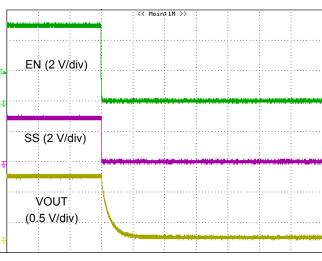

### **TYPICAL CHARACTERISTICS CURVES (Continued)**

#### 6. Start-up

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 1.0 V, I<sub>OUT</sub> = 0 A, Switching Frequency = 600 kHz, FCCM, C<sub>O</sub> = 66  $\mu$ F (22  $\mu$ F x 3)

EN (2 V/div) SS (2 V/div) VOUT (0.5 V/div) TIME (10 ms/div)

EN = Low to High

EN = High to Low

TIME (10 ms/div)

## **TYPICAL CHARACTERISTICS CURVES (Continued)**

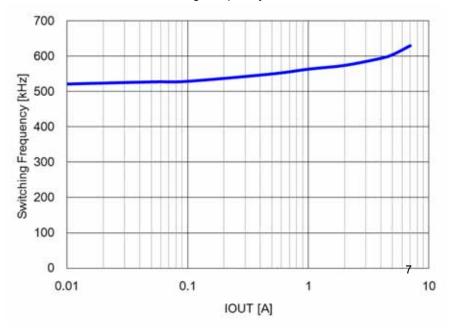

#### 7. Switching Frequency

Condition :  $V_{IN}$  = 12 V,  $V_{OUT}$  Setting = 1.0 V, Switching Frequency = 600 kHz, FCCM,  $C_0$  = 66  $\mu$ F (22  $\mu$ F x 3)

Switching Frequency FCCM

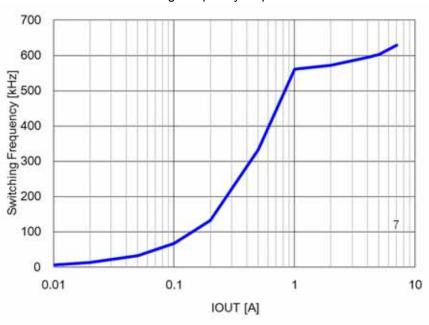

Condition :  $V_{IN}$  = 12 V,  $V_{OUT}$  Setting = 1.0 V, Switching Frequency = 600 kHz, Skip mode,  $C_0$  = 66 µF (22 µF x 3)

#### Switching Frequency Skip Mode

Established : 2014-07-03 Revised : 2014-07-08

# **TYPICAL CHARACTERISTICS CURVES (Continued)**

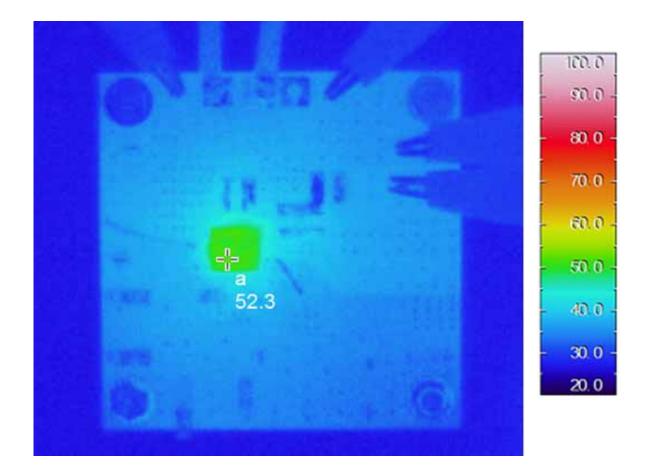

#### 8. Thermal Performance

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 1.0 V, I<sub>OUT</sub> = 7 A, Switching Frequency = 600 kHz, FCCM,  $C_0$  = 66 µF (22 µF x 3)

## **TYPICAL CHARACTERISTICS CURVES (Continued)**

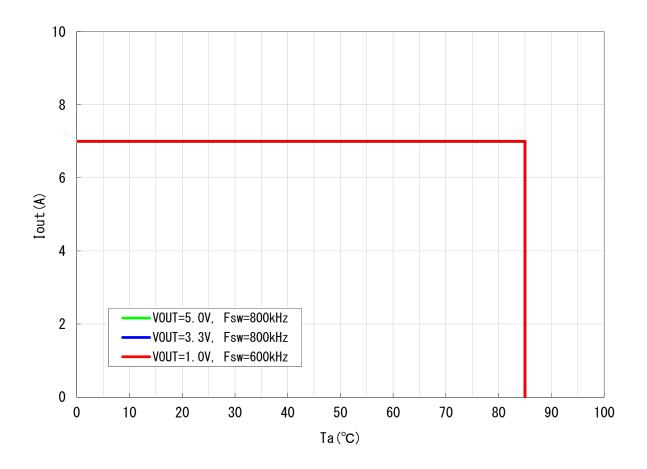

#### 9. Derating Curve

Condition : V<sub>IN</sub> = 12 V, V<sub>OUT</sub> Setting = 1.0 / 3.3 / 5.0 V, Switching Frequency = 600 / 800 kHz, FCCM,  $C_0$  = 66 µF (22 µF x 3), Air flow = 0 LFM

### **APPLICATIONS INFORMATION**

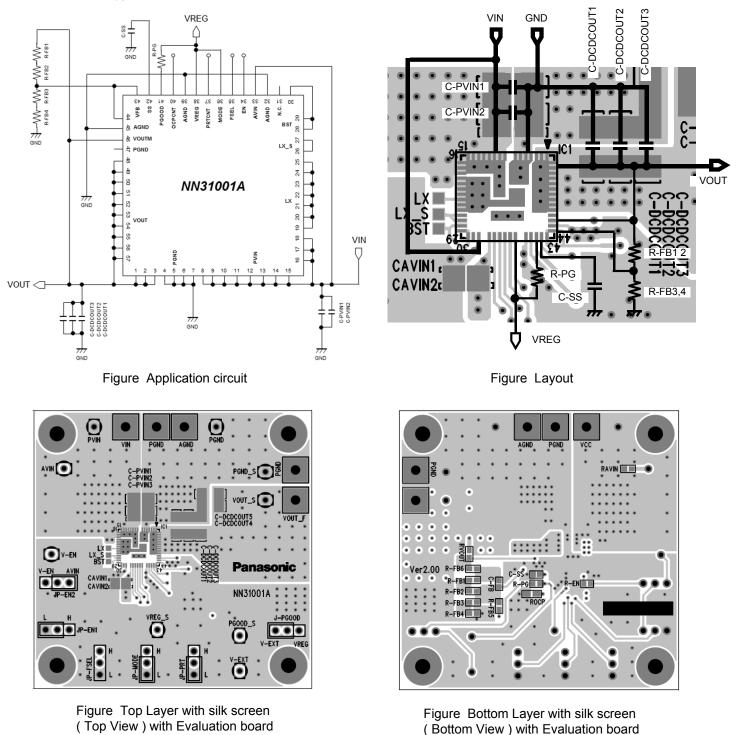

#### **1. Evaluation Board Information**

Condition : V<sub>OUT</sub> Setting = 1.0 V, Switching Frequency = 600 kHz, FCCM

Note : The application circuit diagram and layout diagram explained in this section, should be used as reference examples. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit and the information attached with it, in the design of the equipment.

## **APPLICATIONS INFORMATION (Continued)**

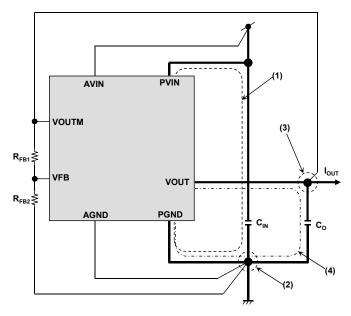

#### 2. Layout Recommendations

Board layout considerations are needed for stable operation of the DC-DC regulator. It is recommended to follow the below notes of caution when designing the board layout.

- (a) The Input capacitor  $C_{IN}$  is recommended to be placed in such a way that the loop (1) in the right figure becomes minimum in order to suppress the switching noise.

- (b) A single point ground connection (2) is recommended for the connection of PGND and AGND to improve operation stability.

- (c) Output current line  $I_{OUT}$  and the output sense line VOUTM is recommended to have small common impedance to reduce output load variations. Output sense line VOUTM must be close to the output capacitor  $C_0$  as indicated by (3) in the right figure.

- (d) Power Loss and output ripple voltage can be reduced by placing the output capacitor  $C_O$  so that the parasitic inductance and the impedance of loop (4) in the right figure becomes minimum. This is achieved by reducing the distance between output capacitor  $C_O$  and (2) / (3).

- (e) Thick lines in the right figure represent lines with large current flow. These lines should be designed as thick as possible.

- (f) VFB / SS / VREG lines should be placed far away from LX, BST pins to reduce the influence of switching noise. These lines should be designed as short as possible. This is especially true for the VFB line, which is a high impedance line.

- (g)  $R_{FB1}$  /  $R_{FB2}$  should also be placed as far away as possible from LX, BST pins to minimize the influence of switching noise.  $R_{FB1}$  /  $R_{FB2}$  should be placed close to the VFB pin.

Figure : Application circuit diagram

Note : The application circuit diagram and layout diagram explained in this section, should be used as reference examples. The operation of the mass production set is not guaranteed. Sufficient evaluation and verification is required in the design of the mass production set. The Customer is fully responsible for the incorporation of the above illustrated application circuit and the information attached with it, in the design of the equipment.

# **APPLICATIONS INFORMATION (Continued)**

#### **3. Recommended Components**

| Reference Designator                   | QTY | Value  | Manufacturer | Part Number        | Note |

|----------------------------------------|-----|--------|--------------|--------------------|------|

| C-PVIN1<br>C-PVIN2                     | 2   | 10 µF  | TAIYO YUDEN  | UMK325AB7106MM-T   | —    |

| C-DCDCOUT1<br>C-DCDCOUT2<br>C-DCDCOUT3 | 3   | 22 µF  | Murata       | GRM32ER71E226KE15L | _    |

| C-SS                                   | 1   | 4.7 nF | Murata       | GRM188R71H472KA01  | —    |

| R-FB1                                  | 1   | 0Ω     | Panasonic    | ERJ3GEY0R00V       | —    |

| R-FB2                                  | 1   | 1 kΩ   | Panasonic    | ERJ3EKF1001V       | —    |

| R-RB3                                  | 1   | 1.5 kΩ | Panasonic    | ERJ3EKF1501V       | —    |

| R-FB4                                  | 1   | 0 Ω    | Panasonic    | ERJ3GEY0R00V       | —    |

| R-PG                                   | 1   | 100 kΩ | Panasonic    | ERJ3EKF1003V       | —    |

Note : The above feedback resistor setting is for  $V_{OUT}$  = 1 V.

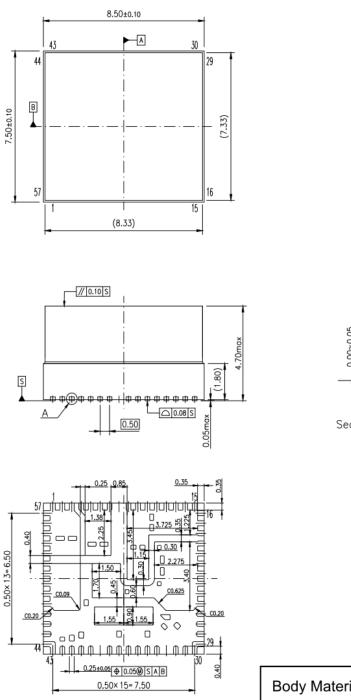

### PACKAGE INFORMATION

#### **Outline Drawing**

Package Code : HQFN057-A-075085

Section A(Reference value)

Body Material : Br/Sb Free Epoxy Resin

Lead Material : Cu Alloy

Lead Finish Method : Sn-Bi Plating

### **IMPORTANT NOTICE**

- 1. When using the IC for new models, verify the safety including the long-term reliability for each product.

- 2. When the application system is designed by using this IC, please confirm the notes in this book.

- Please read the notes to descriptions and the usage notes in the book.

- 3. This IC is intended to be used for general electronic equipment.

Consult our sales staff in advance for information on the following applications: Special applications in which exceptional quality and reliability are required, or if the failure or malfunction of this IC may directly jeopardize life or harm the human body. Any applications other than the standard applications intended.

- (1) Space appliance (such as artificial satellite, and rocket)

- (2) Traffic control equipment (such as for automotive, airplane, train, and ship)

- (3) Medical equipment for life support

- (4) Submarine transponder

- (5) Control equipment for power plant

- (6) Disaster prevention and security device

- (7) Weapon

- (8) Others : Applications of which reliability equivalent to (1) to (7) is required

Our company shall not be held responsible for any damage incurred as a result of or in connection with the IC being used for any special application, unless our company agrees to the use of such special application.

- However, for the IC which we designate as products for automotive use, it is possible to be used for automotive.

- 4. This IC is neither designed nor intended for use in automotive applications or environments unless the IC is designated by our company to be used in automotive applications.

Our company shall not be held responsible for any damage incurred by customers or any third party as a result of or in connection with the IC being used in automotive application, unless our company agrees to such application in this book.

- 5. Please use this IC in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Our company shall not be held responsible for any damage incurred as a result of our IC being used by our customers, not complying with the applicable laws and regulations.

- 6. Pay attention to the direction of the IC. When mounting it in the wrong direction onto the PCB (printed-circuit-board), it might be damaged.

- 7. Pay attention in the PCB (printed-circuit-board) pattern layout in order to prevent damage due to short circuit between pins. In addition, refer to the Pin Description for the pin configuration.

- 8. Perform visual inspection on the PCB before applying power, otherwise damage might happen due to problems such as solder-bridge between the pins of the IC. Also, perform full technical verification on the assembly quality, because the same damage possibly can happen due to conductive substances, such as solder ball, that adhere to the IC during transportation.

- 9. Take notice in the use of this IC that it might be damaged when an abnormal state occurs such as output pin-VCC short (Power supply fault), output pin-GND short (Ground fault), or output-to-output-pin short (load short). Safety measures such as installation of fuses are recommended because the extent of the above-mentioned damage will depend on the current capability of the power supply.

- 10. The protection circuit is for maintaining safety against abnormal operation. Therefore, the protection circuit should not work during normal operation.

Especially for the thermal protection circuit, if the area of safe operation or the absolute maximum rating is momentarily exceeded due to output pin to VCC short (Power supply fault), or output pin to GND short (Ground fault), the IC might be damaged before the thermal protection circuit could operate.

- 11. Unless specified in the product specifications, make sure that negative voltage or excessive voltage are not applied to the pins because the IC might be damaged, which could happen due to negative voltage or excessive voltage generated during the ON and OFF timing when the inductive load of a motor coil or actuator coils of optical pick-up is being driven.

- 12. Product which has specified ASO (Area of Safe Operation) should be operated in ASO

- 13. Verify the risks which might be caused by the malfunctions of external components.

- 14. Connect the metallic plates (fins) on the back side of the IC with their respective potentials (AGND, PVIN, LX, VOUT, PGND). The thermal resistance and the electrical characteristics are guaranteed only when the metallic plates (fins) are connected with their respective potentials.

# Product name : NN31001A Package : HQFN057-A-075085

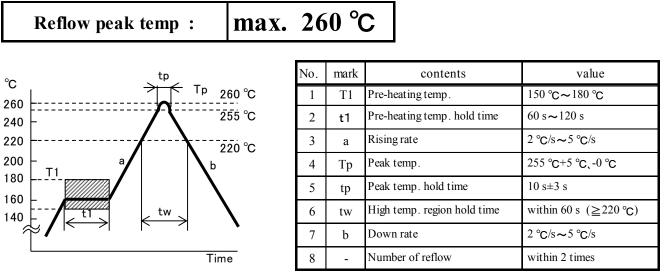

# 1. Recommended Soldering Conditions

For the following soldering conditions, it shows the limitations of heat resistance at mounting a device and it is no guarantee of the soldering reliability. Please set the appropriate condition suitable for the materials such as solder material.

## ① Reflow soldering

\*Peak temperature : less than 260  $^{\circ}$ C

\* Temperature is measured at package surface point

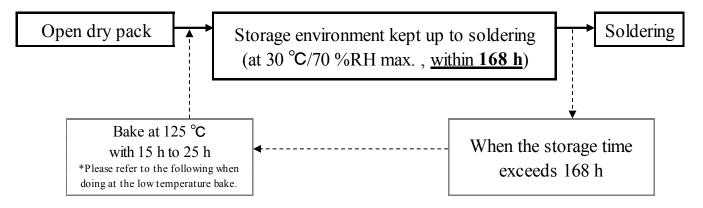

# 2. Storage environment after dry pack opening

Because the taping and the magazine materials are not the heat-resistant materials, the bake at 125°C cannot be done.

Therefore, places colder event thing or control event thing in the rule time.

Therefore, please solder everything or control everything in the rule time.

Please keep them in an equal environment with the moisture-proof packaging or dry box. To control storage time, when bake in the taping and the magazine is necessary, it is necessary for each type to set a bake condition. Please inquire of our company.

☆ Low temperature bake condition : 40°C / 25% RH or less / 192h

# 3. Note

- (1) Storage environment conditions: keep the following conditions Ta=5  $^{\circ}C \sim 30 ^{\circ}C$ , RH=30 %  $\sim 70 ^{\circ}$ .

- (2) Storage period before opening dry pack shall be 1year from a shipping day under Ta=5  $^{\circ}C \sim 30 ^{\circ}C_{\gamma}$  RH=30 %  $\sim 70$  %. When the storage exceeds, Bake at 125  $^{\circ}C$  with 15 h to 25 h.

- (3) Baking cycle should be only one time.

Please be cautious of solderability at baking.

- (4) In case that use reflow two times, 2nd reflow must be finished within 168 hours.

- (5) Remove flux sufficiently from product in the washing process.

(Flux : Chlorineless rosin flux is recommended.)

(6) In case that use ultrasonic for product washing,

There is the possibility that the resonance may occur due to the frequency and shape of PCB.

It may be affected to the strength of lead. Please be cautious of this matter.

# Request for your special attention and precautions in using the technical information and semiconductors described in this book

- (1) If any of the products or technical information described in this book is to be exported or provided to non-residents, the laws and regulations of the exporting country, especially, those with regard to security export control, must be observed.

- (2) The technical information described in this book is intended only to show the main characteristics and application circuit examples of the products. No license is granted in and to any intellectual property right or other right owned by Panasonic Corporation or any other company. Therefore, no responsibility is assumed by our company as to the infringement upon any such right owned by any other company which may arise as a result of the use of technical information described in this book.

- (3) The products described in this book are intended to be used for general applications (such as office equipment, communications equipment, measuring instruments and household appliances), or for specific applications as expressly stated in this book. Consult our sales staff in advance for information on the following applications:

• Special applications (such as for airplanes, aerospace, automotive equipment, traffic signaling equipment, combustion equipment, life support systems and safety devices) in which exceptional quality and reliability are required, or if the failure or malfunction of the products may directly jeopardize life or harm the human body.

It is to be understood that our company shall not be held responsible for any damage incurred as a result of or in connection with your using the products described in this book for any special application, unless our company agrees to your using the products in this book for any special application.

- (4) The products and product specifications described in this book are subject to change without notice for modification and/or improvement. At the final stage of your design, purchasing, or use of the products, therefore, ask for the most up-to-date Product Standards in advance to make sure that the latest specifications satisfy your requirements.

- (5) When designing your equipment, comply with the range of absolute maximum rating and the guaranteed operating conditions (operating power supply voltage and operating environment etc.). Especially, please be careful not to exceed the range of absolute maximum rating on the transient state, such as power-on, power-off and mode-switching. Otherwise, we will not be liable for any defect which may arise later in your equipment.

Even when the products are used within the guaranteed values, take into the consideration of incidence of break down and failure mode, possible to occur to semiconductor products. Measures on the systems such as redundant design, arresting the spread of fire or preventing glitch are recommended in order to prevent physical injury, fire, social damages, for example, by using the products.

(6) Comply with the instructions for use in order to prevent breakdown and characteristics change due to external factors (ESD, EOS, thermal stress and mechanical stress) at the time of handling, mounting or at customer's process. When using products for which damp-proof packing is required, satisfy the conditions, such as shelf life and the elapsed time since first opening the packages.

(7) This book may be not reprinted or reproduced whether wholly or partially, without the prior written permission of our company.

20100202

# **Mouser Electronics**

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Panasonic: NN31001A-BB

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества: