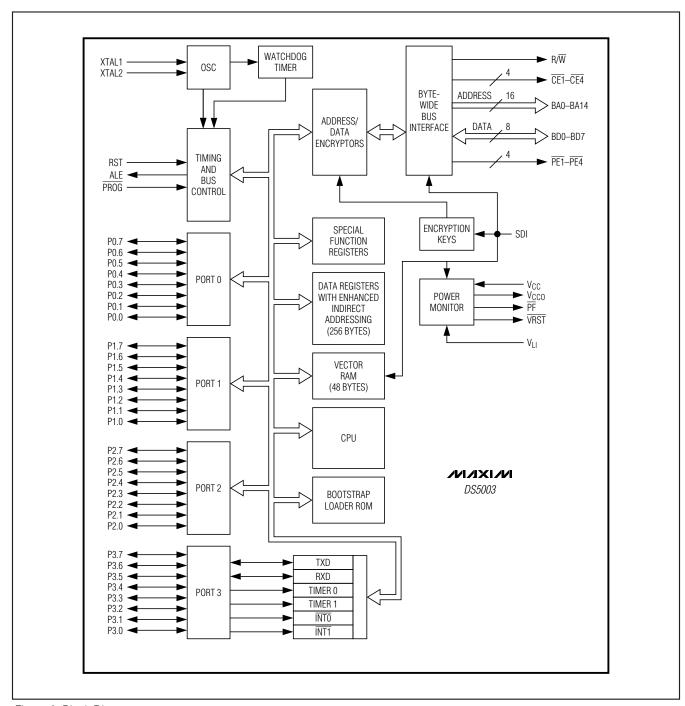

## **General Description**

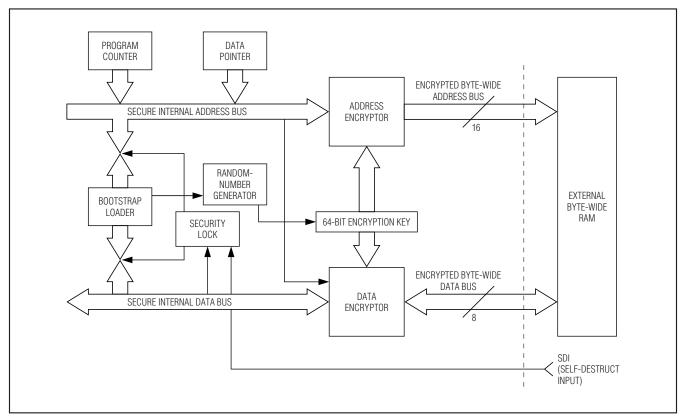

The DS5003 secure microprocessor incorporates sophisticated security features including an array of mechanisms that are designed to resist all levels of threat, including observation, analysis, and physical attack. As a result, a massive effort is required to obtain any information about its memory contents. Furthermore, the "soft" nature of the DS5003 allows frequent modification of the secure information, thereby minimizing the value of any secure information obtained by such a massive effort. The device is an enhanced version of the DS5002FP secure microprocessor chip with additional scratchpad RAM.

### Differences from the DS5002FP

The DS5003 implements only one additional feature from the DS5002FP: it adds 128 bytes of internal scratchpad memory (for a total of 256 bytes) similar to that used in 8032/8052 architectures. This additional memory is accessible through indirect addressing 8051 instructions such as "mov a, @r1," where r1 now can have a value between 0 and 255. It is also usable as stack space for pushes, pops, calls, and returns.

Register indirect addressing is used to access the scratchpad RAM locations above 7Fh. It can also be used to reach the lower RAM (0h-7Fh) if needed. The address is supplied by the contents of the working register specified in the instruction. Thus, one instruction can be used to reach many values by altering the contents of the designated working register. Note that only R0 and R1 can be used as pointers. An example of register indirect addressing is as follows:

ANL A, @RO ;Logical AND the Accumulator with the contents of

> ; the register pointed to by the value stored in R0

> > **Applications**

PIN Pads

Gaming Machines

Any Application Requiring Software Protection

### **Features**

♦ 8051-Compatible Microprocessor for Secure/Sensitive Applications

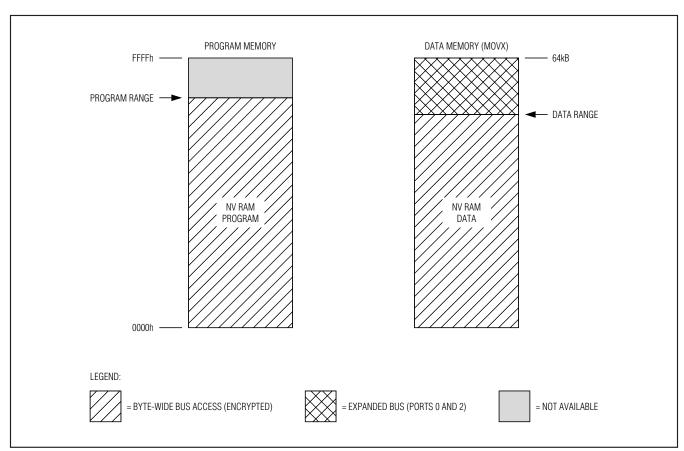

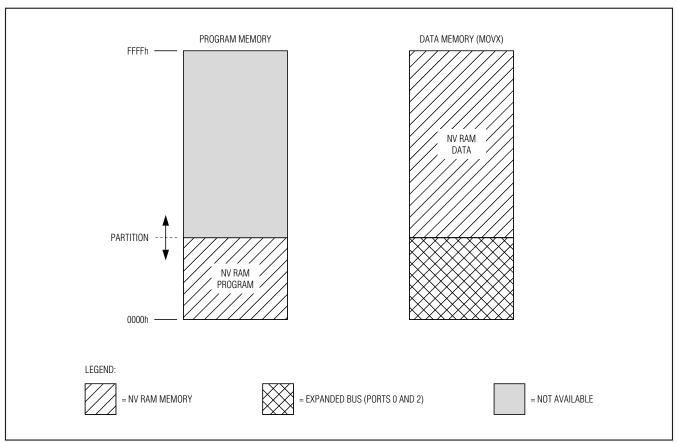

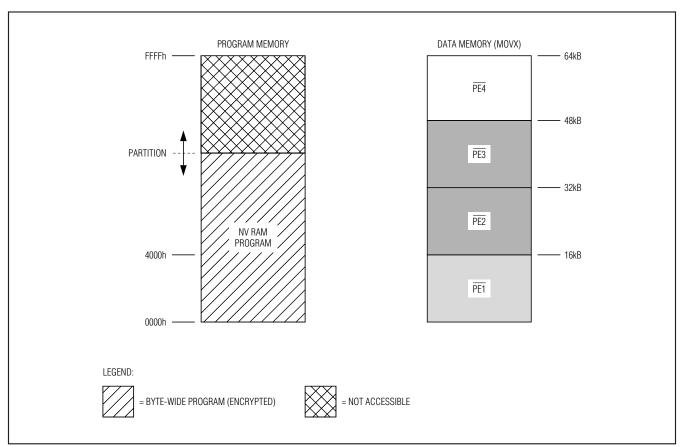

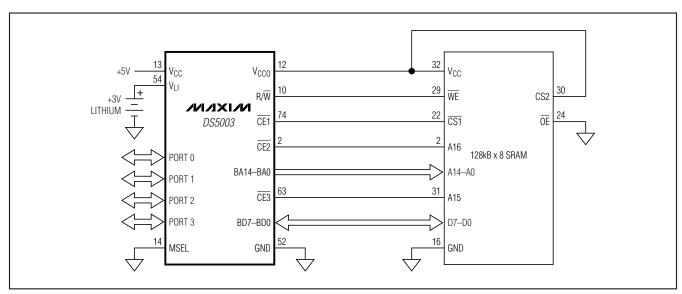

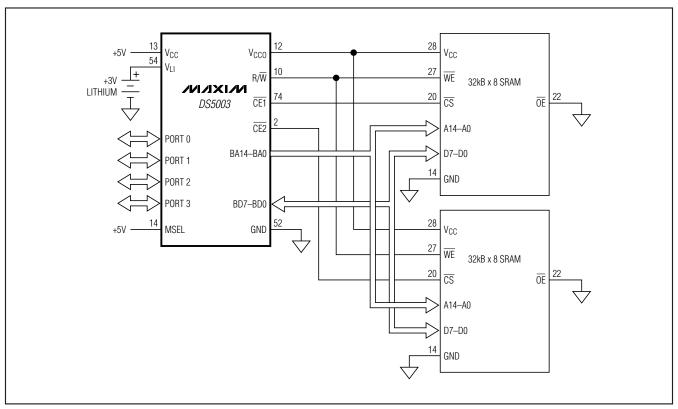

Access 32kB, 64kB, or 128kB of Nonvolatile SRAM for Program and/or Data Storage

128 Bytes of RAM

128 Bytes of Indirect Scratchpad RAM

In-System Programming Through On-Chip **Serial Port**

Can Modify Its Own Program or Data Memory in the End System

**♦ Firmware Security Features**

**Memory Stored in Encrypted Form Encryption Using On-Chip 64-Bit Key Automatic True Random-Key Generator** Self-Destruct Input (SDI) **Top Coating Prevents Microprobing**

**Protects Memory Contents from Piracy**

**♦** Crash-Proof Operation

**Watchdog Timer**

Maintains All Nonvolatile Resources for Over 10 Years (at Room Temperature) in the **Absence of Power Power-Fail Reset Early Warning Power-Fail Interrupt**

### **Ordering Information**

| PART          | TEMP<br>RANGE | INTERNAL<br>MICRO<br>PROBE<br>SHIELD | PIN-<br>PACKAGE |

|---------------|---------------|--------------------------------------|-----------------|

| DS5003FPM-16+ | 0°C to +70°C  | Yes                                  | 80 MQFP         |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

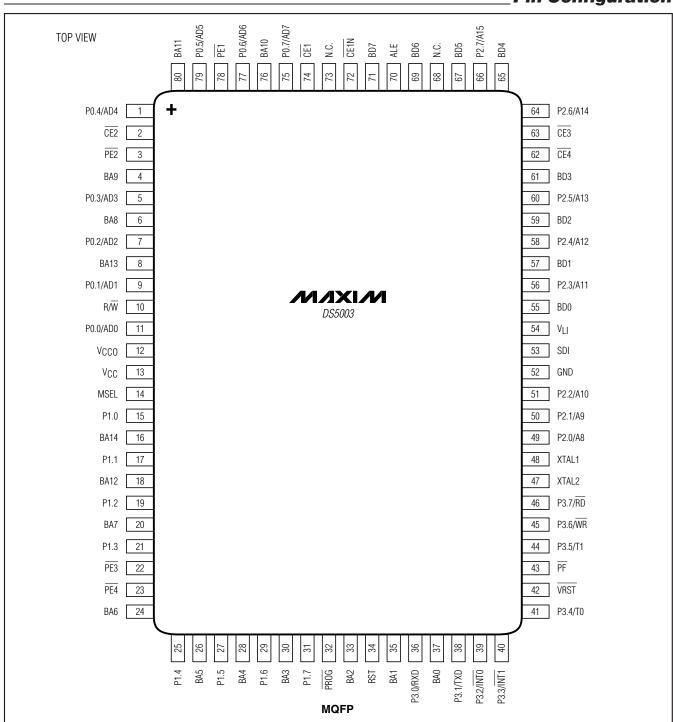

Pin Configuration appears at end of data sheet.

### **ABSOLUTE MAXIMUM RATINGS**

| Voltage Range on Any Pin                  |                                  | Operating Temperature Range | 40°C to +85°C            |

|-------------------------------------------|----------------------------------|-----------------------------|--------------------------|

| Relative to Ground                        | 0.3V to (V <sub>CC</sub> + 0.5V) | Storage Temperature*        | 55°C to +125°C           |

| Voltage Range on V <sub>CC</sub> Relative |                                  | Soldering Temperature       | Refer to the IPC/JEDEC   |

| to Ground                                 | 0.3V to +6.0V                    |                             | J-STD-020 Specification. |

\*Storage temperature is defined as the temperature of the device when  $V_{CC} = 0V$  and  $V_{LI} = 0V$ . In this state, the contents of SRAM are not battery backed and are undefined.

Note: The DS5003 adheres to all AC and DC electrical specifications published for the DS5002FP.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC CHARACTERISTICS

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                                                                | SYMBOL            | CONDITIONS                                 | MIN                       | TYP  | MAX                   | UNITS |

|--------------------------------------------------------------------------|-------------------|--------------------------------------------|---------------------------|------|-----------------------|-------|

| Operating Voltage                                                        | Vcc               | (Note 1)                                   | VCCMIN                    |      | 5.5                   | V     |

| Minimum Operating Voltage                                                | VCCMIN            | 0°C to +70°C (Note 1)                      | 4.00                      | 4.12 | 4.25                  | V     |

| Power-Fail Warning Voltage                                               | V <sub>PFW</sub>  | 0°C to +70°C (Note 1)                      | 4.25                      | 4.37 | 4.50                  | V     |

| Lithium Supply Voltage                                                   | V <sub>LI</sub>   | (Note 1)                                   | 2.5                       |      | 4.0                   | V     |

| Operating Current at 16MHz                                               | Icc               | (Note 2)                                   |                           |      | 36                    | mA    |

| Idle-Mode Current at 12MHz                                               | lidle             | 0°C to +70°C (Note 3)                      |                           |      | 7.0                   | mA    |

| Stop-Mode Current                                                        | ISTOP             | (Note 4)                                   |                           |      | 80                    | μΑ    |

| Pin Capacitance                                                          | CIN               | (Note 5)                                   |                           |      | 10                    | рF    |

| Output Supply Voltage (VCCO)                                             | Vcco <sub>1</sub> | (Notes 1, 2)                               | V <sub>CC</sub> - 0.45    |      |                       | V     |

| Output Supply Battery-Backed Mode (V <sub>CCO</sub> , CE1-CE4, PE1, PE2) | VCCO2             | 0°C to +70°C (Notes 1, 6)                  | V <sub>LI</sub> -<br>0.65 |      |                       | V     |

| Output Supply Current (Note 7)                                           | Icco <sub>1</sub> | V <sub>CCO</sub> = V <sub>CC</sub> - 0.45V |                           |      | 75                    | mA    |

| Lithium-Backed Quiescent<br>Current (Note 8)                             | ILI               | 0°C to +70°C                               |                           | 5    | 75                    | nA    |

| Donat Trip Doint in Stop Mode                                            |                   | BAT = 3.0V (0°C to +70°C) (Note 1)         | 4.00                      |      | 4.25                  | V     |

| Reset Trip Point in Stop Mode                                            |                   | BAT = 3.3V (0°C to +70°C) (Note 1)         | 4.40                      |      | 4.65                  | V     |

| Input Low Voltage                                                        | VIL               | (Note 1)                                   | -0.3                      |      | +0.8                  | V     |

| Input High Voltage                                                       | V <sub>IH1</sub>  | (Note 1)                                   | 2.0                       |      | V <sub>CC</sub> + 0.3 | V     |

| Input High Voltage (RST, XTAL1, PROG)                                    | V <sub>IH2</sub>  | (Note 1)                                   | 3.5                       |      | V <sub>CC</sub> + 0.3 | V     |

| Output Low Voltage at I <sub>OL</sub> = 1.6mA (Ports 1, 2, 3, PF)        | V <sub>OL1</sub>  | (Notes 1, 9)                               |                           | 0.15 | 0.45                  | V     |

## **DC CHARACTERISTICS (continued)**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                                                                                                              | SYMBOL           | CONDITIONS                               | MIN | TYP  | MAX              | UNITS |

|------------------------------------------------------------------------------------------------------------------------|------------------|------------------------------------------|-----|------|------------------|-------|

| Output Low Voltage at I <sub>OL</sub> = 3.2mA (P0.0–P0.7, ALE, BA0–BA14, BD0–BD7, R/W, CE1N, CE1—CE4, PE1—PE4, VRST)   | Vol2             | (Note 1)                                 |     | 0.15 | 0.45             | V     |

| Output High Voltage at IOH = -80µA (Ports 1, 2, 3)                                                                     | V <sub>OH1</sub> | (Note 1)                                 | 2.4 | 4.8  |                  | V     |

| Output High Voltage at I <sub>OH</sub> = -400µA (P0.0–P0.7, ALE, BA0–BA14, BD0–BD7, R/W, CE1N, CE1–CE4, PE1–PE4, VRST) | V <sub>OH2</sub> | (Note 1)                                 | 2.4 | 4.8  |                  | V     |

| Input Low Current,<br>V <sub>IN</sub> = 0.45V (Ports 1, 2, 3)                                                          | IIL              |                                          |     |      | -50              | μA    |

| Transition Current 1 to 0,<br>V <sub>IN</sub> = 2.0V (Ports 1, 2, 3)                                                   | l⊤∟              |                                          |     |      | -500             | μA    |

| SDI Input Low Voltage                                                                                                  | VILS             | (Note 1)                                 |     |      | 0.4              | V     |

| SDI Input High Voltage                                                                                                 | V <sub>IHS</sub> | (Notes 1, 10)                            | 2.0 |      | V <sub>CCO</sub> | V     |

| SDI Pulldown Resistor                                                                                                  | R <sub>SDI</sub> |                                          | 25  |      | 60               | kΩ    |

| Input Leakage<br>(P0.0-P0.7, MSEL)                                                                                     | I <sub>IL</sub>  | 0.45 < V <sub>IN</sub> < V <sub>CC</sub> |     |      | +10              | μA    |

| RST Pulldown Resistor                                                                                                  | R <sub>RE</sub>  | 0°C to +70°C                             | 40  |      | 150              | kΩ    |

| VRST Pullup Resistor                                                                                                   | R <sub>VR</sub>  |                                          |     | 4.7  |                  | kΩ    |

| PROG Pullup Resistor                                                                                                   | R <sub>PR</sub>  |                                          |     | 40   |                  | kΩ    |

## **AC CHARACTERISTICS—SDI PIN**

$(V_{CC} = 0V \text{ to } 5V, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER                      | SYMBOL | CONDITIONS                                    | MIN | TYP | MAX | UNITS |  |

|--------------------------------|--------|-----------------------------------------------|-----|-----|-----|-------|--|

| SDI Pulse Reject (Note 11)     | tspr   | 4.5V < V <sub>CC</sub> < 5.5V                 |     |     | 1.3 |       |  |

|                                |        | V <sub>CC</sub> = 0V, V <sub>BAT</sub> = 2.9V |     |     | 4   | μs    |  |

| SDI Pulse Accept (Note 11) tsp | +00.   | 4.5V < V <sub>CC</sub> < 5.5V                 | 10  |     |     | 110   |  |

|                                | tspa i | V <sub>CC</sub> = 0V, V <sub>BAT</sub> = 2.9V | 50  |     |     | - μs  |  |

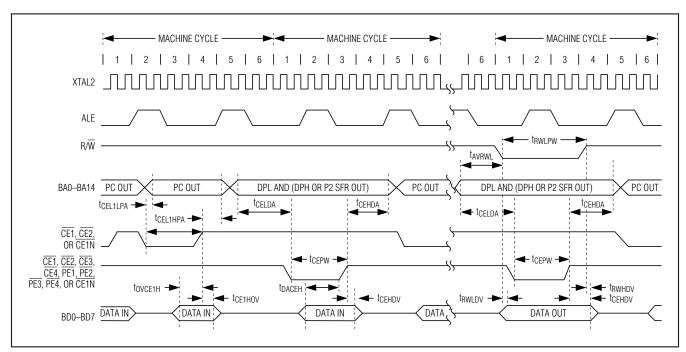

## AC CHARACTERISTICS—EXPANDED BUS-MODE TIMING SPECIFICATIONS

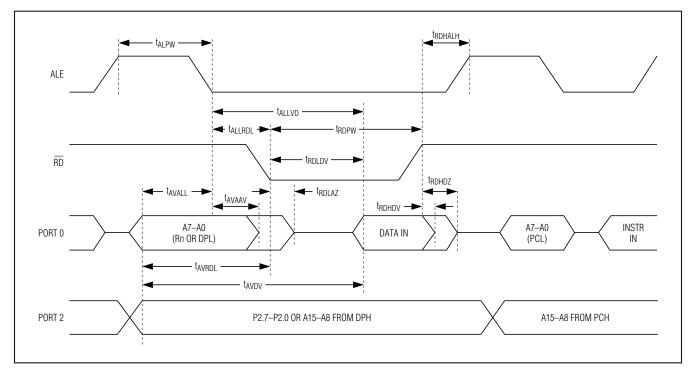

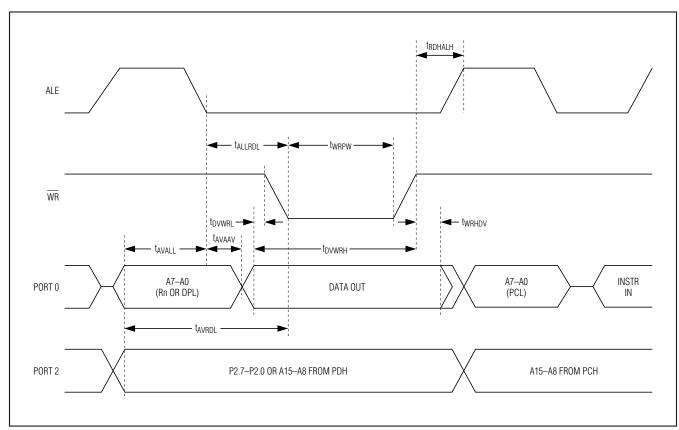

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.) \text{ (Figures 1, 2)}$

| PARAMETER                                         | SYMBOL              | CONDITIONS | MIN                     | MAX                     | UNITS |  |

|---------------------------------------------------|---------------------|------------|-------------------------|-------------------------|-------|--|

| Oscillator Frequency                              | 1/t <sub>CLK</sub>  |            | 1.0                     | 16.0                    | MHz   |  |

| ALE Pulse Width                                   | talpw               |            | 2t <sub>CLK</sub> - 40  |                         | ns    |  |

| Address Valid to ALE Low                          | tavall              |            | t <sub>CLK</sub> - 40   |                         | ns    |  |

| Address Hold After ALE Low                        | tavaav              |            | t <sub>CLK</sub> - 35   |                         | ns    |  |

| RD Pulse Width                                    | t <sub>RDPW</sub>   |            | 6t <sub>CLK</sub> - 100 |                         | ns    |  |

| WR Pulse Width                                    | twrpw               |            | 6t <sub>CLK</sub> - 100 |                         | ns    |  |

| RD Low to Valid Data In                           | top, p,             | 12MHz      |                         | 5t <sub>CLK</sub> - 165 | ns    |  |

| RD Low to Valid Data III                          | trolov              | 16MHz      |                         | 5t <sub>CLK</sub> - 105 | 118   |  |

| Data Hold After RD High                           | trdhdv              |            | 0                       |                         | ns    |  |

| Data Float After RD High                          | tRDHDZ              |            |                         | 2t <sub>CLK</sub> - 70  | ns    |  |

| ALE Low to Valid Data In                          |                     | 12MHz      |                         | 8t <sub>CLK</sub> - 150 | ns    |  |

| ALE LOW to Valid Data III                         | t <sub>ALLVD</sub>  | 16MHz      |                         | 8t <sub>CLK</sub> - 90  | 115   |  |

| Valid Address to Valid Data In                    | ta /D) /            | 12MHz      |                         | 9t <sub>CLK</sub> - 165 | ns    |  |

| Valid Address to Valid Data III                   | tavdv               | 16MHz      |                         | 9t <sub>CLK</sub> - 105 | 115   |  |

| ALE Low to $\overline{RD}$ or $\overline{WR}$ Low | tallrdl             |            | 3t <sub>CLK</sub> - 50  | 3t <sub>CLK</sub> + 50  | ns    |  |

| Address Valid to RD or WR Low                     | tavrdl              |            | 4t <sub>CLK</sub> - 130 |                         | ns    |  |

| Data Valid to WR Going Low                        | tovwrl              |            | t <sub>CLK</sub> - 60   |                         | ns    |  |

| Data Valid to WD High                             |                     | 12MHz      | 7t <sub>CLK</sub> - 150 |                         |       |  |

| Data Valid to WR High                             | tDVWRH              | 16MHz      | 7t <sub>CLK</sub> - 90  |                         | ns    |  |

| Data Valid After WR High                          | twrhdv              |            | t <sub>CLK</sub> - 50   |                         | ns    |  |

| RD Low to Address Float                           | trdlaz              |            |                         | 0                       | ns    |  |

| RD or WR High to ALE High                         | <sup>t</sup> RDHALH |            | t <sub>CLK</sub> - 40   | t <sub>CLK</sub> + 50   | ns    |  |

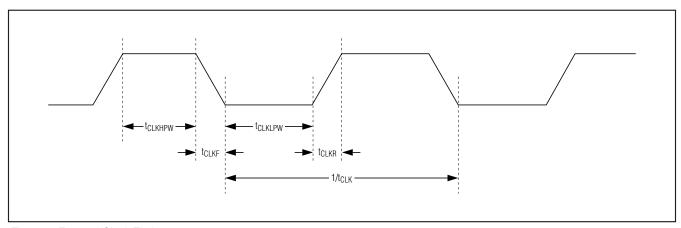

### AC CHARACTERISTICS—EXTERNAL CLOCK DRIVE

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$  (Figure 3)

| PARAMETER                   | SYMBOL   | CONDITIONS | MIN | MAX | UNITS |

|-----------------------------|----------|------------|-----|-----|-------|

| External Clock High Time    | tourupu  | 12MHz      | 20  |     |       |

| External Clock High Time    | tCLKHPW  | 16MHz      | 15  |     | ns    |

| Fishers at Olas Island Time | tour sur | 12MHz      | 20  |     | 20    |

| External Clock Low Time     | tCLKLPW  | 16MHz      | 15  |     | ns    |

| External Clock Rise Time    |          | 12MHz      |     | 20  | 20    |

| External Clock Rise Time    | tCLKR    | 16MHz      |     | 15  | ns    |

| External Clock Fall Time    | tour     | 12MHz      |     | 20  | no    |

|                             | tCLKF    | 16MHz      |     | 15  | ns    |

NIXIN

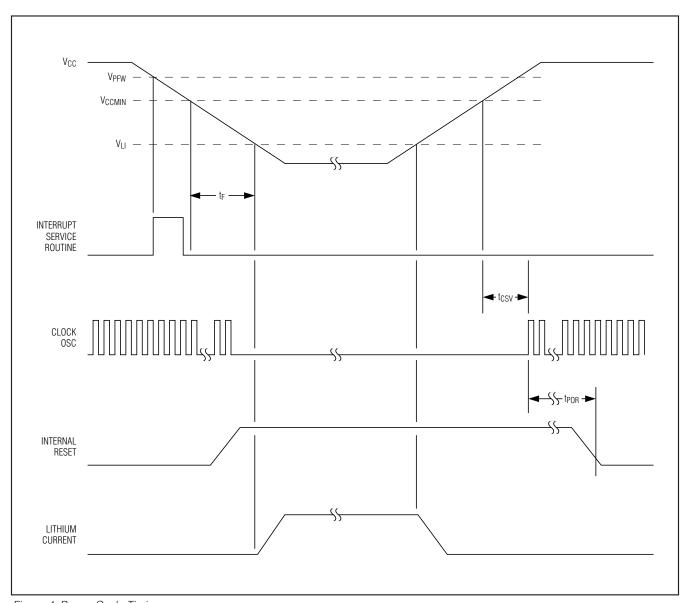

## **AC CHARACTERISTICS—POWER-CYCLE TIME**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$  (Figure 4)

| PARAMETER                                            | SYMBOL         | MIN | MAX       | UNITS |

|------------------------------------------------------|----------------|-----|-----------|-------|

| Slew Rate from V <sub>CCMIN</sub> to V <sub>LI</sub> | t <sub>F</sub> | 130 |           | μs    |

| Crystal Startup Time                                 | tcsu           |     | (Note 12) |       |

| Power-On Reset Delay                                 | tpor           |     | 21,504    | tclk  |

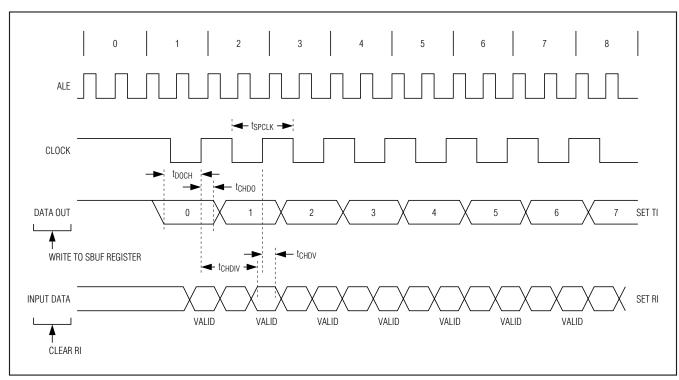

## AC CHARACTERISTICS—SERIAL PORT TIMING (MODE 0)

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.) \text{ (Figure 5)}$

| PARAMETER                                | SYMBOL | MIN                      | MAX                      | UNITS |

|------------------------------------------|--------|--------------------------|--------------------------|-------|

| Serial Port Clock Cycle Time             | tspclk | 12t <sub>CLK</sub>       |                          | μs    |

| Output Data Setup to Rising Clock Edge   | tDOCH  | 10t <sub>CLK</sub> - 133 |                          | ns    |

| Output Data Hold After Rising Clock Edge | tCHDO  | 2t <sub>CLK</sub> - 117  |                          | ns    |

| Clock Rising Edge to Input Data Valid    | tCHDV  |                          | 10t <sub>CLK</sub> - 133 | ns    |

| Input Data Hold After Rising Clock Edge  | tCHDIV | 0                        |                          | ns    |

### AC CHARACTERISTICS—BYTE-WIDE ADDRESS/DATA BUS TIMING

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.) \text{ (Figure 6)}$

| PARAMETER                                                                        | SYMBOL              | MIN                    | MAX | UNITS |

|----------------------------------------------------------------------------------|---------------------|------------------------|-----|-------|

| Delay to Byte-Wide Address Valid from CE1, CE2, or CE1N Low During Op Code Fetch | <sup>t</sup> CE1LPA |                        | 30  | ns    |

| Pulse Width of CE1-CE4, PE1-PE4, or CE1N                                         | tCEPW               | 4t <sub>CLK</sub> - 35 |     | ns    |

| Byte-Wide Address Hold After CE1, CE2, or CE1N High During Op Code Fetch         | <sup>t</sup> CE1HPA | 2t <sub>CLK</sub> - 20 |     | ns    |

| Byte-Wide Data Setup to CE1, CE2, or CE1N High During Op Code Fetch              | tovce1H             | 1t <sub>CLK</sub> + 40 |     | ns    |

| Byte-Wide Data Hold After CE1, CE2, or CE1N High During Op Code Fetch            | <sup>t</sup> CE1HOV | 0                      |     | ns    |

| Byte-Wide Address Hold After CE1-CE4, PE1-PE4, or CE1N High During MOVX          | tCEHDA              | 4t <sub>CLK</sub> - 30 |     | ns    |

| Delay from Byte-Wide Address Valid CE1-CE4, PE1-PE4, or CE1N Low During MOVX     | tcelda              | 4t <sub>CLK</sub> - 35 |     | ns    |

| Byte-Wide Data Setup to CE1-CE4, PE1-PE4, or CE1N High During MOVX (Read)        | tDACEH              | 1t <sub>CLK</sub> + 40 |     | ns    |

| Byte-Wide Data Hold After CE1-CE4, PE1-PE4, or CE1N High During MOVX (Read)      | <sup>†</sup> CEHDV  | 0                      |     | ns    |

| Byte-Wide Address Valid to R/W Active During MOVX (Write)                        | tavrwl              | 3t <sub>CLK</sub> - 35 |     | ns    |

## AC CHARACTERISTICS—BYTE-WIDE ADDRESS/DATA BUS TIMING (continued)

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.) \text{ (Figure 6)}$

| PARAMETER                                                    | SYMBOL | MIN                    | MAX | UNITS |

|--------------------------------------------------------------|--------|------------------------|-----|-------|

| Delay from R/W Low to Valid Data Out During MOVX (Write)     | tRWLDV | 20                     |     | ns    |

| Valid Data Out Hold Time from CE1-CE4, PE1-PE4, or CE1N High | tCEHDV | 1t <sub>CLK</sub> - 15 |     | ns    |

| Valid Data Out Hold Time from R/W High                       | trwhdv | 0                      |     | ns    |

| Write Pulse Width (R/W Low Time)                             | trwlpw | 6t <sub>CLK</sub> - 20 |     | ns    |

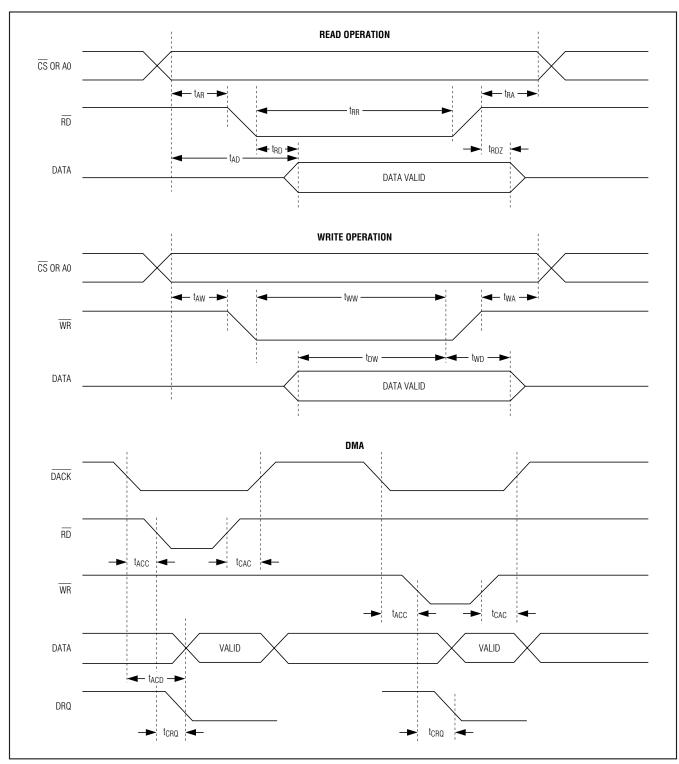

### RPC AC CHARACTERISTICS—DBB READ

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.) \text{ (Figure 7)}$

| PARAMETER                | SYMBOL           | MIN | MAX | UNITS |

|--------------------------|------------------|-----|-----|-------|

| CS, A0 Setup to RD       | t <sub>AR</sub>  | 0   |     | ns    |

| CS, A0 Hold After RD     | t <sub>RA</sub>  | 0   |     | ns    |

| RD Pulse Width           | t <sub>RR</sub>  | 160 |     | ns    |

| CS, A0 to Data Out Delay | t <sub>AD</sub>  |     | 130 | ns    |

| RD to Data Out Delay     | t <sub>RD</sub>  | 0   | 130 | ns    |

| RD to Data Float Delay   | t <sub>RDZ</sub> |     | 85  | ns    |

### RPC AC CHARACTERISTICS—DBB WRITE

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$  (Figure 7)

| PARAMETER          | SYMBOL          | MIN | MAX | UNITS |

|--------------------|-----------------|-----|-----|-------|

| CS, A0 Setup to WR | t <sub>AW</sub> | 0   |     | ns    |

| CS Hold After WR   | twA             | 0   |     | ns    |

| A0 Hold After WR   | twA             | 20  |     | ns    |

| WR Pulse Width     | tww             | 160 |     | ns    |

| Data Setup to WR   | t <sub>DW</sub> | 130 |     | ns    |

| Data Hold After WR | twD             | 20  |     | ns    |

## **AC CHARACTERISTICS—DMA**

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER               | SYMBOL | MIN | MAX | UNITS |

|-------------------------|--------|-----|-----|-------|

| DACK to WR or RD        | tACC   | 0   |     | ns    |

| RD or WR to DACK        | tcac   | 0   |     | ns    |

| DACK to Data Valid      | tACD   | 0   | 130 | ns    |

| RD or WR to DRQ Cleared | tCRQ   |     | 110 | ns    |

### AC CHARACTERISTICS—PROG

$(V_{CC} = 5V \pm 10\%, T_A = 0^{\circ}C \text{ to } +70^{\circ}C.)$

| PARAMETER             | SYMBOL | MIN | MAX | UNITS  |

|-----------------------|--------|-----|-----|--------|

| PROG Low to Active    | tpra   | 48  |     | Clocks |

| PROG High to Inactive | tpri   | 48  |     | Clocks |

- **Note 1:** All voltages are referenced to ground.

- Note 2: Maximum operating I<sub>CC</sub> is measured with all output pins disconnected; XTAL1 driven with  $t_{CLKR}$ ,  $t_{CLKF}$  = 10ns,  $V_{IL}$  = 0.5V; XTAL2 disconnected; RST = Port 0 =  $V_{CC}$ , MSEL =  $V_{SS}$ .

- Note 3: Idle mode, I<sub>IDLE</sub>, is measured with all output pins disconnected; XTAL1 driven with t<sub>CLKR</sub>, t<sub>CLKF</sub> = 10ns, V<sub>IL</sub> = 0.5V; XTAL2 disconnected; Port 0 = V<sub>CC</sub>, RST = MSEL = V<sub>SS</sub>.

- Note 4: Stop mode, I<sub>STOP</sub>, is measured with all output pins disconnected; Port 0 = V<sub>CC</sub>; XTAL2 not connected; RST = MSEL = XTAL1 = V<sub>SS</sub>.

- **Note 5:** Pin capacitance is measured with a test frequency: 1MHz, T<sub>A</sub> = +25°C. This specification is characterized but not production tested

- **Note 6:**  $V_{CCO2}$  is measured with  $V_{CC} < V_{LI}$  and a maximum load of 10µA on  $V_{CCO}$ .

- Note 7: I<sub>CCO1</sub> is the maximum average operating current that can be drawn from V<sub>CCO</sub> in normal operation.

- **Note 8:**  $I_{L1}$  is the current drawn from the  $V_{L1}$  input when  $V_{CC} = 0V$  and  $V_{CCO}$  is disconnected. Battery-backed mode is  $2.5V \le V_{BAT} \le 4.0$ ;  $V_{CC} \le V_{BAT}$ ;  $V_{SDI}$  should be  $\le V_{ILS}$  for  $I_{BAT}$  max.

- **Note 9:**  $\overline{PF}$  pin operation is specified with  $V_{BAT} \ge 3.0V$ .

- Note 10: V<sub>IHS</sub> minimum is 2.0V or V<sub>CCO</sub>, whichever is lower.

- **Note 11:** SDI is deglitched to prevent accidental destruction. The pulse must be longer than t<sub>SPR</sub> to pass the deglitcher, but SDI is not guaranteed unless it is longer than t<sub>SPA</sub>.

- **Note 12:** Crystal startup time is the time required to get the mass of the crystal into vibrational motion from the time that power is first applied to the circuit until the first clock pulse is produced by the on-chip oscillator. The user should check with the crystal vendor for a worst-case specification on this time.

Figure 1. Expanded Data Memory Read Cycle

Figure 2. Expanded Data Memory Write Cycle

Figure 3. External Clock Timing

Figure 4. Power-Cycle Timing

Figure 5. Serial Port Timing (Mode 0)

Figure 6. Byte-Wide Bus Timing

Figure 7. RPC Timing Mode

## Pin Description

|     | riii bescription |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|-----|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| PIN | NAME             | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|     | POWER PINS       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 13  | Vcc              | Power Supply, +5V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| 12  | Vcco             | <b>Vcc Output.</b> This is switched between V <sub>CC</sub> and V <sub>LI</sub> by internal circuits based on the level of V <sub>CC</sub> . When power is above the lithium input, power is drawn from V <sub>CC</sub> . The lithium cell remains isolated from a load. When V <sub>CC</sub> is below V <sub>LI</sub> , V <sub>CCO</sub> switches to the V <sub>LI</sub> source. V <sub>CCO</sub> should be connected to the V <sub>CC</sub> pin of an SRAM.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| 54  | V <sub>LI</sub>  | <b>Lithium Voltage Input.</b> Connect to a lithium cell greater than V <sub>LIMIN</sub> and no greater than V <sub>LIMAX</sub> as shown in the electrical specifications. Nominal value is +3V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 52  | GND              | Logic Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|     |                  | GENERAL-PURPOSE I/O PINS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 11  | P0.0/AD0         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 9   | P0.1/AD1         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 7   | P0.2/AD2         | 7 <u> </u>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 5   | P0.3/AD3         | General-Purpose I/O Port 0. This port is open drain and cannot drive a logic 1. It requires                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 1   | P0.4/AD4         | external pullups. Port 0 is also the multiplexed expanded address/data bus. When used in this mode, it does not require pullups.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 79  | P0.5/AD5         | a mode, it does not require punicps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 77  | P0.6/AD6         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 75  | P0.7/AD7         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 15  | P1.0             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 17  | P1.1             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 19  | P1.2             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 21  | P1.3             | Demonstration of the Post of t |  |  |  |  |

| 25  | P1.4             | General-Purpose I/O Port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| 27  | P1.5             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 29  | P1.6             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 31  | P1.7             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 49  | P2.0/A8          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |