#### **Features**

- · Industry-standard architecture

- Emulates Many 20-pin PALs<sup>®</sup>

- Low-cost, easy to use software tools

- High speed electrically-erasable programmable logic devices (EE PLD)

- 5ns maximum pin-to-pin delay

- Low power, 100µA pin controlled power-down mode option

- CMOS and TTL compatible inputs and outputs

- I/O pin keeper circuits

- Advanced flash technology

- Reprogrammable

- 100% tested

- High reliability CMOS process

- 20 year data retention

- 100 erase/write cycles

- 2,000V ESD protection

- 200mA latchup immunity

- Commercial and industrial temperature ranges

- Dual-in-line and surface mount packages in standard pinouts

- PCI compliant

- Green (ROHS compliant) package options available

#### Description

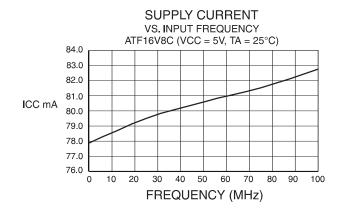

The Atmel® ATF16V8C is a high performance EECMOS programmable logic device (PLD) that utilizes the Atmel proven electrically-erasable (EE) Flash memory technology. Offered options include speeds down to 5ns and a 100 $\mu$ A pin-controlled power-down mode. All speed ranges are specified over the full 5V  $\pm$  10% range for industrial temperature ranges, and 5V  $\pm$  5% for commercial range 5V devices.

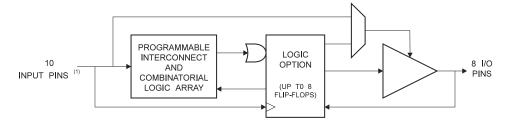

The ATF16V8C incorporates a superset of the generic architectures, which allows direct replacement of the 16R8 family and most 20-pin combinatorial PLDs. Eight outputs are each allocated eight product terms. Three different modes of operation are configured automatically with software, and allow highly complex logic functions to be realized.

The ATF16V8C can significantly reduce total system power, thereby enhancing system reliability and reducing power supply costs. When pin 4 is configured as the power-down control pin, supply current drops to less than 100µA whenever the pin is high. If the power-down feature isn't required for a particular application, pin 4 may be used as a logic input. Also, the pin-keeper circuits eliminate the need for internal pull-up resistors along with their attendant power consumption.

High Performance Electrically-erasable Programmable Logic Devices

Atmel ATF16V8C

Figure 0-1. Block diagram

Note: 1. Includes optional PD control pin

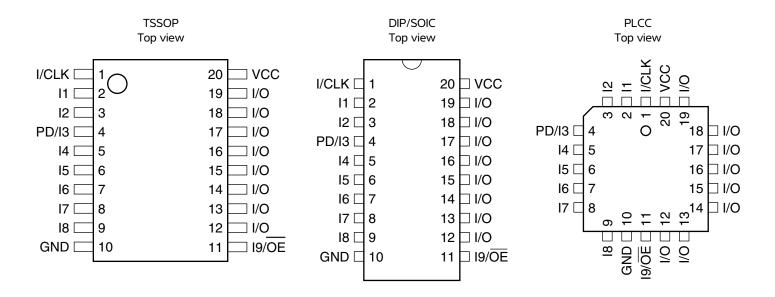

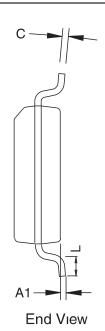

Figure 0-2. Pin configurations

| Pin name        | Function              |

|-----------------|-----------------------|

| CLK             | Clock                 |

| Ţ               | Logic inputs          |

| I/O             | Bidirectinoal buffers |

| ŌE              | Output enable         |

| V <sub>CC</sub> | +5V supply            |

| PD              | Power-down            |

#### Absolute maximum ratings\* 1.

| Temperature under bias40°C to +85°C                                                          |

|----------------------------------------------------------------------------------------------|

| Storage temperature65°C to +150°C                                                            |

| Voltage on any pin with respect to ground2.0V to +7.0V <sup>(1)</sup>                        |

| Voltage on input pins with respect to ground during programming2.0V to +14.0V <sup>(1)</sup> |

| Programming voltage with respect to ground2.0V to +14.0V <sup>(1)</sup>                      |

\*NOTICE: Stresses beyond those listed under "Absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note:

1. Minimum voltage is -0.6V DC, which may undershoot to -2.0V for pulses of less than 20ns. Maximum output pin voltage is  $V_{CC}$  + 0.75V DC, which may overshoot to 7.0V for pulses of less than 20ns.

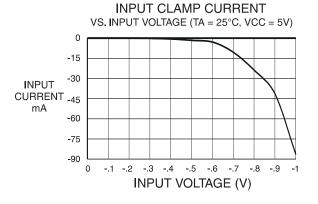

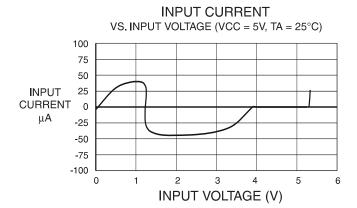

#### 2. DC and AC characteristics

Table 2-1. DC and AC operating conditions

|                                 | Commercial | Industrial   |

|---------------------------------|------------|--------------|

| Operating temperature (Ambient) | 0°C − 70°C | -40°C - 85°C |

| V <sub>CC</sub> power supply    | 5V ± 5%    | 5V ± 10%     |

Table 2-2. DC characteristics

| Symbol                          | Parameter                         | Condition                                             | Condition                   |      | Тур | Max                 | Units |

|---------------------------------|-----------------------------------|-------------------------------------------------------|-----------------------------|------|-----|---------------------|-------|

| I <sub>IL</sub>                 | Input or I/O low leakage current  | $0 \le V_{IN} \le V_{IL} $ (Max)                      |                             |      |     | -10.0               | μA    |

| I <sub>IH</sub>                 | Input or I/O high leakage current | $3.5 \le V_{IN} \le V_{CC}$                           |                             |      |     | 10.0                | μA    |

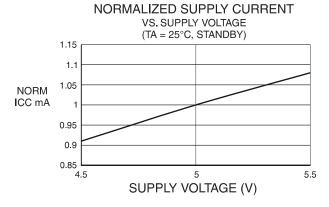

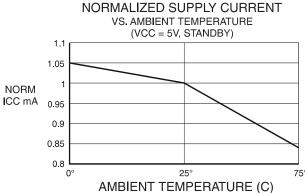

| . (1)                           | Downer gupply gurrent standby     | 15MHz, $V_{CC} = Max$ ,                               | Com.                        |      |     | 115                 | mΑ    |

| l <sub>CC1</sub> <sup>(1)</sup> | Power supply current, standby     | $V_{IN} = 0$ , $V_{CC}$ , outputs open                | Ind.                        |      |     | 130                 | mA    |

|                                 | Power supply current,             | \/ \ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\              | Com.                        |      | 10  | 100                 | μA    |

| I <sub>PD</sub>                 | Power-down mode                   | $V_{CC} = Max$ , $V_{IN} = 0$ , $V_{CC}$              | Ind.                        |      | 10  | 105                 | μA    |

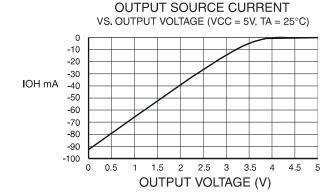

| I <sub>OS</sub>                 | Output short circuit current      | $V_{OUT} = 0.5V;$<br>$V_{CC} = 5V; T_A = 25^{\circ}C$ |                             |      |     | -150                | mA    |

| V <sub>IL</sub>                 | Input low voltage                 | Min < V <sub>CC</sub> < Max                           | Min < V <sub>CC</sub> < Max |      |     | 0.8                 | V     |

| V <sub>IH</sub>                 | Input high voltage                |                                                       |                             | 2.0  |     | V <sub>CC</sub> + 1 | V     |

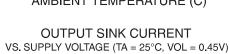

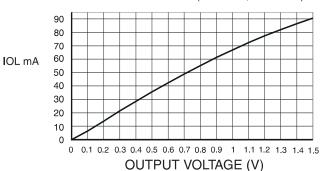

| V <sub>OL</sub>                 | Output low voltage                | $V_{CC} = Min; All outputs$ $I_{OL} = 24mA$           |                             |      |     | 0.5                 | V     |

| V <sub>OH</sub>                 | Output high voltage               | $V_{CC} = Min$ $I_{OL} = -4.0mA$                      |                             | 2.4  |     |                     | V     |

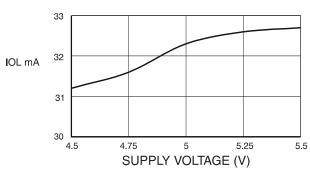

| 1                               | Output love ourroat               | \/ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                | Com.                        | 24.0 |     |                     | mA    |

| l <sub>OL</sub>                 | Output low current $V_{CC} = Min$ |                                                       | Ind.                        | 12.0 |     |                     | mA    |

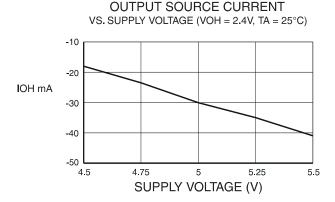

| I <sub>OH</sub>                 | Output high current               | V <sub>CC</sub> = Min                                 | Com., Ind.                  | -4.0 |     |                     | mA    |

Note: 1. All  $I_{CC}$  parameters measured with outputs open

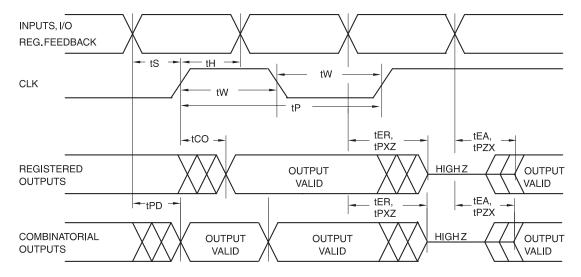

Figure 3. AC waveforms

Note: 1. Timing measurement reference is 1.5V. Input AC driving levels are 0.0V and 3.0V, unless otherwise specified.

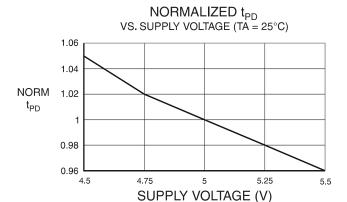

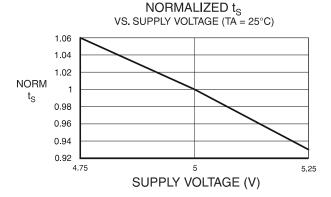

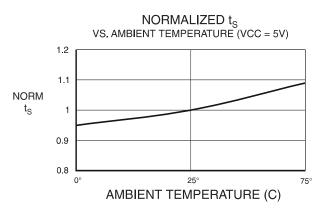

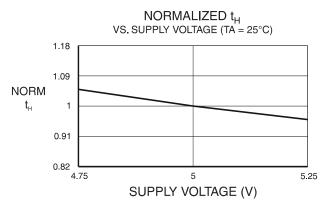

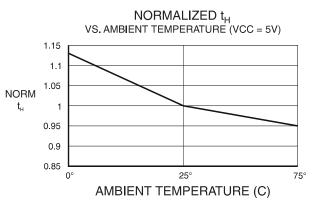

Table 3-1. AC characteristics

|                  |                                            | -   | -5  |     | -7  |     | 10  |       |

|------------------|--------------------------------------------|-----|-----|-----|-----|-----|-----|-------|

| Symbol           | Parameter                                  |     | Max | Min | Max | Min | Max | Units |

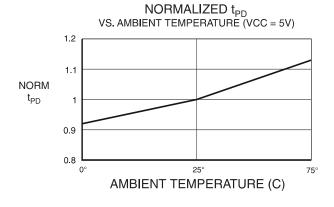

| t <sub>PD</sub>  | Input or feedback to non-registered output |     | 5   | 3   | 7.5 | 3   | 10  | ns    |

| t <sub>CF</sub>  | Clock to feedback                          |     | 3   |     | 3   |     | 6   | ns    |

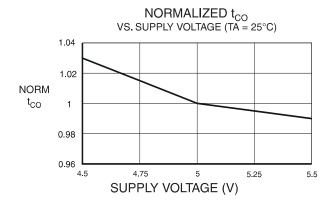

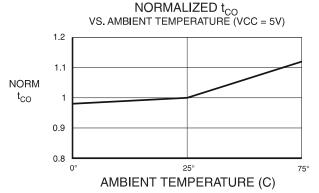

| t <sub>CO</sub>  | Clock to output                            | 1   | 4   | 2   | 5   | 2   | 7   | ns    |

| t <sub>S</sub>   | Input or feedback setup time               | 3   |     | 5   |     | 7.5 |     | ns    |

| t <sub>H</sub>   | Input hold time                            |     |     | 0   |     | 0   |     | ns    |

| t <sub>P</sub>   | Clock period                               | 6   |     | 8   |     | 12  |     | ns    |

| t <sub>W</sub>   | Clock width                                | 3   |     | 4   |     | 6   |     | ns    |

|                  | External feedback $1/(t_S + t_{CO})$       |     | 142 |     | 100 |     | 68  | MHz   |

| $f_{MAX}$        | Internal feedback $1/(t_S + t_{CF})$       |     | 166 |     | 125 |     | 74  | MHz   |

|                  | No feedback 1/(t <sub>P</sub> )            |     | 166 |     | 125 |     | 83  | MHz   |

| t <sub>EA</sub>  | Input to output enable – product term      | 2   | 6   | 3   | 9   | 3   | 10  | ns    |

| t <sub>ER</sub>  | Input to output disable – product term     | 2   | 5   | 2   | 9   | 2   | 10  | ns    |

| t <sub>PZX</sub> | OE pin to output enable                    |     | 5   | 2   | 6   | 2   | 10  | ns    |

| t <sub>PXZ</sub> | OE pin to output disable                   | 1.5 | 5   | 1.5 | 6   | 1.5 | 10  | ns    |

Table 3-2. Power-down AC characteristics<sup>(1)(2)(3)</sup>

|                   |                                | -5  |      | -7  |      | -10 |     |       |

|-------------------|--------------------------------|-----|------|-----|------|-----|-----|-------|

| Symbol            | Parameter                      | Min | Max  | Min | Max  | Min | Max | Units |

| t <sub>IVDH</sub> | Valid Input before PD High     | 5.0 |      | 7.5 |      | 10  |     | ns    |

| t <sub>GVDH</sub> | Valid OE before PD High        | 0   |      | 0   |      | 0   |     | ns    |

| t <sub>CVDH</sub> | Valid Clock before PD High     | 0   |      | 0   |      | 0   |     | ns    |

| t <sub>DHIX</sub> | Input Don't Care after PD High |     | 5.0  |     | 7.5  |     | 10  | ns    |

| t <sub>DHGX</sub> | OE Don't Care after PD High    |     | 5.0  |     | 7.5  |     | 10  | ns    |

| t <sub>DHCX</sub> | Clock Don't Care after PD High |     | 5.0  |     | 7.5  |     | 10  | ns    |

| t <sub>DLIV</sub> | PD Low to Valid Input          |     | 5.0  |     | 7.5  |     | 10  | ns    |

| t <sub>DLGV</sub> | PD Low to Valid OE             |     | 15.0 |     | 20.0 |     | 25  | ns    |

| t <sub>DLCV</sub> | PD Low to Valid Clock          |     | 15.0 |     | 20.0 |     | 25  | ns    |

| t <sub>DLOV</sub> | PD Low to Valid Output         |     | 20.0 |     | 25.0 |     | 30  | ns    |

Note:

- 1. Output data is latched and held

- 2. HI-Z outputs remain HI-Z

- 3. Clock and input transitions are ignored

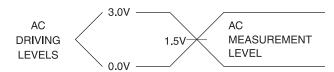

## 4. Input test waveforms and measurement levels:

$t_{R}$ ,  $t_{F}$  < 1.5ns (10% to 90%)

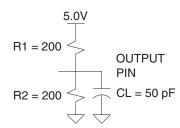

# 5. Output test loads

# 6. Pin capacitance

Table 6-1. Pin capacitance

|                  | Тур | Max | Units | Conditions            |

|------------------|-----|-----|-------|-----------------------|

| C <sub>IN</sub>  | 5   | 8   | pF    | $V_{IN} = OV$         |

| C <sub>OUT</sub> | 6   | 8   | pF    | V <sub>OUT</sub> = 0V |

Note: 1. Typical values for nominal supply voltage. This parameter is only sampled and is not 100% tested.

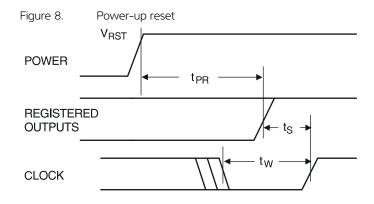

#### 7. Power-up reset

Registers of the ATF16V8C are designed to reset during power-up. At a point delayed slightly from  $V_{CC}$  crossing  $V_{RST}$ , all registers will be reset to the low state. As a result, the registered output state will always be high on power-up.

This feature is critical for state machine initialization. However, due to the asynchronous nature of reset and the uncertainty of how  $V_{CC}$  actually rises in the system, the following conditions are required:

- 1. The  $V_{CC}$  rise must be monotonic, from below 0.7V

- 2. After reset occurs, all input and feedback setup times must be met before driving the clock term high, and

- 3. The signals from which the clock is derived must remain stable during  $t_{PR}$

Table 8-1. Power-up reset parameters

| Parameter        | Description               | Тур | Max   | Units |

|------------------|---------------------------|-----|-------|-------|

| t <sub>PR</sub>  | Power-up<br>Reset Time    | 600 | 1,000 | ns    |

| V <sub>RST</sub> | Power-up<br>Reset Voltage | 3.8 | 4.5   | V     |

#### 9. Power-down mode

The ATF16V8C includes an optional pin controlled powerdown feature. Device pin 4 may be configured as the powerdown pin. When this feature is enabled and the power-down pin is high, total current consumption drops to less than 100µA. In the power-down mode, all output data and internal logic states are latched and held. All registered and combinatorial output data remains valid. Any outputs that were in a high-Z state at the onset of power-down will remain at high-Z. During power-down, all input signals except the power-down pin are blocked. The input and I/O pin-keeper circuits remain active to insure that pins do not float to indeterminate levels. This helps to further reduce system power.

Selection of the power-down option is specified in the ATF16V8C logic design file. The logic compiler will include this option selection in the otherwise standard 16V8 JEDEC fuse file. When the power-down feature is not specified in the design file, pin 4 is available as a logic input, and there is no power-down pin. This allows the ATF16V8C to be programmed using any existing standard 16V8 fuse file.

Note: Some programmers list the JEDEC-compatible 16V8C (No PD used) separately from the non-JEDEC compatible 16V8CEXT. (EXT for extended features.)

# 10. Registered output preload

Registers of the ATF16V8C are provided with circuitry to allow loading of each register with either a high or a low. This feature will simplify testing since any state can be forced into the registers to control test sequencing. A JEDEC file with preload is generated when a source file with vectors is compiled. Once downloaded, the JEDEC file preload sequence will be done automatically by approved programmers.

#### 11. Security fuse usage

A single fuse is provided to prevent unauthorized copying of the ATF16V8C fuse patterns. Once programmed, fuse verify and preload are inhibited. However, the 64-bit user signature remains accessible.

The security fuse will be programmed last, as its effect is immediate.

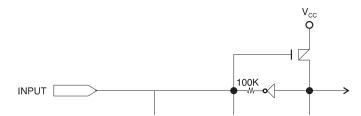

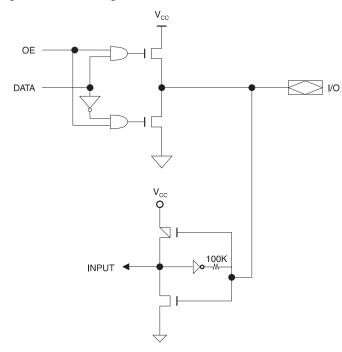

### 12. Input and I/O pin-keeper circuits

The ATF16V8C contains internal input and I/O pin-keeper circuits. These circuits allow each ATF16V8C pin to hold its previous value even when it is not being driven by an external source or by the device's output buffer. This helps insure that all logic array inputs are at known, valid logic levels. This reduces system power by preventing pins from floating to indeterminate levels. By using pin-keeper circuits rather than pull-up resistors, there is no DC current required to hold the pins in either logic state (high or low).

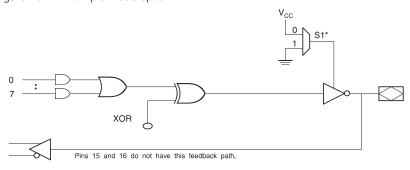

These pin-keeper circuits are implemented as weak feedback inverters, as shown in the Input Diagram below. These keeper circuits can easily be overdriven by standard TTL- or CMOS-compatible drivers. The typical overdrive current required is  $40\mu$ A.

Figure 13. Input diagram

Figure 14. I/O diagram

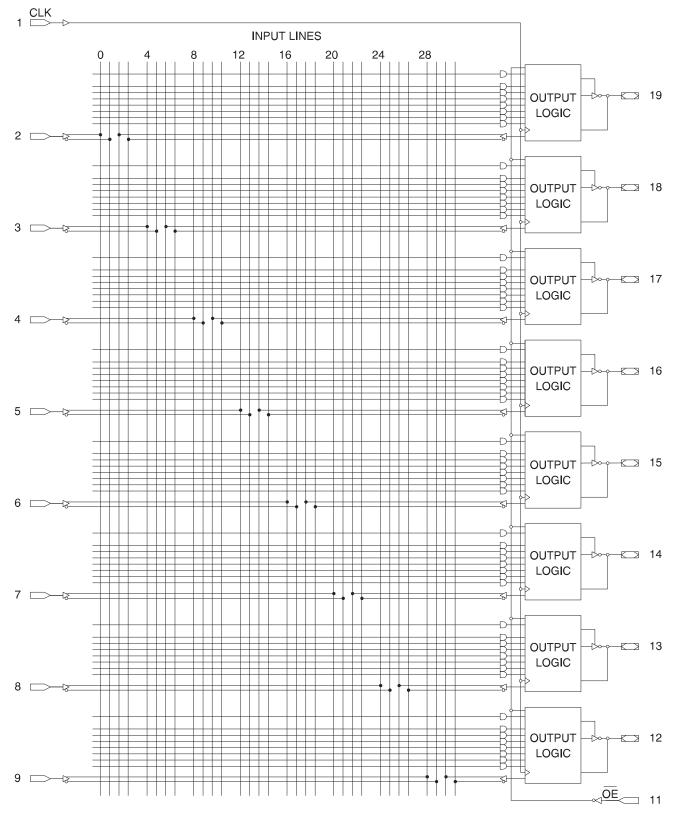

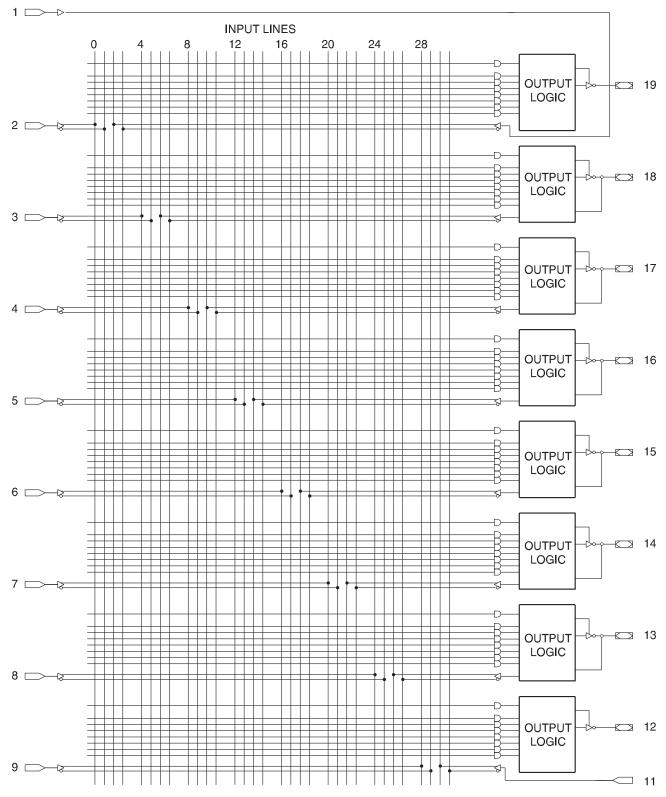

#### 15. Functional logic diagram description

The logic option and functional diagrams describe the ATF16V8C architecture. Eight configurable macrocells can be configured as a registered output, combinatorial I/O, combinatorial output, or dedicated input.

The ATF16V8C can be configured in one of three different modes. Each mode makes the ATF16V8C look like a different device. Most PLD compilers can choose the right mode automatically. The user can also force the selection by supplying the compiler with a mode selection. The determining factors would be the usage of register versus combinatorial outputs and dedicated outputs versus outputs with output enable control.

The ATF16V8C universal architecture can be programmed to emulate many 20-pin PAL devices. These architectural subsets can be found in each of the configuration modes described in the following pages. The user can download the listed subset device JEDEC programming file to the PLD programmer, and the ATF16V8C can be configured to act like the chosen device. Check with your programmer manufacturer for this capability.

Unused product terms are automatically disabled by the compiler to decrease power consumption. A security fuse, when programmed, protects the content of the ATF16V8C. Eight bytes (64 fuses) of user signature are accessible to the user for purposes such as storing project name, part number, revision, or date. The user signature is accessible regardless of the state of the security fuse.

|                       | Registered               | Complex                   | Simple                    | Auto select                      |

|-----------------------|--------------------------|---------------------------|---------------------------|----------------------------------|

| ABEL, Atmel-ABEL      | P16V8R                   | P16V8C                    | P16V8AS                   | P16V8                            |

| With PD ENABLE        | P16V8PDR <sup>(1)</sup>  | P16V8PDC <sup>(1)</sup>   | P16V8PD <sup>(1)</sup>    | P16V8PDS <sup>(1)</sup>          |

| CUPL, Atmel-CUPL      | G16V8MS                  | G16V8MA                   | G16V8AS                   | G16V8A                           |

| With PD ENABLE        | G16V8CPMS                | G16V8CPMA                 | G16V8CPAS                 | G16V8CP                          |

| LOG/iC                | GAL16V8_R <sup>(2)</sup> | GAL16V8_C7 <sup>(2)</sup> | GAL16V8_C8 <sup>(2)</sup> | GAL16V8                          |

| OrCAD-PLD             | "Registered"             | "Complex"                 | "Simple"                  | GAL16V8A                         |

| PLDesigner            | P16V8R                   | P16V8C                    | P16V8C                    | P16V8A                           |

| Synario/Atmel-Synario | NA                       | NA                        | NA                        | ATF16V8C ALL                     |

| With PD ENABLE        | NA                       | NA                        | NA                        | ATF16V8C (PD) ALL <sup>(1)</sup> |

| Tango-PLD             | G16V8R                   | G16V8C                    | G16V8AS                   | G16V8                            |

Table 15-1. Compiler mode selection

Note:

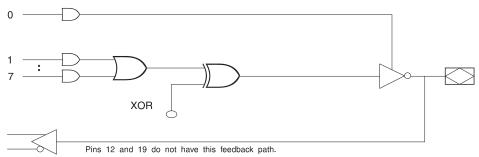

# 16. Macrocell configuration

Software compilers support the three different OMC modes as different device types. These device types are listed in the table below. Most compilers have the ability to automatically select the device type, generally based on the register usage and output enable  $(\overline{OE})$  usage. Register usage on the device forces the software to choose the registered mode. All combinatorial outputs with  $\overline{OE}$  controlled by the product term will force the software to choose the complex mode. The software will choose the simple mode only when all outputs are dedicated combinatorial without  $\overline{OE}$  control. The different device types listed in the table can be used to override the automatic device selection by the software. For further details, refer to the compiler software manuals.

When using compiler software to configure the device, the user must pay special attention to the following restrictions in each mode.

In **registered mode**, pin 1 and pin 11 are permanently configured as clock and output enable, respectively. These pins cannot be configured as dedicated inputs in the registered mode.

In **complex mode**, pin 1 and pin 11 become dedicated inputs and use the feedback paths of pin 19 and pin 12 respectively. Because of this feedback path usage, pin 19 and pin 12 do not have the feedback option in this mode.

<sup>1.</sup> Please call Atmel PLD Hotline at (408) 436-4333 for more information

<sup>2.</sup> Only applicable for version 3.4 or lower

In **simple mode**, all feedback paths of the output pins are routed via the adjacent pins. In doing so, the two inner most pins (pins 15 and 16) will not have the feedback option as these pins are always configured as dedicated combinatorial output.

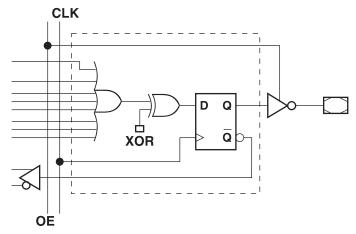

#### 16.1 Atmel ATF16V8C registered mode

**PAL device emulation/PAL replacement.** The registered mode is used if one or more registers are required. Each macrocell can be configured as either a registered or combinatorial output or I/O, or as an input. For a registered output or I/O, the output is enabled by the  $\overline{OE}$  pin, and the register is clocked by the CLK pin. Eight product terms are allocated to the sum term. For a combinatorial output or I/O, the output enable is controlled by a product term, and seven product terms are allocated to the sum term. When the macrocell is configured as an input, the output enable is permanently disabled.

Any register usage will make the compiler select this mode. The following registered devices can be emulated using this mode:

| 16R8 | 16RP8 |

|------|-------|

| 16R6 | 16RP6 |

| 16R4 | 16RP4 |

Figure 17. Registered configuration for registered mode<sup>(1)(2)</sup>

Notes:

1. Pin 1 controls common CLK for the registered outputs.

Pin 11 controls common  $\overline{OE}$  for the registered outputs.

Pin 1 and Pin 11 are permanently configured as CLK and  $\overline{OE}$ .

2. The development software configures all the architecture control bits and checks for proper pin usage automatically.

Figure 18. Combinatorial configuration for registered mode<sup>(1)(2)</sup>

Notes: 1. Pin 1 and Pin 11 are permanently configured as CLK and  $\overline{OE}$ .

2. The development software configures all the architecture control bits and checks for proper pin usage automatically.

Figure 19. Registered mode logic diagram

Note: \* Input not available if power-down mode is enabled

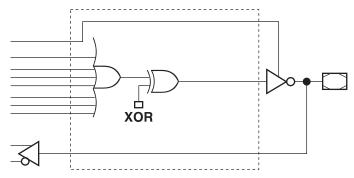

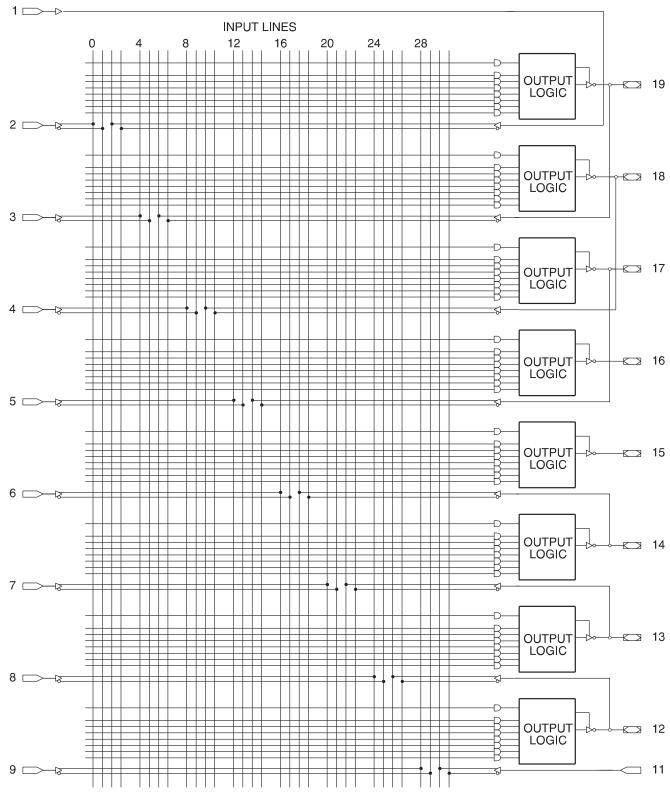

#### 20. Atmel ATF16V8C complex mode

**PAL device emulation/PAL replacement.** In the complex mode, combinatorial output and I/O functions are possible. Pins 1 and 11 are regular inputs to the array. Pins 13 through 18 have pin feedback paths back to the AND-array, which makes full I/O capability possible. Pins 12 and 19 (outermost macrocells) are outputs only. They do not have input capability. In this mode, each macrocell has seven product terms going to the sum term and one product term enabling the output.

Combinatorial applications with an  $\overline{\text{OE}}$  requirement will make the compiler select this mode. The following devices can be emulated using this mode:

16L8 16H8 16P8

Figure 21. Complex Mode Option

## 22. Atmel ATF16V8C simple mode

**PAL device emulation/PAL replacement.** In the simple mode, eight product terms are allocated to the sum term. Pins 15 and 16 (center macrocells) are permanently configured as combinatorial outputs. Other macrocells can be either inputs or combinatorial outputs with pin feedback to the AND-array. Pins 1 and 11 are regular inputs.

The compiler selects this mode when all outputs are combinatorial without  $\overline{OE}$  control. The following simple PALs can be emulated using this mode:

10L8 10H8 10P8 12L6 12H6 12P6 14L4 14H4 14P4 16L2 16H2 16P2

Figure 23. Simple mode option

\* - Pins 15 and 16 are always enabled.

Figure 24. Complex mode logic diagram

Note: \* Input not available if power-down mode is enabled

Note: Simple mode logic diagram

Note: \* Input not available if power-down mode is enabled

# 25. Ordering information

| t <sub>PD</sub> (ns) | t <sub>S</sub> (ns) | t <sub>CO</sub> (ns) | Atmel ordering code*                                             | Package                   | Operation range               |

|----------------------|---------------------|----------------------|------------------------------------------------------------------|---------------------------|-------------------------------|

| 5                    | 3                   | 4                    | ATF16V8C-5JX                                                     | 20J                       | Commercial<br>(0°C to 70°C)   |

| 7.5                  | 5                   | 5                    | ATF16V8C-7JU<br>ATF16V8C-7PU<br>ATF16V8C-7SU                     | 20J<br>20P3<br>20S        | Industrial<br>(-40°C to 85°C) |

| 5                    | 3                   | 4                    | ATF16V8C-5JC                                                     | 20J                       | Commercial<br>(0°C to 70°C)   |

| 7.5                  | _                   | _                    | ATF 16V8C-7JC<br>ATF 16V8C-7PC<br>ATF 16V8C-7SC<br>ATF 16V8C-7XC | 20J<br>20P3<br>20S<br>20X | Commercial<br>(0°C to 70°C)   |

| 7.5                  | 5                   | 5                    | ATF 16V8C-7JI<br>ATF 16V8C-7PI<br>ATF 16V8C-7SI<br>ATF 16V8C-7XI | 20J<br>20P3<br>20S<br>20X | Industrial<br>(-40°C to 85°C) |

| 10                   | 7.5                 | 7                    | ATF16V8C-10JI                                                    | 20Ј                       | Industrial<br>(-40°C to 85°C) |

Using "C" Product for Industrial

To use commercial product for Industrial temperature ranges, down-grade one speed grade from the "I" to the "C" device (7ns "C" = 10ns "I") and de-rate power by 30%.

Notes

- 1. \*Shaded parts are being obsoleted in 2011

- 2. The suffix, "U" and "X" as part of the ordering code, implies the package is ROHS compliant and lead free

|      | Package type                                                    |  |  |  |

|------|-----------------------------------------------------------------|--|--|--|

| 20J  | 20-lead, Plastic J-leaded Chip Carrier (PLCC)                   |  |  |  |

| 20P3 | 20-lead, 0.300 " Wide, Plastic Dual Inline Package (PDIP)       |  |  |  |

| 20S  | 20-lead, 0.300" Wide, Plastic Gull-Wing Small Outline (SOIC)    |  |  |  |

| 20X  | 20-lead, 4.4 mm Wide, Plastic Thin Shrink Small Outline (TSSOP) |  |  |  |

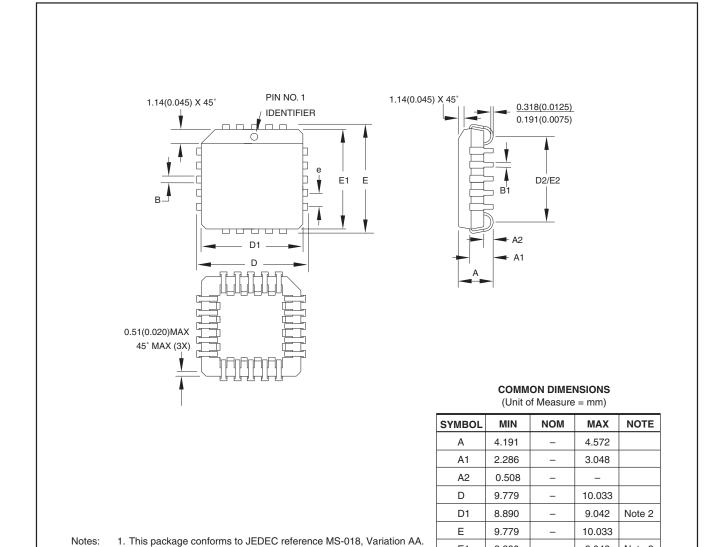

# 26. Package Drawings

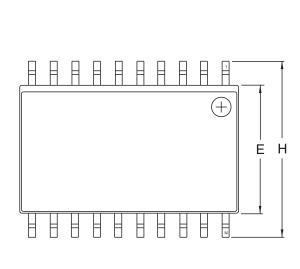

## 20J – PLCC

10/04/01

2325 Orchard Parkway San Jose, CA 95131 **TITLE 20J**, 20-lead, Plastic J-leaded Chip Carrier (PLCC)

2. Dimensions D1 and E1 do not include mold protrusion.

material condition at the upper or lower parting line. 3. Lead coplanarity is 0.004" (0.102 mm) maximum.

Allowable protrusion is .010"(0.254 mm) per side. Dimension D1

and E1 include mold mismatch and are measured at the extreme

E1

D2/E2

В

е

8.890

7.366

0.660

0.330

DRAWING NO. REV.

Note 2

9.042

8.382

0.813

0.533

1.270 TYP

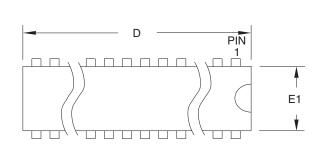

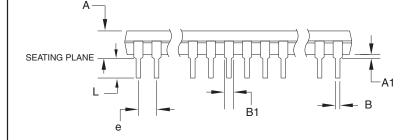

### 20P3 - PDIP

Notes:

- 1. This package conforms to JEDEC reference MS-001, Variation AD.

- Dimensions D and E1 do not include mold Flash or Protrusion. Mold Flash or Protrusion shall not exceed 0.25 mm (0.010").

### COMMON DIMENSIONS

(Unit of Measure = mm)

| SYMBOL | MIN       | NOM | MAX    | NOTE   |

|--------|-----------|-----|--------|--------|

| Α      | _         | _   | 5.334  |        |

| A1     | 0.381     | _   | _      |        |

| D      | 24.892    | _   | 26.924 | Note 2 |

| E      | 7.620     | _   | 8.255  |        |

| E1     | 6.096     | _   | 7.112  | Note 2 |

| В      | 0.356     | _   | 0.559  |        |

| B1     | 1.270     | _   | 1.551  |        |

| L      | 2.921     | _   | 3.810  |        |

| С      | 0.203     | _   | 0.356  |        |

| eB     | _         | _   | 10.922 |        |

| eC     | 0.000     | _   | 1.524  |        |

| е      | 2.540 TYP |     |        |        |

1/23/04

2325 Orchard Parkway San Jose, CA 95131 **TITLE 20P3**, 20-lead (0.300"/7.62 mm Wide) Plastic Dual Inline Package (PDIP)

DRAWING NO. 20P3 REV.

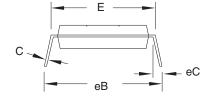

### 20S - SOIC

Side View

### **COMMON DIMENSIONS**

(Unit of Measure - mm)

| SYMBOL | MIN   | NOM     | MAX   | NOTE |

|--------|-------|---------|-------|------|

| Α      | 2.35  |         | 2.65  |      |

| A1     | 0.10  |         | 0.30  |      |

| b      | 0.33  |         | 0.51  | 4    |

| С      | 0.23  |         | 0.32  |      |

| D      | 12.60 |         | 13.00 | 1    |

| Е      | 7.40  |         | 7.60  | 2    |

| Н      | 10.00 |         | 10.65 |      |

| L      | 0.40  |         | 1.27  | 3    |

| е      |       | 1.27 BS | С     |      |

- Notes. 1. This drawing is for general information only; refer to JEDEC Drawing MS-013, Variation AC for additional information.

2. Dimension 'D' does not include mold Flash, protrusions or gate burrs. Mold Flash, protrusions and gate burrs shall not exceed 0.15 mm (0.006') per side.

- 3. Dimension 'E' does not include inter-lead Flash or protrusion. Inter-lead Flash and protrusions shall not exceed 0.25 mm

- (0.010') per side.

4. 'L' is the length of the terminal for soldering to a substrate.

5. The lead width 'b', as measured 0.36 mm (0.014') or greater above the seating plane, shall not exceed a maximum value of 0.61 mm

(0.004') per side. (0.024') per side.

|                                            |                                                                                            | DRAWING NO. | REV. |

|--------------------------------------------|--------------------------------------------------------------------------------------------|-------------|------|

| 2325 Orchard Parkway<br>San Jose, CA 95131 | <b>20S2</b> , 20-lead, 0.300' Wide Body, Plastic Gull<br>Wing Small Outline Package (SOIC) | 20S2        | В    |

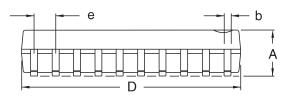

### 20X - TSSOP

Dimensions in Millimeters and (Inches). Controlling dimension: Millimeters. JEDEC Standard MO-153 AC INDEX MARK PIN 4.50 (0.177) 6.50 (0.256) 4.30 (0.169) 6.25 (0.246) 6.60 (.260) 1.20 (0.047) MAX 6.40 (.252) 0.65 (.0256) BSC -> 0.15 (0.006) **SEATING** 0.30 (0.012) 0.19 (0.007) 0.05 (0.002) PLANE 0.20 (0.008) 0.09 (0.004) 0.75 (0.030) 0.45 (0.018) 10/23/03 DRAWING NO. TITLE REV. 2325 Orchard Parkway 20X, (Formerly 20T), 20-lead, 4.4 mm Body Width, 20X С San Jose, CA 95131

Plastic Thin Shrink Small Outline Package (TSSOP)

# 27. Revision history

| Doc. rev. | Date    | Comments                                          |  |

|-----------|---------|---------------------------------------------------|--|

| 0425H     | 03/2011 | Added green (ROHS compliant) package options      |  |

|           |         | Removed lead based packaged from ordering section |  |

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131 USA

**Tel:** (+1) (408) 441-0311 **Fax:** (+1) (408) 487-2600

www.atmel.com

Atmel Asia Limited

Unit 01-5 & 16, 19F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon HONG KONG

**Tel:** (+852) 2245-6100 **Fax:** (+852) 2722-1369

Atmel Munich GmbH

Business Campus Parkring 4 D-85748 Garching b. Munich GERMANY

**Tel:** (+49) 89-31970-0 **Fax:** (+49) 89-3194621

Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 JAPAN

**Tel:** (+81) (3) 3523-3551 **Fax:** (+81) (3) 3523-7581

Atmel<sup>®</sup>, logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estopped or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMERS NO LLABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR SATUTORY WARRANTY EXPRESS, IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NOW-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.