# WCSS0418V1P

# 256K x 18 Synchronous-Pipelined Cache RAM

## **Features**

- Supports 100-MHz bus for Pentium<sup>®</sup> and PowerPC<sup>™</sup> operations with zero wait states

- Fully registered inputs and outputs for pipelined operation

- 256K by 18 common I/O architecture

- 3.3V core power supply

- 2.5V / 3.3V I/O operation

- · Fast clock-to-output times

- -3.5 ns (for 166-MHz device)

- -4.0 ns (for 133-MHz device)

- -5.5 ns (for 100-MHz device)

- User-selectable burst counter supporting Intel®

Pentium interleaved or linear burst sequences

- · Separate processor and controller address strobes

- · Synchronous self-timed writes

- Asynchronous Output Enable

- JEDEC-standard 100 TQFP pinout

- "ZZ" Sleep Mode option and Stop Clock option

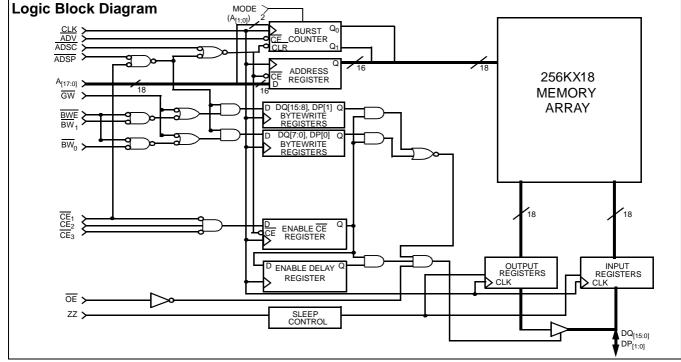

#### **Functional Description**

The WCSS0418V1P is a 3.3V, 256K by 18 synchronous-pipelined cache SRAM designed to support zero wait state secondary cache with minimal glue logic. The WCSS0418V1P I/O pins can operate at either the 2.5V or the 3.3V level. The I/O pins are 3.3V tolerant when V\_D\_DQ=2.5V.

All synchronous inputs pass through input registers controlled by the rising edge of the clock. All data outputs pass through output registers controlled by the rising edge of the clock. Maximum access delay from the clock rise is 3.5 ns (166-MHz device).

The WCSS0418V1P supports either the interleaved burst sequence used by the Intel Pentium processor or a linear burst sequence used by processors such as the PowerPC. The burst sequence is selected through the MODE pin. Accesses can be initiated by asserting either the Processor Address Strobe (ADSP) or the Controller Address Strobe (ADSC) at clock rise. Address advancement through the burst sequence is controlled by the ADV input. A 2-bit on-chip wraparound burst counter captures the first address in a burst sequence and automatically increments the address for the rest of the burst access.

Byte write operations are qualified with the four Byte Write Select  $(\overline{BW}_{[1:0]})$  inputs. A Global Write Enable  $(\overline{GW})$  overrides all byte write inputs and writes data to all four bytes. All writes are conducted with on-chip synchronous self-timed write circuitry.

Three synchronous Chip Selects ( $\overline{CE}_1$ ,  $CE_2$ ,  $\overline{CE}_3$ ) and an asynchronous Output Enable ( $\overline{OE}$ ) provide for easy bank selection and output three-state control. In order to provide proper data during depth expansion,  $\overline{OE}$  is masked during the first clock of a read cycle when emerging from a deselected state.

Intel and Pentium are registered trademarks of Intel Corporation. PowerPC is a trademark of IBM Corporation.

## **Selection Guide**

|                                   |            | -166 | -133 | -100 |

|-----------------------------------|------------|------|------|------|

| Maximum Access Time (ns)          |            | 3.5  | 4.0  | 5.5  |

| Maximum Operating Current (mA)    | Commercial | 420  | 375  | 325  |

| Maximum CMOS Standby Current (mA) | Commercial | 10   | 10   | 10   |

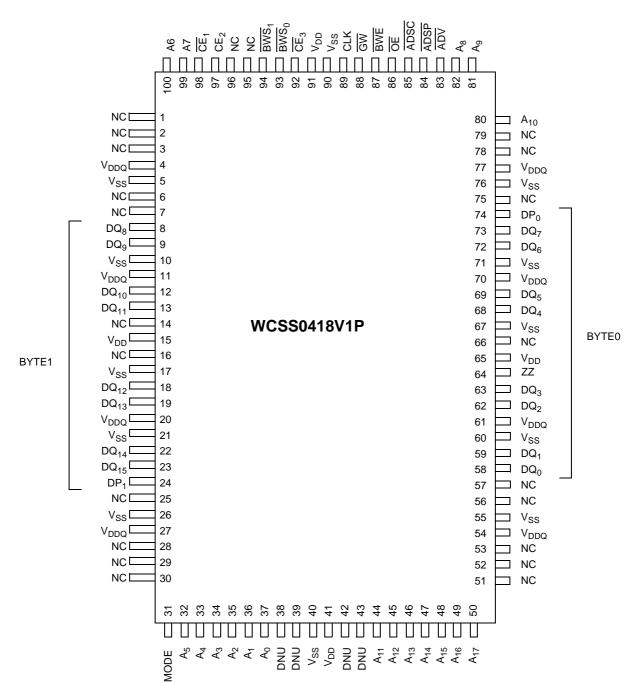

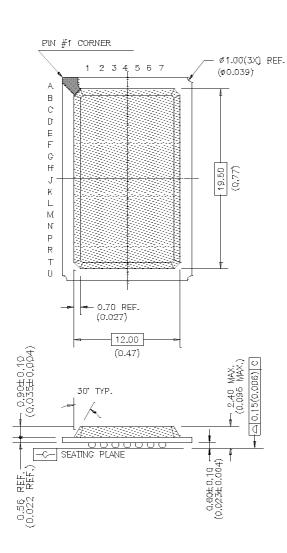

## **Pin Configurations**

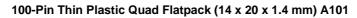

## 100-Lead TQFP

# Pin Configurations (continued)

|   | 1                | 2               | 3               | 4               | 5               | 6               | 7                |

|---|------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------|

| Α | V <sub>DDQ</sub> | А               | А               | ADSP            | А               | Α               | V <sub>DDQ</sub> |

| В | NC               | CE <sub>2</sub> | Α               | ADSC            | А               | CE <sub>3</sub> | NC               |

| С | NC               | Α               | А               | $V_{DD}$        | А               | А               | NC               |

| D | DQb              | NC              | V <sub>SS</sub> | NC              | V <sub>SS</sub> | DQPa            | NC               |

| Е | NC               | DQb             | V <sub>SS</sub> | CE <sub>1</sub> | V <sub>SS</sub> | NC              | DQa              |

| F | V <sub>DDQ</sub> | NC              | V <sub>SS</sub> | OE              | V <sub>SS</sub> | DQa             | $V_{DDQ}$        |

| G | NC               | DQb             | BWb             | ADV             | V <sub>ss</sub> | NC              | DQ <sub>a</sub>  |

| Н | DQb              | NC              | V <sub>SS</sub> | GW              | V <sub>SS</sub> | DQa             | NC               |

| J | $V_{DDQ}$        | $V_{DD}$        | NC              | $V_{DD}$        | NC              | V <sub>DD</sub> | $V_{DDQ}$        |

| к | NC               | DQb             | V <sub>SS</sub> | CLK             | V <sub>SS</sub> | NC              | DQ <sub>a</sub>  |

| L | DQb              | NC              | V <sub>ss</sub> | NC              | BWa             | DQa             | NC               |

| м | V <sub>DDQ</sub> | DQb             | V <sub>SS</sub> | BWE             | V <sub>SS</sub> | NC              | V <sub>DDQ</sub> |

| Ν | DQb              | NC              | V <sub>SS</sub> | A1              | $V_{SS}$        | DQa             | NC               |

| Р | NC               | DQPb            | V <sub>SS</sub> | A0              | V <sub>SS</sub> | NC              | DQa              |

| R | NC               | Α               | MODE            | V <sub>DD</sub> | V <sub>SS</sub> | А               | NC               |

| Т | NC               | Α               | А               | NC              | А               | А               | ZZ               |

| U | $V_{DDQ}$        | NC              | NC              | NC              | NC              | NC              | V <sub>DDQ</sub> |

#### 119-Ball BGA

# **Pin Definitions**

| Name                | I/O                    | Description                                                                                                                                                                                                                                                                                                         |

|---------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A <sub>[17:0]</sub> | Input-<br>Synchronous  | Address Inputs used to select one of the 64K address locations. Sampled at the rising edge of the CLK if ADSP or ADSC is active LOW, and $\overline{CE}_1$ , $\overline{CE}_2$ , and $\overline{CE}_3$ are sampled active. A <sub>[1:0]</sub> feed the 2-bit counter.                                               |

| BW <sub>[1:0]</sub> | Input-<br>Synchronous  | Byte Write Select Inputs, active LOW. Qualified with BWE to conduct byte writes to the SRAM. Sampled on the rising edge of CLK.                                                                                                                                                                                     |

| GW                  | Input-<br>Synchronous  | Global Write Enable Input, active LOW. When asserted LOW on the rising edge of <u>CLK</u> , a global write is conducted (ALL bytes are written, regardless of the values on BW <sub>[1:0]</sub> and BWE).                                                                                                           |

| BWE                 | Input-<br>Synchronous  | Byte Write Enable Input, active LOW. Sampled on the rising edge of CLK. This signal must be asserted LOW to conduct a byte write.                                                                                                                                                                                   |

| CLK                 | Input-Clock            | Clock Input. Used to capture all synchronous inputs to the device. Also used to increment the burst counter when ADV is asserted LOW, during a burst operation.                                                                                                                                                     |

| CE <sub>1</sub>     | Input-<br>Synchronous  | Chip Enable 1 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with $CE_2$ and $CE_3$ to select/deselect the device. ADSP is ignored if $CE_1$ is HIGH.                                                                                                                                    |

| CE <sub>2</sub>     | Input-<br>Synchronous  | Chip Enable 2 Input, active HIGH. Sampled on the rising edge of CLK. Used in conjunction with $\overline{CE}_1$ and $\overline{CE}_3$ to select/deselect the device.                                                                                                                                                |

| CE <sub>3</sub>     | Input-<br>Synchronous  | Chip Enable 3 Input, active LOW. Sampled on the rising edge of CLK. Used in conjunction with $\overline{CE}_1$ and $CE_2$ to select/deselect the device.                                                                                                                                                            |

| ŌE                  | Input-<br>Asynchronous | Output Enable, asynchronous input, active LOW. Controls the direction of the I/O pins. When LOW, the I/O pin <u>s b</u> ehave as outputs. When deasserted HIGH, I/O pins are three-stated, and act as input data pins. OE is masked during the first clock of a read cycle when emerging from a deselected state.   |

| ADV                 | Input-<br>Synchronous  | Advance Input Signal, sampled on the rising edge of CLK. When asserted, it automatically incre-<br>ments the address in a burst cycle.                                                                                                                                                                              |

| ADSP                | Input-<br>Synchronous  | Address Strobe from Processor, sampled on the rising edge of CLK. When asserted LOW, $A_{[17:0]}$ is captured in the address registers. $A_{[1:0]}$ are also loaded into the burst counter. When ADSP and ADSC are both asserted, only ADSP is recognized. ASDP is ignored when CE <sub>1</sub> is deasserted HIGH. |

## Pin Definitions (continued)

| Name                                        | I/O                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ADSC                                        | Input-<br>Synchronous  | Address Strobe from Controller, sampled on the rising edge of CLK. When asserted $LOW$ , $A_{[17:0]}$ is <u>captured</u> in the address registers. $A_{[1:0]}$ are also loaded into the burst counter. When ADSP and ADSC are both asserted, only ADSP is recognized.                                                                                                                                                                                             |

| ZZ                                          | Input-<br>Asynchronous | ZZ "sleep" Input. This active HIGH input places the device in a non-time critical "sleep" condition with data integrity preserved. Leaving ZZ floating or NC will default the device into an active state. ZZ pin has an internal pull-down.                                                                                                                                                                                                                      |

| DQ <sub>[15:0]</sub><br>DP <sub>[1:0]</sub> | I/O-<br>Synchronous    | Bidirectional Data I/O lines. As inputs, they feed into an on-chip data register that is triggered by the rising edge of CLK. As outputs, they deliver the data contained in the memory location specified by $A_{[17:0]}$ during the previous clock rise of the read cycle. The direction of the pins is controlled by OE. When OE is asserted LOW, the pins behave as outputs. When HIGH, $DQ_{[15:0]}$ and $DP_{[1:0]}$ are placed in a three-state condition. |

| V <sub>DD</sub>                             | Power Supply           | Power Supply inputs to the core of the device. Should be connected to 3.3V power supply.                                                                                                                                                                                                                                                                                                                                                                          |

| V <sub>SS</sub>                             | Ground                 | Ground for the core of the device. Should be connected to ground of the system.                                                                                                                                                                                                                                                                                                                                                                                   |

| V <sub>DDQ</sub>                            | I/O Power<br>Supply    | Power Supply for the I/O circuitry. Should be connected to a 3.3V or 2.5V power supply.                                                                                                                                                                                                                                                                                                                                                                           |

| V <sub>SSQ</sub>                            | I/O Ground             | Ground for the I/O circuitry. Should be connected to ground of the system.                                                                                                                                                                                                                                                                                                                                                                                        |

| MODE                                        | Input-<br>Static       | Selects Burst Order. When tied to GND selects linear burst sequence. When tied to $V_{DDQ}$ or left floating selects interleaved burst sequence. This is a strap pin and should remain static during device operation. When left floating or NC, defaults to interleaved burst order. Mode pin has an internal pull-up.                                                                                                                                           |

| NC                                          |                        | No Connects.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

## Introduction

## **Functional Overview**

All synchronous inputs pass through input registers controlled by the rising edge of the clock. All data outputs pass through output registers controlled by the rising edge of the clock. Maximum access delay from the clock rise ( $t_{CO}$ ) is 3.5 ns (166-MHz device).

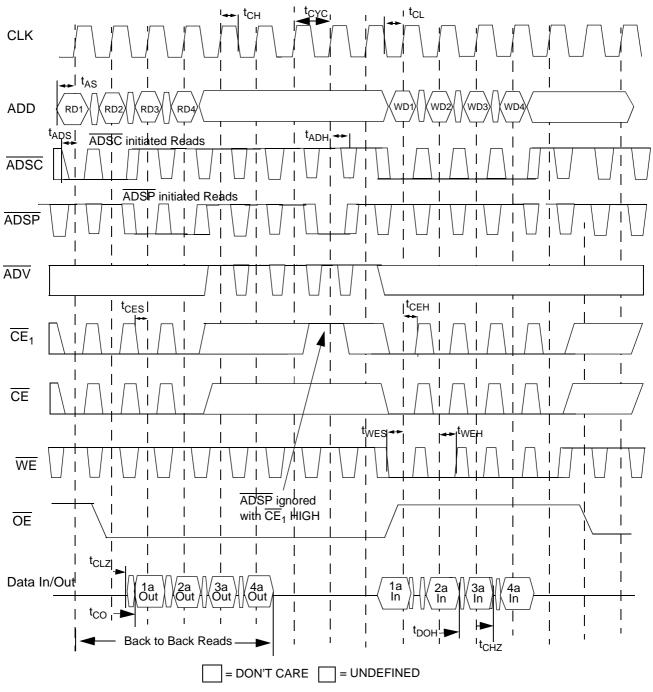

The WCSS0418V1P supports secondary cache in systems utilizing either a linear or interleaved burst sequence. The interleaved burst order supports Pentium and i486 processors. The linear burst sequence is suited for processors that utilize a linear burst sequence. The burst order is user selectable, and is determined by sampling the MODE input. Accesses can be initiated with either the Processor Address Strobe (ADSP) or the Controller Address Strobe (ADSC). Address advancement through the burst sequence is controlled by the ADV input. A two-bit on-chip wraparound burst counter captures the first address for the rest of the burst access.

Byte write operations are qualified with the Byte Write Enable  $(\overline{BWE})$  and Byte Write Select  $(\overline{BW}_{[1:0]})$  inputs. A Global Write Enable  $(\overline{GW})$  overrides all byte write inputs and writes data to all four bytes. All writes are simplified with on-chip synchronous self-timed write circuitry.

Three synchronous Chip Selects ( $\overline{CE}_1$ ,  $CE_2$ ,  $\overline{CE}_3$ ) and an asynchronous Output Enable ( $\overline{OE}$ ) provide for easy bank selection and output three-state control. ADSP is ignored if  $\overline{CE}_1$  is HIGH.

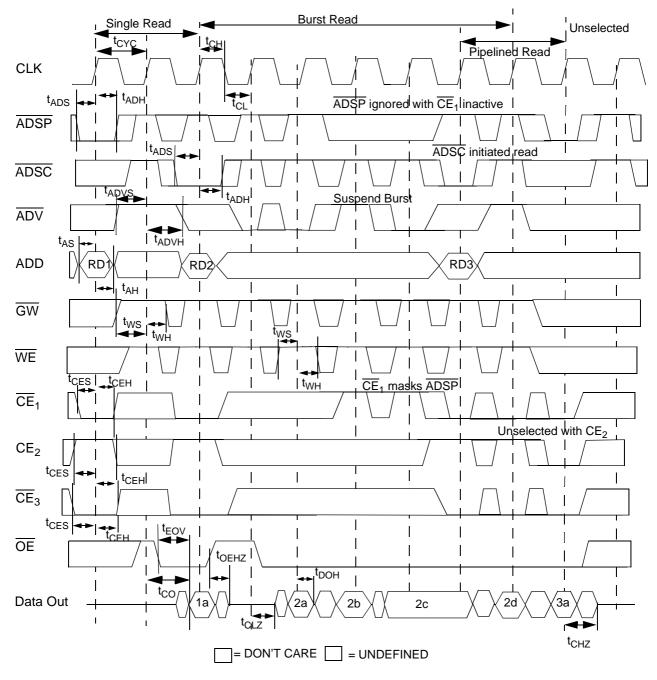

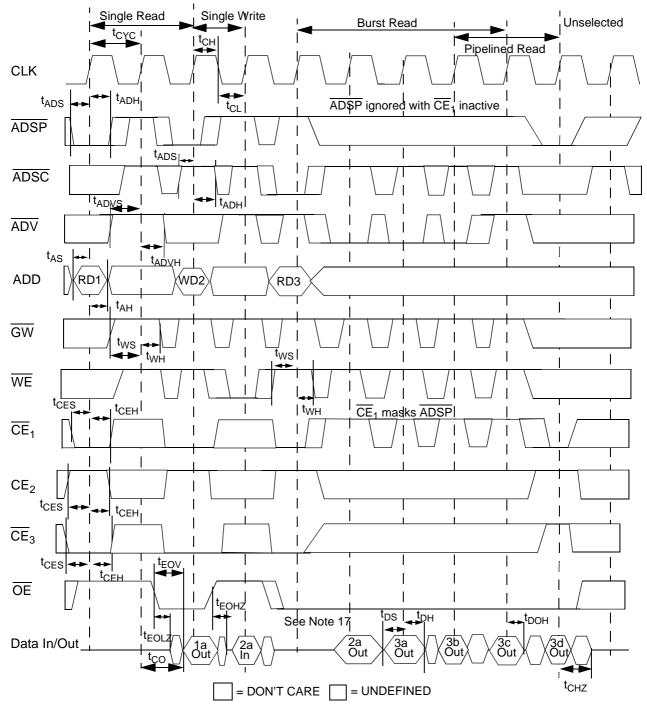

#### Single Read Accesses

This access is initiated when the following conditions are satisfied at clock rise: (1) ADSP or ADSC is asserted LOW, (2)  $\overline{CE_1}$ ,  $\underline{CE_2}$ ,  $\overline{CE_3}$  are all asserted active, and (3) the write signals (GW, BWE) are all deasserted HIGH. ADSP is ignored if  $\overline{CE_1}$

is HIGH. The address presented to the address inputs (A<sub>[17:0]</sub>) is stored into the address advancement logic and the Address Register while being presented to the memory core. The corresponding data is allowed to propagate to the input of the Output Registers. At the rising edge of the next clock the data is allowed to propagate through the output register and onto the data bus within 3.5 ns (166-MHz device) if OE is active LOW. The only exception occurs when the SRAM is emerging from a deselected state to a selected state, its outputs are always three-stated during the first cycle of the access. After the first cycle of the access, the outputs are controlled by the OE signal. Consecutive single read cycles are supported. Once the SRAM is deselected at clock rise by the chip select and either ADSP or ADSC signals, its output will three-state immediately.

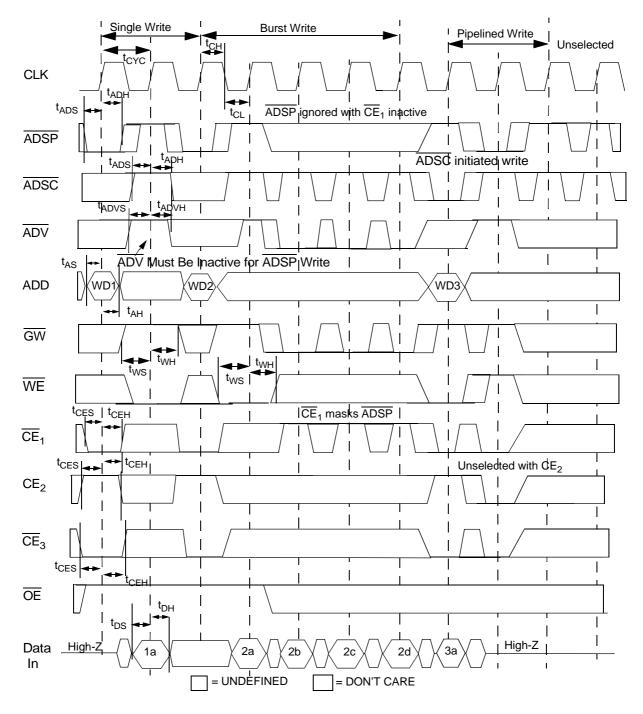

#### Single Write Accesses Initiated by ADSP

This access is initiated when both of the following conditions are satisfied at clock rise: (1) ADSP is asserted LOW, and (2)  $CE_1$ ,  $CE_2$ ,  $CE_3$  are all asserted active. The address presented to  $A_{[17:0]}$  is loaded into the address register and the address advancement logic while being delivered to the RAM core. The write signals (GW, BWE, and BW<sub>[1:0]</sub>) and ADV inputs are ignored during this first cycle.

ADSP-triggered write accesses require two clock cycles to complete. If GW is asserted LOW on the second clock rise, the data presented to the  $DQ_{[15:0]}$  and  $DP_{[1:0]}$  inputs is written into the corresponding address location in the RAM core. If GW is HIGH, then the write operation is controlled by BWE and  $BW_{[1:0]}$  signals. The WCSS0418V1P provides byte write capability that is described in the Write Cycle Description table. Asserting the Byte Write Enable input (BWE) with the selected Byte Write ( $BW_{[1:0]}$ ) input will selectively write to only the desired bytes. Bytes not selected during a byte write operation will remain unaltered. A synchronous self-timed write mechanism has been provided to simplify the write operations.

Because the WCSS0418V1P is a common I/O device, the Output Enable ( $\overline{OE}$ ) must be deasserted HIGH before presenting data to the DQ<sub>[15:0]</sub> and DP<sub>[1:0]</sub> inputs. Doing so will three-state the output drivers. As a safety precaution, DQ<sub>[15:0]</sub> and DP<sub>[1:0]</sub> are automatically three-stated whenever a write cycle is detected, regardless of the state of  $\overline{OE}$ .

#### Single Write Accesses Initiated by ADSC

ADSC write accesses are initiated when the following conditions are satisfied: (1) ADSC is asserted LOW, (2) ADSP is deasserted HIGH, (3)  $\overline{CE}_1$ ,  $CE_2$ ,  $\overline{CE}_3$  are all asserted active, and (4) the appropriate combination of the write inputs (GW, BWE, and BW<sub>[1:0]</sub>) are asserted active to conduct a write to the desired byte(s). ADSC-triggered write accesses require a single clock cycle to complete. The address presented to A<sub>I17:01</sub> is loaded into the address register and the address advancement logic while being delivered to the RAM core. The ADV input is ignored during this cycle. If a global write is conducted, the data presented to the  $DQ_{[15:0]}$  and  $DP_{[1:0]}$  is written into the corresponding address location in the RAM core. If a byte write is conducted, only the selected bytes are written. Bytes not selected during a byte write operation will remain unaltered. A synchronous self-timed write mechanism has been provided to simplify the write operations.

Because the WCSS0418V1P is a common I/O device, the Output Enable ( $\overline{OE}$ ) must be deasserted HIGH before presenting data to the DQ<sub>[15:0]</sub> and DP<sub>[1:0]</sub> inputs. Doing so will three-state the output drivers. As a safety precaution, DQ<sub>[15:0]</sub> and DP<sub>[1:0]</sub> are automatically three-stated whenever a write cycle is detected, regardless of the state of  $\overline{OE}$ .

## **Burst Sequences**

The WCSS0418V1P provides a two-bit wraparound counter, fed by  $A_{[1:0]}$ , that implements either an interleaved or linear burst sequence. The interleaved burst sequence is designed specifically to support Intel Pentium applications. The linear burst sequence is designed to support processors that follow

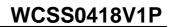

| Parameter          | Description                    | Test Conditions        | Min.              | Max.              | Unit |

|--------------------|--------------------------------|------------------------|-------------------|-------------------|------|

| I <sub>DDZZ</sub>  | Snooze mode<br>standby current | $ZZ \ge V_{DD} - 0.2V$ |                   | 3                 | mA   |

| t <sub>zzs</sub>   | Device operation to ZZ         | $ZZ \ge V_{DD} - 0.2V$ |                   | 2t <sub>CYC</sub> | ns   |

| t <sub>ZZREC</sub> | ZZ recovery time               | ZZ <u>&lt;</u> 0.2V    | 2t <sub>CYC</sub> |                   | ns   |

## ZZ Mode Electrical Characteristics

a linear burst sequence. The burst sequence is user selectable through the MODE input.

Asserting ADV LOW at clock rise will automatically increment the burst counter to the next address in the burst sequence. Both read and write burst operations are supported.

### Interleaved Burst Sequence

| First<br>Address   | Second<br>Address  | Third<br>Address   | Fourth<br>Address  |

|--------------------|--------------------|--------------------|--------------------|

| A <sub>[1:0]</sub> | A <sub>[1:0]</sub> | A <sub>[1:0]</sub> | A <sub>[1:0]</sub> |

| 00                 | 01                 | 10                 | 11                 |

| 01                 | 00                 | 11                 | 10                 |

| 10                 | 11                 | 00                 | 01                 |

| 11                 | 10                 | 01                 | 00                 |

## Linear Burst Sequence

| First<br>Address   | Second<br>Address  | Third<br>Address   | Fourth<br>Address  |

|--------------------|--------------------|--------------------|--------------------|

| A <sub>[1:0]</sub> | A <sub>[1:0]</sub> | A <sub>[1:0]</sub> | A <sub>[1:0]</sub> |

| 00                 | 01                 | 10                 | 11                 |

| 01                 | 10                 | 11                 | 00                 |

| 10                 | 11                 | 00                 | 01                 |

| 11                 | 00                 | 01                 | 10                 |

#### Sleep Mode

The ZZ input pin is an asynchronous input. Asserting ZZ places the SRAM in a power conservation "sleep" mode. Two clock cycles are required to enter into or exit from this "sleep" mode. While in this mode, data integrity is guaranteed. Accesses pending when entering the "sleep" mode are not considered valid nor is the completion of the operation guaranteed. The device must be deselected prior to entering the "sleep" mode.  $\overline{CE}_1$ ,  $\overline{CE}_2$ ,  $\overline{CE}_3$ , ADSP, and ADSC must remain inactive for the duration of  $t_{ZZREC}$  after the ZZ input returns LOW.

# Cycle Descriptions<sup>[1, 2, 3]</sup>

| Next Cycle     | Add. Used | ZZ | CE <sub>3</sub> | CE2 | CE <sub>1</sub> | ADSP | ADSC | ADV | OE | DQ   | Write |

|----------------|-----------|----|-----------------|-----|-----------------|------|------|-----|----|------|-------|

| Unselected     | None      | L  | Х               | Х   | 1               | Х    | 0    | Х   | Х  | Hi-Z | Х     |

| Unselected     | None      | L  | 1               | Х   | 0               | 0    | Х    | Х   | Х  | Hi-Z | Х     |

| Unselected     | None      | L  | Х               | 0   | 0               | 0    | Х    | Х   | Х  | Hi-Z | Х     |

| Unselected     | None      | L  | 1               | Х   | 0               | 1    | 0    | Х   | Х  | Hi-Z | Х     |

| Unselected     | None      | L  | Х               | 0   | 0               | 1    | 0    | Х   | Х  | Hi-Z | Х     |

| Begin Read     | External  | L  | 0               | 1   | 0               | 0    | Х    | Х   | Х  | Hi-Z | Х     |

| Begin Read     | External  | L  | 0               | 1   | 0               | 1    | 0    | Х   | Х  | Hi-Z | Read  |

| Continue Read  | Next      | L  | Х               | Х   | Х               | 1    | 1    | 0   | 1  | Hi-Z | Read  |

| Continue Read  | Next      | L  | Х               | Х   | Х               | 1    | 1    | 0   | 0  | DQ   | Read  |

| Continue Read  | Next      | L  | Х               | Х   | 1               | Х    | 1    | 0   | 1  | Hi-Z | Read  |

| Continue Read  | Next      | L  | Х               | Х   | 1               | Х    | 1    | 0   | 0  | DQ   | Read  |

| Suspend Read   | Current   | L  | Х               | Х   | Х               | 1    | 1    | 1   | 1  | Hi-Z | Read  |

| Suspend Read   | Current   | L  | Х               | Х   | Х               | 1    | 1    | 1   | 0  | DQ   | Read  |

| Suspend Read   | Current   | L  | Х               | Х   | 1               | Х    | 1    | 1   | 1  | Hi-Z | Read  |

| Suspend Read   | Current   | L  | Х               | Х   | 1               | Х    | 1    | 1   | 0  | DQ   | Read  |

| Begin Write    | Current   | L  | Х               | Х   | Х               | 1    | 1    | 1   | Х  | Hi-Z | Write |

| Begin Write    | Current   | L  | Х               | Х   | 1               | Х    | 1    | 1   | Х  | Hi-Z | Write |

| Begin Write    | External  | L  | 0               | 1   | 0               | 1    | 0    | Х   | Х  | Hi-Z | Write |

| Continue Write | Next      | L  | Х               | Х   | Х               | 1    | 1    | 0   | Х  | Hi-Z | Write |

| Continue Write | Next      | L  | Х               | Х   | 1               | Х    | 1    | 0   | Х  | Hi-Z | Write |

| Suspend Write  | Current   | L  | Х               | Х   | Х               | 1    | 1    | 1   | Х  | Hi-Z | Write |

| Suspend Write  | Current   | L  | Х               | Х   | 1               | Х    | 1    | 1   | Х  | Hi-Z | Write |

| ZZ "Sleep"     | None      | Н  | Х               | Х   | Х               | Х    | Х    | Х   | Х  | Hi-Z | Х     |

Notes:

X = "Don't Care," 1 <u>= HIGH, 0</u> = LOW.

Write is defined by BWE, BW<sub>[1:0]</sub>, and GW. See Write Cycle Description table.

The DQ pins are controlled by the current cycle and the OE signal. OE is asynchronous and is not sampled with the clock.

## Write Cycle Description<sup>[4, 5, 6]</sup>

| Function                             | GW | BWE | BW <sub>3</sub> | BW <sub>2</sub> | BW <sub>1</sub> | BW <sub>0</sub> |

|--------------------------------------|----|-----|-----------------|-----------------|-----------------|-----------------|

| Read                                 | 1  | 1   | Х               | Х               | Х               | Х               |

| Read                                 | 1  | 0   | 1               | 1               | 1               | 1               |

| Write Byte 0 - DQ <sub>[7:0]</sub>   | 1  | 0   | 1               | 1               | 1               | 0               |

| Write Byte 1 - DQ <sub>[15:8]</sub>  | 1  | 0   | 1               | 1               | 0               | 1               |

| Write Bytes 1, 0                     | 1  | 0   | 1               | 1               | 0               | 0               |

| Write Byte 2 - DQ <sub>[23:16]</sub> | 1  | 0   | 1               | 0               | 1               | 1               |

| Write Bytes 2, 0                     | 1  | 0   | 1               | 0               | 1               | 0               |

| Write Bytes 2, 1                     | 1  | 0   | 1               | 0               | 0               | 1               |

| Write Bytes 2, 1, 0                  | 1  | 0   | 1               | 0               | 0               | 0               |

| Write Byte 3 - DQ <sub>[31:24]</sub> | 1  | 0   | 0               | 1               | 1               | 1               |

| Write Bytes 3, 0                     | 1  | 0   | 0               | 1               | 1               | 0               |

| Write Bytes 3, 1                     | 1  | 0   | 0               | 1               | 0               | 1               |

| Write Bytes 3, 1, 0                  | 1  | 0   | 0               | 1               | 0               | 0               |

| Write Bytes 3, 2                     | 1  | 0   | 0               | 0               | 1               | 1               |

| Write Bytes 3, 2, 0                  | 1  | 0   | 0               | 0               | 1               | 0               |

| Write Bytes 3, 2, 1                  | 1  | 0   | 0               | 0               | 0               | 1               |

| Write All Bytes                      | 1  | 0   | 0               | 0               | 0               | 0               |

| Write All Bytes                      | 0  | Х   | Х               | Х               | Х               | Х               |

## **Maximum Ratings**

| (Above which the useful life may be impaired. For user guide- |  |

|---------------------------------------------------------------|--|

| lines, not tested.)                                           |  |

| Storage Temperature65°C to +150°C                                                      |

|----------------------------------------------------------------------------------------|

| Ambient Temperature with<br>Power Applied55°C to +125°C                                |

| Supply Voltage on $V_{DD}$ Relative to GND0.5V to +4.6V                                |

| DC Voltage Applied to Outputs                                                          |

| DC Voltage Applied to Outputs in High Z State $^{[7]}$ –0.5V to $V_{\text{DD}}$ + 0.5V |

| DC Input Voltage <sup>[7]</sup> 0.5V to $V_{DD}$ + 0.5V                                |

| Current into Outputs (LOW)                                 | 20 mA   |

|------------------------------------------------------------|---------|

| Static Discharge Voltage<br>(per MIL-STD-883, Method 3015) | >2001V  |

| Latch-Up Current                                           | >200 mA |

## **Operating Range**

| Range      | Ambient<br>Temperature <sup>[8]</sup> | V <sub>DD</sub>  | V <sub>DDQ</sub>      |

|------------|---------------------------------------|------------------|-----------------------|

| Com'l      | 0°C to +70°C                          | 3.3V<br>-5%/+10% | 2.5V –5%<br>3.3V +10% |

| Industrial | –40°C to +85°C                        | -570/+1070       | 3.30 +10%             |

#### Notes:

A. X = "Don't Care," 1 = Logic HIGH, 0 = Logic LOW.

5. The SRAM always initiates a read cycle when ADSP asserted, regardless of the state of GW, BWE, or BW<sub>[1:0]</sub>. Writes may occur only on subsequent clocks after the ADSP or with the assertion of ADSC. As a result, OE must be driven HIGH prior to the start of the write cycle to allow the outputs to three-state. OE is a don't care for the remainder of the write cycle.

6. OE is asynchronous and is not sampled with the clock rise. It is masked internally during write cycles. During a read cycle DQ<sub>[15:0]</sub>;DP<sub>[1:0]</sub> = High-Z when OE is inactive or when the device is deselected, and DQ<sub>[15:0]</sub>;DP<sub>[1:0]</sub> = data when OE is active.

7. Minimum voltage equals –2.0V for pulse durations of less than 20 ns.

8. T<sub>A</sub> is the case temperature.

# Electrical Characteristics Over the Operating Range

| Parameter        | Description                                       | Test Conditions                                                                                |                       |      | Max.                   | Unit |

|------------------|---------------------------------------------------|------------------------------------------------------------------------------------------------|-----------------------|------|------------------------|------|

| V <sub>DD</sub>  | Power Supply Voltage                              | 3.3V -5%/+10%                                                                                  |                       |      | 3.6                    | V    |

| V <sub>DDQ</sub> | I/O Supply Voltage                                | 2.5V -5% to 3.3V +10%                                                                          | 2.375                 | 3.6  | V                      |      |

| V <sub>OH</sub>  | Output HIGH Voltage                               | $V_{DDQ} = 3.3V, V_{DD} = Min., I_{OH} = -4.0$                                                 | 2.4                   |      | V                      |      |

|                  |                                                   | $V_{DDQ} = 2.5V, V_{DD} = Min., I_{OH} = -2.0$                                                 | mA                    | 2.0  |                        | V    |

| V <sub>OL</sub>  | Output LOW Voltage                                | $V_{DDQ} = 3.3V, V_{DD} = Min., I_{OL} = 8.0 m$                                                | A                     |      | 0.4                    | V    |

|                  |                                                   | $V_{DDQ} = 2.5V, V_{DD} = Min., I_{OL} = 2.0 m$                                                | A                     |      | 0.7                    | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                | $V_{DDQ} = 3.3V$                                                                               |                       | 2.0  | V <sub>DD</sub> + 0.3V | V    |

| V <sub>IH</sub>  | Input HIGH Voltage                                | $V_{DDQ} = 2.5V$                                                                               |                       | 1.7  | V <sub>DD</sub> + 0.3V | V    |

| V <sub>IL</sub>  | Input LOW Voltage <sup>[7]</sup>                  | $V_{DDQ} = 3.3V$                                                                               |                       | -0.3 | 0.8                    | V    |

| V <sub>IL</sub>  | Input LOW Voltage <sup>[7]</sup>                  | $V_{DDQ} = 2.5V$                                                                               |                       | -0.3 | 0.7                    | V    |

| I <sub>X</sub>   | Input Load Current<br>except ZZ and MODE          | $GND \le V_I \le V_{DDQ}$                                                                      |                       |      | 5                      | μA   |

|                  | Input Current of MODE                             | Input = V <sub>SS</sub>                                                                        |                       |      |                        | μΑ   |

|                  |                                                   | Input = V <sub>DDQ</sub>                                                                       |                       |      | 5                      | μΑ   |

|                  | Input Current of ZZ                               | Input = V <sub>SS</sub>                                                                        |                       |      |                        | μΑ   |

|                  |                                                   | Input = V <sub>DDQ</sub>                                                                       |                       |      | 30                     | μΑ   |

| I <sub>OZ</sub>  | Output Leakage<br>Current                         | $GND \le V_I \le V_{DDQ_i}$ Output Disabled                                                    |                       |      | 5                      | μΑ   |

| I <sub>DD</sub>  | V <sub>DD</sub> Operating Supply<br>Current       | $V_{DD} = Max., I_{OUT} = 0 mA,$                                                               | 6-ns cycle, 166 MHz   |      | 420                    | mA   |

|                  |                                                   | $f = f_{MAX} = 1/t_{CYC}$                                                                      | 7.5-ns cycle, 133 MHz |      | 375                    | mA   |

|                  |                                                   |                                                                                                | 10-ns cycle, 100 MHz  |      | 325                    | mA   |

| I <sub>SB1</sub> | Automatic CS<br>Power-Down<br>Current—TTL Inputs  | Max. V <sub>DD</sub> , Device Deselected,                                                      | 6-ns cycle, 166 MHz   |      | 150                    | mA   |

|                  |                                                   | $V_{IN} \ge V_{IH} \text{ or } V_{IN} \le V_{IL}$<br>f = f <sub>MAX</sub> = 1/t <sub>CYC</sub> | 7.5-ns cycle, 133 MHz |      | 125                    | mA   |

|                  |                                                   |                                                                                                | 10-ns cycle, 100 MHz  |      | 115                    | mA   |

| I <sub>SB2</sub> | Automatic CS<br>Power-Down<br>Current—CMOS Inputs | Max. $V_{DD}$ , Device Deselected,<br>$V_{IN} \le 0.3V$ or $V_{IN} \ge V_{DDO} - 0.3V$ ,       |                       |      | 10                     | mA   |

| I <sub>SB3</sub> | Automatic CS<br>Power-Down<br>Current—CMOS Inputs | Max. V <sub>DD</sub> , Device Deselected, or                                                   | 6-ns cycle, 166 MHz   |      | 120                    | mA   |

|                  |                                                   | $V_{IN} \le 0.3V$ or $V_{IN} \ge V_{DDQ} - 0.3V$<br>f = f <sub>MAX</sub> = 1/t <sub>CYC</sub>  | 7.5-ns cycle, 133 MHz |      | 95                     | mA   |

|                  |                                                   |                                                                                                | 10-ns cycle, 100 MHz  |      | 85                     | mA   |

| I <sub>SB4</sub> | Automatic CS<br>Power-Down<br>Current—TTL Inputs  | Max. $V_{DD}$ , Device Deselected, $V_{IN} \ge V_{IH}$ or $V_{IN} \le V_{IL}$ , f = 0          |                       |      | 18                     | mA   |

# Capacitance<sup>[9]</sup>

| Parameter Description |                          | Test Conditions                                    | Max. | Unit |

|-----------------------|--------------------------|----------------------------------------------------|------|------|

| C <sub>IN</sub>       | Input Capacitance        | $T_A = 25^{\circ}C, f = 1 \text{ MHz},$            | 4    | pF   |

| C <sub>CLK</sub>      | Clock Input Capacitance  | V <sub>DD</sub> = 3.3V,<br>V <sub>DDQ</sub> = 3.3V | 4    | pF   |

| C <sub>I/O</sub>      | Input/Output Capacitance |                                                    | 4    | pF   |

Note:

9. Tested initially and after any design or process changes that may affect these parameters.

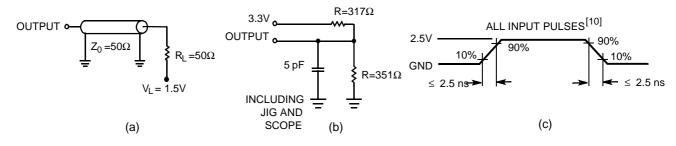

## AC Test Loads and Waveforms

# Switching Characteristics Over the Operating Range<sup>[11, 12, 13]</sup>

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -166 |      | -133 |      | -100 |      |      |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|------|

| Parameter         | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Min. | Max. | Min. | Max. | Min. | Max. | Unit |

| t <sub>CYC</sub>  | Clock Cycle Time                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 6.0  |      | 7.5  |      | 10   |      | ns   |

| t <sub>CH</sub>   | Clock HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1.7  |      | 1.9  |      | 3.5  |      | ns   |

| t <sub>CL</sub>   | Clock LOW                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1.7  |      | 1.9  |      | 3.5  |      | ns   |

| t <sub>AS</sub>   | Address Set-Up Before CLK Rise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2.0  |      | 2.5  |      | 2.5  |      | ns   |

| t <sub>AH</sub>   | Address Hold After CLK Rise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.5  |      | 0.5  |      | 0.5  |      | ns   |

| t <sub>CO</sub>   | Data Output Valid After CLK Rise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      | 3.5  |      | 4.0  |      | 5.5  | ns   |

| t <sub>DOH</sub>  | Data Output Hold After CLK Rise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1.5  |      | 2.0  |      | 2.0  |      | ns   |