# EN25Q32A 32 Megabit Serial Flash Memory with 4Kbyte Uniform Sector

## FEATURES

- Single power supply operation

- Full voltage range: 2.7-3.6 volt

- Serial Interface Architecture

- SPI Compatible: Mode 0 and Mode 3

- 32 M-bit Serial Flash

- 32 M-bit/4096 K-byte/16384 pages

- 256 bytes per programmable page

- Standard, Dual or Quad SPI

- Standard SPI: CLK, CS#, DI, DO, WP#

- Dual SPI: CLK, CS#, DQ<sub>0</sub>, DQ<sub>1</sub>, WP#

- Quad SPI: CLK, CS#, DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, DQ<sub>3</sub>

- High performance

- 100MHz clock rate for one data bit

- 80MHz clock rate for two data bits

- 80MHz clock rate for four data bits

- Low power consumption

- 12 mA typical active current

- 1  $\mu$ A typical power down current

- Uniform Sector Architecture:

- 1024 sectors of 4-Kbyte

- 64 blocks of 64-Kbyte

- Any sector or block can be erased individually

- Software and Hardware Write Protection:

- Write Protect all or portion of memory via software

- Enable/Disable protection with WP# pin

- High performance program/erase speed

- Page program time: 1.3ms typical

- Sector erase time: 90ms typical

- Block erase time 500ms typical

- Chip erase time: 25 seconds typical

- Lockable 512 byte OTP security sector

- Minimum 100K endurance cycle

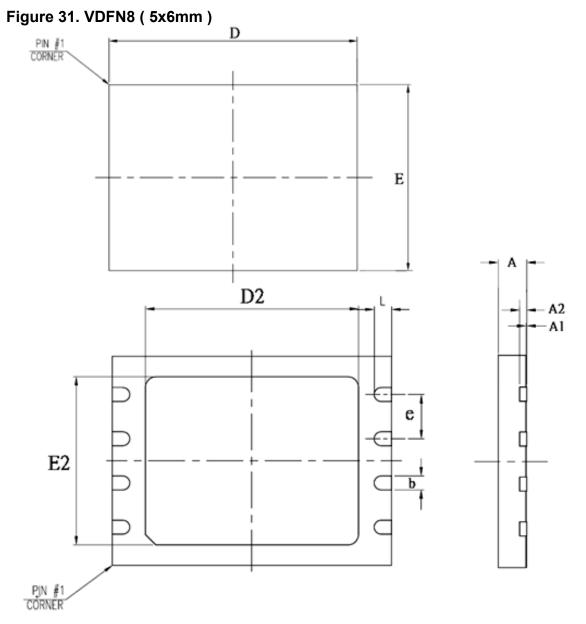

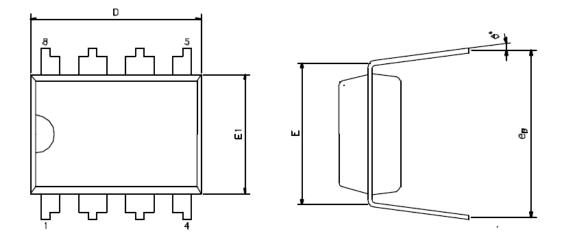

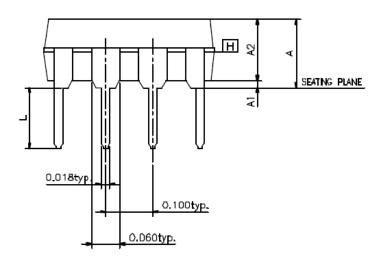

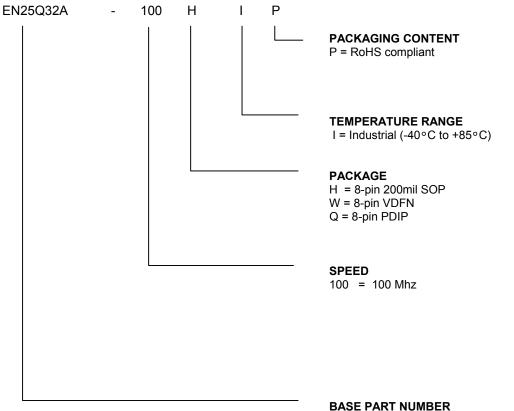

- Package Options

- 8 pins SOP 200mil body width

- 8 contact VDFN

- 8 pins PDIP

- All Pb-free packages are RoHS compliant

- Industrial temperature Range

## GENERAL DESCRIPTION

The EN25Q32A is a 32 Megabit (4096K-byte) Serial Flash memory, with advanced write protection mechanisms. The EN25Q32A supports the standard Serial Peripheral Interface (SPI), and a high performance Dual output as well as Quad I/O using SPI pins: Serial Clock, Chip Select, Serial DQ<sub>0</sub>(DI), DQ<sub>1</sub>(DO), DQ<sub>2</sub>(WP#) and DQ<sub>3</sub>(NC). SPI clock frequencies of up to 80MHz are supported allowing equivalent clock rates of 160MHz for Dual Output and 320MHz for Quad Output when using the Dual/Quad Output Fast Read instructions. The memory can be programmed 1 to 256 bytes at a time, using the Page Program instruction.

The EN25Q32A is designed to allow either single Sector/Block at a time or full chip erase operation. The EN25Q32A can be configured to protect part of the memory as the software protected mode. The device can sustain a minimum of 100K program/erase cycles on each sector or block.

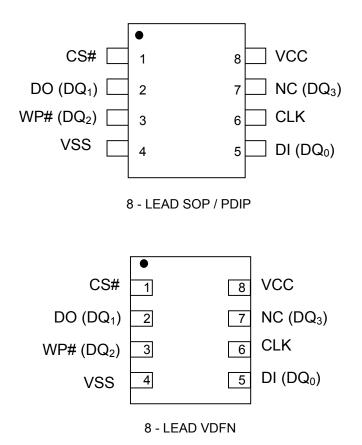

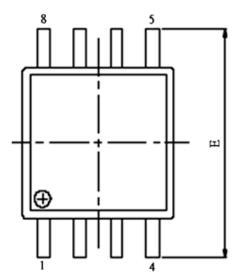

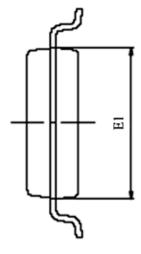

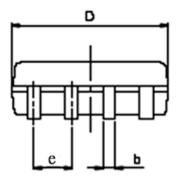

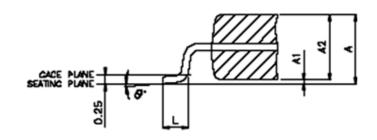

## Figure.1 CONNECTION DIAGRAMS

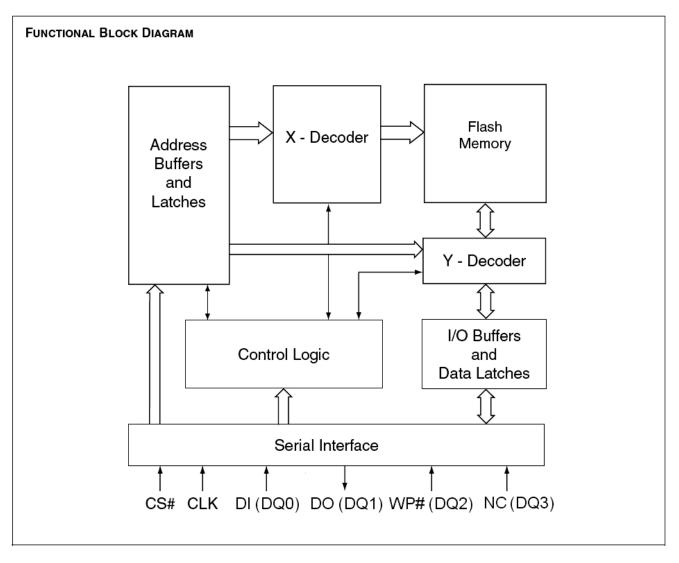

## Figure 2. BLOCK DIAGRAM

## Note:

- 1.  $\mathsf{DQ}_0$  and  $\mathsf{DQ}_1$  are used for Dual and Quad instructions.

- 2.  $DQ_0 \sim DQ_3$  are used for Quad instructions.

## Table 1. Pin Names

| Symbol                 | Pin Name                                    |

|------------------------|---------------------------------------------|

| CLK                    | Serial Clock Input                          |

| DI (DQ <sub>0</sub> )  | Serial Data Input (Data Input Output 0) *1  |

| DO (DQ <sub>1</sub> )  | Serial Data Output (Data Input Output 1) *1 |

| CS#                    | Chip Enable                                 |

| WP# (DQ <sub>2</sub> ) | Write Protect (Data Input Output 2) *2      |

| NC(DQ <sub>3</sub> )   | Not Connect (Data Input Output 3) *2        |

| Vcc                    | Supply Voltage (2.7-3.6V)                   |

| Vss                    | Ground                                      |

| NC                     | No Connect                                  |

Note:

1.  $DQ_0$  and  $DQ_1$  are used for Dual and Quad instructions.

2.  $DQ_0 \sim DQ_3$  are used for Quad instructions.

## SIGNAL DESCRIPTION

## Serial Data Input, Output and IOs (DI, DO and DQ<sub>0</sub>, DQ<sub>1</sub>, DQ<sub>2</sub>, DQ<sub>3</sub>)

The EN25Q32A support standard SPI, Dual SPI and Quad SPI operation. Standard SPI instructions use the unidirectional DI (input) pin to serially write instructions, addresses or data to the device on the rising edge of the Serial Clock (CLK) input pin. Standard SPI also uses the unidirectional DO (output) to read data or status from the device on the falling edge CLK.

Dual and Quad SPI instruction use the bidirectional IO pins to serially write instruction, addresses or data to the device on the rising edge of CLK and read data or status from the device on the falling edge of CLK.

## Serial Clock (CLK)

The SPI Serial Clock Input (CLK) pin provides the timing for serial input and output operations. ("See SPI Mode")

## Chip Select (CS#)

The SPI Chip Select (CS#) pin enables and disables device operation. When CS# is high the device is deselected and the Serial Data Output (DO, or  $DQ_0$ ,  $DQ_1$ ,  $DQ_2$  and  $DQ_3$ ) pins are at high impedance. When deselected, the devices power consumption will be at standby levels unless an internal erase, program or status register cycle is in progress. When CS# is brought low the device will be selected, power consumption will increase to active levels and instructions can be written to and data read from the device. After power-up, CS# must transition from high to low before a new instruction will be accepted.

## Write Protect (WP#)

The Write Protect (WP#) pin can be used to prevent the Status Register from being written. Used in conjunction with the Status Register's Block Protect (BP0, BP1, BP2 and BP3) bits and Status Register Protect (SRP) bits, a portion or the entire memory array can be hardware protected. The WP# function is only available for standard SPI and Dual SPI operation, when during Quad SPI, this pin is the Serial Data IO (DQ<sub>2</sub>) for Quad I/O operation.

## **MEMORY ORGANIZATION**

- The memory is organized as:

- •

- 4,194,304 bytes Uniform Sector Architecture • 64 blocks of 64-Kbyte 1024 sectors of 4-Kbyte

- 16384 pages (256 bytes each) •

Each page can be individually programmed (bits are programmed from 1 to 0). The device is Sector, Block or Chip Erasable but not Page Erasable.

## Table 2. Uniform Block Sector Architecture (Continued)

| Block    | Sector   | Addre              | ss range      |

|----------|----------|--------------------|---------------|

|          | 1023     | 3FF000h            | 3FFFFh 3FFFFh |

| 63       |          |                    |               |

|          | 1008     | 3F0000h            | 3F0FFFh       |

|          | 1007     | 3EF000h            | 3EFFFFh       |

| 62       |          |                    |               |

|          | 992      | 3E0000h            | 3E0FFFh       |

|          | 991      | 3DF000h            | 3DFFFFh       |

| 61       |          |                    |               |

|          | 976      | 3D0000h            | 3D0FFFh       |

|          | 975      | 3CF000h            | 3CFFFFh       |

| 60       |          |                    |               |

|          | 960      | 3C0000h            | 3C0FFFh       |

|          | 959      | 3BF000h            | 3BFFFFh       |

| 59       |          |                    |               |

|          | 944      | 3B0000h            | 3B0FFFh       |

|          | 943      | 3AF000h            | 3AFFFFh       |

| 58       |          |                    |               |

|          | 928      | 3A0000h            | 3A0FFFh       |

|          | 927      | 39F000h            | 39FFFFh       |

| 57       |          |                    |               |

|          | 912      | 390000h            | 390FFFh       |

|          | 911      | 38F000h            | 38FFFFh       |

| 56       |          | :                  |               |

|          | . 896    | 380000h            | 380FFFh       |

|          | 895      | 37F000h            | 37FFFFh       |

| 55       |          |                    |               |

| 00       | 880      | 370000h            | 370FFFh       |

|          | 879      | 36F000h            | 36FFFFh       |

| 54       |          |                    |               |

|          | 864      |                    | 360FFFh       |

|          | 863      | 35F000h            | 35FFFFh       |

| 53       | :        | :                  | :             |

| 55       | 848      | :<br>350000h       | :<br>350FFFh  |

|          | 847      | 34F000h            | 34FFFFh       |

| 52       | :        | :                  |               |

| 52       | 832      | :<br>340000h       | 340FFFh       |

|          | 831      | 33F000h            | 33FFFFh       |

| 51       |          | :                  | :             |

| 51       | 816      | :<br>330000h       | :<br>330FFFh  |

|          | 815      | 32F000h            | 32FFFFh       |

| 50       | 615      | 32F000II           | JZEFFFII<br>: |

| 50       | :<br>800 | :<br>320000h       | :<br>320FFFh  |

|          | 799      | 31F000h            | 31FFFFh       |

| 49       | 199      | 31F00011           | 31777711      |

| 49       | : 794    | 210000             | :<br>210555   |

|          | 784      | 310000h<br>30F000h | 310FFFh       |

| 48       | 783      | 30F000n            | 30FFFFh       |

| 40       | •        | •                  |               |

|          | 768      | 300000h            | 300FFFh       |

| 47       | 767      | 2FF000h            | 2FFFFh        |

| 47       | 750      | 050000             |               |

|          | 752      | 2F0000h            | 2F0FFFh       |

|          | 751      | 2EF000h            | 2EFFFh        |

| 46       |          |                    |               |

|          | 736      | 2E0000h            | 2E0FFFh       |

|          | 735      | 2DF000h            | 2DFFFFh       |

| 45       |          |                    |               |

|          | 720      | 2D0000h            | 2D0FFFh       |

|          | 719      | 2CF000h            | 2CFFFFh       |

| 44       |          |                    |               |

|          | 704      | 2C0000h            | 2C0FFFh       |

|          | 703      | 28F000h            | 2BFFFFh       |

| 43       | 705      | :                  | :             |

|          |          | :<br>20000b        |               |

| <u> </u> | 688      | 2B0000h            | 2B0FFFh       |

This Data Sheet may be revised by subsequent versions 6 ©2004 Eon Silicon Solution, Inc., www.eonssi.com or modifications due to changes in technical specifications.

| Block     | Sector   | Addres       | s range         |

|-----------|----------|--------------|-----------------|

| 2.000     | 687      | 2AF000h      | 2AFFFFh 2AFFFFh |

| 42        |          | :            | E               |

| -         | 672      | 2A0000h      | 2A0FFFh         |

|           | 671      | 29F000h      | 29FFFFh         |

| 41        |          |              |                 |

|           | 656      | 290000h      | :<br>290FFFh    |

|           | 655      | 28F000h      | 28FFFFh         |

| 40        |          |              |                 |

| 40        | 640      | 200000       | 000555          |

|           | 640      | 280000h      | 280FFFh         |

|           | 639      | 27F000h      | 27FFFFh         |

| 39        |          |              |                 |

|           | 624      | 270000h      | 270FFFh         |

|           | 623      | 26F000h      | 26FFFFh         |

| 38        |          |              |                 |

|           | 608      | 260000h      | 260FFFh         |

|           | 607      | 25F000h      | 25FFFFh         |

| 37        |          |              |                 |

|           | 592      | 250000h      | 250FFFh         |

|           | 591      | 24F000h      | 24FFFFh         |

| 36        |          | 2 11 00011   | :               |

| ~~        | 576      | :<br>240000h | 240FFFh         |

|           | 575      | 23F000h      | 23FFFFh         |

| 35        | 575      | 23F000n<br>: | 23FFFFN         |

| 35        | •        |              |                 |

|           | 560      | 230000h      | 230FFFh         |

|           | 559      | 22F000h      | 22FFFFh         |

| 34        |          |              |                 |

|           | 544      | 220000h      | 220FFFh         |

|           | 543      | 21F000h      | 21FFFFh         |

| 33        |          |              |                 |

|           | 528      | 210000h      | 210FFFh         |

|           | 527      | 20F000h      | 20FFFFh         |

| 32        |          |              |                 |

|           | 512      | 200000h      | 200FFFh         |

|           | 511      | 1FF000h      | 1FFFFh          |

| 31        |          |              |                 |

|           | 496      | 1F0000h      | 1F0FFFh         |

|           | 495      | 1EF000h      | 1EFFFFh         |

| 30        |          | 1            |                 |

|           | 480      | 1E0000h      | 1E0FFFh         |

|           | 479      | 1DF000h      | 1DFFFFh         |

| 29        | :        |              |                 |

|           | 464      | :<br>1D0000h | :<br>1D0FFFh    |

|           | 463      | 1CF000h      | 1CFFFFh         |

| 28        | 403      | :            |                 |

|           | :<br>448 | :<br>1C0000h | :<br>1C0FFFh    |

|           | 448      | 1BF000h      | 1BFFFFh         |

| 27        | 447      | :            |                 |

| <i>21</i> | 432      | :<br>1B0000h | :<br>1B0FFFh    |

|           | 432      | 1AF000h      | 1AFFFFh         |

| 26        |          |              |                 |

| 26        | 446      | :            |                 |

|           | 416      | 1A0000h      | 1A0FFFh         |

| 25        | 415      | 19F000h      | 19FFFF<br>:     |

| 25        | 400      | 400000       | 400555          |

|           | 400      | 190000h      | 190FFFh         |

| 24        | 399      | 18F000h      | 18FFFFh         |

| 24        | 001      |              | 1005551         |

|           | 384      | 180000h      | 180FFFh         |

|           | 383      | 17F000h      | 17FFFFh         |

| 23        |          |              |                 |

|           | 368      | 170000h      | 170FFFh         |

|           | 367      | 16F000h      | 16FFFFh         |

| L         |          |              |                 |

| 22        | 352      | 160000       | 160FFFh         |

## Table 2. Uniform Block Sector Architecture (Continued)

| Block | Sector     |                    | s range            |

|-------|------------|--------------------|--------------------|

|       | 351        | 15F000             | 15FFFFh            |

| 21    | :          |                    |                    |

|       | 336        | 150000h            | 150FFFh            |

|       | 335        | 14F000h            | 14FFFh             |

| 20    |            |                    |                    |

|       | 320        | 140000h            | 140FFFh            |

|       | 319        | 13F000h            | 13FFFFh            |

| 19    |            |                    |                    |

|       | 304        | 130000h            | 130FFFh            |

|       | 303        | 12F000h            | 12FFFFh            |

| 18    |            |                    |                    |

|       | 288        | 120000h            | 120FFFh            |

|       | 287        | 11F000h            | 11FFFFh            |

| 17    |            |                    |                    |

|       | 272        | 110000h            | 110FFFh            |

|       | 271        | 10F000h            | 10FFFFh            |

| 16    |            |                    |                    |

|       | 256        | 100000h            | 100FFFh            |

|       | 255        | 0FF000h            | 0FFFFh             |

| 15    |            |                    |                    |

|       | 240        | 0F0000h            | 0F0FFFh            |

|       | 239        | 0EF000h            | 0EFFFFh            |

| 14    |            |                    |                    |

|       | 224        | 0E0000h            | 0E0FFFh            |

|       | 223        | 0DF000h            | 0DFFFFh            |

| 13    |            |                    |                    |

|       | 208        | 0D0000h            | 0D0FFFh            |

|       | 207        | 0CF000h            | 0CFFFFh            |

| 12    | 201        |                    | :                  |

| 12    | 192        | :<br>0C0000h       | :<br>0C0FFFh       |

|       | 192        | 0BF000h            | OBFFFFh            |

| 11    | :          | :                  | OBFFFFII<br>:      |

| 11    | •          |                    |                    |

|       | 176<br>175 | 0B0000h<br>0AF000h | 0B0FFFh<br>0AFFFFh |

| 10    | -          |                    |                    |

| 10    | 100        |                    |                    |

|       | 160        | 0A0000h            | 0A0FFFh            |

|       | 159        | 09F000h            | 09FFFFh            |

| 9     |            |                    |                    |

|       | 144        | 090000h            | 090FFFh            |

|       | 143        | 08F000h            | 08FFFh             |

| 8     |            |                    |                    |

| L     | 128        | 080000h            | 080FFFh            |

|       | 127        | 07F000h            | 07FFFh             |

| 7     |            |                    |                    |

|       | 112        | 070000h            | 070FFFh            |

|       | 111        | 06F000h            | 06FFFFh            |

| 6     |            |                    |                    |

|       | 96         | 060000h            | 060FFFh            |

|       | 95         | 05F000h            | 05FFFFh            |

| 5     |            |                    |                    |

|       | 80         | 05000h             | 050FFFh            |

|       | 79         | 04F000h            | 04FFFFh            |

| 4     |            |                    |                    |

|       | 64         |                    | 040FFFh            |

|       | 63         | 03F000h            | 03FFFFh            |

| 3     |            |                    |                    |

| 5     |            |                    | 030FFFh            |

|       | 48         | 030000h<br>02F000h |                    |

| 2     | 47         | 02F000h            | 02FFFFh            |

| 2     |            | •                  |                    |

| L     | 32         | 020000h            | 020FFFh            |

## Table 2. Uniform Block Sector Architecture (Continued)

| Table 2. | Uniform Block Se | ctor Architecture (End) |

|----------|------------------|-------------------------|

|----------|------------------|-------------------------|

| Block | Sector | Address range           01F000h         01FFFFh |         |  |

|-------|--------|-------------------------------------------------|---------|--|

|       | 31     | 01F000h                                         | 01FFFFh |  |

| 1     |        |                                                 |         |  |

|       | 16     | 010000h                                         | 010FFFh |  |

|       | 15     | 00F000h                                         | 00FFFFh |  |

|       |        |                                                 |         |  |

|       | 4      | 004000h                                         | 004FFFh |  |

| 0     | 3      | 003000h                                         | 003FFFh |  |

|       | 2      | 002000h                                         | 002FFFh |  |

|       | 1      | 001000h                                         | 001FFFh |  |

|       | 0      | 000000h                                         | 000FFFh |  |

## **OPERATING FEATURES**

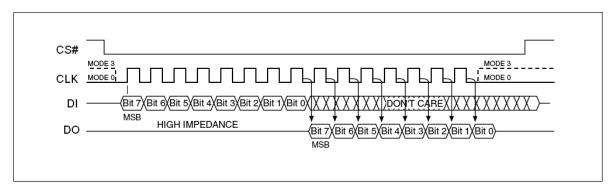

#### **Standard SPI Modes**

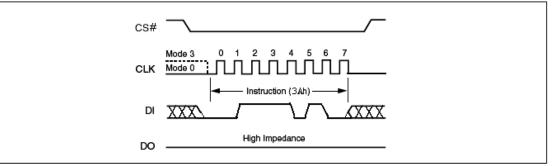

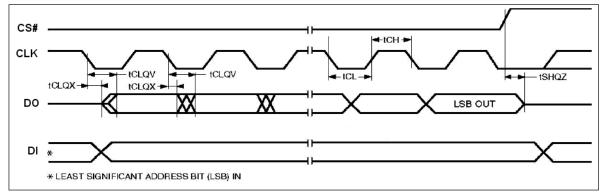

The EN25Q32A is accessed through a SPI compatible bus consisting of four signals: Serial Clock (CLK), Chip Select (CS#), Serial Data Input (DI) and Serial Data Output (DO). Both SPI bus operation Modes 0 (0,0) and 3 (1,1) are supported. The primary difference between Mode 0 and Mode 3, as shown in Figure 3, concerns the normal state of the CLK signal when the SPI bus master is in standby and data is not being transferred to the Serial Flash. For Mode 0 the CLK signal is normally low. For Mode 3 the CLK signal is normally high. In either case data input on the DI pin is sampled on the rising edge of the CLK. Data output on the DO pin is clocked out on the falling edge of CLK.

#### Figure 3. SPI Modes

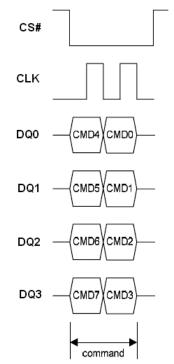

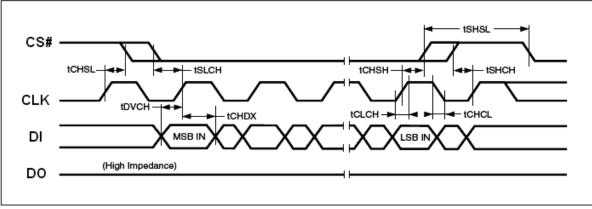

#### **Dual SPI Instruction**

The EN25Q32A supports Dual SPI operation when using the "Dual Output Fast Read and Dual I/O Fast Read " (3Bh and BBh) instructions. These instructions allow data to be transferred to or from the Serial Flash memory at two to three times the rate possible with the standard SPI. The Dual Read instructions are ideal for quickly downloading code from Flash to RAM upon power-up (code-shadowing) or for application that cache code-segments to RAM for execution. The Dual output feature simply allows the SPI input pin to also serve as an output during this instruction. When using Dual SPI instructions the DI and DO pins become bidirectional I/O pins;  $DQ_0$  and  $DQ_1$ . All other operations use the standard SPI interface with single output signal.

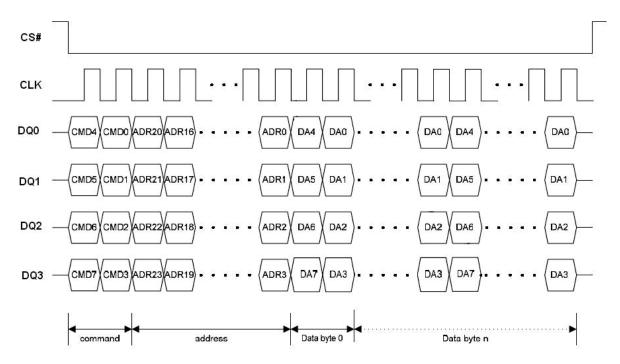

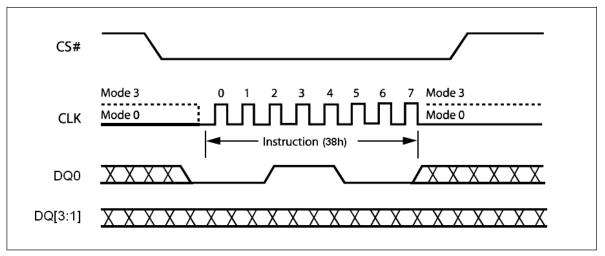

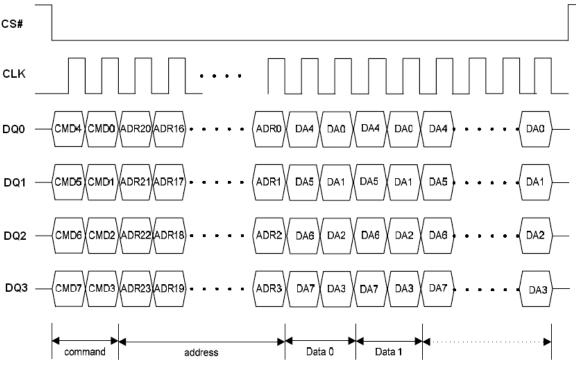

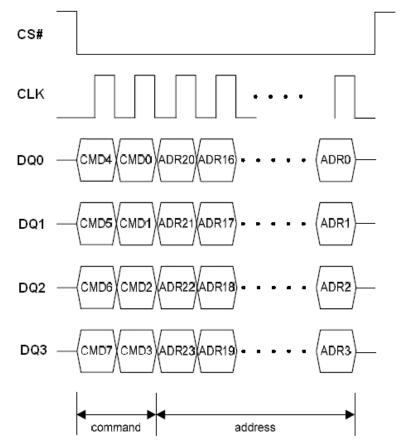

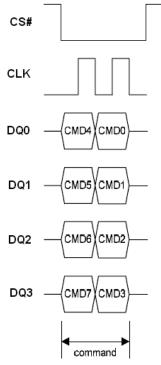

#### **Quad SPI Instruction**

The EN25Q32A supports Quad output operation when using the Quad I/O Fast Read (EBh). This instruction allows data to be transferred to or from the Serial Flash memory at four to six times the rate possible with the standard SPI. The Quad Read instruction offer a significant improvement in continuous and random access transfer rates allowing fast code-shadowing to RAM or for application that cache code-segments to RAM for execution. The EN25Q32A also supports full Quad Mode function while using the Enable Quad I/O (EQIO) (38h). When using Quad SPI instruction the DI and

DO pins become bidirectional I/O pins;  $DQ_0$  and  $DQ_1$  and the WP# and NC pins become  $DQ_2$  and  $DQ_3$  respectively.

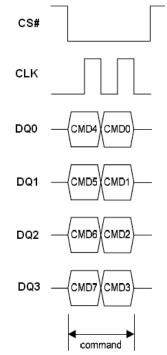

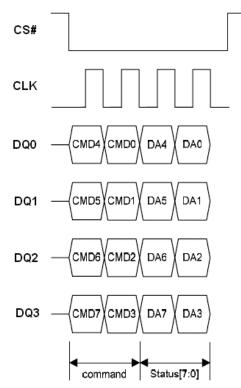

## Figure 4. Quad SPI Modes

### Page Programming

To program one data byte, two instructions are required: Write Enable (WREN), which is one byte, and a Page Program (PP) sequence, which consists of four bytes plus data. This is followed by the internal Program cycle (of duration  $t_{PP}$ ).

To spread this overhead, the Page Program (PP) instruction allows up to 256 bytes to be programmed at a time (changing bits from 1 to 0) provided that they lie in consecutive addresses on the same page of memory.

#### Sector Erase, Block Erase and Chip Erase

The Page Program (PP) instruction allows bits to be reset from 1 to 0. Before this can be applied, the bytes of memory need to have been erased to all 1s (FFh). This can be achieved a sector at a time, using the Sector Erase (SE) instruction, a block at a time using the Block Erase (BE) instruction or throughout the entire memory, using the Chip Erase (CE) instruction. This starts an internal Erase cycle (of duration  $t_{SE}$   $t_{BE}$  or  $t_{CE}$ ). The Erase instruction must be preceded by a Write Enable (WREN) instruction.

#### Polling During a Write, Program or Erase Cycle

A further improvement in the time to Write Status Register (WRSR), Program (PP) or Erase (SE, BE or CE) can be achieved by not waiting for the worst case delay ( $t_W$ ,  $t_{PP}$ ,  $t_{SE}$ ,  $t_{BE}$  or  $t_{CE}$ ). The Write In Progress (WIP) bit is provided in the Status Register so that the application program can monitor its value, polling it to establish when the previous Write cycle, Program cycle or Erase cycle is complete.

## Active Power, Stand-by Power and Deep Power-Down Modes

When Chip Select (CS#) is Low, the device is enabled, and in the Active Power mode. When Chip Select (CS#) is High, the device is disabled, but could remain in the Active Power mode until all internal cycles have completed (Program, Erase, Write Status Register). The device then goes into the Standby Power mode. The device consumption drops to  $I_{CC1}$ .

The Deep Power-down mode is entered when the specific instruction (the Enter Deep Power-down Mode (DP) instruction) is executed. The device consumption drops further to  $I_{CC2}$ . The device remains in this mode until another specific instruction (the Release from Deep Power-down Mode and Read Device ID (RDI) instruction) is executed.

All other instructions are ignored while the device is in the Deep Power-down mode. This can be used as an extra software protection mechanism, when the device is not in active use, to protect the device from inadvertent Write, Program or Erase instructions.

**Status Register.** The Status Register contains a number of status and control bits that can be read or set (as appropriate) by specific instructions.

**WIP bit.** The Write In Progress (WIP) bit indicates whether the memory is busy with a Write Status Register, Program or Erase cycle.

WEL bit. The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch.

**BP3**, **BP2**, **BP1**, **BP0** bits. The Block Protect (BP3, BP2, BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase instructions.

**WPDIS bit.** The Write Protect disable (WPDIS) bit, non-volatile bit, when it is reset to "0" (factory default) to enable WP# function or is set to "1" to disable WP# function (It can be floating during SPI mode.)

**SRP bit / OTP\_LOCK bit** The Status Register Protect (SRP) bit operates in conjunction with the Write Protect (WP#) signal. The Status Register Protect (SRP) bit and Write Protect (WP#) signal allow the device to be put in the Hardware Protected mode. In this mode, the non-volatile bits of the Status Register (SRP, BP3, BP2, BP1, BP0) become read-only bits.

In OTP mode, this bit serves as OTP\_LOCK bit, user can read/program/erase OTP sector as normal sector while OTP\_LOCK bit value is equal 0, after OTP\_LOCK is programmed with 1 by WRSR command, the OTP sector is protected from program and erase operation. The OTP\_LOCK bit can only be programmed once.

**Note :** In OTP mode, the WRSR command will ignore any input data and program OTP\_LOCK bit to 1, user must clear the protect bits before entering OTP mode and program the OTP code, then execute WRSR command to lock the OTP sector before leaving OTP mode.

#### Write Protection

Applications that use non-volatile memory must take into consideration the possibility of noise and other adverse system conditions that may compromise data integrity. To address this concern the EN25Q32A provides the following data protection mechanisms:

- Power-On Reset and an internal timer (t<sub>PUW</sub>) can provide protection against inadvertent changes while the power supply is outside the operating specification.

- Program, Erase and Write Status Register instructions are checked that they consist of a number of clock pulses that is a multiple of eight, before they are accepted for execution.

- All instructions that modify data must be preceded by a Write Enable (WREN) instruction to set the Write Enable Latch (WEL) bit. This bit is returned to its reset state by the following events:

Power-up

- Write Disable (WRDI) instruction completion or Write Status Register (WRSR) instruction completion or Page Program (PP) instruction completion or Sector Erase (SE) instruction completion or Block Erase (BE) instruction completion or Chip Erase (CE) instruction completion

- The Block Protect (BP3, BP2, BP1, BP0) bits allow part of the memory to be configured as readonly. This is the Software Protected Mode (SPM).

- The Write Protect (WP#) signal allows the Block Protect (BP3, BP2, BP1, BP0) bits and Status Register Protect (SRP) bit to be protected. This is the Hardware Protected Mode (HPM).

- In addition to the low power consumption feature, the Deep Power-down mode offers extra software protection from inadvertent Write, Program and Erase instructions, as all instructions are ignored except one particular instruction (the Release from Deep Power-down instruction).

| Status Register Content |            |            | ntent      |                |                 |             |             |  |

|-------------------------|------------|------------|------------|----------------|-----------------|-------------|-------------|--|

| BP3<br>Bit              | BP2<br>Bit | BP1<br>Bit | BP0<br>Bit | Protect Areas  | Addresses       | Density(KB) | Portion     |  |

| 0                       | 0          | 0          | 0          | None           | None            | None        | None        |  |

| 0                       | 0          | 0          | 1          | Block 0 to 62  | 000000h-3EFFFFh | 4032KB      | Lower 63/64 |  |

| 0                       | 0          | 1          | 0          | Block 0 to 61  | 000000h-3DFFFFh | 3968KB      | Lower 62/64 |  |

| 0                       | 0          | 1          | 1          | Block 0 to 59  | 000000h-3BFFFFh | 3840KB      | Lower 60/64 |  |

| 0                       | 1          | 0          | 0          | Block 0 to 55  | 000000h-37FFFFh | 3584KB      | Lower 56/64 |  |

| 0                       | 1          | 0          | 1          | Block 0 to 47  | 000000h-2FFFFFh | 3072KB      | Lower 48/64 |  |

| 0                       | 1          | 1          | 0          | Block 0 to 31  | 000000h-1FFFFh  | 2048KB      | Lower 32/64 |  |

| 0                       | 1          | 1          | 1          | All            | 000000h-3FFFFFh | 4096KB      | All         |  |

| 1                       | 0          | 0          | 0          | None           | None            | None        | None        |  |

| 1                       | 0          | 0          | 1          | Block 63 to 1  | 3FFFFFh-010000h | 4032KB      | Upper 63/64 |  |

| 1                       | 0          | 1          | 0          | Block 63 to 2  | 3FFFFFh-020000h | 3968KB      | Upper 62/64 |  |

| 1                       | 0          | 1          | 1          | Block 63 to 4  | 3FFFFFh-040000h | 3840KB      | Upper 60/64 |  |

| 1                       | 1          | 0          | 0          | Block 63 to 8  | 3FFFFFh-080000h | 3584KB      | Upper 56/64 |  |

| 1                       | 1          | 0          | 1          | Block 63 to 16 | 3FFFFFh-100000h | 3072KB      | Upper 48/64 |  |

| 1                       | 1          | 1          | 0          | Block 63 to 32 | 3FFFFFh-200000h | 2048KB      | Upper 32/64 |  |

| 1                       | 1          | 1          | 1          | All            | 000000h-3FFFFh  | 4096KB      | All         |  |

Table 3. Protected Area Sizes Sector Organization

## INSTRUCTIONS

All instructions, addresses and data are shifted in and out of the device, most significant bit first. Serial Data Input (DI) is sampled on the first rising edge of Serial Clock (CLK) after Chip Select (CS#) is driven Low. Then, the one-byte instruction code must be shifted in to the device, most significant bit first, on Serial Data Input (DI), each bit being latched on the rising edges of Serial Clock (CLK).

The instruction set is listed in Table 4. Every instruction sequence starts with a one-byte instruction code. Depending on the instruction, this might be followed by address bytes, or by data bytes, or by both or none. Chip Select (CS#) must be driven High after the last bit of the instruction sequence has been shifted in. In the case of a Read Data Bytes (READ), Read Data Bytes at Higher Speed (Fast\_Read), Read Status Register (RDSR) or Release from Deep Power-down, and Read Device ID (RDI) instruction, the shifted-in instruction sequence is followed by a data-out sequence. Chip Select (CS#) can be driven High after any bit of the data-out sequence is being shifted out.

In the case of a Page Program (PP), Sector Erase (SE), Block Erase (BE), Chip Erase (CE), Write Status Register (WRSR), Write Enable (WREN), Write Disable (WRDI) or Deep Power-down (DP) instruction, Chip Select (CS#) must be driven High exactly at a byte boundary, otherwise the instruction is rejected, and is not executed. That is, Chip Select (CS#) must driven High when the number of clock pulses after Chip Select (CS#) being driven Low is an exact multiple of eight. For Page Program, if at any time the input byte is not a full byte, nothing will happen and WEL will not be reset.

In the case of multi-byte commands of Page Program (PP), and Release from Deep Power Down (RES) minimum number of bytes specified has to be given, without which, the command will be ignored.

In the case of Page Program, if the number of byte after the command is less than 4 (at least 1 data byte), it will be ignored too. In the case of SE and BE, exact 24-bit address is a must, any less or more will cause the command to be ignored.

All attempts to access the memory array during a Write Status Register cycle, Program cycle or Erase cycle are ignored, and the internal Write Status Register cycle, Program cycle or Erase cycle continues unaffected.

#### Table 4A. Instruction Set

| Instruction Name                                       | Byte 1<br>Code | Byte 2                 | Byte 3     | Byte 4    | Byte 5    | Byte 6    | n-Bytes                   |

|--------------------------------------------------------|----------------|------------------------|------------|-----------|-----------|-----------|---------------------------|

| EQIO                                                   | 38h            |                        |            |           |           |           |                           |

| RSTQIO <sup>(1)</sup>                                  | FFh            |                        |            |           |           |           |                           |

| Write Enable                                           | 06h            |                        |            |           |           |           |                           |

| Write Disable / Exit<br>OTP mode                       | 04h            |                        |            |           |           |           |                           |

| Read Status<br>Register                                | 05h            | (S7-S0) <sup>(2)</sup> |            |           |           |           | continuous <sup>(3)</sup> |

| Write Status<br>Register                               | 01h            | S7-S0                  |            |           |           |           |                           |

| Page Program                                           | 02h            | A23-A16                | A15-A8     | A7-A0     | D7-D0     | Next byte | continuous                |

| Sector Erase / OTP<br>erase                            | 20h            | A23-A16                | A15-A8     | A7-A0     |           |           |                           |

| Block Erase                                            | D8h            | A23-A16                | A15-A8     | A7-A0     |           |           |                           |

| Chip Erase                                             | C7h/ 60h       |                        |            |           |           |           |                           |

| Deep Power-down                                        | B9h            |                        |            |           |           |           |                           |

| Release from Deep<br>Power-down, and<br>read Device ID | ABh            | dummy                  | dummy      | dummy     | (ID7-ID0) |           | (4)                       |

| Release from Deep<br>Power-down                        |                |                        |            |           |           |           |                           |

| Manufacturer/                                          | 90h            | dummy                  | dummy      | 00h       | (M7-M0)   | (ID7-ID0) | (5)                       |

| Device ID                                              |                |                        | -          | 01h       | (ID7-ID0) | (M7-M0)   |                           |

| Read Identification                                    | 9Fh            | (M7-M0)                | (ID15-ID8) | (ID7-ID0) | (6)       |           |                           |

| Enter OTP mode                                         | 3Ah            |                        |            |           |           |           |                           |

#### Notes:

1. Device accepts eight-clocks command in Standard SPI mode, or two-clocks command in Quad SPI mode.

2. Data bytes are shifted with Most Significant Bit first. Byte fields with data in parenthesis "()" indicate data being read from the device on the DO pin.

- The Status Register contents will repeat continuously until CS# terminate the instruction.

The Device ID will repeat continuously until CS# terminates the instruction.

- 5. The Manufacturer ID and Device ID bytes will repeat continuously until CS# terminates the instruction.

- 00h on Byte 4 starts with MID and alternate with DID, 01h on Byte 4 starts with DID and alternate with MID.

6. (M7-M0) : Manufacturer, (ID15-ID8) : Memory Type, (ID7-ID0) : Memory Capacity.

#### Table 4B. Instruction Set (Read Instruction)

| Instruction Name         | Byte 1<br>Code | Byte 2                          | Byte 3                            | Byte 4                  | Byte 5  | Byte 6                  | n-Bytes                                   |

|--------------------------|----------------|---------------------------------|-----------------------------------|-------------------------|---------|-------------------------|-------------------------------------------|

| Read Data                | 03h            | A23-A16                         | A15-A8                            | A7-A0                   | (D7-D0) | (Next byte)             | continuous                                |

| Fast Read                | 0Bh            | A23-A16                         | A15-A8                            | A7-A0                   | dummy   | (D7-D0)                 | (Next Byte) continuous                    |

| Dual Output Fast<br>Read | 3Bh            | A23-A16                         | A15-A8                            | A7-A0                   | dummy   | (D7-D0,) <sup>(1)</sup> | (one byte<br>per 4 clocks,<br>continuous) |

| Dual I/O Fast Read       | BBh            | A23-A8 <sup>(2)</sup>           | A7-A0,<br>dummy <sup>(2)</sup>    | (D7-D0,) (1)            |         |                         | (one byte<br>per 4 clocks,<br>continuous) |

| Quad I/O Fast Read       | EBh            | A23-A0,<br>dummy <sup>(4)</sup> | (dummy,<br>D7-D0 ) <sup>(5)</sup> | (D7-D0,) <sup>(3)</sup> |         |                         | (one byte<br>per 2 clocks,<br>continuous) |

#### Notes:

1. Dual Output data  $DQ_0 = (D6, D4, D2, D0)$  $DQ_1 = (D7, D5, D3, D1)$

2. Dual Input Address

$DQ_0 = A22, A20, A18, A16, A14, A12, A10, A8$ ; A6, A4, A2, A0, dummy 6, dummy 4, dummy 2, dummy 0  $DQ_1 = A23, A21, A19, A17, A15, A13, A11, A9$ ; A7, A5, A3, A1, dummy 7, dummy 5, dummy 3, dummy 1

3. Quad Data

| $DQ_0 = (D4, D0,)$       |

|--------------------------|

| $DQ_1 = (D5, D1, \dots)$ |

| $DQ_2 = (D6, D2,)$       |

| $DQ_3 = (D7, D3, \dots)$ |

4. Quad Input Address

$DQ_0 = A20, A16, A12, A8, A4, A0, dummy 4, dummy 0$  $DQ_1 = A21, A17, A13, A9, A5, A1, dummy 5, dummy 1$  $DQ_2 = A22, A18, A14, A10, A6, A2, dummy 6, dummy 2$  $DQ_3 = A23, A19, A15, A11, A7, A3, dummy 7, dummy 3$

5. Quad I/O Fast Read Data

$\begin{array}{l} DQ_0 = (\ dummy \ 12, \ dummy \ 8, \ dummy \ 4, \ dummy \ 0, \ D4, \ D0 \ ) \\ DQ_1 = (\ dummy \ 13, \ dummy \ 9, \ dummy \ 5, \ dummy \ 1, \ D5, \ D1 \ ) \\ DQ_2 = (\ dummy \ 14, \ dummy \ 10, \ dummy \ 6, \ dummy \ 2, \ D6, \ D2 \ ) \\ DQ_3 = (\ dummy \ 15, \ dummy \ 11, \ dummy \ 7, \ dummy \ 3, \ D7, \ D3 \ ) \end{array}$

Table 5. Manufacturer and Device Identification

| OP Code | (M7-M0) | (ID15-ID0) | (ID7-ID0) |

|---------|---------|------------|-----------|

| ABh     |         |            | 15h       |

| 90h     | 1Ch     |            | 15h       |

| 9Fh     | 1Ch     | 3016h      |           |

## Enable Quad I/O (EQIO) (38h)

The Enable Quad I/O (EQIO) instruction will enable the flash device for Quad SPI bus operation. Upon completion of the instruction, all instructions thereafter will be 4-bit multiplexed input/output until a power cycle or "Reset Quad I/O instruction "instruction, as shown in Figure 5. The device did not support the Read Data Bytes (READ) (03h), Dual Output Fast Read (3Bh) and Dual Input/Output FAST\_READ (BBh) modes while the Enable Quad I/O (EQIO) (38h) turns on.

Figure 5. Enable Quad I/O Sequence Diagram

## Reset Quad I/O (RSTQIO) (FFh)

The Reset Quad I/O instruction resets the device to 1-bit Standard SPI operation. To execute a Reset Quad I/O operation, the host drives CS# low, sends the Reset Quad I/O command cycle (FFh) then, drives CS# high. The device accepts either Standard SPI ( 8 clocks ) or Quad SPI ( 2 clocks) command cycles. For Standard SPI, DQ [3:1] are don't care for this command, but should be driven to  $V_{IL}$ .

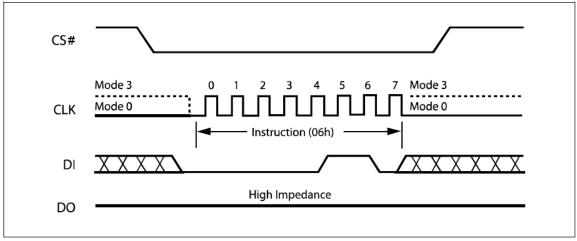

#### Write Enable (WREN) (06h)

The Write Enable (WREN) instruction (Figure 6) sets the Write Enable Latch (WEL) bit. The Write Enable Latch (WEL) bit must be set prior to every Page Program (PP), Sector Erase (SE), Block Erase (BE), Chip Erase (CE) and Write Status Register (WRSR) instruction.

The Write Enable (WREN) instruction is entered by driving Chip Select (CS#) Low, sending the instruction code, and then driving Chip Select (CS#) High.

The instruction sequence is shown in Figure 7.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 6. Write Enable Instruction Sequence Diagram

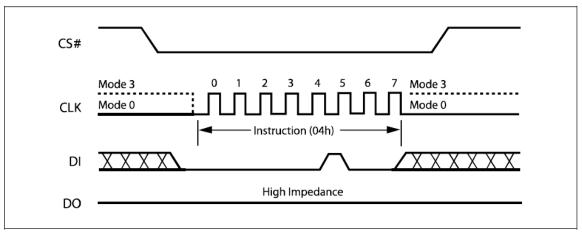

#### Write Disable (WRDI) (04h)

The Write Disable instruction (Figure 7) resets the Write Enable Latch (WEL) bit in the Status Register to a 0 or exit from OTP mode to normal mode. The Write Disable instruction is entered by driving Chip Select (CS#) low, shifting the instruction code "04h" into the DI pin and then driving Chip Select (CS#) high. Note that the WEL bit is automatically reset after Power-up and upon completion of the Write Status Register, Page Program, Sector Erase, Block Erase (BE) and Chip Erase instructions.

The instruction sequence is shown in Figure 7.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 7. Write Disable Instruction Sequence Diagram

Figure 7.1 Write Enable/Disable Instruction Sequence under EQIO Mode

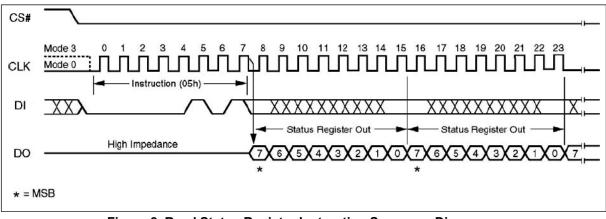

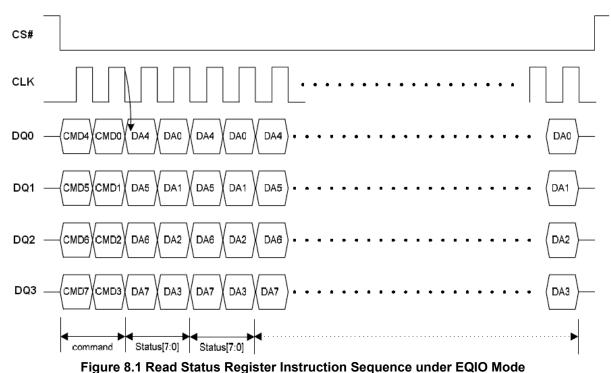

## Read Status Register (RDSR) (05h)

The Read Status Register (RDSR) instruction allows the Status Register to be read. The Status Register may be read at any time, even while a Program, Erase or Write Status Register cycle is in progress. When one of these cycles is in progress, it is recommended to check the Write In Progress (WIP) bit before sending a new instruction to the device. It is also possible to read the Status Register continuously, as shown in Figure 8.

The instruction sequence is shown in Figure 8.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 8. Read Status Register Instruction Sequence Diagram

Table 6. Status Register Bit Locations

| S                                       | 7                                 | S6                                      | S5                               | S4                               | S3                               | S2                               | S1                                             | S0                                                      |

|-----------------------------------------|-----------------------------------|-----------------------------------------|----------------------------------|----------------------------------|----------------------------------|----------------------------------|------------------------------------------------|---------------------------------------------------------|

| SRP<br>Status<br>Register<br>Protect    | OTP_LOCK<br>bit<br>(note 1)       | WPDIS<br>(WP# disable)                  | BP3<br>(Block<br>Protected bits) | BP2<br>(Block<br>Protected bits) | BP1<br>(Block<br>Protected bits) | BP0<br>(Block<br>Protected bits) | WEL<br>(Write Enable<br>Latch)                 | WIP<br>(Write In<br>Progress bit)                       |

| 1 = status<br>register write<br>disable | 1 = OTP<br>sector is<br>protected | 1 = WP#<br>disable<br>0 = WP#<br>enable | (note 2)                         | (note 2)                         | (note 2)                         | (note 2)                         | 1 = write<br>enable<br>0 = not write<br>enable | 1 = write<br>operation<br>0 = not in write<br>operation |

| Non-vol                                 | atile bit                         | Non-volatile bit                        | Non-volatile bit.                | Non-volatile bit                 | Non-volatile bit                 | Non-volatile bit                 | volatile bit                                   | volatile bit                                            |

#### Note

1. In OTP mode, SRP bit is served as OTP\_LOCK bit.

2. See the table "Protected Area Sizes Sector Organization".

The status and control bits of the Status Register are as follows:

**WIP bit.** The Write In Progress (WIP) bit indicates whether the memory is busy with a Write Status Register, Program or Erase cycle. When set to 1, such a cycle is in progress, when reset to 0 no such cycle is in progress.

**WEL bit.** The Write Enable Latch (WEL) bit indicates the status of the internal Write Enable Latch. When set to 1 the internal Write Enable Latch is set, when set to 0 the internal Write Enable Latch is reset and no Write Status Register, Program or Erase instruction is accepted.

**BP3, BP2, BP1, BP0 bits.** The Block Protect (BP3, BP2, BP1, BP0) bits are non-volatile. They define the size of the area to be software protected against Program and Erase instructions. These bits are written with the Write Status Register (WRSR) instruction. When one or both of the Block Protect (BP3, BP2, BP1, BP0) bits is set to 1, the relevant memory area (as defined in Table 3.) becomes protected against Page Program (PP) Sector Erase (SE) and , Block Erase (BE), instructions. The Block Protect (BP3, BP2, BP1, BP0) bits can be written provided that the Hardware Protected mode has not been set.

The Chip Erase (CE) instruction is executed if, and only if, all Block Protect (BP3, BP2, BP1, BP0) bits are 0.

**WPDIS bit.** The Write Protect disable (WPDIS) bit, non-volatile bit, when it is reset to "0" (factory default) to enable WP# function or is set to "1" to disable WP# function (It can be floating during SPI mode.)

**SRP bit / OTP\_LOCK bit.** The Status Register Protect (SRP) bit operates in conjunction with the Write Protect (WP#) signal. The Status Register Write Protect (SRP) bit and Write Protect (WP#) signal allow the device to be put in the Hardware Protected mode (when the Status Register Protect (SRP) bit is set to 1, and Write Protect (WP#) is driven Low). In this mode, the non-volatile bits of the Status Register (SRP, BP3, BP2, BP1, BP0) become read-only bits and the Write Status Register (WRSR) instruction is no longer accepted for execution.

In OTP mode, this bit serves as OTP\_LOCK bit, user can read/program/erase OTP sector as normal sector while OTP\_LOCK value is equal 0, after OTP\_LOCK bit is programmed with 1 by WRSR command, the OTP sector is protected from program and erase operation. The OTP\_LOCK bit can only be programmed once.

**Note :** In OTP mode, the WRSR command will ignore any input data and program OTP\_LOCK bit to 1, user must clear the protect bits before enter OTP mode and program the OTP code, then execute WRSR command to lock the OTP sector before leaving OTP mode.

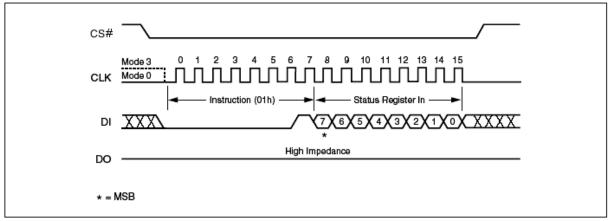

#### Write Status Register (WRSR) (01h)

The Write Status Register (WRSR) instruction allows new values to be written to the Status Register. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded and executed, the device sets the Write Enable Latch (WEL).

The Write Status Register (WRSR) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code and the data byte on Serial Data Input (DI).

The instruction sequence is shown in Figure 8. The Write Status Register (WRSR) instruction has no effect on S1 and S0 of the Status Register. Chip Select (CS#) must be driven High after the eighth bit of the data byte has been latched in. If not, the Write Status Register (WRSR) instruction is not executed. As soon as Chip Select (CS#) is driven High, the self-timed Write Status Register cycle (whose duration is  $t_W$ ) is initiated. While the Write Status Register cycle is in progress, the Status Register may still be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Write Status Register cycle, and is 0 when it is completed. When the cycle is completed, the Write Enable Latch (WEL) is reset.

The Write Status Register (WRSR) instruction allows the user to change the values of the Block Protect (BP3, BP2, BP1, BP0) bits, to define the size of the area that is to be treated as read-only, as defined in Table 3. The Write Status Register (WRSR) instruction also allows the user to set or reset the Status Register Protect (SRP) bit in accordance with the Write Protect (WP#) signal. The Status Register Protect (SRP) bit and Write Protect (WP#) signal allow the device to be put in the Hardware Protected Mode (HPM). The Write Status Register (WRSR) instruction is not executed once the Hardware Protected Mode (HPM) is entered.

The instruction sequence is shown in Figure 9.1 while using the Enable Quad I/O (EQIO) (38h) command.

NOTE : In the OTP mode, WRSR command will ignore input data and program OTP\_LOCK bit to 1.

Figure 9. Write Status Register Instruction Sequence Diagram

Figure 9.1 Write Status Register Instruction Sequence under EQIO Mode

## Read Data Bytes (READ) (03h)

The device is first selected by driving Chip Select (CS#) Low. The instruction code for the Read Data Bytes (READ) instruction is followed by a 3-byte address (A23-A0), each bit being latched-in during the rising edge of Serial Clock (CLK). Then the memory contents, at that address, is shifted out on Serial Data Output (DO), each bit being shifted out, at a maximum frequency  $f_R$ , during the falling edge of Serial Clock (CLK).

The instruction sequence is shown in Figure 10. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The whole memory can, therefore, be read with a single Read Data Bytes (READ) instruction. When the highest address is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.

This Data Sheet may be revised by subsequent versions20©2004 Eon Silicon Solution, Inc.,www.eonssi.comor modifications due to changes in technical specifications.20000

The Read Data Bytes (READ) instruction is terminated by driving Chip Select (CS#) High. Chip Select (CS#) can be driven High at any time during data output. Any Read Data Bytes (READ) instruction, while an Erase, Program or Write cycle is in progress, is rejected without having any effects on the cycle that is in progress.

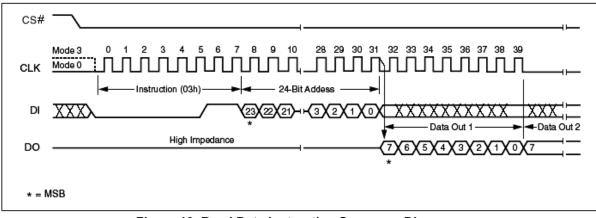

Figure 10. Read Data Instruction Sequence Diagram

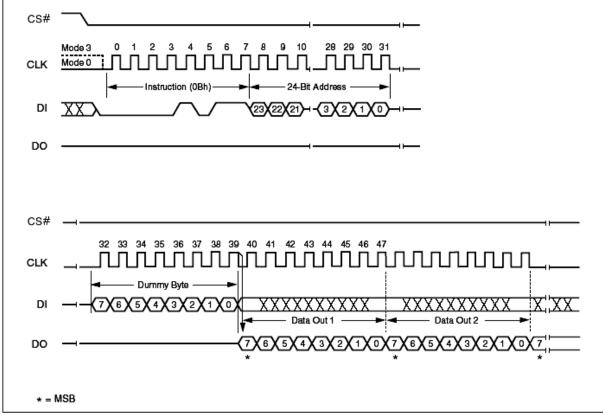

## Read Data Bytes at Higher Speed (FAST\_READ) (0Bh)

The device is first selected by driving Chip Select (CS#) Low. The instruction code for the Read Data Bytes at Higher Speed (FAST\_READ) instruction is followed by a 3-byte address (A23-A0) and a dummy byte, each bit being latched-in during the rising edge of Serial Clock (CLK). Then the memory contents, at that address, is shifted out on Serial Data Output (DO), each bit being shifted out, at a maximum frequency  $F_R$ , during the falling edge of Serial Clock (CLK).

The instruction sequence is shown in Figure 11. The first byte addressed can be at any location. The address is automatically incremented to the next higher address after each byte of data is shifted out. The whole memory can, therefore, be read with a single Read Data Bytes at Higher Speed (FAST\_READ) instruction. When the highest address is reached, the address counter rolls over to 000000h, allowing the read sequence to be continued indefinitely.

The Read Data Bytes at Higher Speed (FAST\_READ) instruction is terminated by driving Chip Select (CS#) High. Chip Select (CS#) can be driven High at any time during data output. Any Read Data Bytes at Higher Speed (FAST\_READ) instruction, while an Erase, Program or Write cycle is in progress, is rejected without having any effects on the cycle that is in progress.

The instruction sequence is shown in Figure 11.1 while using the Enable Quad I/O (EQIO) (38h) command.

EN25Q32A

Figure 11. Fast Read Instruction Sequence Diagram

Figure 11.1 Fast Read Instruction Sequence under EQIO Mode

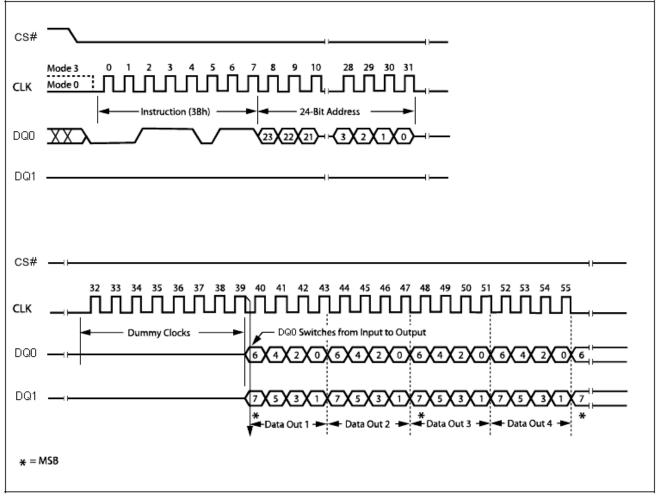

#### Dual Output Fast Read (3Bh)

The Dual Output Fast Read (3Bh) is similar to the standard Fast Read (0Bh) instruction except that data is output on two pins,  $DQ_0$  and  $DQ_1$ , instead of just  $DQ_0$ . This allows data to be transferred from the EN25Q32A at twice the rate of standard SPI devices. The Dual Output Fast Read instruction is ideal for quickly downloading code from to RAM upon power-up or for applications that cache code-segments to RAM for execution.

Similar to the Fast Read instruction, the Dual Output Fast Read instruction can operation at the highest possible frequency of FR (see AC Electrical Characteristics). This is accomplished by adding eight "dummy clocks after the 24-bit address as shown in Figure 12. The dummy clocks allow the device's internal circuits additional time for setting up the initial address. The input data during the dummy clock is "don't care". However, the DI pin should be high-impedance prior to the falling edge of the first data out clock.

Figure 12. Dual Output Fast Read Instruction Sequence Diagram

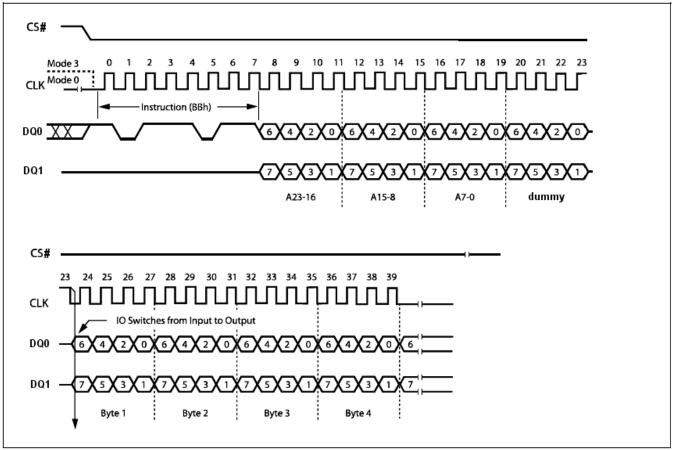

## Dual Input / Output FAST\_READ (BBh)

The Dual I/O Fast Read (BBh) instruction allows for improved random access while maintaining two IO pins,  $DQ_0$  and  $DQ_1$ . It is similar to the Dual Output Fast Read (3Bh) instruction but with the capability to input the Address bits (A23-0) two bits per clock. This reduced instruction overhead may allow for code execution (XIP) directly from the Dual SPI in some applications.

The Dual I/O Fast Read instruction enable double throughput of Serial Flash in read mode. The address is latched on rising edge of CLK, and data of every two bits (interleave 2 I/O pins) shift out on the falling edge of CLK at a maximum frequency. The first address can be at any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single Dual I/O Fast Read instruction. The address counter rolls over to 0 when the highest address has been reached. Once writing Dual I/O Fast Read instruction, the following address/dummy/data out will perform as 2-bit instead of previous 1-bit, as shown in Figure 13.

Figure 13. Dual Input / Output Fast Read Instruction Sequence Diagram

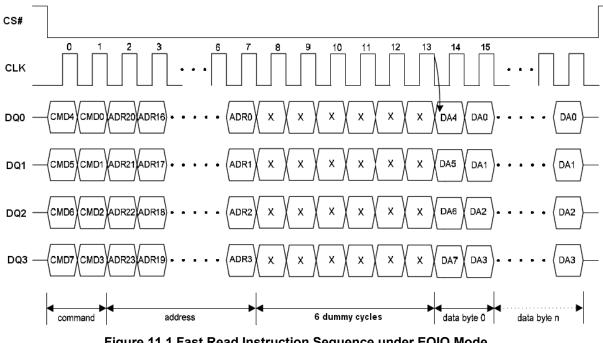

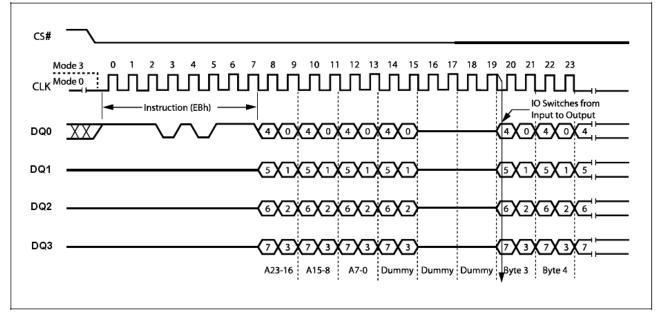

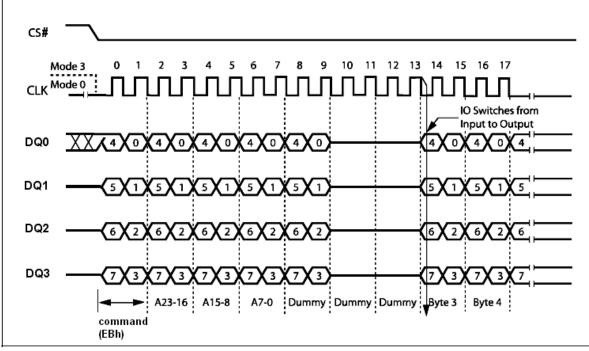

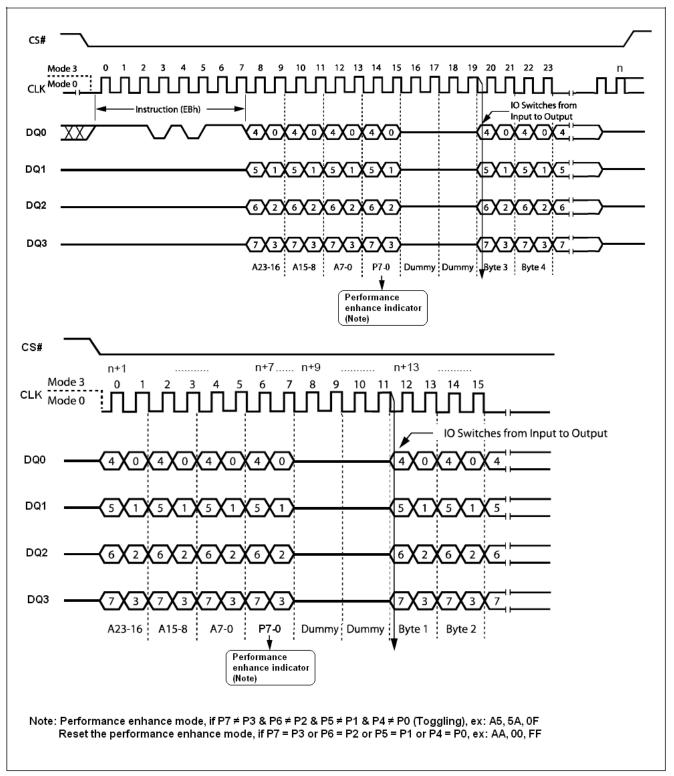

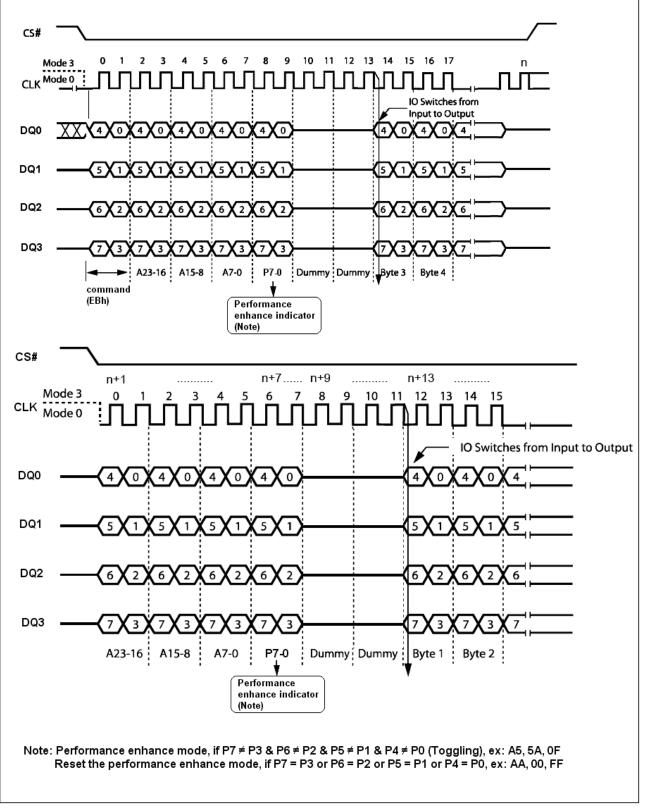

## Quad Input / Output FAST\_READ (EBh)

The Quad Input/Output FAST\_READ (EBh) instruction is similar to the Dual I/O Fast Read (BBh) instruction except that address and data bits are input and output through four pins.  $DQ_0$ ,  $DQ_1$ ,  $DQ_2$  and  $DQ_3$  and four Dummy clocks are required prior to the data output. The Quad I/O dramatically reduces instruction overhead allowing faster random access for code execution (XIP) directly from the Quad SPI. The Quad Input/Output FAST\_READ (EBh) instruction enable guad throughput of Serial Flash in read

The Quad input/Output FAST\_READ (EBn) instruction enable quad throughput of Serial Flash in read mode. The address is latching on rising edge of CLK, and data of every four bits (interleave on 4 I/O pins) shift our on the falling edge of CLK at a maximum frequency  $F_R$ . The first address can be any location. The address is automatically increased to the next higher address after each byte data is shifted out, so the whole memory can be read out at a single Quad Input/Output FAST\_READ instruction. The address counter rolls over to 0 when the highest address has been reached. Once writing Quad Input/Output FAST\_READ instruction, the following address/dummy/data out will perform as 4-bit instead of previous 1-bit.

The sequence of issuing Quad Input/Output FAST\_READ (EBh) instruction is: CS# goes low -> sending Quad Input/Output FAST\_READ (EBh) instruction -> 24-bit address interleave on DQ<sub>3</sub>, DQ<sub>2</sub>, DQ<sub>1</sub> and DQ<sub>0</sub> -> 6 dummy cycles -> data out interleave on DQ<sub>3</sub>, DQ<sub>2</sub>, DQ<sub>1</sub> and DQ<sub>0</sub> -> to end Quad Input/Output FAST\_READ (EBh) operation can use CS# to high at any time during data out, as shown in Figure 14.

The instruction sequence is shown in Figure 14.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 14. Quad Input / Output Fast Read Instruction Sequence Diagram

Figure 14.1. Quad Input / Output Fast Read Instruction Sequence under EQIO Mode

Another sequence of issuing Quad Input/Output FAST\_READ (EBh) instruction especially useful in random access is : CS# goes low -> sending Quad Input/Output FAST\_READ (EBh) instruction -> 24-bit address interleave on DQ<sub>3</sub>, DQ<sub>2</sub>, DQ<sub>1</sub> and DQ<sub>0</sub> -> performance enhance toggling bit P[7:0] -> 4 dummy cycles -> data out interleave on DQ<sub>3</sub>, DQ<sub>2</sub>, DQ<sub>1</sub> and DQ<sub>0</sub> till CS# goes high -> CS# goes low (reduce Quad Input/Output FAST\_READ (EBh) instruction) -> 24-bit random access address, as shown in Figure 15.

In the performance – enhancing mode, P[7:4] must be toggling with P[3:0] ; likewise P[7:0] = A5h, 5Ah, F0h or 0Fh can make this mode continue and reduce the next Quad Input/Output FAST\_READ (EBh) instruction. Once P[7:4] is no longer toggling with P[3:0] ; likewise P[7:0] = FFh, 00h, AAh or 55h. And afterwards CS# is raised, the system then will escape from performance enhance mode and return to normal operation.

While Program/ Erase/ Write Status Register is in progress, Quad Input/Output FAST\_READ (EBh) instruction is rejected without impact on the Program/ Erase/ Write Status Register current cycle.

The instruction sequence is shown in Figure 15.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 15. Quad Input/Output Fast Read Enhance Performance Mode Sequence Diagram

## EN25Q32A

Figure 15.1 Quad Input/Output Fast Read Enhance Performance Mode Sequence under EQIO Mode

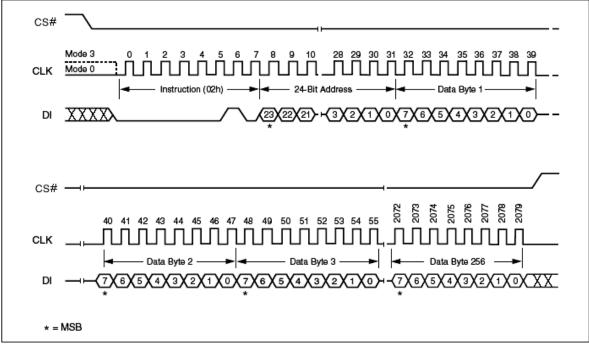

## Page Program (PP) (02h)

The Page Program (PP) instruction allows bytes to be programmed in the memory. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded, the device sets the Write Enable Latch (WEL).

The Page Program (PP) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code, three address bytes and at least one data byte on Serial Data Input (DI). If the 8 least significant address bits (A7-A0) are not all zero, all transmitted data that goes beyond the end of the current page are programmed from the start address of the same page (from the address whose 8 least significant bits (A7-A0) are all zero). Chip Select (CS#) must be driven Low for the entire duration of the sequence.

The instruction sequence is shown in Figure 16. If more than 256 bytes are sent to the device, previously latched data are discarded and the last 256 data bytes are guaranteed to be programmed correctly within the same page. If less than 256 Data bytes are sent to device, they are correctly programmed at the requested addresses without having any effects on the other bytes of the same page.

Chip Select (CS#) must be driven High after the eighth bit of the last data byte has been latched in, otherwise the Page Program (PP) instruction is not executed.

As soon as Chip Select (CS#) is driven High, the self-timed Page Program cycle (whose duration is  $t_{PP}$ ) is initiated. While the Page Program cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Page Program cycle, and is 0 when it is completed. At some unspecified time before the cycle is completed, the Write Enable Latch (WEL) bit is reset.

A Page Program (PP) instruction applied to a page which is protected by the Block Protect (BP3, BP2, BP1, BP0) bits (see Table 3) is not executed.

The instruction sequence is shown in Figure 16.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 16. Page Program Instruction Sequence Diagram

Figure 16.1 Program Instruction Sequence under EQIO Mode

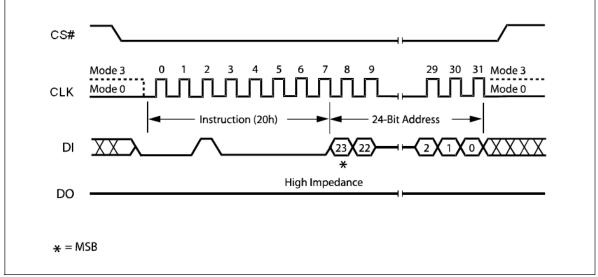

## Sector Erase (SE) (20h)

The Sector Erase (SE) instruction sets to 1 (FFh) all bits inside the chosen sector. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded, the device sets the Write Enable Latch (WEL).

The Sector Erase (SE) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code, and three address bytes on Serial Data Input (DI). Any address inside the Sector (see Table 2) is a valid address for the Sector Erase (SE) instruction. Chip Select (CS#) must be driven Low for the entire duration of the sequence.

The instruction sequence is shown in Figure 17. Chip Select (CS#) must be driven High after the eighth bit of the last address byte has been latched in, otherwise the Sector Erase (SE) instruction is not executed. As soon as Chip Select (CS#) is driven High, the self-timed Sector Erase cycle (whose duration is  $t_{SE}$ ) is initiated. While the Sector Erase cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Sector Erase cycle, and is 0 when it is completed. At some unspecified time before the cycle

is completed, the Write Enable Latch (WEL) bit is reset. A Sector Erase (SE) instruction applied to a sector which is protected by the Block Protect (BP3, BP2, BP1, BP0) bits (see Table 3) is not executed.

The instruction sequence is shown in Figure 18.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 17. Sector Erase Instruction Sequence Diagram

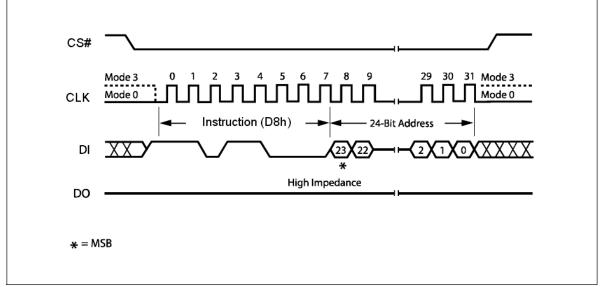

#### Block Erase (BE) (D8h)

The Block Erase (BE) instruction sets to 1 (FFh) all bits inside the chosen block. Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded, the device sets the Write Enable Latch (WEL).

The Block Erase (BE) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code, and three address bytes on Serial Data Input (DI). Any address inside the Block (see Table 2) is a valid address for the Block Erase (BE) instruction. Chip Select (CS#) must be driven Low for the entire duration of the sequence.

The instruction sequence is shown in Figure 18. Chip Select (CS#) must be driven High after the eighth bit of the last address byte has been latched in, otherwise the Block Erase (BE) instruction is not executed. As soon as Chip Select (CS#) is driven High, the self-timed Block Erase cycle (whose duration is  $t_{BE}$ ) is initiated. While the Block Erase cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Block Erase cycle, and is 0 when it is completed. At some unspecified time before the cycle is completed, the Write Enable Latch (WEL) bit is reset.

A Block Erase (BE) instruction applied to a block which is protected by the Block Protect (BP3, BP2, BP1, BP0) bits (see Table 3) is not executed.

The instruction sequence is shown in Figure 18.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 18. Block Erase Instruction Sequence Diagram

Figure 18.1 Block/Sector Erase Instruction Sequence under EQIO Mode

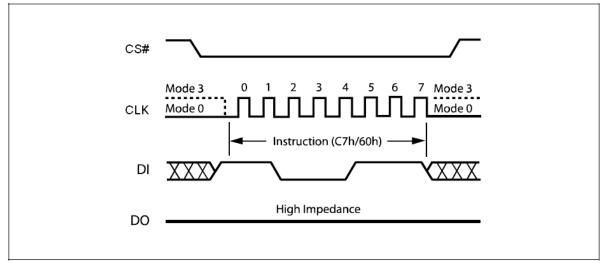

## Chip Erase (CE) (C7h/60h)

The Chip Erase (CE) instruction sets all bits to 1 (FFh). Before it can be accepted, a Write Enable (WREN) instruction must previously have been executed. After the Write Enable (WREN) instruction has been decoded, the device sets the Write Enable Latch (WEL).

The Chip Erase (CE) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code on Serial Data Input (DI). Chip Select (CS#) must be driven Low for the entire duration of the sequence.

The instruction sequence is shown in Figure 19. Chip Select (CS#) must be driven High after the eighth bit of the instruction code has been latched in, otherwise the Chip Erase instruction is not executed. As soon as Chip Select (CS#) is driven High, the self-timed Chip Erase cycle (whose duration is  $t_{CE}$ ) is initiated. While the Chip Erase cycle is in progress, the Status Register may be read to check the value of the Write In Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during the self-timed Chip Erase cycle, and is 0 when it is completed. At some unspecified time before the cycle is completed, the Write Enable Latch (WEL) bit is reset.

The Chip Erase (CE) instruction is executed only if all Block Protect (BP3, BP2, BP1, BP0) bits are 0. The Chip Erase (CE) instruction is ignored if one, or more blocks are protected.

The instruction sequence is shown in Figure 19.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 19. Chip Erase Instruction Sequence Diagram

Figure 19.1 Chip Erase Sequence under EQIO Mode

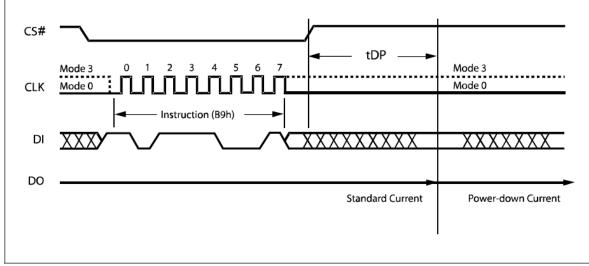

#### Deep Power-down (DP) (B9h)

Executing the Deep Power-down (DP) instruction is the only way to put the device in the lowest consumption mode (the Deep Power-down mode). It can also be used as an extra software protection mechanism, while the device is not in active use, since in this mode, the device ignores all Write, Program and Erase instructions.

Driving Chip Select (CS#) High deselects the device, and puts the device in the Standby mode (if there is no internal cycle currently in progress). But this mode is not the Deep Power-down mode. The Deep Power-down mode can only be entered by executing the Deep Power-down (DP) instruction, to reduce the standby current (from  $I_{CC1}$  to  $I_{CC2}$ , as specified in Table 9.)

Once the device has entered the Deep Power-down mode, all instructions are ignored except the Release from Deep Power-down and Read Device ID (RDI) instruction. This releases the device from this mode. The Release from Deep Power-down and Read Device ID (RDI) instruction also allows the Device ID of the device to be output on Serial Data Output (DO).

The Deep Power-down mode automatically stops at Power-down, and the device always Powers-up in the Standby mode. The Deep Power-down (DP) instruction is entered by driving Chip Select (CS#) Low, followed by the instruction code on Serial Data Input (DI). Chip Select (CS#) must be driven Low for the entire duration of the sequence.

The instruction sequence is shown in Figure 20. Chip Select (CS#) must be driven High after the eighth bit of the instruction code has been latched in, otherwise the Deep Power-down (DP) instruction is not executed. As soon as Chip Select (CS#) is driven High, it requires a delay of  $t_{DP}$  before the supply current is reduced to  $I_{CC2}$  and the Deep Power-down mode is entered.

Any Deep Power-down (DP) instruction, while an Erase, Program or Write cycle is in progress, is rejected without having any effects on the cycle that is in progress.

Figure 20. Deep Power-down Instruction Sequence Diagram

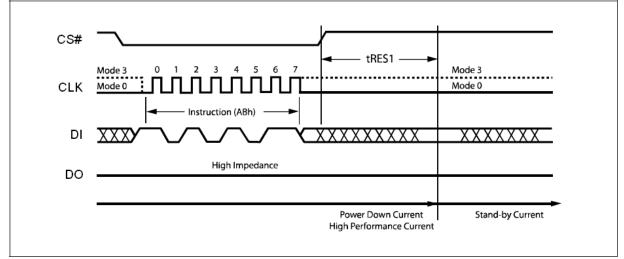

#### Release from Deep Power-down and Read Device ID (RDI)

Once the device has entered the Deep Power-down mode, all instructions are ignored except the Release from Deep Power-down and Read Device ID (RDI) instruction. Executing this instruction takes the device out of the Deep Power-down mode.

Please note that this is not the same as, or even a subset of, the JEDEC 16-bit Electronic Signature that is read by the Read Identifier (RDID) instruction. The old-style Electronic Signature is supported for reasons of backward compatibility, only, and should not be used for new designs. New designs should, instead, make use of the JEDEC 16-bit Electronic Signature, and the Read Identifier (RDID) instruction.

When used only to release the device from the power-down state, the instruction is issued by driving the CS# pin low, shifting the instruction code "ABh" and driving CS# high as shown in Figure 21. After the time duration of  $t_{RES1}$  (See AC Characteristics) the device will resume normal operation and other

instructions will be accepted. The CS# pin must remain high during the  $t_{RES1}$  time duration.

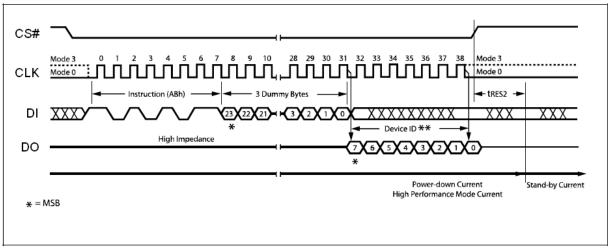

When used only to obtain the Device ID while not in the power-down state, the instruction is initiated by driving the CS# pin low and shifting the instruction code "ABh" followed by 3-dummy bytes. The Device ID bits are then shifted out on the falling edge of CLK with most significant bit (MSB) first as shown in Figure 22. The Device ID value for the EN25Q32A are listed in Table 5. The Device ID can be read continuously. The instruction is completed by driving CS# high.

When Chip Select (CS#) is driven High, the device is put in the Stand-by Power mode. If the device was not previously in the Deep Power-down mode, the transition to the Stand-by Power mode is immediate. If the device was previously in the Deep Power-down mode, though, the transition to the Standby Power mode is delayed by t<sub>RES2</sub>, and Chip Select (CS#) must remain High for at least t<sub>RES2</sub>

(max), as specified in Table 11. Once in the Stand-by Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.

Except while an Erase, Program or Write Status Register cycle is in progress, the Release from Deep Power-down and Read Device ID (RDI) instruction always provides access to the 8bit Device ID of the device, and can be applied even if the Deep Power-down mode has not been entered.

Any Release from Deep Power-down and Read Device ID (RDI) instruction while an Erase, Program or Write Status Register cycle is in progress, is not decoded, and has no effect on the cycle that is in progress.

Figure 21. Release Power-down Instruction Sequence Diagram

Figure 22. Release Power-down / Device ID Instruction Sequence Diagram

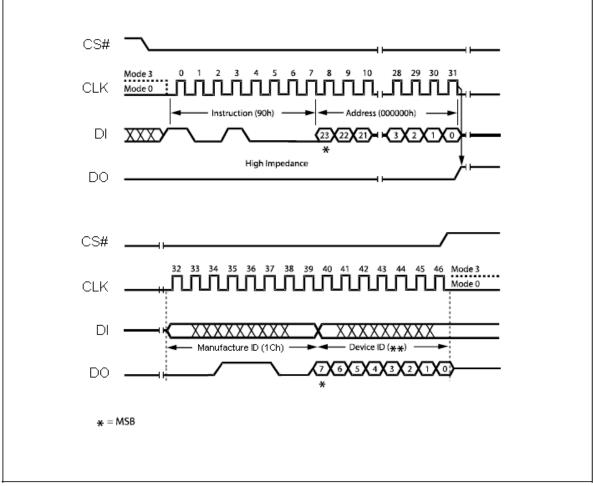

## Read Manufacturer / Device ID (90h)

The Read Manufacturer/Device ID instruction is an alternative to the Release from Power-down / Device ID instruction that provides both the JEDEC assigned manufacturer ID and the specific device ID.

The Read Manufacturer/Device ID instruction is very similar to the Release from Power-down / Device ID instruction. The instruction is initiated by driving the CS# pin low and shifting the instruction code "90h" followed by a 24-bit address (A23-A0) of 000000h. After which, the Manufacturer ID for Eon (1Ch) and the Device ID are shifted out on the falling edge of CLK with most significant bit (MSB) first as shown in Figure 23. The Device ID values for the EN25Q32A are listed in Table 5. If the 24-bit address is initially set to 000001h the Device ID will be read first

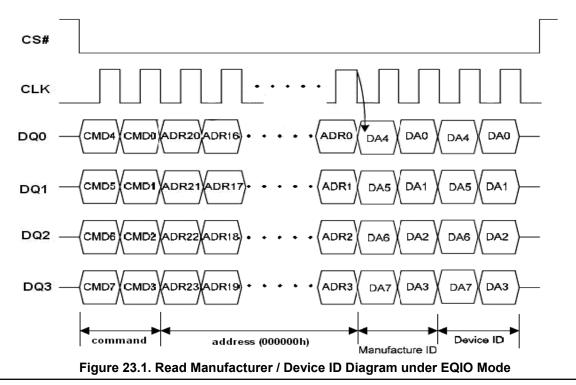

The instruction sequence is shown in Figure 23.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 23. Read Manufacturer / Device ID Diagram

©2004 Eon Silicon Solution, Inc., www.eonssi.com

37

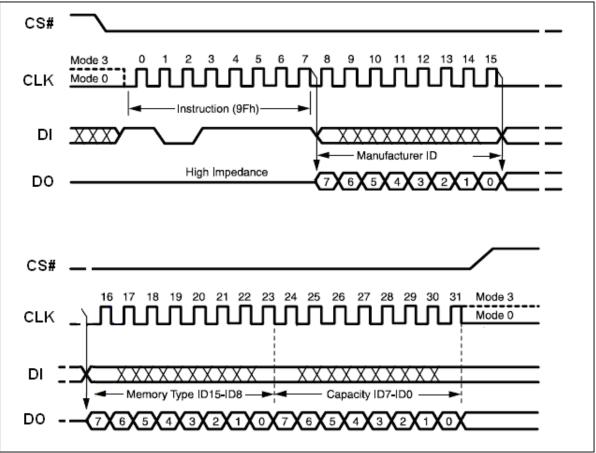

#### Read Identification (RDID) (9Fh)

The Read Identification (RDID) instruction allows the 8-bit manufacturer identification to be read, followed by two bytes of device identification. The device identification indicates the memory type in the first byte, and the memory capacity of the device in the second byte.

Any Read Identification (RDID) instruction while an Erase or Program cycle is in progress, is not decoded, and has no effect on the cycle that is in progress. The Read Identification (RDID) instruction should not be issued while the device is in Deep Power down mode.

The device is first selected by driving Chip Select Low. Then, the 8-bit instruction code for the instruction is shifted in. This is followed by the 24-bit device identification, stored in the memory, being shifted out on Serial Data Output, each bit being shifted out during the falling edge of Serial Clock. The instruction sequence is shown in Figure 24. The Read Identification (RDID) instruction is terminated by driving Chip Select High at any time during data output.

When Chip Select is driven High, the device is put in the Standby Power mode. Once in the Standby Power mode, the device waits to be selected, so that it can receive, decode and execute instructions.

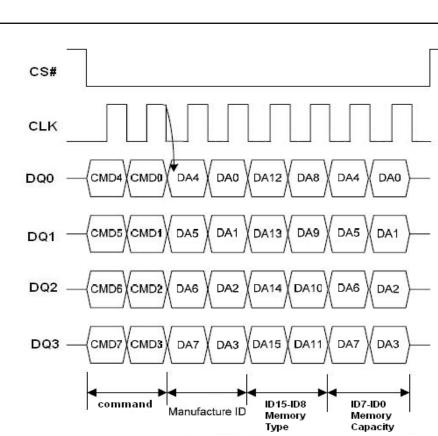

The instruction sequence is shown in Figure 24.1 while using the Enable Quad I/O (EQIO) (38h) command.

Figure 24. Read Identification (RDID)

Figure 24.1. Read Identification (RDID) under EQIO Mode

#### Enter OTP Mode (3Ah)

This Flash has an extra 512 bytes OTP sector, user must issue ENTER OTP MODE command to read, program or erase OTP sector. After entering OTP mode, the OTP sector is mapping to sector 1023, **SRP bit** becomes OTP\_LOCK bit and can be read with RDSR command. Program / Erase command will be disabled when OTP\_LOCK bit is '1'

WRSR command will ignore the input data and program OTP\_LOCK bit to 1.

User must clear the protect bits before enter OTP mode.

OTP sector can only be program and erase before OTP\_LOCK bit is set to '1' and BP [3:0] = '0000'. In OTP mode, user can read other sectors, but program/erase other sectors only allowed when OTP\_LOCK bit equal to '0'.

User can use WRDI (04h) command to exit OTP mode.

The instruction sequence is shown in Figure 25.1 while using the Enable Quad I/O (EQIO) (38h) command.

#### Erase OTP Command (20h)

User can use Sector Erase (20h) command only to erase OTP data.

#### Table 7. OTP Sector Address

| Sector | Sector Size | Address Range     |

|--------|-------------|-------------------|

| 1023   | 512 byte    | 3FF000h – 3FF1FFh |

Note: The OTP sector is mapping to sector 1023

Figure 25. Enter OTP Mode

Figure 25.1 Enter OTP Mode Sequence under EQIO Mode

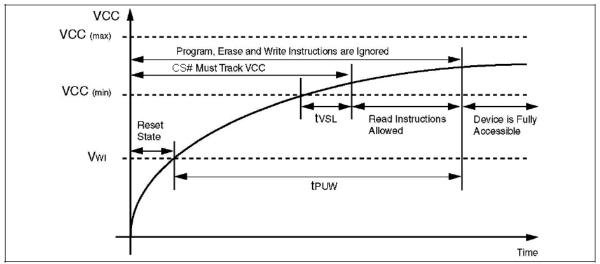

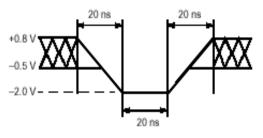

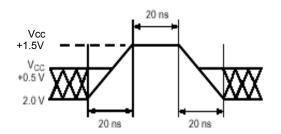

#### **Power-up Timing**

Figure 26. Power-up Timing

## Table 8. Power-Up Timing and Write Inhibit Threshold

| Symbol                          | Parameter                       |    | Max. | Unit |

|---------------------------------|---------------------------------|----|------|------|

| t <sub>VSL</sub> (1)            | VCC(min) to CS# low             | 10 |      | μs   |

| t <sub>PUW</sub> <sup>(1)</sup> | Time delay to Write instruction |    | 10   | ms   |

| VWI(1)                          | Write Inhibit Voltage           | 1  | 2.5  | V    |

#### Note:

1. The parameters are characterized only.

2. VCC (max.) is 3.6V and VCC (min.) is 2.7V

## **INITIAL DELIVERY STATE**

The device is delivered with the memory array erased: all bits are set to 1 (each byte contains FFh). The Status Register contains 00h (all Status Register bits are 0).

# **Table 9. DC Characteristics**

$(T_a = -40^{\circ}C \text{ to } 85^{\circ}C; V_{CC} = 2.7-3.6V)$

| Symbol           | Parameter                | Test Conditions                                                         | Min.                 | Max.                 | Unit |

|------------------|--------------------------|-------------------------------------------------------------------------|----------------------|----------------------|------|

| ILI              | Input Leakage Current    |                                                                         |                      | ± 2                  | μA   |

| ILO              | Output Leakage Current   |                                                                         |                      | ± 2                  | μA   |

| I <sub>CC1</sub> | Standby Current          | CS# = $V_{CC}$ , $V_{IN}$ = $V_{SS}$ or $V_{CC}$                        |                      | 20                   | μA   |

| I <sub>CC2</sub> | Deep Power-down Current  | CS# = $V_{CC}$ , $V_{IN}$ = $V_{SS}$ or $V_{CC}$                        |                      | 20                   | μA   |

|                  | Operating Current (READ) | CLK = 0.1 V <sub>CC</sub> / 0.9 V <sub>CC</sub> at<br>100MHz, DQ = open |                      | 25                   | mA   |