# **Deca Half-Bridge Driver**

The NCV7720 Deca is a ten channel half-bridge driver with protection features designed specifically for automotive and industrial motion control applications. The product has independent controls and diagnostics, and the drivers can be operated in forward, reverse, brake, and high impedance states. The device is controlled via a 16 bit SPI interface and is daisy chain compatible.

### **Features**

- Low Quiescent Current Sleep Mode

- High–Side and Low–Side Drivers

Connected in Half–Bridge Configurations

- Integrated Freewheeling Protection (LS and HS)

- 0.55 A Peak Current

- $R_{DS(on)} = 1.0 \Omega \text{ (typ)}$

- 5 MHz SPI Communication

- 16 Bit Frame Error Detection

- Daisy Chain Compatible with Multiple of 8 bit Devices

- Compliance with 3.3 V and 5 V Systems

- Undervoltage and Overvoltage Lockout

- Discriminated Fault Reporting

- Over Current Protection

- Over-temperature Protection

- Underload Detection

- Exposed Pad Package

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

- This is a Pb-Free Device

### **Typical Applications**

- Automotive

- Industrial

- DC Motor Management for HVAC Application

# ON Semiconductor®

www.onsemi.com

### SSOP24 NB EP CASE 940AK

### **MARKING DIAGRAM**

NCV7720 AWLYWWG NCV7720A AWLYWWG

NCV7720 or = Specific Device Code NCV7720A

NC\/7720 or

= Assembly Location

WL = Wafer Lot Y = Year WW = Work Week

G = Pb–Free Package

# **ORDERING INFORMATION**

See detailed ordering and shipping information on page 24 of this data sheet.

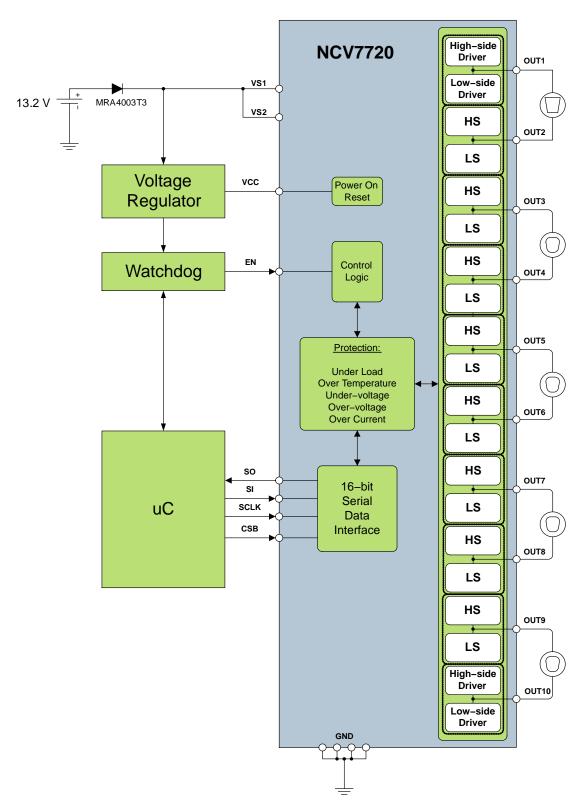

Figure 1. Typical Application

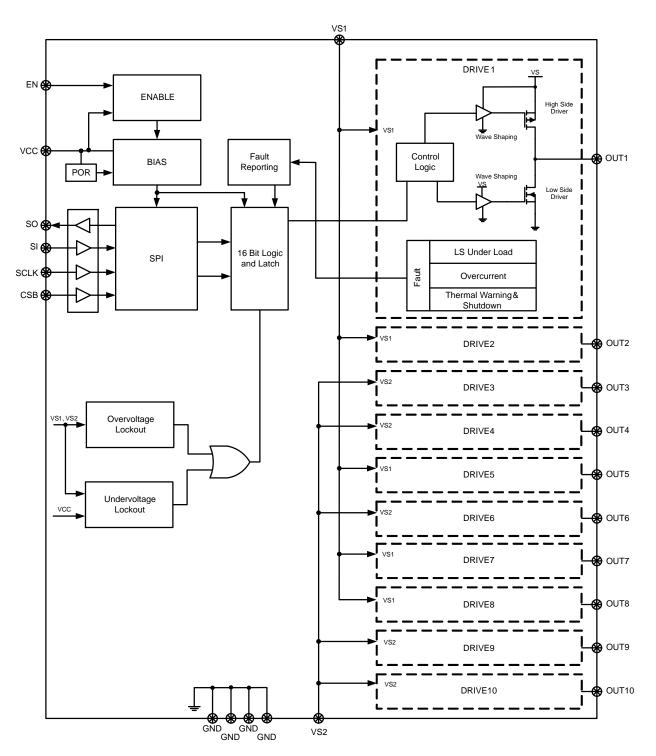

Figure 2. Block Diagram

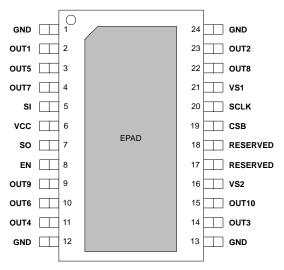

Figure 3. Pinout - SSOP24

### PIN FUNCTION DESCRIPTION The pin-out for the Deca Half-Bridge in SSOP24 package is shown in the table below.

| Pin#<br>SSOP24 | Symbol      | Description                                                                                                            |

|----------------|-------------|------------------------------------------------------------------------------------------------------------------------|

| 1              | GND         | Ground                                                                                                                 |

| 2              | OUT1        | Half-bridge output 1                                                                                                   |

| 3              | OUT5        | Half-bridge output 5                                                                                                   |

| 4              | OUT7        | Half-bridge output 7                                                                                                   |

| 5              | SI          | 16 bit serial communication input. 3.3V/5V (TTL) Compatible – internally pulled down.                                  |

| 6              | VCC         | Power supply input for Logic.                                                                                          |

| 7              | SO          | 16 bit serial communication output. 3.3V/5V Compliant                                                                  |

| 8              | EN          | Enable – active high; wakes the device from sleep mode. 3.3V/5V (TTL) Compatible – internally pulled down.             |

| 9              | OUT9        | Half-bridge output 9                                                                                                   |

| 10             | OUT6        | Half-bridge output 6                                                                                                   |

| 11             | OUT4        | Half-bridge output 4                                                                                                   |

| 12             | GND         | Ground                                                                                                                 |

| 13             | GND         | Ground                                                                                                                 |

| 14             | OUT3        | Half-bridge output 3                                                                                                   |

| 15             | OUT10       | Half-bridge output 10                                                                                                  |

| 16             | VS2         | Power Supply input for outputs 3, 4, 6, 9, and 10. This pin must be connected to VS1 externally.                       |

| 17             | Reserved    | Factory use – connect to GND or leave unconnected – internally pulled down.                                            |

| 18             | Reserved    | Factory use – connect to GND or leave unconnected – internally pulled down.                                            |

| 19             | CSB         | Chip select bar – active low; enables serial communication operation. 3.3V/5V (TTL) Compatible – internally pulled up. |

| 20             | SCLK        | Serial communication clock input. 3.3V/5V (TTL) Compatible – internally pulled down.                                   |

| 21             | VS1         | Power Supply input for outputs 1, 2, 5, 7, 8, and all pre-drivers. This pin must be connected to VS2 externally.       |

| 22             | OUT8        | Half-bridge output 8                                                                                                   |

| 23             | OUT2        | Half-bridge output 2                                                                                                   |

| 24             | GND         | Ground                                                                                                                 |

| EPAD           | Exposed Pad | Connect to GND or leave unconnected.                                                                                   |

# MAXIMUM RATINGS (Voltages are with respect to GND)

|                    | Rating                                                                          | Symbol             | Value                                   | Unit |

|--------------------|---------------------------------------------------------------------------------|--------------------|-----------------------------------------|------|

| VSx Pin Voltage    | (VS1, VS2)<br>(DC)<br>(AC), t < 500 ms, lvsx > -2 A                             | VSxdcMax<br>VSxac  | -0.3 to 40<br>-1.0                      | V    |

| I/O Pin Voltage    | ( Vcc, SI, SCLK, CSB, SO, EN)                                                   | VioMax             | -0.3 to 5.5                             | V    |

| OUTx Pin Voltage   | (DC)<br>(AC)<br>(AC), t< 500 ms, IOUTx > -1.1 A<br>(AC), t< 500 ms, IOUTx < 1 A | VoutxDc<br>VoutxAc | -0.3 to 40<br>-0.3 to 40<br>-1.0<br>1.0 | V    |

| OUTx Pin Current   | (OUT1,, OUT10)                                                                  | loutxlmax          | -2.0 to 2.0                             | А    |

| Junction Temperatu | ure Range                                                                       | TJ                 | -40 to 150                              | °C   |

| Storage Temperatu  | re Range                                                                        | Tstr               | -55 to 150                              | °C   |

| Peak Reflow Solde  | ring Temperature: Pb-free 60 to 150 seconds at 217°C                            | (Note 1)           | 260                                     | °C   |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. See or download ON Semiconductor's Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

### **ATTRIBUTES**

| Characteristic                                                                  | Symbol                                       | Value                                                        | Unit                               |                      |

|---------------------------------------------------------------------------------|----------------------------------------------|--------------------------------------------------------------|------------------------------------|----------------------|

| Short Circuit Reliability Characterization                                      |                                              | AECQ10x                                                      | Grade A                            | _                    |

| ESD Capability Human Body Model per AEC-Q100-002 Machine Model per AEC-Q100-003 | VSx, OUTx<br>All Other Pins                  | Vesd4k<br>Vesd2k<br>Vesd200                                  | ≥ ±4.0 kV<br>≥ ±2.0 kV<br>≥ ±200 V |                      |

| Moisture Sensitivity Level                                                      |                                              | MSL                                                          | MSL2                               | _                    |

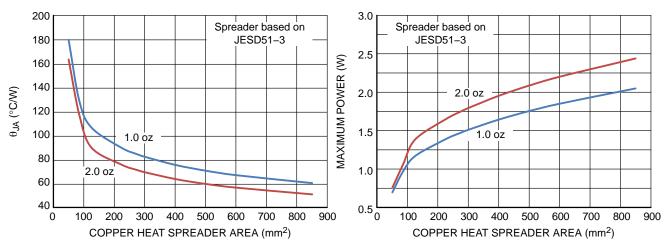

| Package Thermal Resistance – Still–air Junction–to–Ambient Junction–to–Board    | (Note 2)<br>(Note 3)<br>(Note 2)<br>(Note 3) | R <sub>θJA</sub><br>R <sub>θJA</sub><br>RψJBOARD<br>RψJBOARD | 54<br>26<br>22<br>14               | °C/W<br>°C/W<br>°C/W |

<sup>2.</sup> Based on JESD51-3, 1.2 mm thick FR4, 2S0P PCB with 2 oz. copper and 18 thermal vias to 600 mm<sup>2</sup> spreader on bottom layer.

# **RECOMMENDED OPERATING CONDITIONS**

| Parameter                    | Symbol | Min  | Max  | Unit |

|------------------------------|--------|------|------|------|

| Digital Supply Input Voltage | VCCOp  | 3.15 | 5.25 | V    |

| Battery Supply Input Voltage | VSxOp  | 5.5  | 28   | V    |

| DC Output Current            | IxOp   | -    | 0.55 | Α    |

| Junction Temperature         | TjOp   | -40  | 125  | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

<sup>3.</sup> Based on JESD51-7, 1.2 mm thick FR4, 1S2P PCB with 2 oz. copper and 18 thermal vias to 80x80 mm 1 oz. internal spreader planes.

# **ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}C \leq T_{J} \leq 150^{\circ}C,~5.5~V \leq VSx \leq 40~V,~3.15~V \leq V_{CC} \leq 5.25~V,~EN = V_{CC},~unless~otherwise~specified.)$

| Characteristic                                    | Symbol                   | Conditions                                                                             | Min          | Тур    | Max        | Unit                     |

|---------------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|--------------|--------|------------|--------------------------|

| POWER SUPPLIES                                    |                          |                                                                                        |              |        |            |                          |

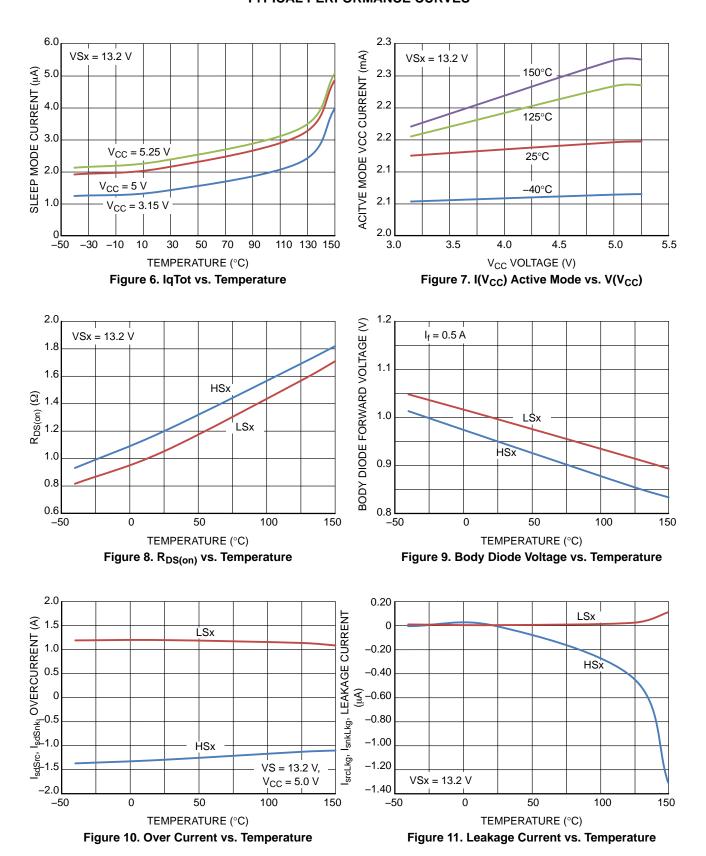

| Supply Current (VS1 + VS2)<br>Sleep Mode          | lqVSx85                  | VS1 = VS2 = 13.2V, V <sub>CC</sub> = 0 V<br>-40°C to 85°C                              | _            | 1.0    | 2.5        | μΑ                       |

| Supply Current (VS1 + VS2)<br>Active Mode         | IvsOp                    | EN = V <sub>CC</sub> , 5.5V < VSx < 28 V<br>No Load                                    | -            | 2.5    | 5.0        | mA                       |

| Supply Current (Vcc)<br>Sleep Mode                | IqV <sub>CC</sub>        | CSB = V <sub>CC</sub> , EN = SI = SCLK = 0 V<br>-40°C to 85°C                          | _            | 1.0    | 2.5        | μΑ                       |

| Active Mode                                       | IV <sub>CC</sub> Op      | EN = CSB = V <sub>CC</sub> , SI = SCLK = 0V<br>No Load                                 | _            | 1.5    | 3.0        | mA                       |

| Total Sleep Mode Current I(VS1) + I(VS2) + I(VCC) | IqTot                    | Sleep Mode, -40°C to 85°C<br>VS1 = VS2 = 13.2 V, No Load                               | -            | 2.0    | 5.0        | μΑ                       |

| VCC Power-on Reset Threshold                      | V <sub>CC</sub> por      | V <sub>CC</sub> increasing                                                             | _            | 2.55   | 2.90       | V                        |

| VSx Undervoltage Detection Threshold              | VSxuv                    | VSx decreasing                                                                         | 3.5          | 4.1    | 4.5        | V                        |

| VSx Undervoltage Detection<br>Hysteresis          | VSxuHys                  |                                                                                        | 100          | -      | 450        | mV                       |

| VSx Overvoltage Detection Threshold               | VsXov                    | VSx increasing                                                                         | 30           | 36     | 40         | V                        |

| VSx Overvoltage Detection Hysteresis              | VSxoHys                  |                                                                                        | 1            | 2.5    | 4          | V                        |

| DRIVER OUTPUT CHARACTERISTICS                     | ;                        |                                                                                        |              |        |            |                          |

| Output High R <sub>DS(on)</sub> (source)          | R <sub>DSon</sub> HS     | lout = -500 mA, Vs = 13.2 V<br>V <sub>CC</sub> = 3.15 V                                | _            | 1.0    | 2.25       | Ω                        |

| Output Low R <sub>DS(on)</sub> (sink)             | R <sub>DSon</sub> LS     | lout = 500 mA, Vs =13.2 V<br>V <sub>CC</sub> = 3.15 V                                  | -            | 1.0    | 2.25       | Ω                        |

| Output Path R <sub>DS(HSx+LSx)</sub>              | RDSonPath                | I <sub>out</sub> =  500  mA, T <sub>J</sub> ≤ 125°C                                    | _            | -      | 4.0        | Ω                        |

| Source Leakage Current                            | IsrcLkg13.2<br>IsrcLkg28 | V <sub>CC</sub> = 5 V,OUT(1-10) = 0 V,<br>-40°C to 85°C;<br>VSx = 13.2 V<br>VSx = 28 V | -1.0<br>-2.0 |        | -<br>-     | μΑ<br>μΑ                 |

| Sink Leakage Current                              | IsnkLkg13.2<br>IsnkLkg28 | V <sub>CC</sub> = 5 V;<br>OUT(1-10) = VSx = 13.2 V<br>OUT(1-10) = VSx = 28 V           | -<br>-       | _<br>_ | 1.0<br>2.0 | μ <b>Α</b><br>μ <b>Α</b> |

| Overcurrent Shutdown Threshold (Source)           | IsdSrc                   | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                    | -2.0         | -1.2   | -0.8       | А                        |

| Overcurrent Shutdown Threshold (Sink)             | IsdSnk                   | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                    | 0.8          | 1.2    | 2.0        | А                        |

| Over Current Delay Timer                          | TdOc                     |                                                                                        | 10           | 25     | 50         | μS                       |

| Underload Detection Threshold (Low Side)          | luldLS                   | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                    | 2.0          | 11     | 20         | mA                       |

| Underload Detection Delay Time                    | TdUld                    | V <sub>CC</sub> = 5 V, VSx = 13.2 V                                                    | 200          | 350    | 600        | μs                       |

| Body Diode Forward Voltage                        | IbdFwd                   | If = 500 mA                                                                            | _            | 0.9    | 1.3        | V                        |

| DRIVER OUTPUT SWITCHING CHARA                     | CTERISTICS               |                                                                                        |              |        |            |                          |

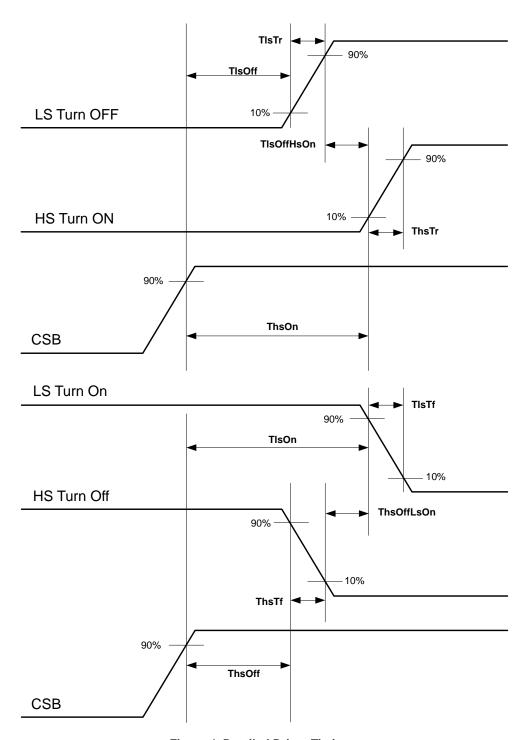

| High Side Turn On Time                            | ThsOn                    | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                                            | -            | 7.5    | 13         | μs                       |

| High Side Turn Off Time                           | ThsOff                   | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                                            | _            | 3.0    | 6.0        | μS                       |

| Low Side Turn On Time                             | TlsOn                    | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                                            | -            | 6.5    | 13         | μS                       |

| Low Side Turn Off Time                            | TIsOff                   | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                                            | -            | 2.0    | 5.0        | μS                       |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 5. This is the minimum time the user must wait between SPI commands.6. This is the minimum time the user must wait between consecutive SRR requests.

# **ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}C \leq T_{J} \leq 150^{\circ}C,~5.5~V \leq VSx \leq 40~V,~3.15~V \leq V_{CC} \leq 5.25~V,~EN = V_{CC},~unless~otherwise~specified.)$

| Characteristic                                   | Symbol           | Conditions                                                         | Min                   | Тур    | Max      | Unit   |

|--------------------------------------------------|------------------|--------------------------------------------------------------------|-----------------------|--------|----------|--------|

| DRIVER OUTPUT SWITCHING CHARA                    | CTERISTICS       | •                                                                  | •                     | •      | •        | •      |

| High Side Rise Time                              | ThsTr            | Vs = 13.2 V, $R_{load}$ = 39 $\Omega$                              | _                     | 4.0    | 8.0      | μS     |

| High Side Fall Time                              | ThsTf            | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                        | <b>-</b>              | 2.0    | 4.0      | μS     |

| Low Side Rise Time                               | TlsTr            | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                        | -                     | 1.0    | 3.0      | μS     |

| Low Side Fall Time                               | TIsTf            | Vs = 13.2 V, $R_{load}$ = 39 $\Omega$                              | -                     | 1.0    | 3.0      | μs     |

| High Side Off to Low Side On<br>Non-Overlap Time | ThsOffLsOn       | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                        | 1.5                   | -      | -        | μS     |

| Low Side Off to High Side On<br>Non-Overlap Time | TlsOffHsOn       | $Vs = 13.2 \text{ V}, R_{load} = 39 \Omega$                        | 1.5                   | -      | -        | μS     |

| THERMAL RESPONSE                                 |                  | •                                                                  |                       | •      | •        | •      |

| Thermal Warning                                  | Twr              | (Note 4)                                                           | 120                   | 140    | 170      | °C     |

| Thermal Warning Hysteresis                       | TwHy             | (Note 4)                                                           | _                     | 20     | -        | °C     |

| Thermal Shutdown                                 | Tsd              | (Note 4)                                                           | 150                   | 175    | 200      | °C     |

| Thermal Shutdown Hysteresis                      | TsdHy            | (Note 4)                                                           | _                     | 20     | -        | °C     |

| LOGIC INPUTS – EN, SI, SCLK, CSB                 |                  |                                                                    |                       |        |          |        |

| Input Threshold High Low                         | VthInH<br>VthInL |                                                                    | 2.0                   | _<br>_ | _<br>0.6 | V<br>V |

| Input Hysteresis - SI, SCLK, CSB                 | VthInHys         |                                                                    | 50                    | 150    | 300      | mV     |

| Input Hysteresis – EN                            | VthENHys         |                                                                    | 150                   | 400    | 800      | mV     |

| Pull-down Resistance - EN, SI, SCLK              | Rpdx             | EN = SI = SCLK = V <sub>CC</sub>                                   | 50                    | 125    | 200      | kΩ     |

| Pull-up Resistance - CSB                         | RpuCSB           | CSB = 0 V                                                          | 50                    | 125    | 250      | kΩ     |

| Input Capacitance                                | Cinx             | (Note 4)                                                           | _                     | -      | 15       | pF     |

| LOGIC OUTPUT - SO                                |                  |                                                                    |                       |        |          |        |

| Output High                                      | VsoH             | ISOURCE = -1 mA                                                    | V <sub>CC</sub> - 0.6 | _      | _        | V      |

| Output Low                                       | VsoL             | ISINK = 1.6 mA                                                     | _                     | -      | 0.4      | V      |

| Tri-state Leakage                                | ItriStLkg        | CSB = 5 V                                                          | -5                    | -      | 5        | μΑ     |

| Tri-state Output Capacitance                     | ItriStCout       | CSB = V <sub>CC</sub> , 0 V < V <sub>CC</sub> < 5.25 V<br>(Note 4) | -                     | -      | 15       | pF     |

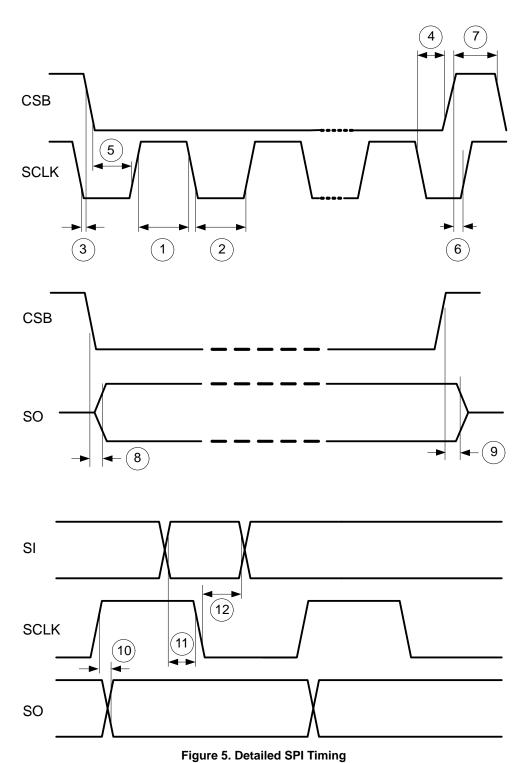

| SERIAL PERIPHERAL INTERFACE                      | •                | •                                                                  | •                     | •      | •        |        |

| -                                                |                  | Timing                                                             |                       |        |          |        |

| Characteristic    | Symbol  | Conditions                                       | Timing<br>Charts # | Min        | Тур | Max    | Unit |

|-------------------|---------|--------------------------------------------------|--------------------|------------|-----|--------|------|

| SCLK Frequency    | Fclk    |                                                  | -                  | -          | -   | 5.0    | MHz  |

| SCLK Clock Period | TpClk   | V <sub>CC</sub> = 5 V<br>V <sub>CC</sub> = 3.3 V | -                  | 200<br>500 | _   | -<br>- | ns   |

| SCLK High Time    | TclkH   |                                                  | 1                  | 85         | -   | _      | ns   |

| SCLK Low Time     | TclkL   |                                                  | 2                  | 85         | _   | _      | ns   |

| SCLK Setup Time   | TclkSup |                                                  | 3, 4               | 85         | _   | _      | ns   |

| SI Setup Time     | TsiSup  |                                                  | 11                 | 50         | -   | -      | ns   |

| SI Hold Time      | TsiH    |                                                  | 12                 | 50         | _   | _      | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 4. Not production tested.

- 5. This is the minimum time the user must wait between SPI commands.

- $\,$  6. This is the minimum time the user must wait between consecutive SRR requests.

# **ELECTRICAL CHARACTERISTICS**

$(-40^{\circ}C \leq T_{J} \leq 150^{\circ}C,~5.5~V \leq VSx \leq 40~V,~3.15~V \leq V_{CC} \leq 5.25~V,~EN = V_{CC},~unless~otherwise~specified.)$

### **SERIAL PERIPHERAL INTERFACE**

| Characteristic                       | Symbol   | Conditions                                               | Timing<br>Charts # | Min | Тур | Max | Unit |

|--------------------------------------|----------|----------------------------------------------------------|--------------------|-----|-----|-----|------|

| CSB Setup Time                       | TcsbSup  |                                                          | 5, 6               | 100 | _   | -   | ns   |

| CSB High Time                        | TcsbH    | (Note 5)                                                 | 7                  | 5.0 | _   | -   | μs   |

| SO enable after CSB falling edge     | TenSo    |                                                          | 8                  | -   | _   | 200 | ns   |

| SO disable after CSB rising edge     | TdisSo   |                                                          | 9                  | -   | _   | 200 | ns   |

| SO Rise/Fall Time                    | TsoR/F   | Cload = 40 pF (Note 4)                                   | -                  | -   | 10  | 25  | ns   |

| SO Valid Time                        | TsoV     | Cload = 40 pF (Note 4)<br>SCLK ↑ to SO 50%               | 10                 | -   | 20  | 50  | ns   |

| EN Low Valid Time                    | TenL     | V <sub>CC</sub> = 5V; EN H→L 50% to OUTx turning off 50% | -                  | 10  | _   | -   | μS   |

| EN High to SPI Valid                 | TenHspiV |                                                          | -                  | -   | _   | 100 | μS   |

| SRR Delay Between Consecutive Frames | Tsrr     | (Note 6)                                                 | -                  | 150 | _   | _   | μS   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

- 4. Not production tested.

- 5. This is the minimum time the user must wait between SPI commands.6. This is the minimum time the user must wait between consecutive SRR requests.

# **CHARACTERISTIC TIMING DIAGRAMS**

Figure 4. Detailed Driver Timing

# **TYPICAL PERFORMANCE CURVES**

### **DETAILED OPERATING DESCRIPTION**

### **General Overview**

The NCV7720 is comprised of twenty power drivers (10 PMOS high–side and 10 NMOS low–side). The drivers are arranged as ten half–bridge output channels, allowing for five independent full–bridge configured loads. Output control and status reporting is handled via the SPI (Serial Peripheral Interface) communications port.

Each output is characterized for a maximum 0.55 A DC load and has a maximum 2.0 A surge capability (at VSx = 13.2 V). Maximum allowable junction temperature is 150°C and may constrain the maximum load current and/or limit the number of drivers active at once.

An active-high enable function (EN) allows global control of the outputs and provides a low quiescent current sleep mode when the device is not being utilized. An internal pull-down resistor is provided on the input to ensure the device enters sleep mode if the input signal is lost.

When EN is asserted, the  $V_{CC}$  POR cycle will proceed and bring the device into normal operation. The device configuration registers can then be programmed via SPI. De–asserting EN clears all registers (no configuration or status data is stored), resets the drivers, and enters sleep mode.

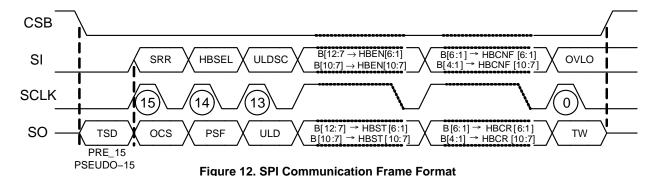

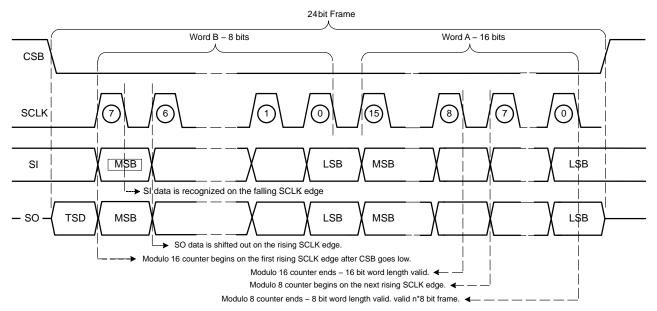

### **SPI Communication**

16-bit full duplex SPI communication has been implemented for device configuration, driver control, and reading the status data. In addition to the 16-bit status data, a pseudo-bit (PRE\_15) can also be retrieved from the SO output.

The device must be enabled (EN = H) for SPI communication. The SPI inputs are TTL compatible and the SO output high level is defined by the applied  $V_{CC}$ . The active–low CSB input has a pull–up resistor and the remaining inputs have pull–down resistors to bias them to known states when the SPI is not active.

The latched thermal shutdown (TSD) status bit PRE\_15 is available on SO until the first rising SCLK edge after CSB goes low. The following conditions must be met for a valid TSD read to be captured:

- 1. SCLK and SI are low before the CSB cycle;

- 2. CSB transitions from high to low;

- 3. CSB setup time (TcsbSup: Figure 5, #5) is satisfied.

Figure 12 shows the SPI communication frame format, and Tables 1 and 2 define the command input and diagnostic status output bits.

Communication is implemented as follows and is also illustrated in Figures 12 and 14:

- 1. SI and SCLK are set to low before the CSB cycle.

- CSB goes low to begin a serial data frame; pseudo-bit PRE\_15 is immediately available at SO.

- 3. SI data is shifted in on every rising edge of SCLK, starting with the most significant bit (MSB), SRR.

- 4. SI data is recognized on every falling edge of the SCLK.

- Current SO data is simultaneously shifted out on every rising edge of SCLK, starting with the MSB (OCS).

- 6. CSB goes high to end the frame and SO becomes tri–state.

- 7. The last 16 bits clocked into SI are transferred to the device's data register if no frame error is detected, otherwise the entire frame is ignored and the previous input data is preserved.

**Table 1. SPI COMMAND INPUT DEFINITIONS**

|      | Channels 10 – 7 (Input Bit # 14 = 1) |                          |                        |                                                         |  |  |  |  |

|------|--------------------------------------|--------------------------|------------------------|---------------------------------------------------------|--|--|--|--|

| Bit# | Name                                 | Function                 | Status*                | Scope                                                   |  |  |  |  |

| 15   | SRR                                  | Status Register Reset**  | 1 = Reset              | Status Reset per HBSEL                                  |  |  |  |  |

| 14   | HBSEL                                | Channel Group Select     | 1 = HB [10:7]          | 1 = HB [10:7]   0 = HB [6:1]                            |  |  |  |  |

| 13   | ULDSC                                | Underload Shutdown       | 1 = Enabled            | Enabled per <b>HBSEL</b> ;<br>Per Half–Bridge Operation |  |  |  |  |

| 12   | X                                    | Not Used                 |                        |                                                         |  |  |  |  |

| 11   | 7 ^                                  | Not Osea                 | -                      | -                                                       |  |  |  |  |

| 10   | HBEN10                               | Enable Half-Bridge 10    |                        |                                                         |  |  |  |  |

| 9    | HBEN9                                | Enable Half-Bridge 9     | 0 = Hi–Z               | Devilled Dridge                                         |  |  |  |  |

| 8    | HBEN8                                | Enable Half-Bridge 8     | 1 = Enabled            | Per Half–Bridge                                         |  |  |  |  |

| 7    | HBEN7                                | Enable Half-Bridge 7     | 1                      |                                                         |  |  |  |  |

| 6    | ,,                                   | N. d. I.                 |                        |                                                         |  |  |  |  |

| 5    | _ X                                  | Not Used                 | -                      | _                                                       |  |  |  |  |

| 4    | HBCNF10                              | Configure Half-Bridge 10 |                        |                                                         |  |  |  |  |

| 3    | HBCNF9                               | Configure Half-Bridge 9  | 0 = LS On, HS Off      |                                                         |  |  |  |  |

| 2    | HBCNF8                               | Configure Half-Bridge 8  | 1 = LS Off, HS On      | Per Half–Bridge                                         |  |  |  |  |

| 1    | HBCNF7                               | Configure Half-Bridge 7  |                        |                                                         |  |  |  |  |

| 0    | OVLO                                 | VSx Overvoltage Lockout  | 1 = Enabled            | Global Lockout                                          |  |  |  |  |

|      | •                                    | Channels 6 -             | 1 (Input Bit # 14 = 0) |                                                         |  |  |  |  |

| Bit# | Name                                 | Function                 | Status*                | Scope                                                   |  |  |  |  |

| 15   | SRR                                  | Status Register Reset**  | 1 = Reset              | Status Reset per HBSEL                                  |  |  |  |  |

| 14   | HBSEL                                | Channel Group Select     | 0 = HB [6:1]           | 1 = HB [10:7]   0 = HB [6:1]                            |  |  |  |  |

| 13   | ULDSC                                | Underload Shutdown       | 1 = Enabled            | Enabled per <b>HBSEL</b> ;<br>Per Half–Bridge Operation |  |  |  |  |

| 12   | HBEN6                                | Enable Half-Bridge 6     |                        |                                                         |  |  |  |  |

| 11   | HBEN5                                | Enable Half-Bridge 5     | 7                      |                                                         |  |  |  |  |

| 10   | HBEN4                                | Enable Half-Bridge 4     | 0 = Hi–Z               |                                                         |  |  |  |  |

| 9    | HBEN3                                | Enable Half-Bridge 3     | 1 = Enabled            | Per Half–Bridge                                         |  |  |  |  |

| 8    | HBEN2                                | Enable Half-Bridge 2     | 7                      |                                                         |  |  |  |  |

| 7    | HBEN1                                | Enable Half-Bridge 1     | 7                      |                                                         |  |  |  |  |

| 6    | HBCNF6                               | Configure Half-Bridge 6  |                        |                                                         |  |  |  |  |

| 5    | HBCNF5                               | Configure Half-Bridge 5  | 7                      |                                                         |  |  |  |  |

| 4    | HBCNF4                               | Configure Half-Bridge 4  | 0 = LS On, HS Off      |                                                         |  |  |  |  |

| 3    | HBCNF3                               | Configure Half-Bridge 3  | 1 = LS Off, HS On      | Per Half–Bridge                                         |  |  |  |  |

| 2    | HBCNF2                               | Configure Half-Bridge 2  | ╡                      |                                                         |  |  |  |  |

| 1    | HBCNF1                               | Configure Half-Bridge 1  | ╡                      |                                                         |  |  |  |  |

| 0    | OVLO                                 | VSx Overvoltage Lockout  | 1 = Enabled            | Global Lockout                                          |  |  |  |  |

<sup>\*</sup>All command input bits are set to 0 at  $V_{CC}$  power–on reset. \*\*Latched faults are cleared and outputs can be re–programmed if no fault exists after SRR asserted.

**Table 2. SPI STATUS OUTPUT DEFINITIONS**

| Channels 10 – 7 (Input Bit # 14 = 1) |        |                                               |                      |                                                              |  |  |  |

|--------------------------------------|--------|-----------------------------------------------|----------------------|--------------------------------------------------------------|--|--|--|

| Bit#                                 | Name   | Function                                      | Status*              | Scope                                                        |  |  |  |

| PRE_15                               | TSD    | Latched Thermal Shutdown                      | 1 = Fault            | Global Notification;<br>Per Half-Bridge Operation            |  |  |  |

| 15                                   | ocs    | Latched Overcurrent<br>Shutdown               | 1 = Fault            | Notification per <b>HBSEL</b> ;<br>Per Half–Bridge Operation |  |  |  |

| 14                                   | PSF    | VS1 and/or VS2<br>Undervoltage or Overvoltage | 1 = Fault            | Global Notification and<br>Global Operation                  |  |  |  |

| 13                                   | ULD    | Underload Detect                              | 1 = Fault            | Notification per <b>HBSEL</b> ;<br>Per Half–Bridge Operation |  |  |  |

| 12                                   | V      | Not Hood                                      | (Hard and data zara) |                                                              |  |  |  |

| 11                                   | X      | Not Used                                      | (Hard coded to zero) | <del>-</del>                                                 |  |  |  |

| 10                                   | HBST10 | Half-Bridge 10 Output Status                  |                      |                                                              |  |  |  |

| 9                                    | HBST9  | Half-Bridge 9 Output Status                   | 0 = Hi–Z             | 5 11 11 5 11                                                 |  |  |  |

| 8                                    | HBST8  | Half-Bridge 8 Output Status                   | 1 = Enabled          | Per Half–Bridge                                              |  |  |  |

| 7                                    | HBST7  | Half-Bridge 7 Output Status                   |                      |                                                              |  |  |  |

| 6                                    | .,     | N II                                          |                      |                                                              |  |  |  |

| 5                                    | Х      | Not Used                                      | (Hard coded to zero) | _                                                            |  |  |  |

| 4                                    | HBCR10 | Half-Bridge 10 Config Status                  |                      |                                                              |  |  |  |

| 3                                    | HBCR9  | Half-Bridge 9 Config Status                   | 0 = LS On, HS Off    |                                                              |  |  |  |

| 2                                    | HBCR8  | Half-Bridge 8 Config Status                   | 1 = LS Off, HS On**  | Per Half-Bridge                                              |  |  |  |

| 1                                    | HBCR7  | Half-Bridge 7 Config Status                   | ]                    |                                                              |  |  |  |

| 0                                    | TW     | Thermal Warning                               | 1 = Fault            | Global Notification;<br>Per Half-Bridge Operation            |  |  |  |

<sup>\*</sup>All status output bits are set to 0 at Vcc power–on reset (POR). \*\*HBCRx is forced to 0 when HBSTx = 0 via POR, SPI, or fault.

**Table 2. SPI STATUS OUTPUT DEFINITIONS**

|        | Channels 6 – 1 (If Previous Input Bit # 14 = 0) |                                               |                     |                                                              |  |  |  |  |  |

|--------|-------------------------------------------------|-----------------------------------------------|---------------------|--------------------------------------------------------------|--|--|--|--|--|

| Bit#   | Name                                            | Function                                      | Status*             | Scope                                                        |  |  |  |  |  |

| PRE_15 | TSD                                             | Latched Thermal Shutdown                      | 1 = Fault           | Global Notification;<br>Per Half–Bridge Operation            |  |  |  |  |  |

| 15     | ocs                                             | Latched Overcurrent<br>Shutdown               | 1 = Fault           | Notification per <b>HBSEL</b> ;<br>Per Half–Bridge Operation |  |  |  |  |  |

| 14     | PSF                                             | VS1 and/or VS2<br>Undervoltage or Overvoltage | 1 = Fault           | Global Notification and<br>Global Operation                  |  |  |  |  |  |

| 13     | ULD                                             | Underload Detect                              | 1 = Fault           | Notification per <b>HBSEL</b> ;<br>Per Half–Bridge Operation |  |  |  |  |  |

| 12     | HBST6                                           | Half-Bridge 6 Output Status                   |                     |                                                              |  |  |  |  |  |

| 11     | HBST5                                           | Half-Bridge 5 Output Status                   |                     |                                                              |  |  |  |  |  |

| 10     | HBST4                                           | Half-Bridge 4 Output Status                   | 0 = Hi–Z            | Deathelf Didne                                               |  |  |  |  |  |

| 9      | HBST3                                           | Half-Bridge 3 Output Status                   | 1 = Enabled         | Per Half–Bridge                                              |  |  |  |  |  |

| 8      | HBST2                                           | Half-Bridge 2 Output Status                   |                     |                                                              |  |  |  |  |  |

| 7      | HBST1                                           | Half-Bridge 1 Output Status                   |                     |                                                              |  |  |  |  |  |

| 6      | HBCR6                                           | Half-Bridge 6 Config Status                   |                     |                                                              |  |  |  |  |  |

| 5      | HBCR5                                           | Half-Bridge 5 Config Status                   |                     |                                                              |  |  |  |  |  |

| 4      | HBCR4                                           | Half-Bridge 4 Config Status                   | 0 = LS On, HS Off   |                                                              |  |  |  |  |  |

| 3      | HBCR3                                           | Half-Bridge 3 Config Status                   | 1 = LS Off, HS On** | Per Half-Bridge                                              |  |  |  |  |  |

| 2      | HBCR2                                           | Half-Bridge 2 Config Status                   | 1                   |                                                              |  |  |  |  |  |

| 1      | HBCR1                                           | Half-Bridge 1 Config Status                   |                     |                                                              |  |  |  |  |  |

| 0      | TW                                              | Thermal Warning                               | 1 = Fault           | Global Notification;<br>Per Half-Bridge Operation            |  |  |  |  |  |

<sup>\*</sup>All status output bits are set to 0 at Vcc power-on reset (POR).

\*\*HBCRx is forced to 0 when HBSTx = 0 via POR, SPI, or fault.

### **Frame Error Detection**

The NCV7720 employs frame error detection to help ensure input data integrity. SCLK is compared to an  $n \times 8$  bit counter and a valid frame (CSB H–L–H cycle) has integer multiples of 8 SCLK cycles. For the first 16 bits shifted into SI, SCLK is compared to a modulo 16 counter (n = 2), and SCLK is compared to a modulo 8 counter (n = 1, 2, ...m) thereafter. This variable modulus facilitates daisy chain operation with devices using different word lengths.

The last 16 bits clocked into SI are transferred to the NCV7720's data register if no frame error is detected, otherwise the entire frame is ignored and the previous input data is preserved.

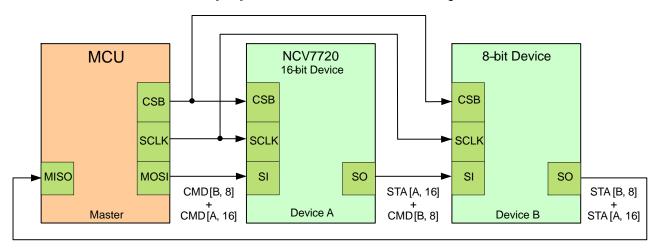

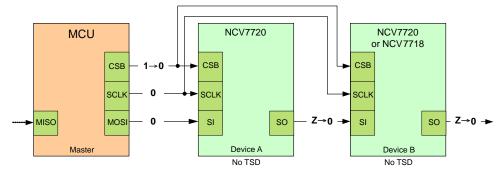

### **Daisy Chain Operation**

Daisy chain operation is possible with multiple 16-bit and 8-bit devices that have a compatible SPI protocol. The clock phase and clock polarity with respect to the data for all the devices in the chain must be the same as the NCV7720.

CSB and SCLK are parallel connected to every device in the chain while SO and SI are series connected between each device.

The master's MOSI is connected to the SI of the first device and the first device's SO is connected to the next device's SI. The SO of the final device in the chain is connected to the master's MISO.

The hardware configuration for the NCV7720 daisy chained with an 8– bit SPI device is shown in Figure 13. A 24–bit frame made of 16–bit word 'A' and 8–bit word 'B' is sent from the master. Command word B is sent first followed by word A. The master simultaneously receives status word B first followed by word A. The progression of data from the MCU through the sequential devices is illustrated in Figure 14.

Compliance with the illustrated frame format is required for proper daisy chain operation. Situations should be avoided where an incorrect multiple of 8 bits is sent to the devices, but the frame length does not cause a frame error in the devices. For example, the word order could be inadvertently interleaved or reversed. Invalid data is accepted by the NCV7720 in such scenarios and possibly by other devices in the chain, depending on their frame error implementation. Data is received as a command by the device at the beginning of the chain, but the device at the end of the chain may receive status data from the preceding device as a command.

CMD [x, n] = Command Word to Device 'x', Length 'n' STA [x, n] = Status Word from Device 'x', Length 'n'

Figure 13. Daisy Chain Configuration

Figure 14. Daisy Chain - 24 bit Frame Format

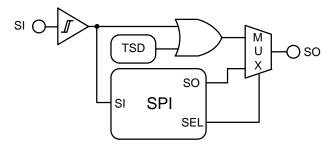

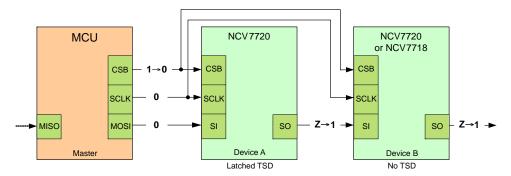

### **TSD Bit in Daisy Chain Operation**

The SO path is designed to allow TSD status retrieval in a daisy chain configuration using NVC7720 or other devices with identical SPI functionality. The TSD status bit is OR'd with SI and then multiplexed with the device's usual status data (Figure 15).

CSB is held high and SI and SCLK are held low by the master before the start of the SPI frame. TSD status is immediately available as bit PRE\_15 at SO (SO = TSD) when CSB goes low to begin the frame. The usual status data (SO = STA) becomes available after the first rising SCLK edge.

The TSD status automatically propagates through the chain from the SO output of the previous device to the SI input of the next. This is shown in Figures 16 and 17, first without a TSD fault in either device (Figure 16), and then subsequently with a latched TSD fault (TSD = 1) in device "A" propagating through to device "B" (Figure 17).

Since the TSD status of any device propagates automatically through the entire chain, it is not possible to determine which device (or devices) has a fault (TSD = 1). The usual status data from each device will need to be examined to determine where a fault (or faults) may exist.

Figure 15. TSD SPI Link

Figure 16. Daisy Chain Without TSD Fault

Figure 17. Daisy Chain With TSD Fault

### **Power Up/Down Control**

The  $V_{CC}$  supply input powers the device's logic core. A  $V_{CC}$  power–on reset (POR) function provides controlled power–up/down.  $V_{CC}$  POR initializes the command input and status output registers to their default states (0x00), and ensures that the bridge output and SO drivers maintain Hi–Z as power is applied. SPI communication and normal device operation can proceed once  $V_{CC}$  rises above the POR threshold.

The VS1 and VS2 supply inputs power their respective output drivers (refer to Figure 2 and the PIN FUNCTION DESCRIPTION). The VSx inputs are monitored to ensure that the supply stays within the recommended operating range. If the VSx supply moves into either of the VS undervoltage or overvoltage regions, the output drivers are switched to Hi–Z but command and status data is preserved.

#### **Driver Control**

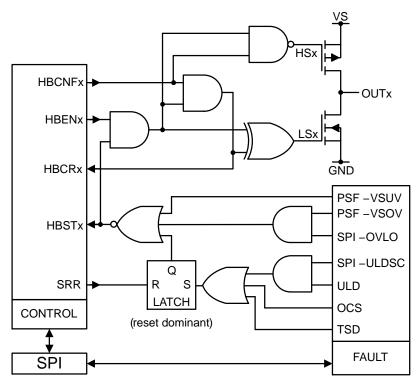

The NCV7720 has the flexibility to control each half-bridge driver channel via SPI. Actual driver output state is determined by the command input and the current fault status bits as shown in Figure 18 and Table 3.

The channels are divided into two groups and each group is selected by the HBSEL input bit (see Table 1). High–side (HSx) and low–side (LSx) drivers of the same channel cannot be active at the same time, and non–overlap delays are imposed when switching between HSx and LSx drivers in the same channel. This control design thus prevents current shoot–through.

After the device has powered up and the drivers are allowed to turn on, the drivers remain on until commanded off via SPI or until a fault condition occurs.

Figure 18. Simplified Half-Bridge Control Logic

Table 3. OUTPUT STATE VS. COMMAND AND STATUS

| Comi  | mand   | Sta   |       |      |

|-------|--------|-------|-------|------|

| HBENx | HBCNFx | HBSTx | HBCRx | OUTx |

| Х     | Х      | 0     | 0     | Z    |

| 0     | Х      | 0     | 0     | Z    |

| 1     | 0      | 1     | 0     | GND  |

| 1     | 1      | 1     | 1     | VS   |

# DIAGNOSTICS, PROTECTIONS, STATUS REPORTING AND RESET

### Overview

The NCV7720 employs diagnostics designed to prevent destructive overstress during a fault condition. Diagnostics are classified as either supervisory or protection functions (Table 4). Supervisory functions provide status information about device conditions. Protection functions provide status information and activate fault management behaviors.

Diagnostics resulting in output shutdown and latched status may depend on a qualifier and may require user

intervention for output recovery and status memory clear. Diagnostics resulting in output lockout and non-latched status (VSOV or VSUV) may recover and clear automatically. Output configurations can be changed during output lockout. Outputs assume the new configurations or resume the previous configurations when an auto-recover fault is resolved. Table 5 shows output states during faults and output recovery modes, and Table 6 shows the status memory and memory clear modes.

**Table 4. Diagnostic Classes and Functions**

| Name  | Class       | Function                    |

|-------|-------------|-----------------------------|

| TSD   | Protection  | Thermal Shutdown            |

| ocs   | Protection  | Overcurrent Shutdown        |

| PSF   | Supervisory | Under/overvoltage Lockout   |

| ULD   | Protection  | Underload Shutdown          |

| HBSTX | Supervisory | Half-Bridge X Output Status |

| HBCRX | Supervisory | Half-Bridge X Config Status |

| TW    | Supervisory | Thermal Warning             |

Table 5. OUTPUT STATE VS. FAULT AND OUTPUT RECOVERY

| Fault      | Qualifier | OUTx<br>State                                | OUTx<br>Recovery |

|------------|-----------|----------------------------------------------|------------------|

| TSD        | -         | →Z                                           | Send SRR         |

| ocs        | -         | →Z                                           | Send SRR         |

| PSF – VSOV | OVLO = 1  | $\rightarrow Z \rightarrow Y_n \mid Y_{n+1}$ | Auto*            |

|            | OVLO = 0  | Unaffected                                   | -                |

| PSF – VSUV | -         | $\rightarrow Z \rightarrow Y_n \mid Y_{n+1}$ | Auto*            |

| ULD        | ULDSC = 1 | →Z                                           | Send SRR         |

|            | ULDSC = 0 | Unaffected                                   | -                |

| TW         | -         | Unaffected                                   | -                |

<sup>\*</sup>OUTx returns to its previous state (Yn) or new state (Yn+1) if fault is removed.

Table 6. STATUS MEMORY VS. FAULT AND MEMORY CLEAR

| Fault      | Qualifier | Status<br>Memory | Memory<br>Clear |

|------------|-----------|------------------|-----------------|

| TSD        | _         | Latched          | Send SRR        |

| ocs        | -         | Latched          | Send SRR        |

| PSF – VSOV | OVLO = X  | Non-Latched      | Auto*           |

| PSF – VSUV | -         | Non-Latched      | Auto*           |

| ULD        | ULDSC = X | Latched          | Send SRR        |

| TW         | ı         | Non-Latched      | Auto*           |

<sup>\*</sup>Status memory returns to its no-fault state if fault is removed.

### **Status Information Retrieval**

Current status information as selected by HBSEL is retrieved during each SPI frame. To preserve device configuration and output states, the previous SI data pattern must be sent during the status retrieval frame.

Status information is prevented from being updated during a SPI frame but new status becomes available after CSB goes high at the end of the frame provided the frame did not contain an SRR request. For certain device faults, it may not be possible to determine which channel (or channels) has a particular fault (or faults) since notification may be via a single global status bit. The complete status data from all channels may need to be examined to determine where a fault may exist.

### Status Register Reset - SRR

Sending SRR = 1 clears status memory and re–activates faulted outputs for channels as selected by HBSEL. The previous SI data pattern must be sent with SRR to preserve device configuration and output states. SRR takes effect at the rising edge of CSB and a timer (Tsrr) is started. Tsrr is the minimum time the user must wait between consecutive SRR requests. If a fault is still present when SRR is sent, protection can be re–engaged and shutdown can recur. The device can also be reset by toggling the EN pin or by VCC power–on reset.

### **Diagnostics Details**

The following sections describe the individual diagnostics and some behaviors. In each description and illustration, a SPI frame is assumed to always be valid and the SI data pattern sent for HBCNFx and HBENx is the same as the previous frame. Actual results can depend on asynchronous fault events and SPI clock frequency and frame rate.

### **Undervoltage Lockout**

### Global Notification, Global Operation

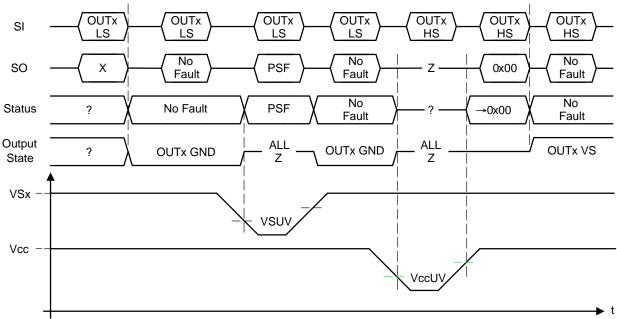

Undervoltage detection and lockout control is provided by monitoring the VS1, VS2 and  $V_{CC}$  supply inputs. Undervoltage hysteresis is provided to ensure clean detection transitions. Undervoltage timing is shown in Figure 19.

Undervoltage at either VSx input turns off all outputs and sets the power supply fail (PSF) status bit. The outputs return to their previously programmed state and the PSF status bit is cleared when VSx rises above the hysteresis voltage level. SPI is available and programmed output enable and configuration states are maintained if proper V<sub>CC</sub> is present during VSx undervoltage. V<sub>CC</sub> undervoltage turns all outputs off and clears the command input and status output registers.

Figure 19. Undervoltage Timing

### **Overvoltage Lockout**

### Global Notification, Global Operation

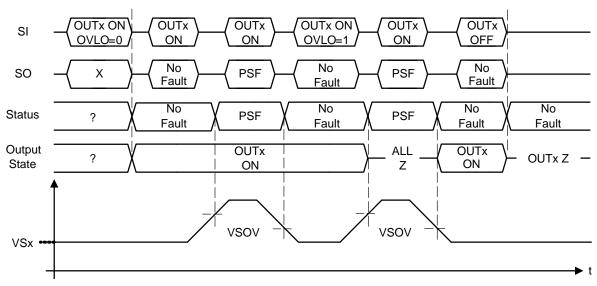

Overvoltage detection and lockout control is provided by monitoring the VS1 and VS2 supply inputs. Overvoltage hysteresis is provided to ensure clean detection transitions. Overvoltage timing is shown in Figure 20.

Overvoltage at either VSx input turns off all outputs if the overvoltage lockout input bit is set (OVLO = 1, HBSEL =

X), and sets the power supply fail (PSF) status bit (see Tables 5 and 6). The outputs return to their previously programmed state and the PSF status bit is cleared when VSx falls below the hysteresis voltage level.

To reduce stress, it is recommended to operate the device with OVLO bit asserted to ensure that the drivers turn off during a load dump scenario.

Figure 20. Overvoltage Timing

### Overcurrent Shutdown

### Notification per HBSEL, Per Half-Bridge Operation

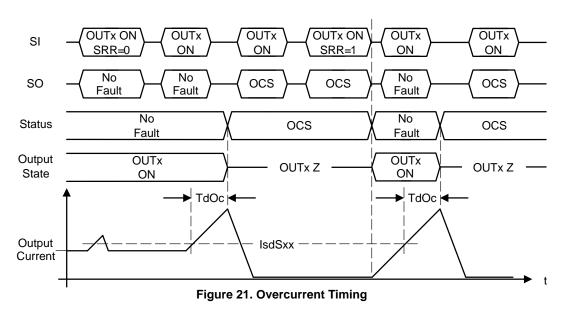

Overcurrent detection and shutdown control is provided by monitoring each HS and LS driver. Overcurrent timing is shown in Figure 21. Overcurrent in either driver starts a channel's overcurrent delay timer. If overcurrent exists after the delay, both drivers are latched off and the overcurrent (OCS) status bit is set. The OCS bit is cleared and channels are re–activated by sending SRR = 1. The channel group select (HBSEL) input bit determines which channels are affected by SRR.

A persistent overcurrent cause should be resolved prior to re–activation to avoid repetitive stress on the drivers. Extended exposure to stress may affect device reliability.

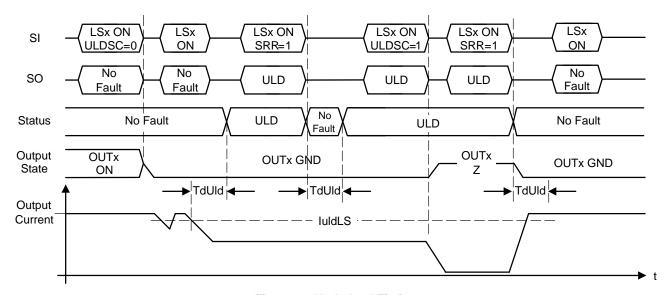

### **Underload Shutdown**

# Notification per HBSEL, Shutdown per HBSEL

Underload detection and shutdown control is provided by monitoring each LS driver. Underload timing is shown in Figure 22. Underload at a LS driver starts the global underload delay timer. If underload occurs in another channel after the global timer has been started, the delay for any subsequent underload will be the remainder of the timer. The timer runs continuously with a persistent underload condition.

If underload exists after the delay and if the underload shutdown (ULDSC) command bit is set, both HS and LS drivers are latched off and the underload (ULD) status bit is set; otherwise the drivers remain on and the ULD bit is set (see Table 5 and 6). The ULD bit is cleared and channels are re–activated by sending SRR = 1. The channel group select (HBSEL) input bit determines which channels are affected by SRR and also determines which half–bridges are latched off via the ULDSC command bit (see Table 1).

Underload may result from a fault (e.g. open-load) condition or normal circuit behavior (e.g. L/R tau). In motor applications it is often desirable to actively brake the motor by turning on both HS or LS drivers in two half-bridge channels. If the configuration is two LS drivers (LS brake), an underload will result as the motor current decays normally. Utilizing HS brake instead will avoid underload notification.

Figure 22. Underload Timing

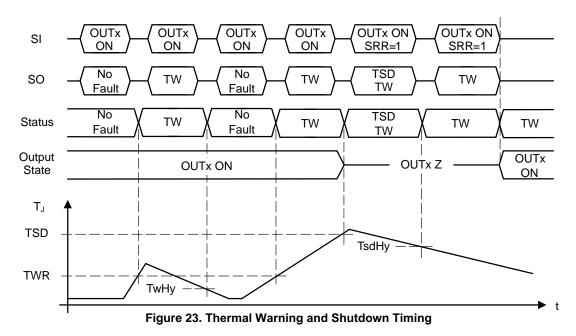

### Thermal Warning and Thermal Shutdown

# Global Notification, Per Half-Bridge Operation

Thermal warning (TW) and thermal shutdown (TSD) detection and control are provided for each half-bridge by monitoring the driver pair's thermal sensor. Thermal hysteresis is provided for each of the warning and shutdown functions to ensure clean detection transitions. Since TW notification precedes TSD, software polling of the TW bit enables avoidance of thermal shutdown. Thermal warning and shutdown timing is shown in Figure 23.

The TW status bit is set when a half-bridge's sensor temperature exceeds the warning level  $(T_J > Twr)$ , and the

bit is automatically cleared when sensor temperature falls below the warning hysteresis level ( $T_J < TwHy$ ). A channel's output state is unaffected by TW.

When sensor temperature exceeds the shutdown level ( $T_J > Tsd$ ), the channel's HS and LS drivers are latched off, the TW bit is/remains set, and the TSD (PRE\_15) bit is set. The TSD bit is cleared and all affected channels in a group are re–activated ( $T_J < TsdHy$ ) by sending SRR = 1. The channel group select (HBSEL) input bit determines which channels are affected by SRR.

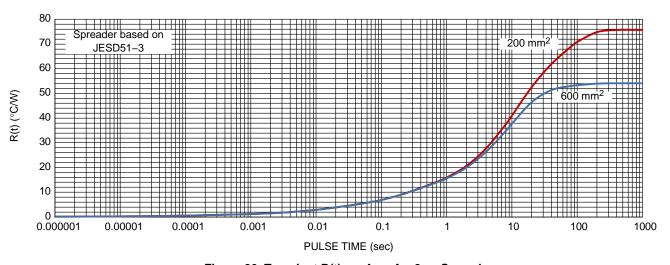

### THERMAL PERFORMANCE ESTIMATES

Figure 24.  $\theta_{JA}$  vs. Cu Area and Thickness

Figure 25. Maximum Power vs. Cu Area and Thickness

Figure 26. Transient R(t) vs. Area for 2 oz Spreader

### **ORDERING INFORMATION**

| Device        | Marking  | Package   | Shipping <sup>†</sup> |

|---------------|----------|-----------|-----------------------|

| NCV7720DQR2G  | NCV7720  | SSOP24    | 2500 / Tape & Reel    |

| NCV7720DQAR2G | NCV7720A | (Pb-Free) |                       |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

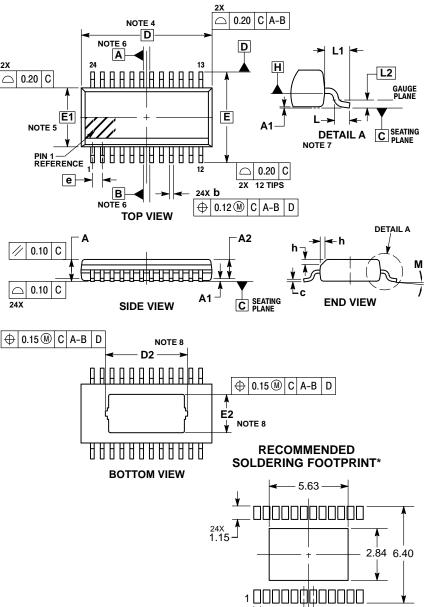

### PACKAGE DIMENSIONS

### SSOP24 NB EP

CASE 940AK **ISSUE O**

0.40

#### NOTES:

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ASME

Y14.5M, 1994.

2. CONTROLLING DIMENSION: MILLIMETERS.

3. DIMENSION 6 DOES NOT INCLUDE DAMBAR

- PROTRUSION. DAMBAR PROTRUSION SHALL BE 0.10 MAX. AT MMC. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OF THE FOOT. DIMENSION 6 APPLIES TO THE FLAT SECTION OF THE LEAD BETWEEN 0.10 TO 0.25 FROM THE LEAD TIP.

- FROM THE LEAD TIP.

DIMENSION D DOES NOT INCLUDE MOLD

FLASH, PROTRUSIONS OR GATE BURRS. MOLD

FLASH, PROTRUSIONS OR GATE BURRS SHALL

NOT EXCEED 0.15 PER SIDE. DIMENSION D IS

DETERMINED AT DATUM PLANE H.

DIMENSION FA DOES NOT INCLUDE INTERLIFED.

- DIMENSION E1 DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 PER SIDE. DIMENSION E1 IS DETERMINED AT DA-TUM PLANE H

- 6. DATUMS A AND B ARE DETERMINED AT DATUM PLANE H.

A1 IS DEFINED AS THE VERTICAL DISTANCE

- AT IS DEFINED AS THE VEH TO ALL DISTANCE FROM THE SEATING PLANE TO THE LOWEST POINT ON THE PACKAGE BODY. CONTOURS OF THE THERMAL PAD ARE UNCONTROLLED WITHIN THE REGION DEFINED

- BY DIMENSIONS D2 AND E2.

|     | MILLIMETERS |          |  |  |

|-----|-------------|----------|--|--|

| DIM | MIN         | MAX      |  |  |

| Α   | -           | 1.70     |  |  |

| A1  | 0.00        | 0.10     |  |  |

| A2  | 1.10        | 1.65     |  |  |

| b   | 0.19        | 0.30     |  |  |

| С   | 0.09        | 0.20     |  |  |

| D   | 8.64 BSC    |          |  |  |

| D2  | 5.28        | 5.58     |  |  |

| Е   | 6.00 BSC    |          |  |  |

| E1  | 3.90        | 3.90 BSC |  |  |

| E2  | 2.44        | 2.64     |  |  |

| е   | 0.65        | 0.65 BSC |  |  |

| h   | 0.25        | 0.50     |  |  |

| L   | 0.40        | 0.85     |  |  |

| L1  | 1.00 REF    |          |  |  |

| L2  | 0.25 BSC    |          |  |  |

| М   | 0°          | 8°       |  |  |

0.65

**PITCH**

DIMENSIONS: MILLIMETERS

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnif

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800–282–9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

# Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: org@eplast1.ru

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.