# TLS205B0

Linear Voltage Post Regulator Low Dropout, Low Noise, 3.3 V, Adjustable, 500 mA

TLS205B0EJV TLS205B0EJV33 TLS205B0LDV TLS205B0LDV33

# Data Sheet

Rev. 1.2, 2015-01-15

# Automotive Power

### Linear Voltage Post Regulator Low Dropout, Low Noise, 3.3 V, Adjustable, 500 mA

TLS205B0

#### Features

- Low Noise down to 24  $\mu V_{\text{RMS}}$  (BW = 10 Hz to 100 kHz)

- 500 mA Current Capability

- Low Quiescent Current: 30 µA

- Wide Input Voltage Range up to 20 V

- Internal circuitry working down to 2.3 V

- 2.5% Output Voltage Accuracy (over full temperature and load range)

- Low Dropout Voltage: 320 mV

- Very low Shutdown Current: < 1 µA</li>

- No Protection Diodes Needed

- Fixed Output Voltage: 3.3 V

- Adjustable Version with Output from 1.22 V to 20 V

- Stable with ≥ 3.3 µF Output Capacitor

- Stable with Aluminium, Tantalum or Ceramic Output Capacitors

- Reverse Polarity Protection

- No Reverse Current

- Overcurrent and Overtemperature Protected

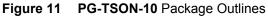

- PG-DSO-8 Exposed Pad and PG-TSON-10 Exposed Pad Package

- Suitable for Use in Automotive Electronics as Post Regulator

- Green Product (RoHS compliant)

- AEC Qualified

The TLS205B0 is a micropower, low noise, low dropout voltage regulator. The device is capable of supplying an output current of 500 mA with a dropout voltage of 320 mV. Designed for use in battery-powered systems, the low quiescent current of 30  $\mu$ A makes it an ideal choice.

A key feature of the TLS205B0 is its low output noise. By adding an external 10 nF bypass capacitor output noise values down to 24  $\mu V_{\text{RMS}}$  over a 10 Hz to 100 kHz bandwidth can be reached. The TLS205B0 voltage regulator

| Туре          | Package              | Marking  |

|---------------|----------------------|----------|

| TLS205B0EJV   | PG-DSO-8 Exposed Pad | 205B0V   |

| TLS205B0EJV33 | PG-DSO-8 Exposed Pad | 205B0V33 |

| TLS205B0LDV   | PG-TSON-10           | 205B0V   |

| TLS205B0LDV33 | PG-TSON-10           | 205B0V3  |

PG-TSON-10

### TLS205B0

#### Overview

is stable with output capacitors as small as 3.3 µF. Small ceramic capacitors can be used without the series resistance required by many other linear voltage regulators.

Internal protection circuitry includes reverse battery protection, current limiting and reverse current protection. The TLS205B0 comes as fixed output voltage variant 3.3 V as well as adjustable device with a 1.22 V reference voltage. It is available in a PG-DSO-8 Exposed Pad and as well as in a PG-TSON-10 Exposed Pad package.

**Block Diagram**

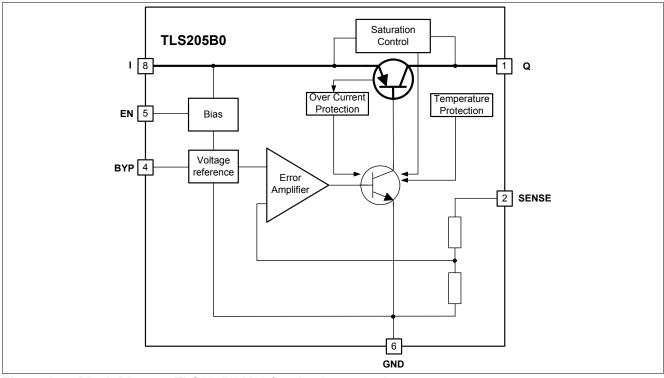

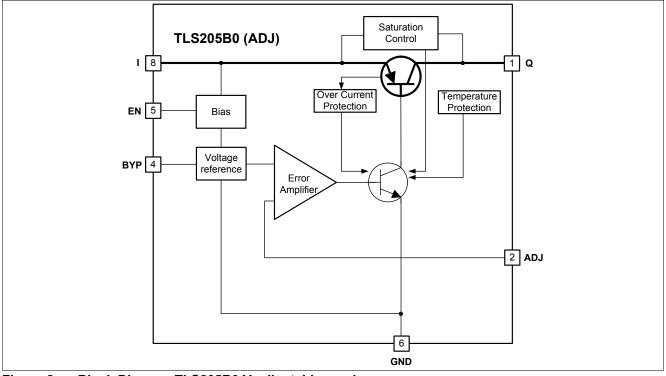

# 2 Block Diagram

Note: Pin numbers in block diagrams refer to the PG-DSO-8 Exposed Pad package type.

Figure 1 Block Diagram TLS205B0 V33 fixed voltage version

Figure 2 Block Diagram TLS205B0 V adjustable version

**Pin Configuration**

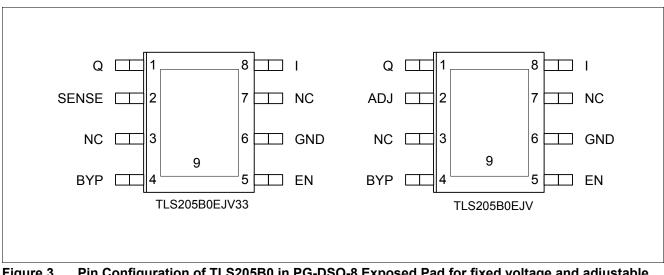

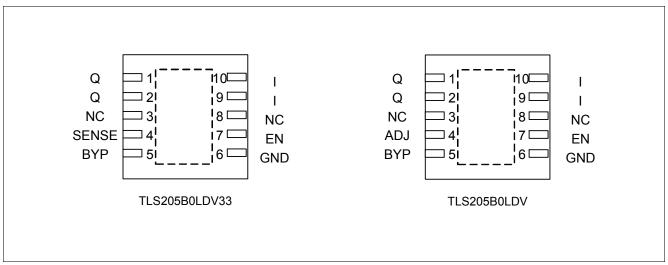

# 3 Pin Configuration

## 3.1 Pin Assignment

Figure 3 Pin Configuration of TLS205B0 in PG-DSO-8 Exposed Pad for fixed voltage and adjustable version

Figure 4 Pin Configuration of TLS205B0 in PG-TSON-10 for fixed voltage and adjustable version

#### **Pin Configuration**

## 3.2 Pin Definitions and Functions

| Pin                               | Symbol                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 (DSO-8 EP)<br>1,2 (TSON-10)     | Q                                 | <b>Output.</b> Supplies power to the load. For this pin a minimum output capacitor of 3.3 $\mu$ F is required to prevent oscillations. Larger output capacitors may be required for applications with large transient loads in order to limit peak voltage transients or when the regulator is applied in conjunction with a bypass capacitor. For more details please refer to "Application Information" on Page 24.                                                                                                                                          |

| 2 (DSO-8 EP)<br>4 (TSON-10)       | SENSE<br>(fix voltage<br>version) | <b>Output Sense.</b> For the fixed voltage version the SENSE pin is the input to the error amplifier. This allows to achieve an optimized regulation performance in case of small voltage drops $R_p$ that occur between regulator and load. In applications where such drops are relevant they can be eliminated by connecting the SENSE pin directly at the load. In standard configuration the SENSE pin can be directly connected to Q. For further details please refer to the section "Kelvin Sense Connection" on Page 25.                              |

| 2 (DSO-8 EP)<br>4 (TSON-10)       | ADJ<br>(adjustable<br>version)    | <b>Adjust.</b> For the adjustable version the ADJ pin is the input to the error amplifier.<br>The ADJ pin voltage is 1.22 V referenced to ground and allows a output voltage range from 1.22 V to 20 V- $V_{DR}$ . The ADJ pin is internally clamped to $\pm$ 7 V. Please note that the bias current of the ADJ pin is flowing into the pin. Its typical value of 60 nA shows a good stability with temperature. For further details please refer to Typical Performance Graph "Adjust Pin Bias Current versus Junction <b>Temperature</b> $T_J$ " on Page 20. |

| 3, 7 (DSO-8 EP)<br>3, 8 (TSON-10) | NC                                | <b>No Connect.</b> The NC Pins have no connection to any internal circuitry. Connect either to GND or leave open.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4 (DSO-8 EP)<br>5 (TSON-10)       | ВҮР                               | <b>Bypass.</b> The BYP pin is used to bypass the reference of the TLS205B0 to achieve low noise performance. The BYP-pin is clamped internally to $\pm 0.6$ V (i.e. one $V_{\text{BE}}$ ). A small capacitor from the output Q to the BYP pin will bypass the reference to lower the output voltage noise <sup>1)</sup> . If not used this pin must be left unconnected.                                                                                                                                                                                       |

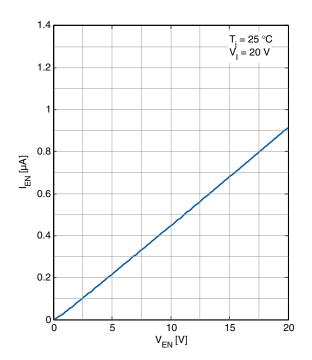

| 5 (DSO-8 EP)<br>7 (TSON-10)       | EN                                | <b>Enable.</b> With the EN pin the TLS205B0 can be put into a low power shutdown state. The output will be off when the EN is pulled low. The EN pin can be driven either by 3.3 V or 5 V logic or as well by open-collector logic with pull-up resistor. The pull-up resistor is required to supply the pull-up current of the open-collector gate <sup>2)</sup> and the EN pin current <sup>3)</sup> . Please note that if the EN pin is not used it must be connected to $V_{\rm I}$ . It must not be left floating.                                        |

| 6 (DSO-8 EP)<br>6 (TSON-10)       | GND                               | <b>Ground.</b> For the ADJ version connect the bottom of the output voltage setting resistor divider directly to the GND pin for optimum load regulation performance.                                                                                                                                                                                                                                                                                                                                                                                          |

#### **Pin Configuration**

| Pin                             | Symbol | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 8 (DSO-8 EP)<br>9, 10 (TSON-10) | 1      | <b>Input.</b> The device is supplied by the input pin I. A capacitor at the input pin is required if the device is more than 6 inches away from the main input filter capacitor or if a non-negligible inductance is present at the input I <sup>4)</sup> . The TLS205B0 is designed to withstand reverse voltages on the input pin I with respect to GND and output Q. In the case of reverse input (e.g. due to a wrongly attached battery) the device will act as if there is a diode in series with its input. In this way there will be no reverse current flowing into the regulator and no reverse voltage will appear at the load. Hence, the device will protect both - the device itself and the load. |

| 9 (DSO-8 EP)<br>11 (TSON-10)    | Tab    | <b>Exposed Pad.</b> To ensure proper thermal performance, solder Pin 11 of TSON-10 to the PCB ground and tie directly to Pin 6. In the case of DSO-8 EP as well solder Pin 9 to the PCB ground and tie directly to Pin 6 (GND).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

1) A maximum value of 10 nF can be used for reducing output voltage noise over the bandwidth from 10 Hz to 100 kHz.

2) Normally several microamperes.

3) Typical value is 1 µA.

In general the output impedance of a battery rises with frequency, so it is advisable to include a bypass capacitor in batterypowered circuits. Depending on actual conditions an input capacitor in the range of 1 to 10 μF is sufficient.

**General Product Characteristics**

# 4 General Product Characteristics

### 4.1 Absolute Maximum Ratings

### Table 1 Absolute Maximum Ratings <sup>1)</sup>

$T_j$  = -40 °C to +150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                            | Symbol                          |          | Values | \$       | Unit | Note /<br>Test Condition | Number   |

|--------------------------------------|---------------------------------|----------|--------|----------|------|--------------------------|----------|

|                                      |                                 | Min.     | Тур.   | Max.     |      |                          |          |

| Input Voltage                        |                                 |          |        | I        |      |                          | 1        |

| Voltage                              | $V_1$                           | -20      | -      | 20       | V    | -                        | P_4.1.1  |

| Output Voltage                       | +                               | <u>!</u> |        | ŧ        |      | +                        | •        |

| Voltage                              | VQ                              | -20      | -      | 20       | V    | -                        | P_4.1.2  |

| Input to Output Differential Voltage | V <sub>1</sub> - V <sub>Q</sub> | -20      | -      | 20       | V    | -                        | P_4.1.3  |

| Sense Pin                            |                                 |          |        |          |      |                          | -        |

| Voltage                              | $V_{SENSE}$                     | -20      | -      | 20       | V    | -                        | P_4.1.4  |

| ADJ Pin                              |                                 | <b>I</b> |        | <b>I</b> |      |                          |          |

| Voltage                              | $V_{ADJ}$                       | -7       | -      | 7        | V    | -                        | P_4.1.5  |

| BYP Pin                              |                                 |          |        |          |      |                          |          |

| Voltage                              | $V_{BYP}$                       | -0.6     | -      | 0.6      | V    |                          | P_4.1.6  |

| Enable Pin                           |                                 |          | •      |          |      |                          |          |

| Voltage                              | $V_{\sf EN}$                    | -20      | -      | 20       | V    | -                        | P_4.1.7  |

| Temperatures                         |                                 |          |        |          |      |                          |          |

| Junction Temperature                 | $T_{\rm j}$                     | -40      | -      | 150      | °C   | -                        | P_4.1.8  |

| Storage Temperature                  | T <sub>stg</sub>                | -55      | -      | 150      | °C   | -                        | P_4.1.9  |

| ESD Susceptibility                   |                                 |          |        |          |      | ·                        |          |

| All Pins                             | $V_{ESD}$                       | -2       | -      | 2        | kV   | HBM <sup>2)</sup>        | P_4.1.10 |

| All Pins                             | $V_{ESD}$                       | -1       | _      | 1        | kV   | CDM <sup>3)</sup>        | P_4.1.11 |

1) Not subject to production testing, specified by design.

2) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 k $\Omega$ , 100 pF)

3) ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101

#### Notes

1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **General Product Characteristics**

## 4.2 Functional Range

#### Table 2Functional Range

| Parameter                                           | Symbol         |                 | Value | S    | Unit | Note /<br>Test Condition            | Number  |

|-----------------------------------------------------|----------------|-----------------|-------|------|------|-------------------------------------|---------|

|                                                     |                | Min.            | Тур.  | Max. |      |                                     |         |

| Input Voltage Range<br>(fix voltage version)        | V <sub>1</sub> | 3.8 V           | -     | 20   | V    | -                                   | P_4.2.1 |

| Input Voltage Range<br>(adjustable voltage version) | V <sub>1</sub> | 2.3             | -     | 20   | V    | _1)                                 | P_4.2.2 |

| Output Capacitor's Requirements for Stability       | C <sub>Q</sub> | 3.3             | -     | -    | μF   | $C_{\rm BYP}$ = 0 nF <sup>2)</sup>  | P_4.2.3 |

| Output Capacitor's Requirements for Stability       | C <sub>Q</sub> | 6.8             | -     | -    | μF   | $0 < C_{\rm BYP} \le 10$ nF $^{2)}$ | P_4.2.4 |

| ESR                                                 | ESR            | _ <sup>3)</sup> | _     | 3    | Ω    | - <sup>2)</sup>                     | P_4.2.5 |

| Operating Junction Temperature                      | Tj             | -40             | _     | 125  | °C   | -                                   | P_4.2.6 |

1) For the TLS205B0 adjustable version the minimum limit of the functional range  $V_1$  is tested and specified with the ADJ- pin connected to the Q pin.

2) for further details see corresponding graph.

3)  $C_{\text{BYP}} = 0 \text{ nF}$ ,  $C_{\text{Q}} \ge 3.3 \mu\text{F}$ ; please note that for cases where a bypass capacitor at BYP is used – depending on the actual applied capacitance of  $C_{\text{Q}}$  and  $C_{\text{BYP}}$  a minimum requirement for ESR of  $C_{\text{Q}}$  may apply.

Note: Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

#### Table 3Thermal Resistance 1)

| Parameter              | Symbol              |      | Value    | S    | Unit | Note /                                                 | Number  |

|------------------------|---------------------|------|----------|------|------|--------------------------------------------------------|---------|

|                        |                     | Min. | Тур.     | Max. |      | <b>Test Condition</b>                                  |         |

| TLS205B0EJ (PG-DSO-8 I | Exposed Pad)        | L    | <b>I</b> |      |      |                                                        |         |

| Junction to Case       | R <sub>thJC</sub>   | -    | 7.0      | -    | K/W  | -                                                      | P_4.3.1 |

| Junction to Ambient    | R <sub>thJA</sub>   | -    | 39       | _    | K/W  | - <sup>2)</sup>                                        | P_4.3.2 |

| Junction to Ambient    | R <sub>thJA</sub>   | -    | 155      | _    | K/W  | Footprint only 3)                                      | P_4.3.3 |

| Junction to Ambient    | R <sub>thJA</sub>   | -    | 66       | -    | K/W  | 300 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.4 |

| Junction to Ambient    | R <sub>thJA</sub>   | -    | 52       | -    | K/W  | 600 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.5 |

| TLS205B0LD (PG-TSON-1  | 0)                  |      |          |      |      |                                                        |         |

| Junction to Case       | $R_{\mathrm{thJC}}$ | -    | 6.4      | -    | K/W  | -                                                      | P_4.3.6 |

| Junction to Ambient    | R <sub>thJA</sub>   | -    | 53       | -    | K/W  | - <sup>2)</sup>                                        | P_4.3.7 |

| Junction to Ambient    | $R_{thJA}$          | -    | 183      | _    | K/W  | Footprint only <sup>3)</sup>                           | P_4.3.8 |

#### **General Product Characteristics**

#### Table 3Thermal Resistance 1)

| Parameter           | Symbol            |      | Value | s    | Unit | Note /<br>Test Condition                               | Number   |

|---------------------|-------------------|------|-------|------|------|--------------------------------------------------------|----------|

|                     |                   | Min. | Тур.  | Max. |      |                                                        |          |

| Junction to Ambient | R <sub>thJA</sub> | -    | 69    | -    | K/W  | 300 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.9  |

| Junction to Ambient | R <sub>thJA</sub> | -    | 57    | -    | K/W  | 600 mm <sup>2</sup> heatsink area on PCB <sup>3)</sup> | P_4.3.10 |

1) Not subject to production test, specified by design.

Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70 μm Cu, 2 x 35 μm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

3) Specified  $R_{\text{thJA}}$  value is according to JEDEC JESD 51-3 at natural convection on FR4 1s0p board; The Product (Chip+Package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 1 copper layer (1 x 70 µm Cu).

#### Table 4 Electrical Characteristics

-40 °C <  $T_j$  < 125 °C; all voltages with respect to ground; positive current defined flowing out of pin; unless otherwise specified.

| Parameter                                                        | Symbol          | Values |       |       | Unit | Note / Test Condition                                                                        | Number   |

|------------------------------------------------------------------|-----------------|--------|-------|-------|------|----------------------------------------------------------------------------------------------|----------|

|                                                                  |                 | Min.   | Тур.  | Max.  |      |                                                                                              |          |

| Minimum Operating Voltage                                        | <sup>1)</sup>   |        |       |       |      |                                                                                              |          |

| Minimum Operating Voltage                                        | $V_{\rm I,min}$ | -      | 1.8   | 2.3   | V    | $I_{\rm Q}$ = 500 mA <sup>2) 3)</sup>                                                        | P_5.0.1  |

| Output Voltage 4)                                                |                 | 1      |       | _     | ł    |                                                                                              | 1        |

| TLS205B0EJV33<br>TLS205B0LDV33                                   | V <sub>Q</sub>  | 3.220  | 3.30  | 3.380 | V    | 1 mA < $I_Q$ < 500 mA ;<br>4.3 V < $V_1$ < 20 V                                              | P_5.0.2  |

| TLS205B0EJV<br>TLS205B0LDV                                       | V <sub>Q</sub>  | 1.190  | 1.220 | 1.250 | V    | 1 mA < $I_{\rm Q}$ < 500 mA ;<br>2.3V < $V_{\rm I}$ < 20 V <sup>3)</sup>                     | P_5.0.3  |

| Line Regulation                                                  |                 | 1      |       | _     | ł    |                                                                                              | 1        |

| TLS205B0EJV33<br>TLS205B0LDV33                                   | $\Delta V_{Q}$  | -      | 1     | 20    | mV   | $\Delta V_1$ = 3.8 V to 20 V ;<br>$I_Q$ = 1 mA                                               | P_5.0.4  |

| TLS205B0EJV<br>TLS205B0LDV                                       | $\Delta V_{Q}$  | -      | 1     | 20    | mV   | $\Delta V_1$ = 2.0 V to 20 V ;<br>$I_Q$ = 1 mA <sup>3</sup>                                  | P_5.0.5  |

| Load Regulation                                                  | I               |        |       |       |      |                                                                                              |          |

| TLS205B0EJV33<br>TLS205B0LDV33                                   | $\Delta V_{Q}$  | -      | 9     | 22    | mV   | $T_{\rm J}$ = 25 °C; $V_{\rm I}$ = 4.3 V ;<br>$\Delta I_{\rm Q}$ = 1 to 500 mA               | P_5.0.6  |

| TLS205B0EJV33<br>TLS205B0LDV33                                   | $\Delta V_{Q}$  | -      | -     | 38    | mV   | $V_1 = 4.3 \text{ V};$<br>$\Delta I_0 = 1 \text{ to 500 mA}$                                 | P_5.0.7  |

| TLS205B0EJV<br>TLS205B0LDV                                       | $\Delta V_{Q}$  | -      | 4     | 8     | mV   | $T_{\rm J}$ = 25 °C ; $V_{\rm I}$ = 2.3 V ;<br>$\Delta I_{\rm Q}$ = 1 to 500 mA <sup>3</sup> | P_5.0.8  |

| TLS205B0EJV<br>TLS205B0LDV                                       | $\Delta V_{Q}$  | -      | -     | 14    | mV   | $V_1 = 2.3 \text{ V};$<br>$\Delta I_Q = 1 \text{ to 500 mA}^{3)}$                            | P_5.0.9  |

| Dropout Voltage <sup>2) 5) 6)</sup>                              |                 |        |       | 1     |      |                                                                                              | 1        |

| Dropout Voltage                                                  | V <sub>DR</sub> | -      | 130   | 190   | mV   | $I_{\rm Q}$ = 10 mA ; $V_{\rm I}$ = $V_{\rm Q,nom}$ ;<br>$T_{\rm J}$ = 25 °C                 | P_5.0.10 |

| Dropout Voltage                                                  | V <sub>DR</sub> | _      | -     | 250   | mV   | $I_{\rm Q}$ = 10 mA ; $V_{\rm I}$ = $V_{\rm Q,nom}$                                          | P_5.0.11 |

| Dropout Voltage                                                  | V <sub>DR</sub> | -      | 170   | 220   | mV   | $I_{\rm Q}$ = 50 mA ; $V_{\rm I}$ = $V_{\rm Q,nom}$ ;<br>$T_{\rm J}$ = 25 °C                 | P_5.0.12 |

| Dropout Voltage                                                  | $V_{DR}$        | _      | -     | 320   | mV   | $I_{\rm Q}$ = 50 mA ; $V_{\rm I}$ = $V_{\rm Q,nom}$                                          | P_5.0.13 |

| Dropout Voltage                                                  | V <sub>DR</sub> | -      | 200   | 240   | mV   | $I_{\rm Q} = 100 \text{ mA}$ ;<br>$V_{\rm I} = V_{\rm Q,nom}$ ; $T_{\rm J} = 25 \text{ °C}$  | P_5.0.14 |

| Dropout Voltage                                                  | V <sub>DR</sub> | _      | _     | 340   | mV   | $I_{\rm Q}$ = 100 mA ; $V_{\rm I}$ = $V_{\rm Q,nom}$                                         | P_5.0.15 |

| Dropout Voltage                                                  | V <sub>DR</sub> | -      | 320   | 350   | mV   | $I_{\rm Q} = 500 \text{ mA}$ ;<br>$V_{\rm I} = V_{\rm Q,nom}$ ; $T_{\rm J} = 25 \text{ °C}$  | P_5.0.16 |

| Dropout Voltage                                                  | V <sub>DR</sub> | -      | -     | 450   | mV   | $I_{\rm Q}$ = 500 mA ; $V_{\rm I}$ = $V_{\rm Q,nom}$                                         | P_5.0.17 |

| Quiescent Current                                                |                 | 1      |       |       | 1    |                                                                                              |          |

| Quiescent Current <sup>5) 7)</sup><br>(Active-Mode, EN-pin high) | Iq              | -      | 30    | 60    | μA   | $V_{\rm I}$ = $V_{\rm Q,nom}$ ;<br>$I_{\rm Q}$ = 0 mA                                        | P_5.0.18 |

#### Table 4 Electrical Characteristics (cont'd)

-40 °C <  $T_j$  < 125 °C; all voltages with respect to ground; positive current defined flowing out of pin; unless otherwise specified.

| Parameter                                                                        | Symbol              | Values |      |      | Unit              | Note / Test Condition                                                                                                                   | Number   |

|----------------------------------------------------------------------------------|---------------------|--------|------|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                                                  |                     | Min.   | Тур. | Max. | _                 |                                                                                                                                         |          |

| Quiescent Current<br>(Off-Mode, EN-pin low)                                      | Iq                  | -      | 0.1  | 1    | μA                | $V_{\rm I} = 6 \ {\rm V} \ ; \ V_{\rm EN} = 0 \ {\rm V} \ ; \ T_{\rm J} = 25 \ {\rm ^{\circ}C}$                                         | P_5.0.19 |

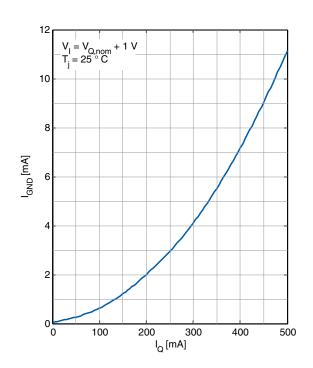

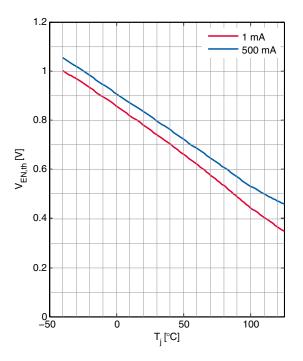

| GND Pin Current <sup>5) 7)</sup>                                                 | I                   | 1      |      | 1    |                   |                                                                                                                                         |          |

| GND Pin Current                                                                  | $I_{\rm GND}$       | -      | 50   | 100  | μA                | $V_{\rm I} = V_{\rm Q,nom};$<br>$I_{\rm Q} = 1 \text{ mA}$                                                                              | P_5.0.20 |

| GND Pin Current                                                                  | $I_{\rm GND}$       | -      | 300  | 850  | μA                | $V_1 = V_{Q,nom};$<br>$I_Q = 50 \text{ mA}$                                                                                             | P_5.0.21 |

| GND Pin Current                                                                  | $I_{\rm GND}$       | -      | 0.7  | 2.2  | mA                | $V_{\rm I} = V_{\rm Q,nom}$ ;<br>$I_{\rm Q}$ = 100 mA                                                                                   | P_5.0.22 |

| GND Pin Current                                                                  | $I_{\rm GND}$       | -      | 3    | 8    | mA                | $V_{\rm I} = V_{\rm Q,nom}$ ;<br>$I_{\rm Q}$ = 250 mA                                                                                   | P_5.0.23 |

| GND Pin Current                                                                  | $I_{\rm GND}$       | -      | 11   | 22   | mA                | $V_{I} = V_{Q,nom}$ ;<br>$I_{Q} = 500 \text{ mA}$ ; $T_{J} \ge 25 \text{ °C}$                                                           | P_5.0.24 |

| GND Pin Current                                                                  | I <sub>GND</sub>    | -      | 11   | 31   | mA                | $V_{\rm I}$ = $V_{\rm Q,nom}$ ; $I_{\rm Q}$ = 500 mA;<br>$T_{\rm J}$ < 25 °C                                                            | P_5.0.25 |

| Enable                                                                           | L                   |        |      |      |                   |                                                                                                                                         |          |

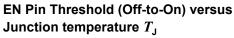

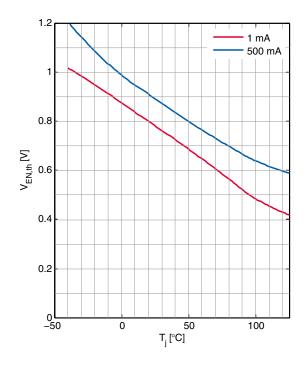

| Enable Threshold High                                                            | $V_{th,EN}$         | -      | 0.8  | 2.0  | V                 | $V_{\rm Q}$ = Off to On                                                                                                                 | P_5.0.26 |

| Enable Threshold Low                                                             | V <sub>tl,EN</sub>  | 0.25   | 0.65 | _    | V                 | $V_{\rm Q}$ = On to Off                                                                                                                 | P_5.0.27 |

| EN Pin Current <sup>8)</sup>                                                     | I <sub>EN</sub>     | _      | 0.01 | _    | μA                | $V_{\rm EN} = 0  \text{V}$ ; $T_{\rm J} = 25  ^{\circ}\text{C}$                                                                         | P_5.0.28 |

| EN Pin Current <sup>8)</sup>                                                     | I <sub>EN</sub>     | _      | 1    | _    | μA                | $V_{\rm EN} = 20V$ ; $T_{\rm J} = 25 ^{\circ}{\rm C}$                                                                                   | P_5.0.29 |

| Adjust Pin Bias Current 9)                                                       |                     |        |      |      |                   |                                                                                                                                         |          |

| ADJ Pin Bias Current                                                             | $I_{\rm bias, ADJ}$ | _      | 60   | _    | nA                | <i>T</i> <sub>1</sub> = 25 °C                                                                                                           | P_5.0.30 |

| Output Voltage Noise <sup>10)</sup>                                              | 5100,7120           |        |      |      |                   | •                                                                                                                                       |          |

| Output Voltage Noise<br>TLS205B0EJV <sup>11)</sup><br>TLS205B0LDV <sup>11)</sup> | e <sub>no</sub>     | -      | 41   | -    | $\mu V_{\rm RMS}$ | $C_{\rm Q}$ = 10 µF ;<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz                                     | P_5.0.31 |

| Output Voltage Noise<br>TLS205B0EJV <sup>11)</sup><br>TLS205B0LDV <sup>11)</sup> | e <sub>no</sub>     | -      | 28   | -    | μV <sub>RMS</sub> | $C_{\rm Q}$ = 10 µF<br>+250mΩ resistor in series;<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz         | P_5.0.32 |

| Output Voltage Noise<br>TLS205B0EJV <sup>11)</sup><br>TLS205B0LDV <sup>11)</sup> | e <sub>no</sub>     | -      | 29   | -    | $\mu V_{\rm RMS}$ | $C_{\rm Q}$ = 22 µF<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz                                       | P_5.0.33 |

| Output Voltage Noise<br>TLS205B0EJV <sup>11)</sup><br>TLS205B0LDV <sup>11)</sup> | e <sub>no</sub>     | _      | 24   | -    | μV <sub>RMS</sub> | $C_{\rm Q}$ = 22 µF<br>+250m $\Omega$ resistor in series;<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz | P_5.0.34 |

#### Table 4 Electrical Characteristics (cont'd)

-40 °C <  $T_j$  < 125 °C; all voltages with respect to ground; positive current defined flowing out of pin; unless otherwise specified.

| Parameter                                              | Symbol               | Values |          |      | Unit              | Note / Test Condition                                                                                                           | Number   |

|--------------------------------------------------------|----------------------|--------|----------|------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|----------|

|                                                        |                      | Min.   | Тур.     | Max. |                   |                                                                                                                                 |          |

| Output Voltage Noise<br>TLS205B0EJV33<br>TLS205B0LDV33 | e <sub>no</sub>      | -      | 45       | -    | $\mu V_{\rm RMS}$ | $C_{\rm Q}$ = 10 µF ;<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz                             | P_5.0.35 |

| Output Voltage Noise<br>TLS205B0EJV33<br>TLS205B0LDV33 | e <sub>no</sub>      | -      | 35       | -    | μV <sub>RMS</sub> | $C_{\rm Q}$ = 10 µF<br>+250mΩ resistor in series;<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz | P_5.0.36 |

| Output Voltage Noise<br>TLS205B0EJV33<br>TLS205B0LDV33 | e <sub>no</sub>      | -      | 33       | -    | $\mu V_{\rm RMS}$ | $C_{\rm Q}$ = 22 µF<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz                               | P_5.0.37 |

| Output Voltage Noise<br>TLS205B0EJV33<br>TLS205B0LDV33 | e <sub>no</sub>      | -      | 30       | -    | μV <sub>RMS</sub> | $C_{\rm Q}$ = 22 µF<br>+250mΩ resistor in series;<br>$C_{\rm BYP}$ = 10 nF ;<br>$I_{\rm Q}$ = 500 mA ;<br>BW = 10 Hz to 100 kHz | P_5.0.38 |

| Power Supply Ripple Rejection                          | on <sup>10)</sup>    | •      | <u>!</u> | - !  |                   |                                                                                                                                 |          |

| Power Supply Ripple Rejection                          | PSRR                 | -      | 65       | -    | dB                | $V_{\rm I}$ - $V_{\rm Q}$ = 1.5 V (avg) ;<br>$V_{\rm RIPPLE}$ = 0.5 Vpp ;<br>$f_{\rm r}$ = 120 Hz ; $I_{\rm Q}$ = 500 mA        | P_5.0.39 |

| Output Current Limitation                              | !                    |        | i        |      |                   | •                                                                                                                               |          |

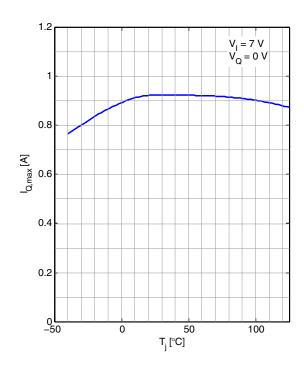

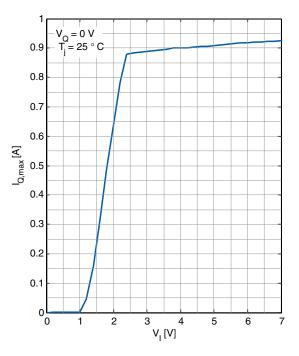

| Output Current Limit                                   | $I_{\rm Q,limit}$    | 520    | -        | -    | mA                | $V_{\rm I}$ = 7 V ; $V_{\rm Q}$ = 0 V                                                                                           | P_5.0.40 |

| Output Current Limit                                   | $I_{\rm Q,limit}$    | 520    | -        | -    | mA                | $V_{\rm I} = V_{\rm Q,nom} + 1  \text{V}  \text{or}$<br>2.3 V <sup>12</sup> ; $\Delta V_{\rm Q} = -0.1  \text{V}$               | P_5.0.41 |

| Input Reverse Leakage Curre                            | nt                   |        | i        |      |                   | •                                                                                                                               |          |

| Input Reverse Leakage                                  | $I_{\rm leak, rev}$  | -      | -        | 1    | mA                | $V_{\rm I}$ = -20 V ; $V_{\rm Q}$ = 0 V                                                                                         | P_5.0.42 |

| Reverse Output Current <sup>13)</sup>                  |                      |        |          |      |                   |                                                                                                                                 |          |

| Fixed Voltage Version                                  | I <sub>Reverse</sub> | _      | 10       | 20   | μA                | $V_{\rm Q} = V_{\rm Q,nom}$ ; $V_{\rm I} < V_{\rm Q,nom}$ ;<br>$T_{\rm J} = 25 \ ^{\circ}{\rm C}$                               | P_5.0.43 |

| Adjustable Voltage Version                             | I <sub>Reverse</sub> | -      | 5        | 10   | μA                | $V_{\rm Q}$ = 1.22 V ; $V_{\rm I}$ < 1.22 V ;<br>$T_{\rm I}$ = 25 °C <sup>3)</sup>                                              | P_5.0.44 |

1) This parameter defines the minimum input voltage for which the device is powered up and provides the maximum nominal output current of 500 mA. The output voltage of the adjustable version in this condition depends on the chosen setting of the external voltage divider as well as on the applied conditions – thus the device is either regulating its nominal output voltage or is in tracking mode. The 3.3 V fixed voltage version is by definition in tracking mode for such low input voltages.

2) For the adjustable version of the TLS205B0 the dropout voltage for certain output voltage / load conditions will be restricted by the minimum input voltage specification.

3) The adjustable version of the TLS205B0 is tested / specified for these conditions with the ADJ pin connected to the Q pin.

- 4) The operation conditions are limited by the maximum junction temperature. The regulated output voltage specification will only apply for conditions where the limit of the maximum junction temperature is fulfilled. It will therefore not apply for all possible combinations of input voltage and output current at a given output voltage. When operating at maximum input voltage, the output current must be limited for thermal reasons. The same holds true when operating at maximum output current where the input voltage range must be limited for thermal reasons.

- 5) To satisfy requirements for minimum input voltage, the TLS205B0 adjustable version is tested and specified for these conditions with an external resistor divider (two 250 k resistors) for an output voltage of 2.44 V. The external resistors will add a 5 µA DC load on the output.

- 6) The dropout voltage is the minimum input to output voltage differential needed to maintain regulation at a specified output current. In dropout, the output voltage will be equal to  $V_1 V_{DR}$

- 7) GND-pin current is tested with  $V_1 = V_{Q,nom}$  and a current source load. This means that this parameter is tested while being in the dropout region. The GND pin current will in most cases decrease slightly at higher input voltages please also refer to the corresponding typical performance graphs.

- 8) The EN pin current flows into EN pin.

- 9) The ADJ pin current flows into ADJ pin.

- 10) Not subject to production test, specified by design.

- 11) ADJ pin connected to output pin Q.

- 12) Whichever of the two values of  $V_{\rm l}$  is greater in order to also satisfy the requirements for  $V_{\rm l,min}$ .

- 13) Reverse output current is tested with the I pin grounded and the Q pin forced to the rated output voltage. This current flows into the Q pin and out of the GND pin.

- Note: The listed characteristics are ensured over the operating range of the integrated circuit. Typical characteristics specified mean values expected over the production spread. If not otherwise specified, typical characteristics apply at  $T_A = 25$  °C and the given supply voltage.

### TLS205B0

#### **Electrical Characteristics**

## 5.1 Typical Performance Characteristics

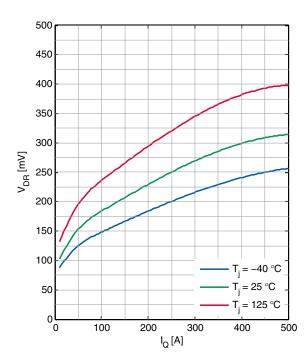

Dropout Voltage  $V_{\rm DR}$  versus Output Current  $I_{\rm Q}$

Dropout Voltage  $V_{\text{DR}}$  versus Junction Temperature  $T_{i}$

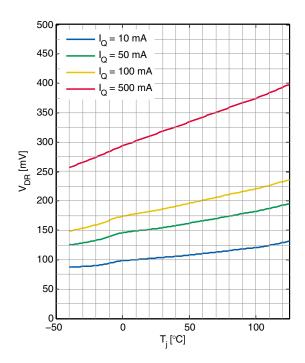

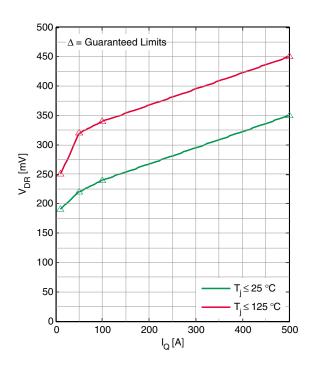

# Guaranteed Dropout Voltage $V_{\rm DR}$ versus Output Current $I_{\rm Q}$

Quiescent Current versus Junction Temperature  $T_i$

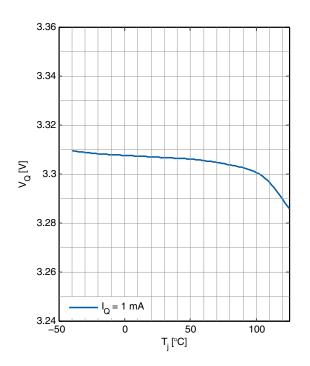

# Output Voltage $V_{\rm Q}$ versus Junction Temperature $T_{\rm J}$ (TLS205B0EJV33)

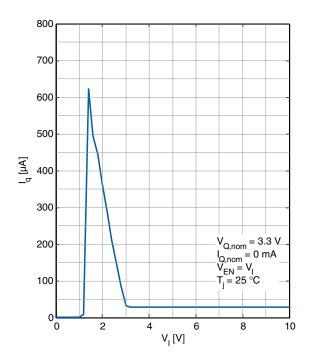

Quiescent Current  $I_q$  versus Input Voltage  $V_1$  (TLS205B0EJV33)

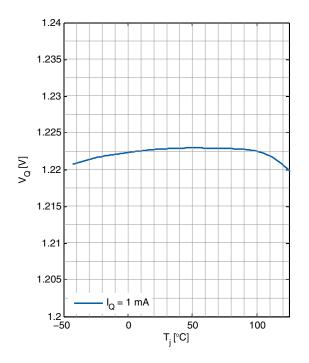

Output Voltage  $V_{\rm Q}$  versus Junction Temperature  $T_{\rm J}$  (TLS205B0EJV)

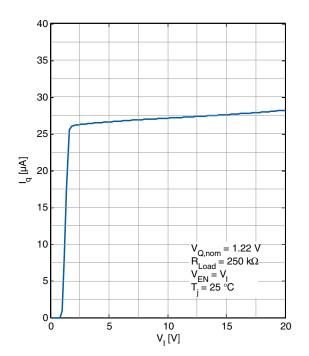

Quiescent Current  $I_{\rm q}$  versus Input Voltage  $V_{\rm I}$  (TLS205B0EJV)

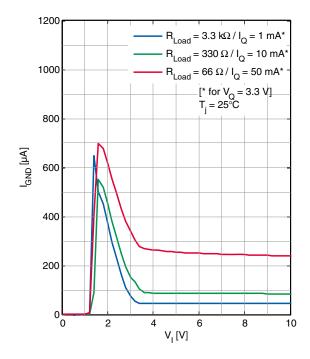

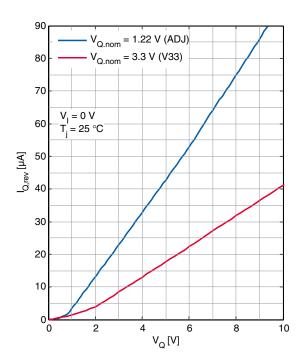

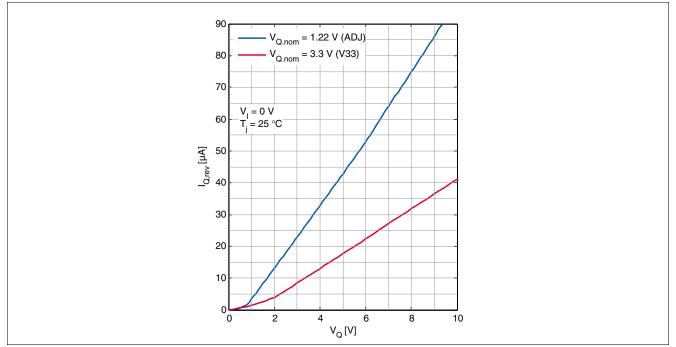

# GND Pin Current $I_{\rm GND}$ versus Input Voltage $V_{\rm I}$ (TLS205B0EJV33)

GND Pin Current  $I_{GND}$  versus Input Voltage  $V_1$  (TLS205B0EJV33)

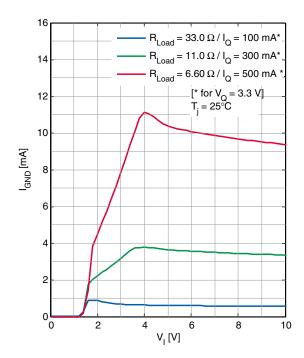

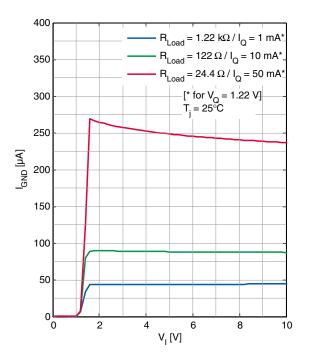

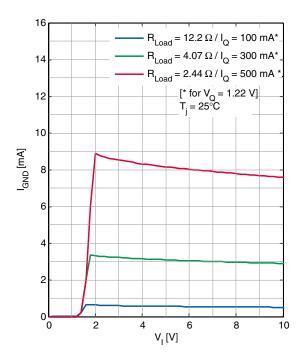

#### GND Pin Current $I_{GND}$ versus Input Voltage $V_1$ (TLS205B0EJV)

GND Pin Current  $I_{GND}$  versus Input Voltage  $V_1$  (TLS205B0EJV)

# GND Pin Current $I_{\rm GND}$ versus Output Current $I_{\rm Q}$

# EN Pin Threshold (On-to-Off) versus Junction Temperature $T_{\rm J}$

EN Pin Input Current (On-to-Off) versus EN Pin Voltage  $V_{\rm EN}$

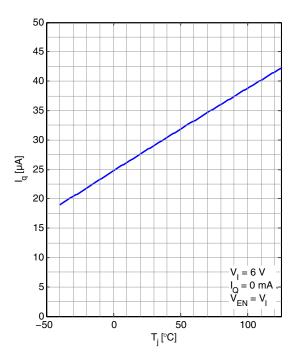

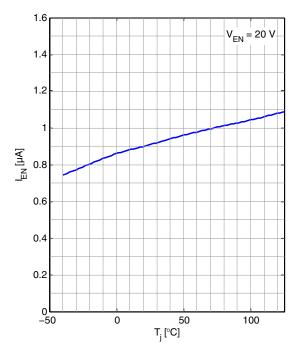

# EN Pin Current versus Junction Temperature $T_{\rm J}$

Current Limit versus Junction Temperature  $T_{J}$

Current Limit versus Input Voltage  $V_{\rm I}$

Reverse Output Current versus Output Voltage  $V_{\rm Q}$

**Reverse Output Current versus**

Junction Temperature  $T_{\rm J}$

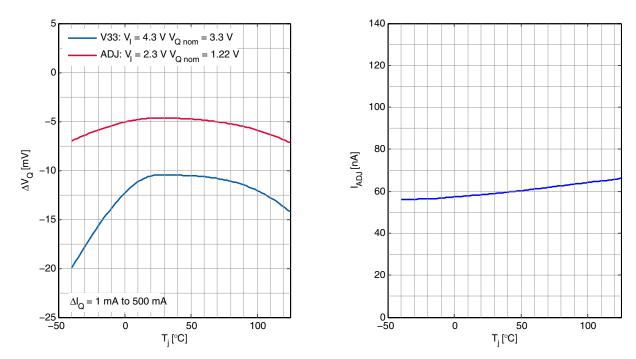

#### **Electrical Characteristics**

### 20 $V_{Q.nom} = 1.22 V (ADJ)$ 18 V<sub>Q.nom</sub> = 3.3 V (V33) 16 $V_1 = 0 V_2$ 14 12 l<sub>Q,rev</sub> [µA] 10 8 6 4 2 0 50– 0 100 50 T<sub>i</sub> [°C]

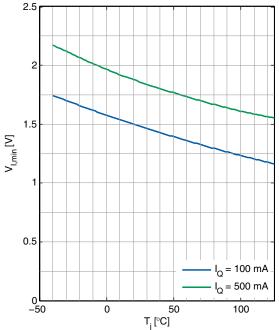

Minimum Input Voltage <sup>1)</sup> versus Junction Temperature  $T_{J}$

Adjust Pin Bias Current versus

Junction Temperature  $T_{\rm J}$

Load Regulation versus Junction Temperature  $T_{\rm J}$

1)  $V_{l,min}$  is referred here as the minimum input voltage for which the requested current is provided and  $V_{Q}$  reaches 1 V.

20

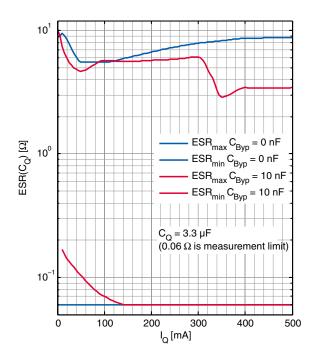

### ESR Stability versus Output Current $I_Q$ (for $C_Q$ = 3.3 µF)

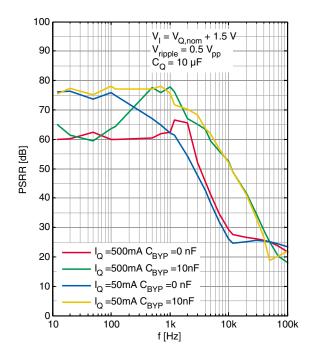

Input Ripple Rejection PSRR versus Frequency f

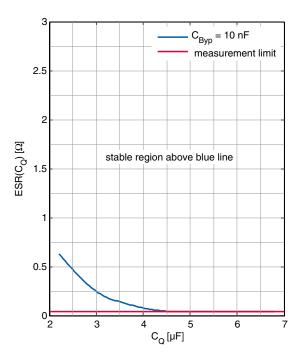

#### ESR( $C_{\rm Q}$ ) with $C_{\rm BYP}$ = 10 nF versus Output Capacitance $C_{\rm Q}$

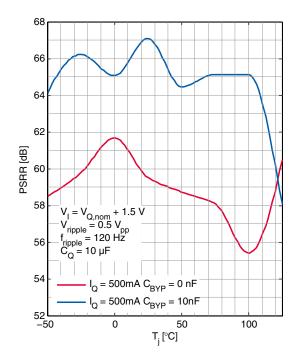

Input Ripple Rejection PSRR versus Junction Temperature  $T_{\rm J}$

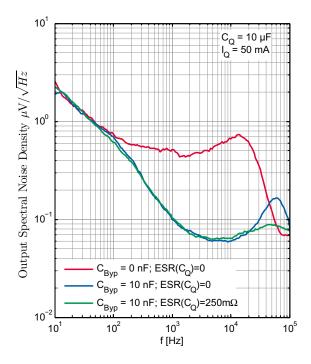

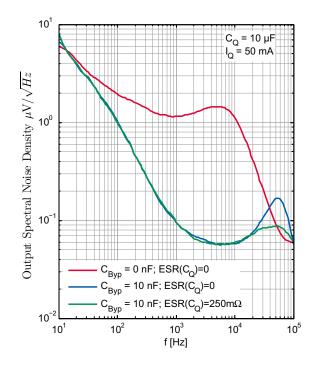

# Output Noise Spectral Density (ADJ) versus Frequency $f(C_{\rm Q}$ = 10 µF, $I_{\rm Q}$ = 50 mA)

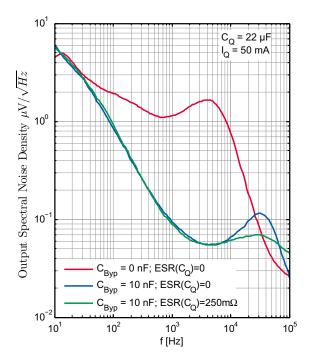

Output Noise Spectral Density (3.3V) versus Frequency  $f(C_q = 10 \ \mu\text{F}, I_q = 50 \ \text{mA})$

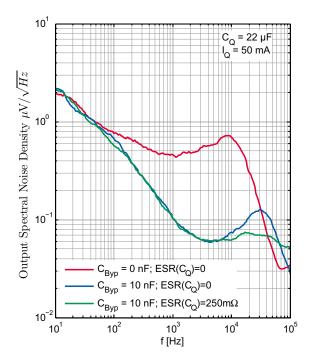

Output Noise Spectral Density (ADJ) versus Frequency  $f(C_Q = 22 \ \mu\text{F}, I_Q = 50 \text{ mA})$

Output Noise Spectral Density (3.3V) versus Frequency  $f(C_Q = 22 \ \mu\text{F}, I_Q = 50 \ \text{mA})$

100

100

#### **Electrical Characteristics**

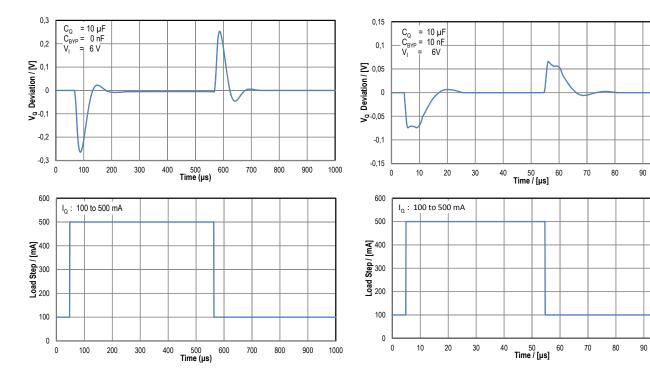

## Transient Response $C_{\text{BYP}}$ = 0 nF (TLS205B0EJV33)

Transient Response  $C_{\rm BYP}$ = 10 nF (TLS205B0EJV33)

Note: The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

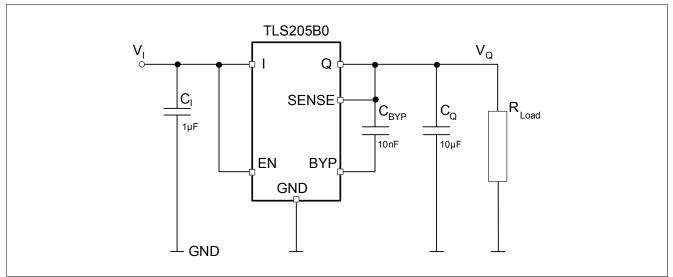

Figure 5 Typical Application Circuit TLS205B0 (fixed voltage version)

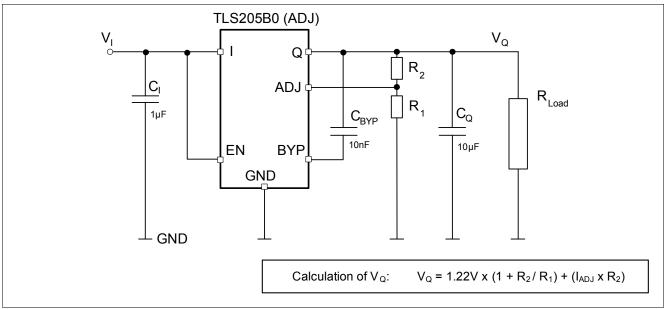

Figure 6 Typical Application Circuit TLS205B0 (adjustable version)

# Note: This is a very simplified example of an application circuit. The function must be verified in the real application. <sup>1) 2)</sup>

<sup>1)</sup> Please note that in case a non-negligible inductance at the input pin I is present, e.g. due to long cables, traces, parasitics, etc, a bigger input capacitor  $C_1$  may be required to filter its influence. As a rule of thumb if the I pin is more than six inches away from the main input filter capacitor an input capacitor value of  $C_1 = 10 \ \mu\text{F}$  is recommended.

<sup>2)</sup> For specific needs a small optional resistor may be placed in series to very low ESR output capacitors  $C_{Q}$  for enhanced noise performance (for details please see "Bypass Capacitance and Low Noise Performance" on Page 25).

The TLS205B0 is a 500 mA low dropout regulator with very low quiescent current and Enable-functionality. The device is capable of supplying 500 mA at a dropout voltage of 320 mV. Output voltage noise numbers down to 24  $\mu V_{\text{RMS}}$  can be achieved over a 10 Hz to 100 kHz bandwidth with the addition of a 10 nF reference bypass capacitor. The usage of a reference bypass capacitor will additionally improve transient response of the regulator, lowering the settling time for transient load conditions. The device has a low operating quiescent current of typical 30  $\mu$ A that drops to less than 1  $\mu$ A in shutdown (EN-pin pulled to low level). The device also incorporates several protection features which makes it ideal for battery-powered systems. It is protected against both reverse input and reverse output voltages.

## 6.1 Adjustable Operation

The adjustable version of the TLS205B0 has an output voltage range of 1.22 V to 20 V -  $V_{DR}$ . The output voltage is set by the ratio of two external resistors, as it can be seen in **Figure 6**. The device controls the output to maintain the ADJ pin at 1.22 V referenced to ground. The current in R1 is then equal 1.22 V / R1 and the current in R2 equals the current in R1 plus the ADJ pin bias current. The ADJ pin bias current, which is ~60 nA @ 25 °C, flows through R2 into the ADJ pin. The value of R1 should be not greater than 250 k $\Omega$  in order to minimize errors in the output voltage caused by the ADJ pin bias current. Note that when the device is shutdown (i.e. low level applied to EN pin) the output is turned off and consequently the divider current will be zero. For details of the ADJ Pin Bias current see also the corresponding typical performance graph "Adjust Pin Bias Current versus Junction Temperature T<sub>J</sub>" on Page 20.

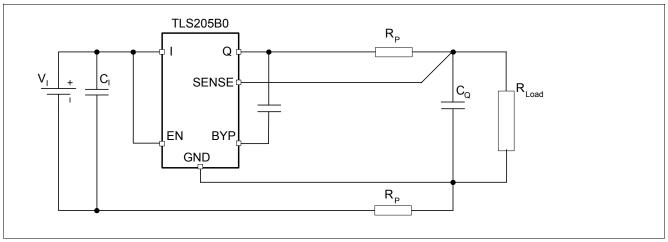

## 6.2 Kelvin Sense Connection

For the fixed voltage version of the TLS205B0 the SENSE pin is the input to the error amplifier. An optimum regulation will be obtained at the point where the SENSE pin is connected to the output pin Q of the regulator. In critical applications however small voltage drops may be caused by the resistance  $R_p$  of the PC-traces and thus may lower the resulting voltage at the load. This effect may be eliminated by connecting the SENSE pin to the output as close as possible at the load (see **Figure 7**). Please note that the voltage drop across the external PC trace will add up to the dropout voltage of the regulator.

Figure 7 Kelvin Sense Connection

## 6.3 Bypass Capacitance and Low Noise Performance

The TLS205B0 regulator may be used in combination with a bypass capacitor connecting the output pin Q to the BYP pin in order to minimize output voltage noise <sup>1</sup>). This capacitor will bypass the reference of the regulator, providing a low frequency noise pole. The noise pole provided by such a bypass capacitor will lower the output

<sup>1)</sup> a good quality low leakage capacitor is recommended.

voltage noise in the considered bandwidth. For a given output voltage actual numbers of the output voltage noise will - next to the bypass capacitor itself - be dependent on the capacitance of the applied output capacitor  $C_{Q}$  and its ESR: In case of the TLS205B0EJV / TLS205B0LDV applied with unity gain (i.e.  $V_{Q}$  = 1.22V) the usage of a bypass capacitor of 10 nF in combination with a (low ESR) ceramic  $C_{\Omega}$  of 10  $\mu$ F will result in output voltage noise numbers of typical 41  $\mu V_{\text{RMS}}$ . This Output Noise level can be reduced to typical 28  $\mu V_{\text{RMS}}$  under the same conditions by adding a small resistor of ~250 m n in series to the 10 µF ceramic output capacitor acting as additional ESR. A reduction of the output voltage noise can also be achieved by increasing capacitance of the output capacitor. For  $C_0$  = 22 µF (ceramic low ESR) the output voltage noise will be typically around 29  $\mu V_{\text{RMS}}$  and can again be further lowered to 24  $\mu V_{\text{RMS}}$  by adding a small resistance of ~250 m $\Omega$  in series to  $C_{\text{Q}}$ . In case of the fix voltage version TLS205B0EJV33 / TLS205B0LDV33 the output voltage noise for the described cases vary from 45  $\mu V_{\text{RMS}}$  down to 30  $\mu V_{\text{RMS}}$ . For further details please also see "Output Voltage Noise <sup>10</sup>)" on Page 12,, of the Electrical Characteristics. Please note that next to reducing the output voltage noise level the usage of a bypass capacitor has the additional benefit of improving transient response which will be also explained in the next chapter. However one needs to take into consideration that on the other hand the regulator start-up time is proportional to the size of the bypass capacitor and slows down to values around 15 ms when using a 10 nF bypass capacitor in combination with a 10  $\mu$ F  $C_{0}$  output capacitor.

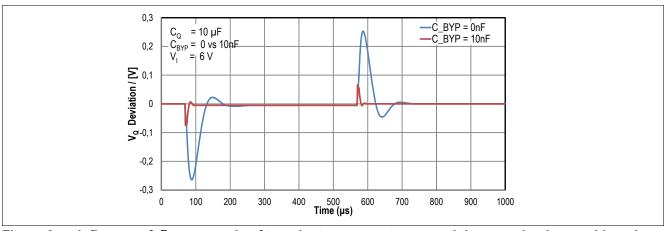

## 6.4 Output Capacitance and Transient Response

The TLS205B0 is designed to be stable with a wide range of output capacitors. The ESR of the output capacitor is an essential parameter with regard to stability, most notably with small capacitors. A minimum output capacitor of 3.3  $\mu$ F with an ESR of 3  $\Omega$  or less is recommended to prevent oscillations. Like in general for LDO's the output transient response of the TLS205B0 will be a function of the output capacitance. Larger values of output capacitance decrease peak deviations and thus improve transient response for larger load current changes. Bypass capacitors, used to decouple individual components powered by the TLS205B0 will increase the effective output capacitor value. Please note that with the usage of bypass capacitors for low noise operation either larger values of output capacitors may be needed or a minimum ESR requirement of C<sub>Q</sub> may have to be considered (see also typical performance graph "ESR( $C_Q$ ) with  $C_{BYP}$  = 10 nF versus Output Capacitance  $C_Q$ " on Page 21 as example). In conjunction with the usage of a 10 nF bypass capacitor an output capacitor  $C_{0} \ge 6.8 \,\mu\text{F}$  is recommended. The benefit of a bypass capacitor to the transient response performance is impressive and illustrated as one example in Figure 8 where the transient response of the TLS205B0EJV33 to one and the same load step from 100 mA to 500 mA is shown with and without a 10 nF bypass capacitor: for the given configuration of  $C_{\rm Q}$  = 10 µF with no bypass capacitor the load step will settle in the range of less than 100 µs while for  $C_{0}$  = 10 µF in conjunction with a 10 nF bypass capacitor the same load step will settle in the range of 10 µs. Due to the shorter reaction time of the regulator by adding the bypass capacitor not only the settling time improves but also output voltage deviations due to load steps are sharply reduced.

Figure 8 Influence of  $C_{\text{BYP}}$ : example of transient response to one and the same load step with and without  $C_{\text{BYP}}$  of 10 nF ( $I_{\text{Q}}$ : 100 mA to 500 mA, TLS205B0EJV33)

## 6.5 **Protection Features**

The TLS205B0 regulators incorporate several protection features which make them ideal for use in batterypowered circuits. In addition to normal protection features associated with monolithic regulators like current limiting and thermal limiting the device is protected against reverse input voltage, reverse output voltage and reverse voltages from output to input.

Current limit protection and thermal overload protection are intended to protect the device against current overload conditions at the output of the device. For normal operation the junction temperature must not exceed 125 °C.

The input of the device will withstand reverse voltages of 20 V. Current flowing into the device will be limited to less than 1 mA (typically less than 100  $\mu$ A) and no negative voltage will appear at the output. The device will protect both itself and the load. This provides protection against batteries being plugged backwards.

The output of the TLS205B0 can be pulled below ground without damaging the device. If the input is left opencircuit or grounded, the output can be pulled below ground by 20 V. Under such conditions the output of the device by itself behaves like an open circuit with practically no current flowing out of the pin <sup>1)</sup>. In more application relevant cases however where the output is either connected to the SENSE pin (fix voltage variant) or tied either via an external voltage divider or directly to the ADJ pin (adjustable variant) a small current will be present from this origin. In the case of the fixed voltage version this current will typically be below 100  $\mu$ A while for the adjustable version it depends on the magnitude of the top resistor of the external voltage divider <sup>2)</sup>. If the input is powered by a voltage source the output will source the short circuit current of the device and will protect itself by thermal limiting. In this case grounding the EN pin will turn off the device and stop the output from sourcing the short-circuit current.

The ADJ pin of the adjustable device can be pulled above or below ground by as much as 7 V without damaging the device. If the input is grounded or left open-circuit, the ADJ pin will act inside this voltage range like a large resistor (typically 100 k $\Omega$ ) when being pulled above ground and like a resistor (typically 5 k $\Omega$ ) in series with a diode when being pulled below ground. In situations where the ADJ pin is at risk of being pulled outside its absolute maximum ratings ±7 V the ADJ pin current must be limited to 1 mA (e.g. in cases where the ADJ pin is connected to a resistor divider that would pull the ADJ pin above its 7 V clamp voltage). Let's consider for example the case where a resistor divider is used to provide a 1.5 V output from the 1.22 V reference and the output is forced to 20 V. The top resistor of the resistor divider must then be chosen to limit the current into the ADJ pin to 1 mA or less when the ADJ pin is at 7 V. The 13 V difference between output and ADJ pin divided by the 1 mA maximum current into the ADJ pin requires a minimum resistor value of 13 k $\Omega$ .

In circuits where a backup battery is required, several different input/output conditions can occur. The output voltage may be held up while the input is either pulled to ground, pulled to some intermediate voltage or is left open-circuit. Current flow back into the output will follow the curve as shown in **Figure 9** below.

<sup>1)</sup> typically < 1  $\mu$ A for the mentioned conditions,  $V_{\rm Q}$  being pulled below ground with other pins either grounded or open.

<sup>2)</sup> In case there is no external voltage divider applied i.e. the ADJ pin is directly connected to the output Q and the output is pulled below ground by 20 V the current flowing out of the ADJ pin will be typically ~ 4 mA. Please ensure in such cases that the absolute maximum ratings of the ADJ pin are respected.

Figure 9 Reverse Output Current

**Package Outlines**

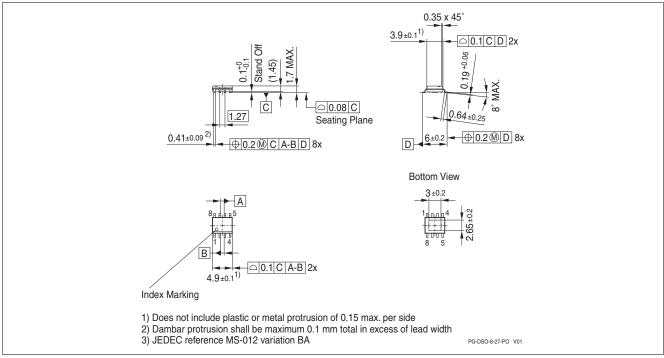

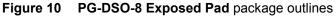

# 7 Package Outlines

#### Green Product (RoHS compliant)

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS-Compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

For further information on alternative packages, please visit our website: http://www.infineon.com/packages.

Dimensions in mm

**Revision History**

# 8 Revision History

| Revision       | Date       | Changes                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

|----------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1.2 2015-01-15 |            | <ul> <li>Data Sheet - Revision 1.2:</li> <li>PG - TSON - 10 package variants added: Product Overview, Pin Configuration, Thermal Resistance, etc - wording and description added or updated accordingly.</li> <li>Editorial changes.</li> </ul>                                                        |  |  |  |  |  |  |

| 1.1            | 2014-06-03 | <ul> <li>Data Sheet - Revision 1.1:</li> <li>Order of footnotes in Table 3 "Thermal Resistance" on Page 9 corrected.</li> <li>Application Information Chapter 6.5 updated: Clarification and correction of wording. Typical values updated and footnotes added.</li> <li>Editorial changes.</li> </ul> |  |  |  |  |  |  |

| 1.0            | 2014-02-27 | Data Sheet - Initial Release                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

Edition 2015-01-15

Published by Infineon Technologies AG 81726 Munich, Germany © 2015 Infineon Technologies AG All Rights Reserved.

#### Legal Disclaimer

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics. With respect to any examples or hints given herein, any typical values stated herein and/or any information regarding the application of the device, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation, warranties of non-infringement of intellectual property rights of any third party.

#### Information

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### Warnings

Due to technical requirements, components may contain dangerous substances. For information on the types in question, please contact the nearest Infineon Technologies Office.

Infineon Technologies components may be used in life-support devices or systems only with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов;

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001;

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный) **Факс:** 8 (812) 320-02-42 **Электронная почта:** <u>org@eplast1.ru</u> **Адрес:** 198099, г. Санкт-Петербург, ул. Калинина, дом 2, корпус 4, литера А.