#### **Features**

- 32-Mbit DataFlash and 4-Mbit SRAM

- Single 62-ball (8 mm x 12 mm x 1.2 mm) CBGA Package

- 2.7V to 3.3V Operating Voltage

#### **DataFlash**

- Single 2.7V to 3.3V Supply

- Serial Peripheral Interface (SPI) Compatible

- 20 MHz Max Clock Frequency

- Page Program Operation

- Single Cycle Reprogram (Erase and Program)

- 8192 Pages (528 Bytes/Page) Main Memory

- Supports Page and Block Erase Operations

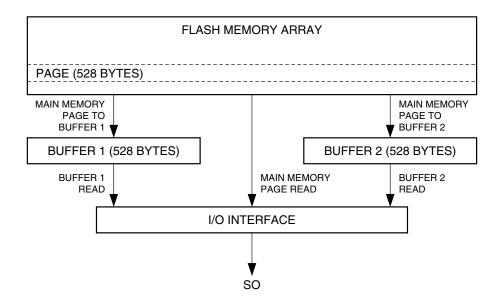

- Two 528-byte SRAM Data Buffers Allows Receiving of Data while Reprogramming of Nonvolatile Memory

- Continuous Read Capability through Entire Array

- Ideal for Code Shadowing Applications

- Low Power Dissipation

- 4 mA Active Read Current Typical

- 2 µA CMOS Standby Current Typical

- Hardware Data Protection Feature

- Industrial Temperature Range

#### **SRAM**

- 4-megabit (256K x 16)

- 2.7V to 3.3V V<sub>CC</sub>

- 70 ns Access Time

- Fully Static Operation and Tri-state Output

- 1.2V (Min) Data Retention

- Industrial Temperature Range

32-megabit

DataFlash®

+ 4-megabit

SRAM

Stack Memory

AT45BR3214B

Rev. 3356B-DFLASH-10/04

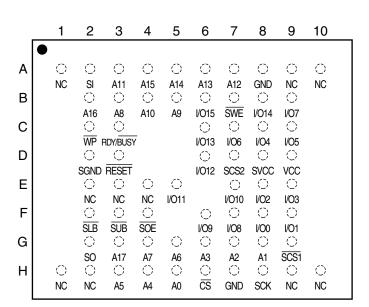

## **Pin Configuration**

| Pin Name     | Function                 |

|--------------|--------------------------|

| CS           | Chip Select              |

| SCK          | Serial Clock             |

| SI           | Serial Input             |

| SO           | Serial Output            |

| WP           | Write Protect            |

| RESET        | Reset                    |

| RDY/BUSY     | READY BUSY               |

| VCC          | Flash Power Supply       |

| GND          | Flash Ground             |

| A0 - A17     | SRAM Address Input       |

| I/O0 - I/O15 | SRAM Data Inputs/Outputs |

| SLB          | SRAM Lower Byte          |

| SUB          | SRAM Upper Byte          |

| SVCC         | SRAM Power               |

| SGND         | SRAM Ground              |

| SCS1         | SRAM Chip Select 1       |

| SCS2         | SRAM Chip Select 2       |

| SWE          | SRAM Write Enable        |

| SOE          | SRAM Output Enable       |

| NC           | No Connect               |

# AT45BR3214B (Top View)

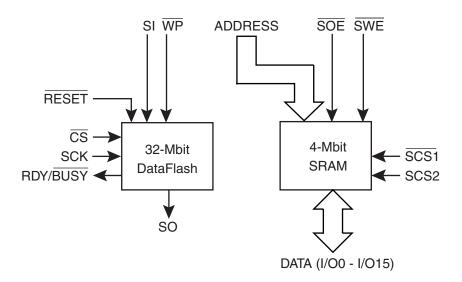

#### **Block Diagram**

#### **Description**

The AT45BR3214B combines a 32-megabit DataFlash (32M x 1) and a 4-megabit SRAM (organized as 256K x 16) in a stacked 62-ball CBGA package. The stacked module operates at 2.7V to 3.3V in the industrial temperature range.

#### **Absolute Maximum Ratings**

| Temperature under Bias40°C to +85°C    |

|----------------------------------------|

|                                        |

| Storage Temperature55°C to +150°C      |

|                                        |

| All Input Voltages (including NC Pins) |

| ,                                      |

| with Respect to Ground0.2V to +3.3V    |

|                                        |

| All Output Voltages                    |

| with Respect to Ground0.2V to +0.2V    |

|                                        |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC and AC Operating Range**

|                              |            | AT45BR3214B  |

|------------------------------|------------|--------------|

| Operating Temperature (Case) | Industrial | -40°C - 85°C |

| V <sub>CC</sub> Power Supply |            | 2.7V to 3.3V |

## 32-Mbit DataFlash Description

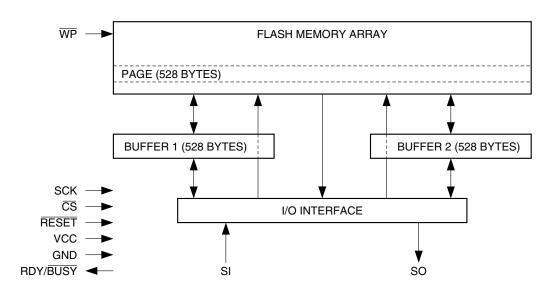

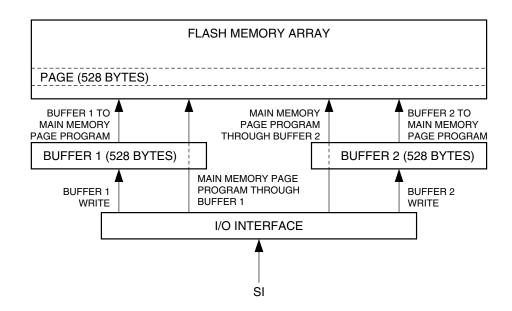

The 32-Mbit DataFlash is a 2.7-volt only, serial interface Flash memory ideally suited for a wide variety of digital voice-, image-, program code- and data-storage applications. Its 34,603,008 bits of memory are organized as 8192 pages of 528 bytes each. In addition to the main memory, the 32-Mbit DataFlash also contains two SRAM data buffers of 528 bytes each. The buffers allow receiving of data while a page in the main memory is being reprogrammed, as well as reading or writing a continuous data-stream. EEPROM emulation (bit or byte alterability) is easily handled with a self-contained three step Read-Modify-Write operation. Unlike conventional Flash memories that are accessed randomly with multiple address lines and a parallel interface, the DataFlash uses a SPI serial interface to sequentially access its data. DataFlash supports SPI mode 0 and mode 3. The simple serial interface facilitates hardware layout, increases system reliability, minimizes switching noise, and reduces package size and active pin count. The device is optimized for use in many commercial and industrial applications where high density, low pin count, low voltage, and low power are essential. The device operates at clock frequencies up to 20 MHz with a typical active read current consumption of 4 mA.

To allow for simple in-system reprogrammability, the 32-Mbit DataFlash does not require high input voltages for programming. The device operates from a single power supply, 2.7V to 3.3V, for both the program and read operations. The 32-Mbit DataFlash is enabled through the chip select pin ( $\overline{\text{CS}}$ ) and accessed via a three-wire interface consisting of the Serial Input (SI), Serial Output (SO), and the Serial Clock (SCK).

All programming cycles are self-timed, and no separate erase cycle is required before programming. When the device is shipped from Atmel, the most significant page of the memory array may not be erased. In other words, the contents of the last page may not be filled with FFH.

## DataFlash Block Diagram

#### **Memory Array**

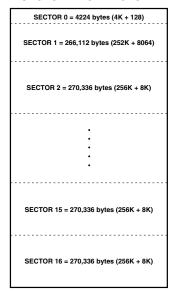

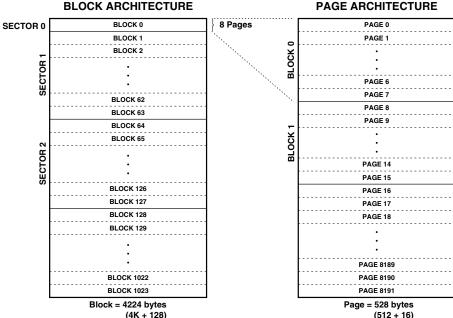

To provide optimal flexibility, the memory array of the 32-Mbit DataFlash is divided into three levels of granularity comprising of sectors, blocks, and pages. The Memory Architecture Diagram illustrates the breakdown of each level and details the number of pages per sector and block. All program operations to the DataFlash occur on a page-by-page basis; however, the optional erase operations can be performed at the block or page level.

## **Memory Architecture Diagram**

#### SECTOR ARCHITECTURE

#### **BLOCK ARCHITECTURE**

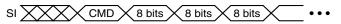

#### **Device Operation**

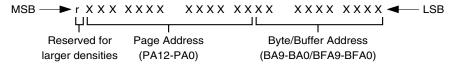

The device operation is controlled by instructions from the host processor. The list of instructions and their associated opcodes are contained in Tables 1 through 4. A valid instruction starts with the falling edge of  $\overline{CS}$  followed by the appropriate 8-bit opcode and the desired buffer or main memory address location. While the CS pin is low, toggling the SCK pin controls the loading of the opcode and the desired buffer or main memory address location through the SI (serial input) pin. All instructions, addresses and data are transferred with the most significant bit (MSB) first.

Buffer addressing is referenced in the datasheet using the terminology BFA9 - BFA0 to denote the ten address bits required to designate a byte address within a buffer. Main memory addressing is referenced using the terminology PA12 - PA0 and BA9 - BA0 where PA12 - PA0 denotes the 13 address bits required to designate a page address and BA9 - BA0 denotes the ten address bits required to designate a byte address within the page.

#### **Read Commands**

By specifying the appropriate opcode, data can be read from the main memory or from either one of the two data buffers. The DataFlash supports two categories of read modes in relation to the SCK signal. The differences between the modes are in respect to the inactive state of the SCK signal as well as which clock cycle data will begin to be output. The two categories, which are comprised of four modes total, are defined as Inactive Clock Polarity Low or Inactive Clock Polarity High and SPI Mode 0 or SPI Mode 3. A separate opcode (refer to Table 1 on page 11 for a complete list) is used to select which category will be used for reading. Please refer to the "Detailed Bit-level Read Timing" diagrams in this datasheet for details on the clock cycle sequences for each mode.

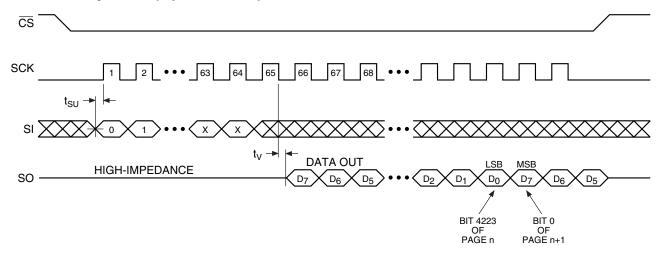

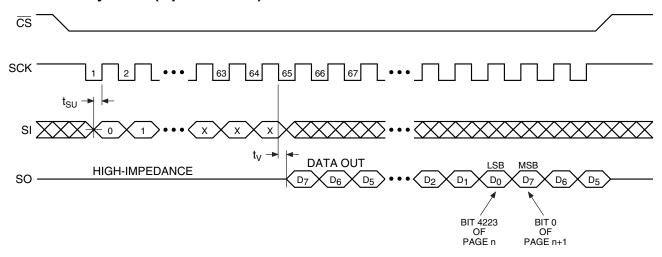

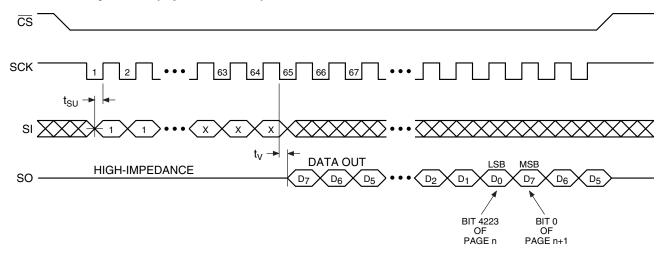

CONTINUOUS ARRAY READ: By supplying an initial starting address for the main memory array, the Continuous Array Read command can be utilized to sequentially read a continuous stream of data from the device by simply providing a clock signal; no additional addressing information or control signals need to be provided. The DataFlash incorporates an internal address counter that will automatically increment on every clock

cycle, allowing one continuous read operation without the need of additional address sequences. To perform a continuous read, an opcode of 68H or E8H must be clocked into the device followed by 24 address bits and 32 don't care bits. The first bit of the 24-bit address sequence is reserved for upward and downward compatibility to larger and smaller density devices (see Notes under "Command Sequence for Read/Write Operations" diagram). The next 13 address bits (PA12 - PA0) specify which page of the main memory array to read, and the last ten bits (BA9 - BA0) of the 24-bit address sequence specify the starting byte address within the page. The 32 don't care bits that follow the 24 address bits are needed to initialize the read operation. Following the 32 don't care bits, additional clock pulses on the SCK pin will result in serial data being output on the SO (serial output) pin.

The  $\overline{\text{CS}}$  pin must remain low during the loading of the opcode, the address bits, the don't care bits, and the reading of data. When the end of a page in main memory is reached during a Continuous Array Read, the device will continue reading at the beginning of the next page with no delays incurred during the page boundary crossover (the crossover from the end of one page to the beginning of the next page). When the last bit in the main memory array has been read, the device will continue reading back at the beginning of the first page of memory. As with crossing over page boundaries, no delays will be incurred when wrapping around from the end of the array to the beginning of the array.

A low-to-high transition on the  $\overline{\text{CS}}$  pin will terminate the read operation and tri-state the SO pin. The maximum SCK frequency allowable for the Continuous Array Read is defined by the  $f_{\text{CAR}}$  specification. The Continuous Array Read bypasses both data buffers and leaves the contents of the buffers unchanged.

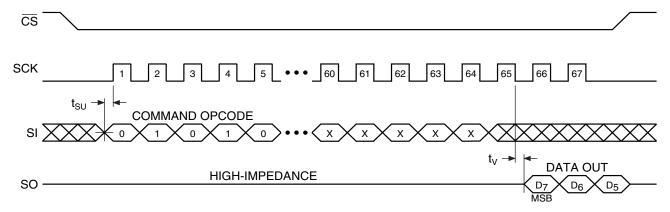

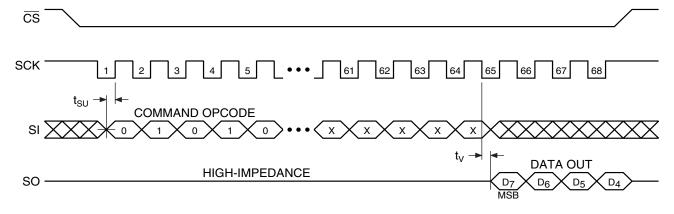

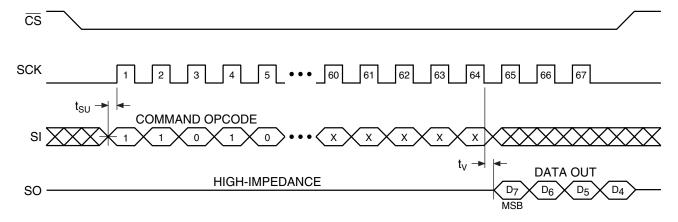

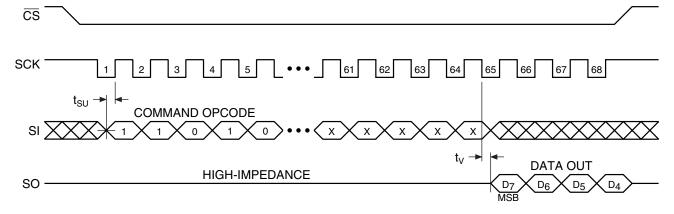

MAIN MEMORY PAGE READ: A Main Memory Page Read allows the user to read data directly from any one of the 8192 pages in the main memory, bypassing both of the data buffers and leaving the contents of the buffers unchanged. To start a page read, an opcode of 52H or D2H must be clocked into the device followed by 24 address bits and 32 don't care bits. The first bit of the 24-bit address sequence is a reserved bit, the next 13 address bits (PA12 - PA0) specify the page address, and the next ten address bits (BA9 - BA0) specify the starting byte address within the page. The 32 don't care bits which follow the 24 address bits are sent to initialize the read operation. Following the 32 don't care bits, additional pulses on SCK result in serial data being output on the SO (serial output) pin. The  $\overline{CS}$  pin must remain low during the loading of the opcode, the address bits, the don't care bits, and the reading of data. When the end of a page in main memory is reached during a Main Memory Page Read, the device will continue reading at the beginning of the same page. A low-to-high transition on the  $\overline{CS}$  pin will terminate the read operation and tri-state the SO pin.

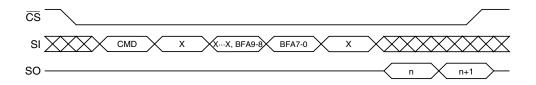

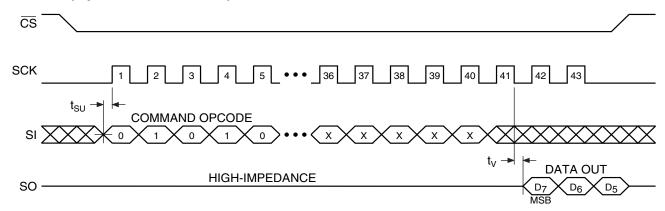

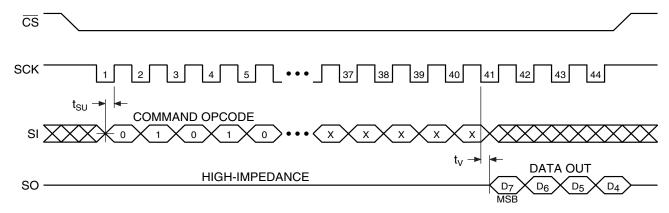

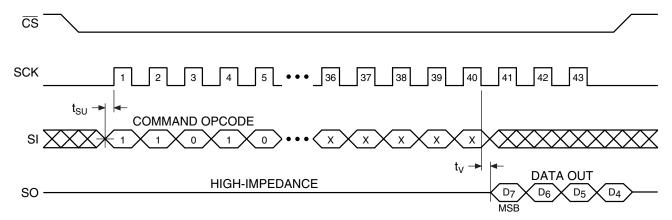

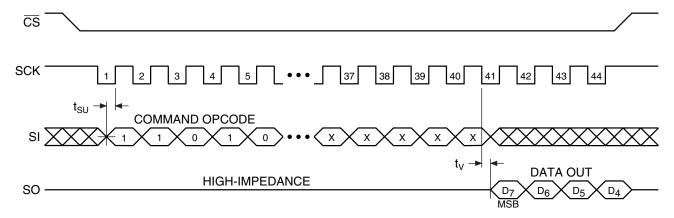

**BUFFER READ:** Data can be read from either one of the two buffers, using different opcodes to specify which buffer to read from. An opcode of 54H or D4H is used to read data from buffer 1, and an opcode of 56H or D6H is used to read data from buffer 2. To perform a Buffer Read, the eight bits of the opcode must be followed by 14 don't care bits, ten address bits, and eight don't care bits. Since the buffer size is 528 bytes, ten address bits (BFA9 - BFA0) are required to specify the first byte of data to be read from the buffer. The  $\overline{\text{CS}}$  pin must remain low during the loading of the opcode, the address bits, the don't care bits, and the reading of data. When the end of a buffer is reached, the device will continue reading back at the beginning of the buffer. A low-to-high transition on the  $\overline{\text{CS}}$  pin will terminate the read operation and tri-state the SO pin.

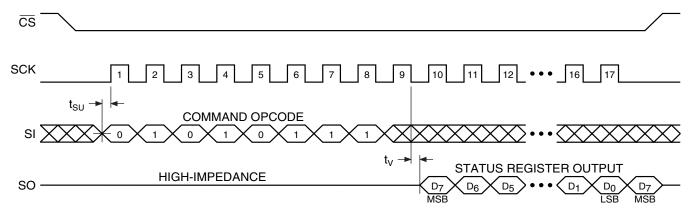

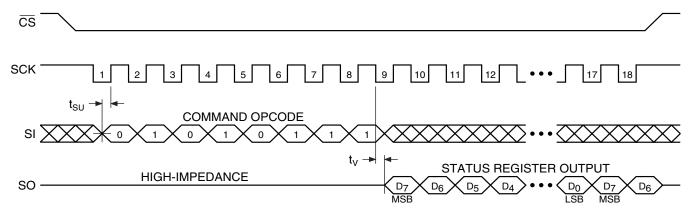

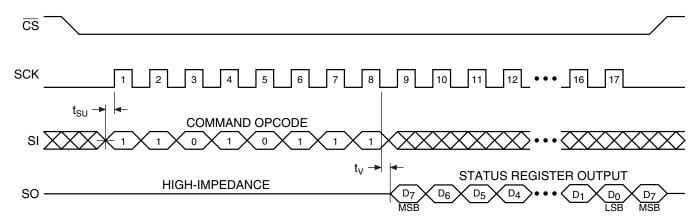

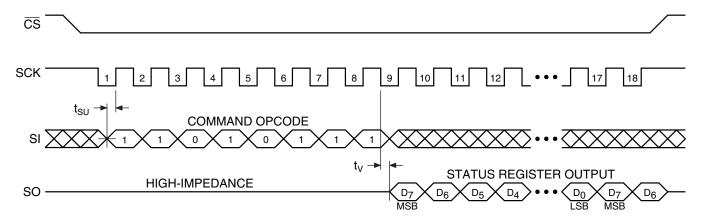

**STATUS REGISTER READ:** The status register can be used to determine the device's Ready/Busy status, the result of a Main Memory Page to Buffer Compare operation, or the device density. To read the status register, an opcode of 57H or D7H must be

loaded into the device. After the last bit of the opcode is shifted in, the eight bits of the status register, starting with the MSB (bit 7), will be shifted out on the SO pin during the next eight clock cycles. The five most significant bits of the status register will contain device information, while the remaining three least-significant bits are reserved for future use and will have undefined values. After bit 0 of the status register has been shifted out, the sequence will repeat itself (as long as  $\overline{\text{CS}}$  remains low and SCK is being toggled) starting again with bit 7. The data in the status register is constantly updated, so each repeating sequence will output new data.

#### **Status Register Format**

| Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|-------|-------|-------|-------|-------|-------|

| RDY/BUSY | COMP  | 1     | 1     | 0     | 1     | Х     | Х     |

Ready/Busy status is indicated using bit 7 of the status register. If bit 7 is a 1, then the device is not busy and is ready to accept the next command. If bit 7 is a 0, then the device is in a busy state. The user can continuously poll bit 7 of the status register by stopping SCK at a low level once bit 7 has been output. The status of bit 7 will continue to be output on the SO pin, and once the device is no longer busy, the state of SO will change from 0 to 1. There are eight operations which can cause the device to be in a busy state: Main Memory Page to Buffer Transfer, Main Memory Page to Buffer Compare, Buffer to Main Memory Page Program with Built-in Erase, Buffer to Main Memory Page Program, and Auto Page Rewrite.

The result of the most recent Main Memory Page to Buffer Compare operation is indicated using bit 6 of the status register. If bit 6 is a 0, then the data in the main memory page matches the data in the buffer. If bit 6 is a 1, then at least one bit of the data in the main memory page does not match the data in the buffer.

The device density is indicated using bits 5, 4, 3 and 2 of the status register. For the 32-Mbit DataFlash, the four bits are 1, 1, 0 and 1. The decimal value of these four binary bits does not equate to the device density; the four bits represent a combinational code relating to differing densities of Serial DataFlash devices, allowing a total of sixteen different density configurations.

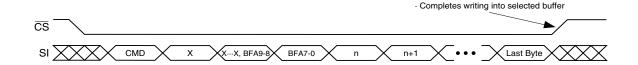

# Program and Erase Commands

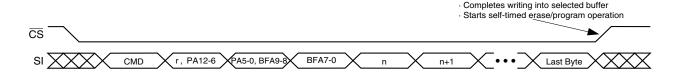

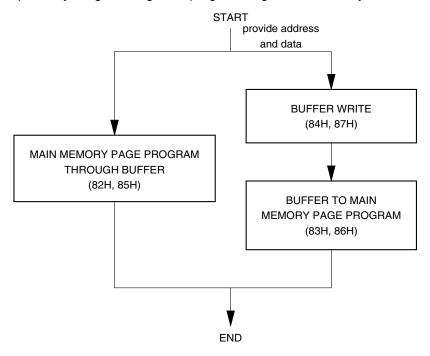

**BUFFER WRITE:** Data can be shifted in from the SI pin into either buffer 1 or buffer 2. To load data into either buffer, an 8-bit opcode, 84H for buffer 1 or 87H for buffer 2, must be followed by 14 don't care bits and ten address bits (BFA9 - BFA0). The ten address bits specify the first byte in the buffer to be written. The data is entered following the address bits. If the end of the data buffer is reached, the device will wrap around back to the beginning of the buffer. Data will continue to be loaded into the buffer until a low-to-high transition is detected on the  $\overline{\text{CS}}$  pin.

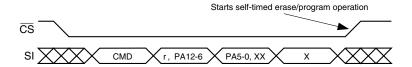

BUFFER TO MAIN MEMORY PAGE PROGRAM WITH BUILT-IN ERASE: Data written into either buffer 1 or buffer 2 can be programmed into the main memory. To start the operation, an 8-bit opcode, 83H for buffer 1 or 86H for buffer 2, must be followed by one reserved bit, 13 address bits (PA12 - PA0) that specify the page in the main memory to be written, and ten additional don't care bits. When a low-to-high transition occurs on the  $\overline{\text{CS}}$  pin, the part will first erase the selected page in main memory to all 1s and then program the data stored in the buffer into the specified page in the main memory. Both the erase and the programming of the page are internally self-timed and should take place in a maximum time of  $t_{\text{EP}}$ . During this time, the status register will indicate that the part is busy.

BUFFER TO MAIN MEMORY PAGE PROGRAM WITHOUT BUILT-IN ERASE: A previously erased page within main memory can be programmed with the contents of either buffer 1 or buffer 2. To start the operation, an 8-bit opcode, 88H for buffer 1 or 89H for buffer 2, must be followed by the one reserved bit, 13 address bits (PA12 - PA0) that specify the page in the main memory to be written, and ten additional don't care bits. When a low-to-high transition occurs on the  $\overline{CS}$  pin, the part will program the data stored in the buffer into the specified page in the main memory. It is necessary that the page in main memory that is being programmed has been previously erased. The programming of the page is internally self-timed and should take place in a maximum time of  $t_P$ . During this time, the status register will indicate that the part is busy.

Successive page programming operations without doing a page erase are not recommended. In other words, changing bytes within a page from a "1" to a "0" during multiple page programming operations without erasing that page is not recommended.

**PAGE ERASE:** The optional Page Erase command can be used to individually erase any page in the main memory array allowing the Buffer to Main Memory Page Program without Built-in Erase command to be utilized at a later time. To perform a Page Erase, an opcode of 81H must be loaded into the device, followed by one reserved bit, 13 address bits (PA12 - PA0), and ten don't care bits. The 13 address bits are used to specify which page of the memory array is to be erased. When a low-to-high transition occurs on the  $\overline{\text{CS}}$  pin, the part will erase the selected page to 1s. The erase operation is internally self-timed and should take place in a maximum time of  $t_{\text{PE}}$ . During this time, the status register will indicate that the part is busy.

**BLOCK ERASE:** A block of eight pages can be erased at one time allowing the Buffer to Main Memory Page Program without Built-in Erase command to be utilized to reduce programming times when writing large amounts of data to the device. To perform a Block Erase, an opcode of 50H must be loaded into the device, followed by one reserved bit, ten address bits (PA12 - PA3), and 13 don't care bits. The ten address bits are used to specify which block of eight pages is to be erased. When a low-to-high transition occurs on the  $\overline{\text{CS}}$  pin, the part will erase the selected block of eight pages to 1s. The erase operation is internally self-timed and should take place in a maximum time of  $t_{\text{BE}}$ . During this time, the status register will indicate that the part is busy.

## **Block Erase Addressing**

| PA12 | PA11 | PA10 | PA9 | PA8 | PA7 | PA6 | PA5 | PA4 | PA3 | PA2 | PA1 | PA0 | Block |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|

| 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | Χ   | Χ   | Χ   | 0     |

| 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 1   | Χ   | Χ   | Χ   | 1     |

| 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 0   | Χ   | Χ   | Χ   | 2     |

| 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 1   | 1   | Χ   | Χ   | Χ   | 3     |

| •    | •    | •    | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •     |

| •    | •    | •    | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •     |

| •    | •    | •    | •   | •   | •   | •   | •   | •   | •   | •   | •   | •   | •     |

| 1    | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 0   | 0   | Χ   | Χ   | Χ   | 1020  |

| 1    | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 0   | 1   | Χ   | Χ   | Χ   | 1021  |

| 1    | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 0   | Χ   | Χ   | Χ   | 1022  |

| 1    | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   | Χ   | Χ   | Χ   | 1023  |

**MAIN MEMORY PAGE PROGRAM THROUGH BUFFER:** This operation is a combination of the Buffer Write and Buffer to Main Memory Page Program with Built-in Erase operations. Data is first shifted into buffer 1 or buffer 2 from the SI pin and then programmed into a specified page in the main memory. To initiate the operation, an 8-bit opcode, 82H for buffer 1 or 85H for buffer 2, must be followed by one reserved bit and 23 address bits. The 13 most significant address bits (PA12 - PA0) select the page in the main memory where data is to be written, and the next ten address bits (BFA9 - BFA0) select the first byte in the buffer to be written. After all address bits are shifted in, the part will take data from the SI pin and store it in one of the data buffers. If the end of the buffer is reached, the device will wrap around back to the beginning of the buffer. When there is a low-to-high transition on the  $\overline{\text{CS}}$  pin, the part will first erase the selected page in main memory to all 1s and then program the data stored in the buffer into the specified page in the main memory. Both the erase and the programming of the page are internally self-timed and should take place in a maximum of time  $t_{\text{EP}}$ . During this time, the status register will indicate that the part is busy.

#### **Additional Commands**

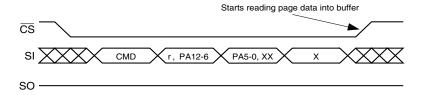

**MAIN MEMORY PAGE TO BUFFER TRANSFER:** A page of data can be transferred from the main memory to either buffer 1 or buffer 2. To start the operation, an 8-bit opcode, 53H for buffer 1 and 55H for buffer 2, must be followed by one reserved bit, 13 address bits (PA12 - PA0) which specify the page in main memory that is to be transferred, and ten don't care bits. The  $\overline{CS}$  pin must be low while toggling the SCK pin to load the opcode, the address bits, and the don't care bits from the SI pin. The transfer of the page of data from the main memory to the buffer will begin when the  $\overline{CS}$  pin transitions from a low to a high state. During the transfer of a page of data ( $t_{XFR}$ ), the status register can be read to determine whether the transfer has been completed or not.

**MAIN MEMORY PAGE TO BUFFER COMPARE:** A page of data in main memory can be compared to the data in buffer 1 or buffer 2. To initiate the operation, an 8-bit opcode, 60H for buffer 1 and 61H for buffer 2, must be followed by 24 address bits consisting of one reserved bit, 13 address bits (PA12 - PA0) which specify the page in the main memory that is to be compared to the buffer, and ten don't care bits. The  $\overline{CS}$  pin must be low while toggling the SCK pin to load the opcode, the address bits, and the don't care bits from the SI pin. On the low-to-high transition of the  $\overline{CS}$  pin, the 528 bytes in the selected main memory page will be compared with the 528 bytes in buffer 1 or buffer 2. During this time ( $t_{XFR}$ ), the status register will indicate that the part is busy. On completion of the compare operation, bit 6 of the status register is updated with the result of the compare.

**AUTO PAGE REWRITE:** This mode is only needed if multiple bytes within a page or multiple pages of data are modified in a random fashion. This mode is a combination of two operations: Main Memory Page to Buffer Transfer and Buffer to Main Memory Page Program with Built-in Erase. A page of data is first transferred from the main memory to buffer 1 or buffer 2, and then the same data (from buffer 1 or buffer 2) is programmed back into its original page of main memory. To start the rewrite operation, an 8-bit opcode, 58H for buffer 1 or 59H for buffer 2, must be followed by one reserved bit, 13 address bits (PA12 - PA0) that specify the page in main memory to be rewritten, and ten additional don't care bits. When a low-to-high transition occurs on the  $\overline{\text{CS}}$  pin, the part will first transfer data from the page in main memory to a buffer and then program the data from the buffer back into same page of main memory. The operation is internally self-timed and should take place in a maximum time of  $t_{\text{EP}}$ . During this time, the status register will indicate that the part is busy.

If a sector is programmed or reprogrammed sequentially page-by-page, then the programming algorithm shown in Figure 1 on page 28 is recommended. Otherwise, if multiple bytes in a page or several pages are programmed randomly in a sector, then the programming algorithm shown in Figure 2 on page 29 is recommended. Each page within a sector must be updated/rewritten at least once within every 10,000 cumulative page erase/program operations in that sector.

# Operation Mode Summary

The modes described can be separated into two groups – modes which make use of the Flash memory array (Group A) and modes which do not make use of the Flash memory array (Group B).

Group A modes consist of:

- 1. Main Memory Page Read

- 2. Main Memory Page to Buffer 1 (or 2) Transfer

- 3. Main Memory Page to Buffer 1 (or 2) Compare

- 4. Buffer 1 (or 2) to Main Memory Page Program with Built-in Erase

- 5. Buffer 1 (or 2) to Main Memory Page Program without Built-in Erase

- 6. Page Erase

- 7. Block Erase

- 8. Main Memory Page Program through Buffer

- 9. Auto Page Rewrite

Group B modes consist of:

- 1. Buffer 1 (or 2) Read

- 2. Buffer 1 (or 2) Write

- 3. Status Register Read

If a Group A mode is in progress (not fully completed) then another mode in Group A should not be started. However, during this time in which a Group A mode is in progress, modes in Group B can be started.

This gives the Serial DataFlash the ability to virtually accommodate a continuous datastream. While data is being programmed into main memory from buffer 1, data can be loaded into buffer 2 (or vice versa). See application note AN-4 ("Using Atmel's Serial DataFlash") for more details.

#### **Pin Descriptions**

**SERIAL INPUT (SI):** The SI pin is an input-only pin and is used to shift data into the device. The SI pin is used for all data input including opcodes and address sequences.

**SERIAL OUTPUT (SO):** The SO pin is an output-only pin and is used to shift data out from the device.

**SERIAL CLOCK (SCK):** The SCK pin is an input-only pin and is used to control the flow of data to and from the DataFlash. Data is always clocked into the device on the rising edge of SCK and clocked out of the device on the falling edge of SCK.

**CHIP SELECT (\overline{\text{CS}}):** The DataFlash is selected when the  $\overline{\text{CS}}$  pin is low. When the device is not selected, data will not be accepted on the SI pin, and the SO pin will remain in a high-impedance state. A high-to-low transition on the  $\overline{\text{CS}}$  pin is required to start an operation, and a low-to-high transition on the  $\overline{\text{CS}}$  pin is required to end an operation.

**WRITE PROTECT:** If the  $\overline{WP}$  pin is held low, the first 256 pages of the main memory cannot be reprogrammed. The only way to reprogram the first 256 pages is to first drive the protect pin high and then use the program commands previously mentioned. If this pin and feature are not utilized it is recommended that the  $\overline{WP}$  pin be driven high externally.

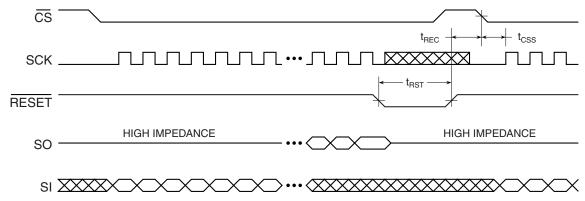

**RESET:** A low state on the reset pin (RESET) will terminate the operation in progress and reset the internal state machine to an idle state. The device will remain in the reset condition as long as a low level is present on the RESET pin. Normal operation can resume once the RESET pin is brought back to a high level.

The device incorporates an internal power-on reset circuit, so there are no restrictions on the RESET pin during power-on sequences. If this pin and feature are not utilized it is recommended that the RESET pin be driven high externally.

**READY/BUSY:** This open drain output pin will be driven low when the device is busy in an internally self-timed operation. This pin, which is normally in a high state (through a 1 k $\Omega$  external pull-up resistor), will be pulled low during programming operations, compare operations, and during page-to-buffer transfers.

The busy status indicates that the Flash memory array and one of the buffers cannot be accessed; read and write operations to the other buffer can still be performed.

#### **Power-on/Reset State**

When power is first applied to the device, or when recovering from a reset condition, the device will default to SPI Mode 3. In addition, the SO pin will be in a high-impedance state, and a high-to-low transition on the  $\overline{CS}$  pin will be required to start a valid instruction. The SPI mode will be automatically selected on every falling edge of  $\overline{CS}$  by sampling the inactive clock state. After power is applied and Vcc is at the minimum datasheet value, the system should wait 20 ms before an operational mode is started.

Table 1. Read Commands

| Command               | SCK Mode                            | Opcode |

|-----------------------|-------------------------------------|--------|

| Continuous Arroy Dood | Inactive Clock Polarity Low or High | 68H    |

| Continuous Array Read | SPI Mode 0 or 3                     | E8H    |

| Main Managar Paga     | Inactive Clock Polarity Low or High | 52H    |

| Main Memory Page Read | SPI Mode 0 or 3                     | D2H    |

| Duffer 1 Deed         | Inactive Clock Polarity Low or High | 54H    |

| Buffer 1 Read         | SPI Mode 0 or 3                     | D4H    |

| Duffer O Deed         | Inactive Clock Polarity Low or High | 56H    |

| Buffer 2 Read         | SPI Mode 0 or 3                     | D6H    |

| Ctatus Basistar Basel | Inactive Clock Polarity Low or High | 57H    |

| Status Register Read  | SPI Mode 0 or 3                     | D7H    |

Table 2. Program and Erase Commands

| Command                                                     | SCK Mode | Opcode |

|-------------------------------------------------------------|----------|--------|

| Buffer 1 Write                                              | Any      | 84H    |

| Buffer 2 Write                                              | Any      | 87H    |

| Buffer 1 to Main Memory Page Program with Built-in Erase    | Any      | 83H    |

| Buffer 2 to Main Memory Page Program with Built-in Erase    | Any      | 86H    |

| Buffer 1 to Main Memory Page Program without Built-in Erase | Any      | 88H    |

| Buffer 2 to Main Memory Page Program without Built-in Erase | Any      | 89H    |

| Page Erase                                                  | Any      | 81H    |

| Block Erase                                                 | Any      | 50H    |

| Main Memory Page Program through Buffer 1                   | Any      | 82H    |

| Main Memory Page Program through Buffer 2                   | Any      | 85H    |

Table 3. Additional Commands

| Command                               | SCK Mode | Opcode |

|---------------------------------------|----------|--------|

| Main Memory Page to Buffer 1 Transfer | Any      | 53H    |

| Main Memory Page to Buffer 2 Transfer | Any      | 55H    |

| Main Memory Page to Buffer 1 Compare  | Any      | 60H    |

| Main Memory Page to Buffer 2 Compare  | Any      | 61H    |

| Auto Page Rewrite through Buffer 1    | Any      | 58H    |

| Auto Page Rewrite through Buffer 2    | Any      | 59H    |

Note: In Tables 2 and 3, an SCK mode designation of "Any" denotes any one of the four modes of operation (Inactive Clock Polarity Low, Inactive Clock Polarity High, SPI Mode 0, or SPI Mode 3).

Table 4. Detailed Bit-level Addressing Sequence

|        | Address Byte    |          |      |      |      |     |     |     | Ad  | ddre | ss B | yte |     |     |     |     | Ac  | ldre | ss B | yte |     |     |     |     |     |                                               |

|--------|-----------------|----------|------|------|------|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|------|------|-----|-----|-----|-----|-----|-----|-----------------------------------------------|

| Opcode | Opcode          | Reserved | PA12 | PA11 | PA10 | PA9 | PA8 | PA7 | PA6 | PA5  | PA4  | PA3 | PA2 | PA1 | PA0 | BA9 | BA8 | BA7  | BA6  | BA5 | BA4 | BA3 | BA2 | BA1 | BA0 | Additional<br>Don't Care<br>Bytes<br>Required |

| 50H    | 0 1 0 1 0 0 0 0 | r        | Р    | Р    | Р    | Р   | P   | Р   | Р   | Р    | Р    | Р   | Х   | Х   | Х   | Х   | Х   | х    | Х    | х   | Х   | Х   | Х   | Х   | х   | N/A                                           |

| 52H    | 0 1 0 1 0 0 1 0 | r        | P    | P    | Р    | P   | P   | P   | Р   | P    | P    | P   | P   | P   | P   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 4 Bytes                                       |

| 53H    | 0 1 0 1 0 0 1 1 | r        | P    | P    | Р    | P   | P   | P   | Р   | P    | P    | P   | P   | P   | P   | Х   | Х   | х    | Х    | x   | Х   | Х   | Х   | Х   | х   | N/A                                           |

| 54H    | 0 1 0 1 0 1 0 0 | х        | Х    | Х    | х    | Х   | X   | Х   | х   | х    | Х    | Х   | Х   | Х   | Х   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 1 Byte                                        |

| 55H    | 0 1 0 1 0 1 0 1 | r        | P    | Р    | Р    | Р   | Р   | Р   | Р   | Р    | Р    | Р   | Р   | P   | Р   | х   | х   | х    | Х    | x   | Х   | Х   | Х   | Х   | x   | N/A                                           |

| 56H    | 0 1 0 1 0 1 1 0 | х        | Х    | Х    | х    | Х   | X   | Х   | х   | х    | Х    | Х   | Х   | Х   | Х   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 1 Byte                                        |

| 57H    | 0 1 0 1 0 1 1 1 |          |      |      | Ν    | I/A |     |     |     |      |      |     | ١   | N/A |     |     |     |      |      |     | ١   | N/A |     |     |     | N/A                                           |

| 58H    | 0 1 0 1 1 0 0 0 | r        | P    | P    | Р    | P   | P   | P   | Р   | P    | P    | P   | P   | P   | P   | Х   | Х   | х    | Х    | x   | Х   | Х   | Х   | Х   | х   | N/A                                           |

| 59H    | 0 1 0 1 1 0 0 1 | r        | Р    | Р    | Р    | Р   | Р   | Р   | Р   | Р    | Р    | Р   | Р   | P   | Р   | х   | х   | х    | Х    | x   | Х   | Х   | Х   | Х   | x   | N/A                                           |

| 60H    | 0 1 1 0 0 0 0 0 | r        | P    | P    | P    | P   | P   | P   | P   | Р    | P    | P   | P   | P   | Р   | х   | х   | х    | Х    | x   | Х   | Х   | Х   | Х   | х   | N/A                                           |

| 61H    | 0 1 1 0 0 0 0 1 | r        | Р    | P    | Р    | P   | Р   | P   | Р   | Р    | P    | P   | Р   | Р   | Р   | x   | x   | х    | Х    | х   | X   | х   | х   | Х   | х   | N/A                                           |

| 68H    | 0 1 1 0 1 0 0 0 | r        | P    | P    | P    | P   | P   | P   | P   | Р    | P    | P   | P   | P   | Р   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 4 Bytes                                       |

| 81H    | 1 0 0 0 0 0 0 1 | r        | P    | P    | P    | P   | P   | P   | P   | Р    | P    | P   | P   | P   | Р   | х   | х   | х    | Х    | x   | Х   | Х   | Х   | Х   | х   | N/A                                           |

| 82H    | 1 0 0 0 0 0 1 0 | r        | Р    | P    | Р    | P   | Р   | P   | Р   | Р    | P    | P   | Р   | Р   | Р   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | N/A                                           |

| 83H    | 1 0 0 0 0 0 1 1 | r        | P    | P    | P    | P   | P   | P   | P   | Р    | P    | P   | P   | P   | Р   | х   | х   | х    | Х    | x   | Х   | Х   | Х   | Х   | х   | N/A                                           |

| 84H    | 1 0 0 0 0 1 0 0 | х        | Х    | Х    | х    | х   | Х   | Х   | х   | х    | х    | Х   | Х   | Х   | Х   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | N/A                                           |

| 85H    | 1 0 0 0 0 1 0 1 | r        | Р    | Р    | Р    | P   | P   | P   | Р   | Р    | P    | P   | Р   | Р   | Р   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | N/A                                           |

| 86H    | 1 0 0 0 0 1 1 0 | r        | Р    | Р    | Р    | Р   | Р   | P   | Р   | Р    | Р    | P   | Р   | Р   | Р   | х   | x   | х    | Х    | х   | Х   | х   | х   | Х   | х   | N/A                                           |

| 87H    | 1 0 0 0 0 1 1 1 | х        | Х    | Х    | х    | х   | Х   | х   | х   | х    | х    | х   | Х   | Х   | Х   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | N/A                                           |

| 88H    | 1 0 0 0 1 0 0 0 | r        | Р    | Р    | Р    | Р   | Р   | Р   | Р   | Р    | Р    | Р   | Р   | Р   | Р   | х   | х   | х    | Х    | х   | Х   | х   | х   | Х   | х   | N/A                                           |

| 89H    | 1 0 0 0 1 0 0 1 | r        | Р    | Р    | Р    | Р   | Р   | Р   | Р   | Р    | Р    | Р   | Р   | Р   | Р   | Х   | Х   | х    | х    | х   | х   | х   | х   | х   | х   | N/A                                           |

| D2H    | 1 1 0 1 0 0 1 0 | r        | Р    | Р    | P    | Р   | Р   | Р   | Р   | Р    | Р    | Р   | Р   | Р   | Р   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 4 Bytes                                       |

| D4H    | 1 1 0 1 0 1 0 0 | х        | Х    | х    | х    | х   | Х   | х   | х   | х    | х    | х   | Х   | Х   | Х   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 1 Byte                                        |

| D6H    | 1 1 0 1 0 1 1 0 | х        | Х    | х    | х    | х   | х   | х   | х   | х    | х    | х   | Х   | Х   | х   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 1 Byte                                        |

| D7H    | 1 1 0 1 0 1 1 1 |          |      |      | Ν    | I/A |     |     |     |      |      |     | ١   | N/A |     |     |     |      |      |     | ١   | N/A |     |     |     | N/A                                           |

| E8H    | 1 1 1 0 1 0 0 0 | r        | Р    | Р    | Р    | Р   | Р   | Р   | Р   | Р    | Р    | Р   | Р   | Р   | Р   | В   | В   | В    | В    | В   | В   | В   | В   | В   | В   | 4 Bytes                                       |

Note: r = Reserved Bit

P = Page Address Bit

B = Byte/Buffer Address Bit

x = Don't Care

## **Absolute Maximum Ratings\***

| Temperature under Bias55°C to +125°C                                        |

|-----------------------------------------------------------------------------|

| Storage Temperature65°C to +150°C                                           |

| All Input Voltages (including NC Pins) with Respect to Ground0.6V to +6.25V |

| All Output Voltages with Respect to Ground0.6V to V <sub>CC</sub> + 0.6V    |

\*NOTICE:

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **DC and AC Operating Range**

|                                             |      | 32-Mbit DataFlash |

|---------------------------------------------|------|-------------------|

| Operating Temperature (Coop)                | Com. | 0°C to 70°C       |

| Operating Temperature (Case)                | Ind. | -40°C to 85°C     |

| V <sub>CC</sub> Power Supply <sup>(1)</sup> |      | 2.7V to 3.3V      |

Note: 1. After power is applied and V<sub>CC</sub> is at the minimum specified datasheet value, the system should wait 20 ms before an operational mode is started.

#### **DC Characteristics**

| Symbol                          | Parameter                                  | Condition                                                                                                                      | Min                    | Тур | Max | Units |

|---------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-----|-------|

| I <sub>SB</sub>                 | Standby Current                            | $\overline{\text{CS}}$ , $\overline{\text{RESET}}$ , $\overline{\text{WP}} = \text{V}_{\text{CC}}$ , all inputs at CMOS levels |                        | 2   | 10  | μA    |

| I <sub>CC1</sub> <sup>(1)</sup> | Active Current, Read<br>Operation          | $ f = 20 \text{ MHz; } I_{\text{OUT}} = 0 \text{ mA; } $ $V_{\text{CC}} = 3.3 \text{V} $                                       |                        | 4   | 10  | mA    |

| I <sub>CC2</sub>                | Active Current,<br>Program/Erase Operation | V <sub>CC</sub> = 3.3V                                                                                                         |                        | 15  | 35  | mA    |

| I <sub>LI</sub>                 | Input Load Current                         | V <sub>IN</sub> = CMOS levels                                                                                                  |                        |     | 1   | μA    |

| I <sub>LO</sub>                 | Output Leakage Current                     | V <sub>I/O</sub> = CMOS levels                                                                                                 |                        |     | 1   | μA    |

| V <sub>IL</sub>                 | Input Low Voltage                          |                                                                                                                                |                        |     | 0.6 | V     |

| V <sub>IH</sub>                 | Input High Voltage                         |                                                                                                                                | 2.0                    |     |     | V     |

| V <sub>OL</sub>                 | Output Low Voltage                         | I <sub>OL</sub> = 1.6 mA; V <sub>CC</sub> = 2.7V                                                                               |                        |     | 0.4 | V     |

| V <sub>OH</sub>                 | Output High Voltage                        | I <sub>OH</sub> = -100 μA                                                                                                      | V <sub>CC</sub> - 0.2V |     |     | V     |

Note: 1.  $I_{cc1}$  during a buffer read is 20mA maximum.

## **AC Characteristics**

|                  |                                         | 32-Mbit [ | DataFlash |       |

|------------------|-----------------------------------------|-----------|-----------|-------|

| Symbol           | Parameter                               | Min       | Max       | Units |

| f <sub>SCK</sub> | SCK Frequency                           |           | 20        | MHz   |

| f <sub>CAR</sub> | SCK Frequency for Continuous Array Read |           | 20        | MHz   |

| t <sub>WH</sub>  | SCK High Time                           | 22        |           | ns    |

| t <sub>WL</sub>  | SCK Low Time                            | 22        |           | ns    |

| t <sub>CS</sub>  | Minimum CS High Time                    | 250       |           | ns    |

| t <sub>CSS</sub> | CS Setup Time                           | 250       |           | ns    |

| t <sub>CSH</sub> | CS Hold Time                            | 250       |           | ns    |

| t <sub>CSB</sub> | CS High to RDY/BUSY Low                 |           | 200       | ns    |

| t <sub>SU</sub>  | Data In Setup Time                      | 5         |           | ns    |

| t <sub>H</sub>   | Data In Hold Time                       | 10        |           | ns    |

| t <sub>HO</sub>  | Output Hold Time                        | 0         |           | ns    |

| t <sub>DIS</sub> | Output Disable Time                     |           | 18        | ns    |

| t <sub>V</sub>   | Output Valid                            |           | 20        | ns    |

| t <sub>XFR</sub> | Page to Buffer Transfer/Compare Time    |           | 250       | μs    |

| t <sub>EP</sub>  | Page Erase and Programming Time         |           | 20        | ms    |

| t <sub>P</sub>   | Page Programming Time                   |           | 14        | ms    |

| t <sub>PE</sub>  | Page Erase Time                         |           | 8         | ms    |

| t <sub>BE</sub>  | Block Erase Time                        |           | 12        | ms    |

| t <sub>RST</sub> | RESET Pulse Width                       | 10        |           | μs    |

| t <sub>REC</sub> | RESET Recovery Time                     |           | 1         | μs    |

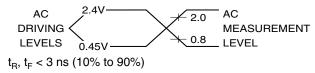

#### **Input Test Waveforms and Measurement Levels**

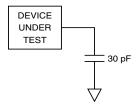

#### **Output Test Load**

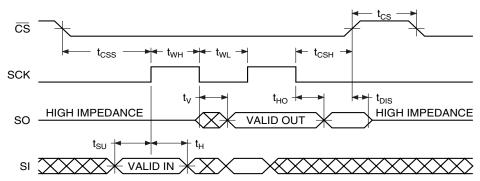

#### **AC Waveforms**

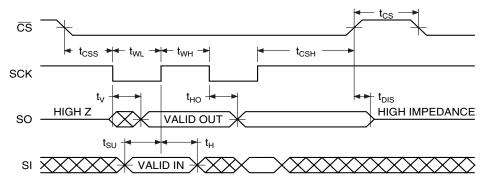

Two different timing diagrams are shown below. Waveform 1 shows the SCK signal being low when  $\overline{\text{CS}}$  makes a high-to-low transition, and Waveform 2 shows the SCK signal being high when  $\overline{\text{CS}}$  makes a high-to-low transition. Both waveforms show valid timing diagrams. The setup and hold times for the SI signal are referenced to the low-to-high transition on the SCK signal.

Waveform 1 shows timing that is also compatible with SPI Mode 0, and Waveform 2 shows timing that is compatible with SPI Mode 3.

#### Waveform 1 – Inactive Clock Polarity Low and SPI Mode 0

#### Waveform 2 – Inactive Clock Polarity High and SPI Mode 3

#### **Reset Timing (Inactive Clock Polarity Low Shown)**

Note: The  $\overline{CS}$  signal should be in the high state before the  $\overline{RESET}$  signal is deasserted.

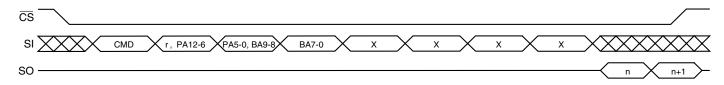

#### Command Sequence for Read/Write Operations (except Status Register Read)

Notes: 1. "r" designates bits reserved for larger densities.

- 2. It is recommended that "r" be a logical "0" for densities of 32M bits or smaller.

- 3. For densities larger than 32M bits, the "r" bits become the most significant Page Address bit for the appropriate density.

#### **Write Operations**

The following block diagram and waveforms illustrate the various write sequences available.

#### **Main Memory Page Program through Buffers**

#### **Buffer Write**

## **Buffer to Main Memory Page Program (Data from Buffer Programmed into Flash Page)**

Each transition represents 8 bits and 8 clock cycles

n = 1st byte read n+1 = 2nd byte read

#### **Read Operations**

The following block diagram and waveforms illustrate the various read sequences available.

#### **Main Memory Page Read**

#### Main Memory Page to Buffer Transfer (Data from Flash Page Read into Buffer)

#### **Buffer Read**

Each transition represents 8 bits and 8 clock cycles

n = 1st byte readn+1 = 2nd byte read

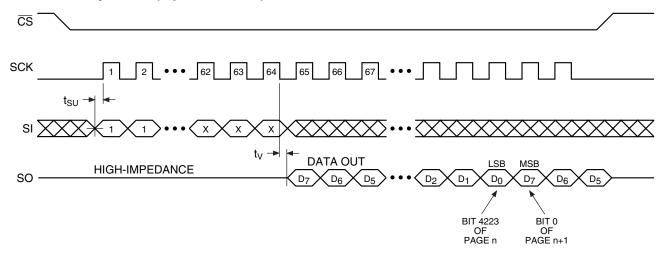

## **Detailed Bit-level Read Timing – Inactive Clock Polarity Low**

## **Continuous Array Read (Opcode: 68H)**

#### Main Memory Page Read (Opcode: 52H)

## **Detailed Bit-level Read Timing – Inactive Clock Polarity Low (Continued)**

## Buffer Read (Opcode: 54H or 56H)

#### **Status Register Read (Opcode: 57H)**

## **Detailed Bit-level Read Timing – Inactive Clock Polarity High**

## **Continuous Array Read (Opcode: 68H)**

#### Main Memory Page Read (Opcode: 52H)

## **Detailed Bit-level Read Timing – Inactive Clock Polarity High (Continued)**

## **Buffer Read (Opcode: 54H or 56H)**

#### **Status Register Read (Opcode: 57H)**

## **Detailed Bit-level Read Timing – SPI Mode 0**

## **Continuous Array Read (Opcode: E8H)**

#### **Main Memory Page Read (Opcode: D2H)**

## **Detailed Bit-level Read Timing – SPI Mode 0 (Continued)**

#### **Buffer Read (Opcode: D4H or D6H)**

#### **Status Register Read (Opcode: D7H)**

## **Detailed Bit-level Read Timing – SPI Mode 3**

## **Continuous Array Read (Opcode: E8H)**

## Main Memory Page Read (Opcode: D2H)

## **Detailed Bit-level Read Timing – SPI Mode 3 (Continued)**

#### **Buffer Read (Opcode: D4H or D6H)**

#### **Status Register Read (Opcode: D7H)**

Figure 1. Algorithm for Sequentially Programming or Reprogramming the Entire Array

- Notes: 1. This type of algorithm is used for applications in which the entire array is programmed sequentially, filling the array page-by-

- 2. A page can be written using either a Main Memory Page Program operation or a Buffer Write operation followed by a Buffer to Main Memory Page Program operation.

- 3. The algorithm above shows the programming of a single page. The algorithm will be repeated sequentially for each page within the entire array.

Figure 2. Algorithm for Randomly Modifying Data

Notes: 1. To preserve data integrity, each page of a DataFlash sector must be updated/rewritten at least once within every 10,000 cumulative page erase/program operations.

- 2. A Page Address Pointer must be maintained to indicate which page is to be rewritten. The Auto Page Rewrite command must use the address specified by the Page Address Pointer.

- 3. Other algorithms can be used to rewrite portions of the Flash array. Low-power applications may choose to wait until 10,000 cumulative page erase/program operations have accumulated before rewriting all pages of the sector. See application note AN-4 ("Using Atmel's Serial DataFlash") for more details.

## **Sector Addressing**

| PA12 | PA11 | PA10 | PA9 | PA8 | PA7 | PA6 | PA5 | PA4 | PA3 | Sector |

|------|------|------|-----|-----|-----|-----|-----|-----|-----|--------|

| 0    | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0      |

| 0    | 0    | 0    | 0   | Χ   | X   | Χ   | X   | X   | Х   | 1      |

| 0    | 0    | 0    | 1   | Χ   | X   | Χ   | X   | X   | Х   | 2      |

| 0    | 0    | 1    | 0   | Χ   | X   | Χ   | X   | X   | Х   | 3      |

| •    | •    | •    | •   | •   | •   | •   | •   | •   | •   | •      |

| •    | •    | •    | •   | •   | •   | •   | •   | •   | •   | •      |

| •    | •    | •    | •   | •   | •   | •   | •   | •   | •   | •      |

| 1    | 1    | 0    | 0   | Χ   | X   | X   | Χ   | X   | Х   | 13     |

| 1    | 1    | 0    | 1   | Χ   | X   | X   | Χ   | X   | Х   | 14     |

| 1    | 1    | 1    | 0   | Χ   | Χ   | Χ   | Х   | X   | Х   | 15     |

| 1    | 1    | 1    | 1   | Χ   | Χ   | Χ   | Χ   | Χ   | Х   | 16     |

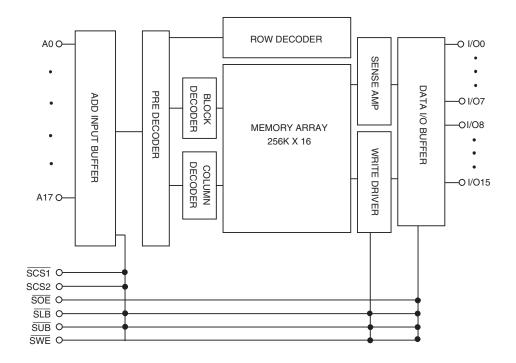

# 4-megabit SRAM Description

The 4-megabit SRAM is a high-speed, super low-power CMOS SRAM organized as 256K words by 16 bits. The SRAM uses high-performance full CMOS process technology and is designed for high-speed and low-power circuit technology. It is particularly well-suited for the high-density low-power system application. This device has a data retention mode that guarantees data to remain valid at a minimum power supply voltage of 1.2V.

#### **Features**

- Fully Static Operation and Tri-state Output

- TTL Compatible Inputs and Outputs

- Battery Backup

- 1.2V (Min) Data Retention

| Voltage (V) | Speed (ns) | Operation<br>Current/I <sub>CC</sub> (mA)<br>(Max) | Standby<br>Current (µA)<br>(Max) | Temperature<br>(°C) |

|-------------|------------|----------------------------------------------------|----------------------------------|---------------------|

| 2.7 - 3.3   | 70         | 3                                                  | 10                               | -40 - 85            |

## **Block Diagram**

## **Absolute Maximum Ratings**(1)

| Symbol                             | Parameter             | Rating      | Unit |

|------------------------------------|-----------------------|-------------|------|

| V <sub>IN</sub> , V <sub>OUT</sub> | Input/Output Voltage  | -0.3 to 3.6 | V    |

| V <sub>CC</sub>                    | Power Supply          | -0.3 to 3.6 | V    |

| T <sub>A</sub>                     | Operating Temperature | -40 to 85   | °C   |

| T <sub>STG</sub>                   | Storage Temperature   | -55 to 150  | °C   |

| P <sub>D</sub>                     | Power Dissipation     | 1.0         | W    |

Note: 1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is stress rating only and the functional operation of the device under these or any other conditions above those indicated in the operation of this specification is not implied. Exposure to the absolute maximum rating conditions for extended period may affect reliability.

#### **Truth Table**

|                  |      |     |     |                    |                    |                 | I/O              | Pin              |         |

|------------------|------|-----|-----|--------------------|--------------------|-----------------|------------------|------------------|---------|

| SCS1             | SCS2 | SWE | SOE | SLB <sup>(2)</sup> | SUB <sup>(2)</sup> | Mode            | I/O0 - I/O7      | I/O8 - I/O15     | Power   |

| H <sup>(1)</sup> | Х    |     |     | V                  | V                  |                 |                  |                  |         |

| X <sup>(1)</sup> | L    | X   | Х   | X                  | Х                  | Deselected      | High-Z           | High-Z           | Standby |

| Х                | Х    |     |     | Н                  | Н                  |                 |                  |                  |         |

|                  |      |     |     | L                  | Н                  |                 |                  |                  |         |

| L <sup>(1)</sup> | Н    | Н   | Н   | Н                  | L                  | Output Disabled | High-Z           | High-Z           | Active  |

|                  |      |     |     | L                  | L                  |                 |                  |                  |         |

|                  |      |     |     | L                  | Н                  |                 | D <sub>IN</sub>  | High-Z           |         |

| L                | Н    | L   | X   | Н                  | L                  | Write           | High-Z           | D <sub>IN</sub>  | Active  |

|                  |      |     |     | L                  | L                  |                 | D <sub>IN</sub>  | D <sub>IN</sub>  |         |

|                  |      |     |     | L                  | Н                  |                 | D <sub>OUT</sub> | High-Z           |         |

| L                | Н    | Н   | L   | Н                  | L                  | Read            | High-Z           | D <sub>OUT</sub> | Active  |

|                  |      |     |     | L                  | L                  |                 | D <sub>OUT</sub> | D <sub>OUT</sub> |         |

H = V<sub>IH</sub>, L = V<sub>IL</sub>, X = Don't Care (V<sub>IL</sub> or V<sub>IH</sub>)

SUB, SLB (Upper, Lower Byte Enable). These active LOW inputs allow individual bytes to be written or read. When SLB is LOW, data is written or read to the lower byte, I/O0 - I/O7. When SUB is LOW, data is written or read to the upper byte, I/O8 - I/O15.

### **Recommended DC Operating Condition**

| Symbol                         | Parameter          | Min                 | Тур | Max                   | Unit |

|--------------------------------|--------------------|---------------------|-----|-----------------------|------|

| V <sub>CC</sub>                | Supply Voltage     | 2.7                 | 3.0 | 3.3                   | V    |

| V <sub>SS</sub>                | Ground             | 0                   | 0   | 0                     | V    |

| V <sub>IH</sub>                | Input High Voltage | 2.2                 |     | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> <sup>(1)</sup> | Input Low Voltage  | -0.3 <sup>(1)</sup> |     | 0.6                   | V    |

1. Undershoot:  $V_{IL} = -1.5V$  for pulse width less than 30 ns. Undershoot is sampled, not 100% tested. Note:

## **DC Electrical Characteristics**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol           | Parameter                      | Test Condition                                                                                                                                                                                                                                       | Min | Max | Unit |

|------------------|--------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|------|

| I <sub>LI</sub>  | Input Leakage Current          | $V_{SS} < V_{IN} < V_{CC}$                                                                                                                                                                                                                           | -1  | 1   | μΑ   |

| I <sub>LO</sub>  | Output Leakage Current         | $\begin{split} & \frac{V_{SS} < V_{OUT} < V_{CC},}{\overline{SCS1} = V_{IH} \text{ or } SCS2 = V_{IL} \text{ or } \overline{SOE} = V_{IH} \text{ or } \overline{SWE} = VIL \text{ or } \overline{SUB} = V_{IH}, \overline{SLB} = V_{IH} \end{split}$ | -1  | 1   | μА   |

| I <sub>CC</sub>  | Operating Power Supply Current | $\overline{SCS1} = V_{IL}, SCS2=V_{IH},$ $V_{IN} = V_{IH} \text{ or } V_{IL}, I_{I/O} = 0 \text{ mA}$                                                                                                                                                |     | 3   | mA   |

| I <sub>CC1</sub> | Average Operating Current      |                                                                                                                                                                                                                                                      |     | 15  | mA   |

|                  |                                | $\overline{SCS1}$ < 0.2V, SCS2 > V <sub>CC</sub> - 0.2V<br>V <sub>IN</sub> < 0.2V or V <sub>IN</sub> > V <sub>CC</sub> - 0.2V,<br>Cycle Time = 1 µs<br>100% Duty, I <sub>I/O</sub> = 0 mA                                                            |     | 2   | mA   |

| I <sub>SB</sub>  | Standby Current (TTL Input)    | $\begin{split} \overline{SCS1} &= V_{IH} \text{ or } SCS2 = V_{IL} \text{ or } \\ \overline{SUB}, \ \overline{SLB} &= V_{IH} \\ V_{IN} &= V_{IH} \text{ or } V_{IL} \end{split}$                                                                     |     | 300 | μА   |

| I <sub>SB1</sub> | Standby Current (CMOS Input)   | $\begin{split} & \overline{SCS1} > V_{CC} - 0.2V \text{ or} \\ & \underline{SCS2} < V_{SS} + 0.2V \text{ or} \\ & \overline{SUB}, \overline{SLB} > V_{CC} - 0.2V \\ & V_{IN} > V_{CC} - 0.2V \text{ or} \\ & V_{IN} < V_{SS} + 0.2V \end{split}$     |     | 10  | μА   |

| $V_{OL}$         | Output Low                     | I <sub>OL</sub> = 2.1 mA                                                                                                                                                                                                                             |     | 0.4 | V    |

| V <sub>OH</sub>  | Output High                    | I <sub>OH</sub> = -1.0 mA                                                                                                                                                                                                                            | 2.4 |     | V    |

# Capacitance<sup>(1)</sup>

$(Temp = 25^{\circ}C, f = 1.0 MHz)$

| Symbol           | Parameter                                               | Condition              | Max | Unit |

|------------------|---------------------------------------------------------|------------------------|-----|------|

| C <sub>IN</sub>  | Input Capacitance (Add, SCS1, SCS2, SLB, SUB, SWE, SOE) | V <sub>IN</sub> = 0 V  | 8   | pF   |

| C <sub>OUT</sub> | Output Capacitance (I/O)                                | V <sub>I/O</sub> = 0 V | 10  | pF   |

Note: 1. These parameters are sampled and not 100% tested.

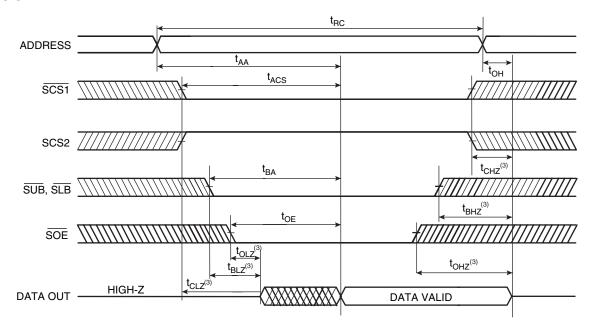

## **AC Characteristics**

$T_A = -40$ °C to 85°C, Unless Otherwise Specified

|    |                  |                                      | 70  | ns  |      |

|----|------------------|--------------------------------------|-----|-----|------|

| #  | Symbol           | Parameter                            | Min | Max | Unit |

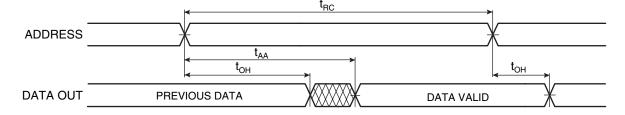

| 1  | t <sub>RC</sub>  | Read Cycle Time                      | 70  |     | ns   |

| 2  | t <sub>AA</sub>  | Address Access Time                  |     | 70  | ns   |

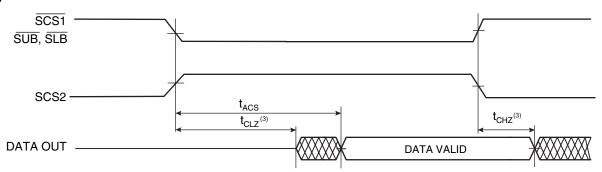

| 3  | t <sub>ACS</sub> | Chip Select Access Time              |     | 70  | ns   |

| 4  | t <sub>OE</sub>  | Output Enable to Output Valid        |     | 35  | ns   |

| 5  | t <sub>BA</sub>  | SLB, SUB Access Time                 |     | 70  | ns   |

| 6  | t <sub>CLZ</sub> | Chip Select to Output in Low Z       | 10  |     | ns   |

| 7  | t <sub>OLZ</sub> | Output Enable to Output in Low Z     | 5   |     | ns   |

| 8  | t <sub>BLZ</sub> | SLB, SUB Enable to Output in Low Z   | 10  |     | ns   |

| 9  | t <sub>CHZ</sub> | Chip Deselection to Output in High Z | 0   | 25  | ns   |

| 10 | t <sub>OHZ</sub> | Out Disable to Output in High Z      | 0   | 25  | ns   |

| 11 | t <sub>BHZ</sub> | SLB, SUB Disable to Output in High Z | 0   | 25  | ns   |

| 12 | t <sub>OH</sub>  | Output Hold from Address Change      | 10  |     | ns   |

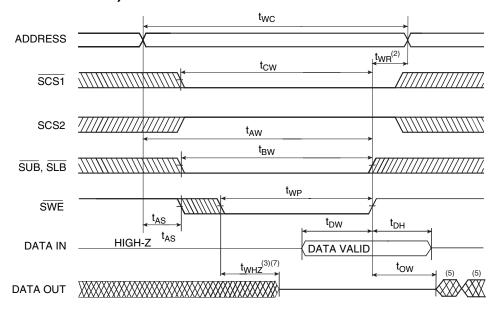

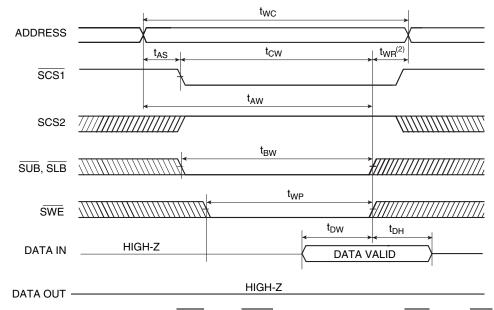

| 13 | t <sub>WC</sub>  | Write Cycle Time                     | 30  |     | ns   |

| 14 | t <sub>CW</sub>  | Chip Selection to End of Write       | 30  |     | ns   |

| 15 | t <sub>AW</sub>  | Address Valid to End of Write        | 30  |     | ns   |

| 16 | t <sub>BW</sub>  | SLB, SUB Valid to End of Write       | 30  |     | ns   |

| 17 | t <sub>AS</sub>  | Address Setup Time                   | 0   |     | ns   |

| 18 | t <sub>WP</sub>  | Write Pulse Width                    | 30  |     | ns   |

| 19 | t <sub>WR</sub>  | Write Recovery Time                  | 0   |     | ns   |

| 20 | t <sub>WHZ</sub> | Write to Output in High Z            | 0   | 5   | ns   |

| 21 | t <sub>DW</sub>  | Data to Write Time Overlap           | 25  |     | ns   |

| 22 | t <sub>DH</sub>  | Data Hold from Write Time            | 0   |     | ns   |

| 23 | t <sub>OW</sub>  | Output Active from End of Write      | 5   |     | ns   |

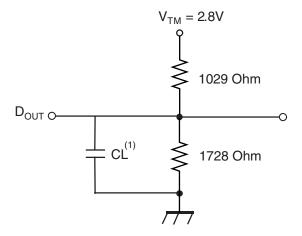

#### **AC Test Conditions**

TA = -40°C to 85°C, Unless Otherwise Specified

| Parameter               |                                                                                                                          | Value                   |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| Input Pulse Level       |                                                                                                                          | 0.4V to 2.2V            |  |  |

| Input Rise and Fall Tim | ne                                                                                                                       | 5 ns                    |  |  |

| Input and Output Timin  | g Reference Level                                                                                                        | 1.5V                    |  |  |

| Output Load             | $t_{\text{CLZ}},t_{\text{OLZ}},t_{\text{BLZ}},t_{\text{CHZ}},t_{\text{OHZ}},t_{\text{BHZ}},t_{\text{WHZ}},t_{\text{OW}}$ | CL = 5 pF + 1 TTL Load  |  |  |

|                         | Others                                                                                                                   | CL = 30 pF + 1 TTL Load |  |  |

#### **AC Test Loads**

Note: Including jig and scope capacitance.

#### **Timing Diagrams**

## Read Cycle 1<sup>(1),(4)</sup>

#### **Read Cycle 2**<sup>(1),(2),(4)</sup>

## **Read Cycle 3**<sup>(1),(2),(4)</sup>

Note:

- 1. Read Cycle occurs whenever a high on the SWE and SOE is low, while SUB and/or SLB and SCS1 and SCS2 are in active status.

- 2.  $\overline{SOE} = V_{IL}$

- 3.  $\underline{\text{Transition}}$  is measured  $\pm$  200 mV from steady state voltage. This parameter is sampled and not 100% tested.

- 4. SCS1 in high for the standby, low for active. SCS2 in low for the standby, high for active. SUB and SLB in high for the standby, low for active.

#### Write Cycle 1 (SWE Controlled)(1),(4),(8)

#### Write Cycle 2 (SCS1, SCS2 Controlled)(1),(4),(8)

Notes:

- 1. A write occurs during the overlap of a low SWE, a low SCS1, a high SCS2 and a low SUB and/or SLB.

- 2. t<sub>WB</sub> is measured from the earlier of SCS1, SLB, SUB, or SWE going high or SCS2 going low to the end of write cycle.

- 3. During this period, I/O pins are in the output state so that the input signals of opposite phase to the output must not be applied.

- 4. If the SCS1, SLB and SUB low transition and SCS2 high transition occur simultaneously with the SWE low transition or after the SWE transition, outputs remain in a high impedance state.

- 5. Q (data out) is the same phase with the write data of this write cycle.

- 6. Q (data out) is the read data of the next address.

- 7. Transition is measured ± 200 mV from steady state. This parameter is sampled and not 100% tested.

- 8. SCS1 in high for the standby, low for active SCS2 in low for the standby, high for active. SUB and SLB in high for the standby, low for active.

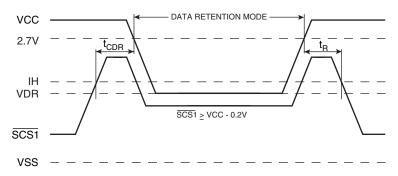

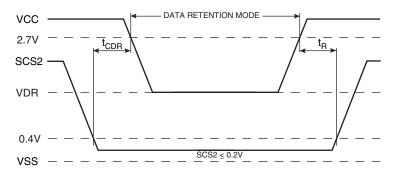

#### **Data Retention Electric Characteristic**

$T_A = -40^{\circ}C$  to  $85^{\circ}C$

| Symbol            | Parameter                               | Test Condition                                                                                                                                                                                                                                                                                                                                                                                    | Min             | Тур | Max | Unit |

|-------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----|-----|------|

| V <sub>DR</sub>   | V <sub>CC</sub> for Data Retention      | $\begin{split} \overline{SCS1} &> V_{CC} - 0.2V \text{ or} \\ SCS2 &< V_{SS} + 0.2V \text{ or} \\ \overline{SUB}, \overline{SLB} &> V_{CC} - 0.2V \\ V_{IN} &> V_{CC} - 0.2V \text{ or} \\ V_{IN} &< V_{SS} + 0.2V \end{split}$                                                                                                                                                                   | 1.2             |     | 3.3 | V    |

| I <sub>CCDR</sub> | Data Retention Current                  | $\begin{split} & \frac{\text{Vcc=1.5V,}}{\text{SCS1}} > \text{V}_{\text{CC}} - 0.2\text{V or} \\ & \frac{\text{SCS2}}{\text{SUB,}} < \text{V}_{\text{SS}} + 0.2\text{V or} \\ & \frac{\text{SUB,}}{\text{SUB}} > \text{V}_{\text{CC}} - 0.2\text{V} \\ & \text{V}_{\text{IN}} > \text{V}_{\text{CC}} - 0.2\text{V or} \\ & \text{V}_{\text{IN}} < \text{V}_{\text{SS}} + 0.2\text{V} \end{split}$ |                 | 0.2 | 6   | μА   |

|                   |                                         |                                                                                                                                                                                                                                                                                                                                                                                                   |                 |     |     |      |

| t <sub>CDR</sub>  | Chip Deselect to Data<br>Retention Time | See Data Retention Timing Diagram                                                                                                                                                                                                                                                                                                                                                                 | 0               |     |     | ns   |

| t <sub>R</sub>    | Operating Recovery Time                 |                                                                                                                                                                                                                                                                                                                                                                                                   | t <sub>RC</sub> |     |     | ns   |

Typical values are under the condition of T<sub>A</sub> = 25°C. Typical values are sampled and not 100% tested.

t<sub>RC</sub> is read cycle time. Notes:

#### **Data Retention Timing Diagram 1**

#### **Data Retention Timing Diagram 2**

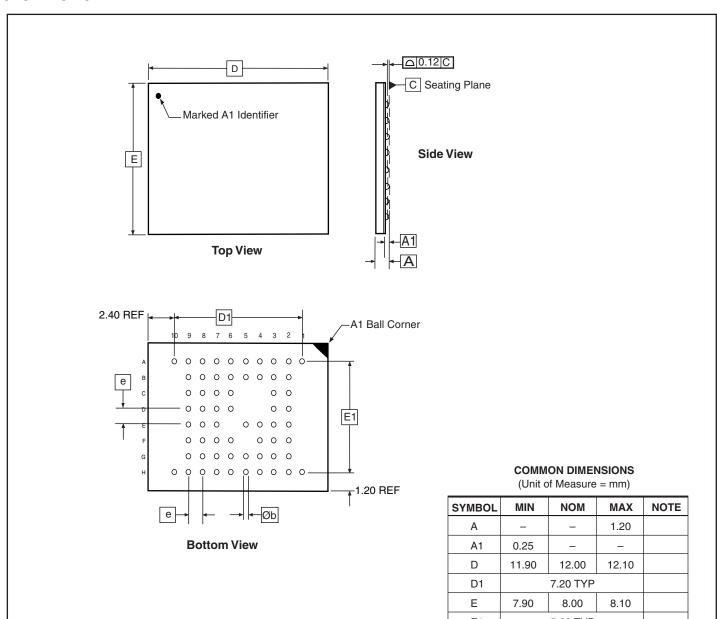

# **Ordering Information**

| DataFlas<br>f <sub>SCK</sub> (MH |    | Ordering Code  | DataFlash | SRAM      | Package | Operation Range               |

|----------------------------------|----|----------------|-----------|-----------|---------|-------------------------------|

| 20                               | 70 | AT45BR3214B-C1 | 32M x 1   | 256k x 16 | 62C1    | Industrial<br>(-40°C to 85°C) |

| Package Type |                                                    |  |  |  |  |

|--------------|----------------------------------------------------|--|--|--|--|

| 62C1         | 62-ball, Plastic Chip-scale Ball Grid Array (CBGA) |  |  |  |  |

## **Packaging Information**

#### 62C1 - CBGA

| SYMBOL      | MIN      | NOM   | MAX   | NOTE |

|-------------|----------|-------|-------|------|

| Α           | _        | _     | 1.20  |      |

| A1          | 0.25     | _     | 1     |      |

| D           | 11.90    | 12.00 | 12.10 |      |

| D1          | 7.20 TYP |       |       |      |

| E           | 7.90     | 8.00  | 8.10  |      |

| E1 5.60 TYP |          |       |       |      |

| е           |          |       |       |      |

| Øb          | 0.40 TYP |       |       |      |

|             |          |       |       |      |

05/12/03

TITLE **62C1**, 62-ball (10 x 8 Array), 12 x 8 x 1.2 mm Body, 0.8 mm Ball Plastic Chip-scale Ball Grid Array Package (CBGA) DRAWING NO. REV. 62C1 Α

#### **Atmel Corporation**

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311

Fax: 1(408) 487-2600

#### Regional Headquarters

#### Europe

Atmel Sarl Route des Arsenaux 41 Case Postale 80 CH-1705 Fribourg Switzerland

Tel: (41) 26-426-5555 Fax: (41) 26-426-5500

#### Asia

Room 1219 Chinachem Golden Plaza 77 Mody Road Tsimshatsui East Kowloon Hong Kong

Tel: (852) 2721-9778 Fax: (852) 2722-1369

#### Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan

Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Atmel Operations**

#### Memory

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

#### Microcontrollers

2325 Orchard Parkway San Jose, CA 95131, USA Tel: 1(408) 441-0311 Fax: 1(408) 436-4314

La Chantrerie BP 70602 44306 Nantes Cedex 3, France Tel: (33) 2-40-18-18-18

Fax: (33) 2-40-18-19-60

#### ASIC/ASSP/Smart Cards

Zone Industrielle 13106 Rousset Cedex, France Tel: (33) 4-42-53-60-00

Fax: (33) 4-42-53-60-01

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Scottish Enterprise Technology Park Maxwell Building East Kilbride G75 0QR, Scotland

Tel: (44) 1355-803-000 Fax: (44) 1355-242-743

#### RF/Automotive

Theresienstrasse 2 Postfach 3535 74025 Heilbronn, Germany Tel: (49) 71-31-67-0

Tel: (49) 71-31-67-0 Fax: (49) 71-31-67-2340

1150 East Cheyenne Mtn. Blvd. Colorado Springs, CO 80906, USA

Tel: 1(719) 576-3300 Fax: 1(719) 540-1759

Biometrics/Imaging/Hi-Rel MPU/ High Speed Converters/RF Datacom

Avenue de Rochepleine

BP 123

38521 Saint-Egreve Cedex, France

Tel: (33) 4-76-58-30-00 Fax: (33) 4-76-58-34-80

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDITIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© Atmel Corporation 2004. All rights reserved. Atmel<sup>®</sup>, logo and combinations thereof, and DataFlash<sup>®</sup> are registered trademarks, and Everywhere You Are<sup>SM</sup> is the trademark of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## Microchip:

AT24C64B-10TU-1.8 AT24C64B-10TU-2.7

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.