# High Efficiency, Secondary-Side Synchronous Forward Controller

## FEATURES

- Direct Flux Limit™ Guarantees No Saturation

- Fast and Accurate Average Current Limit

- Clean Start-Up Into Pre-Biased Output

- Secondary-Side Control for Fast Transient Response

- Simple, Self-Starting Architecture

- Synchronous MOSFET Reverse Current Limit

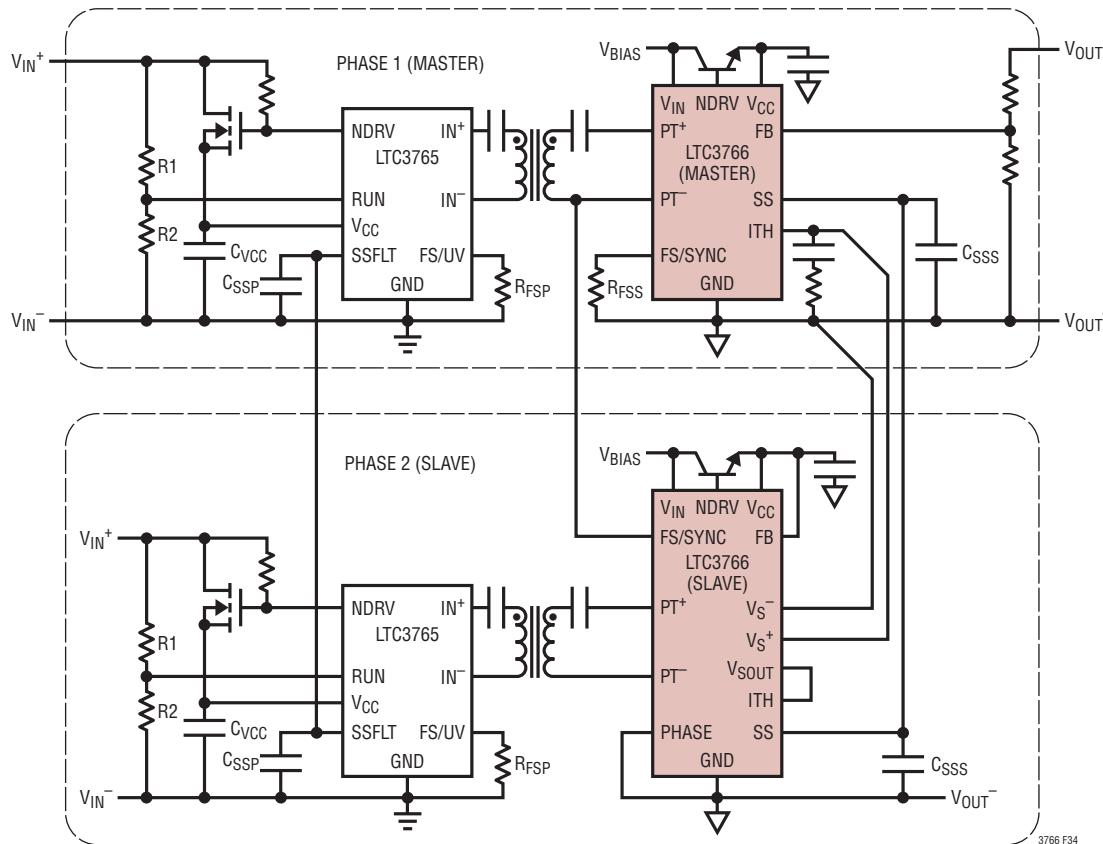

- PolyPhase® Operation Eases High-Power Design

- True Remote Sense Differential Amplifier

- Remote Sense Reverse Protection

- High Voltage Linear Regulator Controller

- Internal LDO Powers Gate Drive from  $V_{OUT}$

- Overtemperature/Overvoltage Protection

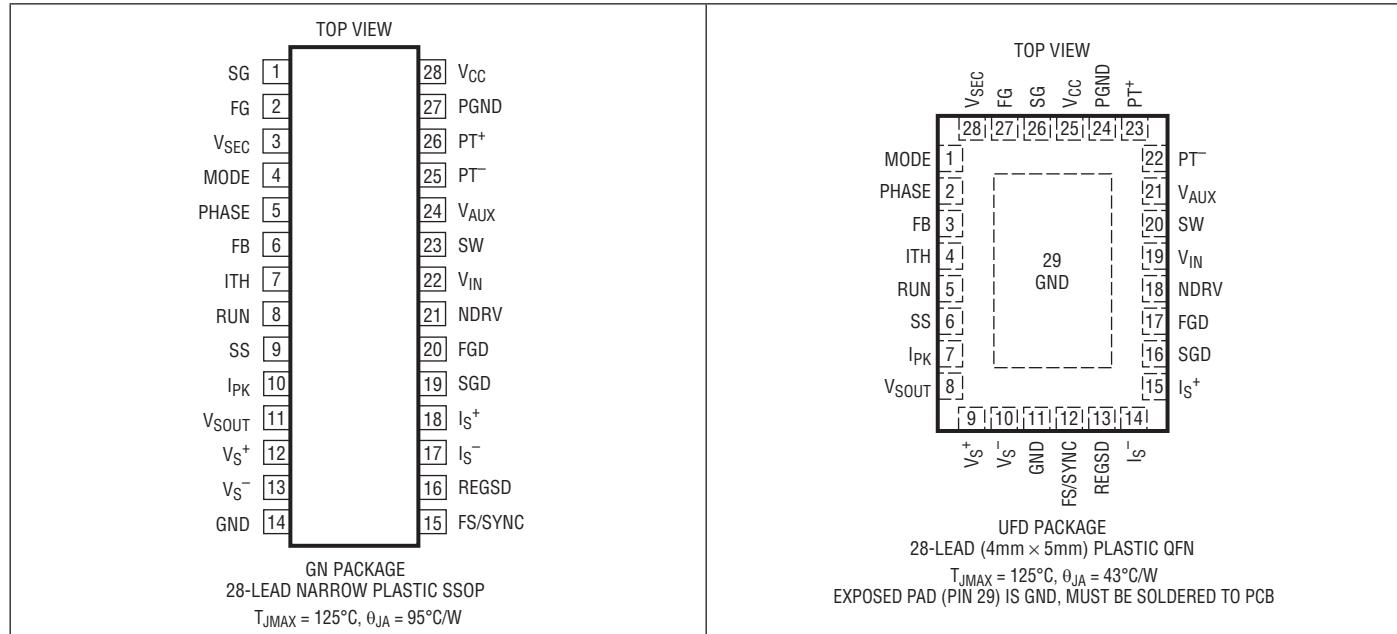

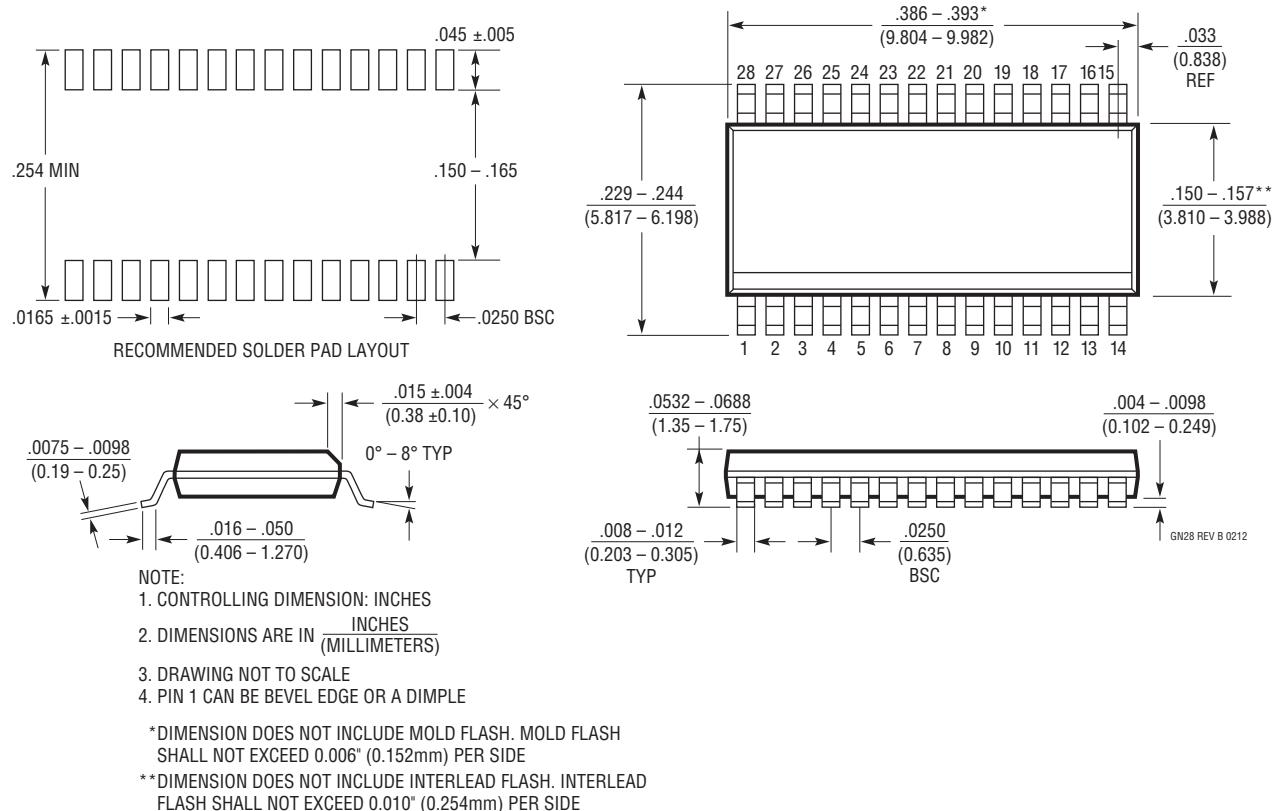

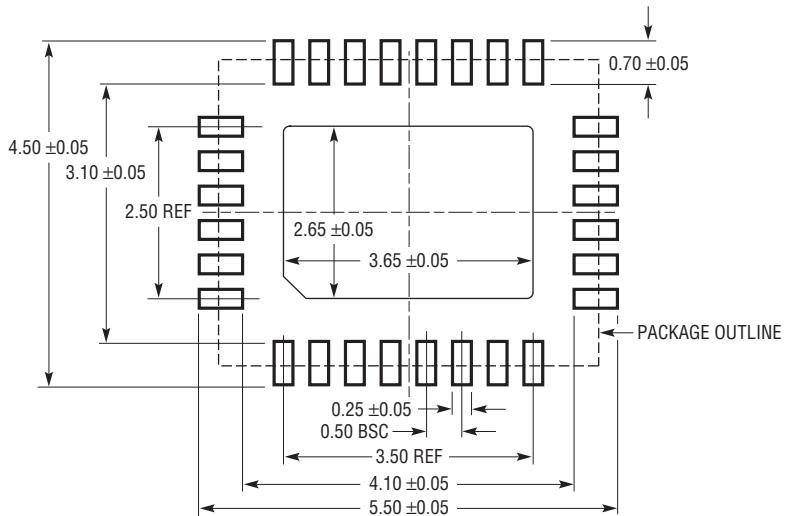

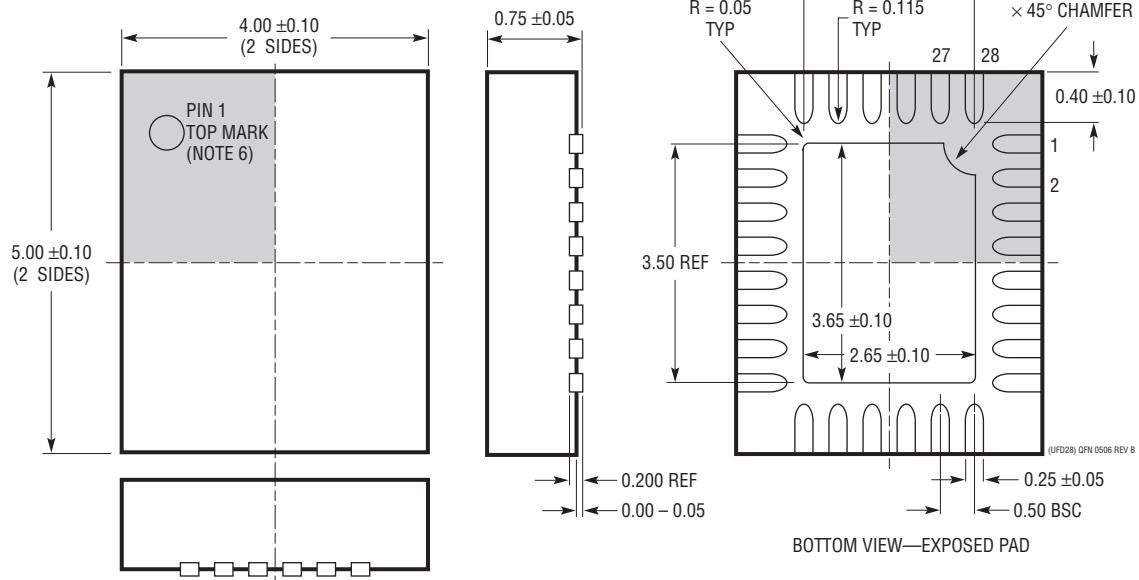

- Low Profile 4mm × 5mm QFN and Narrow 28-Lead SSOP Packages

## APPLICATIONS

- Isolated 48V Telecommunication Systems

- Isolated Battery Chargers

- Automotive and Military Systems

- Industrial, Avionics and Heavy Equipment

LT, LTC, LTM, PolyPhase, Linear Technology and the Linear logo are registered and Direct Flux Limit is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 7200014 and 6144194. Other patents pending.

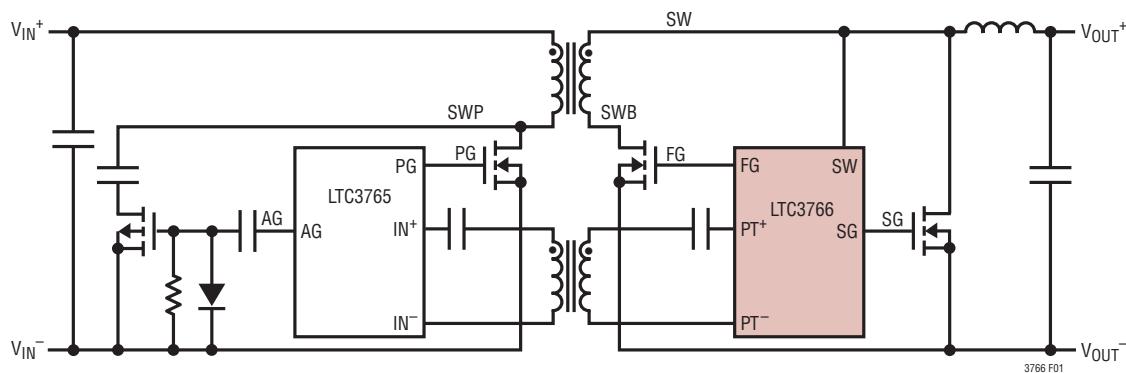

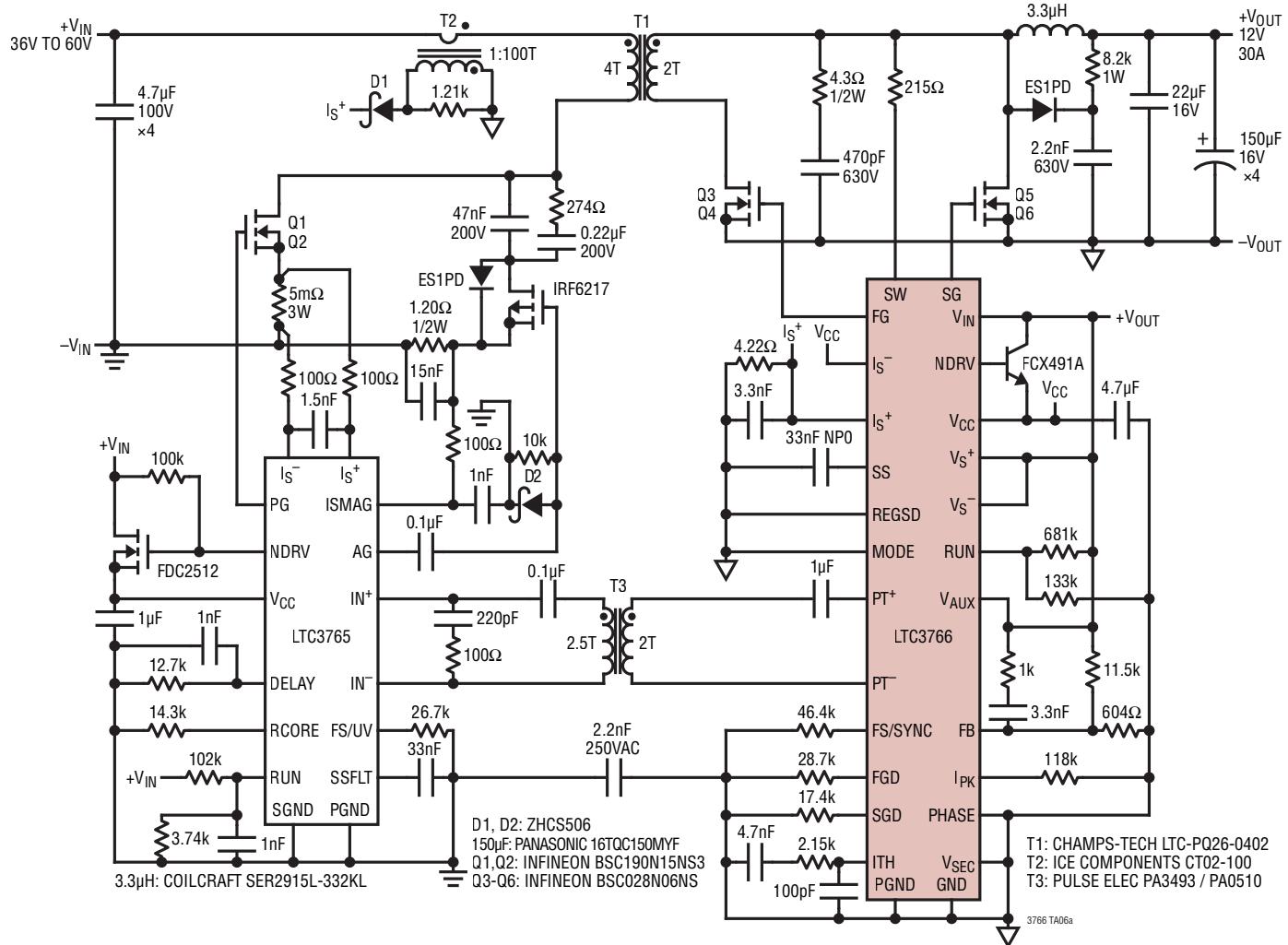

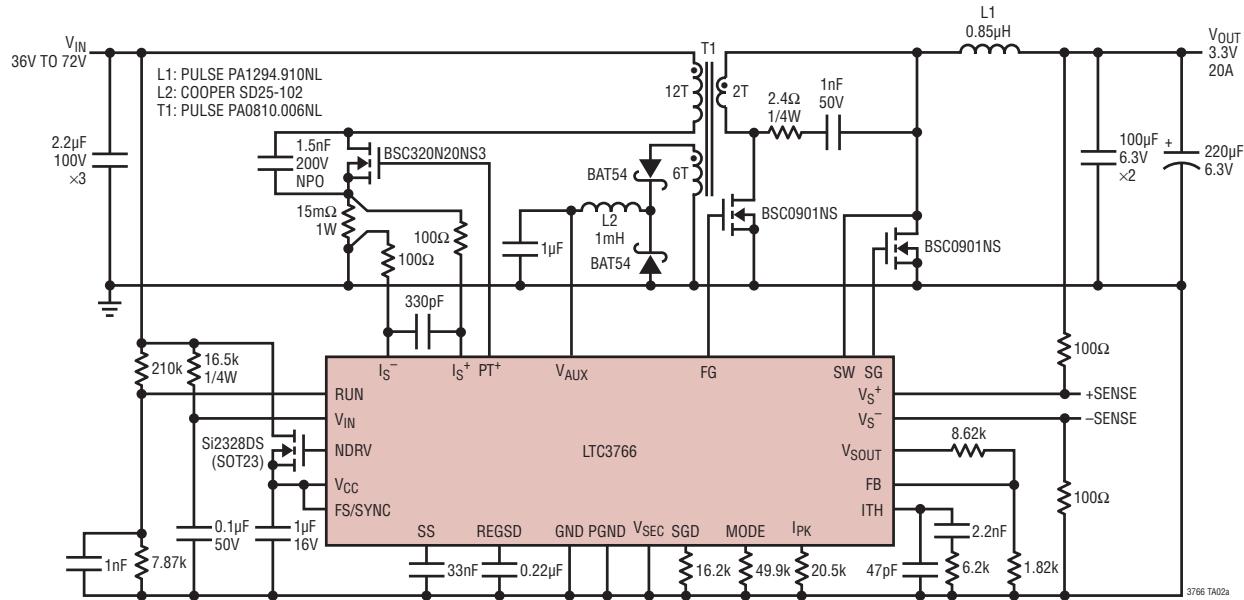

## TYPICAL APPLICATION

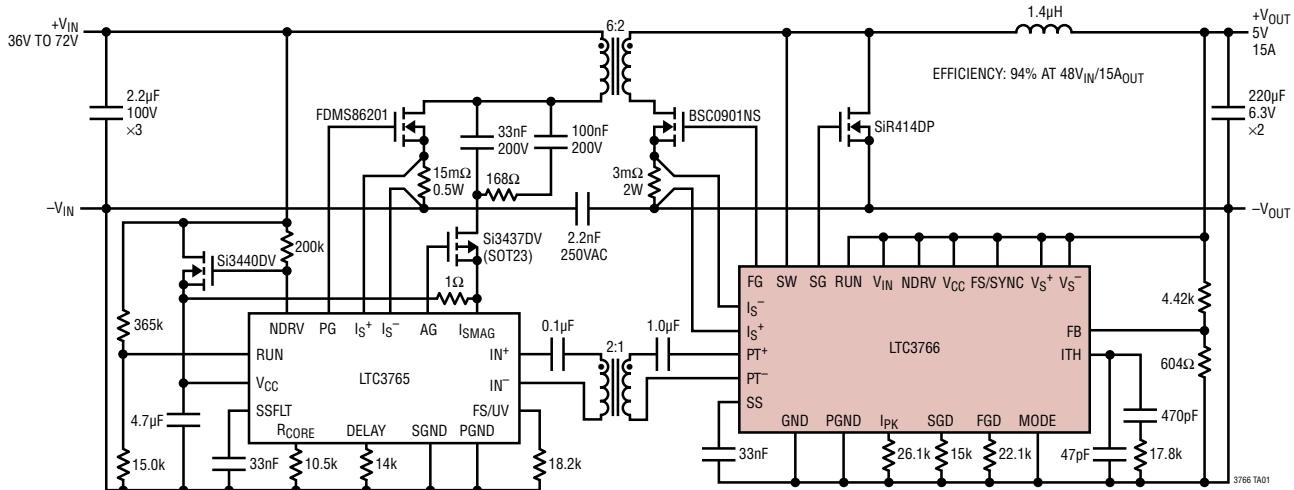

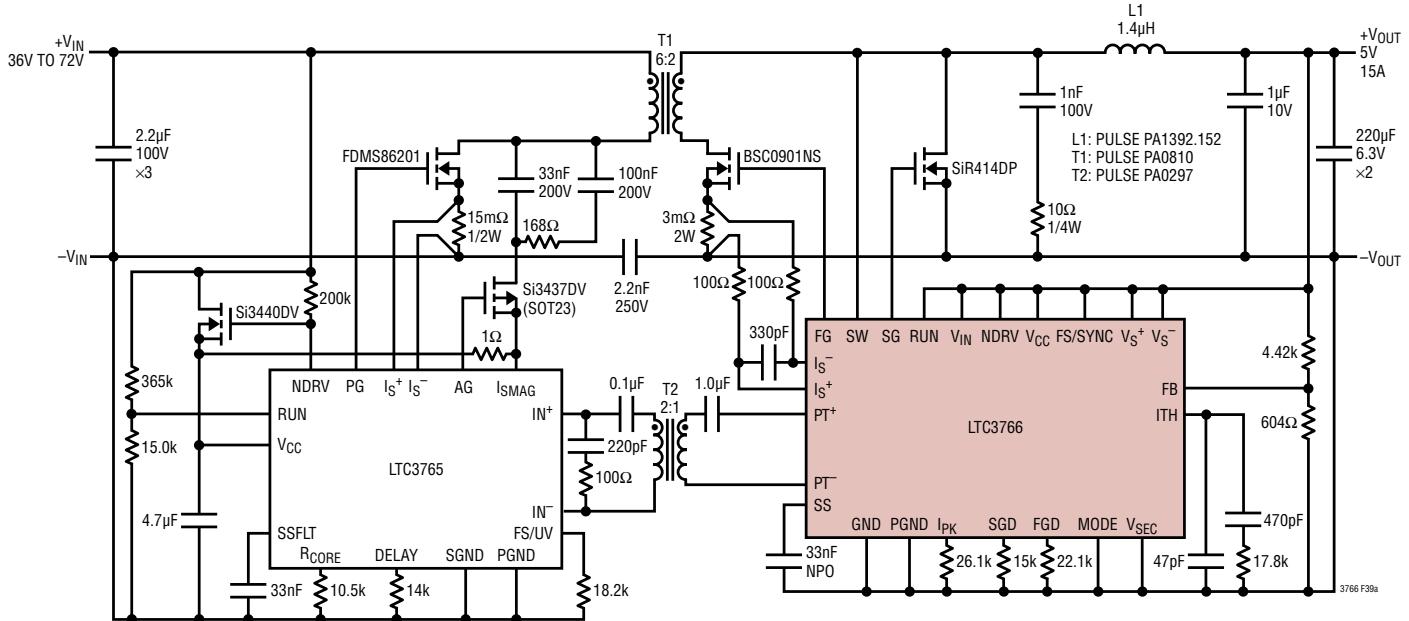

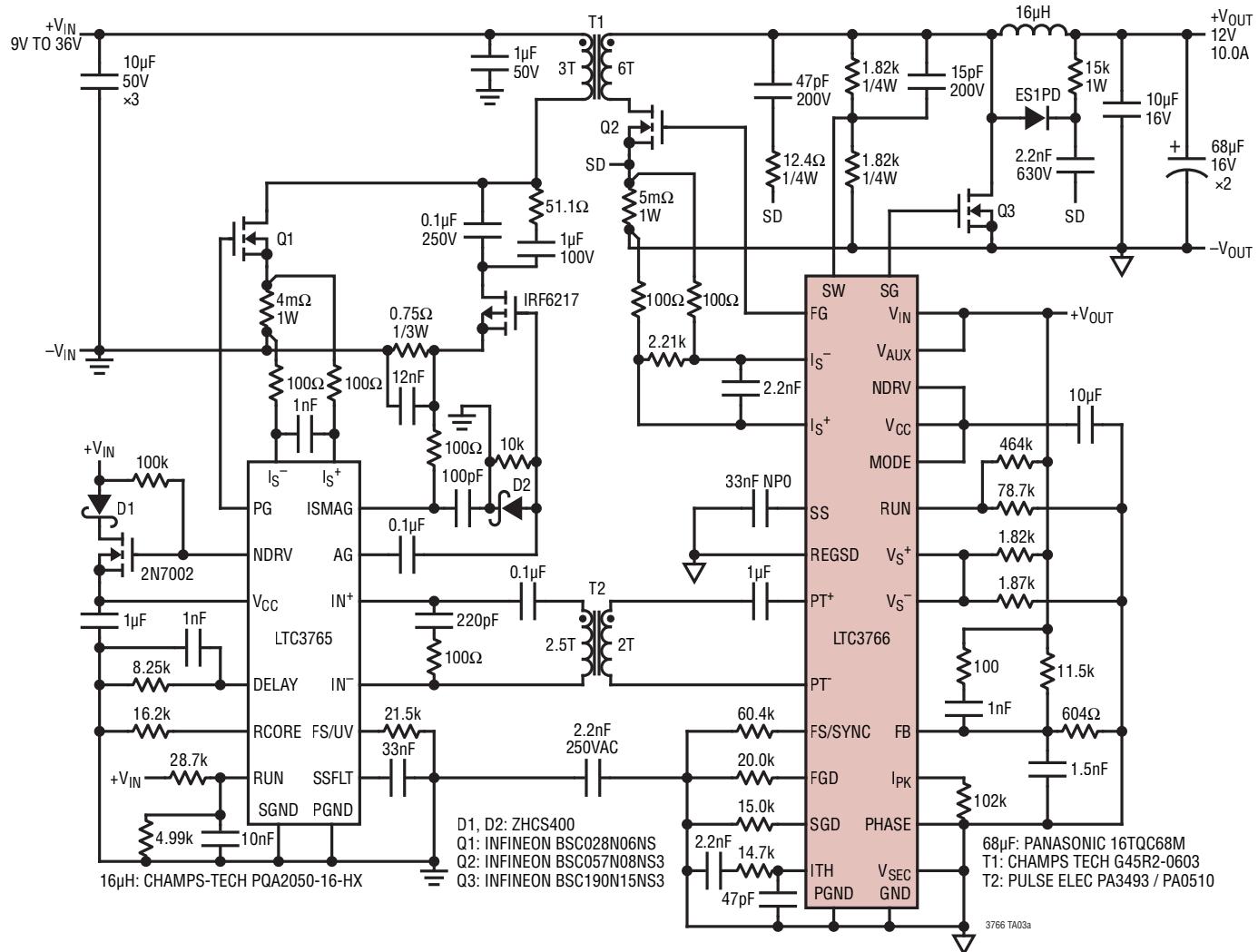

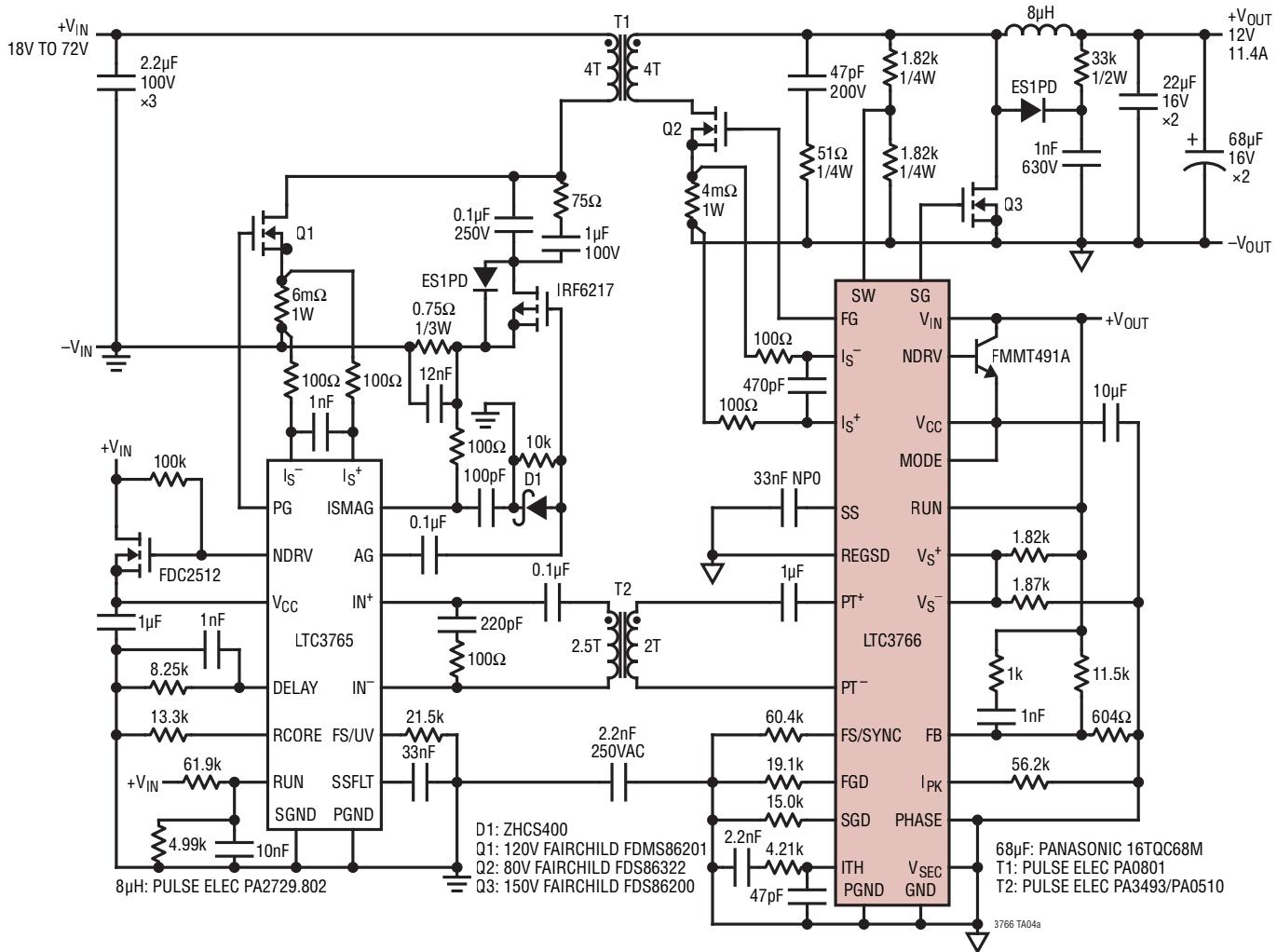

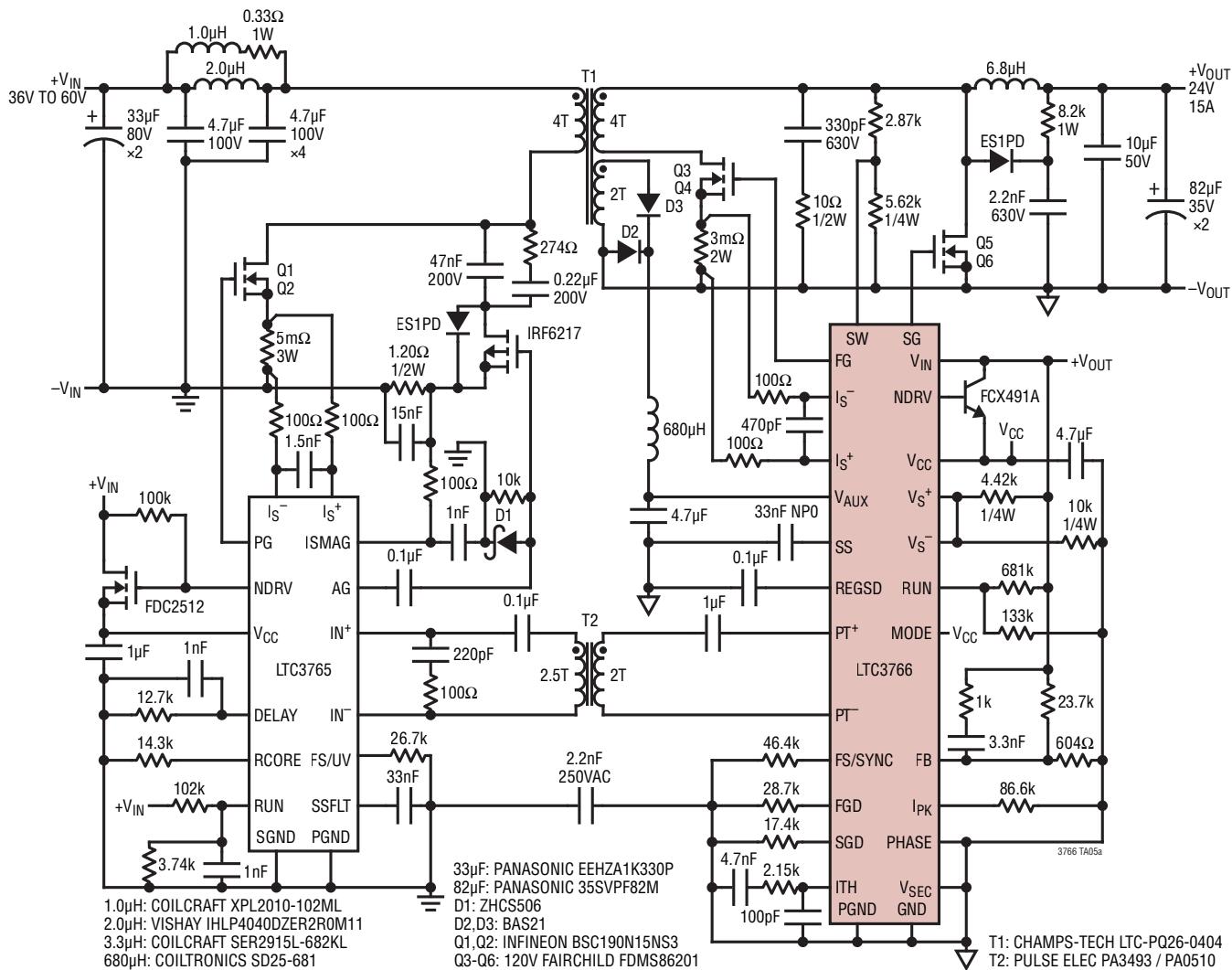

### 36V – 72V to 5V/15A Active Clamp Isolated Forward Converter

3766 TA01

## ABSOLUTE MAXIMUM RATINGS (Note 1)

|                                                                                                                |                                   |                                                  |                |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------|----------------|

| V <sub>CC</sub> Voltage                                                                                        | −0.3V to 12V                      | V <sub>SEC</sub> Voltage                         | −0.3V to 3V    |

| V <sub>IN</sub> Voltage                                                                                        | −0.3V to 33V                      | I <sub>PK</sub> , SS Voltages                    | −0.3V to 4V    |

| RUN Voltage                                                                                                    | −0.3V to 33V                      | Operating Junction Temperature Range (Notes 2,3) |                |

| SW                                                                                                             |                                   | LTC3766E, LTC3766I                               | −40°C to 125°C |

| Low Impedance Source                                                                                           | −5V to 40V                        | LTC3766H                                         | −40°C to 150°C |

| Current Fed                                                                                                    | 2mA DC or 0.2A for <1μs Into Pin* | LTC3766MP                                        | −55°C to 150°C |

| V <sub>AUX</sub> , V <sub>S<sup>+</sup></sub> , V <sub>S<sup>−</sup></sub> , V <sub>SOUT</sub> , NDRV Voltages | −0.3V to 16V                      | Storage Temperature Range                        | −65°C to 150°C |

| ITH, I <sub>S<sup>+</sup></sub> , REGSD Voltages                                                               | −0.3V to 6V                       | Lead Temperature (Soldering, 10 sec)             |                |

| PHASE Voltage                                                                                                  | −0.3V to 6V                       | GN Package                                       | 300°C          |

| I <sub>S<sup>−</sup></sub> , SGD, FGD Voltages                                                                 | −0.3V to 12V                      |                                                  |                |

| FS/SYNC, FB, MODE Voltages                                                                                     | −0.3V to 12V                      |                                                  |                |

\*The LTC3766 contains an internal 50V clamp that limits the voltage on the SW pin.

## PIN CONFIGURATION

## ORDER INFORMATION

<http://www.linear.com/product/LTC3766#orderinfo>

| LEAD FREE FINISH | TAPE AND REEL     | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|-------------------|---------------|---------------------------------|-------------------|

| LTC3766EGN#PBF   | LTC3766EGN#TRPBF  | LTC3766GN     | 28-Lead Narrow Plastic SSOP     | -40°C to 125°C    |

| LTC3766IGN#PBF   | LTC3766IGN#TRPBF  | LTC3766GN     | 28-Lead Narrow Plastic SSOP     | -40°C to 125°C    |

| LTC3766HGN#PBF   | LTC3766HGN#TRPBF  | LTC3766GN     | 28-Lead Narrow Plastic SSOP     | -40°C to 150°C    |

| LTC3766MPGN#PBF  | LTC3766MPGN#TRPBF | LTC3766GN     | 28-Lead Narrow Plastic SSOP     | -55°C to 150°C    |

| LTC3766EUFD#PBF  | LTC3766EUFD#TRPBF | 3766          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC3766IUFD#PBF  | LTC3766IUFD#TRPBF | 3766          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 125°C    |

| LTC3766HUFD#PBF  | LTC3766HUFD#TRPBF | 3766          | 28-Lead (4mm × 5mm) Plastic QFN | -40°C to 150°C    |

| LTC3766MPUD#PBF  | LTC3766MPUD#TRPBF | 3766          | 28-Lead (4mm × 5mm) Plastic QFN | -55°C to 150°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: <http://www.linear.com/leadfree/>

For more information on tape and reel specifications, go to: <http://www.linear.com/tapeandreel/>. Some packages are available in 500 unit reels through designated sales channels with #TRMPBF suffix.

## ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^\circ\text{C}$ . (Note 2)  $V_{IN} = 15\text{V}$ ,  $\text{GND} = \text{PGND} = 0\text{V}$ , unless otherwise noted.

| SYMBOL                   | PARAMETER                            | CONDITIONS                                                                                                        | MIN        | TYP         | MAX         | UNITS    |

|--------------------------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------|------------|-------------|-------------|----------|

| <b>Main Control Loop</b> |                                      |                                                                                                                   |            |             |             |          |

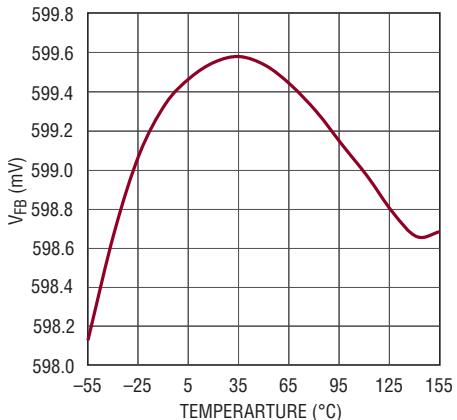

| $V_{FB}$                 | Regulated Feedback Voltage           | (Note 4) ITH = 1.2V                                                                                               | ●          | 0.592       | 0.600       | 0.608    |

| $I_{FB}$                 | Feedback Input Current               | (Note 4)                                                                                                          |            | 2           | 50          | nA       |

| $\Delta V_{FB(LINREG)}$  | Feedback Voltage Line Regulation     | $V_{IN} = 5\text{V}$ to $32\text{V}$ , ITH = 1.2V                                                                 |            | 0.001       |             | %/V      |

| $\Delta V_{FB(LOADREG)}$ | Feedback Voltage Load Regulation     | Measured in Servo Loop, ITH = 0.5V to 2V                                                                          | ●          | -0.01       | -0.1        | %        |

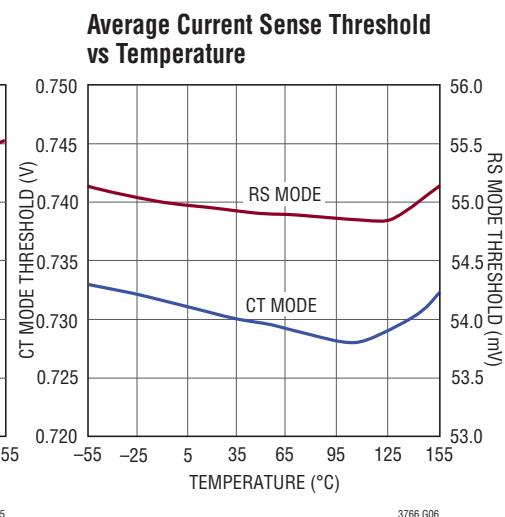

| $V_{ISAVG}$              | Average Current Sense Threshold      | Resistor Sense (RS) Mode<br>Current Transformer (CT) Mode                                                         | 47<br>0.66 | 55<br>0.73  | 63<br>0.80  | mV<br>V  |

| $V_{ISADJ}$              | Current Sense Ripple Compensation    | RS Mode<br>CT Mode<br>$V_{SW} = 10\text{V}$ , $V_S^+ = 5\text{V}$ , FS/SYNC = $V_{CC}$ , $R_{IPK} = 23.7\text{k}$ |            | 10<br>140   |             | mV<br>mV |

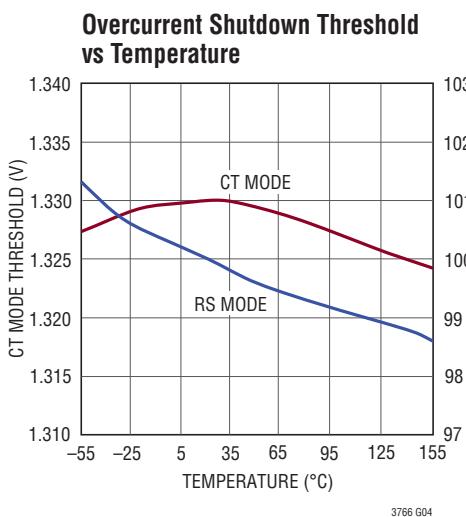

| $V_{ISOC}$               | Overcurrent Shutdown Threshold       | RS Mode: $V_{IS^-} = 0\text{V}$<br>CT Mode: $V_{IS^-} = V_{CC}$                                                   | 86<br>1.22 | 100<br>1.33 | 113<br>1.44 | mV<br>V  |

| $I_{SIN}$                | $I_S^+$ and $I_S^-$ Input Current    |                                                                                                                   |            | 280         | 500         | nA       |

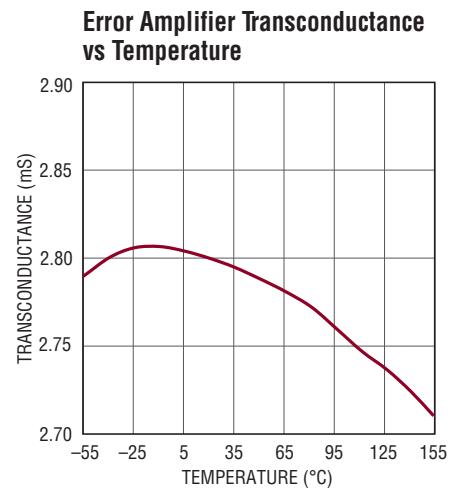

| $g_m$                    | Error Amplifier $g_m$                |                                                                                                                   |            | 2.2         | 2.7         | 3.2      |

| $R_{EA}$                 | Error Amplifier Output Resistance    | (Note 7)                                                                                                          |            | 5           |             | MΩ       |

| $I_{SOFT(C)}$            | Soft-Start Charge Current            | $V_{SS} = 2\text{V}$                                                                                              |            | 4           | 5           | 6        |

| $I_{SOFT(D)}$            | Soft-Start Discharge Current         | $V_{SS} = 2\text{V}$                                                                                              |            | 3           |             | μA       |

| $V_{RUNR}$               | RUN Pin On Threshold                 | $V_{RUN}$ Rising                                                                                                  | ●          | 1.18        | 1.22        | 1.26     |

| $V_{RUNF}$               | RUN Pin Off Threshold                | $V_{RUN}$ Falling                                                                                                 | ●          | 1.13        | 1.17        | 1.21     |

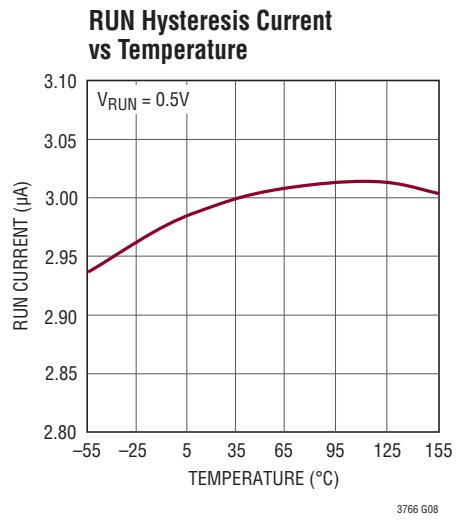

| $I_{RUN}$                | RUN Pin Hysteresis Current           | $V_{RUN} = 0.5\text{V}$                                                                                           |            | 2.2         | 3.0         | 3.6      |

| $t_{ON(MIN)}$            | Minimum Controllable On Time         |                                                                                                                   |            | 200         |             | ns       |

| $D_{MAX}$                | Maximum Duty Cycle                   | FGD = SGD = GND                                                                                                   |            | 77          | 79          | 81       |

| $\Delta V_{SEC(TH)}$     | Volt-Second Limit Threshold Accuracy | $2\text{V} \leq V_{SW} < 5\text{V}$<br>$5\text{V} \leq V_{SW} \leq 40\text{V}$                                    | -6<br>-4   | 6<br>4      |             | %        |

| $R_{VSDN}$               | Volt-Second Discharge Resistance     |                                                                                                                   |            | 75          |             | Ω        |

| $V_{SWCL}$               | SW Clamp Voltage                     | $I_{SW} = 1\text{mA}$                                                                                             |            | 43          | 51          | 60       |

| $\Delta V_{FB(OV)}$      | Output Overvoltage Threshold         | $V_{FB}$ Rising                                                                                                   |            | 15          | 17          | 19       |

## ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^\circ\text{C}$ . (Note 2)  $V_{IN} = 15\text{V}$ ,  $GND = PGND = 0\text{V}$ , unless otherwise noted.

| SYMBOL                             | PARAMETER                                                     | CONDITIONS                                                                 | MIN          | TYP          | MAX          | UNITS                          |

|------------------------------------|---------------------------------------------------------------|----------------------------------------------------------------------------|--------------|--------------|--------------|--------------------------------|

| <b>Drivers and Control</b>         |                                                               |                                                                            |              |              |              |                                |

| $FG, SG\ R_{UP}$                   | FG, SG Driver Pull-Up On-Resistance                           |                                                                            |              | 1.5          |              | $\Omega$                       |

| $FG, SG\ R_{DOWN}$                 | FG, SG Driver Pull-Down On-Resistance                         |                                                                            |              | 1.0          |              | $\Omega$                       |

| $PT^+, PT^-\ R_{UP}$               | PT <sup>+</sup> , PT <sup>-</sup> Driver Pull-Up Resistance   |                                                                            |              | 1.5          |              | $\Omega$                       |

| $PT^+, PT^-\ R_{DOWN}$             | PT <sup>+</sup> , PT <sup>-</sup> Driver Pull-Down Resistance |                                                                            |              | 1.5          |              | $\Omega$                       |

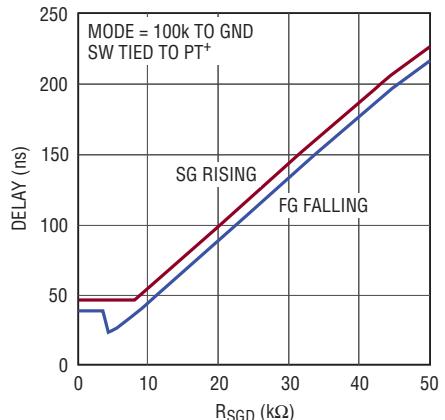

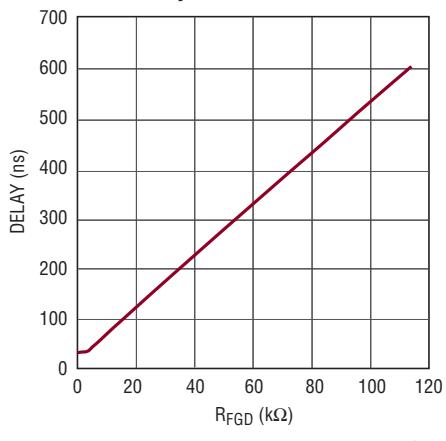

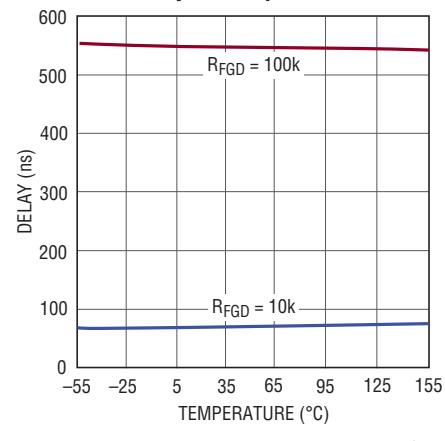

| $t_{FGD}$                          | FGD Delay                                                     | $R_{FGD} = 10\text{k}\Omega$<br>$R_{FGD} = 100\text{k}\Omega$              | 50<br>436    | 65<br>545    | 80<br>654    | ns<br>ns                       |

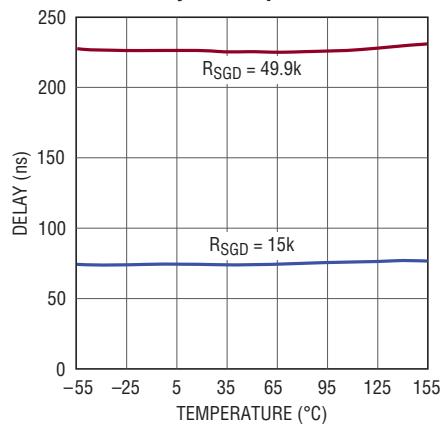

| $t_{SGD}$                          | SGD Delay                                                     | $R_{SGD} = 15\text{k}\Omega$<br>$R_{SGD} = 50\text{k}\Omega$               | 60<br>195    | 75<br>230    | 90<br>265    | ns<br>ns                       |

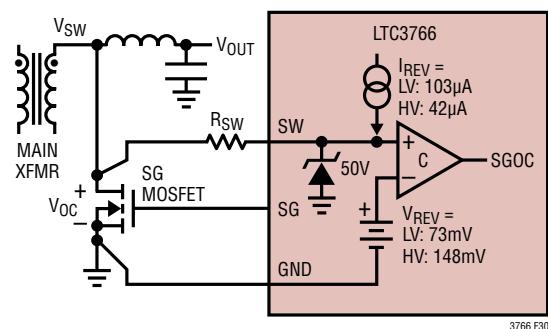

| $V_{SW(\text{REV})}$               | SG Reverse Overcurrent SW Threshold                           | LV MODE<br>HV MODE                                                         | 66<br>140    | 73<br>148    | 79<br>156    | mV<br>mV                       |

| $I_{SW(\text{REV})}$               | SG Reverse Overcurrent Adjust Current                         | LV MODE<br>HV MODE                                                         | -86<br>-34.5 | -103<br>-42  | -120<br>-49  | $\mu\text{A}$<br>$\mu\text{A}$ |

| <b><math>V_{CC}</math> Supply</b>  |                                                               |                                                                            |              |              |              |                                |

| $V_{CCOP}$                         | $V_{CC}$ Operating Voltage Range                              |                                                                            |              | 5            | 10           | V                              |

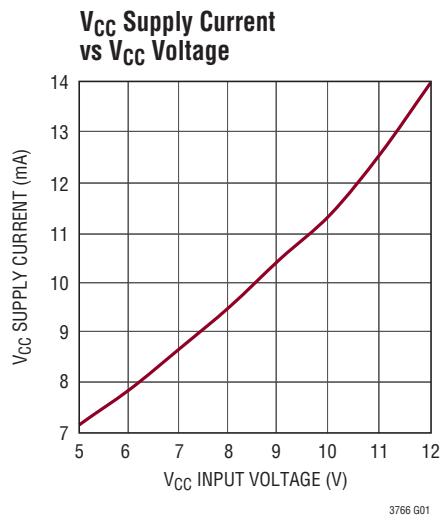

| $I_{CC}$                           | Supply Current<br>Normal Mode<br>Shutdown                     | $V_{FS/SYNC} = V_{CC} = 7\text{V}$ (Note 5)<br>$V_{RUN} = GND$             |              | 5<br>210     |              | $\text{mA}$<br>$\mu\text{A}$   |

| $V_{UVLOR}$                        | UV Lockout Rising                                             | $V_{CC}$ Rising, LV MODE<br>$V_{CC}$ Rising, HV MODE                       | ●<br>●       | 4.6<br>7.7   | 4.7<br>7.9   | 4.8<br>8.1                     |

| $V_{UVLOF}$                        | UV Lockout Falling                                            | $V_{CC}$ Falling, LV MODE<br>$V_{CC}$ Falling, HV MODE                     | ●<br>●       | 3.8<br>6.7   | 3.9<br>6.9   | 4.0<br>7.1                     |

| $V_{REGSD}$                        | REGSD Threshold Voltage                                       | $V_{REGSD}$ Rising                                                         |              |              | 1.21         | V                              |

| $I_{REGSD(C)}$                     | REGSD Charge Current                                          | $V_{REGSD} = 0.7\text{V}$                                                  |              |              | 13           | $\mu\text{A}$                  |

| $I_{REGSD(D)}$                     | REGSD Discharge Current                                       | $V_{REGSD} = 0.7\text{V}$                                                  |              |              | 3            | $\mu\text{A}$                  |

| <b><math>V_{AUX}</math> Supply</b> |                                                               |                                                                            |              |              |              |                                |

| $V_{AUXOP}$                        | $V_{AUX}$ Operating Voltage Range                             |                                                                            |              | 5            | 15           | V                              |

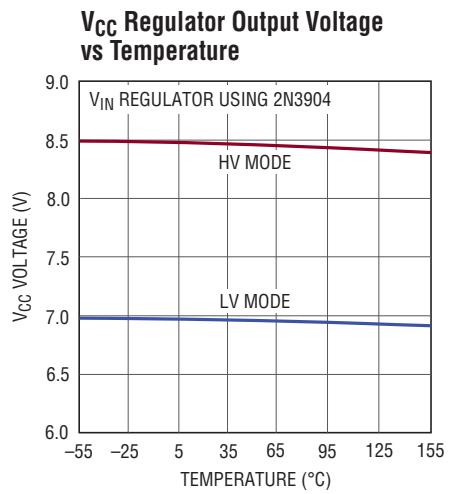

| $V_{CCVAUX}$                       | Regulated $V_{CC}$ Output Voltage                             | $V_{AUX} = 15\text{V}$ , LV MODE<br>$V_{AUX} = 15\text{V}$ , HV MODE       |              | 6.7<br>8.1   | 7.0<br>8.5   | 7.3<br>8.9                     |

| $V_{AUXLR}$                        | $V_{CC}$ Load Regulation                                      | $I_{CC} = 0\text{mA}$ to $120\text{mA}$ , $V_{AUX} = 8\text{V}$ , LV MODE  |              |              | 0.8          | 2                              |

| $V_{AUXSWP}$                       | $V_{AUX}$ Switchover Voltage Rising                           | $V_{AUX}$ Ramping Positive, LV MODE<br>$V_{AUX}$ Ramping Positive, HV MODE |              | 4.50<br>7.65 | 4.70<br>8.00 | 4.88<br>8.35                   |

| $V_{AUXSWN}$                       | $V_{AUX}$ Switchover Voltage Falling                          | $V_{AUX}$ Ramping Negative, LV MODE<br>$V_{AUX}$ Ramping Negative, HV MODE |              | 4.30<br>7.35 | 4.50<br>7.70 | 4.70<br>8.05                   |

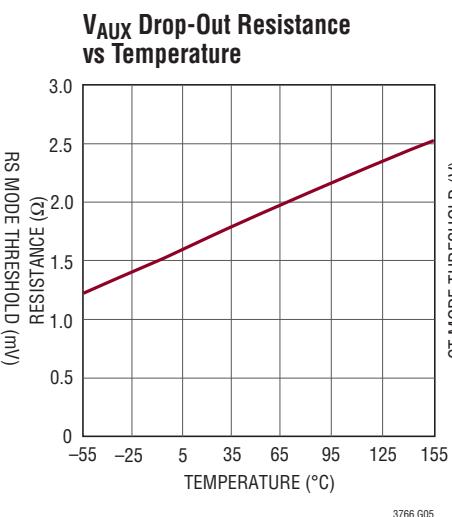

| $R_{AUX}$                          | $V_{AUX}$ Dropout Resistance                                  | $I_{CC} = 120\text{mA}$ , $V_{AUX} = 4.9\text{V}$                          |              |              | 1.7          | 2.5                            |

| $R_{PSL}$                          | $V_{AUX}$ Pre-Switchover Load                                 | $V_{AUX} = 4\text{V}$                                                      |              |              | 920          | $\Omega$                       |

| <b><math>V_{IN}</math> Supply</b>  |                                                               |                                                                            |              |              |              |                                |

| $V_{INOP}$                         | $V_{IN}$ Operating Voltage Range                              |                                                                            |              | 5            | 32           | V                              |

| $V_{INCL}$                         | $V_{IN}$ Clamp Voltage                                        | $I_{VIN} = 2\text{mA}$ , $V_{RUN} = GND$                                   |              | 28           | 30           | 32                             |

| $I_{CLMAX}$                        | $V_{IN}$ Clamp Current Limit                                  | $V_{IN} = 33\text{V}$ , $V_{RUN} = GND$                                    |              | 3.8          | 5.5          | 7.2                            |

| $V_{CCVIN}$                        | Regulated $V_{CC}$ Output Voltage                             | LV MODE (Note 6)<br>HV MODE (Note 6)                                       |              | 6.7<br>8.1   | 7.2<br>8.5   | 7.3<br>8.9                     |

| $I_{IN}$                           | Supply Current<br>Operating<br>Shutdown                       | $V_{FS/SYNC} = V_{CC}$<br>$V_{RUN} = GND$                                  |              |              | 900<br>450   | 1200                           |

| $V_{INUVLO}$                       | $V_{IN}$ Undervoltage Lockout                                 | $V_{IN}$ Rising                                                            |              | 2.6          | 3.2          | 3.8                            |

**ELECTRICAL CHARACTERISTICS**

The ● denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^\circ\text{C}$ . (Note 2)  $V_{IN} = 15\text{V}$ ,  $GND = PGND = 0\text{V}$ , unless otherwise noted.

| SYMBOL                                  | PARAMETER                           | CONDITIONS                                                             | MIN      | TYP | MAX  | UNITS            |

|-----------------------------------------|-------------------------------------|------------------------------------------------------------------------|----------|-----|------|------------------|

| <b>Oscillator and Phase-Locked Loop</b> |                                     |                                                                        |          |     |      |                  |

| $I_{FS/SYNC}$                           | FS/SYNC Pin Sourcing Current        |                                                                        |          | 20  |      | $\mu\text{A}$    |

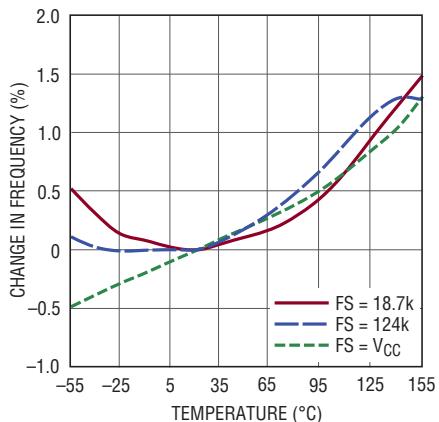

| $f_{HIGH}$                              | Oscillator High Frequency Set Point | $V_{FS/SYNC} = V_{CC}$                                                 | 234      | 275 | 316  | $\text{kHz}$     |

| $\Delta f (R_{FS/SYNC})$                | Oscillator Resistor Set Accuracy    | $18.75\text{k}\Omega < R_{FS/SYNC} < 125\text{k}\Omega$                | ●<br>-12 | 12  |      | %                |

| $f_{PLL(RANGE)}$                        | PLL Sync Frequency Range            |                                                                        | 100      |     | 500  | $\text{kHz}$     |

| <b>Differential Amplifier</b>           |                                     |                                                                        |          |     |      |                  |

| $A_{DA}$                                | Gain                                | $1.5\text{V} \leq V_{SOUT} \leq 15\text{V}$ , $V_{IN} = 20\text{V}$    | 0.99     | 1   | 1.01 | $\text{V/V}$     |

| $CMRR_{DA}$                             | Common Mode Rejection Ratio         | $V_{IN} = 20\text{V}$                                                  |          | 75  |      | $\text{dB}$      |

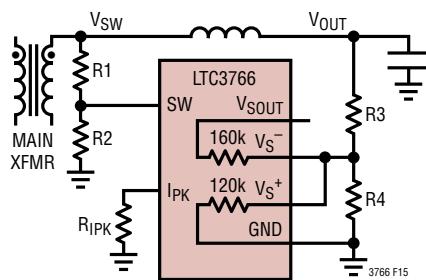

| $R_{INP}$                               | $V_S^+$ Input Resistance            | $V_{IN} = 20\text{V}$                                                  |          | 120 |      | $\text{k}\Omega$ |

| $R_{INM}$                               | $V_S^-$ Input Resistance            | $V_{IN} = 20\text{V}$                                                  |          | 160 |      | $\text{k}\Omega$ |

| $I_{OH}$                                | Output Sourcing Current             | $V_{IN} = 20\text{V}$ , $V_S^+ = 5\text{V}$ , $V_{SOUT} = 2.5\text{V}$ | ●<br>0.8 | 3.0 |      | $\text{mA}$      |

| $V_{IN-V_{OHST}}$                       | Output High Fault Threshold         | $V_S^+$ Rising                                                         |          | 1.2 | 1.5  | $\text{V}$       |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3766E is guaranteed to meet specifications from  $0^\circ\text{C}$  to  $85^\circ\text{C}$  with specifications over the  $-40^\circ\text{C}$  to  $125^\circ\text{C}$  operating junction temperature range assured by design, characterization and correlation with statistical process controls. The LTC3766I is guaranteed over the  $-40^\circ\text{C}$  to  $125^\circ\text{C}$  operating junction temperature range, the LTC3766H is guaranteed over the  $-40^\circ\text{C}$  to  $150^\circ\text{C}$  operating junction temperature range, and the LTC3766MP is tested and guaranteed over the  $-55^\circ\text{C}$  to  $150^\circ\text{C}$  operating junction temperature range. High junction temperatures degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than  $125^\circ\text{C}$ . Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

**Note 3:**  $T_J$  is calculated from the ambient temperature,  $T_A$ , and power dissipation,  $P_D$ , according to the following formula:

$$T_J = T_A + (P_D \cdot \theta_{JA} \text{ } ^\circ\text{C/W})$$

where  $\theta_{JA}$  is  $95^\circ\text{C/W}$  for the SSOP and  $43^\circ\text{C/W}$  for the QFN package.

**Note 4:** The LTC3766 is tested in a feedback loop that servos  $V_{FB}$  to a voltage near the internal  $0.6\text{V}$  reference voltage to obtain the specified  $ITH$  voltage ( $V_{ITH} = 1.2\text{V}$ ).

**Note 5:** Operating supply current is measured in test mode. Dynamic supply current is higher due to the internal gate charge being delivered at the switching frequency. See Typical Performance Characteristics.

**Note 6:** The  $V_{IN}$  Regulator employs an external pass device to produce the regulated  $V_{CC}$  output voltage. The LTC3766 is tested using a 2N3904 NPN transistor as an external pass device.

**Note 7:** Guaranteed by design.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

Oscillator Frequency vs Temperature

FB Voltage vs Temperature

SGD Delay vs Resistance

FGD Delay vs Resistance

SGD Delay vs Temperature

FGD Delay vs Temperature

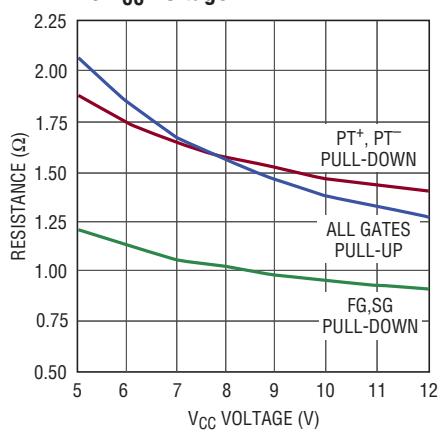

Gate Driver On-Resistance vs V<sub>CC</sub> Voltage

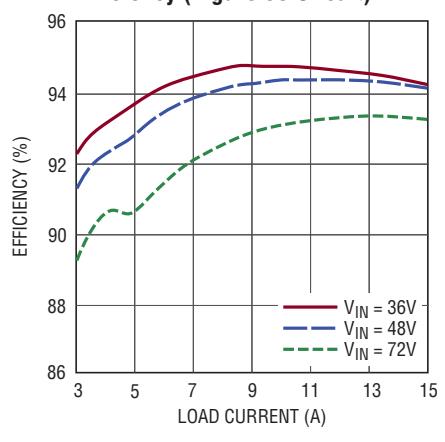

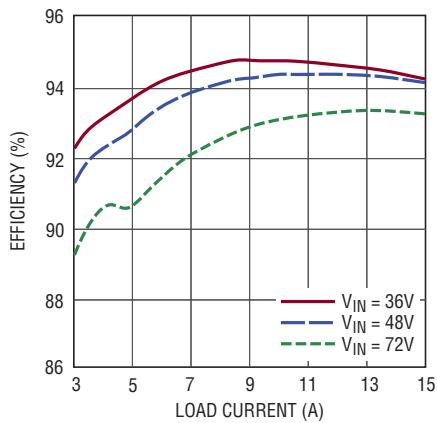

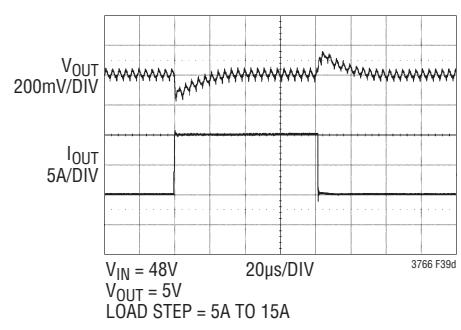

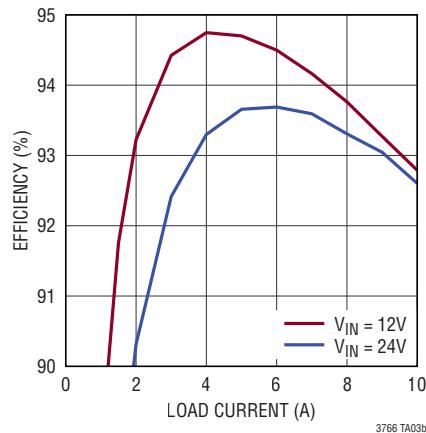

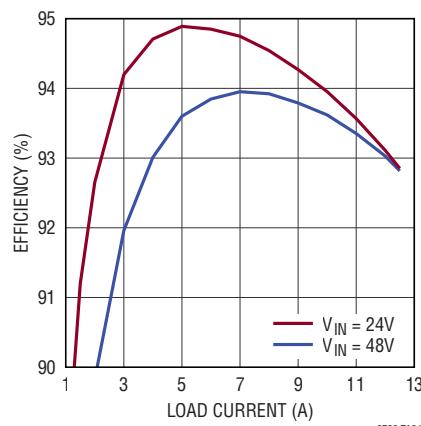

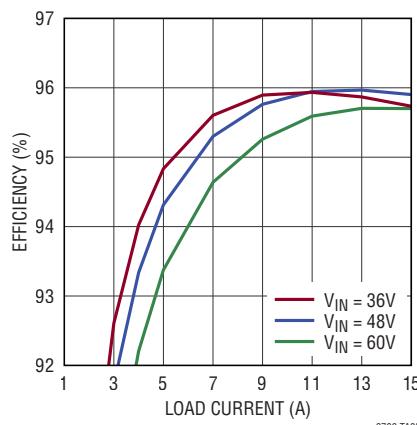

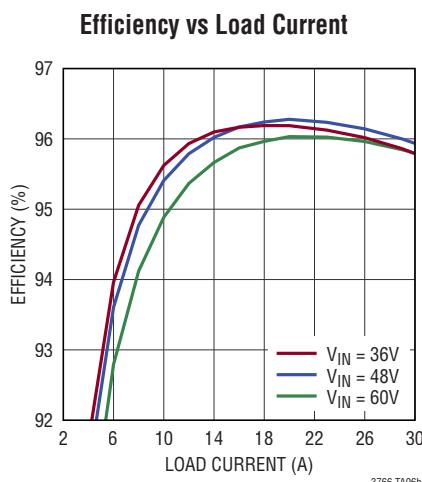

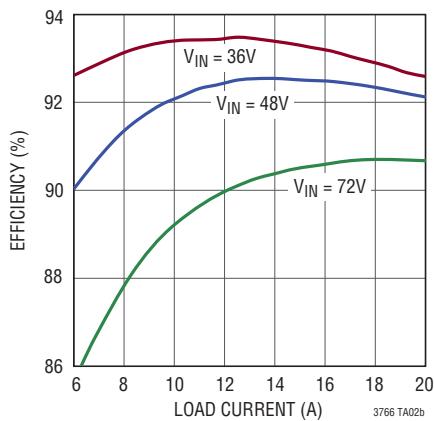

Efficiency (Figure 39 Circuit)

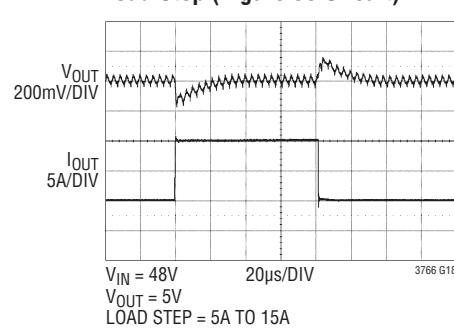

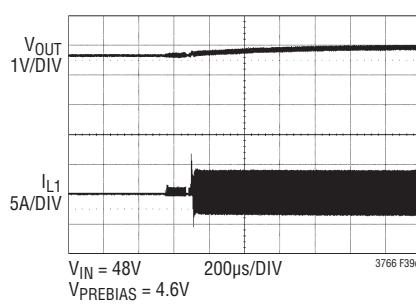

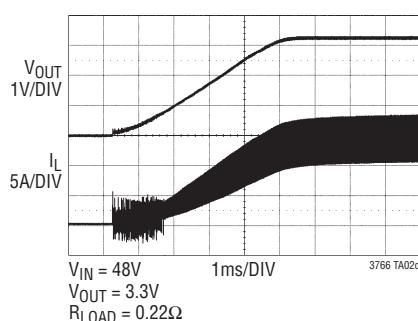

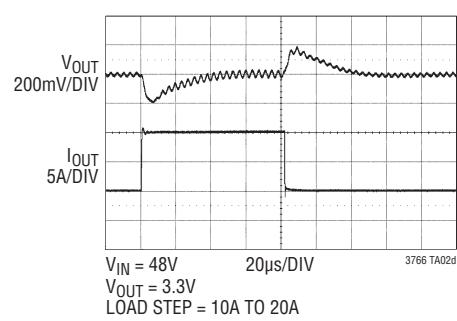

Load Step (Figure 39 Circuit)

## PIN FUNCTIONS (SSOP/QFN)

**SG (Pin 1/Pin 26):** Gate Drive for the Synchronous MOSFET.

**FG (Pin 2/Pin 27):** Gate Drive for the Forward MOSFET.

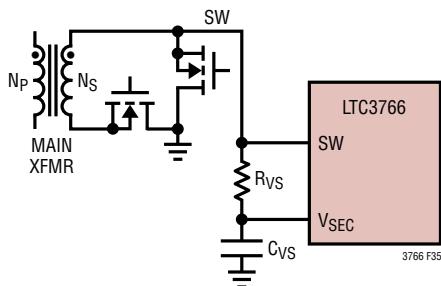

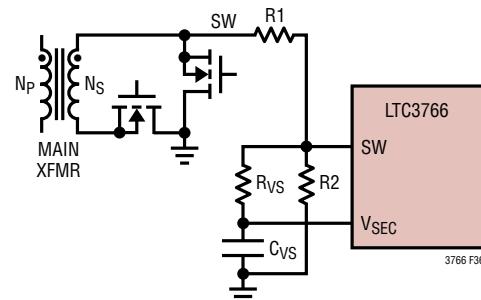

**V<sub>SEC</sub> (Pin 3/Pin 28):** Volt-Second Limit. Connect a resistor from SW to V<sub>SEC</sub>, and a capacitor from V<sub>SEC</sub> to GND to set the maximum volt-second product that is applied to the main power transformer. The PWM on-time is terminated when the V<sub>SEC</sub> voltage exceeds the internally generated threshold. Tie to GND if not used.

**MODE (Pin 4/Pin 1):** For normal isolated applications using the LTC3765, tie to either GND or V<sub>CC</sub> to set the operating voltage to either low voltage or high voltage modes respectively, as needed to drive the gates of the synchronous and forward MOSFETs. For nonisolated applications, tie to ground through either a 100k or 50k resistor to activate standalone mode (for low voltage or high voltage operation respectively). In this mode, the PT<sup>+</sup> pin may be directly connected to the gate of a primary-side MOSFET, and a reference clock signal is generated on the PT<sup>-</sup> pin. In standalone mode, the FGD pin is ignored and the associated delay is set adaptively.

**PHASE (Pin 5/Pin 2):** Control Input to the Phase Selector. This pin determines the phasing of the internal controller CLK relative to the synchronizing signal at the FS/SYNC pin.

**FB (Pin 6/Pin 3):** The Inverting Input of the Main Loop Error Amplifier. Tie to V<sub>CC</sub> or other voltage greater than 2.5V to enable slave mode in PolyPhase applications.

**ITH (Pin 7/Pin 4):** The Output of the Main Loop Error Amplifier. Place compensation components between the ITH pin and GND.

**RUN (Pin 8/Pin 5):** Run Control Input. Holding this pin below 1.22V will shut down the IC and reset the soft-start and REGSD pins to 0V.

**SS (Pin 9/Pin 6):** Soft-Start Inputs. A capacitor to ground sets the ramp time of the output voltage.

**I<sub>PK</sub> (Pin 10/Pin 7):** Peak Current Limit Inductor Ripple Cancellation. This pin is used to adjust the peak current limit based on the amount of inductor current ripple, thereby providing a constant average output current during current limit. Place a resistor to GND that is proportional to the main output inductor. Leave this pin floating for constant peak current limit. Minimize parasitic capacitance on this pin.

**V<sub>SOUT</sub>, V<sub>S</sub><sup>+</sup>, V<sub>S</sub><sup>-</sup> (Pins 11, 12, 13/Pins 8, 9, 10):** V<sub>SOUT</sub> is the output of a precision, unity-gain differential amplifier. Tie V<sub>S</sub><sup>+</sup> and V<sub>S</sub><sup>-</sup> to the output of the main DC/DC converter to achieve true remote differential sensing. Also, V<sub>S</sub><sup>+</sup> is used for directly sensing the output voltage for inductor ripple cancellation. Do not exceed the output sourcing current specification on the V<sub>SOUT</sub> pin or a fault will be generated. See the Applications Information section for details.

**GND (Pin 14/Exposed Pad Pin 29):** Signal Ground and Kelvin Sense for SG Reverse Overcurrent. Connect to power ground at the source of the synchronous MOSFET. The exposed pad must be soldered to PCB ground for rated thermal performance.

**FS/SYNC (Pin 15/Pin 12):** Combination Frequency Set and Sync Pin. Tie to V<sub>CC</sub> to run at 275kHz. Place a resistor to ground at this pin to set the frequency between 75kHz and 500kHz. To synchronize, drive this pin with a clock signal to achieve PLL synchronization from 100kHz to 500kHz. Sources 20 $\mu$ A of current.

**REGSD (Pin 16/Pin 13):** Regulator Shutdown Timer. Place a capacitor to ground to limit the time allowed for the high voltage linear regulator controller to operate. When the REGSD voltage exceeds 1.21V, the linear regulator is shut down. This pin sources 13 $\mu$ A of current when the linear regulator is active.

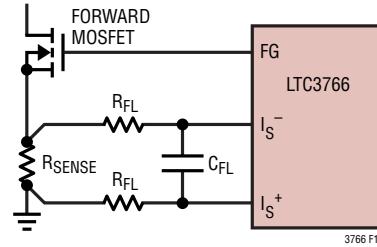

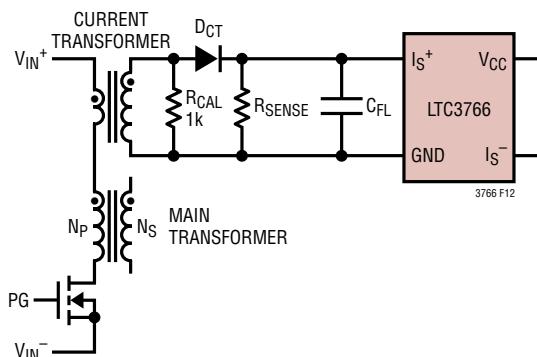

**I<sub>S</sub><sup>-</sup> (Pin 17/Pin 14):** Negative Input to the Current Sense Circuit. Connect to the negative end of a low side current sense resistor. When using a current sense transformer, tie this pin to V<sub>CC</sub> for single-ended sensing on I<sub>S</sub><sup>+</sup> with a higher maximum trip level.

**I<sub>S</sub><sup>+</sup> (Pin 18/Pin 15):** Positive Input to the Current Sense Circuit. Connect to the positive end of a low side current sense resistor or to the output of a current sense transformer.

**SGD (Pin 19/Pin 16):** Synchronous Gate Rising Edge Delay. A resistor to GND sets the delay from primary gate turn-off (PT<sup>+</sup> falling) to SG rising (and FG falling). This delay is used to optimize the dead time between the turn-off of the primary-side MOSFET and the turn-on of SG. Tie SGD to GND to set this delay adaptively based on the falling edge of the SW pin voltage. See Setting the Gate Driver Delays in the Applications Information section.

## PIN FUNCTIONS (SSOP/QFN)

**FGD (Pin 20/Pin 17):** Forward Gate Rising Edge Delay. A resistor to GND sets the delay from  $PT^+$  rising to FG rising (and SG falling). This delay is used to optimize the dead time between the turn-off of SG and the turn-on of the primary-side MOSFET. In standalone mode (100k or 50k resistor on MODE), this dead time is set adaptively and the FGD pin can be grounded. See Setting the Gate Driver Delays in the Applications Information section.

**NDRV (Pin 21/Pin 18):** Drive Output for the External Pass Device of the High Voltage Linear Regulator Controller. Connect to the base (NPN) or gate (MOSFET) of an external N-type device. Tie to  $V_{CC}$  pin if only using the internal LDO ( $V_{AUX}$  pin).

**$V_{IN}$  (Pin 22/Pin 19):** Connect to a higher voltage bias supply when using the linear regulator controller. The  $V_{IN}$  pin supplies bias to the internal standby and monitoring circuits, the linear regulator controller, and the differential amplifier. Tie to  $V_{AUX}$  pin if only using the internal LDO.

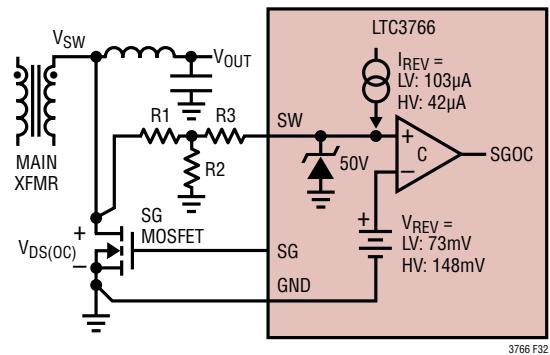

**SW (Pin 23/Pin 20):** Connect (Kelvin) to the drain of the synchronous MOSFET. This input is used for adaptive shoot-through prevention and leading-edge blanking, monitoring the high level SW node voltage and SG reverse-current protection. When SW is high, the voltage on this pin is internally measured for use in the inductor ripple cancellation and volt-second limit circuits. When SW is low and SG is high, this pin sources a small current and is used for SG reverse overcurrent protection. A resistor can be placed between the SW pin and the drain of the synchronous MOSFET to adjust the SG reverse-over current threshold. The SW pin is internally clamped to 50V.

**$V_{AUX}$  (Pin 24/Pin 21):** Auxiliary Power Input. This is the power input to an internal LDO that is connected to  $V_{CC}$ . Whenever  $V_{AUX}$  is greater than 4.7V (or 8V for high voltage mode), this LDO will supply power to  $V_{CC}$ , bypassing the main linear regulator that is powered from  $V_{IN}$ . See  $V_{AUX}$  Connection in the Applications Information section. Do not exceed 16V on the  $V_{AUX}$  pin.

**$PT^-, PT^+$  (Pin 25, 26/Pin 22, 23):** Pulse Transformer Driver Outputs. For most applications, these connect to a pulse transformer through a series DC-blocking capacitor. The PWM information is multiplexed together with DC power and sent through the pulse transformer to the primary side. The PWM signal is then decoded by the LTC3765 active clamp forward controller and gate driver. In standalone mode (100k or 50k resistor on MODE), the  $PT^+$  pin has a standard PWM signal and may be directly connected to the gate of a primary-side MOSFET, while a reference clock is generated on the  $PT^-$  pin.

**PGND (Pin 27/Pin 24):** Gate Driver Ground Pin. Connect to power ground at the source of the synchronous MOSFET.

**$V_{CC}$  (Pin 28/Pin 25):** Main  $V_{CC}$  Input for All Driver and Control Circuitry.

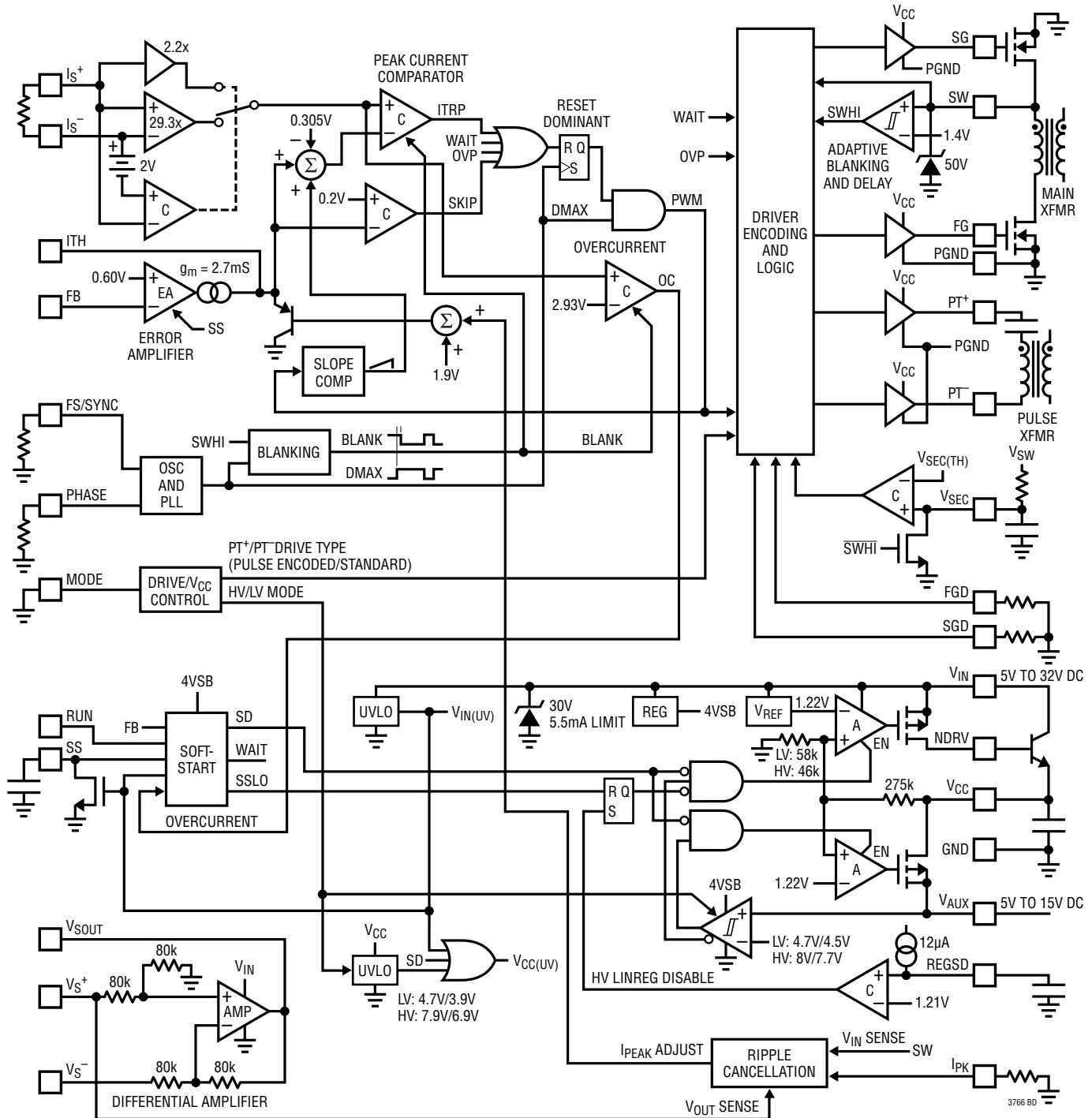

## BLOCK DIAGRAM

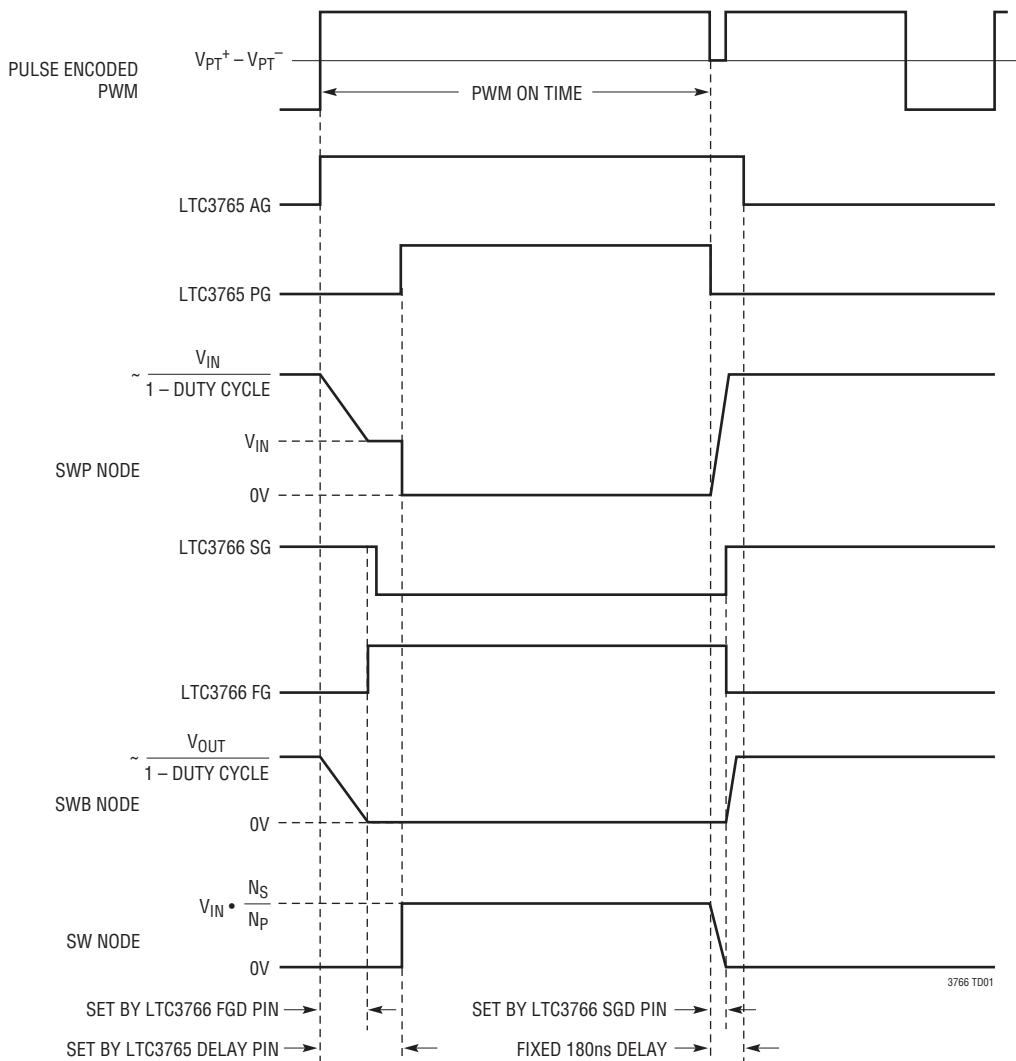

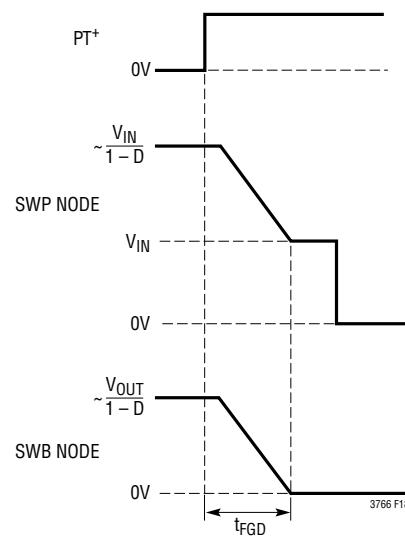

## TIMING DIAGRAM

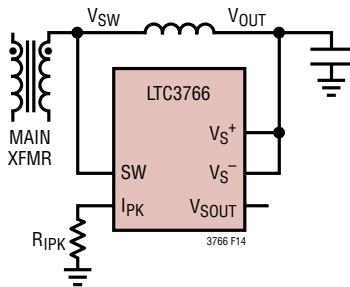

Figure 1. Reference Schematic for Timing Diagram

## OPERATION

The LTC3766 is a secondary-side PWM controller designed for use in a forward converter with active clamp reset and synchronous rectification. When used in conjunction with the LTC3765 active-clamp forward controller and gate driver, it forms a highly efficient and robust isolated power supply with a minimum number of external components. By making use of a secondary-side control architecture, the LTC3766 is able to provide exceptional transient response while directly monitoring the load to ensure that both output voltage and output current are precisely controlled. This architecture provides superior performance and greater simplicity, and is particularly well suited to high power battery charger applications.

### Self-Starting Start-Up

In most applications, the LTC3766 will be used with the LTC3765 to create a self-starting forward converter with secondary-side control. Since there is initially no bias voltage available on the secondary side, the LTC3765 must manage the start-up in an open-loop fashion on the primary side. When power is first applied on the primary side, the LTC3765 begins an open-loop soft-start using its own internal oscillator. Power is supplied to the secondary by switching the main primary-side MOSFET with a gradually increasing duty cycle from 0% to 70%, as controlled by the rate of rise of the voltage on the SSFLT pin. On the secondary side, bias voltage can be generated directly from the main transformer using a peak charge circuit, or other technique as appropriate. When the LTC3766 has adequate voltage to satisfy its start-up requirements, it provides duty cycle information through the pulse transformer as shown in Figure 2. The LTC3765 detects this signal and transfers control of the gate drivers to the LTC3766, which continues the soft-start of the output voltage. Typically, this hand-off from primary to secondary occurs when the output voltage is less than one half of its final level. The LTC3765 then turns off the linear regulator and, through an on-chip rectifier, extracts bias power for the primary-side MOSFETs from this signal.

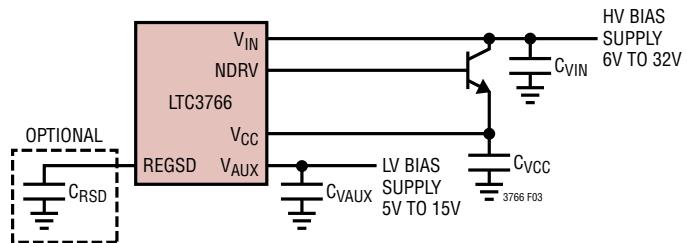

### Linear Regulators

In general, the bias voltage generated on the secondary side is higher than the level desired for operation of the forward and synchronous MOSFETs. Consequently, the LTC3766 contains a high voltage linear regulator controller as well as

a 15V  $V_{AUX}$  bypass regulator with an internal PMOS, either of which can be used to regulate the voltage on the  $V_{CC}$  pin. The linear regulator controller is used by tying the NDRV pin to the base or gate of an external N-type pass device. The LTC3766  $V_{IN}$  pin provides bias to the linear regulator controller as well as to internal standby and monitoring circuitry. If adequate voltage is detected on the  $V_{AUX}$  pin, then the  $V_{AUX}$  bypass regulator will be activated and the high voltage linear regulator controller will be shut down to reduce power loss. Alternatively, if only the  $V_{AUX}$  regulator is needed, then the NDRV pin can be tied off to  $V_{CC}$ , while  $V_{IN}$  is tied to  $V_{AUX}$ . This flexible arrangement of two linear regulators allows for the convenient and efficient generation of  $V_{CC}$  bias voltage for a wide array of applications.

Using the MODE pin, the output voltage of both linear regulators can be set to either 7V or 8.5V, depending on the level needed to drive the gates of the forward and synchronous MOSFETs. Note that the undervoltage lock-out (UVLO) set points as well as  $V_{AUX}$  switchover levels are adjusted along with the  $V_{CC}$  regulation levels. This ensures that the MOSFETs are only switched when there is adequate gate drive voltage.

### Run Control and Soft-Start

The main on/off control for the LTC3766 is the RUN pin. This pin features precision thresholds with both internal and externally adjustable hysteresis. This pin can be used to monitor the secondary-side bias voltage or main output voltage, thereby controlling the point at which hand-off from primary to secondary side occurs. Alternatively, it can be driven directly with a control signal. In nonisolated applications when the LTC3766 is used standalone, this pin can be used as an undervoltage lockout by monitoring the main power supply input voltage. See Nonisolated Applications in the Applications Information section for details.

The LTC3766 will begin a soft-start sequence when the RUN pin is high, adequate voltage is present on both the  $V_{IN}$  and  $V_{CC}$  pins, and switching is detected on the SW pin. Note that the LTC3766 must see switching on the SW pin prior to initiating a soft-start sequence to ensure that the LTC3765 is ready for control hand-off. The soft-start sequence begins by first measuring the voltage on the FB pin and then rapidly pre-setting the soft-start capacitor voltage to a level that corresponds to the output voltage,

## OPERATION

$V_{OUT}$ . This is done to provide a smooth ramp on the output voltage as control is transferred from primary to secondary, as well as to avoid any unnecessary start-up delay. Once the soft-start capacitor has been pre-set to the appropriate level, the LTC3766 then sends a brief sequence of pulses through the pulse transformer to establish a communication lock between the LTC3766 and the LTC3765. At this point, the LTC3766 assumes control of the primary-side MOSFETs, and the soft-start capacitor begins charging with a constant current of  $5\mu A$ , continuing the soft-start of the main output voltage. Note that the soft-start voltage is used to limit the effective level of the reference into the error amplifier. This technique maintains closed-loop control of the output voltage during the secondary-side soft-start interval.

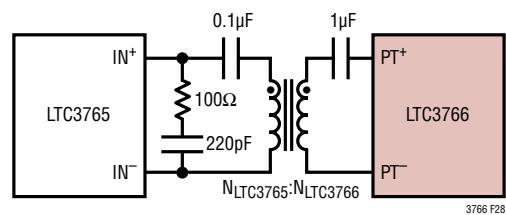

### Gate Drive Encoding

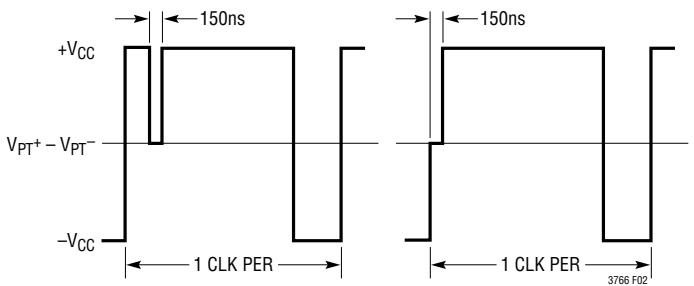

Since the LTC3766 controller normally resides on the secondary side of an isolation barrier, communication to the primary-side gate driver must be done through a small pulse transformer. A common scheme for communicating gate drive (PWM) information makes use of short pulses and relies on receiver latches to “remember” whether power MOSFETs should be either on or off. However, this system is prone to get into the wrong state, and has difficulty distinguishing a loss of signal from a legitimate zero duty cycle signal. To alleviate these concerns, the LTC3766 uses a proprietary gate drive encoding scheme that reliably maintains constant contact across the isolation barrier without introducing any delay.

The LTC3766 encodes PWM information onto the  $PT^+$  and  $PT^-$  outputs, which are in turn connected to a small pulse transformer through a DC-blocking capacitor. These outputs are driven in a complementary fashion, with a constant 79% duty cycle. This results in a stable volt-second balance, so that the signal amplitude transferred across the pulse transformer is constant. As shown in Figure 2, the beginning of the interval when  $(V_{PT^+} - V_{PT^-})$  is positive approximately coincides with the turn-on of the main primary-side MOSFET. Likewise, the beginning of the interval when  $(V_{PT^+} - V_{PT^-})$  is negative coincides with the maximum duty cycle (forced turn-off of main primary-side MOSFET). At the appropriate time during the positive interval, the end of the “on” time (PWM going low) is

signaled by briefly applying a zero-volt differential across the pulse transformer. In the event that a zero duty-cycle signal needs to be sent, this is accomplished naturally by placing the zero-voltage differential at the beginning of the positive interval. In this manner, any duty cycle from 0% to the maximum of 79% can be sent across the pulse transformer without delay. Figure 2 illustrates the operation of this encoding scheme.

Figure 2: Gate Drive Encoding Scheme

(MODE = GND or MODE =  $V_{CC}$ )

On the primary side, the LTC3765 receives the signal from the pulse transformer through a DC restoring capacitor. After communication lock has been established between the two parts, the LTC3765 extracts clock and duty cycle information from the signal and uses it to control its gate driver outputs. Note that, except for a tiny pulse, this scheme is constantly applying a differential voltage across the pulse transformer. Therefore, the LTC3765 can almost instantly detect a loss of signal and shut off the power MOSFETs.

### Forward Converter and Main Loop Operation

Once communication lock has been established between the LTC3766 and the LTC3765, the LTC3766 will have control over the switching of the primary-side MOSFETs. During normal operation, the main primary-side MOSFET (connected to PG on the LTC3765) is turned on somewhat after the forward MOSFET on the secondary side. This applies the input voltage across the transformer, causing the SW node on the secondary side to rise. Since the SW node voltage is greater than the output voltage, the inductor current ramps upward. When the current in the inductor has ramped up to the peak value as commanded by the voltage on the ITH pin, the current sense comparator trips, turning off the primary-side MOSFET. After a short delay,

## OPERATION

the forward MOSFET is turned off and the synchronous MOSFET is turned back on, causing the inductor current to ramp back downwards. At the next rising edge of the LTC3766 internal clock, the cycle repeats as the synchronous MOSFET is turned off and the forward and main primary-side MOSFETs are again turned on. The LTC3766 error amplifier senses the main output voltage, and adjusts the ITH voltage to obtain the peak inductor current needed to keep the output voltage at the desired regulation level.

In some applications, there can be considerable resistive voltage drops between the main output voltage and the load. To address this, the LTC3766 contains a precision differential amplifier, which can be used to remotely sense a load voltage as high as 15V.

### Current Sensing, Slope Compensation and Blanking

The LTC3766 supports current sensing either with a current sense resistor or with an isolated current transformer. When using a current sense resistor, the  $I_S^+$  and  $I_S^-$  pins operate differentially, and the maximum peak current threshold is approximately 75mV. Normally, the current sense resistor is placed in the source of the forward MOSFET to minimize power loss. If a current transformer is used to sense the primary-side switch current, then the  $I_S^-$  input should be tied to  $V_{CC}$  and the  $I_S^+$  pin to the output of the current transformer. This causes the gain of the internal current sense amplifier to be reduced, so that the maximum peak current threshold is increased to approximately 1V.

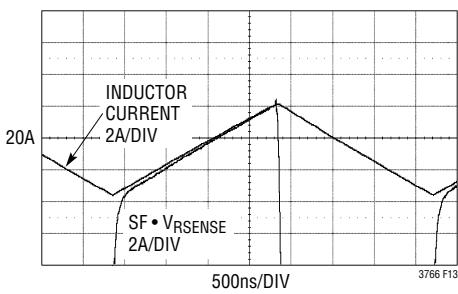

As with any PWM controller that uses constant-frequency peak current control, slope compensation is needed to provide current-loop stability and improve noise margin. The LTC3766 has fixed internal slope compensation. The amount of slope has been chosen to be adequate for a wide range of applications. Normally, the use of slope compensation would have a negative impact on the accuracy of the current limit, but the LTC3766 uses a proprietary circuit to nullify the effect of slope compensation on the current limit performance.

Since the LTC3766 current loop is sensing switch current, leading edge blanking is needed to avoid a current comparator false trip due to the MOSFET turn-on current spike. The LTC3766 uses the voltage on the SW pin (tied to the drain of the synchronous MOSFET) to implement an

adaptive leading-edge blanking of approximately 180ns. The blanking of the current comparator begins only after the voltage on SW has risen above 1.4V. This adaptive blanking is essential because of the potentially long delay from the time that  $PT^+$  rises to the time that the SW node rises, and current begins ramping up in the output inductor. This blanking also minimizes the need for external filtering.

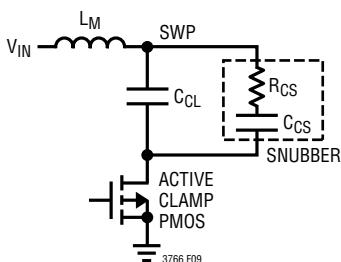

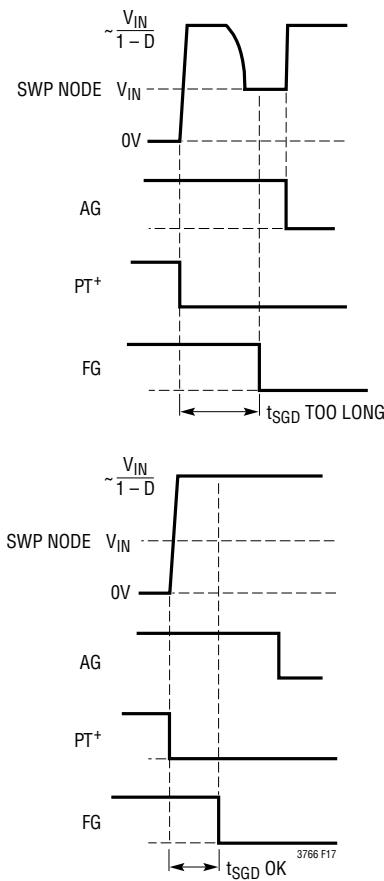

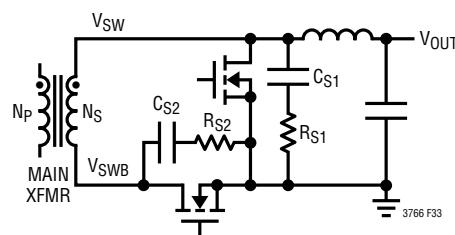

### Gate Driver Delay Adjustment

As in all forward converters, the main transformer core must be properly reset so as to maintain a balanced volt-second product and prevent saturation. This job is handled on the primary side by the LTC3765, which features an active clamp gate driver. The active clamp MOSFET works together with a capacitor to generate an optimal reset voltage for the main transformer. This optimal reset voltage minimizes voltage stress on the main primary-side MOSFET and maximizes the utilization of the power transformer core by reducing the magnetic flux density excursion.

In general, the active clamp MOSFET is switched in a complimentary fashion to the main primary-side MOSFET. Since the active clamp MOSFET is a PMOS, the active clamp gate driver (AG) and the main primary-side gate driver (PG) voltages are therefore “in-phase,” with a programmable overlap time set by the LTC3765 DELAY pin.

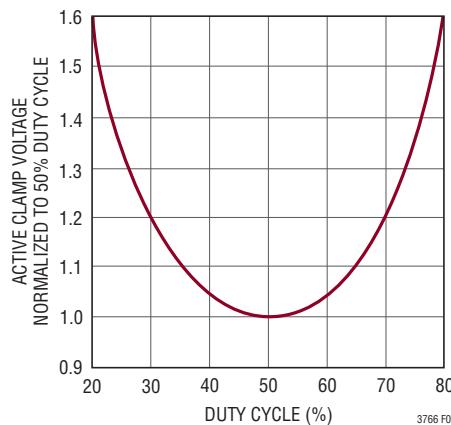

The delay time between the active clamp PMOS turn-off and the primary switch NMOS turn-on is critical for optimizing efficiency. When the active clamp is on, the drain of the primary NMOS, or primary switch node (SWP), is driven to a voltage of approximately  $V_{IN}/(1-D)$  by the main transformer. When the active clamp turns off, the current in the magnetizing inductance of the transformer ramps this voltage linearly down to  $V_{IN}$ . Power loss is minimized by turning on the primary switch when the SWP voltage is at a minimum. A resistor from the LTC3765 DELAY pin to ground sets a fixed time for the PG turn-on delay.

The delay time between the primary switch turn-off and the active clamp turn-on is substantially less critical. When the primary switch turns off, the main transformer leakage inductance is biased with the peak current of the inductor reflected through the transformer. This current drives the voltage across the active clamp PMOS quickly to 0V. Turning on the PMOS after this transition results in

## OPERATION

minimal switching power loss. The LTC3765 active clamp turn on delay is internally fixed to 180ns, which normally achieves zero voltage switching on the active clamp PMOS.

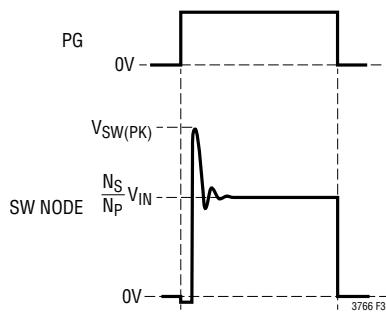

On the secondary side, the turn-on delay of the forward gate (FG) and synchronous gate (SG) MOSFETs are adjusted by the FGD and SGD pins respectively. These delays are set using resistors to GND so as to minimize the dead time (when the load current is being carried by MOSFET body diodes) while avoiding shoot-through with the primary-side MOSFETs. A shoot-through condition exists if either the PG and SG gates, or the AG and FG gates are high at the same time. Note that the SG MOSFET turn-on delay has a minimum limit that is established by the falling edge of the SW node. The SG pin will normally not go high until SW has fallen below 0.5V. After a 180ns timeout, however, the SG pin will go high regardless of the SW voltage. Refer to Delay Resistor Selection in the Applications Information section for more detailed information. In standalone mode (100k or 50k resistor on MODE), the dead time between PG and SG is set adaptively to prevent shoot-through.

### Frequency Setting and Synchronization

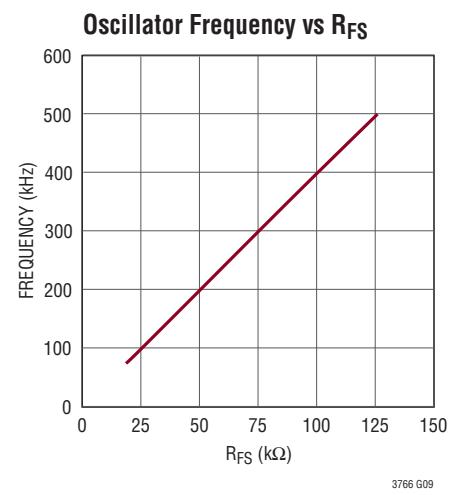

The LTC3766 uses a single pin to set the operating frequency or to synchronize the internal oscillator to a reference clock using and on-chip phase-locked loop (PLL). The FS/SYNC pin sources a 20 $\mu$ A current, and it may be tied to V<sub>CC</sub> for fixed 275kHz operation or have a single resistor to GND to set the switching frequency to  $f_{SW} = 4R_{FS}$ . If a clock signal (>2V) is detected at the FS pin, the LTC3766 will automatically synchronize to the falling edge of this signal using an internal PLL.

### Current Limit and Inductor Ripple Cancellation

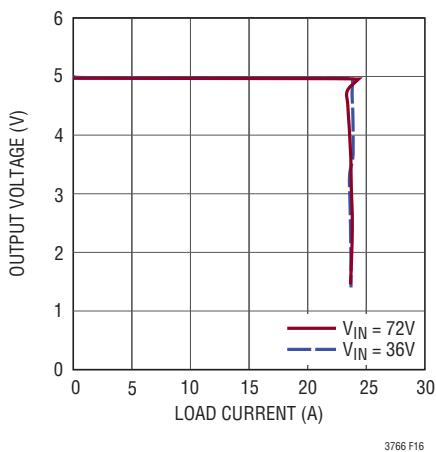

Since the LTC3766 utilizes peak current control, the peak inductor current is limited when the load current demand increases above the current limit set point. The peak current limit is established by an internal clamp on the maximum level of the ITH voltage. The average current, however, will be less than the peak current by an amount equal to one-half of the inductor ripple current. During current limit, this ripple current will change significantly with variations in V<sub>IN</sub>, V<sub>OUT</sub> and switching frequency. Without inductor ripple cancellation, this variation in ripple current would

also result in an average output current that changes significantly, even though the peak current is held at a constant value.

In order to keep the average output current approximately constant during current limit, the LTC3766 cancels the effect of the ripple current by adjusting the value of the peak current limit (or ITH clamp level) in proportion to the amount of inductor ripple current. This is achieved by generating an internal ramp that mimics the inductor current ramp, and then adding the amplitude of this internal ramp to the ITH clamp voltage on a cycle-by cycle basis. During the on time, the slope of the inductor current is given by:

$$\frac{dI_L}{dt} = \frac{V_{SW} - V_S^+}{L}$$

The LTC3766 establishes a voltage on the I<sub>PK</sub> pin of  $(V_{SW} - V_S^+)/15$ , which is one-fifteenth of the voltage across the output inductor during the on-time when SW is high. By choosing a resistor R<sub>IPK</sub> that is proportional to the value of the output inductor (R<sub>IPK</sub> = KL), the current flowing in R<sub>IPK</sub> becomes proportional to the slope of the inductor current:

$$I_{RIPK} = \frac{V_{SW} - V_S^+}{15R_{IPK}} = \frac{V_{SW} - V_S^+}{15KL}$$

During the time when SW is high, the LTC3766 uses the R<sub>IPK</sub> current to create an internal ramp by charging an on-chip capacitor C<sub>RIP</sub>. The slope of this internal ramp voltage is given by:

$$\frac{dV_{RAMP}}{dt} = \frac{I_{RIPK}}{C_{RIP}} = \frac{V_{SW} - V_S^+}{15KLC_{RIP}}$$

The amplitude of this internal ramp is then added to the ITH clamp level dynamically. By choosing the appropriate value of R<sub>IPK</sub>, therefore, the average current during current limit will be essentially independent of changes in ripple current.

As is the case with all DC/DC converters that maintain constant frequency operation, a cycle by cycle current limit is only effective at duty cycles where the on time is greater than the minimum controllable on-time. Under short-circuit conditions, for example, the LTC3766 limits

## OPERATION

the current using a separate overcurrent comparator. When this overcurrent comparator is tripped, the LTC3766 generates a fault followed by a soft-start retry. This hiccup mode overcurrent protection is highly effective at minimizing power losses under short-circuit conditions.

### Direct Flux Limit

In active clamp forward converters, it is essential to establish an accurate limit to the transformer flux density in order to avoid core saturation during load transients or when starting up into a pre-biased output. Although the active clamp technique provides a suitable reset voltage during steady-state operation, the sudden increase in duty cycle caused in response to a load step can cause the transformer flux to accumulate or “walk,” potentially leading to saturation. This occurs because the reset voltage on the active clamp capacitor cannot keep up with the rapidly changing duty cycle. This effect is most pronounced at low input voltage, where the voltage loop demands a greater increase in duty cycle due to the lower voltage available to ramp up the current in the output inductor.

Traditionally, transformer core saturation has been avoided either by limiting the maximum duty cycle of the converter or by slowing down the loop to limit the rate at which the duty cycle changes. Limiting the maximum duty cycle does help the converter avoid saturation for a load step at low input voltage, since the duty cycle maximum is clamped; however, transformer saturation can also easily occur at higher input voltage where the maximum duty cycle clamp is ineffective. Limiting the rate of duty cycle change such that the active clamp capacitor can sufficiently track the duty cycle change also helps to prevent saturation in many situations, but results in a very poor transient response. Neither of these traditional techniques is guaranteed to prevent the transformer from saturating in all situations. For example, saturation can easily occur using these traditional techniques when starting up into a pre-biased output, where the duty cycle can quickly change from 0% to 75%. Moreover, neither of these traditional techniques is able to prevent saturation in the negative direction, which can result from sudden decreases in duty cycle.

The LTC3765 and LTC3766 implement a new unique system for monitoring and directly limiting the flux accumulation in the transformer core. During a reset cycle, when

the active clamp PMOS is on, the magnetizing current is directly measured and limited through a sense resistor in series with the PMOS source. This prevents saturation in the negative direction. When the PMOS turns off and the main NMOS switch turns on, the LTC3765 generates an accurate internal estimate of the magnetizing current based on the sensed input voltage on the LTC3765 RUN pin and transformer core parameters customized to the particular core by a resistor from the LTC3765  $R_{CORE}$  pin to ground. The magnetizing current is then limited during the on-time by this accurate internal approximation. Unlike previous methods, the Direct Flux Limit directly measures and monitors flux accumulation and guarantees that the transformer will not saturate in either direction, even when starting into a pre-biased output. This technique also provides the best possible transient response, as it will temporarily allow very high duty cycles, only limiting the duty cycle when absolutely necessary. Moreover, this technique prevents overcurrent damage to the active clamp PMOS, which is a potentially significant weakness in many active clamp forward converter designs.

### Additional Protection Features

The LTC3766 contains a wide array of protection features, which protect the DC/DC converter in the event that abnormal conditions persist. In general, protection features are either classified as a fault or a limit. When a fault is detected, all switching stops and the LTC3766 initiates a soft-start retry. Faults of this nature include overcurrent, overtemperature, differential amplifier miswire and communication-lock fault.

An overcurrent fault occurs if the peak current exceeds approximately 133% of its normal value during current limit. Note that when inductor ripple cancellation is used, the value of the peak current during current limit will vary with inductor current ripple. The overtemperature fault is set at 165°C, with 20°C of hysteresis. This is helpful for limiting the temperature of the DC/DC converter in the event of some external device failure or other abnormal condition. The differential amplifier wiring fault is generated if the inputs on the differential amplifier are reversed, or if there is not enough voltage on the  $V_{IN}$  pin to support the voltage needed on  $V_{SOUT}$ . This is important to avoid an overvoltage condition on the output.

3766fc

## OPERATION

Finally, since it is essential that the LTC3766 be in constant communication with the LTC3765, a loss of communication lock will also generate a fault. A lock condition is detected by monitoring the SW node voltage, and ensuring that it is both rising and falling as it should in response to the PWM signal being sent to the primary side. If the SW node voltage is not rising and falling in an appropriate manner, than a lock fault is generated. In particular, if the SW node does not rise within approximately 800ns of PT<sup>+</sup> rising, then a fault is immediately generated. Likewise, if the SW node does not fall within approximately 180ns of PT<sup>+</sup> falling, then a fault will also be generated, but only if this condition persists and the LTC3766 is operating at maximum duty cycle.

In addition to the four protection features that generate faults, there are also four protection features that establish a clamp or limit, without generating a fault. First, the LTC3766 contains a precision volt-second clamp. This feature is not needed when the LTC3766 is used in conjunction with the LTC3765, which incorporates the Direct Flux Limit feature. If the LTC3766 is used standalone, however, the volt-second limit can be used by placing a resistor from the SW node to the V<sub>SEC</sub> pin and a capacitor from V<sub>SEC</sub> to GND. When the SW node is low, the capacitor is discharged by an on-chip NMOS. When the SW node is high, the capacitor on V<sub>SEC</sub> is charged. If the capacitor voltage exceeds an internally generated threshold, then the main primary switch will be turned off, thereby limiting the volt-second product applied to the main transformer. To compensate for the exponential nature of the RC charging circuit, the LTC3766 adjusts the threshold of the volt-second comparator according to:

$$V_{SEC(TH)} = 0.6 - \frac{0.16}{V_{SW(HI)}}$$

where V<sub>SW(HI)</sub> is the voltage on the SW pin during the on-time of the primary switch. This keeps the volt-second limit essentially constant for SW node voltages in the range of 2V to 40V.

Second, in the event that the main output voltage exceeds its regulation target by more than 17%, the LTC3766 will detect an overvoltage condition. If this happens, the LTC3766 will immediately turn off the main primary MOSFET and turn on the synchronous MOSFET. This has the effect of

pulling down the output voltage to protect the load from potential damage. Overvoltage protection is not latched, and normal operation is restored when the output voltage has been reduced to within 15% of its regulation level.

Third, the LTC3766 contains an adjustable synchronous MOSFET reverse overcurrent. This is accomplished by monitoring the SW voltage when the synchronous MOSFET is on (SG pin is high). If the voltage on SW exceeds a pre-determined threshold, then the synchronous MOSFET will be turned off, protecting it from potentially damaging current levels. This SW threshold for reverse overcurrent detection can be reduced by placing a resistor in series with the SW pin, which sources a current when the SG pin is high. Note that the SG reverse overcurrent threshold and the SW pin source current are adjusted based on the state of the MODE pin. This is done to accommodate the use of either high voltage or low voltage MOSFETs, which normally have significantly different on resistances. In an overvoltage condition, the SG reverse overcurrent will override the overvoltage protection and force SG low, essentially regulating the reverse SG MOSFET current at a high level while the overvoltage condition persists. However, the SG reverse overcurrent is only active after the LTC3766 has achieved communication lock.

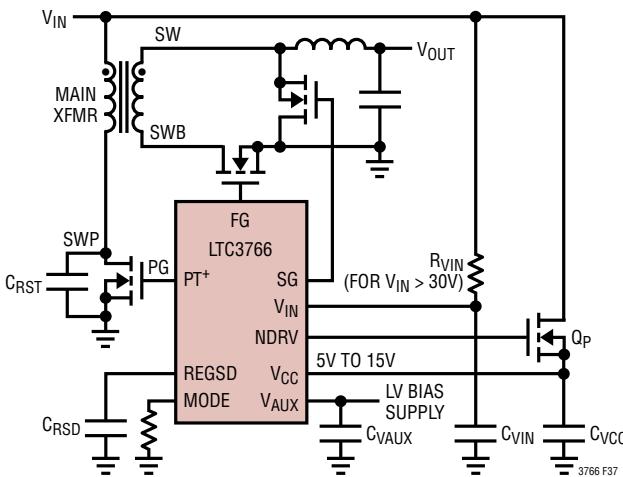

Finally, the REGSD pin can be used to limit the amount of time that the high voltage linear regulator controller is active. This is particularly useful when the LTC3766 is used standalone in a nonisolated forward converter. In this application, the pass device of the linear regulator controller may be dissipating considerable power. When the linear regulator controller is active, the REGSD pin sources a 13µA current. If a capacitor from REGSD to GND charges to a voltage greater than 1.21V, then linear regulator controller is disabled.

### Gate Driver Mode Control

In addition to being used in conjunction with the LTC3765, the LTC3766 can also be used standalone in a nonisolated forward converter application. In this case, the MODE pin can be used to disable gate drive encoding by tying MODE to GND through either a 100k (for V<sub>CC</sub> = 7V operation) or 50k (for V<sub>CC</sub> = 8.5V operation) resistor. This causes a normal PWM signal to appear on PT<sup>+</sup> and a reference clock to appear on PT<sup>-</sup>.

## APPLICATIONS INFORMATION

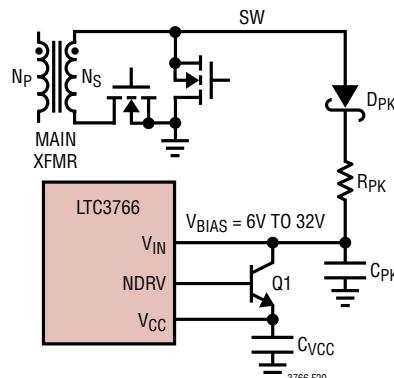

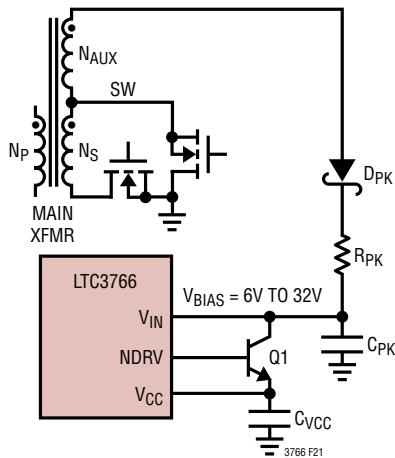

### Secondary-Side Bias and Start-Up

In most applications, the LTC3766 will receive its bias voltage from a supply that is generated on the secondary side. The manner in which the secondary bias is generated depends upon the output voltage as well as the variation in the input voltage of the DC/DC converter. In all applications, however, the secondary bias must always come up before the output reaches the regulation level. This is essential to avoid an overvoltage condition on the output, since the initial start-up is performed from the primary side in an open-loop fashion. See Generating the Secondary-Side Bias for more information.

Note that the LTC3766 will not begin a soft-start sequence and initiate switching until the RUN pin is high, adequate voltage is present on both the  $V_{IN}$  and  $V_{CC}$  pins, and switching is detected on the SW pin. The LTC3766 looks for switching on the SW pin to ensure that the LTC3765 is active and ready for control hand-off. For switching to be detected, the SW node waveform must have at least eight consecutive pulses in the range of 50kHz to 700kHz. The SW node waveform must also have a peak that is greater than 1.4V and a valley that is less than 0.5V. In standalone mode, the LTC3766 begins the soft-start sequence without waiting for a switching waveform to be detected on the SW pin.

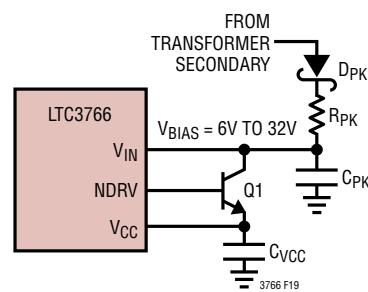

### Linear Regulator Operation

The LTC3766 contains two linear regulators that are used to regulate the available bias voltage down to a level suitable for driving MOSFETs. If the bias supply voltage is greater than 15V, then the high voltage linear regulator controller may be used. This makes use of an external N-type pass device. Place a capacitor of 0.22 $\mu$ F or greater on  $V_{IN}$  and 1 $\mu$ F or greater on  $V_{CC}$ . If the bias supply connected to the  $V_{IN}$  pin has a relatively high output impedance, it may be necessary to use a larger capacitor on  $V_{IN}$  to prevent the  $V_{IN}$  pin voltage from dropping when the  $V_{CC}$  capacitor is being charged. The  $V_{CC}$  charge rate during linear regulator start-up is set by the LTC3766 to approximately 0.5V/ $\mu$ s, which will create a charging current of  $(0.5 \cdot 10^6) C_{VCC}$ . Care should be taken to ensure that this charging current

does not exceed the SOA of the N-type pass device, particularly when operating at higher  $V_{IN}$  voltages. The  $V_{CC}$  regulation level can be set to either 7V or 8.5V as desired using the MODE pin. See the section on  $V_{CC}$  and Drive Mode Selection for details.

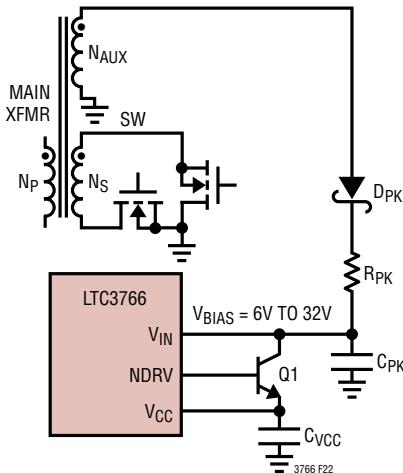

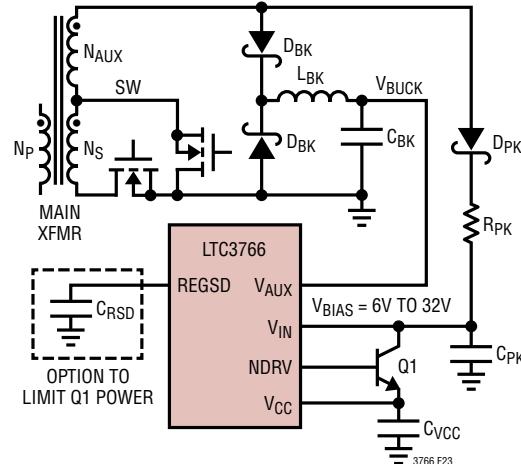

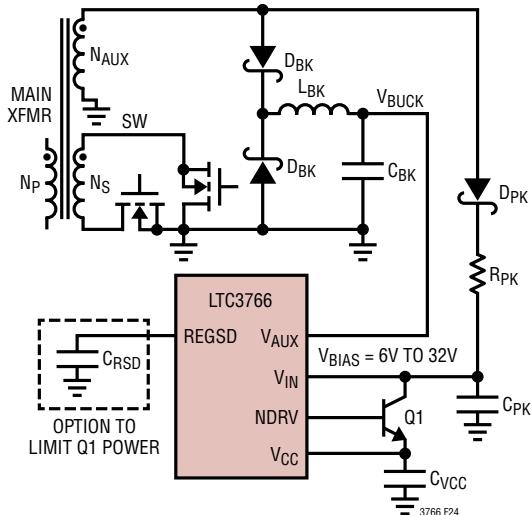

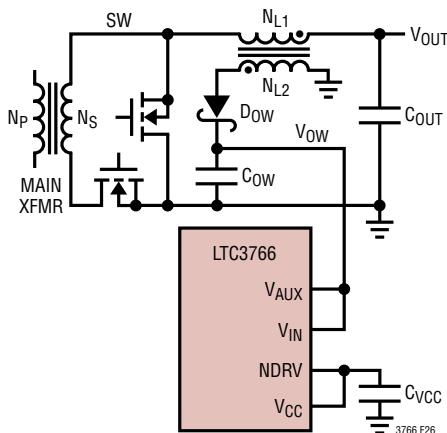

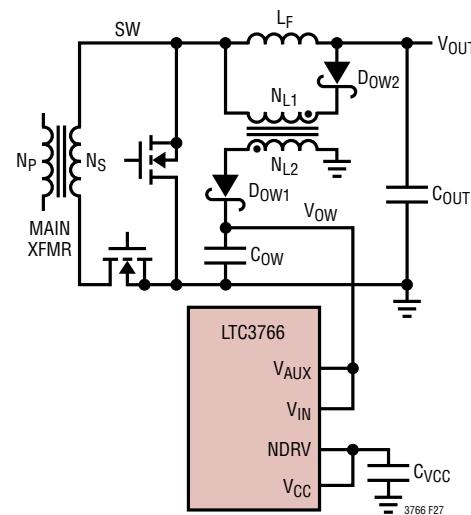

The LTC3766 also contains a 15V internal bypass LDO. If the voltage on the  $V_{AUX}$  pin exceeds the  $V_{AUX}$  switchover threshold, then the high voltage linear regulator is disabled, and an internal PMOS-pass LDO uses the  $V_{AUX}$  voltage to supply power to  $V_{CC}$ . This allows the high voltage linear regulator to be used for initial start-up and the higher efficiency bypass LDO to be used during normal operation. Figure 3 illustrates such a configuration that uses both linear regulators.

If the voltage on the  $V_{AUX}$  pin is below the switchover threshold, then the  $V_{AUX}$  pin is internally loaded with a resistance of approximately 920 $\Omega$ . This internal load is removed after the  $V_{AUX}$  regulator is enabled, and is used to ensure that the  $V_{AUX}$  supply is reasonably stiff before the bypass regulator is activated.

In some cases, it is desirable to use the high voltage linear regulator only briefly during start-up, so as to limit the temperature rise in the external pass device. To accomplish this, place a capacitor on the REGSD pin to ground (see Figure 3) such that:

$$C_{RSD} = \frac{t_{HVREG} (13\mu A)}{1.21V}$$

where  $t_{HVREG}$  is the time that the high voltage regulator will operate. When the high voltage regulator is operating, a 13 $\mu$ A current is sourced from the REGSD pin, and when it is shut down (e.g., the bypass regulator is active), a 3 $\mu$ A current is sunk into the REGSD pin. If the REGSD voltage exceeds 1.21V, the high voltage regulator

Figure 3. Typical Linear Regulator Connections

## APPLICATIONS INFORMATION

is disabled. Choose a time  $t_{HVREG}$  that is greater than the normal start-up time. After start-up, if the voltage on the  $V_{AUX}$  pin drops, the high-voltage linear regulator will be re-energized, but only for a limited time.

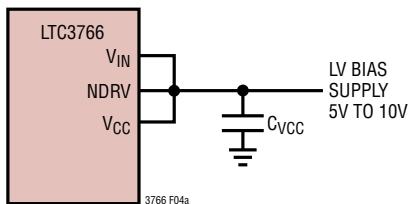

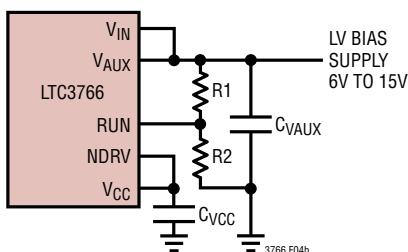

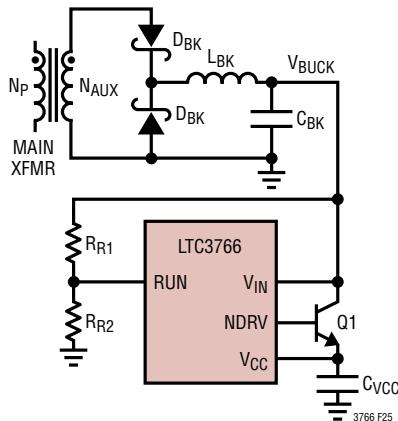

When used with a bias supply that is between 5V and 10V, the  $V_{CC}$  pin can be directly connected to the bias supply as shown in Figure 4a. Note that the  $V_{IN}$  and  $NDRV$  pins must also be connected to the bias supply for proper operation of internal circuitry. When a bias supply between 6V and 15V is available, the  $V_{AUX}$  bypass linear regulator can be used standalone as shown in Figure 4b. In this case, proper start-up is assured by connecting the  $NDRV$  pin to  $V_{CC}$ . Since there is no external pass device on  $NDRV$ , however, the effective UVLO levels will be dictated by the  $V_{AUX}$  switchover thresholds instead of the  $V_{CC}$  UVLO thresholds. Rather than relying on the  $V_{AUX}$  thresholds, the start-up and shutdown levels are normally set by using the RUN pin to monitor the bias supply voltage as shown in Figure 4b. See the RUN Pin Operation section for details.

For applications where the available bias supply is greater than 30V, the LTC3766 also contains a current-limited 30V clamp on the  $V_{IN}$  pin. This clamp can sink up to 3.5mA

Figure 4a. No Linear Regulator Used

Figure 4b.  $V_{AUX}$  Regulator Used Standalone

to allow the  $V_{IN}$  pin to be used as a shunt regulator. This is especially useful in nonisolated applications where the LTC3766 is used standalone. See the Nonisolated Applications section for more information.

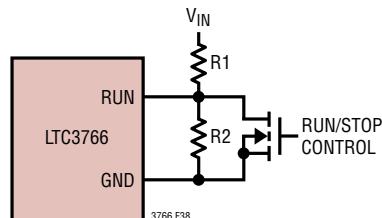

### RUN Pin Operation

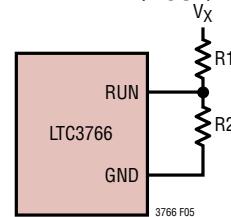

Normal operation is enabled when the voltage on RUN rises above its 1.22V threshold. As shown in Figure 5, the RUN pin can be used with an external resistor divider to enable the LTC3766 operation based on a sensed voltage  $V_X$ . In self-starting applications,  $V_X$  is normally either the converter output voltage ( $V_{OUT}$ ) or a bias voltage. In

Figure 5. Using the RUN Pin to Determine Start-Up

nonisolated applications,  $V_X$  is normally the converter input voltage ( $V_{IN}$ ). See Nonisolated Applications for more information on the use of the RUN pin in nonisolated applications.

A 3 $\mu$ A current is pulled into the RUN pin when it is below its threshold that, when combined with the value chosen for R1, increases the hysteresis beyond the internal amount of 4%. When used in this manner, the values for R1 and R2 can be calculated from the desired rising and falling  $V_X$  thresholds by the following equations:

$$R1 = \frac{V_{X(RISING)} - 1.043 \cdot V_{X(FALLING)}}{3\mu A}$$

$$R2 = \frac{1.17 \cdot R1}{V_{X(FALLING)} - 1.17}$$

In self-starting applications where the LTC3765 performs an open-loop soft-start, the voltage  $V_X$  can be tied to  $V_{OUT}$  of the converter ( $V_X = V_{OUT}$ ) to inhibit the LTC3766 start-up until the output voltage is above a given level. This

## APPLICATIONS INFORMATION

sets the exact output voltage at which soft-start control is handed off from primary to secondary. This hand-off output voltage should be set high enough so as to avoid pulse-skipping operation when the LTC3766 initially takes control. If excessive pulse skipping occurs in applications that use a peak charge circuit to generate bias voltage, this can cause the bias supply to fall, preventing proper start-up. To preclude this possibility, use the RUN pin to inhibit the LTC3766 start-up until the output voltage is at least:

$$V_{OUT(ON)} > 300\text{ns} \frac{N_S f_{SW} V_{IN(MAX)}}{N_P}$$

Note that in self-starting applications, direct RUN/STOP control should be handled only on the primary side using the LTC3765. If the LTC3765 gets disabled, the LTC3766 will sense that the primary side is no longer switching and automatically shut down. To avoid a possible output overvoltage, do not manually disable the LTC3766 unless the LTC3765 is also manually disabled.

If the RUN pin function is not needed, it can be tied directly to the  $V_{IN}$  pin.

### Setting the Switching Frequency and Synchronization

The switching frequency of the LTC3766 is set using the FS/SYNC pin. This pin sources a  $20\mu\text{A}$  current, and a resistor to ground on this pin sets the switching frequency to a value equal to:

$$f_{SW} = 4R_{FS}$$

Alternatively, the FS/SYNC pin can be tied to  $V_{CC}$ , which sets the switching frequency to a fixed value of  $275\text{kHz}$ . In general, a higher switching frequency will result in a smaller size for inductors and transformers, but at the cost of reduced efficiency. Although the LTC3766 can operate from  $75\text{kHz}$  to  $500\text{kHz}$ , the best balance between efficiency and size for a forward converter is found when operating between  $150\text{kHz}$  and  $350\text{kHz}$ .

If a clock signal ( $>2\text{V}$ ) is detected at the FS pin, the LTC3766 will automatically synchronize to the falling edge of this signal. Table 1 summarizes the operation of the FS/SYNC pin.

**Table 1**

| FS/SYNC PIN     | SWITCHING FREQUENCY                                       |

|-----------------|-----------------------------------------------------------|

| $V_{CC}$        | $275\text{kHz}$                                           |

| $R_{FS}$ to GND | $f_{SW} = 4R_{FS}$                                        |

| Reference Clock | $f_{SW} = f_{REF}$ ( $100\text{kHz}$ to $500\text{kHz}$ ) |

In PolyPhase applications, synchronization can be achieved by tying the  $PT^-$  pin of the master to the FS/SYNC pin of each slave. The relative phase delay of each slave is set using the PHASE pin. Any one of five preset values can be selected as shown in Table 2. Note that the phase delay is relative to the falling edge of the incoming reference clock on the FS/SYNC pin, since the falling edge of  $PT^-$  corresponds to the beginning of the PWM cycle.

**Table 2**

| PHASE PIN                 | PHASE DELAY | APPLICATION         |

|---------------------------|-------------|---------------------|

| GND                       | $180^\circ$ | 2-Phase and 4-Phase |

| $25\text{k}$ to GND       | $240^\circ$ | 3-Phase             |

| $50\text{k}$ to GND       | $120^\circ$ | 3-Phase             |

| $100\text{k}$ to GND      | $90^\circ$  | 4-Phase             |

| $100\text{k}$ to $V_{CC}$ | $270^\circ$ | 4-Phase             |

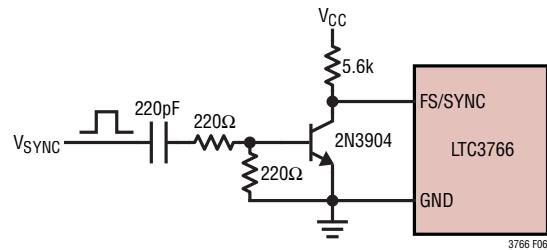

In general, the external synchronizing clock should be present before the LTC3766 is enabled, so that the switching frequency has stabilized before the gate drivers begin switching. In some applications, however, it may be necessary to synchronize the LTC3766 after it has begun switching. In this case, the circuit in Figure 6 can be used.

Using the circuit Figure 6, the LTC3766 will run at  $275\text{kHz}$  until the  $3.3\text{V} - 5\text{V}$  amplitude synchronization signal  $V_{SYNC}$  begins toggling. This circuit creates a  $100\text{ns}$  low-pulse at the FS/SYNC pin, which ensures a smooth transition into synchronization. As shown in Figure 6, the  $V_{CC}$  pin can

**Figure 6. Synchronization After LTC3766 Start-Up**

## APPLICATIONS INFORMATION

normally be used to provide the pull-up voltage, which must be between 5V and 12V. In addition, the rise time of the voltage on the FS/SYNC pin must be less than 200ns. Consequently, parasitic capacitance on the FS/SYNC pin must be minimized.

**Once the LTC3766 has been synchronized, do not remove the external synchronizing clock unless the LTC3766 is also shut down.** Removal of the external clock after synchronization will result in operation at low frequencies for a period of time, which can lead to very high currents in external power components.

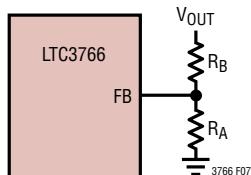

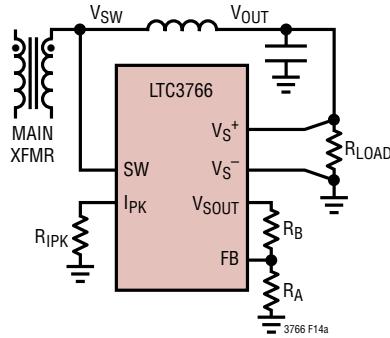

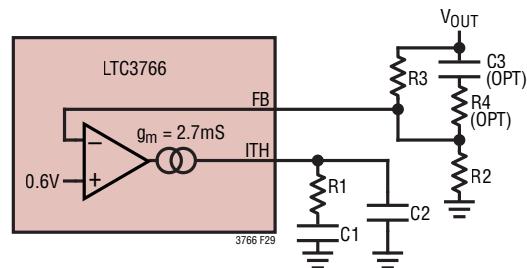

### Setting the Output Voltage

The LTC3766 output voltage is set by an external feedback resistor divider placed across the output as shown in Figure 7. The regulated output voltage is determined by:

$$V_{OUT} = 0.6V \cdot \left(1 + \frac{R_B}{R_A}\right)$$

Be careful to keep these divider resistors very close to the FB pin to minimize the trace length and noise pick-up on the sensitive FB signal. Using a low resistance (<2k) for the output voltage divider also minimizes noise on the FB pin. If the remote sense amplifier is used, then the divider should be placed between the  $V_{SOUT}$  pin and GND. See the Remote Sensing section for details.

Figure 7. Setting the Output Voltage

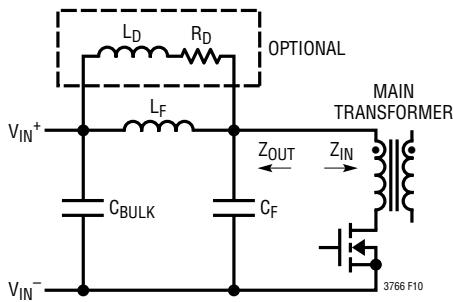

### Selecting the Main Transformer

The job of the transformer in a forward converter is to step the voltage either up or down while providing isolation between the primary and secondary grounds. Ideally,

this transformer would not store any energy (it would have infinite magnetizing inductance). Note that this objective is very different from that of the transformer used in a flyback converter. The transformer used in a flyback converter is really a coupled inductor, the purpose of which is to store energy during the primary-side on time and then deliver it to the secondary during the off-time. In a forward converter, by contrast, the power is transferred during the primary-side on-time, and the off-time is used to recover the small amount of energy that was inadvertently stored in the core of the transformer.

For nearly all applications, an off-the-shelf transformer can be selected. Transformers using planar winding technology are widely available and are a good choice for minimizing leakage inductance as well as component height. There are two basic items to consider in selecting an appropriate family of off-the-shelf transformers: 1) the isolation requirements and 2) the power level requirements. If the application circuit has specific isolation requirements, choose a family of transformers whose isolation level satisfies that requirement. In addition to an isolation voltage rating, the application may require a transformer with certification from a particular agency, or it may require a specific type of isolation (e.g., basic or functional). In terms of power level, choose a family of transformers whose rated power level exceeds that of the required amount of output power. Be careful to allow for room to "grow," as the power requirements of many electronic systems tend to increase throughout development.

Once a family of transformers has been selected, the next step is to choose a suitable transformer from within that family. This mainly consists of choosing the correct number of primary and secondary turns ( $N_P$  and  $N_S$ ). The value of  $N_S$  can be calculated from:

$$N_S = \frac{10^8 V_{OUT}}{f_{sw} A_C B_M}$$

where  $A_C$  is the cross-sectional area of the core in  $\text{cm}^2$  (as normally given in the transformer data sheet) and  $B_M$  is the maximum AC flux density desired. For the Pulse PA08xx series power transformers used in the Typical Applications

## APPLICATIONS INFORMATION