#### Is Now Part of

# ON Semiconductor®

# To learn more about ON Semiconductor, please visit our website at www.onsemi.com

Please note: As part of the Fairchild Semiconductor integration, some of the Fairchild orderable part numbers will need to change in order to meet ON Semiconductor's system requirements. Since the ON Semiconductor product management systems do not have the ability to manage part nomenclature that utilizes an underscore (\_), the underscore (\_) in the Fairchild part numbers will be changed to a dash (-). This document may contain device numbers with an underscore (\_). Please check the ON Semiconductor website to verify the updated device numbers. The most current and up-to-date ordering information can be found at <a href="www.onsemi.com">www.onsemi.com</a>. Please email any questions regarding the system integration to Fairchild <a href="guestions@onsemi.com">guestions@onsemi.com</a>.

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any EDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officer

December 2015

# FSL4110LR 1000 V SenseFET Integrated Power Switch

#### **Features**

- Built-in Avalanche Rugged 1000 V SenseFET

- Precise Fixed Operating Frequency: 50 kHz

- V<sub>CC</sub> can be supplied from either bias-winding or selfbiasing.

- Soft Burst-Mode Operation Minimizing Audible Noise

- Random Frequency Fluctuation for Low EMI

- Pulse-by-Pulse Current Limit

- Various Protection Functions: Overload Protection (OLP), Over-Voltage Protection (OVP), Abnormal Over-Current Protection (AOCP), Internal Thermal Shutdown (TSD) with Hysteresis. Under-Voltage Lockout (UVLO) and Line Over-Voltage Protection (LOVP) with Hysteresis.

- Built-in Internal Startup and Soft-Start Circuit

- Fixed 1.6 s Restart Time for Safe Auto-Restart Mode of All Protections

#### **Description**

The FSL4110LR is an integrated pulse width modulation (PWM) controller and 1000 V avalanche rugged SenseFET specifically designed for high input voltage offline Switching Mode Power Supplies (SMPS) with minimal external components.  $V_{\text{CC}}$  can be supplied through integrated high-voltage power regulator without auxiliary bias winding.

The integrated PWM controller includes a fixed-frequency oscillator, Under-Voltage Lockout (UVLO), Leading-Edge Blanking (LEB), optimized gate driver, soft-start, temperature-compensated precise current sources for loop-compensation, and variable protection circuitry.

Compared with a discrete MOSFET and PWM controller solution, the FSL4110LR reduces total cost, component count, PCB size, and weight; while simultaneously increasing efficiency, productivity, and system reliability. This device provides a basic platform for cost-effective design of a flyback converter.

## **Applications**

- SMPS for Electric Metering

- Auxiliary Power Supply for 3-Phase Input Industrial Systems

## **Ordering Information**

| Part Number |         | Operating<br>Junction<br>Temperature | Current<br>Limit | _                          | Output Power Table <sup>(1)</sup>     |                                       |  |

|-------------|---------|--------------------------------------|------------------|----------------------------|---------------------------------------|---------------------------------------|--|

|             | Package |                                      |                  | R <sub>DS(ON)</sub> (Max.) | 45~460 V <sub>AC</sub> <sup>(2)</sup> | 85~460 V <sub>AC</sub> <sup>(2)</sup> |  |

| FSL4110LRN  | 7-DIP   | −40°C ~ 125°C                        | 0.52 A           | 10 Ω                       | 4 W <sup>(3)</sup>                    | 9 W <sup>(3)</sup>                    |  |

| FSL4110LRLX | 7-LSOP  |                                      |                  |                            | 4 ۷۷`′                                | 9 00 7                                |  |

#### Notes:

- 1. The junction temperature can limit the maximum output power.

- 2. Maximum practical continuous power in an open-frame design at 50 °C ambient temperatures.

- 3. Bias winding condition.

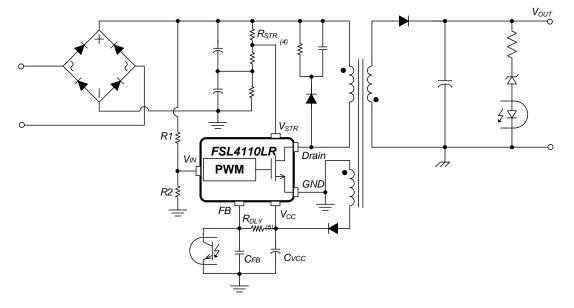

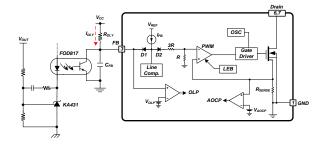

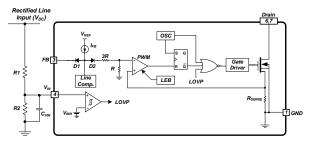

## **Typical Application Circuit**

**Figure 1. Typical Application Circuit**

#### Notes:

- 4. R<sub>STR</sub>: See the functional description 1.

- 5. R<sub>DLY</sub>: See the functional description 3.1.

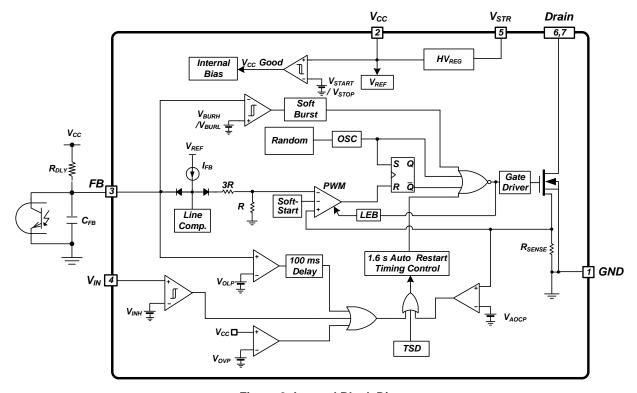

## **Internal Block Diagram**

Figure 2. Internal Block Diagram

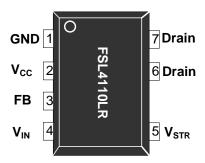

## **Pin Configuration**

Figure 3. Pin Configuration (Top View)

## **Pin Definitions**

| Pin # | Name            | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | GND             | Ground. The SenseFET source terminal on primary side and the internal PWM control ground.                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 2     | V <sub>CC</sub> | Power Supply Voltage Input. This pin is the positive supply input, which provides the internal operating current for startup and steady-state operation. This voltage is supplied from internal high-voltage regulator via pin 5 (V <sub>STR</sub> ) during startup (see Figure 2). When the external bias voltage is higher than 10 V, internal high voltage regulator is disable. A ceramic capacitor need to be placed as close as possible between this pin and pin 1 (GND). Recommended distance is less than 3 mm. |

| 3     | FB              | Feedback. This pin is internally connected to the inverting input to the PWM comparator. This pin has a 100 $\mu$ A current source internally. The collector of an opto-coupler is typically tied to this pin. A capacitor should be placed between this pin and GND. A resitor should be connected between this pin and pin 2 ( $V_{CC}$ ) to generate delay current ( $I_{DELAY}$ ) for overload protection delay time. The resistance should not be exceed 5 M $\Omega$ in self-biasing.                              |

| 4     | V <sub>IN</sub> | Line Over-Voltage Input. This pin is the input of divided line voltage. The voltage is devided by resistors. When this voltage is higher than 2 V, the FSL4110LR is not operationed. If this pin is not used, it should be connected to the ground.                                                                                                                                                                                                                                                                      |

| 5     | $V_{STR}$       | Startup. Connected to the rectified AC line voltage source. At startup, the internal switch supplies internal bias and charges an external storage capacitor placed between $V_{CC}$ pin and ground. Once $V_{CC}$ reaches 12 V, all internal blocks are activated. The internal high-voltage regulator turns on and off to maintain $V_{CC}$ at 10 V without auxiliary bias winding.                                                                                                                                    |

| 6, 7  | Drain           | Drain. Designed to connect directly to the primary lead of the transformer and capable of switching a maximum of 1000 V. Minimizing the length of the trace connecting these pins to the transformer decreases leakage inductance.                                                                                                                                                                                                                                                                                       |

### **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                                                     | Min.                  | Max. | Unit |    |

|------------------|---------------------------------------------------------------|-----------------------|------|------|----|

| V <sub>STR</sub> | V <sub>STR</sub> Pin Voltage                                  |                       |      | 700  | V  |

| V <sub>DS</sub>  | Drain Pin Voltage                                             |                       |      | 1000 | V  |

| V <sub>cc</sub>  | V <sub>CC</sub> Pin Voltage                                   |                       |      | 27   | V  |

| $V_{FB}$         | Feedback Pin Voltage <sup>(6)</sup>                           |                       | -0.3 | 12.0 | V  |

| V <sub>IN</sub>  | V <sub>IN</sub> Pin Voltage <sup>(6)</sup>                    |                       | -0.3 | 12.0 | V  |

| $I_{DM}$         | Drain Current Pulsed                                          |                       |      | 4    | Α  |

|                  | Continuous Switching Drain Current (7)                        | T <sub>C</sub> =25°C  |      | 1    | Α  |

| I <sub>DS</sub>  |                                                               | T <sub>C</sub> =100°C |      | 0.6  | Α  |

| E <sub>AS</sub>  | Single Pulsed Avalanche Energy <sup>(8)</sup>                 |                       |      | 51   | mJ |

| P <sub>D</sub>   | Total Power Dissipation (T <sub>C</sub> =25°C) <sup>(9)</sup> |                       |      | 1.5  | W  |

| <b>T</b>         | Maximum Junction Temperature                                  |                       |      | 150  | °C |

| TJ               | Operating Junction Temperature <sup>(10)</sup>                | -40                   | +125 | °C   |    |

| TSTG             | Storage Temperature                                           |                       | -55  | +150 | °C |

#### Notes

- 6.  $V_{FB}$  and  $V_{IN}$  are clamped by internal clamping diode (11 V,  $I_{CLAMP\_MAX}$  < 100  $\mu A$ ).

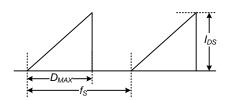

- 7. Repetitive peak switching current when the inductive load is assumed: Limited by maximum duty (D<sub>MAX</sub>=0.73) and junction temperature (see Figure 4).

- 8.  $I_{AS} = 3.2 \text{ A}, L = 10 \text{ mH}, \text{ starting } T_{J} = 25^{\circ}\text{C}$

- 9. Infinite cooling condition (refer to the SEMI G30-88).

- 10. Although this parameter guarantees IC operation, it does not guarantee all electrical characteristics.

Figure 4. Repetitive Peak Switching Current

#### **Thermal Impedance**

| Symbol        | Parameter                                             |    | Unit |

|---------------|-------------------------------------------------------|----|------|

| $\theta_{JA}$ | Junction-to-Ambient Thermal Impedance <sup>(11)</sup> | 85 | °C/W |

#### Note:

11. JEDEC recommended environment, JESD51-2, and test board, JESD51-3, with minimum land pattern.

## **ESD Capability**

| Symbol | Parameter                                     | Value | Unit |

|--------|-----------------------------------------------|-------|------|

| ESD    | Human Body Model, ANSI/ESDA/JEDEC JS-001-2012 | 5.0   | KV   |

| ESD    | Charged Device Model, JESD22-C101             | 2.0   | ΚV   |

## **Electrical Characteristics**

$T_J$  =-40°C to 125°C unless otherwise specified.

| Symbol               | Parameter                                                  | Conditions                                       | Min. | Тур. | Max. | Unit |

|----------------------|------------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| SenseFET             | Section                                                    |                                                  |      |      | ı    |      |

| BV <sub>DSS</sub>    | Drain-Source Breakdown Voltage <sup>(12)</sup>             | $V_{GS} = 0 \text{ V}, I_D = 250 \mu\text{A}$    | 1000 |      |      | V    |

| I <sub>DSS</sub>     | Zero-Gate-Voltage Drain Current <sup>(12)</sup>            | V <sub>DS</sub> = 1000 V, V <sub>GS</sub> = 0 V  |      |      | 250  | μΑ   |

| R <sub>DS(ON)</sub>  | Drain-Source On-State<br>Resistance <sup>(12)</sup>        | V <sub>GS</sub> = 10 V, I <sub>D</sub> = 1.0 A   |      |      | 10   | Ω    |

| C <sub>ISS</sub>     | Input Capacitance (12)(13)                                 | V <sub>DS</sub> = 25 V, V <sub>GS</sub> = 0 V,   |      | 367  | 477  | pF   |

| Coss                 | Output Capacitance <sup>(12)(13)</sup>                     | f = 1 MHz                                        |      | 37.5 | 48.8 | pF   |

| t <sub>d(on)</sub>   | Turn-On Delay Time <sup>(12)</sup>                         |                                                  |      | 13.7 |      | ns   |

| t <sub>r</sub>       | Rise Time <sup>(12)</sup>                                  | $V_{DD} = 500 \text{ V}, I_{D} = 1.0 \text{ A},$ |      | 14   |      | ns   |

| t <sub>d(off)</sub>  | Turn-Off Delay Time <sup>(12)</sup>                        | $V_{GS} = 10 \text{ V}, R_g = 25 \Omega$         |      | 33   |      | ns   |

| t <sub>f</sub>       | Fall Time <sup>(12)</sup>                                  |                                                  |      | 45   |      | ns   |

| Control Se           | ection                                                     |                                                  |      |      |      |      |

| f <sub>S</sub>       | Switching Frequency <sup>(12)</sup>                        | V <sub>CC</sub> = 14 V, V <sub>FB</sub> = 4 V    | 46.5 | 50.0 | 53.5 | kHz  |

| $f_{M}$              | Frequency Modulation <sup>(13)</sup>                       |                                                  |      | ±1.5 |      | kHz  |

| D <sub>MAX</sub>     | Maximum Duty Ratio                                         | V <sub>CC</sub> = 14 V, V <sub>FB</sub> = 4 V    | 61   | 67   | 73   | %    |

| I <sub>FB</sub>      | Feedback Source Current <sup>(12)</sup>                    | $V_{FB} = 0 V$                                   | 70   | 100  | 130  | μΑ   |

| V <sub>START</sub>   | UVLO Threshold Voltage                                     | V <sub>FB</sub> = 0 V, V <sub>CC</sub> Sweep     | 11   | 12   | 13   |      |

| V <sub>STOP</sub>    |                                                            | After Turn-on, V <sub>FB</sub> = 0 V             | 7    | 8    | 9    | V    |

| t <sub>S/S</sub>     | Internal Soft-Start Time                                   | V <sub>STR</sub> = 40 V, V <sub>CC</sub> Sweep   |      | 20   |      | ms   |

| Burst-Mod            | de Section                                                 |                                                  |      |      |      |      |

| V <sub>BURH</sub>    |                                                            |                                                  | 0.45 | 0.50 | 0.55 | V    |

| V <sub>BURL</sub>    | Burst-Mode Voltage <sup>(12)</sup>                         | V <sub>CC</sub> = 14 V, V <sub>FB</sub> Sweep    | 0.35 | 0.40 | 0.45 | V    |

| V <sub>HYS</sub>     |                                                            |                                                  |      | 100  |      | mV   |

| Protection           | Section                                                    |                                                  | I    |      | l    |      |

| I <sub>LIM</sub>     | Peak Drain Current Limit <sup>(12)</sup>                   | di/dt = 240 mA/μs                                | 0.45 | 0.52 | 0.59 | Α    |

| V <sub>OLP</sub>     | Overload Protection <sup>(12)</sup>                        | V <sub>CC</sub> = 14 V, V <sub>FB</sub> Sweep    | 4.0  | 4.4  | 4.8  | V    |

| V <sub>AOCP</sub>    | Abnormal Over-Current<br>Protection <sup>(13)</sup>        | , , , ,                                          |      | 1.0  |      | V    |

| t <sub>LEB</sub>     | Leading-Edge Blanking Time <sup>(13)(14)</sup>             |                                                  |      | 250  |      | ns   |

| t <sub>CLD</sub>     | Current Limit Delay Time <sup>(13)</sup>                   |                                                  |      |      | 200  | ns   |

| V <sub>OVP</sub>     | Over-Voltage Protection                                    | V <sub>CC</sub> Sweep                            | 23.0 | 24.5 | 26.0 | V    |

| V <sub>INH</sub>     | Line Over-Voltage Protection Threshold Voltage             | V <sub>CC</sub> = 14 V, V <sub>IN</sub> Sweep    | 1.9  | 2.0  | 2.1  | V    |

| V <sub>INHYS</sub>   | Line Over-Voltage Protection<br>Hysteresis <sup>(12)</sup> | V <sub>CC</sub> = 14 V, V <sub>IN</sub> Sweep    |      | 100  |      | mV   |

| t <sub>DELAY</sub>   | Overload Protection Delay                                  |                                                  |      | 100  |      | ms   |

| t <sub>RESTART</sub> | Restart Time After Protection <sup>(13)</sup>              |                                                  |      | 1.6  |      | S    |

| TSD                  |                                                            | Shutdown Temperature                             | 130  | 140  | 150  |      |

| T <sub>HYS</sub>     | Thermal Shutdown Temperature <sup>(13)</sup>               | Hysteresis (FSL4110LRN)                          |      | 60   |      | °C   |

| T <sub>HYS</sub>     | ·                                                          | Hysteresis (FSL4110LRLX)                         |      | 30   |      |      |

Continued on the following page...

## **Electrical Characteristics** (Continued)

$T_J$  =-40°C to 125°C unless otherwise specified.

| Symbol               | Parameter                                                                     | Conditions                                                                     | Min. | Тур. | Max. | Unit |  |

|----------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------|------|------|------|--|

| High Volta           | High Voltage Regulator Section                                                |                                                                                |      |      |      |      |  |

| V <sub>HVREG</sub>   | HV Regulator Voltage                                                          | V <sub>FB</sub> = 0 V, V <sub>STR</sub> = 40 V                                 | 9    | 10   | 11   | V    |  |

| Total Device Section |                                                                               |                                                                                |      |      |      |      |  |

| I <sub>OP</sub>      | Operating Supply Current,<br>(Control Part in Burst Mode) <sup>(12)</sup>     | V <sub>CC</sub> = 14 V, V <sub>FB</sub> = 0 V                                  |      | 0.40 | 0.50 | mA   |  |

| I <sub>OPS</sub>     | Operating Switching Current, (Control Part and SenseFET Part) <sup>(12)</sup> | V <sub>CC</sub> = 14 V, V <sub>FB</sub> = 2 V                                  |      | 1.00 | 1.35 | mA   |  |

| I <sub>START</sub>   | Start Current <sup>(12)</sup>                                                 | V <sub>CC</sub> = 11 V (Before V <sub>CC</sub><br>Reaches V <sub>START</sub> ) |      | 160  | 240  | μΑ   |  |

| I <sub>CH</sub>      | Startup Charging Current <sup>(12)</sup>                                      | $V_{CC} = V_{FB} = 0 \text{ V}, V_{STR} = 40 \text{ V}$                        | 1.5  | 2.0  |      | mA   |  |

| V <sub>STR</sub>     | Minimum V <sub>STR</sub> Supply Voltage                                       | $C_{VCC} = 0.1 \mu F$ , $V_{STR}$ Sweep                                        |      |      | 26   | V    |  |

#### Notes:

- 12.  $T_J = 25^{\circ}C$ .

- 13. Although these parameters are guaranteed, they are not 100% tested in production.

- 14. t<sub>LEB</sub> includes gate turn-on time.

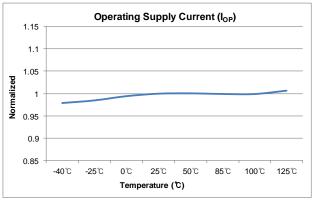

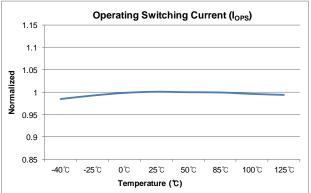

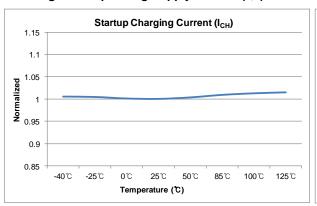

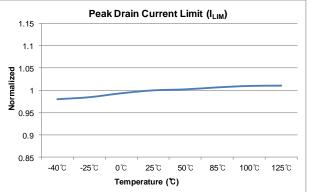

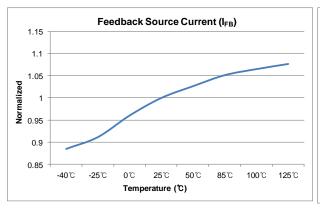

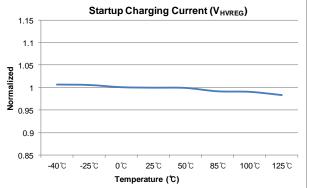

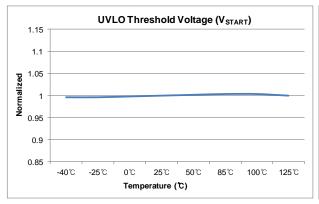

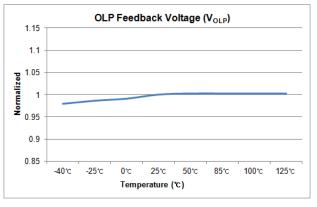

## **Typical Performance Characteristics**

Characteristic graphs are normalized at T<sub>A</sub>=25°C.

Figure 5. Operating Supply Current (IOP) vs. TA

Figure 6. Operating Switching Current (I<sub>OPS</sub>) vs. T<sub>A</sub>

Figure 7. Startup Charging Current (I<sub>CH</sub>) vs. T<sub>A</sub>

Figure 8. Peak Drain Current Limit (I<sub>LIM</sub>) vs. T<sub>A</sub>

Figure 9. Feedback Source Current (IFB) vs. TA

Figure 10. HV Regulator Voltage (V<sub>HVREG</sub>) vs. T<sub>A</sub>

## **Typical Performance Characteristics** (Continued)

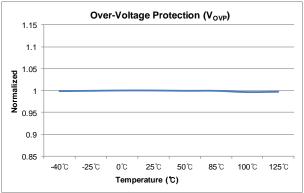

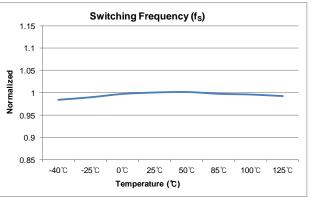

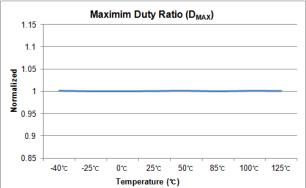

Characteristic graphs are normalized at T<sub>A</sub>=25°C.

UVLO Threshold Voltage (V<sub>STOP</sub>)

1.15

1.1

1.05

1.05

0.95

0.95

0.9

0.85

40°c -25°c 0°c 25°c 50°c 85°c 100°c 125°c Temperature (°c)

Figure 11. UVLO Threshold Voltage ( $V_{START}$ ) vs.  $T_A$

Figure 12. UVLO Threshold Voltage ( $V_{STOP}$ ) vs.  $T_A$

Figure 13. OLP Feedback Voltage (VolP) vs. TA

Figure 14. Over-Voltage Protection (V<sub>OVP</sub>) vs. T<sub>A</sub>

Figure 15. Switching Frequency (fs) vs. TA

Figure 16. Maximum Duty Ratio (D<sub>MAX</sub>) vs. T<sub>A</sub>

#### **Functional Description**

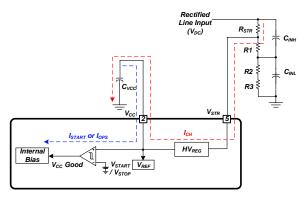

#### 1. Startup and High-Voltage Regulator

During startup, an internal high-voltage current source ( $I_{CH}$ ) of the high-voltage regulator ( $HV_{REG}$ ) supplies the internal bias current ( $I_{START}$ ) and charges the external capacitor ( $C_{VCC}$ ) connected to  $V_{CC}$  pin, as shown in Figure 17. This internal high-voltage current source is enabled until  $V_{CC}$  reaches  $V_{START}$  (12 V). During steady-state operation, this internal high-voltage regulator ( $HV_{REG}$ ) maintains the  $V_{CC}$  with 10 V and provides operating switching current ( $I_{OPS}$ ) for all internal circuits. Therefore, FSL4110LR needs no external bias circuit. The high-voltage regulator is disabled when  $V_{CC}$  supplied by the external bias is higher than 10 V. However in the case of self-biasing, power consumption is increased.

Figure 17. Startup and HV<sub>REG</sub> Block

The startup resistor ( $R_{STR}$ ) can be calculated by the following equation (1).

$$R_{STR} \le \frac{V_{DC\_MIN} - V_{START}}{I_{CH}} \tag{1}$$

where,  $I_{OPS} < I_{CH} < 2 \text{ mA}$ ,

$R_{STR} + R1 = R2 + R3$

#### 2. Feedback Control

FSL4110LR employs current-mode control scheme. An opto-coupler (such as FOD817) and shunt regulator (such as KA431) in secondary-side are typically used to implement the feedback network. Comparing the feedback voltage with the voltage across R<sub>SENSE</sub> resistor makes it possible to control the switching duty cycle. When the input voltage is increased or the output load is decreased, reference input voltage of shunt regulator is increased. If this voltage exceeds internal reference voltage of shunt regulator, opto-diode's current of the opto-coupler increases, pulling down the feedback voltage and reducing drain current.

#### 2.1. Pulse-by-Pulse Current Limit

Because current-mode control is employed, the peak current flowing through the SenseFET is limited by the inverting input of PWM comparator, as shown in Figure 18. Assuming that 100  $\mu$ A current source (I<sub>FB</sub>) flows only through the internal resistors (3R + R = 24 k $\Omega$ ), the cathode voltage of diode D2 is about 2.4 V. Since D1 is

blocked when feedback voltage ( $V_{FB}$ ) exceeds 2.4 V, the maximum voltage of the cathode of D2 is clamped at this voltage. Therefore, the peak value of the current of the SenseFET is limited at:

$$\frac{2.4V}{R_{SENSE}} \times Sense Ratio \tag{2}$$

Figure 18. Pulse Width Modulation Circuit

#### 2.2. Leading Edge Blanking (LEB)

At the instant, the internal SenseFET is turned on, a high-current spike usually occurs through the SenseFET, caused by primary-side capacitance and secondary-side rectifier reverse recovery. Excessive voltage across the  $R_{\text{SENSE}}$  resistor leads to incorrect feedback operation in the current-mode PWM control. To counter this effect, FSL4110LR employs a leading-edge blanking (LEB) circuit. This circuit inhibits the PWM comparator for  $t_{\text{LEB}}$  (250 ns) after the SenseFET is turned on.

#### 3. Protection Circuits

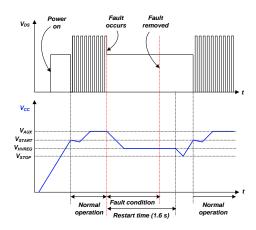

The protective functions include Overload Protection (OLP), Over-Voltage Protection (OVP), Under-Voltage Lockout (UVLO), Abnormal Over-Current Protection (AOCP), and Thermal Shutdown (TSD). All of the protections operate in auto-restart mode as shown in Figure 19. Since these protection circuits are fully integrated inside the IC without external components, reliability is improved without increasing cost and PCB space. If a fault condition occurs, switching is terminated and the SenseFET remains off. At the same time, internal protection timing control is activated to decrease power consumption and stress on passive and active components during auto-restart. When internal protection timing control is activated,  $V_{\text{CC}}$  is regulated with 10 V through the internal high-voltage regulator while switching is terminated. This internal protection timing control continues until restart time (1.6 s) duration is finished. After counting to 1.6 s, the internal high-voltage regulator is disabled and V<sub>CC</sub> is decreased. When V<sub>CC</sub> reaches the UVLO stop voltage, V<sub>STOP</sub> (8 V), the protection is reset and the internal highvoltage current source charges the V<sub>CC</sub> capacitor via the high voltage startup pin  $(V_{STR})$  again. When  $V_{CC}$ reaches the UVLO start voltage, V<sub>START</sub> (12 V), the FSL4110LR resumes normal operation. In this manner. auto-restart function can alternately enable and disable the switching of the power SenseFET until the fault condition is eliminated.

Figure 19. Auto-Restart Protection Waveforms

#### 3.1. Overload Protection (OLP)

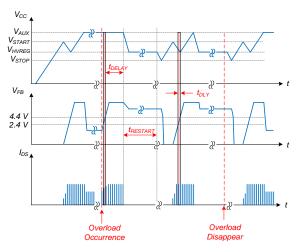

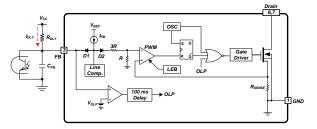

Overload is defined as the load current exceeding its normal level due to an unexpected abnormal event. In this situation, the protection circuit should trigger to protect the SMPS. However, even when the SMPS is in normal operation, the overload protection circuit can be triggered during load transition. To avoid this undesired operation, the overload protection circuit is designed to trigger only after a specified time to determine whether it is a transient situation or a true overload situation. Because of the pulse-by-pulse current-limit capability, the maximum peak current through the SenseFET is limited. If the output consumes more than this maximum power, the output voltage decreases below the set voltage. This reduces the current through the optodiode, which also reduces the opto-coupler transistor current, thus increasing the feedback voltage (VFB). If V<sub>FR</sub> exceeds 2.4 V. internal diode D1 is blocked and the current ( $I_{DLY}$ ) by  $R_{DLY}$  starts to charge  $C_{FB}$ . If feedback voltage reaches 4.4 V, internal fixed delay time (t<sub>DELAY</sub>) starts counting. If feedback voltage maintains over 4.4 V after t<sub>DELAY</sub> (100 ms), the switching operation is terminated (see Figure 20). The internal OLP circuit is shown in Figure 21.

Figure 20. OLP Waveforms

Figure 21. OLP Circuit

Recommended the  $R_{DLY}$  value is less than 5  $M\Omega$  in self-biasing. The delay time  $(t_{DLY})$  can be calculated by equation (3).

$$t_{DLY} = -R_{DLY} \times C_{FB} \times \ln\left(1 - \frac{2}{V_{CC} - 2.4}\right)$$

(3)

Example:

When,  $R_{DLY}=3$  MΩ,  $C_{FB}=68$  nF,  $V_{CC}=15$  V,

$t_{\text{DLY}} = 35 \text{ ms}$

: Total delay time for OLP: 135 ms

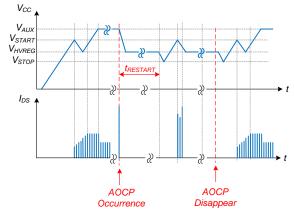

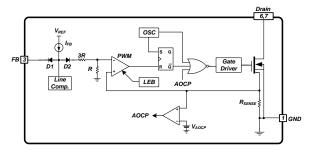

#### 3.2. Abnormal Over-Current Protection (AOCP)

When the secondary rectifier diodes or the transformer pins are shorted, a steep current with extremely high di/dt can flow through the SenseFET during the minimum turn-on time. Overload protection is not enough to protect the FSL4110LR in that abnormal case (see Figure 22); since severe current stress is imposed on the SenseFET until OLP is triggered. The internal AOCP circuit is shown in Figure 23. When the gate turn-on signal is applied to the power SenseFET, the AOCP block is enabled and monitors the current through the sensing-resistor. The voltage across the resistor is compared with a preset AOCP level. If the sensing resistor voltage is greater than the AOCP level, the high signal is applied to input of the NOR gate, resulting in the shutdown of the SMPS.

Figure 22. AOCP Waveforms

Figure 23. AOCP Circuit

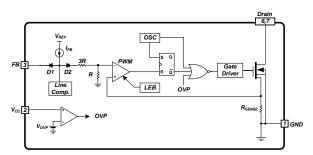

#### 3.3. Over-Voltage Protection (OVP)

If the secondary-side feedback circuit malfunctions or a solder defect causes an opening in the feedback path, the current through the opto-coupler transistor becomes almost zero. Then V<sub>FB</sub> climbs in a similar manner to the overload situation, forcing the preset maximum drain current to flow until the overload protection is triggered. Because more energy than required is provided to the output, the output voltage may exceed the rated voltage before the overload protection is triggered, resulting in the breakdown of the devices in the secondary side. To prevent this situation, an OVP circuit is employed. In general, the V<sub>CC</sub> is proportional to the output voltage when the bias-winding is used and the FSL4110LR uses V<sub>CC</sub> instead of directly monitoring the output voltage. If V<sub>CC</sub> exceeds 24.5 V, an OVP circuit is triggered, resulting in the termination of the switching operation. To avoid undesired activation of OVP during normal operation, V<sub>CC</sub> should be designed to be below 24.5 V in the normal conditions. The internal OVP circuit is shown in Figure 24.

Figure 24. OVP Circuit

#### 3.4. Thermal Shutdown (TSD)

The SenseFET and control IC integrated on the same package makes it easier to detect the temperature of the SenseFET. When the junction temperature exceeds 140°C, thermal shutdown is activated. The FSL4110LR is restarted when the temperature decreases by 60°C within t<sub>RESTART</sub> (1.6 s).

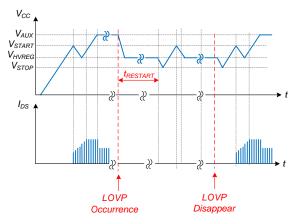

#### 3.5. Line Over-Voltage Protection (LOVP)

If the line input voltage is increased to an undesirable level, high line input voltage creates high-voltage stress on the entire system. To protect the SMPS from this abnormal condition, LOVP is included. It is comprised of detecting  $V_{\text{IN}}$  voltage by using divided resistors. When voltage of  $V_{\text{IN}}$  voltage is higher than 2.0 V, this condition is recognized as an abnormal error and PWM switching shuts down until voltage of  $V_{\text{IN}}$  voltage decreases to

around 1.9 V within  $t_{RESTART}$  (see Figure 25). The internal LOVP circuit is shown in Figure 26.

Figure 25. LOVP Waveforms

Figure 26. LOVP Circuit

Equation (4) calculates the level of input over-voltage to RMS value.

$$R2 = \frac{V_{INH} \times R1}{V_{DC} - V_{INH}} \tag{4}$$

The resistance of divided resistor can be adjusted as necessary. Small resistance can bring relatively large stand-by power consumption at light-load condition. To avoid this situation, a several  $M\Omega$  resistor is recommended. For stable operation, a several  $M\Omega$  resistor should accompany a capacitor (C $_{\text{VIN}}$ ) with hundreds of pF capacitance between the V $_{\text{IN}}$  pin and GND.

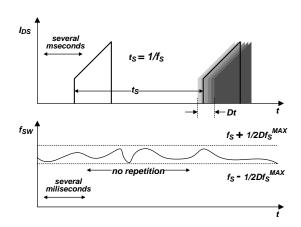

#### 4. Oscillator Block

The oscillator frequency is set internally and the FSL4110LR has a random frequency fluctuation function as shown in Figure 27. Fluctuation of the switching frequency can reduce EMI by spreading the energy over a wider frequency range than the bandwidth measured by the EMI test equipment. The range of frequency variation is fixed internally; however, its selection is randomly chosen by the combination of an external feedback voltage and an internal freerunning oscillator. This randomly chosen switching frequency effectively spreads the EMI noise near switching frequency and allows the use of a cost-effective inductor instead of an AC input line filter to satisfy world-wide EMI requirements.

Figure 27. Frequency Fluctuation Waveforms

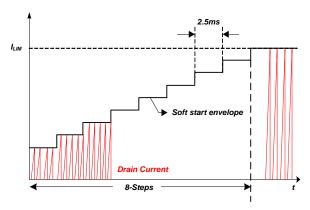

#### 5. Soft-Start

The internal soft-start circuit slowly increases the SenseFET current after it starts. The typical soft-start time is 20 ms, as shown in Figure 28, where progressive increments of the SenseFET current are allowed during startup. The pulse width to the power switching device is progressively increased to establish the correct working conditions for transformers, inductors, and capacitors. The voltage on the output capacitors is gradually increased to smoothly establish the required output voltage. Soft-start also helps to prevent transformer saturation and reduces stress on the secondary diode.

Figure 28. Internal Soft-Start

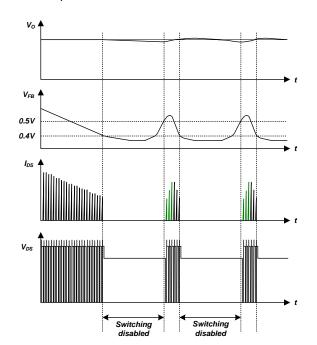

#### 6. Burst Mode Operation

To minimize power dissipation in standby mode, the FSL4110LR enters burst mode. As the load decreases, the feedback voltage decreases. The device automatically enters burst mode when the feedback voltage drops below V<sub>BURL</sub> (400 mV), as shown in Figure 29. At this point, switching stops and the output voltages start to drop at a rate dependent on standby current load. This causes the feedback voltage to rise. Once it passes VBURH (500 mV), switching resumes. Feedback voltage then falls and the process repeats. Burst Mode alternately enables and disables switching of the SenseFET, reducing switching loss in standby

mode. Additionally to reduce the audible noise softburst is implemented.

Figure 29. Burst Mode Operation

#### 7. Line Compensation

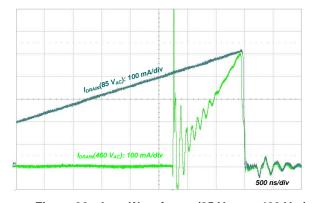

All of switching devices have their own inherent propagation delays. This propagation delay will cause a current limit delay defined as  $t_{\text{CLD}}$ . Because there is a current limit delay,  $t_{\text{CLD}}$ , there is a difference in the current peak between low and high input voltage. The variance in the current peak is related to the difference between the input voltages, a wider gap in input voltage will result in a greater variance of the current peak.

In order to have a constant current peak regardless of the input voltage, line compensation is required. FSL4110LR has line compensation, so the real peak value of high input voltage is similar to that of low input voltage.  $t_{\text{CLD}}$  effect could be neglected as showed Figure 30.

Figure 30. I<sub>LIMIT</sub> Waveforms (85 V<sub>AC</sub> vs. 460 V<sub>AC</sub>)

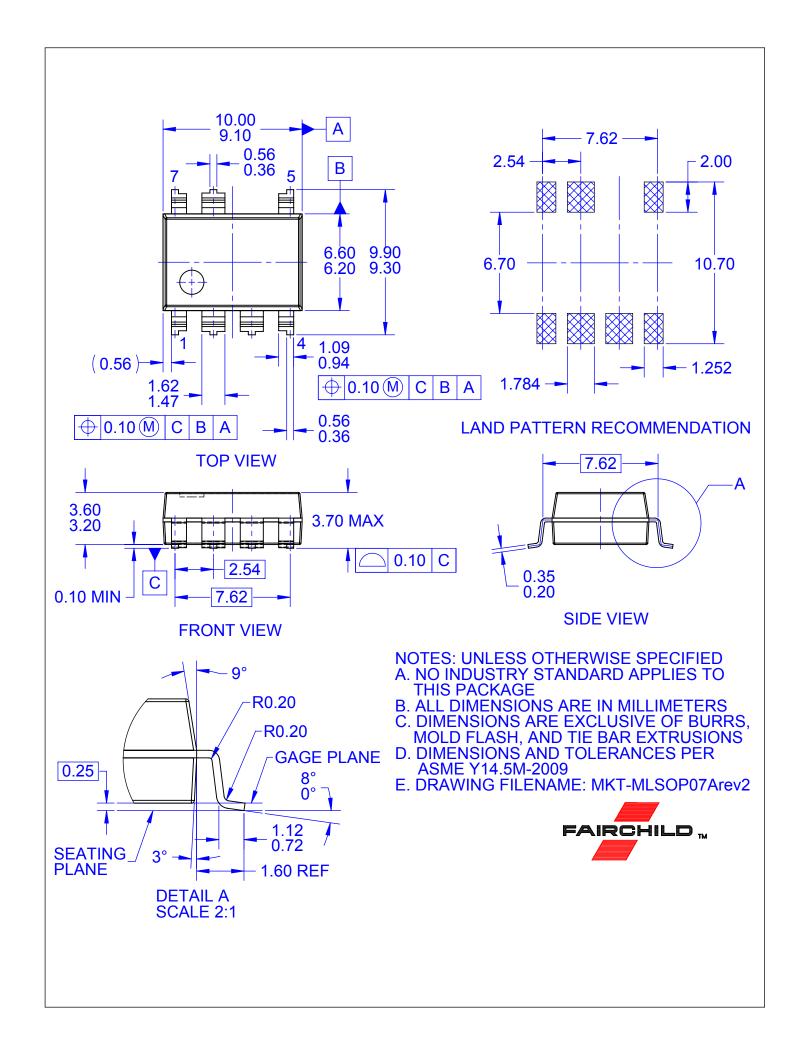

#### **NOTES:**

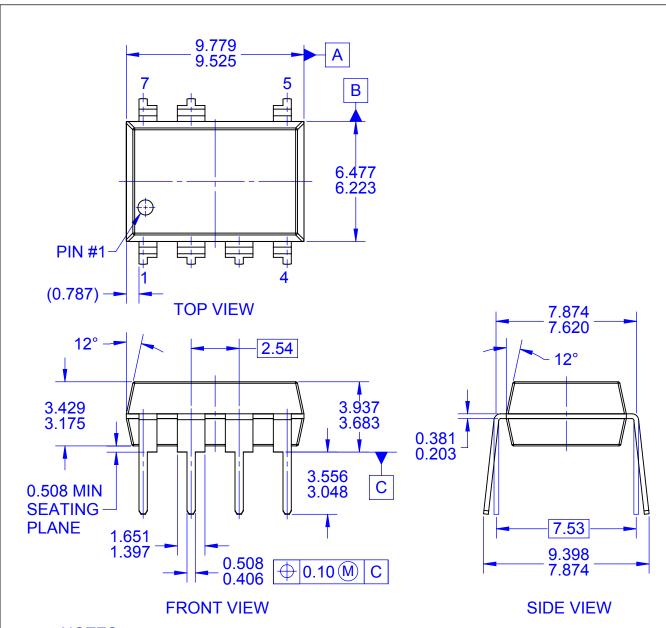

- A. REFERENCE JEDEC MS-001, VARIATION BA EXCEPT FOR NUMBER OF LEADS.

- **B. DIMENSIONS ARE IN MILLIMETERS**

- C. DIMENSIONS AND TOLERANCES PER ASME Y14.5M, 2009

- D. DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH AND TIE BAR EXTRUSIONS.

- E. DRAWING FILENAME: MKT-NA07Drev2

ON Semiconductor and in are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdt/Patent-Marking.pdf">www.onsemi.com/site/pdt/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and exp

#### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor 19521 E. 32nd Pkwy, Aurora, Colorado 80011 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support:

Phone: 421 33 790 2910

Japan Customer Focus Center

Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

## **ON Semiconductor:**

FSL4110LRN FEBFSL4110LR\_CS01U06A FSL4110LRLX FEBFSL4110LR-CS01U06A-GEVB

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.