# CM7000 Series

**C-Programmable Core Module**

**User's Manual**

Revision F

## CM7000 Series Core Modules User's Manual

Part Number 019-0018 • Revision F Last revised on February 18, 1999 • Printed in U.S.A.

## Copyright

© 1999 Z-World • All rights reserved.

Z-World reserves the right to make changes and improvements to its products without providing notice.

#### **Trademarks**

- Dynamic C® is a registered trademark of Z-World

- Windows® is a registered trademark of Microsoft Corporation

- PLCBus<sup>™</sup> is a trademark of Z-World

- Hayes Smart Modem<sup>®</sup> is a registered trademark of Hayes icrocomputer Products, Inc.

#### **Notice to Users**

When a system failure may cause serious consequences, protecting life and property against such consequences with a backup system or safety device is essential. The buyer agrees that protection against consequences resulting from system failure is the buyer's responsibility.

This device is not approved for life-support or medical systems.

All Z-World products are 100 percent functionally tested. Additional testing may include visual quality control inspections or mechanical defects analyzer inspections. Specifications are based on characterization of tested sample units rather than testing over temperature and voltage of each unit. Z-World may qualify components to operate within a range of parameters that is different than the manufacturer's recommended range. This strategy is believed to be more economical and effective. Additional testing or burn-in of an individual unit is available by special arrangement.

## **Company Address**

**Z-World** Telephone: (530) 757-3737 2900 Spafford Street Facsimile: (530) 753-5141

Davis, California 95616-6800 Web Site: http://www.zworld.com USA E-Mail: zworld@zworld.com

## TABLE OF CONTENTS

| About This Manual                                                           | ix |

|-----------------------------------------------------------------------------|----|

| Chapter 1: Overview                                                         | 13 |

| Introduction                                                                | 14 |

| Features                                                                    | 14 |

| Options                                                                     | 14 |

| CM7100 Series                                                               | 14 |

| CM7200 Series                                                               | 16 |

| Software Development and Evaluation Tools                                   | 17 |

| Chapter 2: Getting Started                                                  | 19 |

| Programming Setup                                                           | 20 |

| CM7100                                                                      |    |

| CM7100 Method 1 — Prototyping Board                                         |    |

| CM7100 Method 2 — Development Board                                         | 24 |

| CM7100 Method 3 — Embedded in System                                        | 27 |

| CM7100 Method 4 — In-Target Direct Development                              | 28 |

| Safeguards                                                                  | 29 |

| CM7200                                                                      |    |

| CM7200 Method 1 — Prototyping Board<br>CM7200 Method 2 — Embedded In System | 30 |

| CM7200 Method 2 — Embedded In System                                        | 32 |

| Chapter 3: System Development                                               | 33 |

| General Description                                                         | 34 |

| Interface Description                                                       | 36 |

| CM7000 Subsystems                                                           | 39 |

| DMA                                                                         | 39 |

| DMA Registers                                                               | 40 |

| Software                                                                    | 41 |

| Programmable Timers                                                         |    |

| Software                                                                    |    |

| EPROM                                                                       |    |

| CM7100                                                                      |    |

| CM7200                                                                      |    |

| SRAM                                                                        |    |

| EEPROM                                                                      |    |

| Real-Time Clock (RTC)                                                       | 47 |

| Power Management                                       | 48 |

|--------------------------------------------------------|----|

| Handling Power Fluctuations                            | 49 |

| The Watchdog Timer                                     | 52 |

| Power Shutdown and Reset                               | 52 |

| PFI "Early Warning"                                    | 52 |

| Memory Protection                                      | 53 |

| Battery/Super Capacitor Backup                         | 53 |

| System Reset                                           |    |

| Serial Communication                                   | 56 |

| RS-232 Communication                                   | 57 |

| Receive and Transmit Buffers                           | 58 |

| Echo Option                                            | 58 |

| CTS/RTS Control                                        | 58 |

| XMODEM File Transfer                                   | 58 |

| Modem Communication                                    |    |

| Interrupt Handling for Z180 Port 0                     | 59 |

| Software Support                                       | 60 |

| Master-Slave Networking                                | 60 |

| Software Support                                       | 61 |

| Use of the Serial Ports                                | 62 |

| Attainable Baud Rates                                  | 63 |

| Z180 Serial Ports                                      | 63 |

| Asynchronous Serial Communication Interface            | 65 |

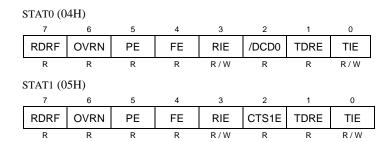

| ASCI Status Registers                                  | 65 |

| /DCD0 (Data Carrier Detect)                            | 65 |

| TIE (Transmitter Interrupt Enable)                     | 65 |

| TDRE (Transmitter Data Register Empty)                 | 65 |

| CTS1E (CTS Enable, Channel 1)                          | 66 |

| RIE (Receiver Interrupt Enable)                        | 66 |

| FE (Framing Error)                                     | 66 |

| PE (Parity Error)                                      | 66 |

| OVRN (Overrun Error)                                   |    |

| RDRF (Receiver Data Register Full)                     | 66 |

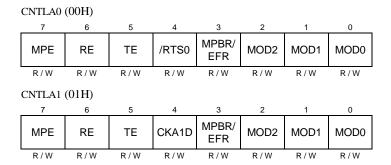

| ASCI Control Register A                                | 67 |

| MOD0-MOD2 (Data Format Mode Bits)                      |    |

| MPBR/EFR (Multiprocessor Bit Receive/Error Flag Reset) |    |

| /RTS0 (Request to Send, Channel 0)                     |    |

| CKA1D (CKA1 Disable)                                   |    |

| TE (Transmitter Enable)                                | 67 |

| RE (Receiver Enable)                                   | 68 |

| MPE (Multiprocessor Enable)                            | 68 |

| ASCI Control Register B                                 | 68 |

|---------------------------------------------------------|----|

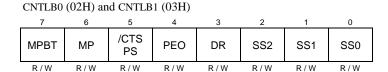

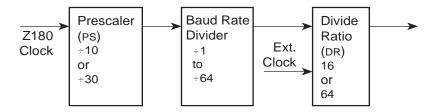

| SS (Source/Speed Select)                                | 68 |

| DR (Divide Ratio)                                       | 69 |

| PEO (Parity Even/Odd)                                   | 69 |

| /CTS/PS (Clear to Send/Prescaler)                       | 69 |

| MP (Multiprocessor Mode)                                | 69 |

| MPBT (Multiprocessor Bit Transmit)                      | 69 |

| Chapter 4: Design Considerations                        | 71 |

| Bus Loading                                             |    |

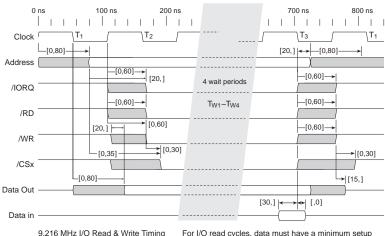

| Bus Timing                                              | 76 |

| Standard I/O Cycles                                     | 76 |

| Wait State Insertion                                    | 77 |

| System Power                                            |    |

| Power-On and Reset Management                           | 79 |

| Watchdog Timer                                          | 79 |

| I/O Addressing                                          | 80 |

| Appendix A: Troubleshooting                             | 81 |

| Out of the Box                                          | 82 |

| Dynamic C Will Not Start                                |    |

| Dynamic C Loses Serial Link                             |    |

| CM7000 Repeatedly Resets                                | 83 |

| Common Programming Errors                               | 84 |

| Appendix B: Specifications                              | 85 |

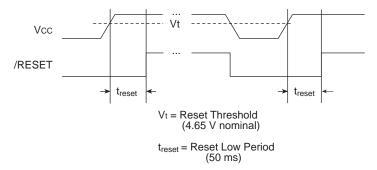

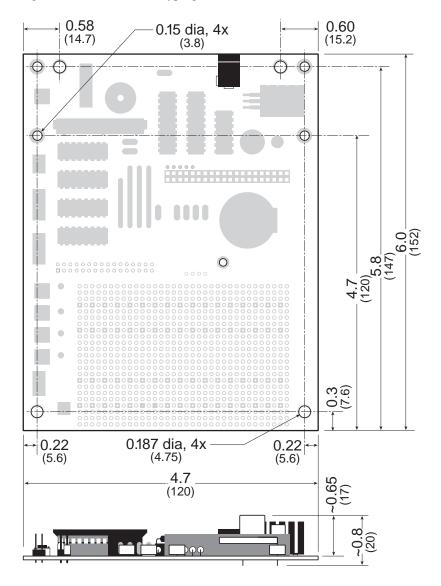

| Electrical and Mechanical Specifications                | 86 |

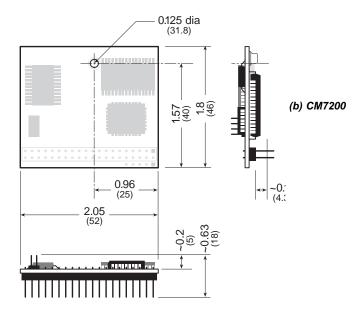

| Mechanical Dimensions                                   |    |

| Jumpers and Headers                                     |    |

| CM7100                                                  |    |

| CM7200                                                  |    |

| Appendix C: Memory, I/O Map, and Interrupt Vectors      | 91 |

| CM7000 Memory                                           |    |

| Execution Timing                                        |    |

| Memory Map                                              |    |

| Input/Output Select Map                                 |    |

| Z180 Internal Input/Output Register Addresses 0x00-0x3F |    |

| Epson 72423 Timer Registers 0x4180–0x418F               |    |

| Other Addresses                                         |    |

| I/O Addressing                                          |    |

| Interrupt Vectors                    | 98  |

|--------------------------------------|-----|

| Nonmaskable Interrupts               | 99  |

| INT0                                 | 99  |

| INT1                                 | 99  |

| INT2                                 | 99  |

| Jump Vectors                         | 100 |

| Interrupt Priorities                 | 100 |

| Appendix D: <b>EEPROM</b>            | 101 |

| Library Routines                     | 103 |

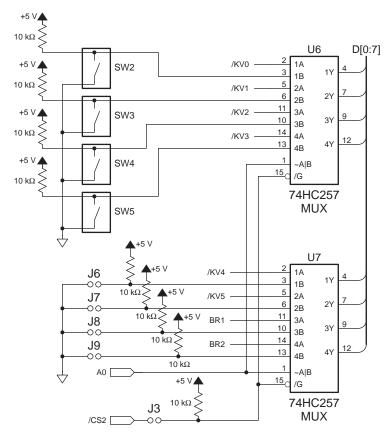

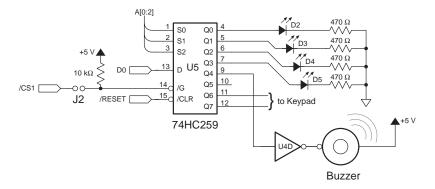

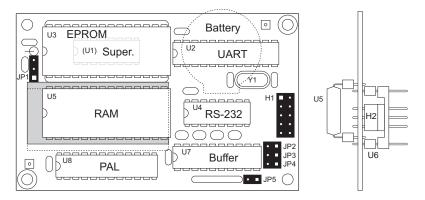

| Appendix E: Serial Interface Board 2 | 105 |

| Introduction                         |     |

| External Dimensions                  | 107 |

| Appendix F: <b>Prototyping Board</b> | 109 |

| Description                          |     |

| Interfaces                           |     |

| Power                                |     |

| Prototyping Area                     |     |

| Reset                                |     |

| Dimensions                           |     |

| Jumpers and Headers                  |     |

| Sample Circuits                      |     |

| Digital Input                        |     |

| Digital Output                       | 120 |

| Appendix G: <b>Development Board</b> | 121 |

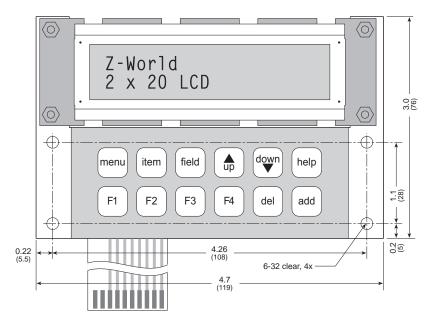

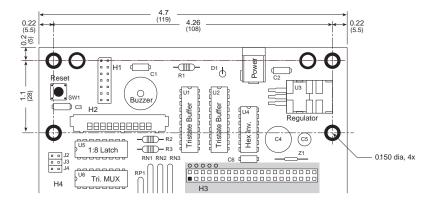

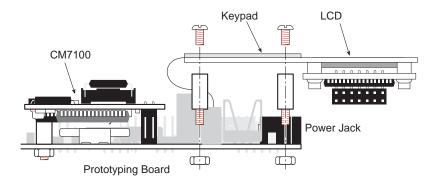

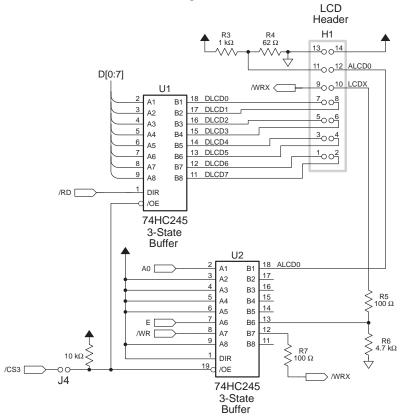

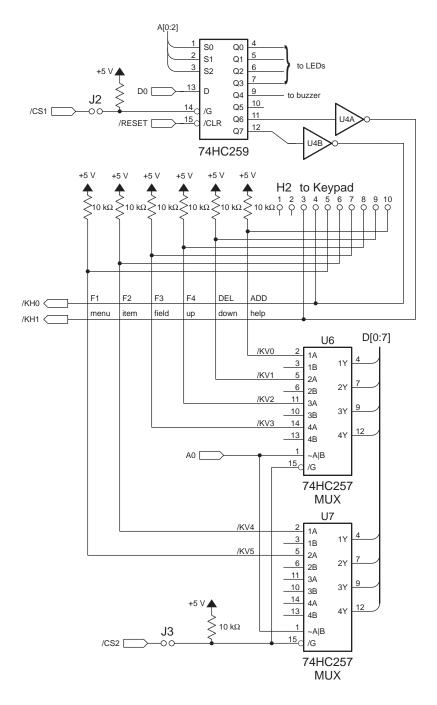

| Appendix H: LCD/Keypad Module        | 125 |

| The LCD Driver                       |     |

| The Keypad Driver                    | 129 |

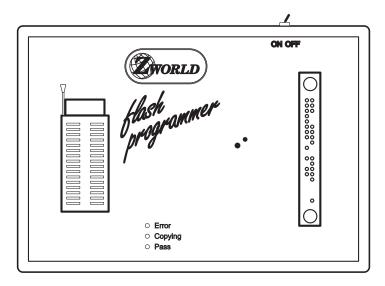

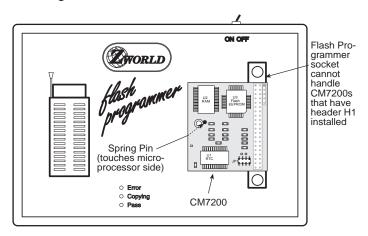

| Appendix I: Flash Programmer         | 131 |

| Introduction                         | 132 |

| Nonremovable Flash EPROM             | 132 |

| Requirements                         |     |

| Selecting a Master EPROM             |     |

| EPROM Sizes                          |     |

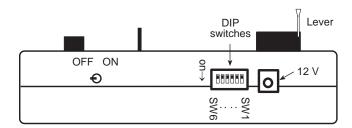

| Back-Panel DIP switches              | 134 |

| Operating Procedure to Copy Application     | 135 |

|---------------------------------------------|-----|

| BIOS Update/Recovery Mode                   | 136 |

| Troubleshooting                             | 137 |

| CM7100 Compatibility                        |     |

| Appendix J: Sample Applications             | 139 |

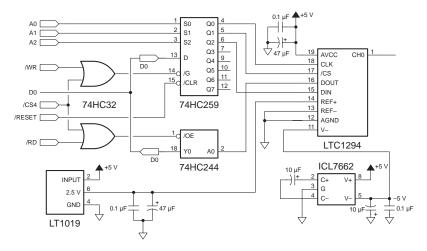

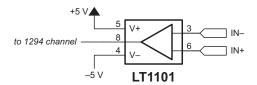

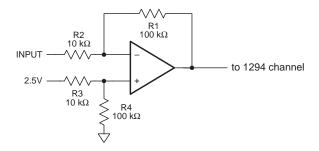

| 12-Bit Analog-to-Digital Converter          | 140 |

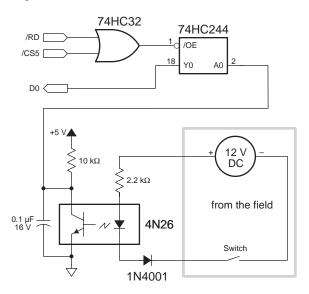

| Optically Isolated Switch Reader            | 143 |

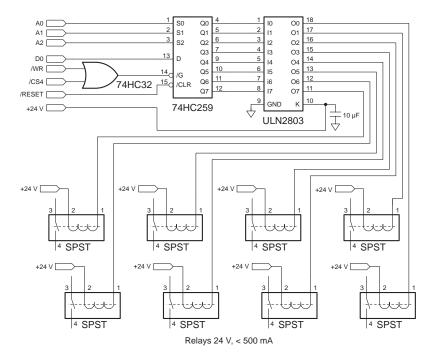

| Relay Circuit                               | 144 |

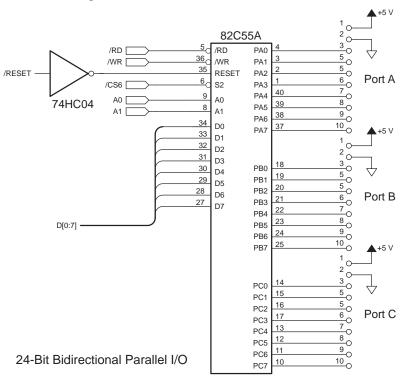

| 24-Bit Parallel I/O                         | 146 |

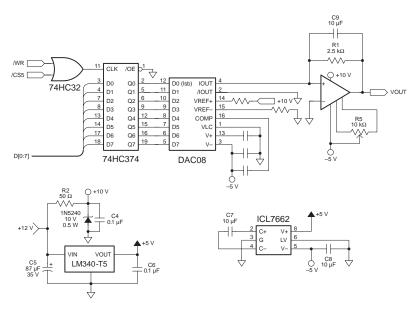

| 8-Bit Digital-to-Analog Converter           | 147 |

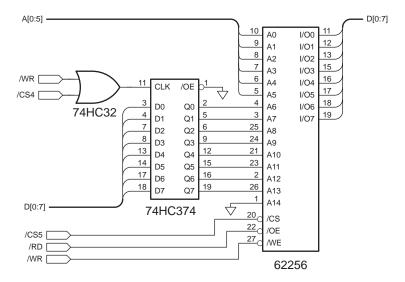

| SRAM Interface                              | 149 |

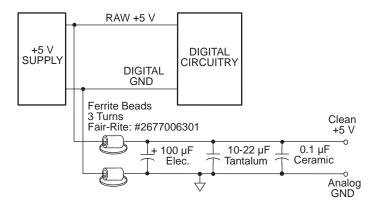

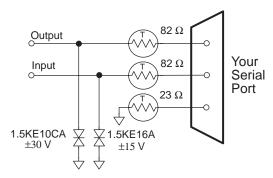

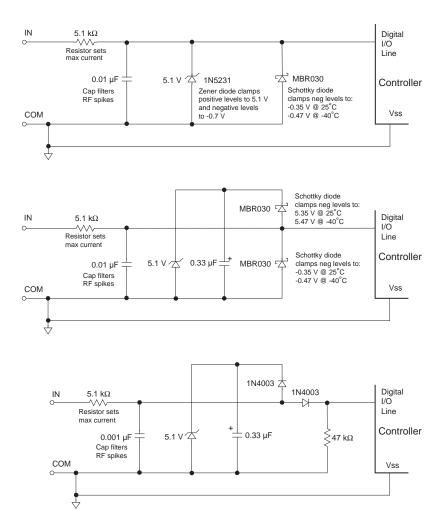

| Protection Circuits                         | 150 |

| Digital-Noise Filter                        | 150 |

| Serial-Port Protection                      | 150 |

| Digital I/O Protection                      | 151 |

| Suppliers of Board-Level Protection Devices | 151 |

| Appendix K: Sample Programs                 | 153 |

| Sample Programs on Special EPROM            | 154 |

| Other Sample Programs                       | 156 |

| Index                                       | 157 |

## Blank

## ABOUT THIS MANUAL

This manual describes the CM7000 Series core modules, their subsystems, and the CM7100 Evaluation Kit. For ease of reference, this manual uses "CM7000" as a generic term referring to any of the CM7100 or CM7200 Series modules. "CM7100" refers to any of the CM7100 Series modules, and "CM7200" refers to the CM7200 Series. Specific models are referenced when appropriate.

Instructions are also provided for using Dynamic C functions.

## **Assumptions**

Assumptions are made regarding the user's knowledge and experience in the following areas:

- Ability to design and engineer a target system that uses a CM7000.

- Understanding of the basics of operating a software program and editing files under Windows on a PC.

- Knowledge of the basics of C programming.

**The C Programming Language** by Kernighan and Ritchie **C: A Reference Manual** by Harbison and Steel

• Knowledge of basic Z80 assembly language and architecture.

Z180 MPU User's Manual Z180 Serial Communication Controllers Z80 Microprocessor Family User's Manual

## **Acronyms**

Table 1 is a list of acronyms that may be used in this manual.

Table 1. Acronyms

| Acronym | Meaning                                                                       |

|---------|-------------------------------------------------------------------------------|

| EPROM   | Erasable Programmable Read Only Memory                                        |

| EEPROM  | Electronically Erasable Programmable Read<br>Only Memory                      |

| LCD     | Liquid Crystal Display                                                        |

| LED     | Light Emitting Diode                                                          |

| NMI     | Nonmaskable Interrupt                                                         |

| PIO     | Parallel Input / Output Circuit<br>(Individually Programmable Input / Output) |

| PRT     | Programmable Reload Timer                                                     |

| RAM     | Random Access Memory                                                          |

| RTC     | Real Time Clock                                                               |

| SIB     | Serial Interface Board                                                        |

| SRAM    | Static Random Access Memory                                                   |

| UART    | Universal Asynchronous Receiver Transmitter                                   |

## **Icons**

Table 2 displays and defines icons that may be used in this manual.

Table 2. Icons

| Icon        | Meaning         | lcon | Meaning      |

|-------------|-----------------|------|--------------|

| 66          | Refer to or see |      | Note         |

|             | Please contact  | A    | High Voltage |

| $\triangle$ | Caution         | Tip  | Tip          |

|             | Factory Default |      |              |

## Conventions

Table 3 lists and defines typographical conventions that may be used in this manual.

Table 3. Typographical Conventions

| Example   | Description                                                                                                                                    |  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------|--|

| while     | Courier font (bold) indicates a program, a fragment of a program, or a Dynamic C keyword or phrase.                                            |  |

| // IN-01  | Program comments are written in Courier font, plain face.                                                                                      |  |

| Italics   | Indicates that something should be typed instead of the italicized words (e.g., in place of <i>filename</i> , type a file's name).             |  |

| Edit      | Sans serif font (bold) signifies a menu or menu selection.                                                                                     |  |

|           | An ellipsis indicates that (1) irrelevant program text is omitted for brevity or that (2) preceding program text may be repeated indefinitely. |  |

| [ ]       | Brackets in a C function's definition or program segment indicate that the enclosed directive is optional.                                     |  |

| < >       | Angle brackets occasionally enclose classes of terms.                                                                                          |  |

| a   b   c | A vertical bar indicates that a choice should be made from among the items listed.                                                             |  |

## Pin Number 1

A black square indicates pin 1 of all headers.

#### Measurements

All diagram and graphic measurements are in inches followed by millimeters enclosed in parenthesis.

## Blank

## CHAPTER 1: **OVERVIEW**

CM7000 Overview + 13

### Introduction

The CM7000 is a microprocessor core module. The CM7000 combines a complete system engine with integrated development software. You build your own controller around the plug-in CM7000.

#### Features

- Small size:  $1.80'' \times 2.05''$  (45.7 mm × 52.1 mm)

- Microprocessor: Z180 running at 9.216 MHz or 18.432 MHz, including two DMA channels, two serial ports, and two programmable timers (PRTs)

- SRAM: 32K or 128K (512K factory-installed SRAM is also available)

- EPROM:

- CM7100—32-pin DIP socket accommodates up to 512K EPROM CM7200—128K flash EPROM at 128 bytes/sector (256K factory-installed flash EPROM is also available)

- I/O support: six chip-select lines, supporting 64 addresses each, control the application's hardware

- Low electromagnetic interference

- Software written for either CM7100 or CM7200 Series is binarycompatible with the other

## **Options**

The CM7000 is available with two types of memory—CM7100s have ROM and CM7200s have flash EPROM.

#### CM7100 Series

Table 1-1 lists the features of each model in the CM7100 Series.

| Model  | Features                                                                                         |

|--------|--------------------------------------------------------------------------------------------------|

| CM7100 | 18.432 MHz clock, 128K SRAM, 512-byte EEPROM, real-time clock, and ADM691 supervisor             |

| CM7110 | CM7100 with 9.216 MHz clock                                                                      |

| CM7120 | CM7100 with 9.216 MHz clock and 32K SRAM                                                         |

| CM7130 | CM7100 with 9.216 MHz clock and 32K SRAM. Without ADM691 supervisor, real-time clock and EEPROM. |

Table 1-1. CM7100 Series Features

14 • Overview CM7000

The CM7100 is available in one of the models listed in Table 1-1 or as part of the Evaluation Kit. The Evaluation Kit contains the following items.

- CM7110 with special EPROM containing sample programs.

- Prototyping Board.

- Manual (with schematics), cables, AC adapter, trial version of Dynamic C development software.

The trial version of Dynamic C included with the Evaluation Kit contains only the libraries associated with the Evaluation Kit. Once a decision is made to proceed with normal development, the standard or deluxe version of Dynamic C must be purchased. The Development Board supplied with the Developer's Kit and the development EPROM are also available for separate purchase.

For help with upgrading to a full-scale system, call your Z-World Sales Representative at (530) 757-3737.

A Developer's Kit is available for the CM7100. The Developer's Kit contains the following items.

- Development EPROM.

- Development Board, which plugs into the CM7100 EPROM socket to emulate ROM with RAM to make it easier to develop and debug large programs.

- Manual (with schematics), cables, and AC adapter.

A 128K EPROM and an LCD/Keypad module (the LCD/Keypad module requires a 9.216 MHz clock) are available separately.

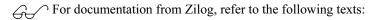

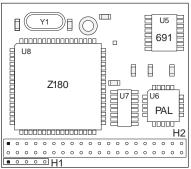

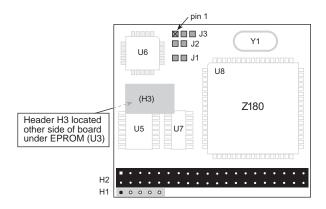

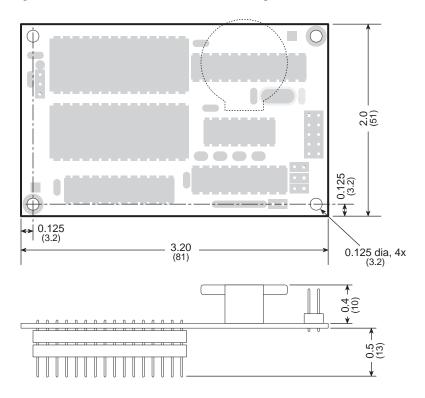

Figure 1-1 shows the CM7100 board layout.

Top Side

Microprocessor Side

Figure 1-1. CM7100 Board Layout

CM7000 Overview + 15

#### CM7200 Series

Table 1-2 lists the features of each model in the CM7200 Series.

Model Features

CM7200 18.432 MHz clock, 128K SRAM, real-time clock, ADM691 supervisor, and 128K flash EPROM

CM7210 CM7200 with 9.216 MHz clock

CM7220 CM7200 with 9.216 MHz clock and 32K SRAM

CM7230 CM7200 with 9.216 MHz clock and 32K SRAM.

Without ADM691 supervisor and real-time clock.

Table 1-2. CM7200 Series Features

A Developer's Kit is available for the CM7200. The Developer's Kit contains the following items.

- Prototyping Board.

- Manual (with schematics), cables and AC adapter.

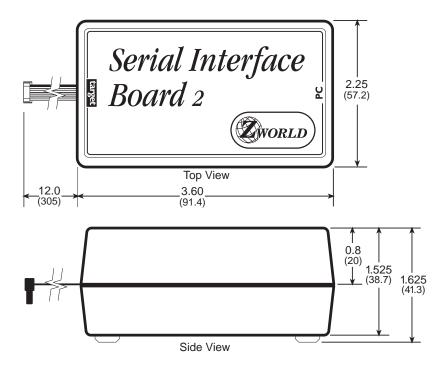

- Serial Interface Board 2.

The following optional accessories are available for the CM7200.

- Flash Programmer to program flash EPROM.

- 256K factory-installed flash EPROM.

- LCD/Keypad module (2 × 20 LCD and 2 × 6 keypad) for use with CM7200 modules with a 9.216 MHz clock.

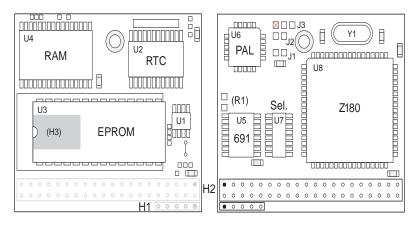

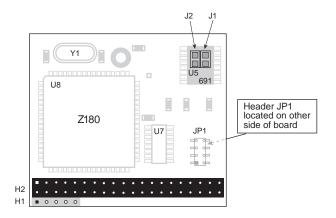

Figure 1-2 shows the CM7200 board layout.

Top Side

Microprocessor Side

Figure 1-2. CM7200 Board Layout

16 • Overview CM7000

## **Software Development and Evaluation Tools**

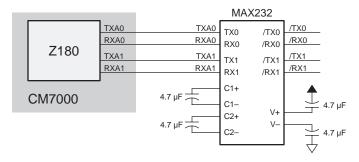

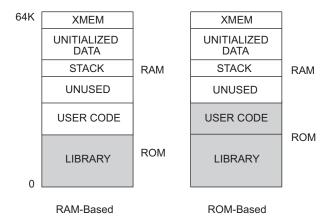

Dynamic C, Z-World's Windows-based real-time C language development system, is used to develop software for the CM7000. The host PC downloads the executable code through the CM7000's RS-232 serial port or through the Serial Interface Board 2 to one of the following places:

- battery-backed RAM,

- ROM written on a separate EPROM programmer and then substituted for the Z-World development EPROM, or

- · flash EPROM.

Dynamic C allows fast in-target development and debugging.

Z-World's Dynamic C reference manuals provide complete software descriptions and programming instructions.

For ordering information or more details about the various options and prices, call your Z-World Sales Representative at (530) 757-3737.

CM7000 Overview + 17

## Blank

18 • Overview CM7000

## CHAPTER 2: **GETTING STARTED**

## **Programming Setup**

Dynamic C, Z-World's C-language development system, is used to develop applications for the CM7000. As a program compiles, Dynamic C downloads it directly to the CM7000's memory via one of the PC COM ports. Serial communication is normally at 19,200 bps, and can be as high as 57,600 bps. The CM7000 remains connected to the PC in most instances while a program is undergoing development. The mechanics of connecting a CM7000 and a PC vary depending on the CM7000 version and the programming strategy.

The programming strategy for a CM7100 depends on the hardware setup. Only one programming method is available for the CM7200 regardless of whether the Developer's Kit or in-target development is used.

#### CM7100

Four methods are available to program the CM7100.

- 1. Using the Prototyping Board. This method is recommended for programming the CM7110 supplied in the Evaluation Kit. This CM7110 has a special EPROM that contains the BIOS and sample programs.

- Method 1 may also be used to program other CM7100s. Since an EPROM is not normally included with CM7100s, except for the CM7110 in the Evaluation Kit, which comes with a special EPROM, a custom EPROM with the contents of the Dynamic C 2903.BIN file must first be burned according to the details in the section "Programming EPROMs" in Chapter 3, "System Development."

- 2. Using the Development Board. The Development Board is included in the Developer's Kit with full Dynamic C, and is also sold separately.

- 3. Using the Development Board with full Dynamic C, and with the CM7100 embedded in your target system.

- 4. Directly in your system without a Development Board. This method requires some hardware setup and minor modifications to the Dynamic C EPROM code.

Methods 1 and 2 are normally used for evaluation or experimentation. Method 3 requires some hardware setup, and ultimately must be used to program a working system. Method 4 can be the fastest and most powerful.

Once program development has been completed, recompile the program for EPROM. An EPROM is burned in a separate operation and is then installed in the EPROM socket on the CM7100.

## CM7100 Method 1 — Prototyping Board

- Check to make sure the power to the Prototyping Board is not connected.

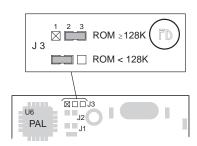

- 2. Check header J3 on the microprocessor side of the CM7100. The surface-mounted jumper should connect pins 2–3 to reflect the 128K memory of the special EPROM. This factory default setting is shown in Figure 2-1.

Figure 2-1. CM7100 Header J3 Configured for Special EPROM

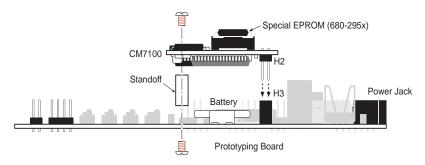

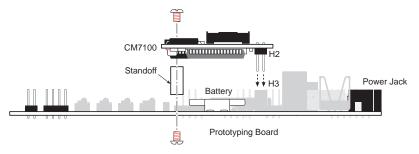

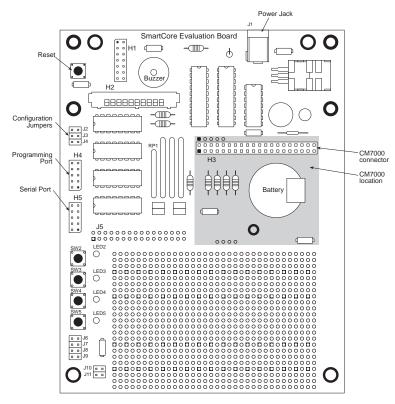

3. Plug the CM7100 into the Prototyping Board as shown in Figure 2-2. Plug header H2 of the CM7100 into connector H3 of the Prototyping Board. Pins 1 of the header and connector must match. The CM7100 will hang over the battery on the Prototyping Board. For maximum stability, install the supplied standoff between the CM7100 and the Prototyping Board.

Figure 2-2. Connecting CM7100 to Prototyping Board

4. If using the CM7110 from the Evaluation Kit, make sure the CM7110 has the special 32-pin EPROM (Z-World part number 680-295x) installed at U3 as shown in Figure 2-3. Custom-burned EPROM are also installed at location U3.

Figure 2-3. Installation of 32-pin EPROM

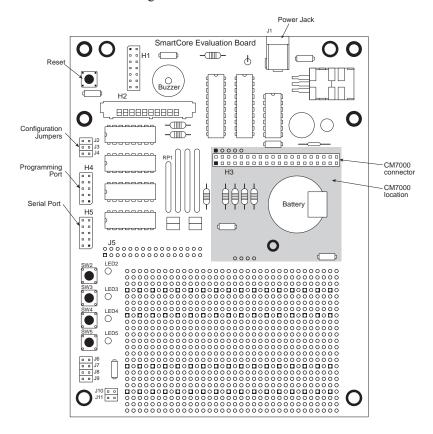

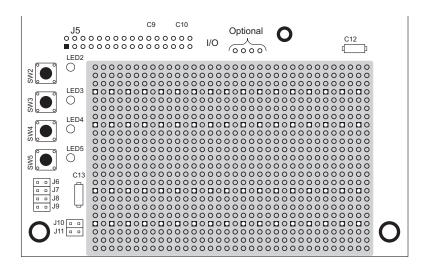

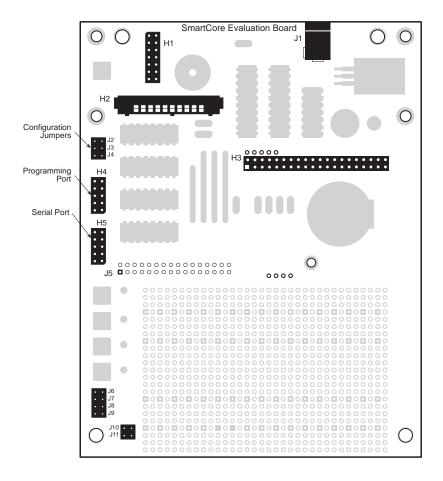

5. Place jumpers across headers J2, J3, and J4 on the Prototyping Board to enable headers J6–J11 on the Prototyping Board. The Prototyping Board is shown in Figure 2-4.

Figure 2-4. CM7100 Prototyping Board

It is necessary to place jumpers across headers J2, J3, and J4 to enable headers J6–J11 on the Prototyping Board. Note that this disables chip selects CS1, CS2, and CS3. The LEDs will not work when CS1 is disabled.

The BIOS on the special EPROM (Z-World part number 680-295x) supplied with the CM7110 in the Evaluation Kit does not support chip selects CS1, CS2, and CS3.

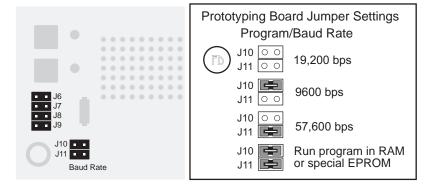

6. Set the Prototyping Board's jumpers. Jumpers across headers J10 and J11 affect the operational mode and the baud rate as shown in Figure 2-5. When both headers J10 and J11 are jumpered, the CM7100 checks headers J6–J9 at startup. If none of these headers is jumpered, the CM7100 will execute the program, if any, stored in RAM. If some of these headers are jumpered, a sample program stored in the special CM7100 EPROM will begin executing.

See Appendix F, "Prototyping Board," for more information on the Prototyping Board and the sample programs in the special EPROM.

Figure 2-5. CM7100 Prototyping Board Program/Mode Jumper Settings

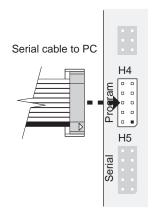

- 7. Connect the serial cable. Connect one end to the PC COM port. Then connect the 10-pin end to header H4 of the Prototyping Board as shown in Figure 2-6. Be careful to match the arrow on the connector to the location of pin 1 on header H4.

- 8. Apply power from the 9 V power supply to the Prototyping Board. The CM7100 is ready for programming, unless the jumpers were set in Step 6 to run a program stored in RAM or to run one of the sample programs stored in the special EPROM.

Figure 2-6. Serial Cable Connection to CM7100 Prototyping Board

### CM7100 Method 2 — Development Board

- Check to make sure the power to the Prototyping Board is not connected.

- 2. Check header J3 on the microprocessor side of the CM7100. The surface-mounted jumper should connect pins 2–3 to use the Development Board. This factory default setting is shown in Figure 2-1.

- 3. Plug the CM7100 into the Prototyping Board as shown in Figure 2-7. Plug header H2 of the CM7100 into connector H3 of the Prototyping Board. Pins 1 of the header and connector must match. The CM7100 will hang over the battery on the Prototyping Board. For maximum stability, install the supplied standoff between the CM7100 and the Prototyping Board.

Figure 2-7. Connecting CM7100 to Prototyping Board

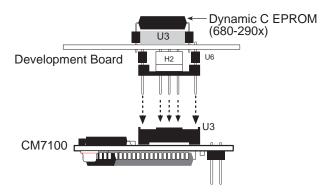

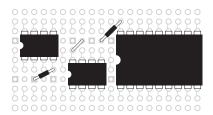

4. If an EPROM is installed in socket U3 on the CM7100, remove the EPROM. Plug a Dynamic C development EPROM (Z-World part number 680-290x) into the EPROM socket (U3) of the Development Board. See Figure 2-8.

Figure 2-8. Installation of CM7100 Development Board and Development EPROM

5. Plug the Development Board into the EPROM (U3) and H3 sockets on the CM7100 as shown in Figure 2-8. Headers U6 and H2 on the underside of the Development Board must match the CM7100 EPROM and H3 sockets exactly.

Be careful! The U6 and H2 pins on the Development Board are delicate and bend easily.

6. Check the jumpers on the Development Board. Figure 2-9 shows the locations of the relevant headers.

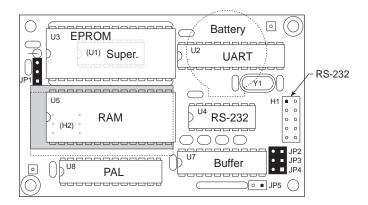

Figure 2-9. CM7100 Development Board

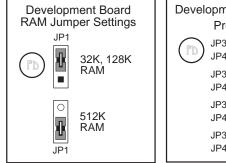

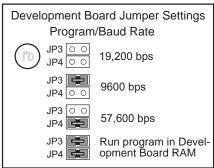

Figure 2-10 shows the jumper settings for different RAM sizes, operational modes, and baud rates.

Figure 2-10. CM7100 Development Board Jumper Settings

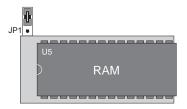

7. If you are using a 28-pin RAM chip, seat the chip in the RAM socket as shown in Figure 2-11.

Figure 2-11. Position of 28-Pin Chip in 32-Pin Socket

Figure 2-12. Serial Cable Connection to CM7100 Development Board

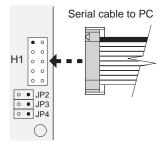

8. Connect the serial cable.

Connect one end to the PC

COM port. Then connect the

10-pin end to H1 of the

Development Board as shown

in Figure 2-12. Be careful to

match the arrow on the

connector to the location of

pin 1 on header H1.

9. Reconnect the 9 V power supply to the Prototyping Board. The CM7100 is ready for programming, unless the jumpers were set in Step 5 to run a program in the Development Board's RAM.

## CM7100 Method 3 — Embedded in System

Method 3 assumes that the CM7100 is already mounted in a system and that the CM7100 is properly connected. At a minimum, regulated power (+5 V) and ground must be provided.

The Development Board plugs into the EPROM socket of the CM7100. The Development Board emulates the system EPROM normally installed in the CM7100, providing up to 504K of program space in addition to the RAM on the CM7100 (used as a data space). The Development Board has its own RS-232 port and communicates directly with the PC during program development.

- 1. Disconnect power from the CM7100.

- 2. If an EPROM is installed in socket U3 on the CM7100, remove the EPROM. Plug a Dynamic C development EPROM (Z-World part number 680-290x) into the EPROM socket (U3) of the Development Board. See Figure 2-8.

- 3. Plug the Development Board into the EPROM (U3) and H3 sockets on the CM7100 as shown in Figure 2-8. Headers U6 and H2 on the underside of the Development Board must match the CM7100 EPROM and H3 sockets exactly.

Be careful! The U6 and H2 pins on the Development Board are delicate and bend easily.

- 4. Check header J3 on the microprocessor side of the CM7100. The surface-mounted jumper should connect pins 2–3 to use the Development Board. This factory default setting is shown in Figure 2-1.

- 5. Check the jumpers on the Development Board. Figure 2-9 shows the locations of the relevant headers.

- Figure 2-10 shows the jumper settings for different RAM sizes, and for the operational mode and baud rates.

- 6. If you are using a 28-pin RAM chip, seat the chip in the RAM socket as shown in Figure 2-11.

- 7. Connect the serial cable. Connect one end to the PC COM port. Then connect the 10-pin end to H1 of the Development Board as shown in Figure 2-12. Be careful to match the arrow on the connector to the location of pin 1 of H1.

- 8. Reconnect power to the CM7100. The CM7100 is ready for programming, unless the jumpers were set in Step 5 to run a program stored in the Development Board RAM.

## CM7100 Method 4 — In-Target Direct Development

It is possible to program directly through a CM7100's built-in serial port without using a Development Board. In this method, the program is held in RAM while the application is under development. At least 128K of RAM is highly recommended. Note that the CTS0 input must be asserted for channel z0 to transmit. Tie CTS0 to ground if RTS/CTS handshake support is not needed.

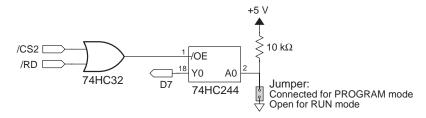

- 1. Build an input port into your hardware using one of the **/CS** lines. One bit of the input will specify whether the Dynamic C monitor in the EPROM enters RUN mode or PROGRAM mode.

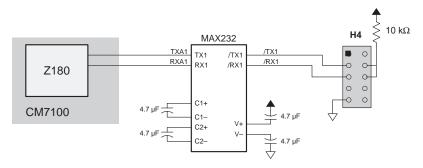

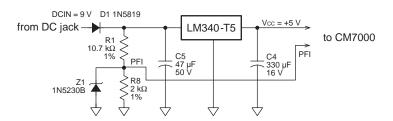

- 2. Build a serial driver into your system based on the one on the Prototyping Board (see Figure 2-13).

Figure 2-13. CM7100 Prototyping Board Serial Driver

If your serial driver has a 10-pin header that conforms to Z-World's programming cable, you will not need to build another programming cable. CTS and RTS are tied together and pulled up.

3. Six bytes of the Dynamic C EPROM (starting at 0x70 in the EPROM file) are reserved as indicated in Table 2-1.

| Address | Name Range               |        | Meaning                                                                                          |

|---------|--------------------------|--------|--------------------------------------------------------------------------------------------------|

| 0x70    | channel                  | 0,1    | Selects serial programming port.                                                                 |

| 0x71    | baud<br>rate             | 1–48   | Programming baud rate in multiples of 1200 bps: 8 = 9600 bps, 16 = 19,200 bps, 48 = 57,600 bps). |

| 0x72,73 | address 0x4000 to 0x417F |        | Address of input port (corresponds to /CS line), low-order bits in byte 72.                      |

| 0x74    | mask                     | 0x0-FF | Active bit(s) of input byte, one bit suffices.                                                   |

| 0x75    | polarity                 | 0,1    | Polarity of input bit.                                                                           |

Table 2-1. Dynamic C EPROM Addresses

Modify the Dynamic C EPROM file (in your Dynamic C directory) and burn a new EPROM with the appropriate new data.

When a system resets, the Dynamic C monitor in the EPROM consults the 6 bytes. If the monitor finds valid data, the system will start operating according to the data. The monitor will attempt to read the specified input port. If it is successful, the monitor will either enter programming mode (communicating with Dynamic C in a PC) or run the program stored in the CM7100's RAM.

For example, the C structure

| (70)    | 0x00   | serial channel 0    |

|---------|--------|---------------------|

| (71)    | 0x10   | 19,200 bps          |

| (72,73) | 0x4040 | /CS2                |

| (74)    | 0x80   | active bit is bit 7 |

(75) 0x00 active bit =  $0 \otimes PROGRAM$  mode else RUN mode

would work and might use an input port such as the one shown in Figure 2-14.

Figure 2-14. Input Port

With the standard CM7100 BIOS (2903 or later), setting the I/O address (bytes 0x72 and 0x73) to 0x0000 will force the CM7100 into development mode. This setting eliminates the need to use a RUN/PROGRAM jumper.

Direct development is not supported by the BIOS of the CM7110 included in the CM7100 Evaluation Kit.

## **Safeguards**

The following safeguards have been adopted.

- 1. If there is no valid program in RAM, the Dynamic C monitor will repeatedly go into a tight loop, forcing a watchdog timeout.

- 2. If byte 0x70 is not a 0 or 1, the monitor is forced to RUN mode.

- 3. If byte 0x71 is not a multiple of 8, the monitor is forced to RUN mode.

- 4. If bytes 0x72 and 0x73 have an address less than 0x4000 or greater than 0x417F, the monitor is forced to RUN mode.

The Dynamic C development EPROM has the six locations all set to 0xFF.

#### CM7200

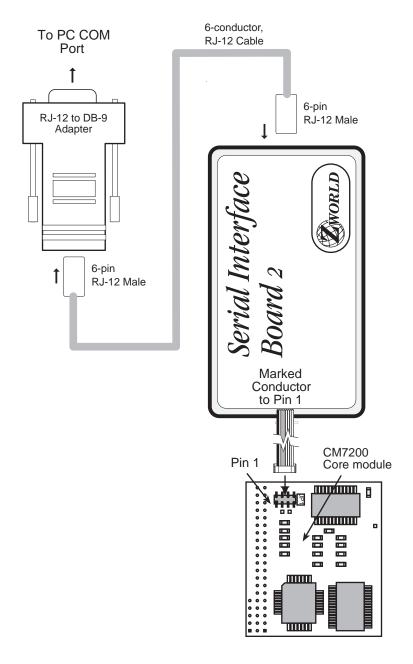

The CM7200 uses its Z180 microprocessor's CSI/O (clocked serial I/O) line for communicating with Dynamic C running on a host PC; Z-World's SIB22 makes the CSI/O port look just like an RS-232 port. Since the CM7200's flash EPROM is electrically reprogrammable in a circuit, the flash EPROM requires no ROM emulation during development. Consequently the CM7200's programming strategy is very simple when compared to the CM7100's.

## CM7200 Method 1 — Prototyping Board

- Check to make sure the power to the Prototyping Board is not connected.

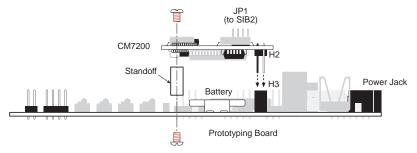

- 2. Plug the CM7200 into the Prototyping Board as shown in Figure 2-15. Plug header H2 of the CM7200 into connector H3 of the Prototyping Board. Pins 1 of the header and connector must match. The CM7200 will extend over the battery on the Prototyping Board. For maximum stability, install the supplied standoff between the CM7200 and the Prototyping Board.

Figure 2-15. Connecting CM7200 to Prototyping Board

- Connect the 6-conductor RJ-12 cable provided with the Developer's

Kit from the PC serial-port adapter to the SIB2 as shown in Figure 216. Connect the 2 mm ribbon cable from the SIB2 to header JP1 on the

CM7200. Be careful to match the arrow on the connector to Pin 1 of

JP1.

- 4. Set the baud rate of the host PC's COM port to 9600 bps, 19,200 bps, or 57,600 bps.

- 5. Apply power to the Prototyping Board. As a minimum, the power supply must have regulated +5 V and GND for the CM7200. The CM7200 is now ready for programming.

Figure 2-16. CM7200 Connection to Serial Interface Board 2

## CM7200 Method 2 — Embedded In System

- 1. Disconnect power from the system.

- 2. Connect the 6-conductor RJ-12 cable provided in the Developer's Kit from the PC's serial-port adapter to the SIB2.

- Connect the 2 mm ribbon cable from the SIB2 to header JP1 on the CM7200. Be careful to match the arrow on the connector to Pin 1 of JP1.

- 4. Set the baud rate of the host PC's COM port to 9600 bps, 19,200 bps, or 57,600 bps.

- 5. Reconnect power to the system. As a minimum, the power supply must have regulated +5 V and GND for the CM7200. The system is now ready for programming.

## CHAPTER 3: SYSTEM DEVELOPMENT

## **General Description**

The CM7000 is a complete system engine that contains the microprocessor and memory around which a controller is built.

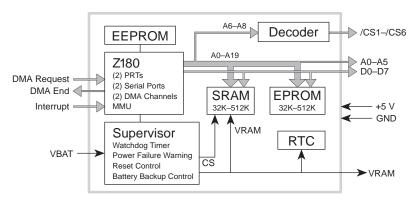

Figure 3-1 shows a block diagram of the CM7100.

Figure 3-1. CM7100 Block Diagram

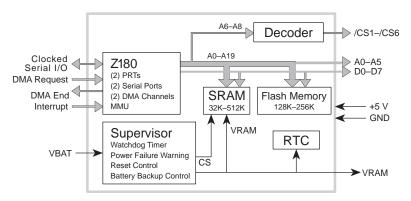

Figure 3-2 shows a block diagram of the CM7200.

Figure 3-2. CM7200 Block Diagram

The microprocessor is a Z180, running at either 9.216 MHz or 18.432 MHz. The Z180 has two asynchronous serial ports, two DMA channels, and two programmable-reload timers (PRTs). Two of the Z180's interrupt lines are available for use in the system.

The Z180 supports a 1M address space with its internal memory management unit (MMU). It has 20 address lines. The data path is 8 bits wide—lines D0–D7.

Six chip-select lines (/CS1–/CS6) enable one of six groups of 64 input/output addresses. Thus, single-tier addressing can directly access 384 distinct devices or registers.

The optional power-supervisor IC, an ADM691, provides several services. It has a watchdog timer, performs power-failure detection, and supports battery backup. When power fails, it protects the RAM from being accidentally overwritten.

Your application can obtain the time and the date from the optional real-time clock IC, an Epson 72423.

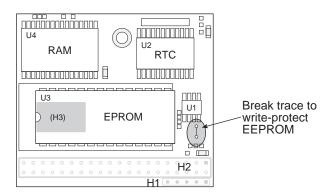

The optional CM7100 EEPROM (24C04) stores 512 bytes of nonvolatile data for system constants and other important values. The upper 256 bytes of the EEPROM can be write-protected by breaking a circuit board trace. The CM7200 simulates the EEPROM in its flash memory. This simulation is software-compatible with the CM7100's Dynamic C EEPROM function calls.

See Appendix D, "EEPROM," for more information on the software function calls and details about write-protecting the CM7100 EEPROM.

## **Interface Description**

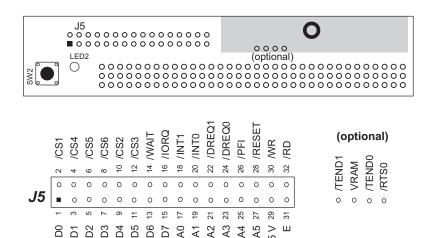

The CM7000 physical interface to a controller is a 40-pin header (H2) with a 5-pin extension (H1). Figure 3-3 shows the location of header H2 and extension H1.

Figure 3-3. Location of Header H2 and Extension H1

The 40-pin header (H2) plugs directly into a 40-pin connector on the controller's printed circuit board. The connector on the Prototyping Board provides an example of this arrangement. The headers use 0.025" square pins on 0.1" centers.

The 5-pin interface extension (H1) comprises five plated through-holes, allowing an additional 5-pin header to be added if needed.

Figure 3-4 provides the pinouts for header H2 and extension H1.

| 40-Pin Interface<br>H2 |    |   |   |    | face             | Extension<br>H1        |

|------------------------|----|---|---|----|------------------|------------------------|

| GND                    | 1  | • | 0 | 2  | +5 V (regulated) | 1 ■ GND                |

| VBAT                   | 3  | 0 | 0 | 4  | /PFI             | 2 O VRAM               |

| D1                     | 5  | 0 | 0 | 6  | /RESET           | 3 O /TENDO             |

| D2                     | 7  | 0 | 0 | 8  | /CS5             | 4 o /TEND1             |

| D3                     | 9  | 0 | 0 | 10 | /CS6             | 5 o /RTS0              |

| D4                     | 11 | 0 | 0 | 12 | /CS1             |                        |

| D5                     | 13 | 0 | 0 | 14 | /CS2 "/"         | signals are active low |

| D6                     | 15 | 0 | 0 | 16 | D0 / 3           | signals are active low |

| /CS4                   | 17 | 0 | 0 | 18 | A0               |                        |

| A1                     | 19 | 0 | 0 | 20 | /CS3             |                        |

| /INT1                  | 21 | 0 | 0 | 22 | /INT0            |                        |

| A3                     | 23 | 0 | 0 | 24 | A2               |                        |

| /WAIT                  | 25 | 0 | 0 | 26 | A4               |                        |

| D7                     | 27 | 0 | 0 | 28 | A5               |                        |

| /WR                    | 29 | 0 | 0 | 30 | /IORQ            |                        |

| /DREQ0                 | 31 | 0 | 0 | 32 | /RD              |                        |

| /DREQ1                 | 33 | 0 | 0 | 34 | TXA1             |                        |

| /CTS0                  | 35 | 0 | 0 | 36 | RXA0             |                        |

| TXA0                   | 37 | 0 | 0 | 38 | RXA1             |                        |

| E                      | 39 | 0 | 0 | 40 | GND              |                        |

Figure 3-4. CM7000 Pinouts for Header H2 and Extension H1

Table 3-1 lists the CM7000 interface signals.

Table 3-1. CM7000 Interface Signals

| Signal<br>Name    | Direction | Description                                                                                                                                                                                                                                                                                                                       |

|-------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0-A5             | Out       | Address lines. CMOS compatible.                                                                                                                                                                                                                                                                                                   |

| D0-D7             | Bi.       | Data lines. TTL/CMOS compatible.                                                                                                                                                                                                                                                                                                  |

| /RD               | Out       | Read. Defines a read cycle. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                                                                      |

| /WR               | Out       | Write. Defines a write cycle. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                                                                    |

| /INT0             | In        | Maskable interrupt request 0. TTL/CMOS compatible.                                                                                                                                                                                                                                                                                |

| /INT1             | In        | Maskable interrupt request 1. TTL/CMOS compatible.                                                                                                                                                                                                                                                                                |

| /IORQ             | Out       | I/O Request. Defines an I/O cycle. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                                                               |

| /CS1-<br>/CS6     | Out       | Chip selects (6). Each selects a group of 64 I/O addresses. TTL/CMOS compatible                                                                                                                                                                                                                                                   |

| /WAIT             | In        | Wait line. Generates wait states for I/O cycles. Allows access to slow I/O devices. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                              |

| /DREQ0,<br>/DREQ1 | In        | DMA request lines. Requests movement of one byte of data on specified DMA channel (0 or 1). Can be edge-or level-sensitive. Ignored during memory-to-memory and serial-to-memory operations. Directly connected to Z180. TTL/CMOS compatible. /DREQ0 can be a clock input or output for serial port 0, running at 16 × baud rate. |

| /TEND0,<br>/TEND1 | Out       | DMA "transfer-end" lines. Signals the end of a DMA transfer on channel 0 or 1. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                   |

| TXA0,<br>TXA1     | Out       | Transmit. Serial data for channels 0 and 1. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                                                      |

| RXA0,<br>RXA1     | In        | Receive. Serial data for channels 0 and 1. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                                                       |

| /CTS0             | In        | Clear-to-send, channel 0. Serial-control signal. Channel 0 will not transmit when this line is high. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                             |

| /RTS0             | Out       | Request-to-send, channel 0. Serial control signal. Directly connected to Z180. TTL/CMOS compatible.                                                                                                                                                                                                                               |

continued...

Table 3-1. CM7000 Interface Signals (concluded)

| Signal<br>Name | Direction | Description                                                                                                                                      |

|----------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT           | In        | Battery voltage. Connects to the ADM691 supervisor. Must be grounded if no battery installed.                                                    |

| VRAM           | Out       | Battery-backed supply voltage for RAM, real-time clock, and other devices.                                                                       |

| PFI            | In        | Power failure input. Connects to the ADM691 supervisor, which generates a nonmaskable interrupt (NMI) when this line falls below 1.3 V ± 0.05 V. |

| /RESET         | Bi.       | System reset. Driven by the ADM691 supervisor. Must be pulled up when supervisor is not installed.                                               |

| Е              | Out       | 6800-compatible timing reference. Directly connected to Z180. TTL/CMOS compatible.                                                               |

# CM7000 Subsystems

This section describes the various subsystems and their signals. Source-code software drivers are available for most of these subsystems. Sample programs (included with Dynamic C) are provided.

See Appendix J, "Sample Applications," for sample circuits to illustrate the use of the CM7000.

#### **DMA**

Two DMA channels are accessible on the CM7000 interface and support memory-memory and memory-I/O transfers. The transfer modes supported by the Z180 are request, burst, and cycle-steal. DMA transfers can access the full 1M address range with a block length of 64K, and can cross over 64K boundaries. Transfers can occur every 6 clock cycles. The DMA channels can also function as high-speed counters, operating at up to 500 kHz (on the 9.216 MHz CM7000) by using the request line as a counter input.

The signals /DREQ0 and /DREQ1 are the DMA-request lines. The DMA channels monitor these lines to determine when an external device is ready for a read or write operation. The signals /TEND0 and /TEND1 are the "transfer end" lines. A DMA device asserts these outputs during the last write cycle of a DMA operation. By monitoring these lines, a system can detect the end of a DMA transfer.

The DMA channel can be programmed to be either edge or level sensitive. If a DMA channel is edge triggered, a single byte gets transferred over the DMA channel when the DMA device asserts the request line. If the DMA channel is level sensitive, multiple bytes will continue to transfer as long as the DMA device asserts the request line (that is, holds it low).

Channel 0 performs memory-memory and memory-I/O transfers. Such transfers include memory-mapped I/O and transfers to and from the serial channels. The transfer modes for Channel 0 are burst and cycle-steal. Channel 0 has memory-address increment, decrement and no-change modes.

Channel 1 performs only memory-I/O transfers. It supports memory address increment and decrement.

Channel 0 has a higher priority than Channel 1.

## **DMA Registers**

Table 3-2 lists the registers associated with the DMA channels.

Table 3-2. DMA Registers

| Register      | Address | Description         |  |

|---------------|---------|---------------------|--|

|               | Chanr   | nel 0               |  |

| SAR0          | 0x20-22 | Source Address      |  |

| DAR0          | 0x23-25 | Destination Address |  |

| BCR0          | 0x26-27 | Byte Count          |  |

|               | Chanr   | nel 1               |  |

| MAR1          | 0x28-2A | Memory Address      |  |

| IAR1          | 0x2B-2C | I/O Address         |  |

| BCR1          | 0x2E-2F | Byte Count          |  |

| Both Channels |         |                     |  |

| DSTAT         | 0x30    | DMA Status          |  |

| DMODE         | 0x31    | DMA Mode            |  |

| DCNTL         | 0x32    | DMA Control         |  |

Memory-address registers span 20 bits. I/O-address registers, on the other hand, span only 16 bits. The byte-count register has 16 bits. The higher order bits of the registers are stored in the bytes with higher addresses.

For details on DMA registers and timing, refer to the Zilog **Z180 MPU User's Manual** and the sample Dynamic C programs SC1DM232.C and SC1DMAPW.C.

#### Software

Table 3-3 lists Dynamic C functions that support the DMA channels.

Table 3-3. DMA Library Functions

| Function               | Description                                                                                                                               | Library     |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| DMA0Count<br>DMA1Count | DMA channel acts as a high-speed counter, interrupting when done.                                                                         | DRIVERS.LIB |

| DMASnapShot            | Reads the number of pulses a DMA channel has counted.                                                                                     | DRIVERS.LIB |

| DMA0_Off<br>DMA1_Off   | Turns DMA channel off.                                                                                                                    | DMA.LIB     |

| DMA0_SerialInit        | Initializes a serial port (0 or 1) for DMA transfer.                                                                                      | DMA.LIB     |

| DMAO_Rx<br>DMAO_Tx     | Initiates a DMA transfer (Rx = receive, Tx = transmit) from a serial port.                                                                | DMA.LIB     |

| DMA0_MIO<br>DMA1_MIO   | Initiates a DMA transfer from memory to an I/O port. The external device must generate a negative pulse to request each byte transferred. | DMA.LIB     |

| DMA0_MM                | Initiates a memory-to-memory transfer.                                                                                                    | DMA.LIB     |

| DMA0_IOM<br>DMA1_IOM   | Initiates a DMA transfer from an I/O port to memory. The external device must generate a negative pulse to request each byte transferred. | DMA.LIB     |

The *Dynamic C Function Reference* manual describes these functions in detail.

## **Programmable Timers**

The Z180 has a two-channel programmable reload timer (PRT). Each channel (PRT0 and PRT1) has a 16-bit down-counter, TMDR, and a 16-bit reload register, RLDR. A single 8-bit timer-control register, TCR, sets up both timers. The down counters decrement every 20 clocks (2.17  $\mu$ s at 9.216 MHz). When the counters reach 0, they automatically reinitialize with the value stored in their respective reload registers.

The two channels are disabled at system reset. By manipulating the bits of the TCR, the timers can be made to cause an interrupt when they time out. Counting can also be enabled and disabled.

When reading the TMDR registers, read the low byte first, then read the high byte. The accuracy of the reading depends on this order. Before writing to a TMDR, you must stop the channel by setting the appropriate bits in the TCR. In general, do not set a reload register unless you have first stopped its timer channel.

Refer to the **Z180 MPU User's Manual** for details on the operation of the PRT.

#### Software

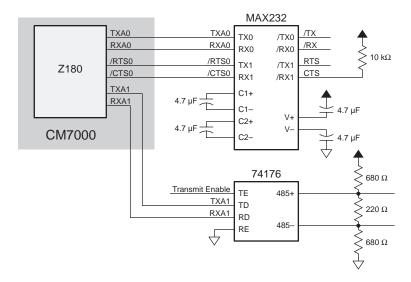

Table 3-4 lists Dynamic C functions that support the programmable reload timer.

Table 3-4. Programmable Timer Library Functions

| Function                           | Description                                                                                             | Library     |

|------------------------------------|---------------------------------------------------------------------------------------------------------|-------------|

| <pre>init_timer0 init_timer1</pre> | Places a count in the timer's reload register.                                                          | DRIVERS.LIB |

| timer0_isr                         | Timer 0 interrupt service routine.<br>Runs RTK (Real-Time Kernel).                                      | DRIVERS.LIB |

| int_timer1                         | Timer 1 interrupt service routine. Drives a beeper and keypad. Runs RTK if <b>RUNKERNEL</b> is defined. | KDM.LIB     |

| Tdelay                             | Waits specified number of milliseconds using timer 1.                                                   | DRIVERS.LIB |

| lk_tdelay                          | Similar to <b>Tdelay</b> .                                                                              | KDM.LIB     |

| lk_int_timer1                      | Similar to int_timer1.                                                                                  | KDM.LIB     |

| lg_init_keypad                     | Initializes timer 1, KDM keypad driver, and graphic LCD.                                                | KDM.LIB     |

The *Dynamic C Function Reference* manual describes these functions in detail.

#### **EPROM**

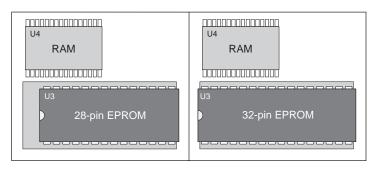

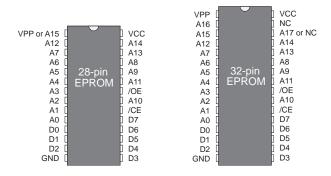

#### CM7100

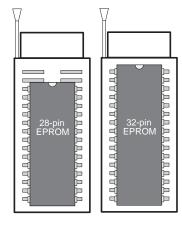

The CM7100 has a 32-pin socket (U3) that accepts 32K to 512K EPROM. The socket accepts either 28-pin or 32-pin EPROM chips. The access time must be less than 70 ns at 18 MHz, or less than 100 ns at 9 MHz.

Figure 3-5 shows how to seat the EPROM chip in the socket according to the number of pins.

Figure 3-5. Placement of 28-pin and 32-pin EPROM on CM7100

Header J3 on the microprocessor side of the CM7100 reflects the EPROM size, as shown in Figure 3-6.

The standard EPROM for the CM7100, Z-World part number 680-290x, supports the full Dynamic C software-development system. This standard EPROM has 28 pins.

Figure 3-6. CM7100 Header J3 Configurations for Different EPROM Sizes

A special 32-pin 128K EPROM (Z-World part number 680-295x) comes with the CM7100 Evaluation Kit. This special EPROM supports the trial version of Dynamic C that comes with the kit, and contains eight sample programs.

When using the CM7100 Development Board (ROM emulator), header J3 on the CM7100 must have pins 2–3 connected. This configuration is the factory default. Also note that the connection on header J3 is a *soldered* jumper consisting of a  $0 \Omega$  resistor.

## **Programming EPROMs**

Dynamic C can be used to create a file for programming an EPROM by selecting the **Compile to File** option in the **COMPILE** menu with the standard EPROM (Z-World part number 680-290x) installed. The CM7100 must be connected to the PC running Dynamic C during this step because essential library routines must be uploaded from the standard EPROM and linked to the resulting file. The output is a binary file (optionally an Intel hex format file) that can be used to build an application EPROM. The application EPROM is then programmed with an EPROM programmer that reads either a binary image or the Intel hex format file. The resulting application EPROM can then replace the standard EPROM.

When doing program development with Dynamic C, it is best to use a 128K SRAM or larger. Dynamic C will work with a 32K SRAM, but the total program space will be limited to 16K of root and 16K of extended memory. This is enough for many programs, but it is inconvenient to run out of memory during development. Once a program is burned into EPROM, there is no reason to use SRAM larger than 32K unless the data space is larger than 32K.

## **Choosing EPROMs**

Socket U3 can accommodate several different types of EPROMs, including the following.

| 27C256 | 32K  | 28 pins |

|--------|------|---------|

| 27C512 | 64K  | 28 pins |

| 27C010 | 128K | 32 pins |

| 27C020 | 256K | 32 pins |

# Copyrights

The Dynamic C library is copyrighted. Place a label containing the following copyright notice on the EPROM whenever an EPROM that contains portions of the Dynamic C library is created.

©1991-1995 Z-World, Inc.

Your own copyright notice may also be included on the label to protect your portion of the code.

Z-World grants purchasers of the Dynamic C software and the copyrighted CM7100 EPROM permission to copy portions of the EPROM library as described above, provided that:

- 1. The resulting EPROMs are used only with the CM7100 cores manufactured by Z-World, and

- 2. Z-World's copyright notice is placed on all copies of the EPROM.

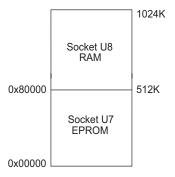

#### CM7200

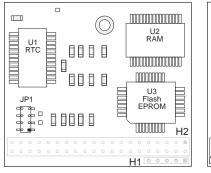

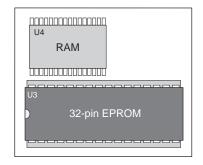

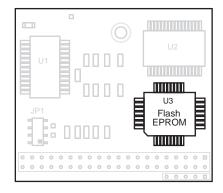

The CM7200 has a 32-pin flash EPROM soldered to the board at U3, as shown in Figure 3-7.

The standard flash EPROM for the CM7200 is a 128K AT29C010A. A 256K AT29C020 chip is available as an option.

Unlike most memory devices, which program a bit or byte at a time, flash EPROM programs a *sector* at a time. That is, even if only a single byte within a sector needs updating, the CM7200 overwrites the entire sector. All bytes not specified in the sector being programmed will erase to 0xFF.

Figure 3-7. Location of CM7200 Flash EPROM

Write cycles execute under both software and hardware data protection. These extra measures prevent invalid write cycles to the flash EPROM that would otherwise possibly corrupt a program or data.

Read operations access the flash EPROM just like an EPROM. The access time must be less than 70 ns for the 18 MHz CM7200, or less than 90 ns for 9 MHz versions.

The CM7200 uses a portion of its flash EPROM to simulate the 512 bytes of EEPROM. However, the access times for the flash EPROM are different from EEPROM. The CM7200 executes the same Dynamic C EEPROM function calls as the CM7100, accommodating hardware differences in its BIOS. An 8-byte section of the flash EPROM contains the CM7200 BIOS.

Dynamic C software drivers handle the read and write operations.

Flash EPROM is rated for 10,000 writes. In practice, flash EPROM has performed for up to 100,000 writes. Z-World recommends that any writes to the flash EPROM be made by the programmer rather than automatically by the software to maximize the life of the flash EPROM.

If you modify the driver software, do not overwrite the sections of the flash EPROM that contain the BIOS and that simulate the EEPROM.

#### **SRAM**

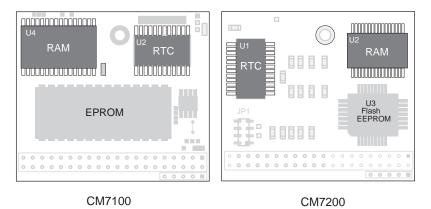

The RAM is not socketed, but is soldered to the board as shown in Figure 3-8. CM7000s may be ordered with 32K or 128K RAM already installed. CM7000s with 512K RAM are also available.

Figure 3-8. Locations of CM7100 and CM7200 SRAM and RTC

The ROM addresses range from 0x0 to 0x7FFFF. The range of RAM addresses depends on the RAM chip as shown in Table 3-5.

SRAM Size

Address Range

32K

0x80000 to 0x87FFF

128K

0xA0000 to 0xBFFFF

512K

0x80000 to 0xFFFFF

Table 3-5. SRAM Addresses

The CM7000 address decoder makes data *appear* to be replicated. Data in 32K RAM appear to be replicated 16 times throughout the range 0x80000–FFFFF. Data in 128K RAM appear to be replicated throughout the range 0xE0000–FFFFF.

#### **EEPROM**

The CM7100 has an optional 512-byte EEPROM at location U1. The EEPROM is nonvolatile memory and holds system constants. The CM7200 emulates this EEPROM in its flash EPROM, and executes all of Dynamic C's EEPROM function calls. Consequently, despite the dissimilar hardware, the memory map for both versions is exactly the same.

See Appendix D, "EEPROM," for more information on the software function calls and details about the EEPROM.

# Real-Time Clock (RTC)

The CM7000 has an optional Epson 72423 chip as shown in Figure 3-8. The chip stores time and date, and accounts for the number of days in a month, and for leap year. A user-supplied backup battery will allow the values in the RTC to be preserved if a power failure occurs.

The Dynamic C function library DRIVERS. LIB provides the following RTC functions.

tm\_rd

Reads time and date values from the RTC.

tm\_wr

Writes time and date values into the RTC.

The *Dynamic C Function Reference* manual describes these functions and the associated data structure tm.

The following points apply when using the RTC.

- 1. The AM/PM bit is 0 for AM, 1 for PM. The RTC also has a 24-hour mode.

- 2. Set the year to 96 for 1996, 97 for 1997, and so on.

Constantly reading the RTC in a tight loop will result in a loss of accuracy.

# Power Management

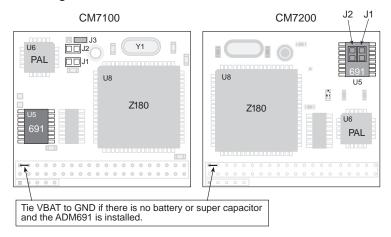

The CM7000 has an optional ADM691 supervisor chip, whose location is shown in Figure 3-9.

Figure 3-9. Locations of ADM691 Supervisor Chip and Associated Headers

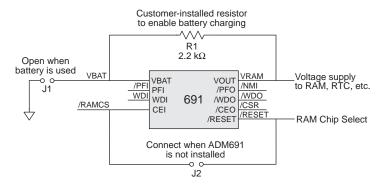

If the ADM691 supervisor chip is installed, and there is no battery or super capacitor, connect the VBAT input to ground using the VBAT pin of header H2 as shown in Figure 3-9. Alternatively for the CM7100, a jumper may be soldered across header J1. The grounding keeps the ADM691 VIN from floating.

If the CM7100 ADM691 supervisor chip is removed, solder a jumper across header J2. J2 connects the **/RAMCS** signal to the RAM. Further, you must connect VRAM to  $\pm$ 5 V. One way to make this connection is to solder together pads 2 and 3 at U5.

Figure 3-10 provides a schematic representation of these connections.

Figure 3-10. CM7100 Power Management Circuit

For the CM7200, solder a jumper across headers J1 and J2, located under the ADM691 chip (U5). J1 connects the /RAM signal to the RAM, and J2 provides power to the RAM. Further, you must connect VRAM to +5 V. One way to make this connection is to solder together pads 2 and 3 at U5.

Conversely, if a supervisor IC is installed on a CM7000 shipped from the factory without one, you would first have to remove the jumpers at headers J1 and J2 on the CM7200, and from header J2 on the CM7100.

Be sure *not* to connect VBAT to ground if the ADM691 is present *and* a battery or a super capacitor has been included in the system.

The ADM691 chip performs the following services.

- · Watchdog timer resets the microprocessor if software "hangs."

- Performs a power-failure shutdown and reset.

- Generates an "early warning" power-failure interrupt (PFI) that lets the system know when power is about to fail.

- Memory protection feature prevents writes to RAM when power is low.

- Supports battery or super capacitor backup.

## **Handling Power Fluctuations**

During a normal power-down, an interrupt service routine is used in response to a nonmaskable interrupt (NMI) to save vital state information for the application for when power recovers. The amount of code that the interrupt service routine can execute depends on the rate of decrease of voltage to the controller.

Theoretically, a power failure would cause a single NMI. Then, the interrupt service routine would restore the previous state data when the voltage recovers.

However, fluctuations in the DC input line could cause the supervisor IC to see multiple crossings of the 1.3 V input power-reset threshold. These multiple negative-edge transitions would, in turn, cause the processor to see multiple NMIs.

When the Z180 generates an NMI, it saves the program counter (PC) on the processor's stack. It next copies the maskable interrupt flag, IEF1, to IEF2 and zeroes IEF1. The Z180 will restore saved state information when it executes a RETN (return from nonmaskable interrupt) instruction.

See Appendix C, "Memory, I/O Map, and Interrupt Vectors," for more information on interrupts.

Ideally, the processor should be able to pop the stack and return to the location where the program was first interrupted. But the original IEF1 flag is not recoverable because the second and subsequent NMIs will have saved IEF1 = 0 to IEF2. Also, depending on the number of fluctuations of the DC input (and hence, the number of stacked NMIs), the processor's stack can overflow, possibly into your program's code or data.

The following sample program shows how to handle an NMI. This program assumes that the controller monitors power failures and that the CM7000's watchdog timer is enabled.

```

main(){

}

char dummy [24];

#define NMI_BIT

0

; bit 0

#JUMP VEC NMI VEC myint

#asm

myint::

ld

sp,dummy+24

; force stack pointer

; to top of dummy vector

; to prevent overwriting

; code or data

do whatever service, within allowable execution time

```

```

loop:

call hitwd

; make sure no watchdog reset

; while low voltage

ld

bc,NMI

; load the read NMI register

; to bc

in

; read the read NMI register

a,(c)

; for /PFO

NMI BIT, a ; check for status of /PFO

z,loop

jr

; wait until the brownout

; clears

timeout:

; then...a tight loop to

; force a watchdog timeout,

timeout ; resetting the Z180

αĖ

#endasm

```

If the watchdog is not enabled, the following sample program can be used to force the processor to restart execution at 0x0000.

```

char dummy[24];

#define NMI_BIT 0 ; bit 0

#JUMP_VEC NMI_VEC myint

#asm

myint::

ld sp,dummy+24

; reset stack pointer

; to top of dummy array

; to prevent overwriting

; user code/data space

do whatever service, within allowable execution time

loop:

ld

bc,NMI

; load the read NMI register

; to bc

in a,(c)

; read the read NMI register

; for /PF0

bit NMI_BIT,a ; check for status of /PF0

jr

z,loop

; wait until the brownout

; clears

restart:

1d a,0xE2 ; make sure 0x0000 points

; to start of EPROM BIOS

out0 (CBAR),a

; set the CBAR

0000h

; jump to logical (also

jр

; physical) address 0x0000

```

Of course, if the DC input voltage continues to decrease, then the controller will just power down.

If the watchdog timer is enabled, call the Dynamic C function hitwd during the power-failure service routine to make sure that the watchdog timer does not time out and thereby reset the processor. The controller can continue to run at low voltages, and so it might not be able to detect the low-voltage condition after the watchdog timer resets the processor.

#endasm

## The Watchdog Timer

To increase reliability, the ADM691's watchdog timer forces a system reset if a program does not notify the supervisor nominally every second. The assumption is that if the program fails to "hit" the watchdog, the program must be stuck in a loop or halted. The Dynamic C function for hitting the watchdog timer is hitwd. To hold the watchdog timer at bay, make a call to hitwd in a routine that runs periodically at the lowest software priority level.

A program can read the state of the **/WDO** line with a call to **wderror**. This makes it possible to determine whether a watchdog timeout occurred. The following sample program shows how to do this when a program starts or restarts.

```

main() {

if( wderror() ) wd_cleanup();

hitwd();

...

}

```

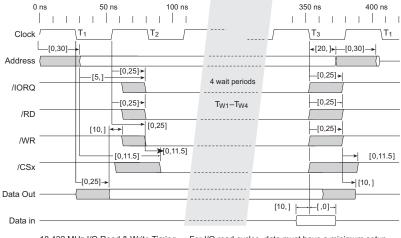

#### Power Shutdown and Reset

When  $V_{\rm CC}$  (+5 V) drops below  $V_{\rm MIN}$  (between 4.5 V and 4.75 V), the ADM691 supervisor asserts /RESET and holds it until  $V_{\rm CC}$  goes above  $V_{\rm MIN}$  and stays that way for at least 50 ms. This delay allows the system's devices to power up and stabilize before the CPU starts.

## PFI "Early Warning"

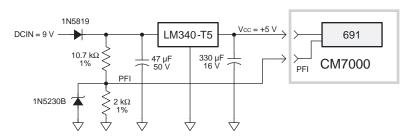

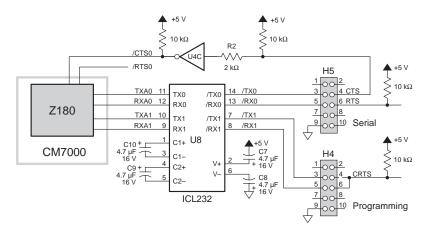

A power supply like that of the Prototyping Board (Figure 3-11) allows power failures to be detected before they cause operational failures. Connect the signals PFI and  $V_{CC}$  (+5 V) to the CM7000 via header H2.

Figure 3-11. Prototyping Board Power Supply

When PFI drops below 1.3 V  $\pm$  0.05 V (i.e., DCIN drops below  $\sim$ 7.5 V), the supervisor asserts /NMI (nonmaskable interrupt), and allows the program to clean up and get ready for shutdown. The underlying assumption is that PFI will cause the interrupt during a power failure before the ADM691 asserts /RESET.

If the CM7000 has no ADM691 supervisor, solder together pads 9 and 10 at U5 to connect **PFI** directly to /**NMI** for a nonmaskable interrupt line.

#### **Memory Protection**

When /RESET is active, the ADM691 supervisor disables the RAM chipselect line, preventing accidental writes.

## **Battery/Super Capacitor Backup**

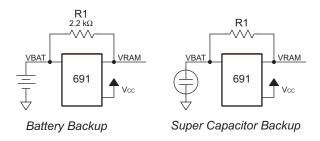

You can connect a battery or super capacitor to protect data in the RAM and RTC. Solder a connector across pins 1–3 on header H2. Connect the battery or the super capacitor across VBAT and ground, as shown in Figure 3-12. Use a resistor to recharge the battery (if it is rechargeable) or the super cap. Make sure jumper J1 on the CM7100 is not connected.

The RAM cannot be battery-backed unless the ADM691 or a similar supervisor chip is present.

Figure 3-12. Battery or Super Capacitor Installation

VRAM, the voltage supplied to the RAM and RTC, can also protect other devices attached to the system against power failures. The ADM691 supervisor switches VRAM to VBAT or  $V_{\rm CC}$ , whichever is greater. (To prevent "hunting," the switchover actually occurs when  $V_{\rm cc}$  is 50 mV higher than VBAT.)

Both the RAM and the RTC require 2 V or more to retain data. A 3 V lithium battery (such as the coin-type CR2325 from Panasonic) works well. The RTC draws 3  $\mu$ A during powerdown; the RAM draws only 1  $\mu$ A. The CR2325 is rated at 185 mA·h, and will provide current for a total downtime of 46,250 hours or 5.27 years.

The circuit draws no current from the battery once regular power is applied. The standby current for the RAM depends strongly on the storage temperature.

An alternative to a battery is a large capacitor and resistor that create an RC discharge circuit on the VBAT line. When power is applied, the capacitor will charge up until it reaches VRAM. When power is removed, the capacitor will power the RAM and RTC until discharged. As stated above, the RAM and RTC require a total of 4  $\mu$ A. This current draw means that the capacitor's full backup time is approximately 725 ks/F.

The larger the value of this capacitor, the longer the available backup time. Connect this capacitor between the VBAT line and ground, as shown in Figure 3-12. The CM7000 provides a resistor location (R1) to add a series resistor to complete an RC charging circuit. The value of this resistor affects the recharge time and limits the load on the power supply as the capacitor recharges. The resistor has an insignificant effect during discharge because the resistance from VBAT to VRAM on the ADM691 is typically 15  $\Omega$ .

The capacitor will recharge to 98 percent of its nominal capacity in about four time constants ( $4 \times RC$ ). This recharge time limits the system's ability to withstand closely spaced power outages. Panasonic sells a line of gold capacitors ideally suited for this application with capacitance up to 10 F.

Table 3-6 provides backup times for several scenarios.

220

220

| Resistance (Ω) | 5 V load*<br>(mA) | Charge Time<br>(to 98%)         | Backup Time**<br>(4.9 V to 2.0 V)                                                                                 |

|----------------|-------------------|---------------------------------|-------------------------------------------------------------------------------------------------------------------|

| 2200           | 2.3               | 4.1 s                           | 5.67 min                                                                                                          |

| 1000           | 5                 | 6.67 min                        | 20 h                                                                                                              |