#### **MAX17521**

# 60V, 1A, Dual-Output, High-Efficiency, Synchronous Step-Down DC-DC Converter

#### **General Description**

The MAX17521 dual-output, high-efficiency, high-voltage, synchronous step-down DC-DC converter with integrated MOSFETs operates over a 4.5V to 60V input. The converter can deliver up to 1A at each output. Each output is programmable from 0.9V to 92%V<sub>IN</sub>. The feedback voltage regulation accuracy over -40°C to +125°C is ±1.7%.

The MAX17521 uses peak-current-mode control. Each output can be operated in the pulse-width modulation (PWM) or pulse-frequency modulation (PFM) control schemes.

The MAX17521 is available in a 24-pin (4mm x 5mm) TQFN package. Simulation models are available.

#### **Applications**

- Industrial Control Power Supplies

- CPU. DSP. or FPGA Power

- Distributed Supply Regulation

- General-Purpose Point of Load

Ordering Information appears at end of data sheet.

#### **Benefits and Features**

- Reduces External Components and Total Cost

- · No Schottky—Synchronous Operation

- · All-Ceramic Capacitors, Compact Layout

- Reduces Number of DC-DC Regulators to Stock

- Wide 4.5V to 60V Input

- Each Output Adjustable From 0.9V to 92%V<sub>IN</sub>

- Pin-Selectable 560kHz or 300kHz Switching Frequency

- Independent Input Voltage Pin for Each Output

- Reduces Power Dissipation

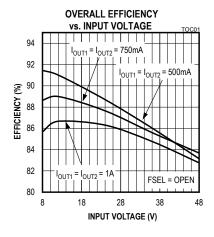

- Peak Efficiency > 90%

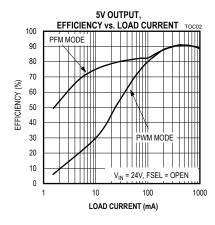

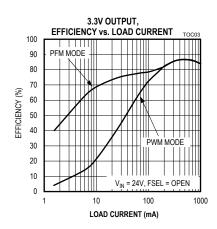

- PFM Mode Enables Enhanced Light-Load Efficiency

- 1µA Shutdown Current

- Operates Reliably in Adverse Industrial Environments

- · Hiccup Mode Overload Protection

- · Adjustable Soft-Start Pin for Each Output

- Built-In Output Voltage Monitoring with RESET for Each Output

- Adjustable EN/UVLO Threshold for Each Output

- Monotonic Startup Into Prebiased Load

- Overtemperature Protection

- · -40°C to +125°C Operation

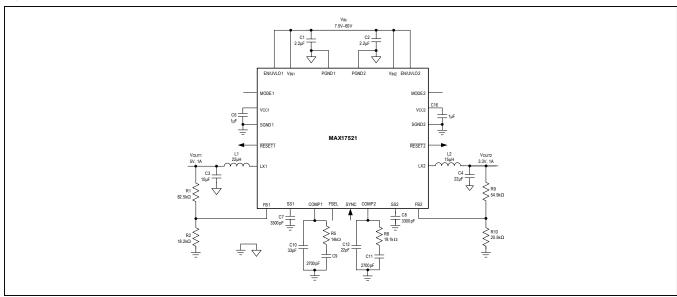

## **Typical Application Circuit**

## **Absolute Maximum Ratings**

| V <sub>IN</sub> to PGND0.3V to +6                     | 65V Output Short-Circuit Duration       | ntinuous |

|-------------------------------------------------------|-----------------------------------------|----------|

| EN/UVLO_ to SGND                                      | .3V) Operating Temperature Range40°C to | ) +125°C |

| LX_ to PGND0.3V to (V <sub>IN</sub> + 0.3             | .3V) Junction Temperature               | +150°C   |

| FB_, RESET_, FSEL, MODE_,                             | Storage Temperature Range65°C to        | ) +160°C |

| COMP_, V <sub>CC</sub> , SYNC, SS_ to SGND0.3V to +   | +6V Lead Temperature (soldering, 10s)   | +300°C   |

| SGND_ to PGND0.3V to +0.                              | 0.3V Soldering Temperature (reflow)     | +260°C   |

| LX Total RMS Current±1.                               | 1.6A                                    |          |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C) |                                         |          |

| (derate 28.6mW/°C above +70°C)                        |                                         |          |

| (multilayer board)2285.7m                             | 'mW                                     |          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **Package Thermal Characteristics (Note 1)**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......35°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).......1.8°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN}\_=+24V,V_{SGND}\_=V_{PGND}\_=V_{FSEL}=0V,C_{IN}\_=2.2\mu\text{F},C_{VCC}\_=1\mu\text{F},V_{EN/UVLO}\_=1.5V,C_{SS}\_=0.01\mu\text{F},FB}\_=0.98\text{ x }V_{FB-REG},COMP\_=\text{unconnected},LX\_=\text{unconnected},RESET\_=\text{unconnected},T_A=T_J=-40^{\circ}\text{C to }+125^{\circ}\text{C},\text{ unless otherwise noted}.Typical values are at T_A=+25^{\circ}\text{C}.$  All voltages are referenced to SGND\_, unless otherwise noted.) (Note 2)

| PARAMETER                       | SYMBOL                    | CONDITIONS                                                      |                          | MIN  | TYP   | MAX  | UNITS |  |  |

|---------------------------------|---------------------------|-----------------------------------------------------------------|--------------------------|------|-------|------|-------|--|--|

| INPUT SUPPLY (V <sub>IN</sub> ) |                           |                                                                 |                          |      |       |      |       |  |  |

| Input Voltage Range             | V <sub>IN</sub> _         |                                                                 |                          | 4.5  |       | 60   | V     |  |  |

| Input Shutdown Current          | I <sub>IN-SH</sub>        | V <sub>EN</sub> _ = 0V, shutdow                                 | n mode                   |      | 1     | 3.5  | μA    |  |  |

|                                 | I <sub>Q_PFM_</sub>       | V <sub>MODE</sub> _> 2V                                         |                          |      | 135   | 260  | μA    |  |  |

| Input Switching Current         | 1                         | V <sub>MODE</sub> _< 0.8V,                                      | V <sub>FSEL</sub> > 2V   |      | 5     |      | mA    |  |  |

|                                 | IQ_PWM_                   | V <sub>COMP</sub> _= 0.8V                                       | V <sub>FSEL</sub> < 0.8V |      | 3.7   |      | IIIA  |  |  |

| ENABLE/UVLO (EN_)               |                           |                                                                 |                          |      |       |      |       |  |  |

| EN_Threshold                    | V <sub>EN_R</sub>         | V <sub>EN</sub> _rising                                         |                          | 1.19 | 1.215 | 1.24 |       |  |  |

|                                 | V <sub>EN_F</sub>         | V <sub>EN</sub> _falling                                        |                          | 1.11 | 1.135 | 1.16 |       |  |  |

|                                 | V <sub>EN</sub><br>TRUESD | V <sub>EN</sub> _falling, true shutdown                         |                          |      | 0.75  |      |       |  |  |

| EN_ Input Leakage Current       | I <sub>EN</sub> _         | V <sub>EN</sub> = V <sub>IN</sub> = 60V, T <sub>A</sub> = +25°C |                          |      |       | 300  | nA    |  |  |

| FREQUENCY SELECTOR (FSE         | L)                        |                                                                 |                          |      |       |      |       |  |  |

| FSEL Threshold                  | V <sub>FSELR</sub>        | V <sub>FSEL</sub> low level                                     |                          |      |       | 0.8  | V     |  |  |

| FSEL THIESHOID                  | V <sub>FSELF</sub>        | V <sub>FSEL</sub> high level                                    |                          | 2    |       |      | V     |  |  |

| FSEL Input Leakage Current      | I <sub>FSEL</sub>         | V <sub>FSEL</sub> = V <sub>CC</sub> , T <sub>A</sub> = +25°C    |                          | -2.5 |       | +2.5 | μA    |  |  |

| MODE SELECTOR (MODE_)           |                           |                                                                 |                          |      |       |      |       |  |  |

| MODE Throubold                  | V <sub>MODE_R</sub>       | V <sub>MODE</sub> low level                                     |                          |      |       | 1.9  | V     |  |  |

| MODE_ Threshold                 | V <sub>MODE_F</sub>       | V <sub>MODE</sub> high level                                    |                          | 2.5  |       |      | ·     |  |  |

| MODE_ Input Leakage Current     | I <sub>MODE</sub> _       | V <sub>MODE</sub> = V <sub>CC</sub> , T <sub>A</sub> = +25°C    |                          |      |       | 300  | nA    |  |  |

## **Electrical Characteristics (continued)**

$(V_{IN}\_=+24V,V_{SGND}\_=V_{PGND}\_=V_{FSEL}=0V,C_{IN}\_=2.2\mu\text{F},C_{VCC}\_=1\mu\text{F},V_{EN/UVLO}\_=1.5V,C_{SS}\_=0.01\mu\text{F},FB}\_=0.98~x~V_{FB-REG},COMP\_=unconnected,~LX\_=unconnected,~RESET\_=unconnected,~T_A=T_J=-40^{\circ}\text{C}~to~+125^{\circ}\text{C},~unless~otherwise~noted.}$  Typical values are at  $T_A=+25^{\circ}\text{C}$ . All voltages are referenced to SGND\_, unless otherwise noted.) (Note 2)

| PARAMETER                              | SYMBOL                       | CONDITIONS                                                                                                           |                                                                               | MIN                                                         | TYP   | MAX                       | UNITS                     |

|----------------------------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|-------------------------------------------------------------|-------|---------------------------|---------------------------|

| LDO (V <sub>CC_</sub> )                |                              |                                                                                                                      |                                                                               |                                                             |       |                           |                           |

| V <sub>CC</sub> _ Output Voltage Range | V <sub>VCC</sub> _           | 6V < V <sub>IN</sub> _ <<br>12V < V <sub>IN</sub> _ <                                                                | 12V, 0mA < I <sub>VCC</sub> _ < 10mA<br>< 60V, 0mA < I <sub>VCC</sub> _ < 2mA | 4.65                                                        | 5     | 5.35                      | V                         |

| V <sub>CC</sub> _ Current Limit        | I <sub>VCCMAX</sub>          | V <sub>CC</sub> _ = 4.3V                                                                                             | , V <sub>IN</sub> _ = 12V                                                     | 17                                                          | 40    | 80                        | mA                        |

| V <sub>CC</sub> _ Dropout              | V <sub>CCDO</sub>            | V <sub>IN</sub> _ = 4.5V,                                                                                            | I <sub>VCC</sub> _ = 5mA                                                      | 4.1                                                         |       |                           | V                         |

| V <sub>CC</sub> UVLO                   | V <sub>VCCUVR</sub>          | V <sub>CC</sub> _rising                                                                                              |                                                                               | 3.85                                                        | 4     | 4.15                      | V                         |

|                                        | V <sub>CCUVF</sub>           | V <sub>CC</sub> _falling                                                                                             |                                                                               | 3.55                                                        | 3.7   | 3.85                      |                           |

| POWER MOSFETs                          |                              |                                                                                                                      |                                                                               |                                                             |       |                           |                           |

| High-Side_ pMOS                        | D                            | I <sub>LX</sub> = 0.5A                                                                                               | T <sub>A</sub> = +25°C                                                        |                                                             | 0.6   | 0.8                       | 0                         |

| On-Resistance                          | R <sub>DSONH</sub>           | (sourcing)                                                                                                           | $T_A = T_J = +125^{\circ}C \text{ (Note 3)}$                                  |                                                             |       | 1.2                       | Ω                         |

| Low-Side_ nMOS                         |                              | I <sub>LX</sub> = 0.5A                                                                                               | T <sub>A</sub> = +25°C                                                        |                                                             | 0.2   | 0.35                      |                           |

| On-Resistance                          | R <sub>DSONL</sub>           |                                                                                                                      | $T_A = T_J = +125^{\circ}C \text{ (Note 3)}$                                  |                                                             |       | 0.45                      | Ω                         |

| LX_ Leakage Current                    | I <sub>LX_LKG</sub>          | V <sub>EN</sub> _ = 0V, T <sub>A</sub> = +25°C, V <sub>LX</sub> = (V <sub>PGND</sub> _ + 1V) to (V <sub>IN</sub> 1V) |                                                                               |                                                             |       | 3                         | μA                        |

| SOFT-START (SS_)                       |                              |                                                                                                                      |                                                                               |                                                             |       |                           |                           |

| Charging Current_                      | I <sub>SS</sub> _            | V <sub>SS</sub> = 0.5V                                                                                               |                                                                               | 4.7                                                         | 5     | 5.3                       | μA                        |

| FEEDBACK (FB)                          |                              |                                                                                                                      |                                                                               |                                                             |       |                           | •                         |

|                                        |                              | MODE_ = SGND_                                                                                                        |                                                                               | 0.885                                                       | 0.9   | 0.915                     | T                         |

| FB Regulation Voltage                  | V <sub>FB_REG</sub>          | MODE_ = unconnected                                                                                                  |                                                                               |                                                             | 0.915 |                           | V                         |

| FB Input Bias Current                  | I <sub>FB</sub>              | V <sub>FB</sub> = 0.9V                                                                                               |                                                                               |                                                             | 15    | 100                       | nA                        |

| OUTPUT VOLTAGE (V <sub>OUT</sub> )     | •                            |                                                                                                                      |                                                                               |                                                             |       |                           |                           |

| Output Valtage Banco                   | V                            | V <sub>FSEL</sub> > 2V; no load (Note 3)  V <sub>FSEL</sub> < 0.8V; no load (Note 3)                                 |                                                                               | 0.92                                                        |       | 0.92 x<br>V <sub>IN</sub> | V                         |

| Output Voltage Range                   | VOUT                         |                                                                                                                      |                                                                               | V <sub>OUT</sub> V <sub>FSEL</sub> < 0.8V; no load (Note 3) | 0.92  |                           | 0.96 x<br>V <sub>IN</sub> |

| TRANSCONDUCTANCE AMPL                  | IFIER (COMP)                 |                                                                                                                      |                                                                               |                                                             |       |                           |                           |

| Transconductance                       | GM_                          | I <sub>COMP</sub> _ = ±2                                                                                             | 5μA                                                                           | 510                                                         | 590   | 650                       | μS                        |

| COMP_ Source Current                   | ICOMPSRC                     |                                                                                                                      |                                                                               | 19                                                          | 33    | 55                        | μA                        |

| COMP_ Sink Current                     | I <sub>COMP</sub> _<br>_SINK |                                                                                                                      |                                                                               | 19                                                          | 33    | 55                        | μA                        |

| Current Sense Transresistance          | R <sub>CS</sub>              |                                                                                                                      |                                                                               | 0.455                                                       | 0.5   | 0.545                     | Ω                         |

## **Electrical Characteristics (continued)**

$(V_{IN}\_=+24V,V_{SGND}\_=V_{PGND}\_=V_{FSEL}=0V,C_{IN}\_=2.2\mu\text{F},C_{VCC}\_=1\mu\text{F},V_{EN/UVLO}\_=1.5V,C_{SS}\_=0.01\mu\text{F},FB}\_=0.98~x~V_{FB-REG},COMP\_=unconnected,~LX\_=unconnected,~RESET\_=unconnected,~T_A=T_J=-40^{\circ}\text{C}~to~+125^{\circ}\text{C},~unless~otherwise~noted.}$  Typical values are at  $T_A=+25^{\circ}\text{C}$ . All voltages are referenced to SGND\_, unless otherwise noted.) (Note 2)

| PARAMETER                                                  | SYMBOL                        | CONDITIO                                       | ONS                                  | MIN  | TYP                     | MAX                     | UNITS  |

|------------------------------------------------------------|-------------------------------|------------------------------------------------|--------------------------------------|------|-------------------------|-------------------------|--------|

| CURRENT LIMIT                                              |                               |                                                |                                      |      |                         |                         |        |

| Peak Current Limit Threshold                               | IPEAKLIMIT                    |                                                |                                      | 1.35 | 1.6                     | 1.85                    | Α      |

| Runaway Current Limit<br>Threshold                         | I <sub>RUNAWAY</sub><br>LIMIT |                                                |                                      | 1.45 | 1.85                    | 2.05                    | А      |

| Olah Olah at the sale at the                               |                               | V <sub>MODE_</sub> < 0.8V                      |                                      |      | 0.65                    |                         | Α      |

| Sink Current Limit Threshold                               | ISINK-LIMIT                   | V <sub>MODE</sub> _ > 2V                       |                                      |      | 0                       |                         | Α      |

| PFM Peak Current                                           | I <sub>PFM</sub> _            | V <sub>MODE</sub> _ > 2V                       |                                      | 0.2  | 0.3                     | 0.4                     | Α      |

| TIMINGS                                                    |                               |                                                |                                      |      |                         |                         |        |

|                                                            |                               | V > V                                          | V <sub>FSEL</sub> > 2V               | 510  | 560                     | 600                     |        |

| Switching Frequency                                        | f <sub>SW</sub> _             | V <sub>FB</sub> _ > V <sub>OUT</sub> HICF      | V <sub>FSEL</sub> < 0.8V             | 280  | 300                     | 320                     | kHz    |

|                                                            |                               | V <sub>FB</sub> _ <v<sub>OUTHICF</v<sub>       | V <sub>FSEL</sub> > 2V               | 280  | 300                     | 320                     |        |

| V <sub>FB</sub> _ Under Voltage Trip Level to Cause HICCUP | V <sub>OUTHICF</sub>          | V <sub>SS</sub> _> 0.95V (soft-start           | is done)                             | 68.5 | 70                      | 72.5                    | %      |

| HICCUP Timeout                                             |                               |                                                |                                      |      | 4096                    |                         | Cycles |

| Minimum On-Time                                            | T <sub>ONMIN</sub>            |                                                |                                      |      | 85                      | 120                     | ns     |

| Maximum Duty Cycle                                         | D <sub>MAX</sub> _            | V <sub>FB</sub> _ = 0.98 x V <sub>FB</sub> REG | V <sub>FSEL</sub> > 2V               | 92   | 94                      | 96                      | %      |

| waxiinuin buty Cycle                                       |                               |                                                | V <sub>FSEL</sub> < 0.8V             | 96   | 97                      | 98                      |        |

| LX_ Dead Time                                              |                               |                                                |                                      |      | 5                       |                         | ns     |

| FREQUENCY SYNCHRONIZAT                                     | IONS (SYNC)                   |                                                |                                      |      |                         |                         |        |

| SYNC Threshold                                             | V <sub>SYNC_R</sub>           |                                                |                                      |      |                         | 8.0                     | V      |

| OTIVO TITICONOIU                                           | V <sub>SYNC_F</sub>           |                                                |                                      | 2    |                         |                         | •      |

| SYNC Input Leakage Current                                 | ISYNC                         | V <sub>SYNC</sub> = 5V ; T <sub>A</sub> = +25° | С                                    |      |                         | 300                     | nA     |

| SYNC Pulse Duration                                        | T <sub>SYNC</sub>             |                                                |                                      | 50   |                         |                         | ns     |

| SYNC Frequency                                             | F <sub>SYNC</sub>             | F <sub>SW</sub> = 300kHz or 560kH              | z                                    |      | 1.1x<br>f <sub>SW</sub> | 1.4x<br>f <sub>SW</sub> | kHz    |

| RESET_                                                     |                               |                                                |                                      |      |                         |                         |        |

| RESET_ Output Level Low                                    |                               | I <sub>RESET</sub> = 1mA                       |                                      |      |                         | 0.02                    | V      |

| RESET_ Output Leakage Current High                         |                               | V <sub>FB</sub> _ = 1.01 x V <sub>FB</sub> REG | <sub>S</sub> , T <sub>A</sub> = 25°C |      |                         | 0.5                     | μΑ     |

| V <sub>OUT</sub> _ Threshold for RESET Falling             | V <sub>OUT</sub> OKF          | V <sub>FB</sub> _ falling                      |                                      | 90.5 | 92.5                    | 94.5                    | %      |

| V <sub>OUT</sub> _Threshold for RESET_<br>Rising           | V <sub>OUT</sub> OKR          | V <sub>FB</sub> _ rising                       |                                      | 93.5 | 95.5                    | 97.5                    | %      |

| RESET _ Delay After FB_<br>Reaches 95% Regulation          |                               |                                                |                                      |      | 1024                    |                         | Cycles |

#### **Electrical Characteristics (continued)**

$(V_{IN}\_=+24V,V_{SGND}\_=V_{PGND}\_=V_{FSEL}=0V,C_{IN}\_=2.2\mu\text{F},C_{VCC}\_=1\mu\text{F},V_{EN/UVLO}\_=1.5V,C_{SS}\_=0.01\mu\text{F},FB}\_=0.98\text{ x V}_{FB-REG},COMP\_=\text{unconnected},LX\_=\text{unconnected},RESET\_=\text{unconnected},T_A=T_J=-40^{\circ}\text{C to }+125^{\circ}\text{C},\text{ unless otherwise noted}.$  Typical values are at  $T_A=+25^{\circ}\text{C}$ . All voltages are referenced to SGND\_, unless otherwise noted.) (Note 2)

| PARAMETER                   | SYMBOL | CONDITIONS         | MIN | TYP | MAX | UNITS |

|-----------------------------|--------|--------------------|-----|-----|-----|-------|

| THERMAL SHUTDOWN            |        |                    |     |     |     |       |

| Thermal-Shutdown Threshold  |        | Temperature rising |     | 165 |     | °C    |

| Thermal-Shutdown Hysteresis |        |                    |     | 10  |     | °C    |

Note 2: Limits are 100% tested at  $T_A = +25^{\circ}C$ . Limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 3: Guaranteed by design, not production tested.

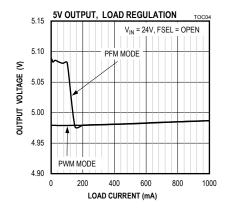

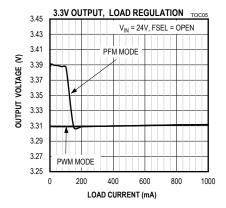

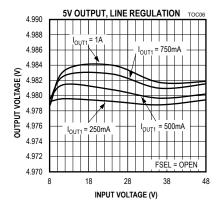

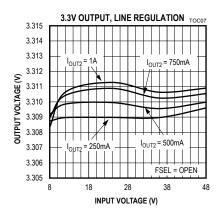

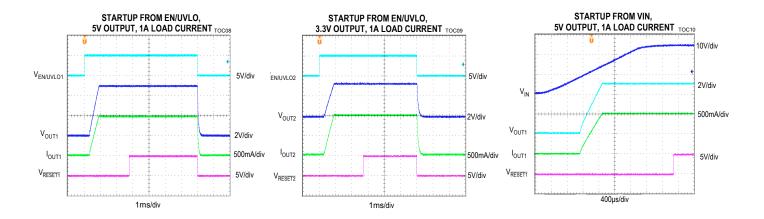

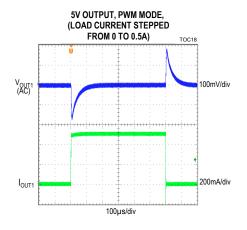

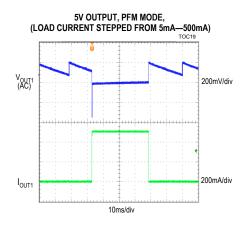

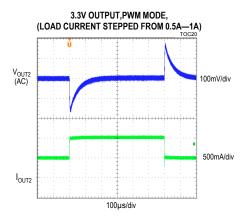

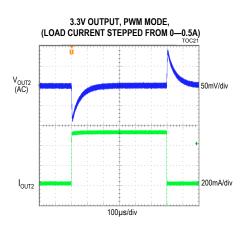

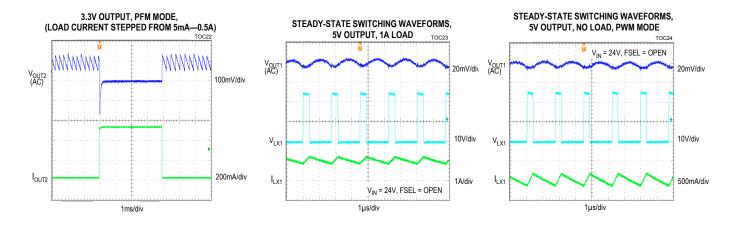

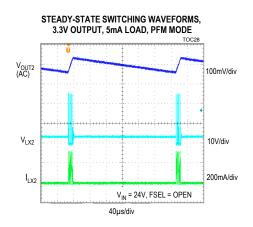

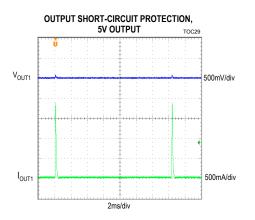

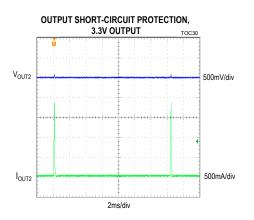

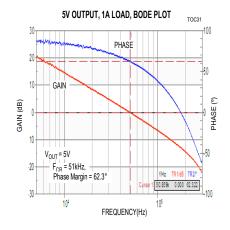

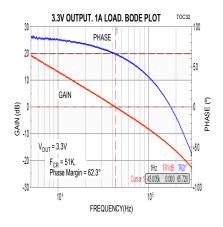

#### **Typical Operating Characteristics**

$(V_{IN} = 24V, V_{SGND} = V_{PGND} = 0V, C_{VIN} = 2.2\mu F, C_{VCC} = 1\mu F, V_{EN/UVLO} = 1.5V, C_{SS} = 3300pF, V_{FB} = 0.98 x V_{OUT}, LX_ = unconnected, RESET_ = unconnected, FSEL = unconnected, MODE_ = unconnected, T_A = T_J = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND, unless otherwise noted.)$

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 24V, V_{SGND} = V_{PGND} = 0V, C_{VIN} = 2.2\mu F, C_{VCC} = 1\mu F, V_{EN/UVLO} = 1.5V, C_{SS} = 3300pF, V_{FB} = 0.98 x V_{OUT}, LX_ = unconnected, RESET_ = unconnected, FSEL = unconnected, MODE_ = unconnected, T_A = T_J = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND, unless otherwise noted.)$

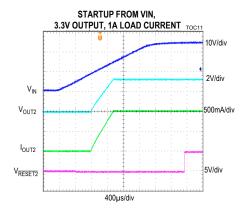

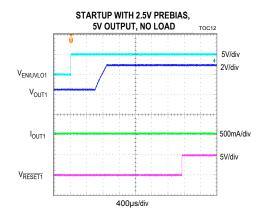

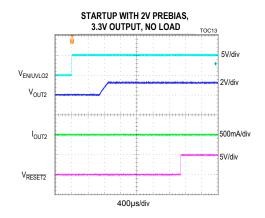

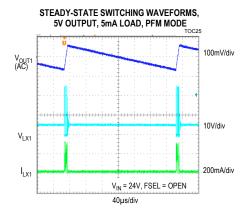

#### **Typical Operating Characteristics (continued)**

$(V_{IN} = 24V, V_{SGND} = V_{PGND} = 0V, C_{VIN} = 2.2\mu F, C_{VCC} = 1\mu F, V_{EN/UVLO} = 1.5V, C_{SS} = 3300pF, V_{FB} = 0.98 x V_{OUT}, LX_ = unconnected, RESET_ = unconnected, FSEL = unconnected, MODE_ = unconnected, T_A = T_J = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND, unless otherwise noted.)$

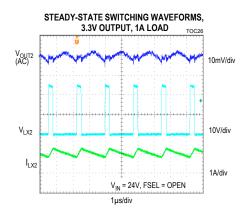

#### **Typical Operating Characteristics (continued)**

$(V_{IN} = 24V, V_{SGND} = V_{PGND} = 0V, C_{VIN} = 2.2\mu F, C_{VCC} = 1\mu F, V_{EN/UVLO} = 1.5V, C_{SS} = 3300pF, V_{FB} = 0.98 x V_{OUT}, LX_ = unconnected, RESET_ = unconnected, FSEL = unconnected, MODE_ = unconnected, T_A = T_J = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND, unless otherwise noted.)$

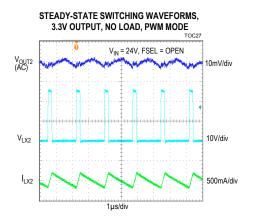

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 24V, V_{SGND} = V_{PGND} = 0V, C_{VIN} = 2.2\mu F, C_{VCC} = 1\mu F, V_{EN/UVLO} = 1.5V, C_{SS} = 3300pF, V_{FB} = 0.98 x V_{OUT}, LX_ = unconnected, RESET_ = unconnected, FSEL = unconnected, MODE_ = unconnected, T_A = T_J = -40°C to +125°C, unless otherwise noted. Typical values are at T_A = +25°C. All voltages are referenced to SGND, unless otherwise noted.)$

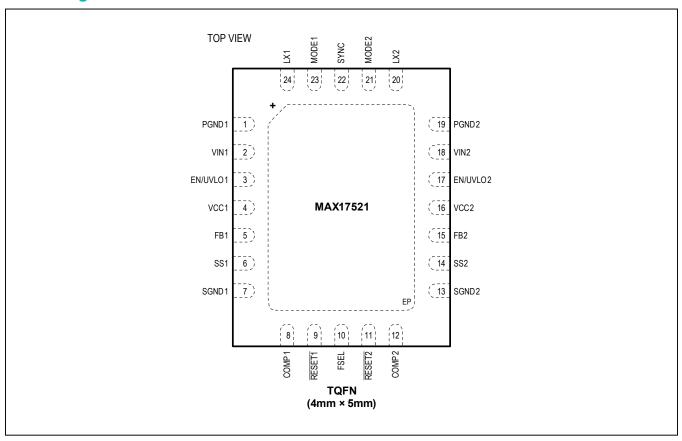

## **Pin Configuration**

## **Pin Description**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                         |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | PGND1    | Power Ground Connection of Converter 1. Connect PGND1 externally to the power ground plane. Connect SGND and PGND pins together at the ground return path of the V <sub>CC</sub> bypass capacitors.                                                                                              |

| 2   | VIN1     | Power-Supply Input of Converter 1. The input supply range is from 4.5V to 60V. Decouple to PGND1 with a 2.2µF capacitor; place the capacitor close to the V <sub>IN1</sub> and PGND1 pins.                                                                                                       |

| 3   | EN/UVLO1 | Enable/Undervoltage Lockout Input for Converter 1. Drive EN/UVLO1 high to enable converter 1. Connect to the center of the resistive divider between $V_{\text{IN1}}$ and SGND1 to set the input voltage at which the converter 1 turns on. Pull up to $V_{\text{IN1}}$ for always-on operation. |

| 4   | VCC1     | 5V LDO Output for Converter 1. Bypass V <sub>CC1</sub> with 1μF ceramic capacitance to SGND1.                                                                                                                                                                                                    |

| 5   | FB1      | Feedback Input for Converter 1. Connect FB1 to the center of the resistive divider between V <sub>OUT1</sub> and SGND1. See the <i>Adjusting Output Voltage</i> section for more details.                                                                                                        |

| 6   | SS1      | Soft-start Input for Converter 1. Connect a capacitor from SS1 to SGND1 to set the soft-start time for converter 1.                                                                                                                                                                              |

| 7   | SGND1    | Analog Ground Connection for Converter 1.                                                                                                                                                                                                                                                        |

| 8   | COMP1    | Loop Compensation Pin for Converter 1. Connect an RC network from COMP1 to SGND1. See the Loop Compensation section for more details.                                                                                                                                                            |

## **Pin Description (continued)**

| PIN | NAME     | FUNCTION                                                                                                                                                                                                                                                                                         |

|-----|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9   | RESET1   | Open-Drain RESET1 Output. The RESET1 output is driven low if FB1 drops below 92.5% of its set value. RESET1 goes high 1024 clock cycles after FB1 rises above 95.5% of its set value. RESET1 is valid when the device is enabled and V <sub>IN</sub> is above 4.5V.                              |

| 10  | FSEL     | Configures the Switching Frequency of the MAX17521. Leaving FSEL unconnected sets the switching frequency of both the converters at 560kHz. Connecting FSEL pin to SGND_ sets the switching frequency of both the converters at 300kHz.                                                          |

| 11  | RESET2   | Open-Drain RESET2 Output. The RESET2 output is driven low if FB2 drops below 92.5% of its set value. RESET2 goes high 1024 clock cycles after FB2 rises above 95.5% of its set value. RESET2 is valid when the device is enabled and V <sub>IN</sub> is above 4.5V.                              |

| 12  | COMP2    | Loop Compensation Pin for Converter 2. Connect an RC network from COMP2 to SGND2. See the Loop Compensation section for more details.                                                                                                                                                            |

| 13  | SGND2    | Analog Ground Connection for Converter 2.                                                                                                                                                                                                                                                        |

| 14  | SS2      | Soft-Start Input for Converter 2. Connect a capacitor from SS2 to SGND2 to set the soft-start time for converter 2.                                                                                                                                                                              |

| 15  | FB2      | Feedback Input for Converter 2. Connect FB2 to the center of the resistive divider between V <sub>OUT2</sub> and SGND2. See the <i>Adjusting Output Voltage</i> section for more details.                                                                                                        |

| 16  | VCC2     | 5V LDO Output for converter 2. Bypass V <sub>CC2</sub> with 1µF ceramic capacitance to SGND2.                                                                                                                                                                                                    |

| 17  | EN/UVLO2 | Enable/Undervoltage Lockout Input for Converter 2. Drive EN/UVLO2 high to enable converter 2. Connect to the center of the resistive divider between $V_{\text{IN}2}$ and SGND2 to set the input voltage at which the converter 2 turns on. Pull up to $V_{\text{IN}2}$ for always on operation. |

| 18  | VIN2     | Power-Supply Input of Converter 2. The input supply range is from 4.5V to 60V. Decouple to PGND2 with a 2.2µF capacitor; place the capacitor close to the V <sub>IN2</sub> and PGND2 pins.                                                                                                       |

| 19  | PGND2    | Power Ground Connection of Converter 2. Connect PGND2 externally to the power ground plane. Connect SGND and PGND pins together at the ground return path of the V <sub>CC</sub> bypass capacitors.                                                                                              |

| 20  | LX2      | Switching Node of Converter 2. Connect LX2 to the switching side of the inductor.                                                                                                                                                                                                                |

| 21  | MODE2    | Configures Converter 2 to Operate in PWM or PFM Modes of Operation. Leave MODE2 unconnected for PFM operation (pulse skipping at light loads). Connect MODE2 to SGND2 for constant frequency PWM operation at all loads. See the <i>MODE Setting</i> section for more details.                   |

| 22  | SYNC     | Synchronizes Device to an External Clock. See the External Frequency Synchronization section for more details.                                                                                                                                                                                   |

| 23  | MODE1    | Configures Converter 1 to Operate in PWM or PFM Modes of Operation. Leave MODE1 unconnected for PFM operation (pulse skipping at light loads). Connect MODE1 to SGND1 for constant frequency PWM operation at all loads. See the <i>MODE Setting</i> section for more details.                   |

| 24  | LX1      | Switching Node of Converter 1. Connect LX1 to the switching-side of the inductor.                                                                                                                                                                                                                |

| _   | EP       | Exposed Pad. Connect to the SGND pins. Connect to a large copper plane below the IC to improve heat dissipation capability.                                                                                                                                                                      |

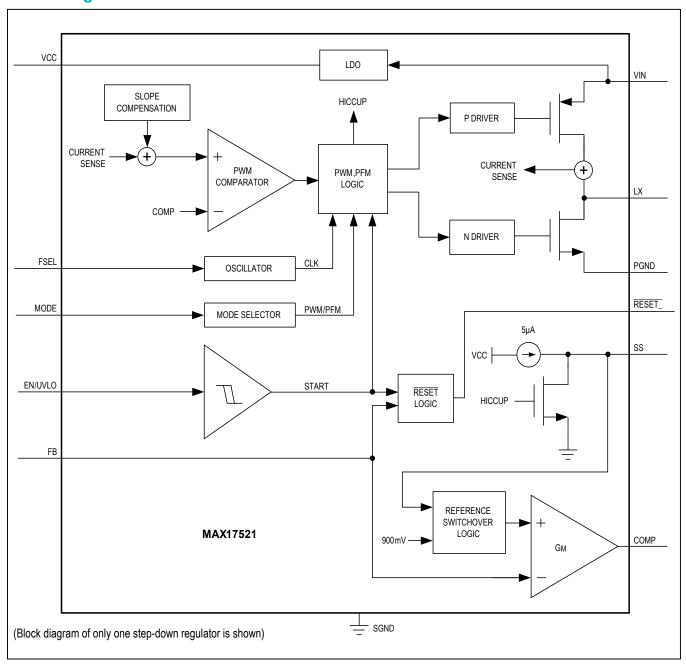

## **Block Diagram**

#### **Detailed Description**

The MAX17521 dual step-down regulator operates from 4.5V to 60V and delivers up to 1A load current on each output. Feedback voltage regulation accuracy meets ±1.7% over load, line and temperature.

The device uses a peak-current-mode control scheme. For each output, an internal transconductance error amplifier generates an integrated error voltage. The error voltage sets the duty cycle using a PWM comparator, a high-side current-sense amplifier, and a slope-compensation generator. At each rising edge of the clock, the high-side pMOSFET turns on and remains on until either the appropriate or maximum duty cycle is reached, or the peak current limit is detected.

During the high-side MOSFET's on-time, the inductor current ramps up. During the second half of the switching cycle, the high-side MOSFET turns off and the low-side nMOSFET turns on and remains on until either the next rising edge of the clock arrives or sink current limit is detected. The inductor releases the stored energy as its current ramps down, and provides current to the output (the internal low  $R_{\mbox{\scriptsize DSON}}$  pMOS/nMOS switches ensure high efficiency at full load).

This device also integrates switching frequency selector pin and individual mode of operation selector pins, enable/undervoltage lockout (EN/UVLO) pins, programmable soft-start pins, and open-drain RESET signals for each output.

#### **Mode of Operation Selection**

The logic state of the MODE pins are latched when  $V_{CC}$  and EN/UVLO voltages exceed the respective UVLO rising thresholds and all internal voltages are ready to allow LX switching. If the MODE pin is open at power-up, the corresponding output operates in PFM mode at light loads. If the MODE pin is grounded at power-up, the corresponding output operates in constant-frequency PWM mode at all loads. State changes on the MODE pins are ignored during normal operation.

#### **PWM Mode Operation**

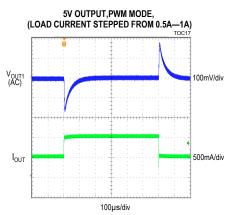

In PWM mode, the inductor current is allowed to go negative. PWM operation provides constant frequency operation at

all loads, and is useful in applications sensitive to switching frequency. However, the PWM mode of operation gives lower efficiency at light loads compared to the PFM mode of operation.

#### **PFM Mode Operation**

PFM mode of operation disables negative inductor current and additionally skips pulses at light loads for high efficiency. In PFM mode, the inductor current is forced to a fixed peak of 300mA every clock cycle until the output rises to 103% of the nominal voltage. Once the output reaches 103% of the nominal voltage, both the high-side and low-side FETs are turned off and the device enters hibernate operation until the load discharges the output to 101% of the nominal voltage. Most of the internal blocks are turned off in hibernate operation to save quiescent current. After the output falls below 101% of the nominal voltage, the device comes out of hibernate operation, turns on all internal blocks and again commences the process of delivering pulses of energy to the output until it reaches 103% of the nominal output voltage.

The advantage of the PFM mode is higher efficiency at light loads because of lower quiescent current drawn from supply. The disadvantage is that the output-voltage ripple is higher compared to PWM mode of operation and switching frequency is not constant at light loads.

#### Linear Regulator (V<sub>CC</sub>)

Two internal linear regulators ( $V_{CC1}$ ,  $V_{CC2}$ ) provide 5V nominal supplies to power the internal blocks and the low-side MOSFET drivers. The output of the  $V_{CC}$  linear regulators should be bypassed with 1µF ceramic capacitors to SGND. The device employs two undervoltage-lockout circuits that disable the internal linear regulators when  $V_{CC}$  falls below 3.7V (typ). Each of the  $V_{CC}$  regulators can source up to 40mA (typ) to supply the device and to power the low-side gate drivers.

#### **Switching Frequency Selection**

The FSEL pin programs the switching frequency of both the converters. If the FSEL pin is open at power-up, both the outputs operate at 560 kHz switching frequency. If the FSEL pin is grounded at power-up, both the outputs operate at 300kHz switching frequency.

#### **Operating Input Voltage Range**

The minimum and maximum operating input voltages for a given output voltage should be calculated as follows:

$$\begin{split} V_{IN(MIN)} = & \frac{V_{OUT} + (I_{OUT(MAX)} \times (R_{DCR} + 0.47))}{D_{MAX}} \\ & + (I_{OUT(MAX)} \times 0.73) \\ V_{IN(MAX)} = & \frac{V_{OUT}}{f_{SW(MAX)} \times t_{ON(MIN)}} \end{split}$$

where  $V_{OUT}$  is the steady-state output voltage,  $I_{OUT}$  (MAX) is the maximum load current,  $R_{DCR}$  is the DC resistance of the inductor,  $D_{MAX}$  is the maximum allowable duty ratio,  $f_{SW(MAX)}$  is the maximum switching frequency and  $t_{ON-MIN}$  is the worst-case minimum switch on-time (120ns). The following table lists the  $f_{SW(MAX)}$  and  $D_{MAX}$  values to be used for calculation for different switching frequency selection

| FSEL | f <sub>SW(MAX)</sub> (kHz) | D <sub>MAX</sub> |

|------|----------------------------|------------------|

| OPEN | 600                        | 0.92             |

| SGND | 320                        | 0.96             |

#### **External Frequency Synchronization (SYNC)**

The internal oscillator of the device can be synchronized to an external clock signal on the SYNC pin. The external synchronization clock frequency must be between 1.1 x  $f_{SW}$  and 1.4 x  $f_{SW}$ , where  $f_{SW}$  is the frequency selected by the FSEL pin. The minimum external clock pulse-width high should be greater than 50ns. See the SYNC section in the *Electrical Characteristics* table for details.

#### **Overcurrent Protection/HICCUP Mode**

The device is provided with a robust overcurrent-protection scheme that protects the device under overload and output short-circuit conditions. A cycle-by-cycle peak current limit turns off the high-side MOSFET whenever the high-side switch current exceeds an internal limit of 1.6A (typ). A runaway current limit on the high-side switch current at 1.85A (typ) protects the device under high input voltage, short-circuit conditions when there is insufficient output voltage available to restore the inductor

current that built up during the on period of the step-down converter. One occurrence of the runaway current limit triggers a hiccup mode. In addition, if due to a fault condition, output voltage drops to 70% (typ) of its nominal value any time after soft-start is complete, hiccup mode is triggered.

In hiccup mode, the converter is protected by suspending switching for a hiccup timeout period of 4096 clock cycles. Once the hiccup timeout period expires, soft-start is attempted again. This operation results in minimal power dissipation under overload fault conditions.

#### **RESET Output**

The device includes two  $\overline{\text{RESET}}$  comparators to monitor the output voltages. The open-drain  $\overline{\text{RESET}}$  outputs require an external pull-up resistor.  $\overline{\text{RESET}}$  can sink 2mA of current while low.  $\overline{\text{RESET}}$  goes high (high impedance) 1024 switching cycles after the corresponding output voltage increases above 95.5% of the nominal regulated voltage.  $\overline{\text{RESET}}$  goes low when the output voltage drops to below 92.5% of the nominal regulated voltage.  $\overline{\text{RESET}}$  also goes low during thermal shutdown.  $\overline{\text{RESET}}$  is valid when the device is enabled and  $V_{\text{IN}}$  is above 4.5V.

#### Coincident/Ratiometric Tracking and Output Voltage Sequencing

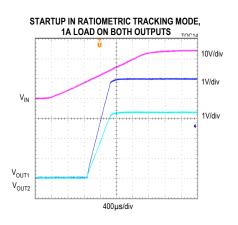

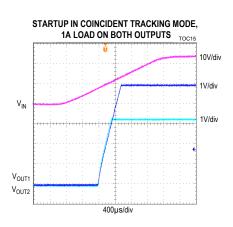

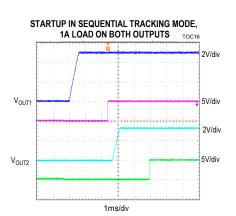

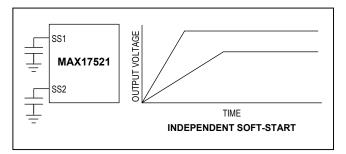

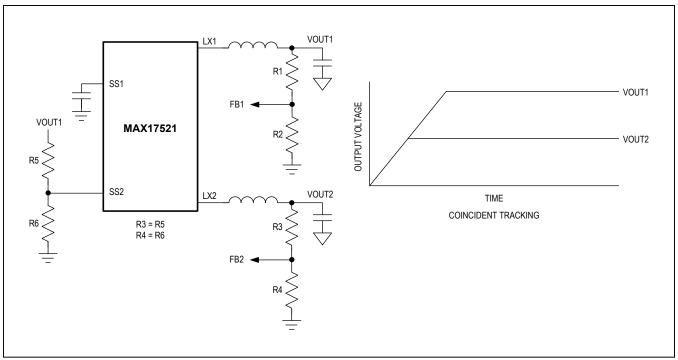

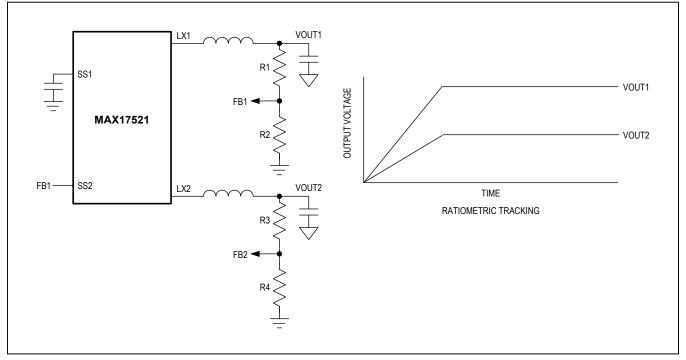

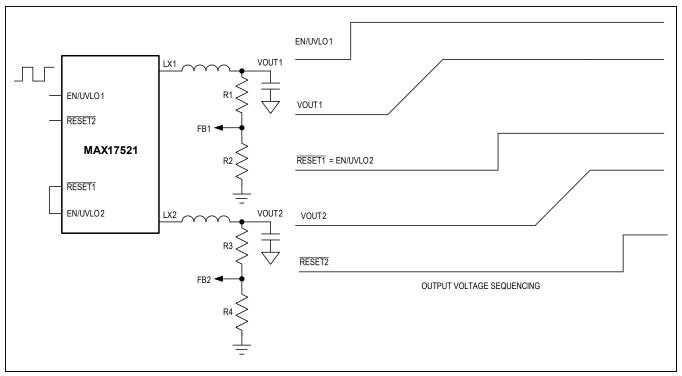

The soft-start pins (SS\_) can be used to track the output voltages to that of another power supply at startup. This requires connecting the SS\_ pins to an external resistor divider from the supply which needs to be tracked. The following figures (Figure 1 to Figure 3) show the possible ways of configuring the MAX17521 in various tracking modes.

Figure 1. Independent Soft-Start of Each Output

Figure 2. Coincident Tracking of the Outputs

Figure 3. Ratiometric Tracking of the Outputs

Figure 4. Output Voltage Sequencing

During power-off, the output voltages discharge to ground at a rate which depends on the respective output capacitor and load.

The RESET\_ pins and EN/UVLO\_ pins can be daisy-chained to generate power sequencing, as shown in Figure 4.

#### **Prebiased Output**

When the device starts into a prebiased output, both the high-side and low-side switches of the corresponding channel are turned off so that the converter does not sink current from the output. High-side and low-side switches do not start switching until the PWM comparator commands the first PWM pulse, at which point switching commences first with the high-side switch. The output voltage is then smoothly ramped up to the target value in alignment with the internal reference.

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the device. When the junction temperature of the device exceeds +165°C, an on-chip thermal sensor shuts down the device, allowing the device to cool. The thermal sensor turns the device on again after the junction temperature cools by 10°C. Soft-start resets during

thermal shutdown. Carefully evaluate the total power dissipation (see the <u>Power dissipation</u> section) to avoid unwanted triggering of the thermal-overload protection in normal operation.

#### **Applications Information**

#### Input Capacitor Selection

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. The input capacitor RMS current requirement (I<sub>RMS</sub>) for a single output is defined by the following equation:

$$I_{RMS} = I_{OUT(MAX)} \times \frac{\sqrt{V_{OUT} \times (V_{IN} - V_{OUT})}}{V_{IN}}$$

where,  $I_{OUT(MAX)}$  is the maximum load current.  $I_{RMS}$  has a maximum value when the input voltage equals twice the output voltage ( $V_{IN} = 2 \times V_{OUT}$ ), so  $I_{RMS(MAX)} = I_{OUT(MAX)}/2$  when only one converter is enabled. When both the converters are enabled and are operating out-of-phase, the RMS current is shared by both the input capacitors and therefore the maximum RMS current carried by each of the input capacitors is  $I_{OUT(MAX)}/4$ .

Choose an input capacitor that exhibits less than +10°C temperature rise at the RMS input current for optimal long-term reliability. Use low-ESR ceramic capacitors with high-ripple-current capability at the input. X7R capacitors are recommended in industrial applications for their temperature stability. When both the converters are enabled, calculate the input capacitance using the following equation:

$$C_{IN} = \frac{0.5 \times I_{OUT(MAX)} \times D \times (1 - D)}{\eta \times f_{SW} \times \Delta V_{IN}}$$

where D =  $V_{OUT}/V_{IN}$  is the duty ratio of the controller,  $f_{SW}$  is the switching frequency,  $\Delta V_{IN}$  is the allowable input voltage ripple, and  $\eta$  is the efficiency.

In applications where the source is located distant from the device input, an electrolytic capacitor should be added in parallel to the ceramic capacitor to provide necessary damping for potential oscillations caused by the inductance of the longer input power path and input ceramic capacitor.

#### Inductor Selection

Three key inductor parameters must be specified for operation with the device: inductance value (L), inductor saturation current ( $I_{SAT}$ ) and DC resistance ( $R_{DCR}$ ). The switching frequency and output voltage determine the inductor value as follows:

$$L = \frac{2.2 \times V_{OUT}}{f_{SW}}$$

where  $V_{OUT}$  and  $f_{SW}$  are nominal values. Select an inductor whose value is nearest to the value calculated by the previous formula.

Select a low-loss inductor closest to the calculated value with acceptable dimensions and having the lowest possible DC resistance. The saturation current rating (I<sub>SAT</sub>) of the inductor must be high enough to ensure that saturation can occur only above the peak current-limit value of 1.85A.

#### **Output Capacitor Selection**

X7R Ceramic Output capacitors are preferred due to their stability over temperature in Industrial applications. The output capacitor is usually sized to support a step load of 50% of the maximum output current in the application, such that the output voltage deviation is contained to 3%

of the output voltage change. The output capacitance may be calculated as follows:

$$C_{OUT} = \frac{1}{2} \times \frac{I_{STEP} \times t_{RESPONSE}}{\Delta V_{OUT}}$$

$$t_{RESPONSE} \cong (\frac{0.33}{f_C} + \frac{1}{f_{sw}})$$

Where I<sub>STEP</sub> is the load current step,  $t_{RESPONSE}$  is the response time of the controller,  $\Delta V_{OUT}$  is the allowable output voltage deviation,  $f_C$  is the target closed-loop crossover frequency and  $f_{SW}$  is the switching frequency.  $f_C$  is generally chosen to be  $1/9^{th}$  of  $f_{SW}$ .

#### **Soft-Start capacitor selection**

The device implements adjustable soft-start operation to reduce inrush current. A capacitor connected from the SS pin to SGND programs the soft-start time for the corresponding output voltage. The selected output capacitance ( $C_{SEL}$ ) and the output voltage ( $V_{OUT}$ ) determine the minimum required soft-start capacitor as follows:

$$C_{SS} \ge 56 \times 10^{-6} \times C_{SEL} \times V_{OUT}$$

The soft-start time ( $t_{SS}$ ) is related to the capacitor connected at SS ( $C_{SS}$ ) by the following equation:

$$t_{SS} \ge \frac{C_{SS}}{5.55 \times 10^{-6}}$$

For example, to program a 1ms soft-start time, a 5.6nF capacitor should be connected from the SS pin to SGND.

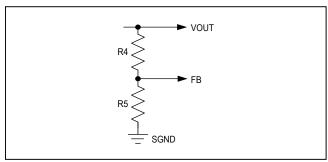

#### **Adjusting Output Voltage**

Set the output voltages with resistive voltage-dividers connected from the positive terminal of the output capacitor (V<sub>OUT)</sub> to SGND (see <u>Figure 1</u>). Connect the centre node of the divider to the FB pin. To optimize efficiency and output accuracy, use the following calculations to choose the resistive divider values:

$$R4 = \frac{15 \times V_{OUT}}{0.9}$$

$$R5 = \frac{R4 \times 0.9}{(V_{OUT} - 0.9)}$$

where R4 and R5 are in  $k\Omega$ .

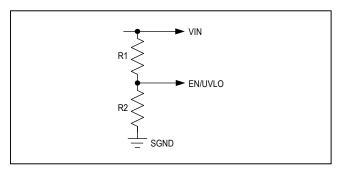

#### Setting the Undervoltage-Lockout Level

The device offers an adjustable input undervoltagelockout level for each output. Set the voltage at which each converter turns on with a resistive voltage-divider connected from VIN to SGND (see Figure 2). Connect the center node of the divider to EN/UVLO pin.

Choose R1 to be  $3.3M\Omega$ , and then calculate R2 as:

$$R2 = \frac{R1 \times 1.218}{(V_{INIJ} - 1.218)}$$

where V<sub>INU</sub> is the input voltage at which a particular converter is required to turn on.

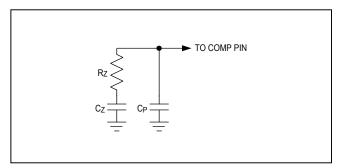

#### **Loop Compensation for Adjustable Output Version**

The MAX17521 uses peak current-mode control scheme and needs only simple RC networks connected from the COMP pins to SGND to have a stable, high-bandwidth

Figure 5. Adjusting Output Voltage

Figure 6. Setting the Undervoltage Lockout Level

control loop. The basic regulator loop is modeled as a power modulator, an output feedback divider, and an error amplifier. The power modulator has DC gain GMOD(dc), with a pole and zero pair. The following equation defines the power modulator DC gain:

$$G_{MOD(dc)} = \frac{2}{\frac{1}{R_{LOAD}} + \frac{0.4}{V_{IN}} + \frac{(0.5 - D)}{f_{SW} \times L_{SEL}}}$$

Where  $R_{LOAD}$  =  $V_{OUT}/I_{OUT(MAX)}$ ,  $f_{SW}$  is the switching frequency,  $L_{SEL}$  is the selected output inductance, D is the duty ratio, D =  $V_{OUT}/V_{IN}$ .

The compensation network is shown in Figure 3.

R<sub>7</sub> can be calculated as:

$$R_7 = 6000 \times f_C \times C_{SFI} \times V_{OUT}$$

where  $R_Z$  is in  $\Omega$ . Choose  $f_C$  to be 1/9<sup>th</sup> of the switching frequency.

CZ can be calculated as follows:

$$C_Z = \frac{C_{SEL} \times G_{MOD(dc)}}{2 \times R_Z}$$

C<sub>P</sub> can be calculated as follows:

$$C_P = \frac{1}{\pi \times R_Z \times f_{SW}}$$

Figure 7. Loop Compensation for Adjustable Output Version

#### **Power Dissipation**

The exposed pad of the IC should be properly soldered to the PCB to ensure good thermal contact. Ensure that the junction temperature of the device does not exceed +125°C under the operating conditions specified for the power supply.

At high ambient temperatures, based on the operating condition, the heat dissipated in the IC might exceed the maximum junction temperature of +125°C. Heat sink should be used to reduce  $\theta_{JA}$  at such operating conditions.

To prevent the part from exceeding 125°C junction temperature, users need to do some thermal analysis. At a particular operating condition, the power losses that lead to temperature rise of the device are estimated as follows:

$$P_{LOSS} = (P_{OUT} \times (\frac{1}{\eta} - 1)) - (I_{OUT}^2 \times R_{DCR})$$

$$P_{OUT} = V_{OUT} \times I_{OUT}$$

where  $P_{OUT}$  is the output power,  $\eta$  is the efficiency of the device and  $R_{DCR}$  is the DC resistance of the output inductor (refer to the <u>Typical Operating Characteristics</u> for more information on efficiency at typical operating conditions).

The maximum power that can be dissipated in the 24-pin TQFN package is 2285.7mW at +70°C temperature. The power dissipation capability should be derated as the temperature goes above +70°C at 28.6mW/°C. For a typical multilayer board, the thermal performance metrics for the package are given as:

$$\theta_{JA} = 35^{\circ}C/W$$

$\theta_{JC} = 1.8^{\circ}C/W$

The junction temperature of the device can be estimated at any given maximum ambient temperature  $(T_{A\_MAX})$  from the following equation:

$$T_{J\_MAX} = T_{A\_MAX} + (\theta_{JA} \times P_{LOSS})$$

If the application has a thermal-management system that ensures that the exposed pad of the device is maintained at a given temperature (TEP\_MAX) by using proper heat sinks, then the junction temperature of the device can be estimated at any given maximum ambient temperature as:

$$T_{J\_MAX} = T_{EP\_MAX} + (\theta_{JC} \times P_{LOSS})$$

#### **PCB Layout Guidelines**

Careful PCB layout is critical to achieve low switching losses and stable operation. For a sample layout that ensures first-pass success, refer to the MAX17521 evaluation kit layouts available at <a href="https://www.maximintegrated.com">www.maximintegrated.com</a>. Follow these guidelines for good PCB layout:

- All connections carrying pulsed currents must be very short and as wide as possible. The loop area of these connections must be made very small to reduce stray inductance and radiated EMI.

- A ceramic input filter capacitor should be placed close to the VIN pins of the device. The bypass capacitor for the VCC pins should also be placed close to the VCC pins. External compensation components should be placed close to the IC and far from the inductor. The feedback trace should be routed as far as possible from the inductor.

- The analog small-signal ground and the power ground for switching currents must be kept separate. They should be connected together at a point where switching activity is at minimum, typically the return terminal of the VCC bypass capacitors. The ground plane should be kept continuous as much as possible.

- A number of thermal vias that connect to a large ground plane should be provided under the exposed pad of the device, for efficient heat dissipation.

## **Ordering Information**

| PART         | PIN-PACKAGE | PACKAGE-SIZE |

|--------------|-------------|--------------|

| MAX17521ATG+ | 24 TQFN-EP* | 4mm x 5mm    |

<sup>\*</sup>EP = Exposed pad.

### **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE  | OUTLINE | LAND        |

|---------|----------|---------|-------------|

| TYPE    | CODE     | NO.     | PATTERN NO. |

| 24 TQFN | T2445+1C | 21-0201 | 90-0083     |

## MAX17521

## 60V, 1A, Dual-Output, High-Efficiency, Synchronous Step-Down DC-DC Converter

## **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 3/15          | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

Компания «ЭлектроПласт» предлагает заключение долгосрочных отношений при поставках импортных электронных компонентов на взаимовыгодных условиях!

#### Наши преимущества:

- Оперативные поставки широкого спектра электронных компонентов отечественного и импортного производства напрямую от производителей и с крупнейших мировых складов:

- Поставка более 17-ти миллионов наименований электронных компонентов;

- Поставка сложных, дефицитных, либо снятых с производства позиций;

- Оперативные сроки поставки под заказ (от 5 рабочих дней);

- Экспресс доставка в любую точку России;

- Техническая поддержка проекта, помощь в подборе аналогов, поставка прототипов;

- Система менеджмента качества сертифицирована по Международному стандарту ISO 9001:

- Лицензия ФСБ на осуществление работ с использованием сведений, составляющих государственную тайну;

- Поставка специализированных компонентов (Xilinx, Altera, Analog Devices, Intersil, Interpoint, Microsemi, Aeroflex, Peregrine, Syfer, Eurofarad, Texas Instrument, Miteq, Cobham, E2V, MA-COM, Hittite, Mini-Circuits, General Dynamics и др.);

Помимо этого, одним из направлений компании «ЭлектроПласт» является направление «Источники питания». Мы предлагаем Вам помощь Конструкторского отдела:

- Подбор оптимального решения, техническое обоснование при выборе компонента;

- Подбор аналогов;

- Консультации по применению компонента;

- Поставка образцов и прототипов;

- Техническая поддержка проекта;

- Защита от снятия компонента с производства.

#### Как с нами связаться

**Телефон:** 8 (812) 309 58 32 (многоканальный)

Факс: 8 (812) 320-02-42

Электронная почта: <u>org@eplast1.ru</u>

Адрес: 198099, г. Санкт-Петербург, ул. Калинина,

дом 2, корпус 4, литера А.