# Hi-Speed USB to 10/100 Ethernet Bridge

## **General Description**

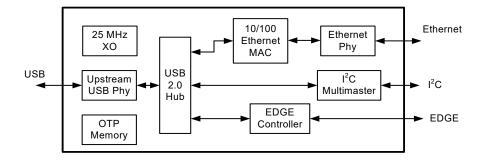

The XR22800 is a Hi-Speed USB 2.0 compound device with an embedded hub and 3 downstream USB functions: 10/100 Ethernet MAC and PHY, multi-master capable I<sup>2</sup>C controller, and an Enhanced Dedicated GPIO Entity (EDGE) controller.

The upstream USB interface has an integrated USB 2.0 PHY and device controller that is compliant with both Hi-Speed (480Mbps) and Full-Speed (12Mbps) USB 2.0. The vendor ID, product ID, power mode, remote wakeup support and maximum power consumption are amongst the values that can be programmed using the on-chip One-Time Programmable (OTP) memory.

The 10/100 Ethernet MAC and PHY is compliant with IEEE 802.3 and supports auto-negotiation, auto-MDIX, checksum offload, auto-polarity correction in 10Base-T and remote wakeup capabilities.

The multi-master capable I<sup>2</sup>C controller and EDGE controller (8 GPIOs) can be accessed via the USB HID interface. The EDGE pins or I<sup>2</sup>C interface can be used for controlling and monitoring other peripherals. Up to 2 EDGE pins can be configured as a PWM generator.

#### **FEATURES**

- USB 2.0 Compliant Interface

- 10/100 Ethernet MAC and PHY

- I<sup>2</sup>C Multi-master

- Enhanced Dedicated GPIO Entity (EDGE)

- Single +5.0V Power Supply Input

- Regulated +3.3V Output Power

- Single 25MHz Crystal

- ±15kV HBM ESD Protection on USB data pins

- ±8kV HBM ESD Protection on all other pins

- USB CDC-ECM and HID compliant

- Custom Software Drivers

#### **APPLICATIONS**

- USB to Ethernet Dongles

- POS Terminals

- Test Instrumentation

- Networking

- Factory Automation and Process Controls

- Industrial Applications

Ordering Information - Back Page

## **Block Diagram**

#### **Extended Features**

- USB 2.0 Compliant Interface

- Integrated USB 2.0 PHY

- Supports 480 Mbps USB Hi-Speed and 12 Mbps USB Full-Speed data rate

- Supports USB suspend, resume and remote wakeup operations

- Compatible with USB CDC-ECM

- 10/100 Ethernet MAC and PHY

- Compliant with IEEE 802.3

- Integrated 10/100 Ethernet MAC and PHY

- 10BASE-T and 100BASE-TX support

- Full-duplex and half-duplex support

- Full-duplex and half-duplex flow control

- Preamble generation and removal

- Automatic 32-bit CRC generation and checking

- Automatic payload padding and pad removal

- Diagnostic loop-back modes

- TCP/UDP/IP/ICMP checksum offload support

- · Flexible Address filtering modes

- Wakeup packet support

- Support for 2 status LEDs

- I<sup>2</sup>C Multi-master

- Up to 400 kbps transfers

- Multi-master capable

- Enhanced Dedicated GPIO Entity (EDGE)

- Parallel GPIO access

- Two PWM generators

- Custom software drivers

- Windows XP, Vista, 7, 8, 8.1 and 10

- Windows CE 6.0

- Linux

- Mac OS X

# **Absolute Maximum Ratings**

Stresses beyond the limits listed below may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

| V <sub>CC</sub> Supply Voltage+5.75V                 |

|------------------------------------------------------|

| Input Voltage                                        |

| (all pins except SCL, SDA, USBD+, USBD-)0.3 to +4.0V |

| Input Voltage (USBD+ and USBD-)0.3V to +5.75V        |

| Input Voltage (SCL and SDA)0.3V to +6.0V             |

| Junction Temperature125°C                            |

# **Operating Conditions**

| Operating Temperature Range    | 40°C to +85°C   |

|--------------------------------|-----------------|

| V <sub>CC</sub> Supply Voltage | +4.4V to +5.25V |

## **Electrical Characteristics**

Unless otherwise noted:  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 4.4V$  to 5.25V

| Symbol            | Parameter                    | Conditions                                                   | Min  | Тур | Max     | Units |

|-------------------|------------------------------|--------------------------------------------------------------|------|-----|---------|-------|

| Power Cor         | nsumption                    |                                                              |      |     |         |       |

| I <sub>CC</sub>   | Operating Current            | No load on GPIO pins or 3V3_OUT                              |      | 185 | 250     | mA    |

| I <sub>SUSP</sub> | Suspend Mode Current         | No load on GPIO pins or 3V3_OUT                              |      | 3   | 4.5     | mA    |

| VBUS_SE           | NSE, LOW_PWR# and EDGE Pins  |                                                              | Į.   |     | <u></u> |       |

| V <sub>IL</sub>   | Input Low Voltage            |                                                              | -0.3 |     | 0.8     | V     |

| V <sub>IH</sub>   | Input High Voltage           |                                                              | 2.0  |     | 3.6     | V     |

| V <sub>OL</sub>   | Output Low Voltage           | I <sub>OL</sub> = 4mA                                        |      |     | 0.3     | V     |

| V <sub>OH</sub>   | Output High Voltage          | I <sub>OL</sub> = -4mA                                       | 2.2  |     |         | V     |

| I <sub>IL</sub>   | Input Low Leakage Current    |                                                              |      |     | ±10     | μA    |

| I <sub>IH</sub>   | Input High Leakage Current   |                                                              |      |     | ±10     | μA    |

| C <sub>IN</sub>   | Input Pin Capacitance        |                                                              |      |     | 5       | pF    |

| USB I/O P         | ins                          |                                                              |      |     |         |       |

| V <sub>OL</sub>   | Output Low Voltage           | Full-speed USB. External 15kΩ to GND on USBD+ and USBD- pins | 0    |     | 0.3     | V     |

| V <sub>OH</sub>   | Output High Voltage          | Full-speed USB. External 15kΩ to GND on USBD+ and USBD- pins | 2.8  |     | 3.6     | V     |

| V <sub>OL</sub>   | Output Low Voltage           | Hi-speed USB. External 45 Ω to GND on USBD+ and USBD- pins   | -300 |     | 300     | mV    |

| V <sub>OH</sub>   | Output High Voltage          | Hi-speed USB. External 45 Ω to GND on USBD+ and USBD- pins   | 360  |     | 440     | mV    |

| $V_{DrvZ}$        | Driver Output Impedance      |                                                              |      | 45  |         | Ω     |

| losc              | Output Short Circuit Current | 1.5V on USBD+ and USBD- pins                                 |      |     | 52      | mA    |

| Symbol           | Parameter                                    | Conditions                                                                                  |  | Min  | Тур | Max   | Units |  |  |  |

|------------------|----------------------------------------------|---------------------------------------------------------------------------------------------|--|------|-----|-------|-------|--|--|--|

| Ethernet I/      | Ethernet I/O Pins - 100Base-TX transmit mode |                                                                                             |  |      |     |       |       |  |  |  |

| V <sub>PPH</sub> | Peak Differential Output Voltage High        |                                                                                             |  | 950  |     | 1050  | mV    |  |  |  |

| $V_{PPL}$        | Peak Differential Output Voltage Low         | Measured at line side of transformer, line                                                  |  | -950 |     | -1050 | mV    |  |  |  |

| $V_{SAS}$        | Signal Amplitude Symmetry                    | replaced by differential resistance of 100 ohms.                                            |  | 98   |     | 102   | %     |  |  |  |

| T <sub>RF</sub>  | Signal Rise and Fall Time                    |                                                                                             |  | 3    |     | 5     | ns    |  |  |  |

| D <sub>CD</sub>  | Duty Cycle Distortion                        |                                                                                             |  | 0    |     | 0.5   | ns    |  |  |  |

| V <sub>OS</sub>  | Overshoot and Undershoot                     |                                                                                             |  | 0    |     | 5     | %     |  |  |  |

| -                | Transmit Jitter                              | Measured differentially                                                                     |  | 0    |     | 1.4   | ns    |  |  |  |

| Ethernet I/      | O Pins - 10Base-T transmit mode              |                                                                                             |  |      |     |       |       |  |  |  |

| V <sub>PPH</sub> | Peak Differential Output Voltage High        | Measured at line side of transformer, line replaced by differential resistance of 100 ohms. |  | 2.2  |     | 2.8   | V     |  |  |  |

| 3.3V Regu        | 3.3V Regulated Power Output                  |                                                                                             |  |      |     |       |       |  |  |  |

| V <sub>OUT</sub> | Output Voltage                               | Max load current 50 mA                                                                      |  | 3.0  | 3.3 | 3.6   | V     |  |  |  |

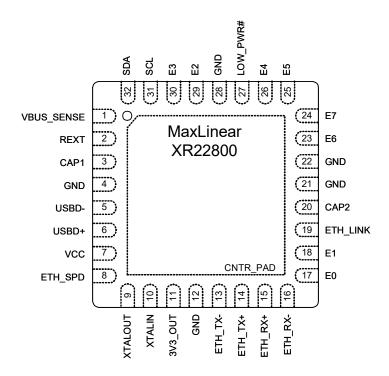

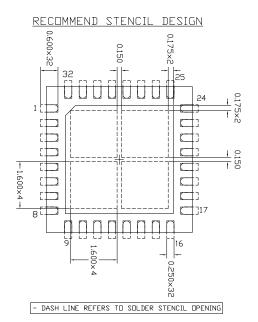

# **Pin Configuration**

Top View

# **Pin Assignments**

| Pin No. | Pin Name   | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VBUS_SENSE | -    | VBUS Sense input. In self-powered mode, the VBUS from the USB connector needs to be connected to this pin through a voltage divider circuit (VBUS = 5V, VBUS_SENSE = 3.3V input) using large resistance values to minimize power. It should also be decoupled by a 0.1uF capacitor. This feature may be enabled via the OTP whenever the hub function is configured for self-powered mode. The VBUS_SENSE input is used to disable the pull-up resistor on the USBD+ signal when VBUS is not present. In bus-powered mode, this pin is ignored. |

| 2       | REXT       | 1    | Connect externally using short trace to 226 ohm 1% resistor to ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 3       | CAP1       | 1    | Connect externally to CAP2 and 3V3_OUT using short trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 4       | GND        | PWR  | Power supply common, ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5       | USBD-      | I/O  | USB port differential data negative.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 6       | USBD+      | I/O  | USB port differential data positive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 7       | VCC        | PWR  | 5.0V power supply input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8       | ETH_SPD    | 0    | Ethernet 10/100 Mbps Speed Indicator. Asserted high for 100 Mbps.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 9       | XTALOUT    | 0    | Crystal or buffered clock output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 10      | XTALIN     | I    | 25 MHz +/- 50 ppm Crystal or external clock input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 11      | 3V3_OUT    | PWR  | 3.3 V output power. Connect externally to CAP1 and CAP2 using short trace and decouple with minimum of 4.7uF capacitor                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12      | GND        | PWR  | Power supply common, ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13      | ETH_TX-    | 0    | Ethernet transmit data out negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Pin No. | Pin Name | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------|----------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14      | ETH_TX+  | 0      | Ethernet transmit data out positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 15      | ETH_RX+  | I      | Ethernet receive data in positive                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 16      | ETH_RX-  | I      | Ethernet receive data in negative                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 17      | E0       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 18      | E1       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 19      | ETH_LINK | 0      | Ethernet 10/100 Activity Indicator. Toggles with activity.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 20      | CAP2     | I      | Connect externally to CAP1 and 3V3_OUT using short trace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 21      | GND      | PWR    | Power supply common, ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 22      | GND      | PWR    | Power supply common, ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 23      | E6       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 24      | E7       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 25      | E5       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 26      | E4       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 27      | LOW_PWR# | 0      | The LOW_PWR# pin will be asserted whenever it is not safe to draw the amount of current requested from VBUS in the Device Maximum Power field of the Configuration Descriptor. The LOW_PWR# pin is asserted when the XR22800 is in suspend mode or when it is not yet configured. The LOW_PWR# pin will be de-asserted whenever it is safe to draw the amount of current requested in the Device Maximum Power field. Note that the XR22800 device is a high power device. The default polarity of the LOW_PWR# output pin is active low and is programmable via the OTP. |

| 28      | GND      | PWR    | Power supply common, ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 29      | E2       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 30      | E3       | I/O    | Enhanced general purpose IO. Defaults to input with internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 31      | SCL      | I/O OD | I <sup>2</sup> C Master controller serial clock (open-drain) External pull-up resistor required on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 32      | SDA      | I/O OD | I <sup>2</sup> C Master controller data (open-drain). External pull-up resistor required on this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|         | CNTR_PAD | PWR    | Must be connected to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Type: I = Input, O = Output, I/O = Input/Output, PWR = Power, OD = Open-Drain

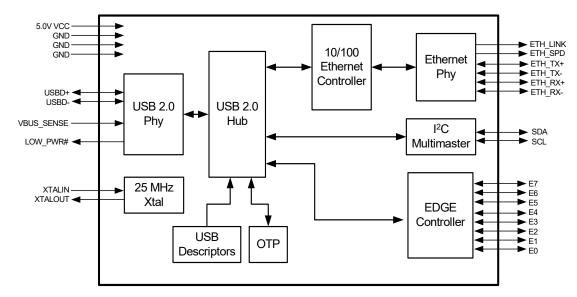

# **Functional Block Diagram**

## **Functional Description**

#### **USB** Interface

The XR22800 is a USB compound device with an embedded hub and 3 downstream USB functions. The downstream functions of the XR22800 are 10/100 Ethernet, an I<sup>2</sup>C function, and an Enhanced Dedicated GPIO Entity (EDGE) function. The upstream USB interface of the XR22800 is compliant with both USB 2.0 full and hi-speed specifications. All functions downstream of the hub are hi-speed functions.

The XR22800 will have a single vendor ID and vendor string. Each function in the XR22800 will have an individual product string and serial string. The default serial number strings will be based upon the uniquely assigned Ethernet MAC address for each XR22800 device. The serial strings for multiple functions within the same device will differ only by a single character which will be assigned a value between 0 and 7. All string and ID values can be overridden via OTP.

The XR22800 can be placed into a low power or suspended state by the USB host. By default the XR22800 hub is configured for bus powered mode with a maximum power of 250 mA. All other functions in the XR22800 are configured for self-powered mode. In bus powered mode, the Ethernet Phy must be powered down during suspended state to meet USB suspend power requirements. The Ethernet Phy may remain enabled to support Ethernet remote wakeup during suspend if the device is self-powered and the usb OTP is modified to report the hub function as self-powered in the USB descriptors. See Ethernet Remote Wakeup section on page 10.

Each function of the XR22800 supports one configuration and utilizes the following USB endpoints:

- USB hub

- Control endpoint

- Interrupt-in endpoint

- Ethernet function

- Control endpoint

- Interrupt-in endpoint

- Bulk-in and bulk-out endpoints

- I<sup>2</sup>C function

- Control endpoint

- Interrupt-in and interrupt-out endpoints

- EDGE Controller function

- Control endpoint

- · Interrupt-in and interrupt-out endpoints

#### **USB Vendor ID**

Exar's USB vendor ID is 0x04E2. This is the default vendor ID that is used for the XR22800. Companies may obtain their own vendor ID, by becoming members of USB.org. The XR22800 OTP can then be modified to report this vendor ID in the USB descriptors.

#### **USB Product ID**

Each function in the XR22800 has an individual USB product ID. The default product IDs for each of the functions are shown in Table 1. These values can be modified by programming the OTP. Companies using their own vendor ID may also select their own product IDs. Additionally, upon request MaxLinear will provide a selection of different product IDs for use with Exar's vendor ID for companies that do not wish to become members of USB.org, but wish to use their own product ID.

Table 1: Default XR22800 Product IDs

| XR22800 Function | Default Product ID |

|------------------|--------------------|

| Hub              | 0x0800             |

| Ethernet 10/100  | 0x1300             |

| I <sup>2</sup> C | 0x1100             |

| EDGE             | 0x1200             |

#### **USB Suspend**

All USB peripheral devices must support the USB suspend mode. Per USB standard, the XR22800 device will begin to enter the suspend state if it does not detect any activity, (including Start of Frame or SOF packets) on its USB data lines for 3 ms. The peripheral device must then reduce power consumption from VBUS power within the next 7 ms to the allowed limit of 2.5 mA per function for the suspended state. Because the XR22800 is a compound device with 4 functions, the suspend state power limit is 10 mA for the device. Note that in this context, the "device" is all circuitry (including the XR22800) that draws power from the host VBUS.

**USB Strings**

USB specifies three character string descriptors that are provided to the USB host during enumeration in string descriptors: the manufacturer, product and serial strings. In a compound device such as the XR22800, each function provides these strings to the USB host. The default manufacturer string for the XR22800 device is "Exar Corp.". The default product strings for the hub, Ethernet function, I<sup>2</sup>C function and EDGE function are shown in Table 2. The serial number string is a unique alpha-numeric ASCII string programmed into the device at the factory.

Table 2: Default XR22800 Product Strings

| XR22800 Function | Default Product String    |

|------------------|---------------------------|

| Hub              | Exar's XR22800 Hub        |

| Ethernet 10/100  | Exar USB Ethernet         |

| I <sup>2</sup> C | Exar USB I <sup>2</sup> C |

| EDGE             | Exar USB EDGE             |

The OTP may be used to override these strings. However, to ensure unique serial numbers for each device, it is recommended that the factory pre-programmed serial number string be used and not be overwritten via OTP.

#### **USB Device Drivers**

Each of the functions in the XR22800 require a USB device driver for operation. Both the I<sup>2</sup>C and EDGE functions conform to the HID device class and as such, utilize the embedded HID driver that is native to each Operating System. The embedded hub also uses the native hub driver. The Ethernet function conforms to the CDC device class and as such can utilize an embedded CDC-ECM driver. However, at the time of this writing, none of the Microsoft OS provide support for CDC-ECM embedded drivers. Both Linux and Mac OS-X platforms do support CDC-ECM drivers.

The CDC-ECM driver is a class specific driver which provides functionality for USB Ethernet devices. It operates without any ability to access device specific register sets. In some cases, this can limit the functionality and / or throughput capability of the XR22800. MaxLinear provides a custom Ethernet device driver which has been optimized for the best possible data through-put in Windows platforms. Refer to 10/100 Ethernet section on page 10 for more details.

#### 10/100 Ethernet

The Ethernet port is a 10/100 Ethernet MAC and Phy compliant with IEEE 802.3. The Ethernet port supports speed / duplex auto-negotiation, auto-MDIX, 10 Mbps data auto-polarity, full and half duplex data rates at 10 and 100 Mbps, generates and validates the 32-bit FCS, and performs unicast and multicast filtering. The XR22800 also performs TCP, UDP and ICMP checksum offload over IPV4 and IPV6 as well as header checksum offload in IPV4. On chip RAM provides all required packet buffering.

In Windows OS, using the MaxLinear custom Ethernet driver, the properties dialog, advanced properties can be used to set the pause frame flow control, speed and duplex, auto-negotiation, checksum offload, and Ethernet remote wakeup settings. By default, the Ethernet MAC will honor incoming pause frames sent by a peer Ethernet device, but will not generate pause frames. Auto-MDIX is always enabled.

#### **Ethernet Remote Wakeup**

If the XR22800 hub is configured as a self-powered device and has Ethernet remote wakeup enabled, the XR22800 will request the USB host to resume in response to a magic packet or a link state change on the Ethernet port. When the USB host is suspended, the Ethernet Phy remains active and the XR22800 is able to both meet USB suspend mode power requirements as well as respond to magic packet and link state changes.

The magic packet is an Ethernet packet with specific content, i.e. 6 bytes of 0xFF, followed by 16 repetitions of the target MAC address (MAC address of the XR22800 device). This content can occur anywhere in the incoming packet payload. The link state change will wake the USB host if the link is down when the USB host is suspended and then the link goes up, or if the link is up when the USB host is suspended and then the link goes down. EDGE - Enhanced Dedicated GPIO Entity

The XR22800 has 8 EDGE IO pins The EDGE controller allows for GPIO signals to be individually set or cleared or to be grouped, such that the all pins in the group can be simultaneously accessed for reads or writes. Note that on write accesses, output pins will change in 4-bit subgroups on core clock (60 MHz) boundaries. For example, if an 8 bit data group is defined and the data value is written from 0x00 to 0xFF, 4 bits would change from '0' to '1' followed by the next 4 bits one clock cycle (~ 17 ns) later.

EDGE IOs can be configured as inputs or outputs. Outputs can be configured as push-pull or open drain and can be tristated. Inputs can be configured to generate interrupts to the USB host on either negative or postive edge transitions.

Another feature of the EDGE controller is that up to 2 GPIO pins within the EDGE can be assigned to pulse width modulated (PWM) outputs. Each of the PWM outputs can be used to generate an output clock or pulse of varying duty cycle. Both low and high cycles can be configured in steps of 267 ns up to 1.092 ms. The output can be controlled to generate a single "one-shot" pulse or to free run. Refer to the EDGE\_PWM0\_CTRL and EDGE\_PWM1\_CTRL registers on page 22 and page 24 for control of PWM outputs. I<sup>2</sup>C

The XR22800 implements an I<sup>2</sup>C multi-master using the control endpoint of the full-speed USB function to transfer data to and from the I<sup>2</sup>C interface. The I<sup>2</sup>C master supports both standard (100 kbps) and fast (400 kbps) modes and supports multiple master configurations to allow other devices to access slave devices on the I<sup>2</sup>C. The I<sup>2</sup>C function is an HID function and uses the native HID driver. It supports both 7 and 10 bit addressing modes.

Regulated 3.3V Power Output

The XR22800 internal voltage regulator provides 3.3 VDC output power which can be utilized by other circuitry. Refer to Electrical Characteristics" on page 3 for maximum power capability. For bus powered devices, significant utilization of the 3V3 output power may require increasing the maximum power request above the 250 mA default value from the USB host by programming the OTP.

#### **OTP**

The OTP is an on-chip non-volatile memory, that is one-time programmable via the USB interface. Bit locations within the memory may be programmed at various times allowing for customization of the XR22800. Some bits are pre-programmed at the factory and caution must be taken not to program any locations except user defined addresses. Contact the factory uarttechsupport@exar.com for information and assistance in programming the XR22800 OTP.

11 / 27

exar.com/XR22800

## **USB Control Commands**

The following table shows all of the USB Control Commands that are supported by the XR22800. Commands include standard USB commands and USB vendor specific MaxLinear commands.

**Table 3: Supported USB Control Commands**

|                                           | Request | _       | Va                        | lue                       | Inc                  | lex    | Lei        | ngth       |                                         |

|-------------------------------------------|---------|---------|---------------------------|---------------------------|----------------------|--------|------------|------------|-----------------------------------------|

| Name                                      | Туре    | Request | LSB                       | MSB                       | LSB                  | MSB    | LSB        | MSB        | - Description                           |

|                                           |         |         | US                        | B Standa                  | ard Reques           | ts     |            |            |                                         |

| DEV GET_STATUS                            | 0x80    | 0x0     | 0x0                       | 0x0                       | 0x0                  | 0x0    | 0x2        | 0x0        | Device: remote wake-up + self-powered   |

| IF GET_STATUS                             | 0x81    | 0x0     | 0x0                       | 0x0                       | 0x0                  | 0x0    | 0x2        | 0x0        | Interface: zero                         |

| EP GET_STATUS                             | 0x82    | 0x0     | 0x0                       | 0x0                       | 0x0,<br>0x4,<br>0x84 | 0x0    | 0x2        | 0x0        | Endpoint: halted                        |

| DEV CLEAR_FEATURE                         | 0x00    | 0x1     | 0x1                       | 0x0                       | 0x0                  | 0x0    | 0x0        | 0x0        | Device remote wake-up                   |

| EP CLEAR_FEATURE                          | 0x02    | 0x1     | 0x0                       | 0x0                       | 0x0,<br>0x4,<br>0x84 | 0x0    | 0x0        | 0x0        | Endpoint halt                           |

| DEV SET_FEATURE                           | 0x00    | 0x3     | 0x1                       | 0x0                       | 0x0                  | 0x0    | 0x0        | 0x0        | Device remote wake-up                   |

| EP SET_FEATURE                            | 0x02    | 0x3     | 0x0                       | 0x0                       | 0x0,<br>0x4,<br>0x84 | 0x0    | 0x0        | 0x0        | Endpoint halt                           |

| SET_ADDRESS                               | 0x00    | 0x5     | addr                      | 0x0                       | 0x0                  | 0x0    | 0x0        | 0x0        | addr = 1 to 127                         |

| GET_DESCRIPTOR                            | 0x80    | 0x6     | 0x0                       | 0x1                       | 0x0                  | 0x0    | len<br>MSB | len<br>MSB | Device descriptor                       |

| GET_DESCRIPTOR                            | 0x80    | 0x6     | 0x0                       | 0x2                       | LangID               | LangID | len<br>MSB | len<br>MSB | Configuration descriptor                |

| GET_DESCRIPTOR                            | 0x80    | 0x6     | 0x0                       | 0x3                       | 0x0                  | 0x0    | len<br>MSB | len<br>MSB | String descriptor                       |

| GET_CONFIGURATION                         | 0x80    | 0x8     | 0x0                       | 0x0                       | 0x0                  | 0x0    | 0x1        | 0x0        |                                         |

| SET_CONFIGURATION                         | 0x00    | 0x9     | n                         | 0x0                       | 0x0                  | 0x0    | 0x0        | 0x0        | n = 0, 1                                |

|                                           |         |         | USB                       | Class Sp                  | ecific Requ          | ests   |            |            |                                         |

| CDC_ECM_IF_<br>SET_ETH_MCAST_FIL-<br>TERS | 0x21    | 0x40    | Number (N) of filters LSB | Number (N) of filters MSB | 0x0                  | 0x0    | N*6<br>LSB | N*6<br>MSB |                                         |

| CDC_ECM_IF_<br>SET_ETH_PACKET<br>FILTERS  | 0x21    | 0x43    | *Bit-<br>map<br>LSB       | *Bit-<br>map<br>MSB       | 0x0                  | 0x0    | 0x0        | 0x0        | See Bitmap definition in note 1 below   |

| CDC_ECM_IF_<br>GET_ETH_STATISTIC          | 0xA1    | 0x44    | Selec<br>tor              | 0x0                       | 0x0                  | 0x0    | 0x4        | 0x0        | See Selector definition in note 2 below |

**Table 3: Supported USB Control Commands**

| Name                         | Request | Request  | Va  | lue | Ind | lex | Ler | ıgth | Description                                                           |

|------------------------------|---------|----------|-----|-----|-----|-----|-----|------|-----------------------------------------------------------------------|

| Name                         | Туре    | riequest | LSB | MSB | LSB | MSB | LSB | MSB  | Description                                                           |

| USB Vendor Specific Requests |         |          |     |     |     |     |     |      |                                                                       |

| XR_GET_CHIP_ID               | 0xC0    | 0xFF     | 0x0 | 0x0 | 0x0 | 0x0 | 0x6 | 0x0  | Get Exar VID (2 bytes),<br>PID (2 bytes) and bcdDe-<br>vice (2 bytes) |

#### Note 1: SET\_ETH\_PACKET\_FILTERS Bitmap definition:

D15..D5: reserved

D4: MULTICAST If 1, packets with multicast addresses set by SetEthernetMulticastFilter are forwarded to the host. 0 = Disabled.

D3: BROADCAST If 1, broadcast packets are forwarded to the host. 0 = Disabled.

D2: DIRECTED If 1, unicast packets with a matching address are forwarded to the host. 0 = Disabled.

D1: ALL\_MULTICAST If 1, all multicast packets are forwarded to the host. 0 = Disabled.

D0: PROMISCUOUS If 1, all packets are forwarded to the host, regardless of address. 0 = Disbled.

Note 2: SET\_ETH\_PACKET\_FILTERS Selector definition:

$0x01 = XMIT_OK$

$0x02 = RCV_OK$

$0x03 = XMIT\_ERROR$

$0x04 = RCV\_ERROR$

0x05 = RCV\_NO\_BUFFER

0x0d = DIRECTED\_FRAME\_RCV

0x0f = MULTICAST\_FRAME\_RCV

$0x11 = BROADCAST_FRAME_RCV$

0x12 = RCV\_CRC\_ERROR

0x13 = XMIT\_QUEUE\_LENGTH

0x14 = RCV\_ERR\_ALIGNMENT

0x19 = RCV\_OVERRUN

## **HID Reports**

The  $I^2C$  and EDGE functions in the XR22800 are HID functions.  $I^2C$  data may be read or written to / from the slave device using the interrupt in and interrupt out endpoints via HID input and output reports. Additionally, XR22800 device register access using the control endpoint for both  $I^2C$  and EDGE functions is performed via HID feature reports. Reading uses indirect addressing such that for register reads, the register address must first be written and the register value may then be read. Both types of reports are described below.

Input and Output Reports

Input and output reports using the interrupt in and interrupt out endpoints follow the following format. For more information on reading and writing on the I<sup>2</sup>C interface refer to AN220, Programming applications using the XR2280x I<sup>2</sup>C Interface.

#### **I2C SLAVE OUT**

Transfer Type: Interrupt Out Transfer Size: 37 bytes

The I2C\_SLAVE\_OUT report writes and / or reads up to 32 bytes of data on the I<sup>2</sup>C interface. Note that all interrupt out transfers will be automatically followed by an interrupt in transfer. For write only transfers, the interrupt in packet will contain the status of the interrupt out transfer. For read only or write and read transfers, the interrupt in packet will contain the read data, as well as the status of the interrupt out transfer. The format of the interrupt out packet is given below.

| Field     | Offset | Size | Value  | Description                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------|--------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Report ID | 0      | 1    | 0x00   | Write, read, or write and read I <sup>2</sup> C data                                                                                                                                                                                                                                                                                                                                                                         |

| Flags     | 1      | 1    | Bitmap | Transfer options D0: Prefix transfer with a start bit. D1: Append a stop bit to the transfer. D2: ACK last read to extend a read transfer (e.g. if more than 32 bytes need to be read). The default is to NAK the last read in the transfer. This bit has no effect if RdSize is 0. D3: Reserved D7D4: Sequence number. This can help the host to correlate an IN response with a prior OUT command. This field is optional. |

| WrSize    | 2      | 1    | Number | Number of data bytes to write. Valid values are 0 to 32. The 7-bit slave address should not be included in this total.                                                                                                                                                                                                                                                                                                       |

| RdSize    | 3      | 1    | Number | Number of bytes to read. Valid values are 0 to 32.                                                                                                                                                                                                                                                                                                                                                                           |

| SlaveAddr | 4      | 1    | Number | The 7-bit slave address* to send. The XR22800 will automatically set the I2 C read/write bit, so bit D0 of this field is ignored.                                                                                                                                                                                                                                                                                            |

| Data      | 5      | 32   | Data   | Data to be written to the slave. HID uses a fixed report size for each specific report ID so this field will always be 32 bytes long. However, only the number of bytes specified in WrSize will be written. Other bytes will be ignored.                                                                                                                                                                                    |

<sup>\*</sup> Note: To support 10-bit addressing the standard 7-bit address must be set to 1111 0xxB where xx are the most significant bits of the 10-bit address. All 4 of these 7-bit addresses are reserved and will not be used by any slaves with 7-bit only addresses. The least significant bit of the address byte still specifies the direction. For writes, the first data byte which was previously unformatted is now reserved for the least significant 8 bits of the 10-bit address. Additional data bytes remain unformatted. For reads, the write-then-read combined transfer format is always used. During the write portion of the combined transfer the master must send at least one data byte which contains the least significant 8 bits of the 10-bit address. After all of the write data is sent the master then sends a restart bit. This is followed with an address byte which has the same 7-bit address 1111 0xxB as in the write portion. However, the direction bit is now 1 for reading. The slave then sends the read data as usual. The least significant 8 bits of the 10-bit address are not sent again after the restart bit.

#### I2C\_SLAVE\_IN

Transfer Type: Interrupt In Transfer Size: 37 bytes

Interrupt in packet status only, or status and read data from the I2C interface.

| Field     | Offset | Size | Value  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------|--------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Report ID | 0      | 1    | 0x00   | I <sup>2</sup> C response packet                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Flags     | 1      | 1    | Bitmap | Status of the requested transfer.  D0: Request Error. If 1, the OUT request had an error (e.g. invalid size) and was not executed.  D1: A byte sent to a slave received an I2C NAK response. The transfer was aborted.  D2: Arbitration was lost. The transfer was aborted.  D3: Timeout. Bus free condition was not observed within 256 ms or an individual byte transfer extended longer than 10ms.  D7.D4: Sequence number. This number matches the value provided in the corresponding OUT command packet. |

| WrSize    | 2      | 1    | Number | Number of bytes written, 0 to 32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RdSize    | 3      | 1    | Number | Number of bytes read, 0 to 32.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Reserved  | 4      | 1    | 0x00   | This field is reserved and should always return a value of 0x00.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Data      | 5      | 32   | Data   | The read data that was received from the slave. HID uses a fixed report size for each specific report ID, so this field will always be 32 bytes long. However, only the number of bytes specified in RdSize are valid. Other bytes should be ignored.                                                                                                                                                                                                                                                          |

#### **Feature Reports**

Access to XR22800 registers via HID feature reports along with the register descriptions are given in the following sections.

WRITE\_HID\_REGISTER

Transfer Type: Control

Transfer Size: 5 bytes

The WRITE\_HID\_REGISTER report writes 2 bytes of data to the specified register address.

| Field             | Offset | Size | Value | Description        |

|-------------------|--------|------|-------|--------------------|

| Report ID         | 0      | 1    | 0x3C  | Write HID register |

| Write Address LSB | 1      | 1    |       | Write address      |

| Write Address MSB | 2      | 1    |       |                    |

| Write Data LSB    | 3      | 1    |       | Write data         |

| Write Data MSB    | 4      | 1    |       |                    |

#### SET\_HID\_READ\_ADDRESS

Transfer Type: Control Transfer Size: 3 bytes

The SET\_HID\_READ\_ADDRESS report sets the address for the READ\_HID\_REGISTER report.

| Field            | Offset | Size | Value | Description                       |

|------------------|--------|------|-------|-----------------------------------|

| Report ID        | 0      | 1    | 0x4B  | Set address for HID register read |

| Read Address LSB | 1      | 1    |       | Read address                      |

| Read Address MSB | 2      | 1    |       |                                   |

## READ\_HID\_REGISTER Transfer Type: Control Transfer Size: 3 bytes

The READ\_HID\_REGISTER report reads register data from the address set by the SET\_HID\_READ\_ADDRESS report.

| Field         | Offset | Size | Value | Description       |

|---------------|--------|------|-------|-------------------|

| Report ID     | 0      | 1    | 0x5A  | Read HID register |

| Read Data LSB | 1      | 1    |       | Read data         |

| Read Data MSB | 2      | 1    |       |                   |

# HID Register Map

Table 4: XR22800 HID Register Map

| Address                  | Register Name                        | Bit 7<br>(15) | Bit 6<br>(14) | Bit 5<br>(13) | Bit 4<br>(12) | Bit 3<br>(11) | Bit 2<br>(10) | Bit 1<br>(9) | Bit 0<br>(8) |  |  |

|--------------------------|--------------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--|--|

| I <sup>2</sup> C Registe | rs                                   |               |               |               |               |               |               |              |              |  |  |

| 0x341                    | I <sup>2</sup> C_SCL_LOW MSB [15:8]  | VALUE (MSB)   |               |               |               |               |               |              |              |  |  |

| 0x341                    | I <sup>2</sup> C_SCL_LOW LSB [7:0]   | VALUE (LSB)   |               |               |               |               |               |              |              |  |  |

|                          | I <sup>2</sup> C_SCL_HIGH MSB [15:8] |               |               |               | VALUE         | (MSB)         |               |              |              |  |  |

| 0x342                    | I <sup>2</sup> C_SCL_HIGH LSB [7:0]  |               |               |               | VALUE         | (LSB)         |               |              |              |  |  |

| EDGE Reg                 | isters                               |               |               |               |               |               |               |              |              |  |  |

| 0x3C1                    | EDGE_DIR                             | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C2                    | EDGE_SET                             | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C3                    | EDGE_CLEAR                           | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C4                    | EDGE_STATE                           | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C5                    | EDGE_TRI_STATE                       | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C6                    | EDGE_OPEN_DRAIN                      | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C7                    | EDGE_PULL_UP                         | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C8                    | EDGE_PULL_DOWN                       | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3C9                    | EDGE_INTR_MASK                       | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0x3CA                    | EDGE_INTR_POS_<br>EDGE               | E7            | E6            | E5            | E4            | E3            | E2            | E1           | E0           |  |  |

| 0000                     | EDGE_PWM0_CTRL MSB<br>[15:8]         | 0             | 0             | 0             | 0             | 0             | 0             | 0            | CMD[2]       |  |  |

| 0x3D8                    | EDGE_PWM0_CTRL LSB<br>[7:0]          | CMD[1:0]      |               | EN            | 0             | 0 PIN         |               | 1            |              |  |  |

| 0v2D0                    | EDGE_PWM0_HIGH MSB<br>[15:8]         | 0 0           |               | 0             | 0             | VALUE[11:8]   |               |              |              |  |  |

| 0x3D9                    | EDGE_PWM0_HIGH LSB<br>[7:0]          | VALUE [7:0]   |               |               |               |               |               |              |              |  |  |

| 0x3DA                    | EDGE_PWM0_LOW MSB<br>[15:8]          | 0             | 0 0 0         |               | 0             | VALUE[11:8]   |               |              |              |  |  |

| UXSDA                    | EDGE_PWM0_LOW LSB<br>[7:0]           | VALUE [7:0]   |               |               |               |               |               |              |              |  |  |

| 0x3DB                    | EDGE_PWM1_CTRL MSB<br>[15:8]         | 0             | 0             | 0             | 0             | 0             | 0             | 0            | CMD[2]       |  |  |

| UXSDB                    | EDGE_PWM1_CTRL<br>LSB [7:0]          | СМЕ           | D[1:0]        | EN            | 0             | 0             |               | PIN          |              |  |  |

## Table 4: XR22800 HID Register Map

| Address | Register Name                | Bit 7<br>(15) | Bit 6<br>(14) | Bit 5<br>(13) | Bit 4<br>(12) | Bit 3<br>(11) | Bit 2<br>(10) | Bit 1<br>(9) | Bit 0<br>(8) |  |

|---------|------------------------------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--|

| 0x3DC   | EDGE_PWM1_HIGH MSB<br>[15:8] | 0             | 0             | 0             | 0             | VALUE[11:8]   |               |              |              |  |

| OXSDC   | EDGE_PWM1_HIGH LSB<br>[7:0]  | VALUE [7:0]   |               |               |               |               |               |              |              |  |

| 0x3DD   | EDGE_PWM1_LOW MSB<br>[15:8]  | 0             | 0             | 0             | 0             | VALUE[11:8]   |               |              |              |  |

| OXSDD   | EDGE_PWM1_LOW LSB [7:0]      | VALUE [7:0]   |               |               |               |               |               |              |              |  |

#### **HID Register Descriptions**

Note that all register reset default values are '0' unless otherwise specified. All registers are 16 bits.  $I^2C\_SCL\_LOW$  (0x341) - Read/Write

| Bit  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | 0x0144  | Value  Specifies the number of periods that SCL will be asserted low by the XR22800 I <sup>2</sup> C master. Note that in clock stretching, the I <sup>2</sup> C slave may extend the SCL low period to delay the next transaction. For 100 kbps transfer rate this value must be at least 252 (0x00FC) and the sum of high and low periods must be at least 600 (0x0258). For 400kbps transfer rate this value must be at least 78 (0x004E) and the sum of the high and low periods must be at least 150 (0x0096). Measured in 60 MHz core clock periods, i.e. approximately 16.7 ns. |

# I<sup>2</sup>C\_SCL\_HIGH (0x342) - Read/Write

| Bit  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:0 | 0x0114  | Value  Specifies the number of periods that SCL will be asserted high by the XR22800 I <sup>2</sup> C master. Note that another multi-master may assert SCL low before the XR22800 high period is completed. For 100 kbps transfer rate this value must be at least 240 (0x00F0) and the sum of the high and low periods must be at least 600 (0x0258). For 400 kbps transfer rate this value must be at least 36 (0x0024) and the sum of the high and low periods must be at least 150 (0x0096). Measured in 60 MHz core clock periods, i.e. approximately 16.7 ns |

#### EDGE\_DIR (0x3C1) - Read/Write

Note that when setting direction of an EDGE IO to output, the EDGE\_PULL\_UP for that IO pin should also be disabled and when setting an EDGE IO pin to input, the EDGE\_PULL\_UP for that IO pin should also be enabled.

| Bit  | Default | Description                                                                                                                          |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | 0x00    | Reserved These bits are reserved and should be written as '0'.                                                                       |

| 7:0  | 0x00    | E[7:0] 0: IO pin assigned to EDGE function is configured as an input 1: IO pin assigned to EDGE function is configured as an output. |

#### EDGE\_SET (0x3C2) - Write Only

| Bit  | Default | Description                                                                                            |

|------|---------|--------------------------------------------------------------------------------------------------------|

| 15:8 | 0x00    | Reserved These bits are reserved and should be written as '0'.                                         |

| 7:0  | 0x00    | E[7:0] 0: No effect 1: Set IO pin assigned to EDGE function and configured as an output to a logic '1' |

EDGE\_CLEAR (0x3C3) - Write Only

| Bit  | Default | Description                                                                                              |

|------|---------|----------------------------------------------------------------------------------------------------------|

| 15:8 | 0x00    | Reserved These bits are reserved and should be written as '0'.                                           |

| 7:0  | 0x00    | E[7:0] 0: No effect 1: Clear IO pin assigned to EDGE function and configured as an output to a logic '0' |

## EDGE\_STATE (0x3C4) - Read/Write

| Bit  | Default | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | 0xFF    | Reserved These bits are reserved and should be written as '1'.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7:0  | 0x00    | E[7:0] Writing in this register sets or clears the EDGE IO pin(s) configured as an output. Writing to an EDGE pin configured as an input has no effect. Reading this register returns the state of each IO pin configured as an EDGE pin irrespective of whether it is configured as an input or output. Note that output transitions across multiple IO pins may be slightly staggered. Refer to page 10.  0: Write clears the corresponding bit to a '0'. Read returns the current state.  1: Write sets the corresponding bit to a '1'. Read returns the current state. |

## EDGE\_TRI\_STATE (0x3C5) - Read/Write

| Bit  | Default | Description                                                                                                                                                             |

|------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | 0x00    | Reserved These bits are reserved and should be written as '0'.                                                                                                          |

| 7:0  | 0x00    | E[7:0] 0: IO pin assigned to EDGE function and configured as an output is actively driven 1: IO pin assigned to EDGE function and configured as an output is tri-stated |

## EDGE\_OPEN\_DRAIN (0x3C6) - Read/Write

| Bit  | Default | Description                                                                                                                                                                    |

|------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | 0x00    | Reserved These bits are reserved and should be written as '0'.                                                                                                                 |

| 7:0  | 0x00    | E[7:0]  Note that XR22800 open drain outputs have a weak internal pull-up.                                                                                                     |

|      |         | O: IO pin assigned to EDGE function and configured as an output is a push-pull output     IO pin assigned to EDGE function and configured as an output is an open drain output |

## EDGE\_PULL\_UP (0x3C7) - Read/Write

| Bit  | Default | Description                                                                                                                                                                                                   |

|------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:8 | 0xFF    | Reserved These bits are reserved and should be written as '1'.                                                                                                                                                |

| 7:0  | 0xFF    | E[7:0] 0: Disable internal pull-up resistor on IO pin assigned to EDGE function and configured as an input 1: Enable internal pull-up resistor on IO pin assigned to EDGE function and configured as an input |

## EDGE\_PULL\_DOWN (0x3C8) - Read/Write