### **General Description**

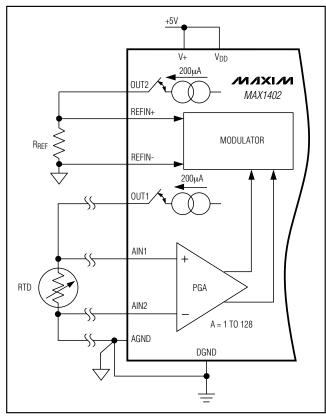

The MAX1402 low-power, multichannel, serial-output analog-to-digital converter (ADC) features matched 200µA current sources for sensor excitation. This ADC uses a sigma-delta modulator with a digital decimation filter to achieve 16-bit accuracy. The digital filter's userselectable decimation factor allows the conversion resolution to be reduced in exchange for a higher output data rate. True 16-bit performance is achieved at an output data rate of up to 480sps. In addition, the modulator sampling frequency may be optimized for either lowest power dissipation or highest throughput rate. The MAX1402 operates from a +5V supply.

This device offers three fully differential input channels that may be independently programmed with a gain between +1V/V and +128V/V. Furthermore, it can compensate an input-referred DC offset up to 117% of the selected full-scale range. These three differential channels may also be configured to operate as five pseudodifferential input channels. Two additional, fully differential system-calibration channels are provided for gain and offset error correction.

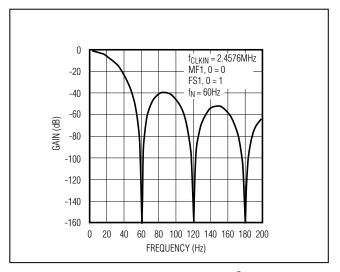

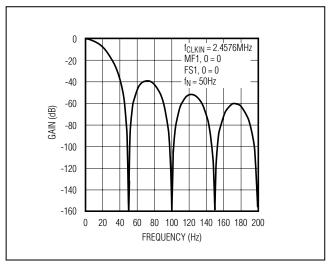

The MAX1402 may be configured to sequentially scan all signal inputs and provide the results via the serial interface with minimum communications overhead. When used with a 2.4576MHz or 1.024MHz master clock, the digital decimation filter can be programmed to produce zeros in its frequency response at the line frequency and associated harmonics, ensuring excellent line rejection without the need for further post-filtering.

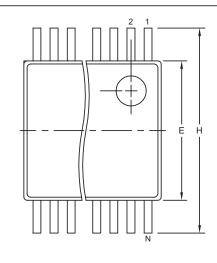

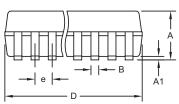

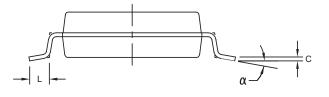

The MAX1402 is available in a 28-pin SSOP package.

### **Applications**

Portable Industrial Instruments Portable Weigh Scales Loop-Powered Systems Pressure Transducers

### **Ordering Information**

| PART       | TEMP RANGE     | PIN-<br>PACKAGE | PKG<br>CODE |

|------------|----------------|-----------------|-------------|

| MAX1402CAI | 0°C to +70°C   | 28 SSOP         | A28-2       |

| MAX1402EAI | -40°C to +85°C | 28 SSOP         | A28-2       |

SPI and QSPI are trademarks of Motorola, Inc.

#### Features

- ♦ 18-Bit Resolution, Sigma-Delta ADC

- ♦ 16-Bit Accuracy with No Missing Codes to 480sps

- **♦ Low Quiescent Current** 250µA (operating mode) 2µA (power-down mode)

- ♦ Matched On-Board Current Sources (200µA) for Sensor Excitation

- ♦ 3 Fully Differential or 5 Pseudo-Differential Signal Input Channels

- ♦ 2 Additional, Fully Differential Calibration **Channels/Auxiliary Input Channels**

- ♦ Programmable Gain and Offset

- **♦** Fully Differential Reference Inputs

- **♦** Converts Continuously or On Command

- **♦ Automatic Channel Scanning and Continuous Data Output Mode**

- ♦ Operates with +5V Analog Supply and +3V or +5V **Digital Supply**

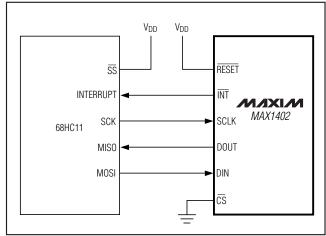

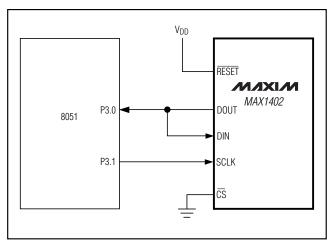

- **♦** 3-Wire Serial Interface—SPI™/QSPI™ Compatible

- ♦ 28-Pin SSOP Package

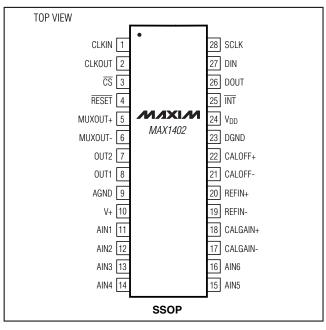

### Pin Configuration

Maxim Integrated Products 1

#### **ABSOLUTE MAXIMUM RATINGS**

| V+ to AGND, DGND                 | 0.3V to +6V                      |

|----------------------------------|----------------------------------|

| VDD to AGND, DGND                | 0.3V to +6V                      |

| AGND to DGND                     | 0.3V to +0.3V                    |

| Analog Inputs to AGND            | 0.3V to (V+ + 0.3V)              |

| Analog Outputs to AGND           | 0.3V to $(V + + 0.3V)$           |

| Reference Inputs to AGND         | 0.3V to $(V + + 0.3V)$           |

| CLKIN and CLKOUT to DGND         | 0.3V to (V <sub>DD</sub> + 0.3V) |

| All Other Digital Inputs to DGND | 0.3V to +6V                      |

| All Digital Outputs to DGND      | 0.3V to (V <sub>DD</sub> + 0.3V) |

|                                  |                                  |

| Maximum Current Input into Any Pir | ı50mA             |

|------------------------------------|-------------------|

| Continuous Power Dissipation (TA = |                   |

| 28-Pin SSOP (derate 9.52mW/°C      | above +70°C)524mW |

| Operating Temperature Ranges       |                   |

| MAX1402CAI                         | 0°C to +70°C      |

| MAX1402EAI                         | 40°C to +85°C     |

| Storage Temperature Range          | 60°C to +150°C    |

| Lead Temperature (soldering, 10s). | +300°C            |

|                                    |                   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V+ = +5V \pm 5\%, V_{DD} = +2.7V \text{ to } +5.25V, V_{REFIN+} = +2.50V, REFIN- = AGND, f_{CLKIN} = 2.4576MHz, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at T\_A = +25°C.)

| PARAMETER                         | SYMBOL | CONDITIONS                                                              | MIN     | TYP      | MAX    | UNITS   |

|-----------------------------------|--------|-------------------------------------------------------------------------|---------|----------|--------|---------|

| STATIC PERFORMANCE                | •      |                                                                         | 1       |          |        |         |

| Noise-Free Resolution             |        | No missing codes guaranteed by design; for filter settings with FS1 = 0 | 16      |          |        | Bits    |

| Output Noise                      |        | Depends on filter setting and selected gain                             |         | Table 16 |        |         |

| Integral Nonlinearity             | INL    | Bipolar mode, filter settings with FS1 = 0                              | -0.0015 |          | 0.0015 | %FSR    |

| Nominal Gain (Note 1)             |        |                                                                         |         | 0.98     |        |         |

| Unipolar Offset Error             |        | Relative to nominal of 1% FSR                                           | -1      |          | 2      | %FSR    |

| Unipolar Offset Drift             |        | For gains of 1, 2, 4                                                    |         | 0.5      |        | µV/°C   |

| Onipolar Oliset Dilit             |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μν/ Ο   |

| Bipolar Zero Error                |        |                                                                         | -2.0    |          | 2.0    | %FSR    |

| Bipolar Zero Drift                |        | For gains of 1, 2, 4                                                    |         | 0.8      |        | μV/°C   |

|                                   |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μν, Ο   |

| Positive Full-Scale Error         |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | -2.5    |          | 2.5    | %FSR    |

| (Note 2)                          |        | For gain of 128                                                         | -3.5    |          | 3.5    | /61 311 |

| Full-Scale Drift (Note 3)         |        | For gains of 1, 2, 4                                                    |         | 0.8      |        | μV/°C   |

| Tull-Scale Difft (Note 3)         |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μν/ Ο   |

| Gain Error (Note 4)               |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | -2      |          | 2      | %FSR    |

| Gain Error (Note 4)               |        | For gain of 128                                                         | -3      |          | 3      | /0F3N   |

| Gain-Error Drift (Note 5)         |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     |         | 1        |        | ppm/°C  |

| Gain-End Diff (Note 3)            |        | For gain of 128                                                         |         | 5        |        | ррпі, С |

| Pipolar Nagativa Full Saala Error |        | For gains of 1, 2, 4, 8, 16, 32, 64                                     | -2.5    |          | 2.5    | %FSR    |

| Bipolar Negative Full-Scale Error |        | For gain of 128                                                         | -3.5    |          | 3.5    | /0F3F   |

| Bipolar Negative Full-Scale Drift |        | For gains of 1, 2, 4                                                    |         | 0.8      |        | μV/°C   |

| Dipolal Negative Full-Scale Dilit |        | For gains of 8, 16, 32, 64, 128                                         |         | 0.3      |        | μν/ Ο   |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = +5V \pm 5\%, V_{DD} = +2.7V \text{ to } +5.25V, V_{REFIN+} = +2.50V, REFIN- = AGND, f_{CLKIN} = 2.4576MHz, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C.$ )

| PARAMETER                                  | SYMBOL     | CONDITIONS                               |                                                                                                                  |                                                        | MIN              | TYP                  | MAX          | UNITS             |

|--------------------------------------------|------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|----------------------|--------------|-------------------|

| OFFSET DAC                                 |            |                                          |                                                                                                                  |                                                        |                  |                      |              |                   |

| Offeet DAC Denge (Note C)                  |            | Unipolar mode                            |                                                                                                                  |                                                        | -116.7           |                      | 116.7        | 0/ FCD            |

| Offset DAC Range (Note 6)                  |            | Bipolar mode                             | Bipolar mode                                                                                                     |                                                        |                  |                      | 58.35        | %FSR              |

| Offset DAC Resolution                      |            | Unipolar mode                            |                                                                                                                  |                                                        |                  | 16.7                 |              | %FSR              |

| Oliset DAC Resolution                      |            | Bipolar mode                             |                                                                                                                  |                                                        | 8.35             |                      | %F3H         |                   |

| Offset DAC Full-Scale Error                |            | Input referred                           | Gain = 1, 2, 4, 8, 16, 32, 64                                                                                    |                                                        | -2.5             |                      | 2.5          | %FSR              |

| Oliset DACT dil-Scale Elloi                |            | input relened                            | Gair                                                                                                             | n = 128                                                | -3.5             |                      | 3.5          | /01 311           |

| Offset DAC Zero-Scale Error                |            |                                          |                                                                                                                  |                                                        |                  | 0                    |              | %FSR              |

| Additional Noise from Offset DAC (Note 7)  |            | DAC code = 000                           | 00                                                                                                               |                                                        |                  | 0                    |              | μV <sub>RMS</sub> |

| ANALOG INPUTS/REFERENCE                    | INPUTS (Sp | pecifications for Al                     | N and                                                                                                            | REFIN, unless otherwise                                | e noted.)        |                      |              |                   |

|                                            |            | At DC                                    |                                                                                                                  |                                                        | 90               |                      |              |                   |

| Common-Mode Rejection                      | CMR        | For filter notch 50l<br>MF1 = 0, MF0 = 0 |                                                                                                                  | 0.02 • f <sub>NOTCH</sub> ,<br>IN = 2.4576MHz (Note 8) | 150              |                      |              | dB                |

|                                            |            |                                          | For filter notch 60Hz, ±0.02 • f <sub>NOTCH</sub> ,<br>MF1 = 0, MF0 = 0, f <sub>CLKIN</sub> = 2.4576MHz (Note 8) |                                                        |                  |                      |              |                   |

| Normal-Mode 50Hz Rejection (Note 8)        | NMR        | For filter notch 50<br>MF1 = 0, MF0 =    |                                                                                                                  | E0.02 • f <sub>NOTCH</sub> ,<br>KIN = 2.4576MHz        | 100              |                      |              | dB                |

| Normal-Mode 60Hz Rejection (Note 8)        | NMR        | For filter notch 60<br>MF1 = 0, MF0 =    |                                                                                                                  | ±0.02 • f <sub>NOTCH</sub> ,<br>KIN = 2.4576MHz        | 100              |                      |              | dB                |

| Common-Mode Voltage Range (Note 9)         |            | REFIN and AIN f                          | or BU                                                                                                            | FF = 0                                                 | VAGND            |                      | V+           | V                 |

| Absolute Input Voltage Range               |            | REFIN and AIN f                          | or BU                                                                                                            | FF = 0                                                 | VAGND<br>- 30mV  |                      | V+<br>+ 30mV | V                 |

| Absolute and Common-Mode AIN Voltage Range |            | BUFF = 1                                 |                                                                                                                  |                                                        | VAGND<br>+ 200mV |                      | V+<br>- 1.5  | V                 |

| DC Input Leakage Current                   |            | REFIN and AIN f                          | or                                                                                                               | T <sub>A</sub> = +25°C                                 |                  | 40                   |              | рА                |

| (Note 10)                                  |            | BUFF = 0                                 |                                                                                                                  | $T_A = T_{MIN}$ to $T_{MAX}$                           |                  |                      | 10           | nA                |

| AIN Input Current (Note 10)                |            | BUFF = 1                                 |                                                                                                                  |                                                        |                  | 10                   | nA           |                   |

|                                            |            |                                          |                                                                                                                  | Gain = 1                                               |                  | 34                   |              |                   |

| AINI land to Company                       |            | BUFF = 0                                 |                                                                                                                  | Gain = 2                                               |                  | 38                   |              |                   |

| AIN Input Capacitance (Note 11)            |            | Gain = 4<br>Gain = 8, 16, 32, 64, 128    |                                                                                                                  | Gain = 4                                               |                  | 45                   |              | рF                |

| · ···                                      |            |                                          |                                                                                                                  |                                                        | 60               |                      |              |                   |

|                                            |            | BUFF = 1, all ga                         | ins                                                                                                              |                                                        |                  | 30                   |              |                   |

| AIN Differential Voltage Range             |            | Unipolar input ra                        | •                                                                                                                | ,                                                      | 0 to             | V <sub>REF</sub> / g | gain         | V                 |

| (Note 12)                                  |            | Bipolar input ran                        | ge (U                                                                                                            | $\overline{/B}$ bit = 0)                               | ±\               | REF / ga             | ain          | v                 |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+=+5V~\pm5\%, V_{DD}=+2.7V~to~+5.25V, V_{REFIN+}=+2.50V, REFIN-=AGND, f_{CLKIN}=2.4576MHz, T_{A}=T_{MIN}~to~T_{MAX}, unless otherwise noted. Typical values are at T_{A}=+25^{\circ}C.)$

| PARAMETER                              | SYMBOL                                |                             | CC                                              | ONDITIONS                         | MIN                   | TYP       | MAX      | UNITS  |

|----------------------------------------|---------------------------------------|-----------------------------|-------------------------------------------------|-----------------------------------|-----------------------|-----------|----------|--------|

| AIN and REFIN Input Sampling Frequency | fS                                    |                             |                                                 |                                   |                       | (Table 15 | )        | Hz     |

| REFIN+ - REFIN- Voltage<br>(Note 13)   |                                       | ±5% for spe<br>with lower \ |                                                 | performance; functional           |                       |           | 2.50     | V      |

| LOGIC INPUTS                           |                                       |                             |                                                 |                                   |                       |           |          |        |

| Input Current                          | liN                                   |                             |                                                 |                                   | -10                   |           | +10      | μΑ     |

|                                        |                                       | All inputs ex               | xcept                                           | $V_{DD} = 5V$                     |                       |           | 0.8      |        |

| la act Laco Valta ac                   | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | CLKIN                       | ·                                               | $V_{DD} = 3.3V$                   |                       |           | 0.4      | \ /    |

| Input Low Voltage                      | VIL                                   | CLKIN only                  |                                                 | V <sub>DD</sub> = 5V              |                       |           | 0.8      | V      |

|                                        |                                       | CLKIN only                  |                                                 | $V_{DD} = 3.3V$                   |                       |           | 0.4      |        |

|                                        |                                       | All inputs ex               | xcept                                           | $V_{DD} = 5V$                     | 2                     |           |          |        |

| Input High Voltage                     | VIH                                   | CLKIN                       |                                                 | V <sub>DD</sub> = 3.3V            | 2                     |           |          | V      |

| Input High Voltage                     |                                       | CLKIN only                  | ,                                               | $V_{DD} = 5V$                     | 3.5                   |           |          | V      |

|                                        |                                       | CLKIN only                  |                                                 | V <sub>DD</sub> = 3.3V            | 2.4                   |           |          |        |

| Input Hystorogia                       | \/. p.co                              | All inputs e                | xcept                                           | V <sub>DD</sub> = 5V              |                       | 200       |          | mV     |

| Input Hysteresis                       | V <sub>H</sub> YS                     | CLKIN                       |                                                 | $V_{DD} = 3.3V$                   |                       | 200       |          | IIIV   |

| LOGIC OUTPUTS                          | •                                     | 1                           |                                                 |                                   | 1                     |           |          |        |

|                                        |                                       | DOUT                        | V <sub>DD</sub> = 5V, I <sub>SINK</sub> = 800μA |                                   |                       |           | 0.4      |        |

| Output Low Voltage (Note 14)           | VOL                                   | and INT                     | $V_{DD}$                                        | = 3.3V, I <sub>SINK</sub> = 100µA | 1                     |           | 0.4      | V      |

| Output Low Voltage (Note 14)           | VOL                                   | CLKOUT                      | V <sub>DD</sub>                                 | = 5V, I <sub>SINK</sub> = 10µA    |                       |           | 0.4      | V      |

|                                        |                                       | CLROOT                      | V <sub>DD</sub>                                 | = 3.3V, ISINK = 10µA              |                       |           | 0.4      |        |

|                                        |                                       | DOUT                        | $V_{DD}$                                        | = 5V, I <sub>SOURCE</sub> = 200µA | 4                     |           |          |        |

| Output High Voltage (Note 14)          | V <sub>OH</sub>                       | and INT                     |                                                 | = 3.3V, ISOURCE = 100µA           | V <sub>DD</sub> - 0.3 | 3         |          |        |

|                                        | 1011                                  | CLKOUT                      |                                                 | = 5V, ISOURCE = 10μA              | 4                     |           |          |        |

|                                        |                                       |                             | VDD                                             | = 3.3V, ISOURCE = 10μA            | V <sub>DD</sub> - 0.3 | 3         |          |        |

| Floating-State Leakage Current         | IL                                    |                             |                                                 |                                   | -10                   |           | 10       | μΑ     |

| Floating-State Output<br>Capacitance   | Со                                    |                             |                                                 |                                   |                       | 9         |          | pF     |

| TRANSDUCER BURN-OUT (Not               | e 15)                                 |                             |                                                 |                                   | _                     |           |          |        |

| Current                                | I <sub>BO</sub>                       |                             |                                                 |                                   |                       | 0.1       |          | μΑ     |

| Initial Tolerance                      |                                       |                             |                                                 |                                   |                       | ±10       |          | %      |

| Drift                                  |                                       |                             |                                                 |                                   |                       | ±0.05     |          | %/°C   |

| TRANSDUCER EXCITATION C                | JRRENTS                               |                             |                                                 |                                   |                       |           |          |        |

| Current                                | IEXC                                  |                             |                                                 |                                   |                       | 200       |          | μΑ     |

| Initial Tolerance                      |                                       |                             |                                                 |                                   |                       |           | 15       | %      |

| Drift                                  |                                       |                             |                                                 |                                   |                       | 100       |          | ppm/°C |

| Match                                  |                                       | OUT1 to Ol                  | JT2                                             |                                   |                       |           | ±1       | %      |

| Drift Match                            |                                       |                             |                                                 |                                   |                       | 5         |          | ppm/°C |

| Compliance Voltage Range               |                                       |                             |                                                 |                                   | Vagnd                 |           | V+ - 1.0 | V      |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = +5V \pm 5\%, V_{DD} = +2.7V \text{ to } +5.25V, V_{REFIN+} = +2.50V, REFIN- = AGND, f_{CLKIN} = 2.4576MHz, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                                       | SYMBOL          | CONDITIONS                      |                   | MIN         | TYP         | MAX          | UNITS     |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|-----------------------------------------------------------------|-----------------|---------------------------------|-------------------|-------------|-------------|--------------|-----------|--------------|-----------|-------------|-------|-------|-------|------------|---|-----|--|--|--|--|--------|--------|------------|--|-----|

| POWER REQUIREMENTS                                              | •               |                                 |                   |             |             | •            |           |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| V+ Voltage                                                      | V+              | For specified pe                | rformano          | ce          |             | 4.75         |           | 5.25         | V         |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| V <sub>DD</sub> Voltage                                         | V <sub>DD</sub> |                                 |                   |             |             | 2.7          |           | 5.25         | V         |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| Power-Supply Rejection V+ (Note 16)                             | PSR             |                                 |                   |             |             | (Note 17)    |           | dB           |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| <b>ANALOG POWER-SUPPLY CL</b> iary currents disabled, X2CLK =   |                 |                                 |                   |             |             | , external ( | CLKIN, bu | ırn-out an   | d auxil-  |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| V+ Standby Current (Note 18)                                    |                 | PD bit = 1, exter               | nal clock         | < stop      | ped         |              | 1         | 10           | μA        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 | 1.0041            | 41.1-       | Buffers off |              | 175       | 210          |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | Normal mode,                    | 1.024             | VIHZ        | Buffers on  |              | 370       | 420          |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | MF1 = 0,<br>MF0 = 0             | 0.4570            | 20.41.1     | Buffers off |              | 250       | 300          |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 | 2.4576            | OIVIHZ      | Buffers on  |              | 610       | 700          | μΑ        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 | 4 00 41           | 41.1        | Buffers off |              | 245       |              | -         |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | 2X mode,                        | 1.024             | VIHZ        | Buffers on  |              | 610       |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | MF1 = 0,<br>MF0 = 1             | 0.4570            | SN 41 1-    | Buffers off |              | 0.42      | 0.55         |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| V. O                                                            |                 | 4X mode, 1<br>MF1 = 1,          | 2.4576            | OIVIHZ      | Buffers on  |              | 1.2       | 1.5          |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| V+ Current                                                      | l <sub>V+</sub> |                                 |                   | 1.0041      | 41.1-       | Buffers off  |           | 0.42         |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 | 1.024MHz          |             | Buffers on  |              | 1.2       |              | - mA      |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 | L 2 4576MHz       | Buffers off |             | 1.8          | 2.2       |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | 5                               |                   | Buffers on  |             | 4.8          | 6         |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | 8X mode,<br>MF1 = 1,<br>MF0 = 1 | MF1 = 1,          | 1.0041      | 41.1-       | Buffers off  |           | 1.8          |           | İ           |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 |                   |             |             |              |           |              |           |             |       | 1.024 | VIHZ  | Buffers on |   | 4.8 |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 |                   | 2.4576      | SN 41 1-    | Buffers off  |           | 1.8          | 2.2       |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 |                                 |                   |             | 5           |              | 0 = 1     | 1,,,,, 0 = 1 | 10 0 = 1  | 1 1 1 1 1 1 | 0 – 1 | 0 – 1 | 0 = 1 | 5          | , | 5   |  |  |  |  | 2.4576 | DIVIMZ | Buffers on |  | 4.8 |

| <b>DIGITAL POWER-SUPPLY CUI</b> currents disabled, X2CLK = 0, C |                 |                                 |                   |             |             | external C   | LKIN, bur | n-out and    | auxiliary |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| V <sub>DD</sub> Standby Current (Note 18)                       |                 | PD bit = 1, exter               | nal clock         | k stop      | ped         |              | 1         | 10           | μΑ        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | Normal mode,                    |                   | 1.024       | ИНz         |              | 70        | 200          | μA        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | MF1 = 0, MF0 =                  | 0                 | 2.4576      | 6MHz        |              | 150       | 300          | μΑ        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | 2X mode,                        |                   | 1.0241      | ИHz         |              | 0.08      |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| 3.3V Digital Supply Current                                     | IDD             | MF1 = 0, MF0 =                  | 1                 | 2.4576      | 6MHz        |              | 0.17      | 0.35         |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| 3.34 Digital Supply Current                                     | טטי             | 4X mode,                        | I .               | 1.024       | ИHz         |              | 0.11      |              | mΔ        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | MF1 = 1, MF0 =                  | 0                 | 2.4576      | 6MHz        |              | 0.22      | 0.40         | mA        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | 8X mode,                        | 8X mode, 1.024MHz |             | ИHz         |              | 0.15      |              |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | MF1 = 1, MF0 =                  | 1 :               | 2.4576      | 6MHz        |              | 0.32      | 0.45         |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | Normal mode,                    |                   | 1.0241      | ИHz         |              | 115       | 300          | μΑ        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| 5V Digital Supply Current                                       | IDD             | MF1 = 0, MF0 =                  | 0                 | 2.4576      | 6MHz        |              | 235       | 450          | μA<br>    |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

| ov Digital Supply Culterit                                      |                 | 2X mode,                        | I .               | 1.024       | ИHz         |              | 0.13      |              | mA        |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

|                                                                 |                 | MF1 = 0, MF0 =                  | 1 ;               | 2.4576MHz   |             |              | 0.28      | 0.5          |           |             |       |       |       |            |   |     |  |  |  |  |        |        |            |  |     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V+ = +5V \pm 5\%, V_{DD} = +2.7V \text{ to } +5.25V, V_{REFIN+} = +2.50V, REFIN- = AGND, f_{CLKIN} = 2.4576MHz, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}C$ .)

| PARAMETER                 | SYMBOL          | CONDITIONS       |           | MIN  | TYP  | MAX | UNITS |

|---------------------------|-----------------|------------------|-----------|------|------|-----|-------|

|                           | 4X mode,        | 1.024MHz         |           | 0.17 |      |     |       |

| 5V Digital Supply Current | loo             | MF1 = 1, MF0 = 0 | 2.4576MHz |      | 0.36 | 0.6 | mA    |

| 3v Digital Supply Current | I <sub>DD</sub> | 8X mode,         | 1.024MHz  |      | 0.24 |     | 111/4 |

|                           |                 | MF1 = 1, MF0 = 1 | 2.4576MHz |      | 0.53 | 0.8 |       |

**5V POWER DISSIPATION** ( $V+ = V_{DD} = +5V$ , digital inputs = 0 or  $V_{DD}$ , external CLKIN, burn-out and auxiliary currents disabled, X2CLK = 0, CLK = 0 for 1.024MHz, CLK = 1 for 2.4576MHz.)

|                           |    |                          | 1 0041411-     | Buffers off | 1.45 | 2.55                                                                                                                                  |       |  |  |

|---------------------------|----|--------------------------|----------------|-------------|------|---------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|

|                           |    | Normal mode,<br>MF1 = 0, | 1.024MHz       | Buffers on  | 2.43 | 2.43 3.6 2.43 3.75 4.23 5.75 1.88 3.7 3.5 5.25 7.4 10 2.95 6.85 10.8 14 25.8 33 10.2 25.2                                             |       |  |  |

|                           |    | MF0 = 0,                 | 2.4576MHz      | Buffers off | 2.43 | 3.75                                                                                                                                  |       |  |  |

|                           |    |                          | 2.4370WITZ     | Buffers on  | 4.23 | 5.75                                                                                                                                  |       |  |  |

|                           |    |                          | 1.024MHz       | Buffers off | 1.88 |                                                                                                                                       |       |  |  |

|                           |    | 2X mode,<br>MF1 = 0,     | 1.024101112    | Buffers on  | 3.7  |                                                                                                                                       |       |  |  |

| Device Dississetion       |    | MF0 = 1                  | 2.4576MHz      | Buffers off | 3.5  | 2.43 3.6<br>2.43 3.75<br>3.23 5.75<br>3.88<br>3.7<br>3.5 5.25<br>7.4 10<br>2.95<br>3.85<br>0.8 14<br>25.8 33<br>0.2<br>25.2<br>1.7 15 |       |  |  |

|                           | PD |                          | 2.437 OIVII 12 | Buffers on  | 7.4  | 10                                                                                                                                    | mW    |  |  |

| Power Dissipation         | 10 |                          | 1.024MHz       | Buffers off | 2.95 | 7.4 10<br>2.95<br>3.85                                                                                                                | 11100 |  |  |

|                           |    | 4X mode,<br>MF1 = 1,     | 1.024101112    | Buffers on  | 6.85 |                                                                                                                                       |       |  |  |

|                           |    | MF0 = 0                  | 2.4576MHz      | Buffers off | 10.8 | 14                                                                                                                                    |       |  |  |

|                           |    |                          | 2.437 OIVII 12 | Buffers on  | 25.8 | 33                                                                                                                                    |       |  |  |

|                           |    |                          | 1.024MHz       | Buffers off | 10.2 |                                                                                                                                       |       |  |  |

|                           |    | 8X mode,<br>MF1 = 1,     | 1.024111112    | Buffers on  | 25.2 |                                                                                                                                       |       |  |  |

|                           |    | MF0 = 1                  | 2.4576MHz      | Buffers off | 11.7 | 15                                                                                                                                    |       |  |  |

|                           |    |                          | 2.707 OIVII 12 | Buffers on  | 26.7 | 34                                                                                                                                    |       |  |  |

| Standby Power Dissipation |    | (Note 18)                | ·              |             | 10   | 100                                                                                                                                   | μW    |  |  |

- **Note 1:** Nominal gain is 0.98. This ensures a full-scale input voltage may be applied to the part under all conditions without causing saturation of the digital output data.

- **Note 2:** Positive Full-Scale Error includes zero-scale errors (unipolar offset error or bipolar zero error) and applies to both unipolar and bipolar input ranges. This error does not include the nominal gain of 0.98.

- Note 3: Full-Scale Drift includes zero-scale drift (unipolar offset drift or bipolar zero drift) and applies to both unipolar and bipolar input ranges.

- **Note 4:** Gain Error does not include zero-scale errors. It is calculated as (full-scale error unipolar offset error) for unipolar ranges and as (full-scale error bipolar zero error) for bipolar ranges. This error does not include the nominal gain of 0.98.

- **Note 5:** Gain-Error Drift does not include unipolar offset drift or bipolar zero drift. It is effectively the drift of the part if zero-scale error is removed.

- Note 6: Use of the offset DAC does not imply that any input may be taken below AGND.

- **Note 7:** Additional noise added by the offset DAC is dependent on the filter cutoff, gain, and DAC setting. No noise is added for a DAC code of 0000.

- Note 8: Guaranteed by design or characterization; not production tested.

- Note 9: The absolute input voltage must be within the input-voltage range specification.

- Note 10: All AIN and REFIN pins have identical input structures. Leakage is production tested only for the AIN3, AIN4, AIN5, CALGAIN and CALOFF inputs.

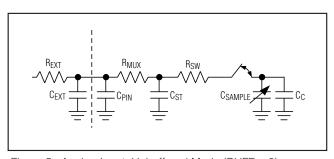

- **Note 11:** The dynamic load presented by the MAX1402 analog inputs for each gain setting is discussed in detail in the *Switching Network* Section. Values are provided for the maximum allowable external series resistance.

- **Note 12:** The input voltage range for the analog inputs is with respect to the voltage on the negative input of its respective differential or pseudo-differential pair. Table 5 shows which inputs form differential pairs.

- Note 13: VREF = VREFIN+ VREFIN-

- Note 14: These specifications apply to CLKOUT only when driving a single CMOS load.

- Note 15: The burn-out currents require a 500mV overhead between the analog input voltage and both V+ and AGND to operate correctly.

- **Note 16:** Measured at DC in the selected passband. PSR at 50Hz will exceed 120dB with filter notches of 25Hz or 50Hz and FAST bit = 0. PSR at 60Hz will exceed 120dB with filter notches of 20Hz or 60Hz and FAST bit = 0.

- Note 17: PSR depends on gain. For a gain of +1V/V, PSR is 70dB typical. For a gain of +2V/V, PSR is 75dB typical. For a gain of +4V/V, PSR is 80dB typical. For gains of +8V/V to +128V/V, PSR is 85dB typical.

- Note 18: Standby power-dissipation and current specifications are valid only with CLKIN driven by an external clock and with the external clock stopped. If the clock continues to run in standby mode, the power dissipation will be considerably higher.

#### TIMING CHARACTERISTICS

$(V+ = +5V \pm 5\%, V_{DD} = +2.7V \text{ to } +5.25V, \text{AGND} = \text{DGND}, f_{CLKIN} = 2.4576\text{MHz}; input logic 0 = 0V; logic 1 = V_{DD}, T_A = T_{MIN} \text{ to } T_{MAX}, unless \text{ otherwise noted.})$  (Notes 19, 20, 21)

| PARAMETER                                              | SYMBOL          | CONDITIONS                                              |                                                                        | MIN      | TYP | MAX | UNITS  |

|--------------------------------------------------------|-----------------|---------------------------------------------------------|------------------------------------------------------------------------|----------|-----|-----|--------|

| Master Clock Frequency                                 | form            | Crystal oscillator or clock exter-                      | X2CLK = 0                                                              | 0.4      |     | 2.5 | MHz    |

| Master Clock Frequency                                 | fCLKIN          | mance (Notes 22, 23)                                    | nally supplied for specified perfor-<br>mance (Notes 22, 23) X2CLK = 1 |          |     | 5.0 | IVIITZ |

| Master Clock Input Low Time                            | fCLKIN LO       | t <sub>CLKIN</sub> = 1 / f <sub>CLKIN</sub> , X2CLK = 0 |                                                                        | 0.4 •    |     |     | ns     |

| 1,                                                     | OLI III LO      | SERVIV 7 SERVIV 2                                       |                                                                        | tclkin   |     |     |        |

| Master Clock Input High Time                           | fCLKIN HI       | t <sub>CLKIN</sub> = 1 / f <sub>CLKIN</sub> , X2CLK = 0 |                                                                        | 0.4 •    |     |     | ns     |

|                                                        |                 |                                                         |                                                                        | tCLKIN   |     |     |        |

|                                                        |                 | $X2CLK = 0, N = 2^{(2 \cdot MF1 + MF0)}$                |                                                                        | 280 / N  |     |     |        |

| INT High Time                                          | tīNT            |                                                         |                                                                        | • tCLKIN |     |     | ns     |

|                                                        |                 | $X2CLK = 1, N = 2^{(2 \cdot MF1 + MF0)}$                |                                                                        | 560 / N  |     |     |        |

|                                                        |                 |                                                         |                                                                        | • tCLKIN |     |     |        |

| RESET Pulse Width Low                                  | t <sub>2</sub>  |                                                         |                                                                        | 100      |     |     | ns     |

| SERIAL-INTERFACE READ OPE                              | RATION          |                                                         |                                                                        |          |     |     |        |

| INT to CS Setup Time (Note 8)                          | t <sub>3</sub>  |                                                         |                                                                        | 0        |     |     | ns     |

| SCLK Setup to Falling Edge CS                          | t <sub>4</sub>  |                                                         |                                                                        | 30       |     |     | ns     |

| CS Falling Edge to SCLK Falling Edge Setup Time        | t <sub>5</sub>  |                                                         |                                                                        | 30       |     |     | ns     |

| SCLK Falling Edge to Data Valid                        | +-              | $V_{DD} = 5V$                                           |                                                                        | 0        |     | 80  | no     |

| Delay (Notes 24, 25)                                   | t <sub>6</sub>  | V <sub>DD</sub> = 3.3V                                  |                                                                        | 0        |     | 100 | ns     |

| SCLK High Pulse Width                                  | t <sub>7</sub>  |                                                         |                                                                        | 100      |     |     | ns     |

| SCLK Low Pulse Width                                   | t <sub>8</sub>  |                                                         |                                                                        | 100      |     |     | ns     |

| CS Rising Edge to SCLK Rising Edge Hold Time (Note 21) | t9              |                                                         |                                                                        | 0        |     |     | ns     |

| Bus Relinquish Time After SCLK                         | t <sub>10</sub> | $V_{DD} = 5V$                                           |                                                                        | 10       |     | 70  | ns     |

| Rising Edge (Note 26)                                  | 110             | $V_{DD} = 3.3V$                                         |                                                                        | 10       |     | 100 | 115    |

| SCLK Rising Edge to INT High                           | t <sub>11</sub> | $V_{DD} = 5V$                                           |                                                                        |          |     | 100 | ns     |

| (Note 27)                                              | 411             | $V_{DD} = 3.3V$                                         |                                                                        |          |     | 200 | 110    |

| SERIAL-INTERFACE WRITE OF                              | ERATION         |                                                         |                                                                        |          |     |     |        |

| SCLK Setup to Falling Edge CS                          | t <sub>12</sub> |                                                         |                                                                        | 30       |     |     | ns     |

#### TIMING CHARACTERISTICS (continued)

$(V+ = +5V \pm 5\%, V_{DD} = +2.7V \text{ to } +5.25V, \text{AGND} = \text{DGND}, f_{CLKIN} = 2.4576\text{MHz}; input logic 0 = 0V; logic 1 = V_{DD}, T_A = T_{MIN} \text{ to } T_{MAX}, unless \text{ otherwise noted.})$  (Notes 19, 20, 21)

| PARAMETER                                                  | SYMBOL          | CONDITIONS | MIN | TYP | MAX | UNITS |

|------------------------------------------------------------|-----------------|------------|-----|-----|-----|-------|

| CS Falling Edge to SCLK Falling Edge Setup Time            | t <sub>13</sub> |            | 30  |     |     | ns    |

| Data Valid to SCLK Rising Edge<br>Setup Time               | t <sub>14</sub> |            | 30  |     |     | ns    |

| Data Valid to SCLK Rising Edge<br>Hold Time                | t <sub>15</sub> |            | 0   |     |     | ns    |

| SCLK High Pulse Width                                      | t <sub>16</sub> |            | 100 |     |     | ns    |

| SCLK Low Pulse Width                                       | t <sub>17</sub> |            | 100 |     |     | ns    |

| CS Rising Edge to SCLK Rising Edge Hold Time               | t <sub>18</sub> |            | 0   |     |     | ns    |

| AUXILIARY DIGITAL INPUTS (D                                | S0 and DS       | 1)         |     |     |     |       |

| DS0/DS1 to SCLK Falling Edge<br>Setup Time (Notes 21 & 28) | t <sub>19</sub> |            | 40  |     |     | ns    |

| DS0/DS1 to SCLK Falling Edge<br>Hold Time (Notes 21 & 28)  | t <sub>20</sub> |            | 0   |     |     | ns    |

- **Note 19:** All input signals are specified with  $t_{\Gamma} = t_f = 5$ ns (10% to 90% of V<sub>DD</sub>) and timed from a voltage level of 1.6V.

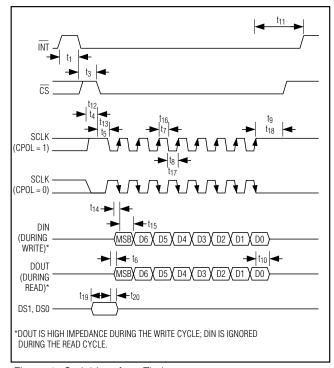

- Note 20: See Figure 4.

- Note 21: Timings shown in tables are for the case where SCLK idles high between accesses. The part may also be used with the SCLK idling low between accesses, provided  $\overline{\text{CS}}$  is toggled. In this case SCLK in the timing diagrams should be inverted and the terms "SCLK Falling Edge" and "SCLK Rising Edge" exchanged in the specification tables. If  $\overline{\text{CS}}$  is permanently tied low, the part should only be operated with SCLK idling high between accesses.

- **Note 22:** CLKIN duty cycle range is 45% to 55%. CLKIN must be supplied whenever the MAX1402 is not in standby mode. If no clock is present, the device can draw higher current than specified.

- Note 23: The MAX1402 is production tested with fCLKIN at 2.5MHz (1MHz for some Ipp tests).

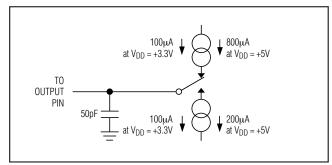

- Note 24: Measured with the load circuit of Figure 1 and defined as the time required for the output to cross the VoL or VoH limits.

- Note 25: For read operations, SCLK active edge is falling edge of SCLK.

- **Note 26:** Derived from the time taken by the data output to change 0.5V when loaded with the circuit of Figure 1. The number is then extrapolated back to remove effects of charging or discharging the 50pF capacitor. This ensures that the times quoted in the timing characteristics are true bus-relinquish times and are independent of external bus loading capacitances.

- Note 27: INT returns high after the first read after an output update. The same data can be read again while INT is high, but be careful not to allow subsequent reads to occur close to the next output update.

- Note 28: Auxiliary inputs DS0 and DS1 are latched on the first falling edge of SCLK during a data-read cycle.

Figure 1. Load Circuit for Bus-Relinquish Time and  $V_{OL}$  and  $V_{OH}$  Levels

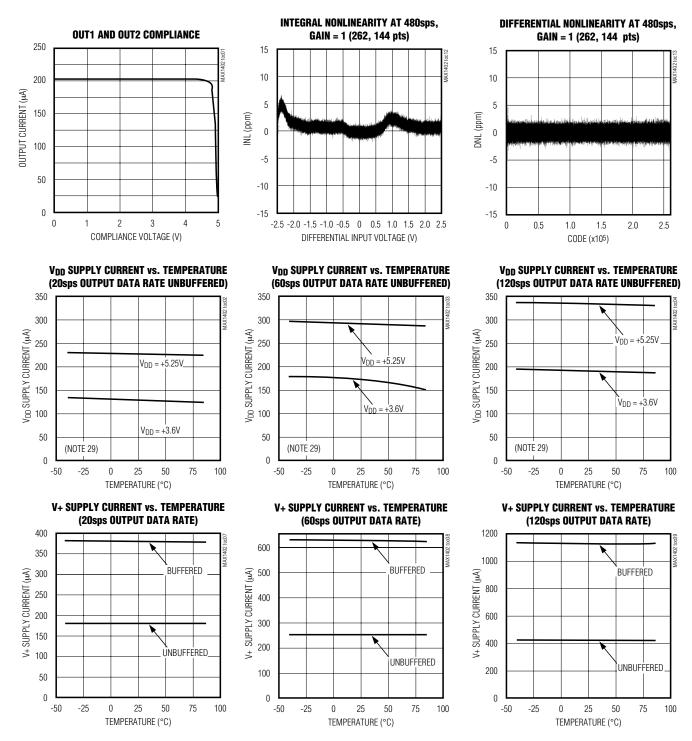

### **Typical Operating Characteristics**

(V+ = +5V, V<sub>DD</sub> = +5V, V<sub>REFIN+</sub> = +2.50V, REFIN- = AGND, f<sub>CLKIN</sub> = 2.4576MHz, T<sub>A</sub> = +25°C, unless otherwise noted.)

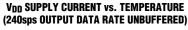

### Typical Operating Characteristics (continued)

$(V+ = +5V, V_{DD} = +5V, V_{REFIN+} = +2.50V, REFIN- = AGND, f_{CLKIN} = 2.4576MHz, T_A = +25^{\circ}C, unless otherwise noted.)$

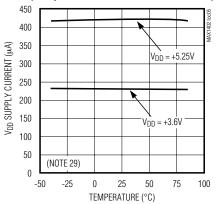

### V+ SUPPLY CURRENT vs. TEMPERATURE (240sps OUTPUT DATA RATE)

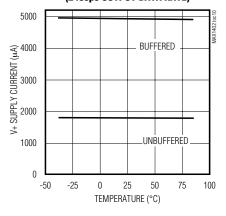

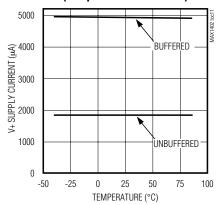

### V<sub>DD</sub> SUPPLY CURRENT vs. TEMPERATURE (480sps OUTPUT DATA RATE UNBUFFERED)

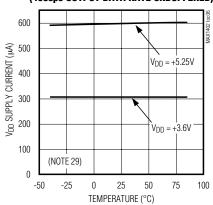

### V+ SUPPLY CURRENT vs. TEMPERATURE (480sps OUTPUT DATA RATE)

**Note 29:** Minimize capacitive loading at CLKOUT for lowest V<sub>DD</sub> supply current. *Typical Operating Characteristics* show V<sub>DD</sub> supply current with CLKOUT loaded by 120pF.

### Pin Description

| PIN | NAME   | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | CLKIN  | Clock Input. A crystal can be connected across CLKIN and CLKOUT. Alternatively, drive CLKIN with a CMOS-compatible clock at a nominal frequency of 2.4576MHz or 1.024MHz, and leave CLKOUT unconnected. Frequencies of 4.9152MHz and 2.048MHz may be used if the X2CLK control bit is set to 1.                                                                                                                                                |

| 2   | CLKOUT | Clock Output. When deriving the master clock from a crystal, connect the crystal between CLKIN and CLKOUT. In this mode, the on-chip clock signal is not available at CLKOUT. Leave CLKOUT unconnected when CLKIN is driven with an external clock.                                                                                                                                                                                            |

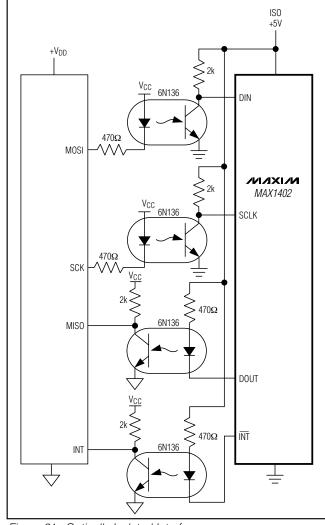

| 3   | CS     | Chip-Select Input. Active-low logic input used to enable the digital interface. With $\overline{\text{CS}}$ hard-wired low, the MAX1402 operates in its 3-wire interface mode with SCLK, DIN and DOUT used to interface to the device. $\overline{\text{CS}}$ is used either to select the device in systems with more than one device on the serial bus, or as a frame-synchronization signal for the MAX1402 when a continuous SCLK is used. |

| 4   | RESET  | Active-Low Reset Input. Drive low to reset the control logic, interface logic, digital filter and analog modulator to power-on status. RESET must be high and CLKIN must be toggling in order to exit reset.                                                                                                                                                                                                                                   |

| 5   | DS1    | Digital Input for Auxiliary Data Input Bit 1. The status of this bit is reflected in the output data by bit D4. Used to communicate the status of DS1 via the serial interface.                                                                                                                                                                                                                                                                |

| 6   | DS0    | Digital Input for Auxiliary Data Input Bit 0. The status of this bit is reflected in the output data by bit D3. Used to communicate the status of DS0 via the serial interface.                                                                                                                                                                                                                                                                |

| 7   | OUT2   | Transducer Excitation Current Source 2                                                                                                                                                                                                                                                                                                                                                                                                         |

| 8   | OUT1   | Transducer Excitation Current Source 1                                                                                                                                                                                                                                                                                                                                                                                                         |

| 9   | AGND   | Analog Ground. Reference point for the analog circuitry. AGND connects to the IC substrate.                                                                                                                                                                                                                                                                                                                                                    |

| 10  | V+     | Analog Positive Supply Voltage (+4.75V to +5.25V).                                                                                                                                                                                                                                                                                                                                                                                             |

| 11  | AIN1   | Analog Input Channel 1. May be used as a pseudo-differential input with AIN6 as common, or as the positive input of the AIN1/AIN2 differential analog input pair (see <i>Communications Register</i> section).                                                                                                                                                                                                                                 |

| 12  | AIN2   | Analog Input Channel 2. May be used as a pseudo-differential input with AIN6 as common, or as the negative input of the AIN1/AIN2 differential analog input pair (see <i>Communications Register</i> section).                                                                                                                                                                                                                                 |

| 13  | AIN3   | Analog Input Channel 3. May be used as a pseudo-differential input with AIN6 as common, or as the positive input of the AIN3/AIN4 differential analog input pair (see <i>Communications Register</i> section).                                                                                                                                                                                                                                 |

| 14  | AIN4   | Analog Input Channel 4. May be used as a pseudo-differential input with AIN6 as common, or as the negative input of the AIN3/AIN4 differential analog input pair (see <i>Communications Register</i> section).                                                                                                                                                                                                                                 |

| 15  | AIN5   | Analog Input Channel 5. Used as a differential or pseudo-differential input with AIN6 (see Communications Register section).                                                                                                                                                                                                                                                                                                                   |

| 16  | AIN6   | Analog Input 6. May be used as a common point for AIN1 through AIN5 in pseudo-differential mode, or as the negative input of the AIN5/AIN6 differential analog input pair (see <i>Communications Register</i> section).                                                                                                                                                                                                                        |

### Pin Description (continued)

| PIN | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17  | CALGAIN-        | Negative Gain Calibration Input. Used for system-gain calibration. It forms the negative input of a fully differential input pair with CALGAIN+. Normally these inputs are connected to reference voltages in the system. When system gain calibration is not required and the auto-sequence mode is used, the CALGAIN+/CALGAIN- input pair provides an additional fully differential input channel.                                                                                                  |

| 18  | CALGAIN+        | Positive Gain Calibration Input. Used for system gain calibration. It forms the positive input of a fully differential input pair with CALGAIN Normally these inputs are connected to reference voltages in the system. When system gain calibration is not required and the auto-sequence mode is used, the CALGAIN+/CALGAIN- input pair provides an additional fully differential input channel.                                                                                                    |

| 19  | REFIN-          | Negative Differential Reference Input. Bias REFIN- between V+ and AGND, provided that REFIN+ is more positive than REFIN                                                                                                                                                                                                                                                                                                                                                                              |

| 20  | REFIN+          | Positive Differential Reference Input. Bias REFIN+ between V+ and AGND, provided that REFIN+ is more positive than REFIN                                                                                                                                                                                                                                                                                                                                                                              |

| 21  | CALOFF-         | Negative Offset Calibration Input. Used for system offset calibration. It forms the negative input of a fully differential input pair with CALOFF+. Normally these inputs are connected to zero-reference voltages in the system. When system offset calibration is not required and the auto-sequence mode is used, the CALOFF+/CALOFF- input pair provides an additional fully differential input channel.                                                                                          |

| 22  | CALOFF+         | Positive Offset Calibration Input. Used for system offset calibration. It forms the positive input of a fully differential input pair with CALOFF Normally these inputs are connected to zero-reference voltages in the system. When system offset calibration is not required and the auto-sequence mode is used, the CALOFF+/CALOFF- input pair provides an additional fully differential input channel.                                                                                            |

| 23  | DGND            | Digital Ground. Reference point for digital circuitry.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 24  | V <sub>DD</sub> | Digital Supply Voltage (+2.7V to +5.25V)                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25  | ĪNT             | Interrupt Output. A logic low indicates that a new output word is available from the data register. INT returns high upon completion of a full output word read operation. INT also returns high for short periods (determined by the filter and clock control bits) if no data read has taken place. A logic high indicates internal activity, and a read operation should not be attempted under this condition. INT can also provide a strobe to indicate valid data at DOUT (MDOUT = 1).          |

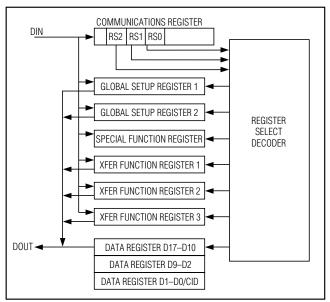

| 26  | DOUT            | Serial Data Output. DOUT outputs data from the internal shift register containing information from the Communications Register, Global Setup Registers, Transfer Function Registers, or Data Register. DOUT can also provide the digital bit stream directly from the $\Sigma$ - $\Delta$ modulator (MDOUT = 1).                                                                                                                                                                                      |

| 27  | DIN             | Serial Data Input. Data on DIN is written to the input shift register and later transferred to the Communications Register, Global Setup Registers, Special Function Register, or Transfer Function Registers, depending on the register selection bits in the Communications Register.                                                                                                                                                                                                               |

| 28  | SCLK            | Serial Clock Input. Apply an external serial clock to transfer data to and from the MAX1402. This serial clock can be continuous, with data transmitted in a train of pulses, or intermittent. If $\overline{CS}$ is used to frame the data transfer, then SCLK may idle high or low between conversions and $\overline{CS}$ determines the desired active clock edge (see <i>Selecting Clock Polarity</i> ). If $\overline{CS}$ is tied permanently low, SCLK must idle high between data transfers. |

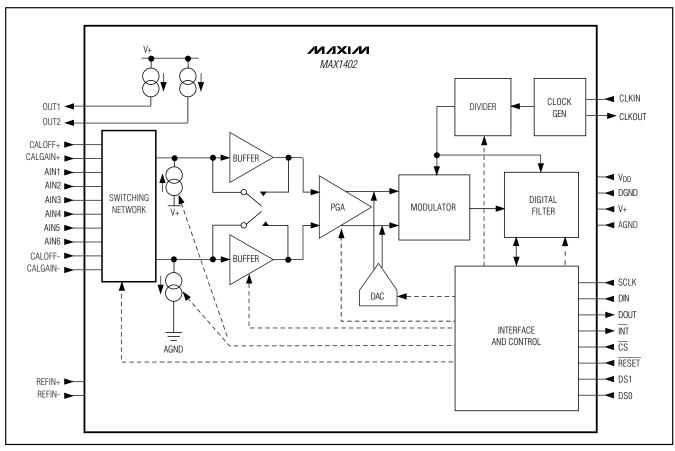

### **Detailed Description**

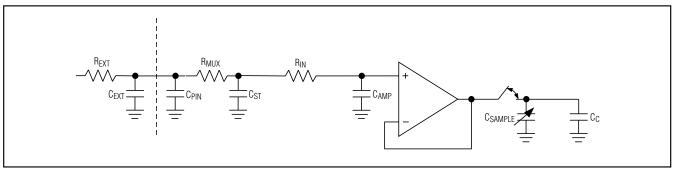

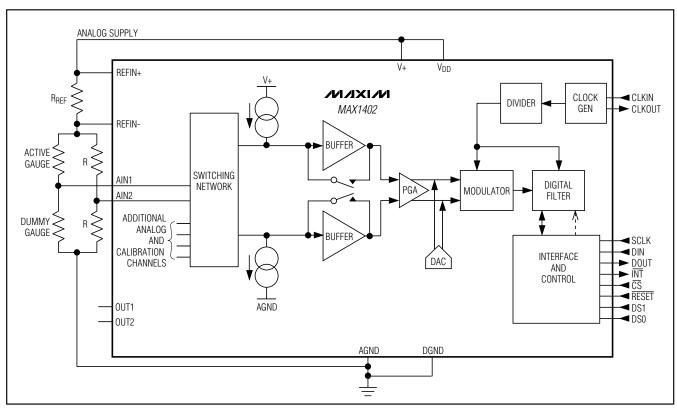

#### **Circuit Description**