# **Serial Digital Interface (SDI) MegaCore Function**

# **User Guide**

101 Innovation Drive San Jose, CA 95134 www.altera.com

UG-SDI1005-16.0

12.1 February 2013

© 2013 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

## **Contents**

| Chapter 1. About This MegaCore Function                     |      |

|-------------------------------------------------------------|------|

| Features                                                    |      |

| Release Information                                         |      |

| Device Family Support                                       |      |

| General Description                                         |      |

| OpenCore Plus Evaluation                                    |      |

| Resource Utilization                                        | 1–6  |

| Chapter 2. Getting Started                                  |      |

| Design Flow                                                 | 2–1  |

| SDI Walkthrough                                             | 2–3  |

| Creating a New Quartus II Project                           | 2–3  |

| Launching MegaWizard Plug-In Manager                        | 2–4  |

| Parameterizing                                              | 2–5  |

| Setting Up Simulation                                       |      |

| Generating Files                                            |      |

| Simulating the Design                                       |      |

| Testbench                                                   |      |

| Simulate with IP Functional Simulation Models               |      |

| Simulating with the ModelSim Simulator                      |      |

| Simulating in Third-Party Simulation Tools Using NativeLink |      |

| Specifying Constraints                                      |      |

| Single Channel                                              |      |

| Multiple Channels                                           |      |

| Compiling the Design                                        |      |

| Programming a Device                                        |      |

| Setting Up Licensing                                        | 2–15 |

| Chapter 3. Functional Description                           |      |

| Block Description                                           | 3–2  |

| Transmitter                                                 | 3–2  |

| HD-SDI LN Insertion                                         | 3–4  |

| HD-SDI CRC Generation and Insertion                         | 3–4  |

| Scrambling and NRZI Coding                                  | 3–5  |

| Transceiver Clock                                           |      |

| Receiver                                                    | 3–6  |

| NRZI Decoding and Descrambling                              |      |

| Word Alignment                                              |      |

| Video Timing Flags Extraction                               |      |

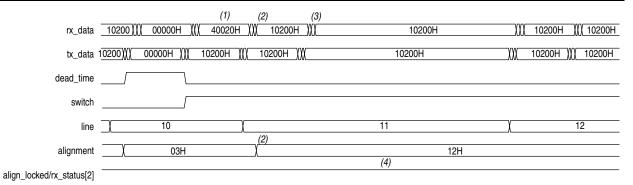

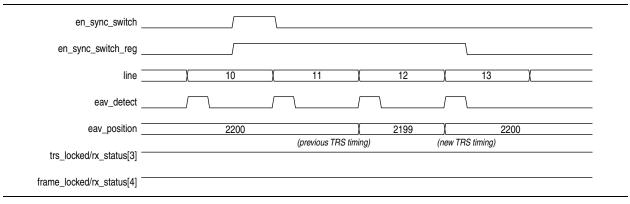

| RP168 Switching Compliance                                  | 3–9  |

| HD-SDI LN Extraction                                        | 3–10 |

| HD-SDI CRC Checking                                         | 3–10 |

| Accessing Transceiver                                       | 3–10 |

| Transceiver Clock                                           | 3–12 |

| Transceiver—Soft-Logic Implementation                       | 3–12 |

| Transmitter                                                 |      |

| Transmitter Clocks                                          |      |

| Receiver                                                    | 3_13 |

iv Contents

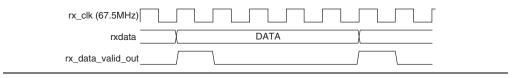

| Receiver Clocks                                                                                | 3–13   |

|------------------------------------------------------------------------------------------------|--------|

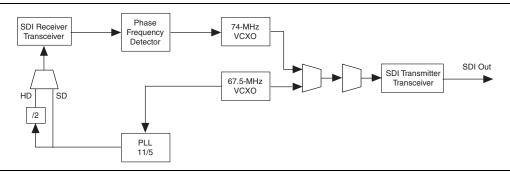

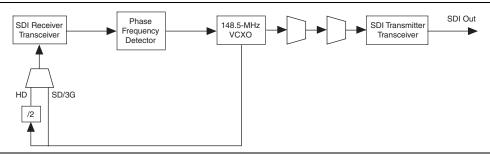

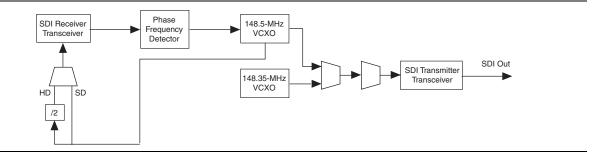

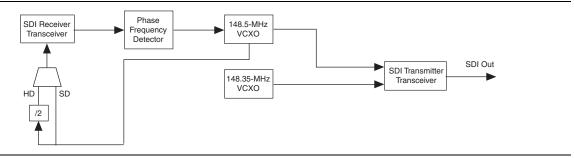

| Transceiver—Stratix GX Devices                                                                 | 3–13   |

| Transmitter Clocks                                                                             | 3–13   |

| Receiver Clocks                                                                                | 3–15   |

| Transmitter Transceiver Interface                                                              | 3–16   |

| Receiver Transceiver Interface                                                                 | 3–17   |

| Transceiver—Arria GX, Arria II GX, Arria V, Cyclone IV GX, Cyclone V, Stratix II GX, Stratix I | IV GX, |

| and Stratix V Devices                                                                          |        |

| Transmitter Clocks                                                                             | 3–19   |

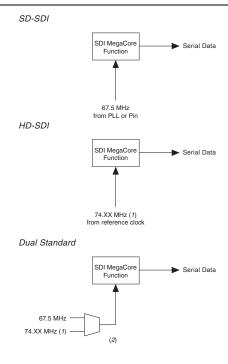

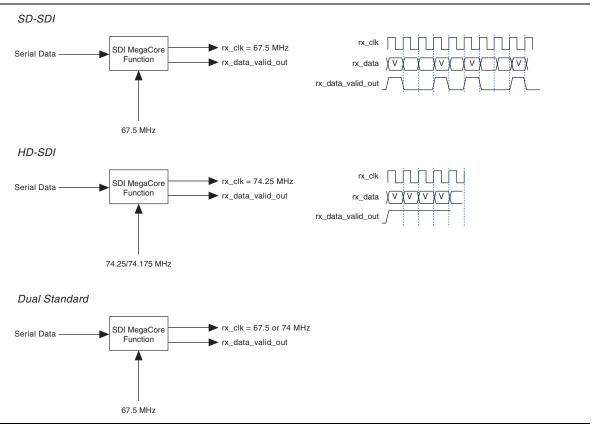

| Receiver Clocks                                                                                | 3–22   |

| Transmitter Transceiver Interface                                                              | 3–23   |

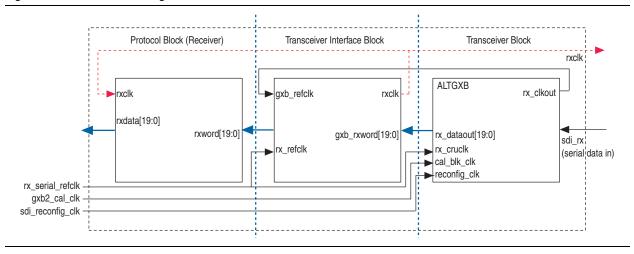

| Receiver Transceiver Interface                                                                 |        |

| Locking to the Incoming SDI Stream                                                             |        |

| Transceiver Dynamic Reconfiguration for Dual Standard and Triple Standard Receivers            |        |

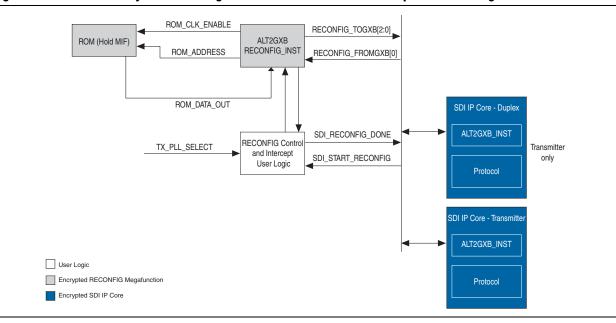

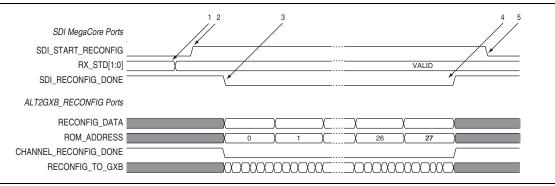

| Transceiver Dynamic Reconfiguration with Channel Reconfiguration Mode—Arria II GX,             |        |

| HardCopy IV GX, Stratix GX, Stratix II GX, and                                                 |        |

| Stratix IV GX                                                                                  | 3–27   |

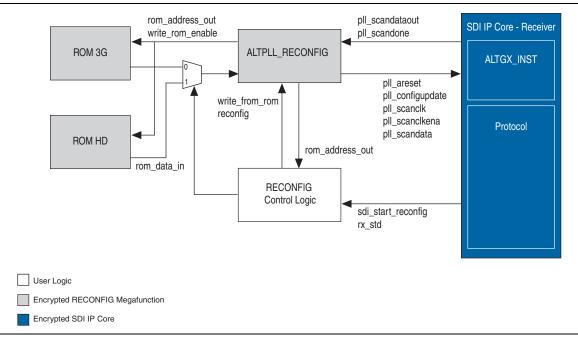

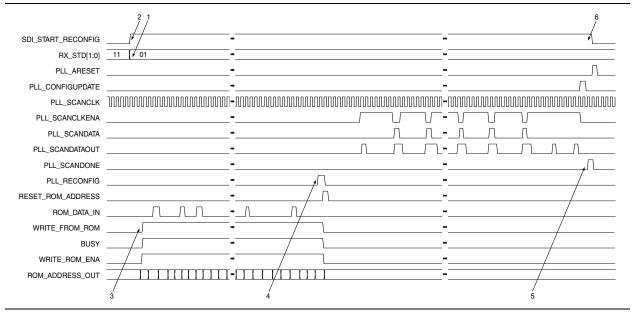

| Transceiver Dynamic Reconfiguration with PLL Reconfiguration Mode—Cyclone IV GX.               |        |

| Reset Requirement During Reconfiguration                                                       |        |

| OpenCore Plus Time-Out Behavior                                                                |        |

| Signals                                                                                        | 3–39   |

| Parameters                                                                                     |        |

| MegaCore Verification                                                                          |        |

| 1129.0010 (0111.011011 111111 111111 111111 111111 111111                                      |        |

| Chapter 4. SDI Audio IP Cores                                                                  |        |

| SDI Audio Embed MegaCore Function                                                              | 4_1    |

| Functional Description                                                                         | 4_2    |

| Parameters                                                                                     |        |

| Signals                                                                                        |        |

| Register Maps                                                                                  |        |

| SDI Audio Extract MegaCore Function                                                            |        |

| Functional Description                                                                         |        |

| Parameters                                                                                     |        |

| Signals                                                                                        |        |

| Register Maps                                                                                  |        |

| Clocked Audio Input MegaCore Function                                                          |        |

| Parameters                                                                                     |        |

| Signals                                                                                        |        |

| Register Maps                                                                                  | 4_18   |

| Clocked Audio Output MegaCore Function                                                         |        |

| Parameters                                                                                     |        |

| Signals                                                                                        |        |

| Register Maps                                                                                  |        |

| AES Format                                                                                     |        |

| Avalon-ST Audio Interface                                                                      |        |

| Instantiating the IP Cores                                                                     |        |

| Simulating the Testbench                                                                       |        |

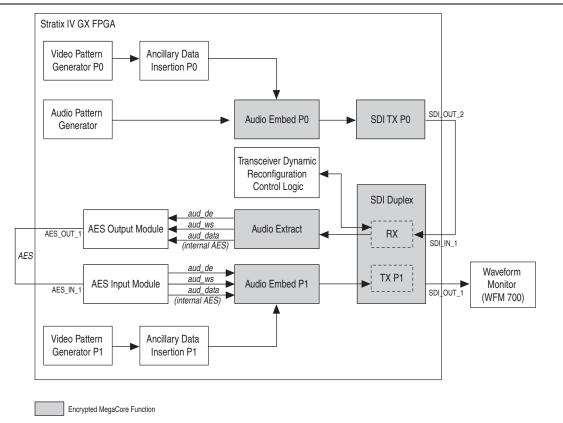

| Design Example                                                                                 |        |

| Components                                                                                     |        |

| SDI Transmitter P0                                                                             |        |

| SDI Duplex                                                                                     |        |

| Audio Extract                                                                                  |        |

| AES Output Module                                                                              |        |

| AES Output Module                                                                              |        |

| The hip at module                                                                              | 4/     |

**Contents**

| Audio Embed P0/P1                                                             |                      |

|-------------------------------------------------------------------------------|----------------------|

| Video Pattern Generator P0/P1                                                 | 4–27                 |

| Audio Pattern Generator                                                       | $\dots \dots 4-27$   |

| Ancillary Data Insertion P0/P1                                                | 4–27                 |

| Transceiver Dynamic Reconfiguration Control Logic                             | 4–27                 |

| Hardware and Software Requirements                                            | $\dots \dots 4 – 28$ |

| Hardware Setup                                                                | 4–28                 |

| Running the Design Example                                                    | 4–30                 |

| Transmit SD-SDI with Embedding of Audio Group 1                               | 4–30                 |

| Transmit HD-SDI with Embedding of Audio Group 1 and 2                         | 4–31                 |

| Transmit 3G-SDI Level A with Embedding of Audio Group 1, 2 and 3              |                      |

| Transmit 3G-SDI Level B with Embedding of Audio Group 1, 2, 3 and 4           |                      |

|                                                                               |                      |

| Appendix A. Constraints                                                       |                      |

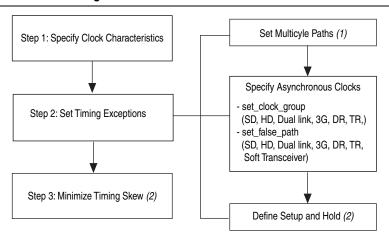

| Specifying TimeQuest Timing Analyzer Constraints                              | A-1                  |

| Specify Clock Characteristics                                                 | A-4                  |

| Set Multicycle Paths                                                          |                      |

| Specify Clocks that are Exclusive or Asynchronous                             |                      |

| Define the Setup and Hold Relationship between 135-MHz Clocks and 337.5-MHz Z |                      |

| Clocks                                                                        |                      |

| Minimize Timing Skew                                                          |                      |

| Constraints for the SDI Soft Transceiver                                      | A-7                  |

| Non Cyclone Devices                                                           | A-8                  |

| Classic Timing Analyzer                                                       |                      |

| TimeQuest Timing Analyzer                                                     | A-8                  |

| Cyclone Devices Only                                                          | A-9                  |

| Classic Timing Analyzer                                                       | A-9                  |

| TimeQuest Timing Analyzer                                                     | A-9                  |

| Appendix B. Clocking                                                          |                      |

| Appendix B. Glocking                                                          |                      |

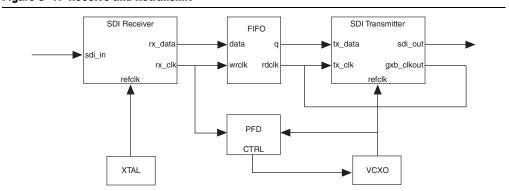

| Appendix C. Receive and Retransmit                                            |                      |

| Loopback FIFO Buffer                                                          | C-1                  |

| 200ponen 1 0 2 miles 111111111111111111111111111111111111                     |                      |

| Additional Information                                                        |                      |

| Document Revision History                                                     | Info-1               |

| How to Contact Altera                                                         | Info-3               |

| Typographic Conventions                                                       | Info-3               |

vi Contents

## 1. About This MegaCore Function

This user guide describes the Altera® Serial Digital Interface (SDI) MegaCore® function and the accompanying SDI Audio IP cores.

The SDI MegaCore function implements a receiver, transmitter, or full-duplex SDI at standard definition (SD), high definition (HD), or 3 gigabits per second (3G). The SDI MegaCore function also supports dual standard (HD-SDI and SD-SDI) and triple standard (SD-SDI, HD-SDI, and 3G-SDI). These modes provide automatic receiver rate detection.

You can instantiate the SDI Audio IP cores with the SDI MegaCore function.

For more information about the SDI Audio cores, refer to "SDI Audio IP Cores" on page 4–1.

### **Features**

Table 1–1 lists the features of the SDI MegaCore function.

Table 1-1. SDI MegaCore Function Features

| Feature                         | Description                                                                   |  |  |

|---------------------------------|-------------------------------------------------------------------------------|--|--|

|                                 | ■ Multiple SDI standards and video formats (refer to Table 1–5 and Table 1–6) |  |  |

| Support                         | <ul> <li>RP168 video switch line requirement</li> </ul>                       |  |  |

|                                 | OpenCore Plus evaluation                                                      |  |  |

|                                 | Cyclical redundancy check (CRC) encoding (HD only)                            |  |  |

| Transmitter                     | <ul><li>Line number (LN) insertion (HD only)</li></ul>                        |  |  |

| Transmitter                     | <ul><li>Word scrambling</li></ul>                                             |  |  |

|                                 | ■ Transmitter clock multiplexer (optional)                                    |  |  |

|                                 | CRC decoding (HD only)                                                        |  |  |

| Danaiyar                        | <ul><li>LN extraction (HD only)</li></ul>                                     |  |  |

| Receiver                        | Framing and extraction of video timing signals                                |  |  |

|                                 | <ul> <li>Word alignment and descrambling</li> </ul>                           |  |  |

| MegaWizard™ Plug-In Manager     | Easy-to-use parameter editor                                                  |  |  |

| IP functional simulation models | <ul> <li>Use in Altera-supported VHDL and Verilog HDL simulators</li> </ul>   |  |  |

### **Release Information**

Table 1–2 lists information about this release of the SDI MegaCore function.

Table 1-2. Release Information

| Item          | Description                  |

|---------------|------------------------------|

| Version       | 12.1                         |

| Release Date  | January 2013                 |

| Ordering Code | IP-SDI                       |

| Product ID(s) | 00AE (SDI MegaCore function) |

|               | 00EF (SDI Audio cores)       |

| Vendor ID     | 6AF7                         |

For more information about this release, refer to the MegaCore IP Library Release Notes and Errata.

Altera verifies that the current version of the Quartus® II software compiles the previous version of each MegaCore function. The MegaCore IP Library Release Notes and Errata report any exceptions to this verification. Altera does not verify compilation with MegaCore function versions older than one release.

## **Device Family Support**

Table 1–3 defines the device support levels for Altera IP cores.

Table 1–3. Altera IP Core Device Support Levels

| FPGA Device Families                                                                                                                                                                                                                                                      | HardCopy Device Families                                                                                                                                                                                                                                                                     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Preliminary support—The IP core is verified with preliminary timing models for this device family. The IP core meets all functional requirements, but might still be undergoing timing analysis for the device family. It can be used in production designs with caution. | HardCopy Companion—The IP core is verified with preliminary timing models for the HardCopy companion device. The IP core meets all functional requirements, but might still be undergoing timing analysis for the HardCopy device family. It can be used in production designs with caution. |

| Final support—The IP core is verified with final timing models for this device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                              | HardCopy Compilation—The IP core is verified with final timing models for the HardCopy device family. The IP core meets all functional and timing requirements for the device family and can be used in production designs.                                                                  |

Table 1-4 shows the level of support offered by the SDI MegaCore function for each Altera device family.

Table 1-4. Device Family Support (Part 1 of 2)

| Device Family | Support                                                          |  |

|---------------|------------------------------------------------------------------|--|

| Arria® GX     | Final                                                            |  |

| Arria II (1)  | Final                                                            |  |

| Arria V       | Refer to the What's New in Altera IP page of the Altera website. |  |

**Device Family Support** Cyclone® Final (3) Cyclone II (2) Final Cyclone III (2) Final Cyclone III LS (2) Final Cyclone IV GX (4) Final Refer to the What's New in Altera IP page of Cyclone V (5) the Altera website. HardCopy® III/ IV E HardCopy Compilation HardCopy IV GX HardCopy Compilation Stratix® (2) Final Stratix GX Final Stratix II (2) Final Stratix II GX Final Stratix III (2) Final Stratix IV (1) Final Refer to the What's New in Altera IP page of Stratix V (1) the Altera website. Other device families No support

Table 1-4. Device Family Support (Part 2 of 2)

#### Notes to Table 1-4:

- (1) If you have only 27 MHz to drive the SDI MegaCore function in SD-SDI mode, you require an additional PLL to generate a 67.5-MHz reference clock.

- (2) The Cyclone series of devices, and Stratix, Stratix II, and Stratix III devices only support soft serializer /deserializer (SERDES).

- (3) Cyclone device support is limited to -6 speed grade devices.

- (4) Transceiver dynamic configuration with channel reconfiguration mode is not supported for dual and triple standard in EP4CGX110 and EP4CGX150 devices. Use transceiver dynamic reconfiguration with PLL reconfiguration mode instead.

- (5) The Cyclone V devices does not support the SDI Audio IP cores.

## **General Description**

The Society of Motion Picture and Television Engineers (SMPTE) have defined an SDI that video system designers use widely as an interconnect between equipment in video production facilities.

The SDI MegaCore function can handle the following SDI data rates:

- 270 megabits per second (Mbps) SD-SDI, as defined by *SMPTE259M-1997 10-Bit* 4:2:2 Component Serial Digital Interface

- 1.5-Gbps HD-SDI, as defined by *SMPTE292M-1998 Bit-Serial Digital Interface for High Definition Television Systems*

- 3-Gbps SDI, as defined by *SMPTE425M-AB 2006 3Gb/s Signal/Data Serial Interface—Source Image Format Mapping*

- Preliminary support for dual link SDI, as defined by *SMPTE372M-Dual Link* 1.5*Gb/s Digital Interface for* 1920×1080 *and* 2048×1080 *Picture Formats*

- Dual standard support for 270-Mbps and 1.5-Gbps SDI

- Triple standard support for 270-Mbps, 1.5-Gbps, and 3-Gbps SDI

- SMPTE425M Level A support (direct source image formatting)

- *SMPTE425M* Level B support (dual link mapping)

Table 1–5 lists the SDI standard support for various devices.

Table 1–5. SDI Standard Support (1)

|                                                                                          | SDI Standard |          |        |                      |               |                 |  |

|------------------------------------------------------------------------------------------|--------------|----------|--------|----------------------|---------------|-----------------|--|

| Device Family                                                                            | SD-SDI       | HD-SDI   | 3G-SDI | HD-SDI Dual Link (2) | Dual Standard | Triple Standard |  |

| Arria GX                                                                                 | ✓            | <b>✓</b> | ✓      | <b>✓</b>             | <b>✓</b>      | ✓               |  |

| Arria II GX                                                                              | ✓            | ✓        | ✓      | ✓                    | ✓             | ✓               |  |

| Arria V                                                                                  | ✓            | <b>✓</b> | ✓      | ✓                    | ✓             | ✓               |  |

| Cyclone                                                                                  | ✓            | _        | _      | _                    | _             | _               |  |

| Cyclone II                                                                               | ✓            | _        | _      | _                    | _             | _               |  |

| Cyclone III                                                                              | ✓            | _        | _      | _                    | _             | _               |  |

| Cyclone IV GX<br>(EP4CGX15,<br>EP4CGX30)                                                 | <b>✓</b>     | _        | _      | _                    | _             | _               |  |

| Cyclone IV GX<br>(EP4CGX30 (F484),<br>EP4CGX50,<br>EP4CGX75,<br>EP4CGX110,<br>EP4CGX150) | ✓            | ~        | ✓      | ~                    | ~             | ~               |  |

| Cyclone V (3)                                                                            | ✓            | ✓        | ✓      | ✓                    | ✓             | ✓               |  |

| HardCopy IV GX                                                                           | ✓            | <b>✓</b> | ✓      | ✓                    | ✓             | ✓               |  |

| Stratix                                                                                  | ✓            | _        | _      | _                    | _             | _               |  |

| Stratix GX                                                                               | ✓            | ✓        | _      | ✓                    | ✓             | _               |  |

| Stratix II                                                                               | ✓            | _        | _      | _                    | _             | _               |  |

| Stratix II GX                                                                            | ✓            | ✓        | ✓      | ✓                    | ✓             | ✓               |  |

| Stratix III                                                                              | <b>✓</b>     | _        | _      | _                    | _             | _               |  |

| Stratix IV (4)                                                                           | ✓            | ✓        | ✓      | ✓                    | ✓             | ✓               |  |

| Stratix V (4)                                                                            | ✓            | ✓        | ✓      | ✓                    | ✓             | ✓               |  |

#### Notes to Table 1-5:

- (1) All standards, other than SD-SDI, require a transceiver based or "GX" device.

- (2) The HD-SDI dual link supports timing difference up to 40 ns between link A and link B, fulfilling the SMPTE372M requirement.

- (3) The 3G-SDI standard is not supported in Cyclone V devices with transceiver speed grade 7, due to the excessive data rate required. For more information about the Cyclone V device, refer to the Overview for Cyclone V Device Family chapter in volume 1 of the Cyclone V Device Handbook.

- (4) Only Stratix IV and Stratix V variants with transceivers support all SDI rates.

Table 1–6 lists the HD-SDI standard video format specification.

Table 1–6. HD-SDI Video Format Specification (1) (2)

| SMPTE292M | Video Format | Sample per<br>Active Line | Active Line<br>per Frame | Sample per<br>Total Line | Total Line<br>per Frame | Frame Rate | SDI 11.1<br>Support |

|-----------|--------------|---------------------------|--------------------------|--------------------------|-------------------------|------------|---------------------|

|           |              |                           |                          | 2200                     | 1125                    | 60         | Yes                 |

|           |              |                           |                          | 2640                     | 1125                    | 50         | Yes                 |

| 274M      | 1920 x 1080  | 1920                      | 1080                     | 2200                     | 1125                    | 30         | Yes                 |

|           |              |                           |                          | 2640                     | 1125                    | 25         | Yes                 |

|           |              |                           |                          | 2750                     | 1125                    | 24         | Yes                 |

|           | 1280 x 720   | 1280                      |                          | 1650                     | 750                     | 60         | Yes                 |

|           |              |                           |                          | 1980                     | 750                     | 50         | Yes                 |

| 296M      |              |                           | 720                      | 3300                     | 750                     | 30         | Yes                 |

|           |              |                           |                          | 3960                     | 750                     | 25         | Yes                 |

|           |              |                           |                          | 4125                     | 750                     | 24         | Yes                 |

| 260M      | 1920 x 1035  | 1920                      | 1035                     | 2200                     | 1125                    | 30         | Yes                 |

| 2051/     | 1920 x 1080  | 1920                      | 1000                     | 2376                     | 1250                    | 25         | Yes                 |

| 295M      | 1920 X 1060  | 1920                      | 1080                     | 2376                     | 1250                    | 50         | Yes                 |

#### Notes to Table 1-6:

### **OpenCore Plus Evaluation**

With Altera's free OpenCore Plus evaluation feature, you can perform the following actions:

- Simulate the behavior of a megafunction (Altera MegaCore function or AMPP<sup>SM</sup> megafunction) within your system.

- Verify the functionality of your design and quickly evaluate its size and speed with ease.

- Generate time-limited device programming files for designs that include MegaCore functions.

- Program a device and verify your design in hardware.

You are required to obtain a license for the MegaCore function only when you are completely satisfied with its functionality and performance, and want to take your design to production.

For more information about OpenCore Plus hardware evaluation using the SDI, refer to "OpenCore Plus Time-Out Behavior" on page 3–39 and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

<sup>(1)</sup> The video formats support  $4:2:2(YC'_BC'_R)/10$ -bit,  $4:4:4(RGB)/(YC'_BC'_R)$ ,  $4:4:4:4(RGB+A)/(YC'_BC'_R+A)/10$ -bit,  $4:4:4(YC'_BC'_R)/12$ -bit, 4:4:4(RGB)/12-bit, and  $4:2:2(YC'_BC'_R)/12$ -bit mapping structures.

<sup>(2) 3</sup>G-SDI is similar to HD-SDI except the data bit rate is twice that of HD-SDI or approximately 3 Gbps.

### **Resource Utilization**

Table 1–7 lists the typical resource utilization for various parameters with the Quartus II software, version 11.1.

The resource utilization of the MegaCore function is based on the bidirectional interface settings unless otherwise specified.

Table 1-7. Resource Utilization (Part 1 of 2)

| Device                                   | Video Standard            | LEs | Combinational ALUTs | Logic Registers |

|------------------------------------------|---------------------------|-----|---------------------|-----------------|

|                                          | SD-SDI                    | _   | 834                 | 640             |

|                                          | HD-SDI                    |     | 919                 | 683             |

|                                          | 3G-SDI                    | _   | 1,161               | 865             |

| Arria GX                                 | Dual link HD-SDI          | _   | 1,906               | 1,423           |

|                                          | Dual standard receiver    | _   | 1,188               | 831             |

|                                          | Dual standard transmitter | _   | 247                 | 185             |

|                                          | Triple standard           | _   | 1,794               | 1,215           |

|                                          | SD-SDI                    | _   | 839                 | 680             |

|                                          | HD-SDI                    | _   | 978                 | 833             |

|                                          | 3G HD-SDI                 | _   | 1,259               | 1,015           |

| Arria II GX                              | Dual-Link HD-SDI          | _   | 2,029               | 1,711           |

|                                          | Dual standard receiver    | _   | 1,257               | 926             |

|                                          | Dual standard transmitter | _   | 267                 | 180             |

|                                          | Triple standard           | _   | 1,891               | 1,305           |

|                                          | SD-SDI                    | _   | 1,189               | 920             |

|                                          | HD-SDI                    | _   | 1,185               | 910             |

|                                          | 3G-SDI                    | _   | 1,444               | 1,142           |

| Arria V                                  | Dual link HD-SDI          | _   | 2,446               | 1,880           |

|                                          | Dual standard receiver    | _   | 1,605               | 1,175           |

|                                          | Dual standard transmitter | _   | 349                 | 269             |

|                                          | Triple standard           | _   | 2,273               | 1,677           |

| Cyclone                                  | SD-SDI                    | 875 | _                   | _               |

| Cyclone II                               | SD-SDI                    | 867 | _                   | _               |

| Cyclone III                              | SD-SDI                    | 874 | _                   | _               |

| Cyclone III LS                           | SD-SDI                    | 929 | _                   | _               |

| Cyclone IV GX<br>(EP4CGX15,<br>EP4CGX30) | SD-SDI                    | 916 | _                   | _               |

Table 1-7. Resource Utilization (Part 2 of 2)

| Device                   | Video Standard            | LEs   | Combinational ALUTs | Logic Registers |

|--------------------------|---------------------------|-------|---------------------|-----------------|

|                          | SD-SDI                    |       | 1,129               | 671             |

| 0 1 11/01/               | HD-SDI                    | _     | 1,164               | 670             |

| Cyclone IV GX (EP4CGX50, | 3G-SDI                    | _     | 1,409               | 790             |

| EP4CGX75,                | Dual link HD-SDI          | _     | 2,515               | 1,467           |

| EP4CGX110, and           | Dual standard receiver    | _     | 1,479               | 755             |

| EP4CGX150)               | Dual standard transmitter | _     | 364                 | 229             |

|                          | Triple standard           | _     | 2,235               | 1,121           |

|                          | SD-SDI                    | _     | 1,140               | 832             |

|                          | HD-SDI                    | _     | 1,122               | 808             |

|                          | 3G-SDI                    | _     | 1,402               | 997             |

| Cyclone V                | Dual link HD-SDI          | _     | 2,351               | 1,696           |

|                          | Dual standard receiver    | _     | 1,539               | 1,042           |

|                          | Dual standard transmitter |       | 352                 | 260             |

|                          | Triple standard           | _     | 2,217               | 1,508           |

| Stratix                  | SD-SDI                    | 875   | _                   | _               |

| Stratix II               | SD-SDI                    | _     | 581                 | 533             |

| Stratix III              | SD-SDI                    | _     | 602                 | 565             |

|                          | SD-SDI                    | 1,182 | _                   | _               |

|                          | HD-SDI                    | 1,316 | _                   | _               |

| Stratix GX               | Dual link HD-SDI          | 2,703 | _                   | _               |

|                          | Dual standard             | 1,819 | _                   | _               |

|                          | SD-SDI                    | _     | 834                 | 640             |

|                          | HD-SDI                    | _     | 919                 | 683             |

|                          | 3G-SDI                    | _     | 1,161               | 865             |

| Stratix II GX            | Dual link HD-SDI          | _     | 1,906               | 1,423           |

|                          | Dual standard receiver    | _     | 1,188               | 831             |

|                          | Dual standard transmitter | _     | 247                 | 185             |

|                          | Triple standard           | _     | 1,794               | 1,215           |

|                          | SD-SDI                    | _     | 839                 | 680             |

|                          | HD-SDI                    | _     | 978                 | 833             |

|                          | 3G-SDI                    | _     | 1,259               | 1,015           |

| Stratix IV GX            | Dual link HD-SDI          | _     | 2,029               | 1,711           |

|                          | Dual standard receiver    | _     | 1,257               | 926             |

|                          | Dual standard transmitter | _     | 267                 | 180             |

|                          | Triple standard           | _     | 1,891               | 1,305           |

|                          | SD-SDI                    | _     | 913                 | 707             |

|                          | HD-SDI                    | _     | 955                 | 703             |

| Stratix V                | 3G-SDI                    | _     | 1,126               | 823             |

|                          | Dual link HD-SDI          | _     | 2,049               | 1,522           |

## 2. Getting Started

### **Design Flow**

To evaluate the SDI MegaCore function using the OpenCore Plus feature, follow these steps in your design flow:

1. Obtain and install the SDI MegaCore function.

The SDI MegaCore function is part of the MegaCore IP Library, which is distributed with the Quartus II software and downloadable from the Altera website at www.altera.com.

For system requirements and installation instructions, refer to *Altera Software Installation & Licensing*.

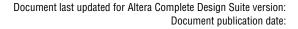

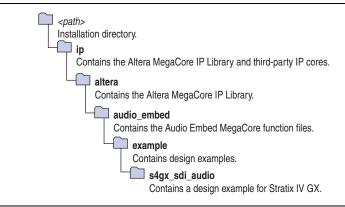

Figure 2–1 shows the directory structure after you install the SDI MegaCore function, where *<path>* is the installation directory. The default installation directory on Windows is **c:\altera**\*<version>*; on Linux, it is */opt/altera*<*version>*.

2-2 Chapter 2: Getting Started

Design Flow

Figure 2-1. Directory Structure

- 1. Create a custom variation of the SDI MegaCore function.

- 2. Implement the rest of your design using the design entry method of your choice.

- 3. Use the IP functional simulation model to verify the operation of your design.

- For more information on IP functional simulation models, refer to the *Simulating Altera Designs* chapter in volume 3 of the *Quartus II Handbook*.

4. Use the Quartus II software to compile your design.

You can also generate an OpenCore Plus time-limited programming file, which you can use to verify the operation of your design in hardware.

5. Purchase a license for the SDI MegaCore function.

After you have purchased a license for the SDI MegaCore function, follow these additional steps:

- 1. Set up licensing.

- 2. Generate a programming file for the Altera device or devices on your board.

- 3. Program the Altera device or devices with the completed design.

### **SDI Walkthrough**

This walkthrough explains how to create an SDI design using the MegaWizard Plug-In Manager and the Quartus II software. After you generate a custom variation of the SDI MegaCore function, you can incorporate it into your overall project.

You can alternatively use the IP Advisor to help start your SDI MegaCore design. On the Quartus II Tools menu, point to **Advisors**, and then click **IP Advisor**. The IP Advisor guides you through a series of recommendations for selecting, parameterizing, evaluating, and instantiating an SDI MegaCore function into your design. It then guides you through a complete Quartus II compilation of your project.

This walkthrough requires the following steps:

- 1. "Creating a New Quartus II Project"

- 2. "Launching MegaWizard Plug-In Manager"

- 3. "Parameterizing"

- 4. "Setting Up Simulation"

- 5. "Generating Files"

### **Creating a New Quartus II Project**

You must create a new Quartus II project with the **New Project Wizard**, which specifies the working directory for the project, assigns the project name, and designates the name of the top-level design entity. To create a new project, follow these steps:

- 1. Choose **Programs > Altera > Quartus II** <*version*> (Windows Start menu) to run the Quartus II software. Alternatively, you can use the Quartus II Web Edition software.

- 2. On the File menu, click **New Project Wizard**.

- 3. Click **Next** in the **New Project Wizard: Introduction** page (the introduction page does not display if you turned it off previously).

- 4. In the **New Project Wizard: Directory, Name, Top-Level Entity** page, enter the following information:

- a. Specify the working directory for your project. For example, this walkthrough uses the **c:\altera\projects\sdi\_project** directory.

The Quartus II software automatically specifies a top-level design entity that has the same name as the project. This walkthrough assumes that the names are the same.

- b. Specify the name of the project. This walkthrough uses **project** for the project name.

- 5. Click Next to close this page and display the New Project Wizard: Add Files page.

When you specify a directory that does not already exist, a message prompts you to create a specified directory. Click **Yes** to create the directory.

- 6. If you installed the MegaCore IP Library in a different directory from where you installed the Quartus II software, you must add the user libraries:

- a. Click User Libraries.

- b. Type <*path*>\ip into the **Library name** field, where <*path*> is the directory in which you installed the SDI.

- c. Click **Add to** add the path to the Quartus II project.

- d. Click **OK** to save the library path in the project.

- 7. Click **Next** to close this page and display the **New Project Wizard: Family & Device Settings** page.

- 8. On the **New Project Wizard: Family & Device Settings** page, choose the target device family in the **Family** list.

- 9. The remaining pages in the **New Project Wizard** are optional. Click **Finish** to complete the Quartus II project.

### Launching MegaWizard Plug-In Manager

To launch the MegaWizard Plug-In Manager in the Quartus II software, follow these steps:

1. On the Tools menu, click MegaWizard Plug-In Manager.

For more information about how to use the MegaWizard Plug-In Manager, refer to Quartus II Help.

- 2. Specify that you want to create a new custom megafunction variation and click **Next**.

- 3. Expand the **Interfaces > SDI** folder and click **SDI** <*version*>.

- 4. Select the output file type for your design; the wizard supports VHDL and Verilog HDL.

- 5. The MegaWizard Plug-In Manager shows the project path that you specified in the **New Project Wizard**. Append a variation name for the MegaCore function output files *<project path>\<variation name>*.

- 6. Click **Next** to display the **Parameter Settings** page for the SDI MegaCore function.

You can change the page that the MegaWizard Plug-In Manager displays by clicking **Next** or **Back** at the bottom of the dialog box. You can move directly to a named page by clicking the **Parameter Settings**, **EDA**, or **Summary** tab.

Also, you can directly display individual parameter settings by clicking on the **Protocol Options**, **Transceiver Options**, or **Receiver/Transmitter Options** tab.

#### **Parameterizing**

To parameterize your MegaCore function, follow these steps:

- 1. Select the video standard. Some of the standards may be grayed out, because they are not supported on the currently selected device family.

- 2. Select **Bidirectional**, **Receiver**, or **Transmitter** interface direction.

- 3. Click the **Transceiver Options** tab.

- 4. Under Transceiver and Protocol, click Generate transceiver and protocol blocks.

- 5. For SD-SDI only, turn on **Use soft logic for transceiver** to implement the transceiver in logic, rather than using Stratix GX, Stratix II GX or Stratix IV GX transceivers.

- 6. Select the starting channel number.

- 7. Turn on **Use PLL reconfiguration for transceiver dynamic reconfiguration** if you select an EP4CGX110 or EP4CGX150 device for Cyclone IV GX using dual and triple standards. You may turn on this option for other Cyclone IV GX devices but it is not recommended.

- 8. Turn on **Enable TX PLL select for 1/1.000 and 1/1.001 data rate reconfiguration** if your design requires two serial input clocks to the TX block.

This feature is only available for the Arria II, Stratix IV GX, and HardCopy IV GX device families.

- 9. Click the **Receiver/Transmitter Options** tab.

- 10. Turn on the required receiver options.

- 11. Turn on the required transmitter options.

- 12. Click **Next** (or the **EDA** tab) to display the **EDA** page.

For more information about parameters, refer to "Parameters" on page 3–56 and, for more information about the protocol options, refer to Table 3–20 on page 3–56. For more information about the transceiver options, refer to Table 3–21 on page 3–56. For more information about the receiver/transmitter options, refer to Table 3–22 on page 3–57.

#### **Setting Up Simulation**

An IP functional simulation model is a cycle-accurate VHDL or Verilog HDL model produced by the Quartus II software. The model allows for fast functional simulation of IP using industry-standard VHDL and Verilog HDL simulators.

You may only use these models for simulation and expressly not for synthesis or any other purposes. Using these models for synthesis creates a nonfunctional design.

To generate an IP functional simulation model for your MegaCore function, follow these steps:

- 1. Turn on Generate simulation model.

- 2. Some third-party synthesis tools can use a netlist that contains only the structure of the MegaCore function, but not detailed logic, to optimize performance of the design that contains the MegaCore function. If your synthesis tool supports this feature, turn on **Generate netlist**.

- 3. Click **Next** (or the **Summary** tab) to display the **Summary** page.

#### **Generating Files**

You can use the check boxes on the **Summary** page to enable or disable the generation of specified files. A gray checkmark indicates a file that is automatically generated; a red checkmark indicates an optional file.

You can click **Back** to display the previous page, or click **Parameters Settings**, **EDA**, or **Summary**, to change any of the MegaWizard options.

To generate the files, follow these steps:

1. Turn on the files you wish to generate.

At this stage, you can still click **Back** to display any of the other pages in the MegaWizard Plug-In Manager to change any of the parameters.

2. To generate the specified files and close the MegaWizard Plug-In Manager, click Finish.

The generation phase may take several minutes to complete.

The Quartus II IP File (.qip) is a file generated by the parameter editor, and contains information about the generated IP core. You are prompted to add this .qip file to the current Quartus II project at the time of file generation. In most cases, the .qip file contains all of the necessary assignments and information required to process the core or system in the Quartus II compiler. Generally, a single .qip file is generated for each MegaCore function or system in the Quartus II compiler.

3. Click **Exit** to close the **Generation** window.

Table 2–1 describes the generated files and other files that may be in your project directory. The names and types of files specified in the MegaWizard Plug-In Manager report vary based on whether you created your design with VHDL or Verilog HDL.

Table 2-1. Generated Files

| Extension                                       | Description                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <variation name="">.v or .vhd</variation>       | A MegaCore function variation file, which defines a VHDL or Verilog HDL description of the custom MegaCore function. Instantiate the entity defined by this file inside of your design. Include this file when compiling your design in the Quartus II software.                                                     |

| <variation name="">.cmp</variation>             | A VHDL component declaration file for the MegaCore function variation. Add the contents of this file to any VHDL architecture that instantiates the MegaCore function.                                                                                                                                               |

| <variation name="">.bsf</variation>             | Quartus II symbol file for the MegaCore function variation. You can use this file in the Quartus II block diagram editor.                                                                                                                                                                                            |

| <variation name="">.html</variation>            | MegaCore function report file.                                                                                                                                                                                                                                                                                       |

| <variation name="">.ppf</variation>             | This XML file describes the MegaCore pin attributes to the Quartus II Pin Planner.  MegaCore pin attributes include pin direction, location, I/O standard assignments, and drive strength. If you launch IP Toolbench outside of the Pin Planner application, you must explicitly load this file to use Pin Planner. |

| <variation name="">_sdi.sdc</variation>         | Contains timing constraints for your SDI variation.                                                                                                                                                                                                                                                                  |

| <variation name="">_constraints.tcl</variation> | Quartus II file that sets the Quartus II to use TimeQuest timing analyzer and patches the generated <b>.sdc</b> script with a new clock name. If your top-level design clock pin names do not match the default clock pin names or a prefixed version, edit the assignments in this file.                            |

| <variation name="">.vo or .vho</variation>      | VHDL or Verilog HDL IP functional simulation model.                                                                                                                                                                                                                                                                  |

| <variation name="">_bb.v</variation>            | A Verilog HDL black-box file for the MegaCore function variation. Use this file when using a third-party EDA tool to synthesize your design.                                                                                                                                                                         |

| <variation name="">.qip</variation>             | Contains Quartus II project information for your MegaCore function variations.                                                                                                                                                                                                                                       |

You can now integrate your custom MegaCore function variation into your design, simulate, and compile.

# **Simulating the Design**

This section describes the following simulation techniques:

- Simulate with IP Functional Simulation Models

- Simulating with the ModelSim Simulator

- Simulating in Third-Party Simulation Tools Using NativeLink

#### **Testbench**

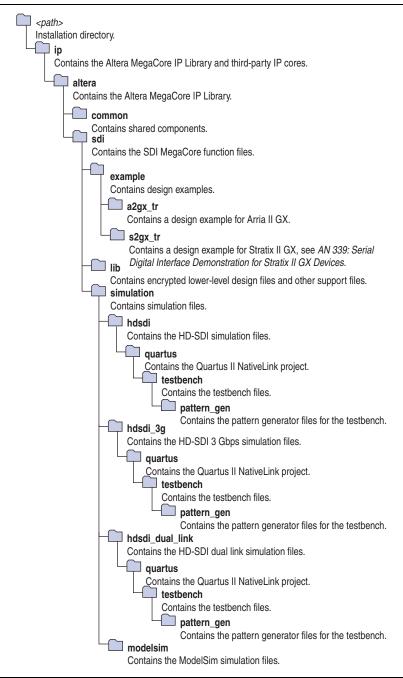

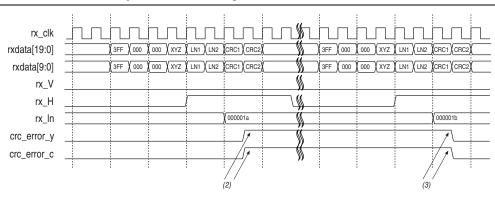

In general, all testbenches are constructed in such a way that the serial transmit data is looped back to receiver. Figure 2–2 shows how the serial transmit data is looped back to the receiver in the testbench.

Figure 2-2. General Simulation Testbench

Note to Figure 2-2:

(1) For dual or triple standard only.

A testbench basically consists of transmit test and receive test. The transmit test accepts the same serial data as the receive device under test (DUT), deserializes and decodes the transmitted data, and computes the number of time reference signals (TRS) seen. The receive test verifies the features that are supported by the SDI receiver by monitoring the received data, status bits, line numbering and other related features.

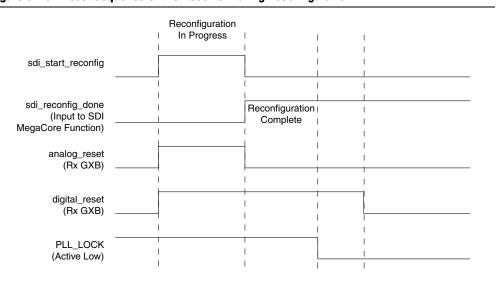

For dual and triple standard modes, the SDI receiver requires reconfiguration. The SDI receiver reconfigures using transceiver dynamic reconfiguration to perform autodetection and locking to different SDI video standards. For more details about transceiver dynamic reconfiguration, refer to "Transceiver Dynamic Reconfiguration for Dual Standard and Triple Standard Receivers" on page 3–27.

#### **Simulate with IP Functional Simulation Models**

You can simulate your design using the MegaWizard-generated VHDL and Verilog HDL IP functional simulation models.

You can use the IP functional simulation model with any Altera-supported VHDL or Verilog HDL simulator.

To use the IP functional simulation model that you created in "Setting Up Simulation" on page 2–6, create a suitable testbench.

For more information about IP functional simulation models, refer to the Simulating *Altera Designs* chapter in volume 3 of the *Quartus II Handbook*.

#### Simulating with the ModelSim Simulator

For Arria and Stratix series of devices, Altera provides two fixed testbenches as examples in the **simulation\modelsim\**<*video standard*>\**modelsim** directory, where <video standard> is hdsdi or hdsdi\_dual\_link. The testbenches instantiate the design and test the HD-SDI or dual link mode of operation. To use one of these testbenches with the ModelSim®-Altera simulator, follow these steps:

1. In a text editor, open the simulation batch file, **simulation\modelsim\**<*video* standard>\modelsim\sdi\_sim.bat. Edit it to point to your installation of the ModelSim-Altera simulator and the Quartus II software, and edit the path:

```

set PATH = %MODELSIM_DIR%\win32aloem

set QUARTUS ROOTDIR=c:\altera\81\quartus

```

For example, edit QUARTUS ROOTDIR=/tools/acds/11.0/157/linux32/quartus.

Where *<video standard>* is **hdsdi** or **hdsdi\_dual\_link**.

- 2. Start the ModelSim-Altera simulator.

- 3. Run sdi sim.bat in the simulation\modelsim\<video standard>\modelsim directory. This file compiles the design and starts the ModelSim-Altera simulator. A selection of signals appears on the waveform viewer. The simulation runs automatically, providing a pass/fail indication on completion.

For Cyclone IV GX devices, Altera provides two new fixed testbenches in the simulation\modelsim\<video standard>\<DPRIO mode>\modelsim directory, where <video standard>\<DPRIO mode> is trsdi\_c4gx\channel\_reconfig or trsdi\_c4gx\pll\_reconfig. The testbenches instantiate the design and test the triple standard mode of operation using Cyclone IV GX devices. The testbenches also demonstrate the transceiver dynamic reconfiguration with channel and phase-locked loop (PLL) reconfiguration modes. To use one of these testbenches with the ModelSim-Altera simulator, follow these steps:

1. In a text editor, open the simulation .do file, simulation\modelsim\<video standard>\<DPRIO mode>\modelsim\sdi sim.do. Edit it to point to your installation of the ModelSim-Altera simulator, and edit the path:

set QUARTUS ROOTDIR = C:\altera\<version>\quartus

Where *<version>* is the version of the Quartus II software you are using.

- 2. Start the ModelSim-Altera simulator.

- 3. Run **sdi sim.do** in the **simulation\modelsim\**<*video standard*>\<*DPRIO mode*>\**modelsim** directory. This file compiles the design and starts the ModelSim-Altera simulator. A selection of signals appears on the waveform viewer.

To test the transmitter operation, the testbench generates a reference clock and parallel video data. The design encodes and serializes this parallel video data. The serial output is sampled, non-return to zero inverted (NRZI) decoded, descrambled, and then reconstructed into parallel form. The testbench detects the presence of TRS tokens (end of active video (EAV) and start of active video (SAV)) in the output to check the correct operation.

To test the receiver operation, the testbench connects the serial transmitter data to the receiver input. The testbench checks that the receiver achieves word alignment and verifies that the extracted LN is correct.

### Simulating in Third-Party Simulation Tools Using NativeLink

You can perform a simulation in a third-party simulation tool from within the Quartus II software, using NativeLink.

For more information about NativeLink, refer to the Simulating Altera Designs chapter in volume 3 of the Quartus II Handbook.

Altera provides the following three Quartus II projects for use with NativeLink in the ip\altera\sdi\simulation directory:

- HD-SDI in the **hdsdi** directory

- HD-SDI 3 Gbps in the hdsdi\_3g directory

- HD-SDI dual link in the **hdsdi\_dual\_link** directory

- Triple standard SDI in the **trsdi** directory

To set up simulation in the Quartus II software using NativeLink, follow these steps:

- On the File menu, click Open Project. Browse to the desired directory: hdsdi, hdsdi\_3g, hdsdi\_dual\_link, or trsdi.

- 2. Open sdi\_sim.qpf.

- 3. Check that the absolute path to your third-party simulator executable is set. On the Tools menu, click **Options** and select **EDA Tools Options**.

- 4. On the Processing menu, point to **Start** and click **Start Analysis & Elaboration**.

- 5. On the Tools menu, point to **Run EDA Simulation Tool** and click **EDA RTL Simulation**.

## **Specifying Constraints**

You must apply the Altera-provided timing constraint file in Synopsys Design Constraints File (.sdc) format and the additional Tcl Script File (.tcl) to ensure the SDI MegaCore function meets the design timing requirements.

To add the .sdc file to your project, click Add/Remove Files in Project on the Project menu and browse to select <*variation name*>\_sdi.sdc file.

To add the additional .tcl file, you must compile your design and perform post compilation timing analysis using the TimeQuest timing analyzer. On the Assignments menu, click Use TimeQuest Timing Analyzer during compilation, and click OK.

You may have to further edit your scripts if your design requires single channel or multiple channels.

### **Single Channel**

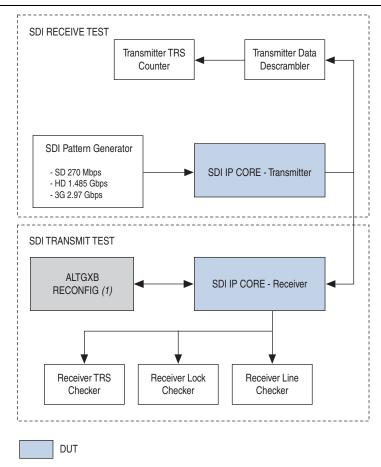

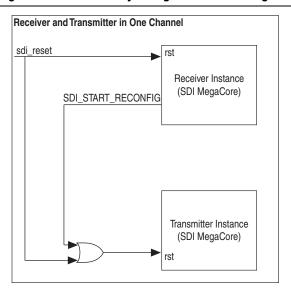

The following section describes what you must do if your design requires a single channel using SDI triple standard transmitter and receiver instances as shown in Figure 2–3 on page 2–11.

Figure 2-3. Instantiating Single Channel of SDI Instances

The SDI instances must have a unique starting channel number if they are merged into a same quad or bank.

To specify the constraints, follow these steps:

Parameterize and generate your SDI MegaCore functions—SDI triple standard transmitter and receiver. 2–12 Chapter 2: Getting Started

Specifying Constraints

2. Edit the Tcl script so that the transceiver top-level reference clock matches the clock pin names that you have chosen for your design, for example tx\_serial\_refclk\_top1. Locate tx\_serial\_refclk\_name in the script and change to tx serial refclk top1.

- 3. Execute the Tcl script to patch the generated .sdc script with the new clock names.

- A back-up copy of the **.sdc** script is created before the patch is made, and any edits that were previously made to the **.sdc** script are preserved.

- 4. Execute the Tcl script in the Quartus II software, and follow these steps:

- a. On the Tools menu, click Tcl script.

- b. Select the Tcl script of the instance SDI triple standard transmitter, and click Run.

- 5. Perform steps 2 to 4 for the SDI triple standard receiver instance.

#### **Multiple Channels**

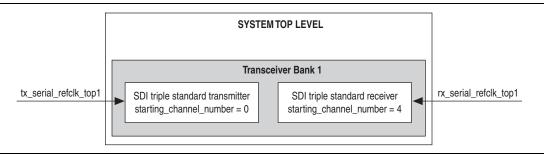

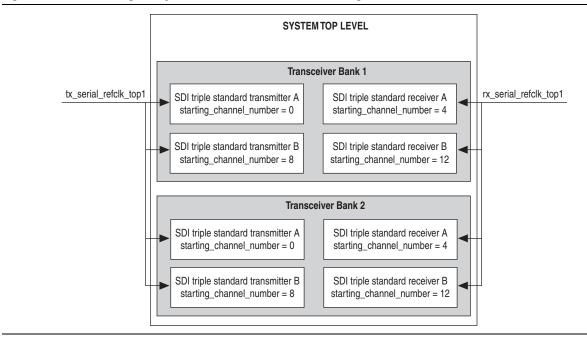

The following section describes what you must do if your design requires multiple channels using four instances of SDI triple standard transmitter and four instances of SDI triple standard receiver. In this case, assume that you must fit all instances into Transceiver Bank 1 and 2 as shown in Figure 2–4, and the SDI instances in both banks have the same video standard. You do not have to regenerate the SDI instances in Transceiver Bank 2.

Figure 2-4. Instantiating Multiple Channels of SDI Instances Sharing Same Reference Clock

To specify the constraints, perform the following steps:

- 1. Parameterize and generate your SDI MegaCore functions—SDI triple standard transmitter A, SDI triple standard transmitter B, SDI triple standard receiver A, and SDI triple standard receiver B—with their unique starting channel number.

- 2. Edit the Tcl script so that the transceiver top-level reference clock matches the name of the clock pin connected to SDI triple standard transmitter A, for example tx\_serial\_refclk\_top1. Locate tx\_serial\_refclk\_name in the script and change to tx serial refclk top1.

- 3. Execute the Tcl script to patch the generated .sdc script with the new clock names.

- A back-up copy of the **.sdc** script is created before the patch is made, and any edits that were previously made to the **.sdc** script are preserved.

- 4. Execute the Tcl script in the Quartus II software, and perform the following steps:

- a. On the Tools menu, click Tcl script.

- b. Select the Tcl script of the instance SDI triple standard transmitter A, and click Run.

- 5. Perform steps 2 to 4 for the other three instances.

SYSTEM TOP LEVEL Transceiver Bank 1 tx\_serial\_refclk\_top1 rx\_serial\_refclk\_top1 SDI triple standard transmitter A SDI triple standard receiver A starting\_channel\_number = 4 starting\_channel\_number = 0 SDI triple standard transmitter B SDI triple standard receiver B starting\_channel\_number = 8 starting\_channel\_number = 12 Transceiver Bank 2 tx\_serial\_refclk\_top2 rx\_serial\_refclk\_top2 SDI triple standard transmitter A SDI triple standard receiver A starting\_channel\_number = 0 starting\_channel\_number = 4 SDI triple standard transmitter B SDI triple standard receiver B starting\_channel\_number = 8 starting\_channel\_number = 12

Figure 2–5. Instantiating Multiple Channels of SDI Instances Sharing Multiple Reference Clocks

To specify constraints for multiple channels of SDI MegaCore function with multiple top-level reference clocks as shown in Figure 2–5, perform the following steps:

- 1. For the SDI instances in Transceiver Bank 1, perform steps 1 to 5 you would do for SDI instances sharing the same reference clock.

- 2. For the SDI instances in Transceiver Bank 2, duplicate an **.sdc** script for SDI triple standard transmitter A and SDI triple standard receiver A in Transceiver Bank 2.

You are not required to duplicate .sdc script for SDI triple standard transmitter B and SDI triple standard receiver B in Transceiver Bank 2. Instances with same video standard can share an .sdc script.

- 3. Edit the .sdc script so that the reference clock name matches the name of the clock pin connected to SDI triple standard transmitter A, for example tx\_serial\_refclk\_top2. Locate tx\_serial\_refclk\_name in the script and change to tx serial refclk top2.

- 4. Edit another .sdc script so that the reference clock name matches the name of the clock pin connected to SDI triple standard receiver A, for example rx\_serial\_refclk\_top2. Locate set rx\_serial\_refclk\_name in the script and change to rx\_serial\_refclk\_top2.

- 5. Add these two duplicate **.sdc** scripts to your project. On the Project menu, click **Add/Remove Files in Project** and browse to select the scripts.

## **Compiling the Design**

You can use the Quartus II software to compile your design. For instructions about performing compilation, refer to Quartus II Help.

You can find an example design using an SDI MegaCore function in the **ip/sdi/example** directory. This design is targeted at the Stratix II GX audio video development kit.

For more information about the example design, refer to *AN 339: Serial Digital Interface Demonstration for Stratix II GX Devices*, and for information about the development kit, refer to *Audio Video Development Kit*, *Stratix II GX Edition*.

## **Programming a Device**

After you have compiled the example design, you can program your targeted Altera device to verify the design in hardware.

With Altera's free OpenCore Plus evaluation feature, you can evaluate the SDI MegaCore function before you obtain a license. OpenCore Plus evaluation allows you to generate an IP functional simulation model, and produce a time-limited programming file.

For more information about OpenCore Plus hardware evaluation using the SDI MegaCore function, refer to "OpenCore Plus Evaluation" on page 1–5, "OpenCore Plus Time-Out Behavior" on page 3–39, and *AN 320: OpenCore Plus Evaluation of Megafunctions*.

## **Setting Up Licensing**

You must purchase a license for the MegaCore function only when you are completely satisfied with its functionality and performance and want to take your design to production.

After you purchase a license for SDI MegaCore function, you can request a license file from the Altera website at www.altera.com/licensing and install it on your computer. When you request a license file, Altera emails you a **license.dat** file. If you do not have Internet access, contact your local Altera representative.

2–16 Chapter 2: Getting Started

Setting Up Licensing

## 3. Functional Description

The SDI MegaCore function implements a receiver, transmitter, or full-duplex interface. The SDI MegaCore function can handle SD, HD, and/or 3G SDIs.

The SDI MegaCore function consists of the following elements:

- Protocol blocks

- SDI receiver

- SDI transmitter

- A transceiver

- A transceiver controller

In the MegaWizard Plug-In Manager, you can specify either protocol or transceiver blocks or both for your design. For example, if you have multiple protocol blocks in a design, you can multiplex them into one transceiver. The transceiver can be either a soft-logic implementation or a GX transceiver.

### **Block Description**

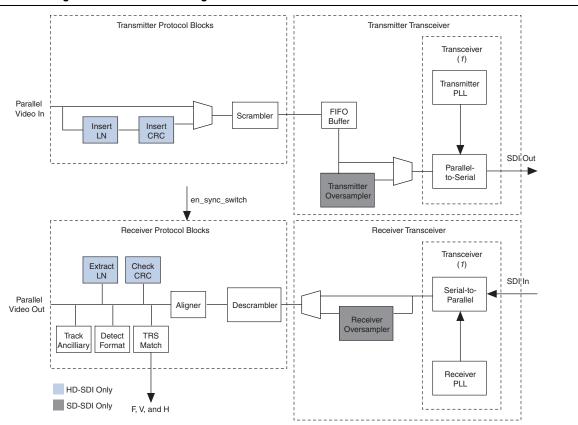

Figure 3–1 shows the SDI MegaCore function block diagram.

Figure 3-1. SDI MegaCore Function Block Diagram

#### Note to Figure 3–1:

(1) For SD-SDI designs only, you can have a soft-logic implementation of the transceiver.

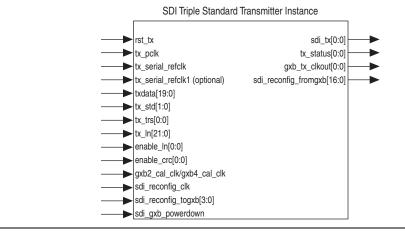

#### **Transmitter**

The transmitter contains the following elements:

- SD/HD-SDI transmitter scrambler

- HD-SDI transmitter data formatter, which includes a CRC and LN insertion

- Transceiver, plus control, and interface logic with multirate (dual or triple standard) SD/HD-SDI transmitter operation

- Transmitter clock multiplexer (optional)

The transmitter performs the following functions:

- HD-SDI LN insertion

- HD-SDI CRC generation and insertion

- Scrambling and NRZI coding

Internal switching between two reference clock signals in the transmitter block. This feature is optional and only available for Arria II GZ, Stratix IV GX, and HardCopy IV devices.

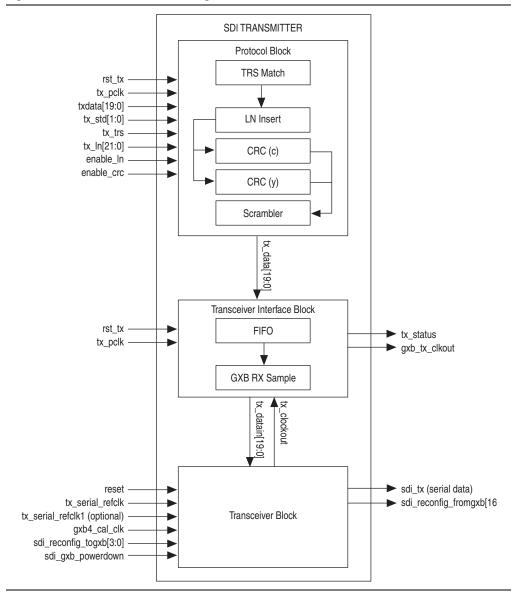

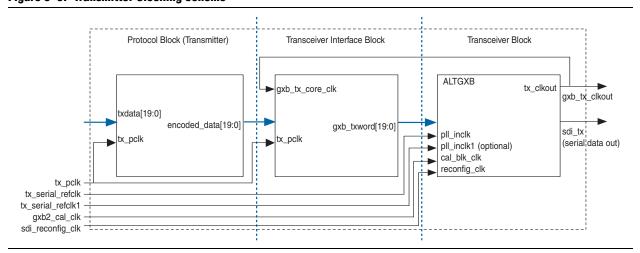

Figure 3–2 shows the top-level block diagram for the SDI transmitter.

Figure 3-2. SDI Transmitter Block Diagram

For HD-SDI, the transmitter accepts 20-bit parallel video data; for SD-SDI, 10-bit parallel data. For txdata bus definition, refer to Table 3–16 on page 3–41.

Table 3–1 lists the bit allocation for txdata.

Table 3-1. Bit Allocation for txdata for Supported Video Standards

| txdata  | SD-SDI                    | HD-SDI | 3G-SDI Level A | 3G-SDI Level B     |

|---------|---------------------------|--------|----------------|--------------------|

| [19:10] | Unused                    | Υ      | Υ              | Cb, Y, Cr, Y       |

|         |                           |        |                | multiplex (link A) |

| [9:0]   | Cb, Y, Cr, Y<br>multiplex | С      | С              | Cb, Y, Cr, Y       |

|         |                           |        |                | multiplex (link B) |

For HD-SDI operation, the current video line number is inserted at the appropriate point in each line. A CRC is also calculated and inserted for the luma and chroma channels.

The parallel video data is scrambled and NRZI encoded according to the SDI specification.

The transceiver converts the encoded parallel data into the high-speed serial output (parallel-to-serial conversion).

#### **HD-SDI LN Insertion**

SMPTE292M section 5.4 defines the format of two words that are included in each HD-SDI video line to indicate the current line number. The HD-SDI LN insertion module takes the lower 11-bit  $tx_1n$ , and formats and inserts it as two words in the output data. The HD-SDI LN insertion module accepts the current line number as an input.

For more information about the line insertion for other video standards, refer to the description for tx ln signal in Table 3–16 on page 3–41.

The LN words (LN0 and LN1) overwrite the two words that follow the "XYZ" word of the EAV TRS sequence. The same value is included in the luma and chroma channels.

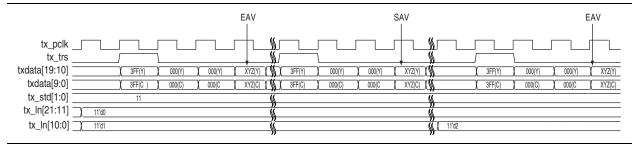

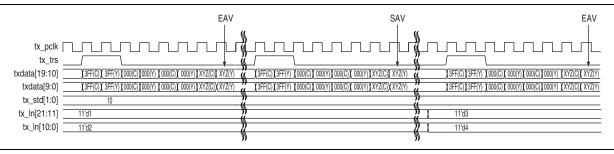

For correct LN insertion, you must assert the tx\_trs signal must be asserted for the first word of both EAV and SAV TRSs (refer to Figure 3–31 on page 3–47 and Figure 3–32 on page 3–48).

If the system does not know the line number, you can implement logic to detect the output video format and then determine the current line. This function is outside the scope of this SDI MegaCore function.

#### **HD-SDI CRC Generation and Insertion**

SMPTE292M section 5.5 defines a CRC that is included in the chroma and luma channels for each HD-SDI video line. The HD-SDI CRC module generates, formats, and inserts the required CRC in the output data.

The HD-SDI CRC module identifies the words that you must include in the CRC calculation, and also determines where you must insert the words in the output data. The formatted CRC data words (YCRO and YCR1 for the luma channel, CCRO and CCR1 for the chroma channel) overwrite the two words that follow the line number words after the EAV. A separate calculation is provided for the luma and chroma channels.

The CRC is calculated for all words in the active digital line, starting with the first active word line and finishing with the final word of the line number (LN1). The initial value of the CRC is set to zero, then the polynomial generator equation  $CRC(X) = X^{18} + X^5 + X^4 + 1$  is applied.

The HD-SDI CRC module implements the CRC calculation by iteratively applying the polynomial generator equation to each bit of the output data, processing the LSB first.

For correct CRC generation and insertion, the tx\_trs signal must be asserted for the first word of both EAV and SAV TRS (refer to Figure 3–31 on page 3–47 and Figure 3–32 on page 3–48).

#### **Scrambling and NRZI Coding**

SMPTE292M section 5 and SMPTE292M section 7 define a common channel coding that is used for both SDI and HD-SDI. This channel coding consists of a scrambling function ( $G_1(X) = X^9 + X^4 + 1$ ) followed by NRZI encoding ( $G_2(X) = X + 1$ ). The scrambling module implements this channel coding. You can configure the module to process either 10-bit or 20-bit parallel data.

The scrambling module implements the channel coding by iteratively applying the scrambling and NRZI encoding algorithm to each bit of the output data, processing the LSB first. Figure C.1 of *SMPTE259M* shows how the algorithm is implemented.

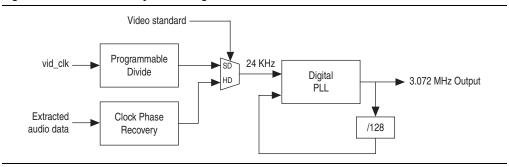

#### **Transceiver Clock**

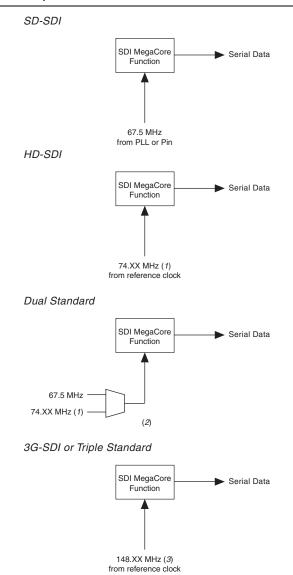

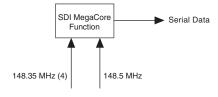

Figure 3–3 shows the clocking scheme for the transmitter.

The tx\_serial\_refclk1 is an optional port that is enabled when you turn on the **Enable TX PLL select for 1/1.000 and 1/1.001 data rate reconfiguration** in the SDI parameter editor.

Figure 3-3. Transmitter Clocking Scheme

#### **Receiver**

The receiver contains the following elements:

- Transceiver, plus control, and interface logic with multirate (dual or triple standard) SD/HD-SDI receiver operation

- SD/HD-SDI receiver descrambler and word aligner

- HD-SDI receiver CRC and LN extractor

- Receiver framing, with extraction of video timing signals

- Identification and tracking of ancillary data

The SDI receiver consists of the following functions:

- NRZI decoding and descrambling

- Word alignment

- Video timing flags extraction

- RP168 switching compliance

- HD-SDI LN extraction

- HD-SDI CRC

- Accessing transceiver

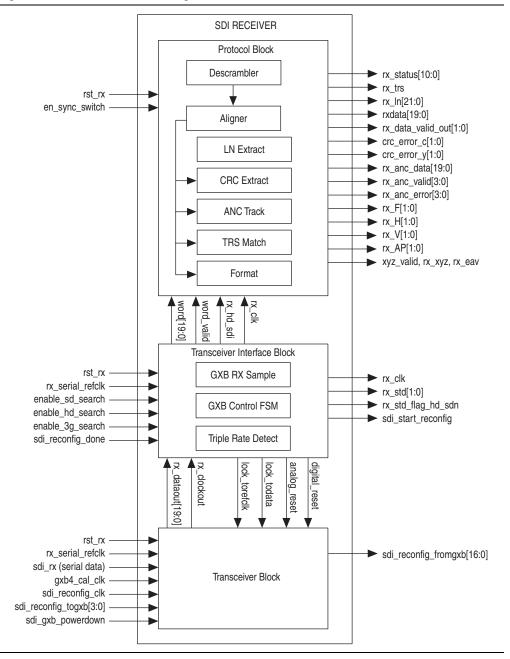

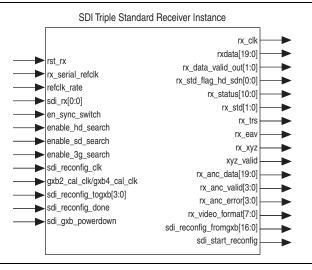

Figure 3–4 shows the top-level block diagram for the SDI receiver.

Figure 3-4. SDI Receiver Block Diagram

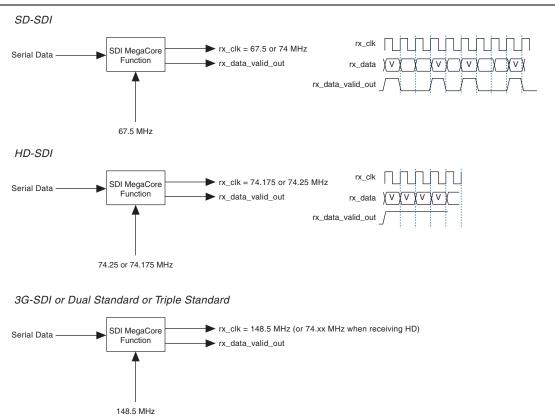

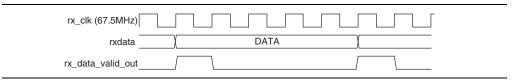

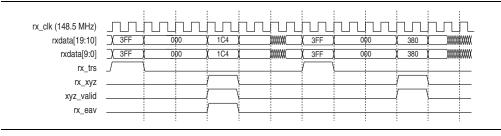

The received data is NRZI decoded and descrambled and then presented as a word-aligned parallel output—20 bit for HD-SDI; 10 bit for SD-SDI (refer to Table 3–16 on page 3–41 for rxdata bus definition).

Table 3–2 lists the bit allocation for rxdata.

Table 3-2. Bit Allocation for rxdata for Supported Video Standards

| rxdata  | SD-SDI       | HD-SDI | 3G-SDI Level A | 3G-SDI Level B     |

|---------|--------------|--------|----------------|--------------------|

| [19:10] | Unused       | V      | V              | Cb, Y, Cr, Y       |

| [19.10] | Onuseu       | 1      | 1              | multiplex (link A) |

| 10.01   | Cb, Y, Cr, Y | C      | C              | Cb, Y, Cr, Y       |

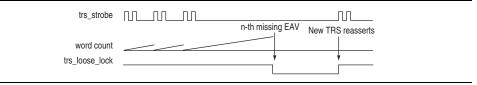

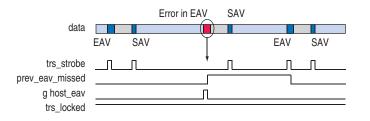

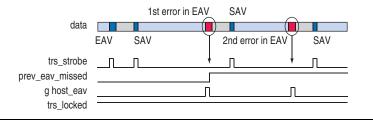

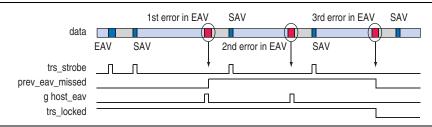

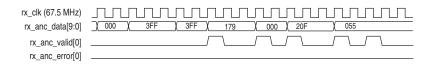

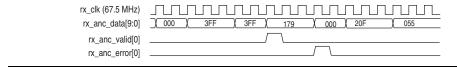

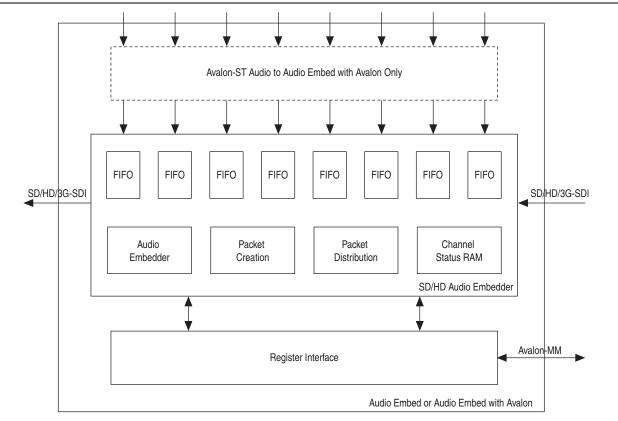

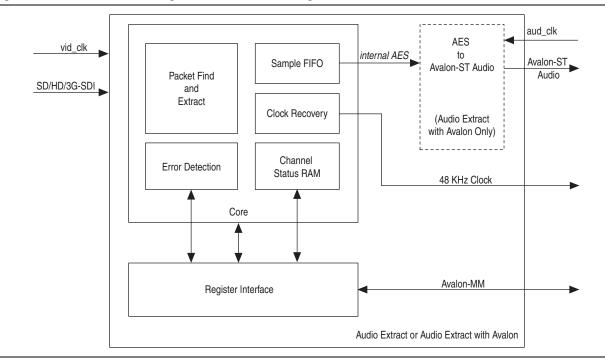

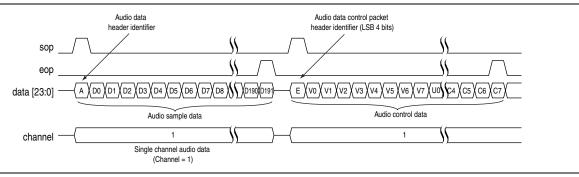

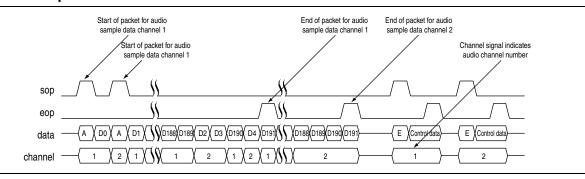

| [9:0]   | multiplex    | U      | U              | multiplex (link B) |